## UC Davis UC Davis Electronic Theses and Dissertations

### Title

A Search for Dark Matter and Investigations in Discrimination Between Neutrons and Gamma-rays

**Permalink** https://escholarship.org/uc/item/3d81x61t

**Author** Johnson, Jyothisraj

Publication Date 2022

Peer reviewed|Thesis/dissertation

#### A Search for Dark Matter and Investigations in Discrimination Between Neutrons and Gamma-rays

By

#### JYOTHISRAJ JOHNSON DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in

Physics

#### in the

#### OFFICE OF GRADUATE STUDIES

of the

#### UNIVERSITY OF CALIFORNIA

DAVIS

Approved:

S. Mani Tripathi, Chair

Michael Mulhearn

Eric Prebys

Committee in Charge

2022

## Abstract

Several independent studies have provided evidence supporting a cold, non-baryonic, nonluminous component of the universe, which is colloquially referred to as dark matter. Weakly interacting massive particles (WIMPs) are a well-motivated candidate to describe the particle nature of this component of the universe. There are several approaches to searching for evidence of these particles. This dissertation focuses on LUX-ZEPLIN (LZ), a direct dark matter search using a dual-phase xenon time projection chamber (TPC). Standard searches for WIMP recoils off xenon nuclei assume a spin-independent or spin-dependent interaction in the zero-momentum limit. This work focuses on a more general interaction basis derived from a non-relativistic effective field theory (EFT) approach to WIMP-nucleus interactions. More specifically, we set limits on the coupling strengths for the fourteen operators that form the basis of inelastic WIMP-nucleus interactions in the non-relativistic regime. The limitsetting analysis was conducted using an extended, unbinned profile likelihood ratio (PLR) method. World-leading limits are achieved for the lower mass-splitting values considered in the analysis.

The second half of this dissertation expands on a key requirement in such dark matter searches: discrimination between nuclear (NR) and electronic recoil (ER) events. One of many methods to achieve this capability is pulse shape discrimination (PSD). Although xenon is not a suitable detection medium to take advantage of this technique, plastic/organic scintillators exhibit this capability. This subclass of scintillators are widely used in the radiation detection and nuclear security fields. This dissertation presents the design of and results from a custom SiPM + Scintillator test bed. The setup was used to study the PSD capability of commercially available plastic/organic scintillators when optically coupled to silicon photomultipliers (SiPMs). Also discussed are the results of a feasibility study, conducted using data taken with the test bed, on the design of a prototype fully custom application specific integrated circuit (ASIC) developed to read out signals from plastic/organic scintillators using SiPMs and provide real-time PSD via a custom analog circuit design on the ASIC. The end goal for this ASIC is integration into a compact, portable, and segmented neutron scatter camera design. The design, simulation, and initial testing results for the chip are presented. Condensed versions of the data sheets are provided as appendices for both versions of the chip that have currently been fabricated. To my parents,

who immigrated to the United States 21 years ago with five-year-old me and my ten-month-old brother in tow and successfully made a new life in a completely foreign country while raising young kids. Thank you for encouraging me to pursue my interests and supporting me in paving my own path in life.

# Contents

| C             | onter | nts         |                  |                      |                      |       |                 |      |      |                   |               |                      |      |              |                           |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | $\mathbf{V}$ |

|---------------|-------|-------------|------------------|----------------------|----------------------|-------|-----------------|------|------|-------------------|---------------|----------------------|------|--------------|---------------------------|--------------|--------------|----|---|-----|-----|-----|-----|-----|----|---|-----|-----|-----|----|----|--------------|

| $\mathbf{Li}$ | st of | Figures     |                  |                      |                      |       |                 |      |      |                   |               |                      |      |              |                           |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | ix           |

| $\mathbf{Li}$ | st of | Tables      |                  |                      |                      |       |                 |      |      |                   |               |                      |      |              |                           |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | xix          |

| 1             | Intr  | oduction to | $\mathbf{D}_{i}$ | aı                   | $\mathbf{rk}$        | М     | 1a <sup>1</sup> | itt  | er   | r                 |               |                      |      |              |                           |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 1            |

|               | 1.1   | Missing Mat | ter              | i i                  | n t                  | he    | e U             | Jn   | iv   | ers               | se            |                      |      | •            |                           |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 1            |

|               |       | 1.1.1 Gala  | ctic             | сI                   | Ro                   | tat   | tio             | m    | С    | ur                | ves           | 5                    |      |              |                           |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 2            |

|               |       | 1.1.2 Inter | acti             | in                   | ıg (                 | Ga    | ıla             | ιxy  | y (  | Clı               | ust           | $\operatorname{ers}$ |      |              |                           |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 3            |

|               |       | 1.1.3 The   | $\cos$           | sm                   | nic                  | Μ     | lic             | cro  | )Wa  | ave               | еE            | Bac                  | kgr  | ou           | nd                        |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 4            |

|               | 1.2   | The WIMP    | Mo               | ode                  | lel <sup>·</sup>     | for   | r N             | Mis  | issi | ing               | g/I           | Dar                  | k I  | Лa           | tte                       | er           |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 8            |

|               |       | 1.2.1 Back  | gro              | oui                  | nd                   | on    | n V             | W    | ΊN   | ЛP                | <b>`</b> s .  |                      |      |              |                           |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 8            |

|               |       | 1.2.2 Expe  | rim              | ne                   | enta                 | al S  | Se              | ear  | rch  | hes               | s fo          | or V                 | VII  | MF           | $\mathbf{P}_{\mathbf{S}}$ |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 11           |

|               |       | 1.2.2       | .1               | ]                    | Inc                  | dir€  | ect             | t I: | De   | ete               | ecti          | ion                  | Se   | aro          | che                       | $\mathbf{s}$ |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 11           |

|               |       | 1.2.2       | .2               | (                    | Co                   | ollic | de              | er S | Se   | ear               | che           | es                   |      | •            |                           |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 12           |

|               |       | 1.2.2       | .3               | ]                    | Di                   | rec   | et I            | De   | ete  | ect               | tio           | n S                  | ear  | ch           | es                        |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 12           |

|               |       | 1.2.3 Othe  | r D              | )aı                  | $\operatorname{trk}$ | M     | at              | ste  | er ( | Cə                | and           | lida                 | ates | 3            |                           |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 19           |

|               |       | 1.2.3       | .1               |                      | Ax                   | cior  | ns              | 5.   |      |                   |               |                      |      |              |                           |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 19           |

|               |       | 1.2.3       | .2               | í,                   | Ste                  | əril  | le              | Ne   | eu   | ıtri              | inc           | $\mathbf{S}$         |      | •            |                           |              | •            | •  |   |     |     |     | •   | •   | •  |   | •   |     | •   |    |    | 20           |

| <b>2</b>      | The   | LUX-ZEP     | LIN              | N                    | E                    | xp    | er              | rir  | me   | $\mathbf{en}^{1}$ | t             |                      |      |              |                           |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | <b>21</b>    |

|               | 2.1   | Dual-Phase  | Xer              | no                   | on                   | Tiı   | me              | le J | Pr   | roj               | ject          | t C                  | hai  | mb           | ers                       | 5.           |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 22           |

|               |       | 2.1.1 Signa | al F             | For                  | $\mathbf{rm}$        | ati   | ior             | n i  | in   | X                 | end           | on                   |      | •            |                           |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 22           |

|               |       | 2.1.2 Dual  | -Ph              | nas                  | ıse                  | Ti    | m               | ie ] | Pr   | roj               | ject          | tior                 | n C  | ha           | mł                        | ber          | $\mathbf{s}$ |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 29           |

|               | 2.2   | The LZ Det  | ecto             | or                   |                      |       |                 |      |      | •                 |               |                      |      |              |                           |              |              |    |   |     |     |     |     |     |    |   |     |     |     |    |    | 33           |

|               |       | 2.2.1 Anal  | og l             | El                   | lec                  | tro   | oni             | ics  | s (  | Ch                | air           | 1                    |      | •            |                           |              | •            | •  |   |     |     |     | •   | •   | •  |   |     |     | •   |    |    | 36           |

| 3             | A S   | earch for D | ark              | k ]                  | $\mathbf{M}$         | att   | te              | er   | ba   | ase               | $\mathbf{ed}$ | or                   | ı a  | $\mathbf{n}$ | Ef                        | fec          | eti          | ve | F | `ie | eld | Т   | `he | eo  | ry |   |     |     |     |    |    | 44           |

|               | 3.1   | Limitations | of t             | $^{\mathrm{th}}$     | ne S                 | 3I 8  | an              | nd   | S    | D                 | W             | IM                   | P S  | Sea          | rcl                       | h            |              |    |   |     |     |     |     |     | •  |   |     |     |     |    |    | 44           |

|               | 3.2   | A General E | ffec             | $\operatorname{cti}$ | ive                  | e Fi  | 'iel            | ld   | T    | ſh€               | eor           | уN                   | loc  | lel          | fo                        | r I          | Dai          | rk | М | at  | te  | r-N | Ju  | cle | on | I | ıt€ | ere | ict | io | ns | 45           |

|          | 3.3  | 8                                                                                                            | 9<br>55 |

|----------|------|--------------------------------------------------------------------------------------------------------------|---------|

| 4        | Inel | astic EFT Limits from LZ SR1 Data 7                                                                          | 3       |

|          | 4.1  | Detector Calibrations                                                                                        | '5      |

|          |      | 4.1.1 Position Correction                                                                                    | 6       |

|          |      | 4.1.2 ER and NR Band Calibrations                                                                            | 7       |

|          | 4.2  | Event Selection                                                                                              | '9      |

|          |      | 4.2.1 Data Quality Cuts                                                                                      | 32      |

|          |      | 4.2.2 S2c-based Cut Acceptance                                                                               | 6       |

|          |      | 4.2.3 S1-based Cut Acceptance                                                                                | 3       |

|          |      | 4.2.4 Nuclear Recoil Acceptance                                                                              | 1       |

|          | 4.3  | Background and Signal Models                                                                                 | 4       |

|          |      | 4.3.1 Backgrounds                                                                                            | 4       |

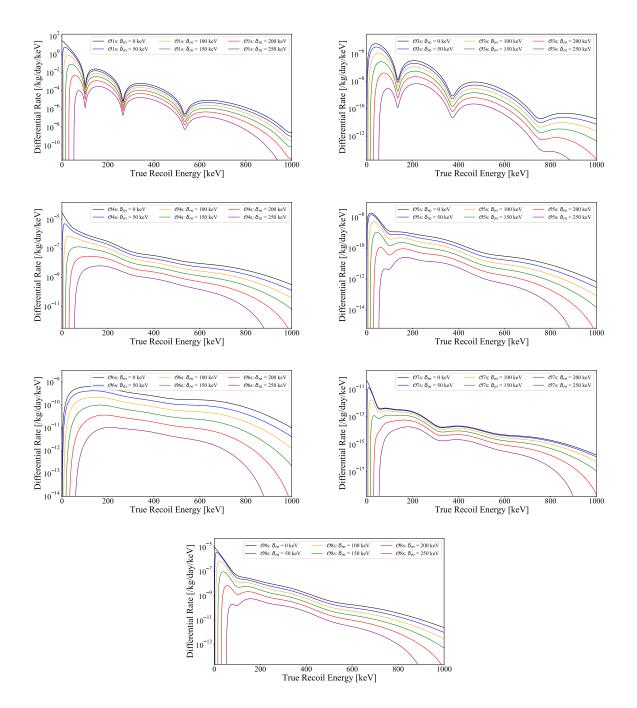

|          |      | 4.3.2 Signal Models                                                                                          | 6       |

|          | 4.4  | Profile Likelihood Ratio for Limit Setting                                                                   | 2       |

|          | 4.5  | SR1 Initial Inelastic EFT Limits                                                                             | 8       |

| <b>5</b> | Stu  | dies in Discriminated Neutron and Gamma Detection 13                                                         | 30      |

| -        | 5.1  | PSD in Organic/Plastic Scintillators                                                                         | 3       |

|          |      | 5.1.1 Origin of PSD Capability 13                                                                            |         |

|          |      | 5.1.2 PSD Results for EJ276 and Stilbene                                                                     | 5       |

|          | 5.2  | SiPMs as Photosensors                                                                                        | 9       |

|          |      | 5.2.1 SiPM Parameters                                                                                        | 3       |

|          |      | 5.2.1.1 Pulse Shape $\ldots$ 14                                                                              | 3       |

|          |      | 5.2.1.2 Fill Factor $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $14$                      | 5       |

|          |      | 5.2.1.3 Breakdown Voltage and Overvoltage                                                                    | 6       |

|          |      | 5.2.1.4 Gain $\ldots$ 14                                                                                     | 6       |

|          |      | 5.2.1.5 Photon Detection Efficiency                                                                          | 7       |

|          |      | 5.2.1.6 Dark Count Rate                                                                                      | 7       |

|          |      | 5.2.1.7 Optical Cross-talk $\ldots \ldots 14$ | 9       |

|          |      | 5.2.1.8 Afterpulsing $\ldots$ 14                                                                             | 9       |

|          |      | 5.2.1.9 Dynamic Range and/or Linearity                                                                       | 0       |

|          |      | 5.2.1.10 Temperature Dependence                                                                              | 1       |

|          |      | 5.2.1.11 A Specific SiPM: The SensL J-series                                                                 | 3       |

|          | 5.3  | Studying PSD Capability of Scintillators Coupled to SiPMs                                                    | 4       |

|          |      | 5.3.1 Trigger and Energy Calibrations                                                                        | 0       |

|          | 5.4  | Neutron Scatter Camera Requirements                                                                          | 6       |

|          |      |                                                                                                              |         |

|          | 5.5  | Design Requirements for the ASIC                                                                             | '3      |

| 6 | Des | ign, Si       | mulations and Testing of PSD_CHIP                      | 195          |

|---|-----|---------------|--------------------------------------------------------|--------------|

|   | 6.1 | The Si        | ingle Channel Signal Chain                             | 199          |

|   |     | 6.1.1         | Custom FOUT Front-end Design                           | 204          |

|   |     |               | 6.1.1.1 The Common Source Amplifier                    | 205          |

|   |     | 6.1.2         | FOUT Triggering Block                                  | 207          |

|   |     | 6.1.3         | FOUT Width Trim Block                                  | 208          |

|   |     | 6.1.4         | Parallel Integration Enable and Hold Line Generation   | 212          |

|   |     | 6.1.5         | Delay Line Generation                                  |              |

|   |     |               | 6.1.5.1 Current Starved Inverter Delay Lines           |              |

|   |     |               | 6.1.5.2 Voltage Ramp Generator Delay Lines             |              |

|   |     |               | 6.1.5.3 Comparison Between the Two Methods             |              |

|   |     | 6.1.6         | Custom SOUT Front-end Design                           | 223          |

|   |     |               | 6.1.6.1 The Issue of Input Capacitance                 |              |

|   |     |               | 6.1.6.2 The Regulated Common Gate Amplifier            |              |

|   |     | 6.1.7         | Parallel Partial and Total Integration Stages          |              |

|   |     |               | 6.1.7.1 A Fully Differential Total Integration Stage   |              |

|   |     |               | 6.1.7.2 A Fully Differential Partial Integration Stage | 233          |

|   |     |               | 6.1.7.3 Integration Enable Pulse Logic                 |              |

|   |     | 6.1.8         | A Fully Differential Subtraction Stage                 |              |

|   |     | 6.1.9         | Final Classification Discriminator                     |              |

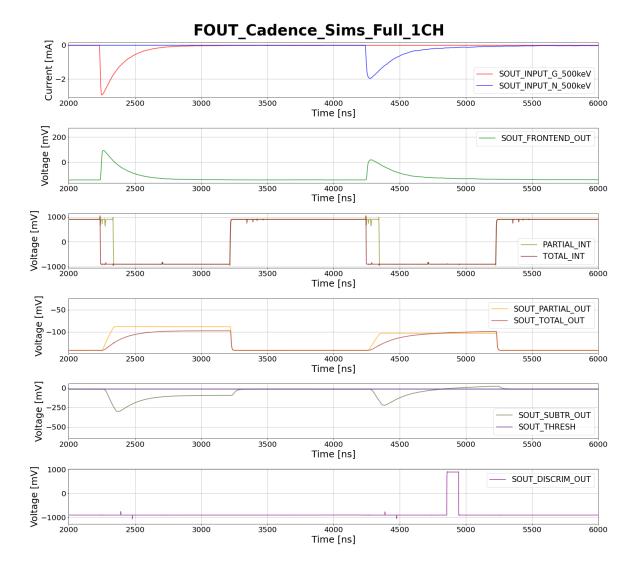

|   | C O |               | Full Channel Simulation                                |              |

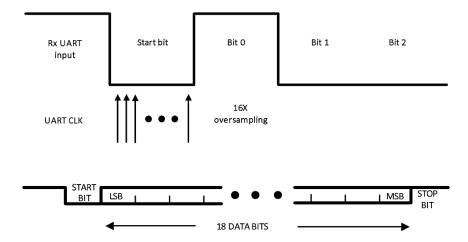

|   | 6.2 | Full C. 6.2.1 | hip Integration                                        | 241          |

|   |     | 0.2.1         | The Digital Core                                       |              |

|   |     | 6.2.2         | Scaling to Four Channels                               |              |

|   |     | 6.2.2         | Digital Test Buses                                     |              |

|   |     | 6.2.3         | Voltage/Current Monitors                               | $244 \\ 245$ |

|   |     | 6.2.1         | Two-Stage Global/Coarse Tunability                     |              |

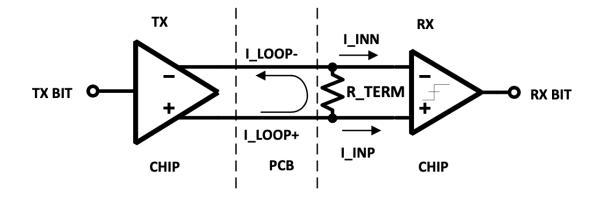

|   |     | 6.2.6         | Digital I/O Using LVDS                                 |              |

|   |     | 6.2.7         | Power Rails and Voltage/Current Biasing                |              |

|   |     | 6.2.8         | A General Overview of Layout Considerations            |              |

|   | 6.3 | Initial       | Testing of PSD_CHIP                                    | 253          |

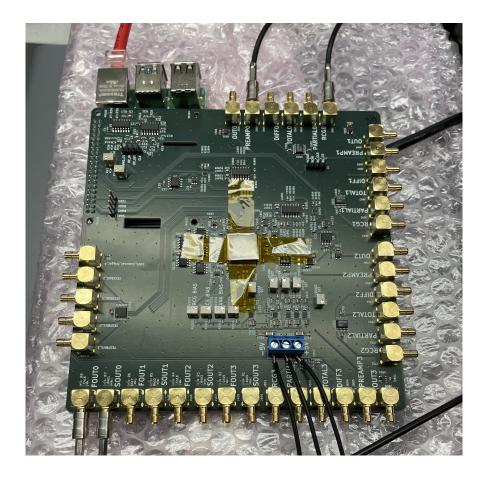

|   |     | 6.3.1         | Custom Test Board Design                               | 253          |

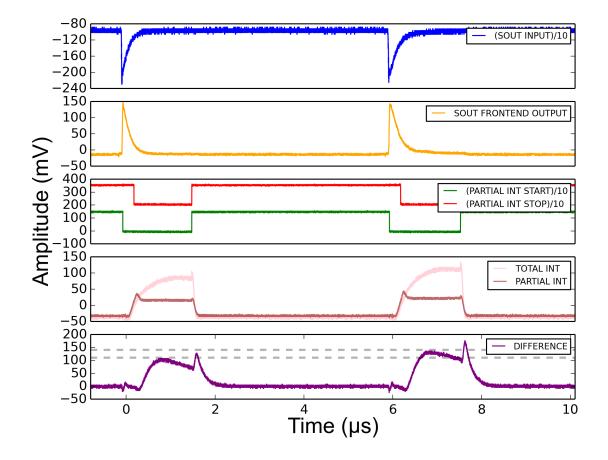

|   |     | 6.3.2         | Initial Results                                        | 256          |

| 7 | Sun | $mary_{/}$    | /Conclusions                                           | 261          |

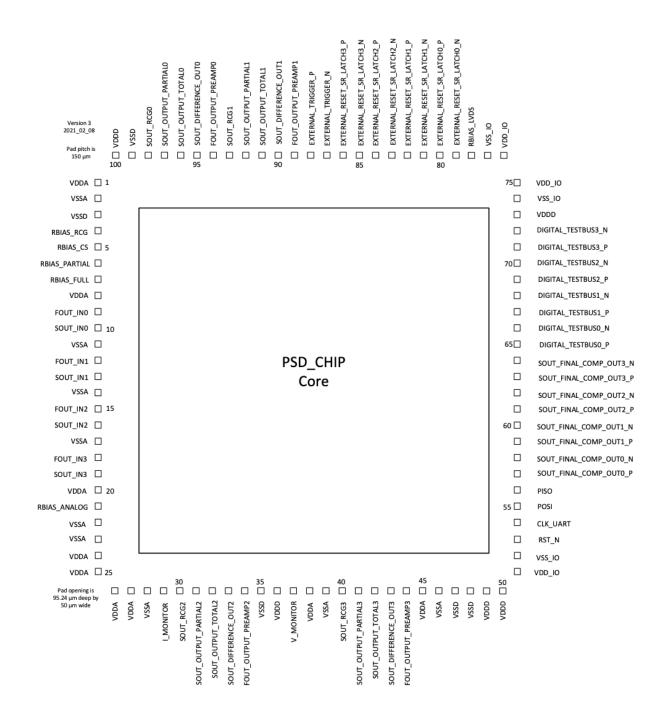

| Α | PSI | ) СНП         | P_V1 Data Sheets                                       | 264          |

|   | A.1 |               | unctions                                               | 264          |

|   | A.2 |               | l I/O Pads                                             |              |

|   | A.3 |               | l Core Registers                                       | 274          |

|   |     | 0             | $\sim$                                                 |              |

|   | A.4 | RBIAS Pads                               |

|---|-----|------------------------------------------|

|   | A.5 | On Chip Voltage and Current DACs         |

|   |     | A.5.1 Voltage DACs                       |

|   |     | A.5.2 Current DACs                       |

|   | A.6 | Digital Test Buses                       |

|   | A.7 | Voltage and Current Monitors             |

|   |     | A.7.1 Voltage Monitor                    |

|   |     | A.7.2 Current Monitor                    |

|   | A.8 | Tunable Resistors                        |

|   |     | A.8.1 Total Integration Tunable Resistor |

|   |     | A.8.2 Subtraction Stage Tunable Resistor |

|   |     |                                          |

| В | PSI | D_CHIP_V2 Data Sheets 297                |

|   | B.1 | Pad Functions    298                     |

|   | B.2 | Digital I/O Pads                         |

|   | B.3 | Digital Core Registers                   |

|   | B.4 | RBIAS Pads    326                        |

|   | B.5 | On Chip Voltage and Current DACs         |

|   |     | B.5.1 Voltage DACs                       |

|   |     | B.5.2 Current DACs                       |

|   | B.6 | Digital Test Buses                       |

|   | B.7 | Voltage and Current Monitors             |

|   |     | B.7.1 Voltage Monitor                    |

|   |     | B.7.2 Current Monitor                    |

|   | B.8 | VRG Delay Line Details                   |

|   | B.9 | Tunable Resistors                        |

|   |     | B.9.1 RCG Tunable Resistor               |

|   |     | B.9.2 Total Integration Tunable Resistor |

|   |     | B.9.3 Subtraction Stage Tunable Resistor |

|   |     |                                          |

|   |     |                                          |

## Bibliography

# List of Figures

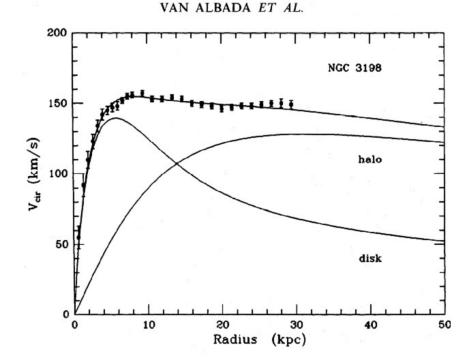

| 1.1 | An example of a fitted rotational curve (for NGC 3198) plotting observed rota-<br>tional velocity as a function of radius from galactic center. The disk and (required)<br>halo contributions are also plotted. Figure from [6]. | 3       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 1.2 | A reconstructed image of the Bullet Cluster. Shown in pink is the x-ray distri-<br>bution of hot gas. Shown in blue is the derived matter distribution profile of the                                                            |         |

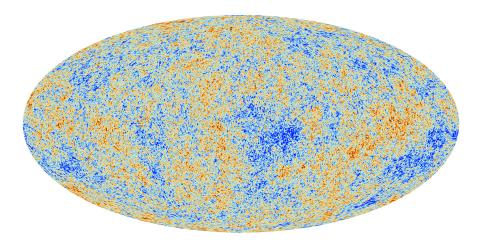

| 1.3 | two galaxy clusters. Figure from the Chandra X-ray Observatory A reconstructed image of the cosmic microwave background from the Planck survey. Warmer (redder) colors show hot spots and cooler (bluer) colors show             | 5       |

|     | cold spots in the background.                                                                                                                                                                                                    | 6       |

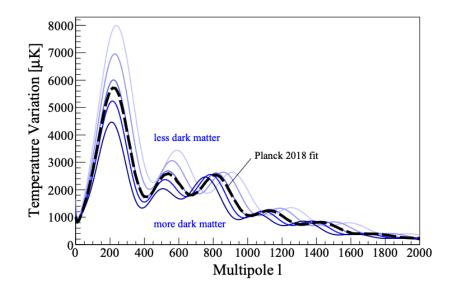

| 1.4 | The calculated power spectrum from Planck is shown in the dashed black line.<br>Simulation results varying dark matter density and the observed shift in peaks                                                                   |         |

|     | is shown. Lighter purple shows less dark matter and darker purple shows more                                                                                                                                                     |         |

|     | dark matter. Figure from $[11]$                                                                                                                                                                                                  | 7       |

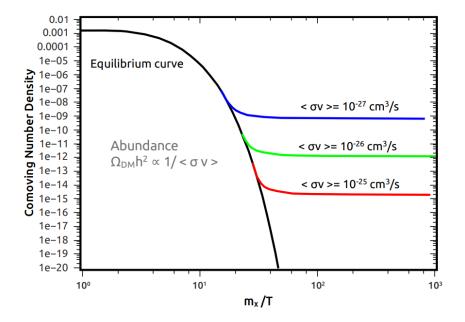

| 1.5 | The co-moving number density is plotted as a function of time (average temper-                                                                                                                                                   |         |

|     | ature) of the universe. Different thermal relic densities for WIMPs are shown                                                                                                                                                    |         |

|     | for various assumed thermally averaged interaction cross sections with the green curve closest to the calculated relic density. Figure from [13]                                                                                 | 9       |

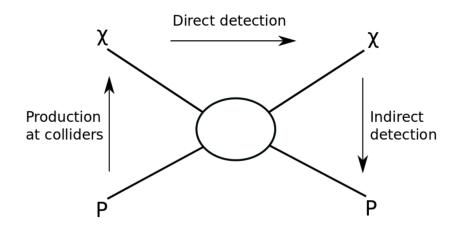

| 1.6 | The various possible detection channels for dark matter, from [15]                                                                                                                                                               | 9<br>10 |

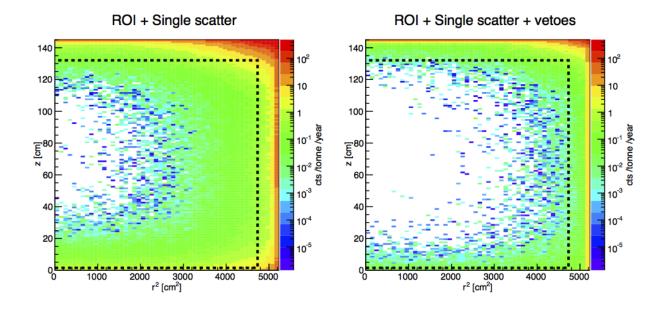

| 2.1 | From [36], the event rate of single scatters in the ROI without (left) and with                                                                                                                                                  |         |

|     | (right) applied vetoes. In both cases, the rate is lowest in the innermost region                                                                                                                                                |         |

|     | of the detector, due to self-shielding                                                                                                                                                                                           | 24      |

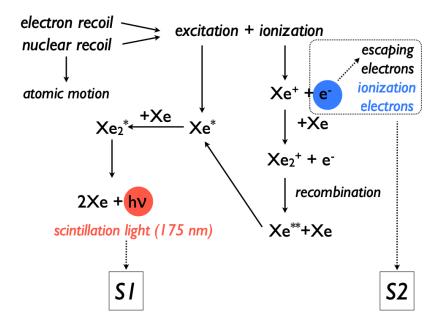

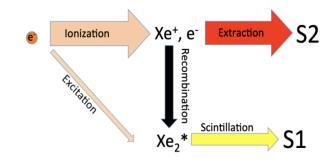

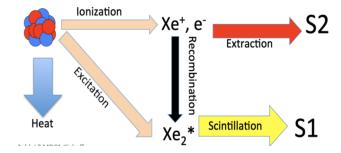

| 2.2 | Signal formation in xenon for both electronic and nuclear recoils, from [37]                                                                                                                                                     | 25      |

| 2.3 | A schematic diagram, which illustrates the scale of each signal formation chan-                                                                                                                                                  |         |

|     | nel in xenon for electronic recoils using width of corresponding arrows. Figure                                                                                                                                                  | 20      |

| 0.4 | courtesy of the LZ collaboration.                                                                                                                                                                                                | 26      |

| 2.4 | A similar diagram for nuclear recoils. Figure courtesy of the LZ collaboration. An interaction event within a dual-phase LXe TPC and the resulting $S1 + S2$                                                                     | 26      |

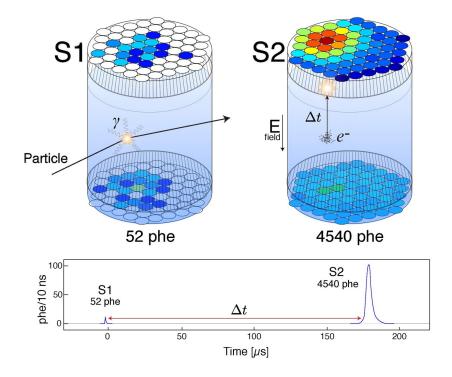

| 2.5 | An interaction event within a dual-phase LXe TPC and the resulting $S1 + S2$<br>waveform. Figure courtesy of the LUX collaboration                                                                                               | 30      |

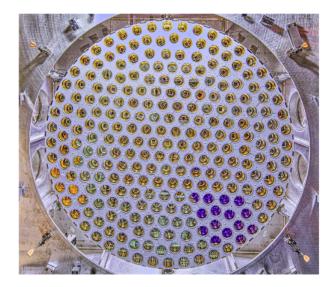

| 2.6 | From [39], a photograph of the top PMT array for LZ, consisting of 253 PMTs.                                                                                                                                                     | 31      |

|     |                                                                                                                                                                                                                                  |         |

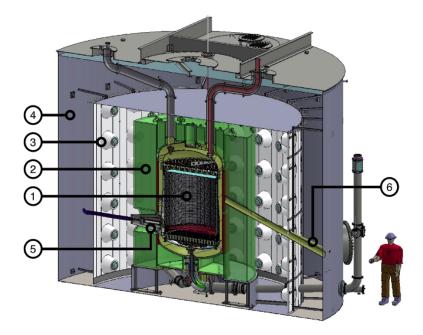

| 2.7  | From [39], the main sub-components of the LZ detector. (1) is the liquid xenon TPC, with a top and bottom array of PMTs. The TPC is contained in a titanium                                                                                                                                                                              |          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | cryostat and surrounded on all sides by a GdLS Outer Detector (2). The cathode                                                                                                                                                                                                                                                           |          |

|      | high voltage connection is made at the lower left (5). The GdLS is monitored                                                                                                                                                                                                                                                             |          |

|      | by 8" PMTs (3) in the water tank (4) which provides shielding for the detector.                                                                                                                                                                                                                                                          |          |

|      | The conduit on the right (6) allows for neutron calibration sources a direct path                                                                                                                                                                                                                                                        |          |

|      | to the inner detector.                                                                                                                                                                                                                                                                                                                   | 34       |

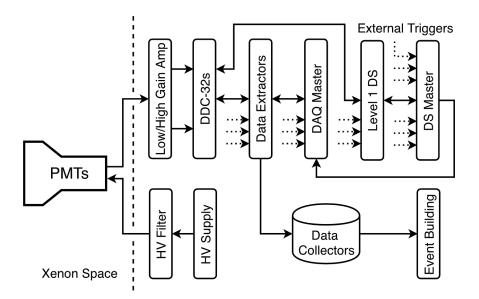

| 2.8  | From [39], a diagram of the full signal processing chain for LZ. The analog elec-<br>tronics chain involves the HV supplies, filters and the amplifier + slow control                                                                                                                                                                    |          |

|      | boards (not shown).                                                                                                                                                                                                                                                                                                                      | 36       |

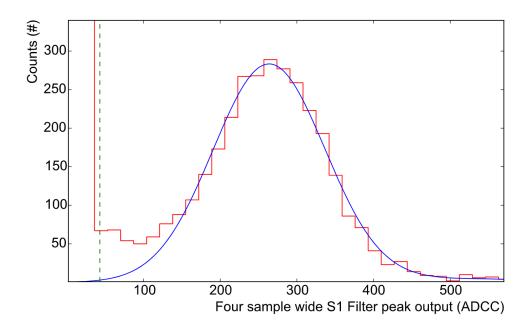

| 2.9  | A histogram of S1 filter peak outputs. The filter threshold is shown as a green dotted line. The calculated SPHE detection efficiency with this threshold is                                                                                                                                                                             |          |

|      | 99.8%. Figure from [39]                                                                                                                                                                                                                                                                                                                  | 37       |

| 2.10 | Photographs of one of the 100 LZ amplifier boards used for initial signal ampli-<br>fication and shaping (Left) and of one of the 25 LZ amplifier crates housing the                                                                                                                                                                     |          |

|      | amplifiers. All of these modules were tested for QA/QC at UC Davis                                                                                                                                                                                                                                                                       | 38       |

| 2.11 |                                                                                                                                                                                                                                                                                                                                          | 00       |

|      | facilitate communication between the amplifiers and Ignition, the primary slow                                                                                                                                                                                                                                                           |          |

|      | control interface.                                                                                                                                                                                                                                                                                                                       | 39       |

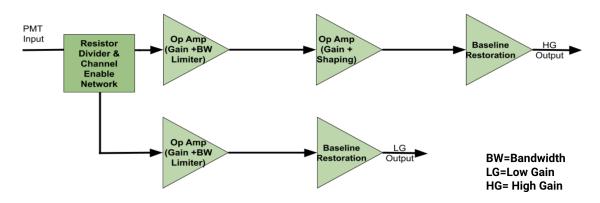

| 2.12 | A system level overview of the main stages of signal progression in a single input                                                                                                                                                                                                                                                       |          |

|      | channel of the LZ amplifier board                                                                                                                                                                                                                                                                                                        | 40       |

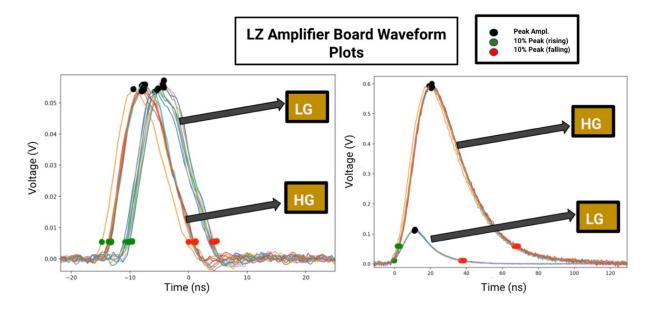

| 2.13 | Digitized outputs of an input test waveform going through the HG and LG chan-<br>nels of one of the amplifier boards from the QA/QC procedure are plotted. The<br>peak amplitude and 10% of peak (rising/falling) locations for the various channels<br>are marked. It is easy to see signal shape and propagation uniformity within the | 10       |

|      | channels                                                                                                                                                                                                                                                                                                                                 | 42       |

| 2.14 | A typical single scatter $(1 \text{ S1} + 1 \text{ S2})$ event within the LZ TPC volume from the Event Viewer. Left inlay zooms into the S1 pulse and the right inlay does the                                                                                                                                                           |          |

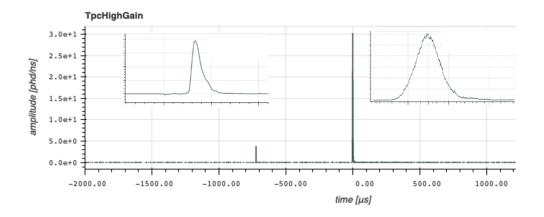

|      | same for the S2 pulse. Event taken from Rn220 calibration data                                                                                                                                                                                                                                                                           | 43       |

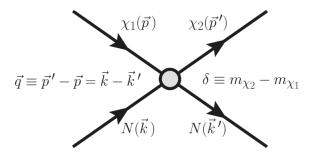

| 3.1  | The general Feynman diagram for inelastic dark matter scattering off a nucleon within a target nucleus [27]                                                                                                                                                                                                                              | 60       |

| 3.2  | within a target nucleus [27]                                                                                                                                                                                                                                                                                                             | 00       |

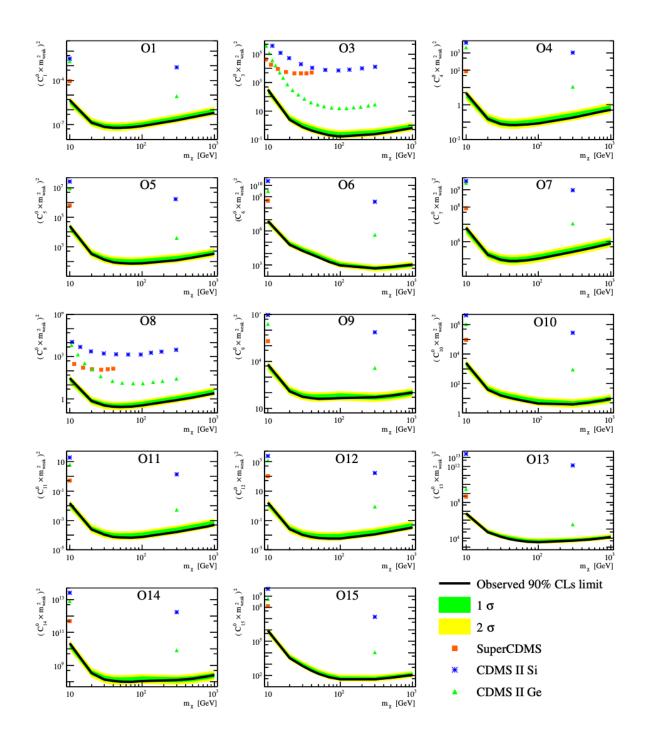

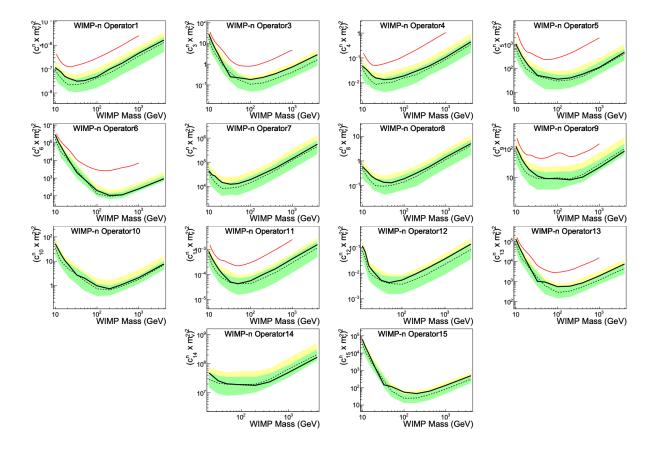

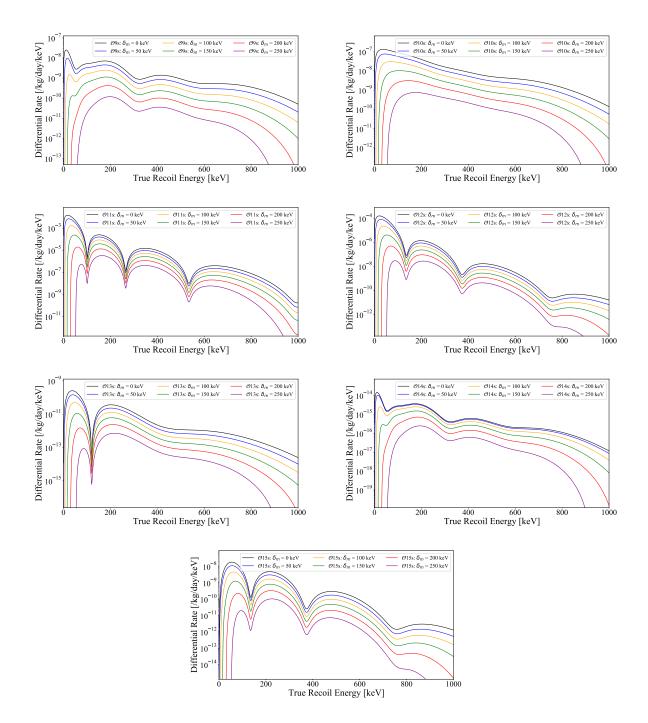

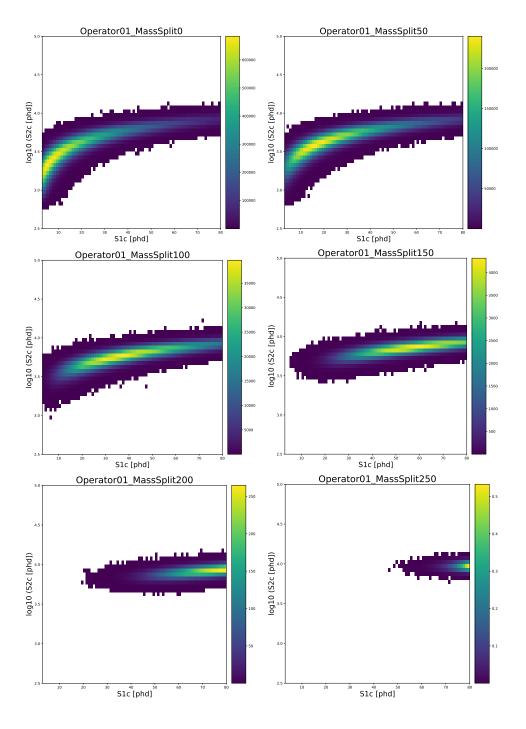

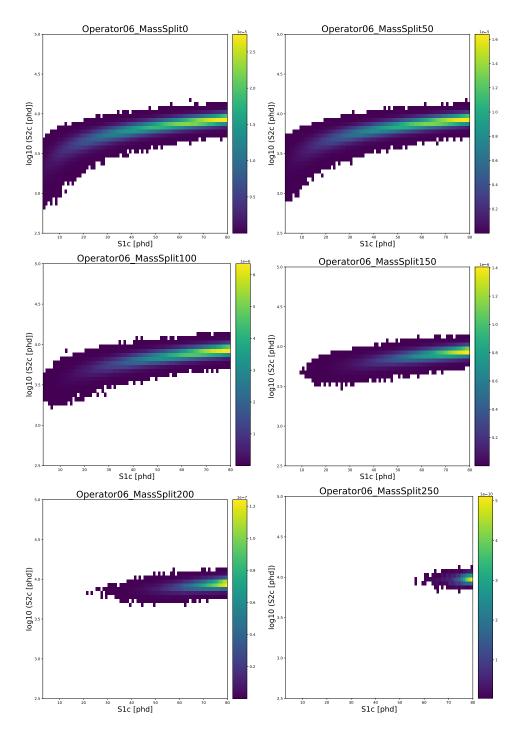

| 3.2  | for each operator are shown                                                                                                                                                                                                                                                                                                              | 68       |

| 3.3  | Results from XENON100's inelastic EFT analysis [44]. Limits on coupling strength                                                                                                                                                                                                                                                         | 00       |

| J.J  | for each operator are shown.                                                                                                                                                                                                                                                                                                             | 69       |

| 24   | Results from LUX's elastic EFT analysis [46]. Limits on coupling strength for                                                                                                                                                                                                                                                            | 09       |

| 3.4  | each operator (WIMP-n) are shown. Solid black lines represent the limit, dashed                                                                                                                                                                                                                                                          |          |

|      | black lines indicate the expected limit, and red lines show limits from previous                                                                                                                                                                                                                                                         |          |

|      | runs. A range of WIMP masses from 10 GeV to 4 TeV are considered for each                                                                                                                                                                                                                                                                | <u> </u> |

|      | operator                                                                                                                                                                                                                                                                                                                                 | 70       |

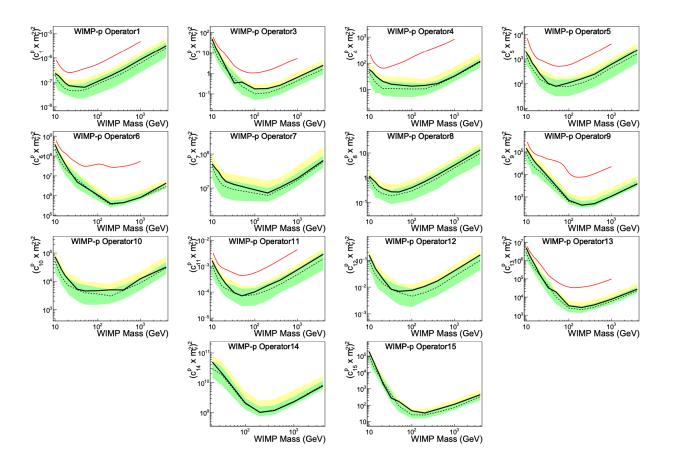

| 3.5 | Results from LUX's elastic EFT analysis [46]. Limits on coupling strength for<br>each operator (WIMP-p) are shown. Solid black lines represent the limit, dashed<br>black lines indicate the expected limits, and red lines show limits from previous<br>runs. A range of WIMP masses from 10 GeV to 4 TeV are considered for each<br>operator                                                                                                                                                                                                                                                                                                                                                                | 71 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

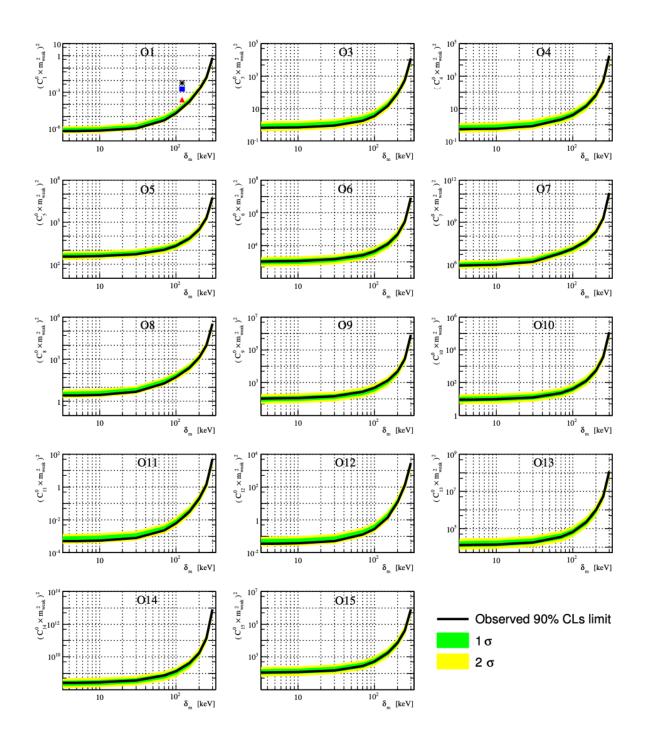

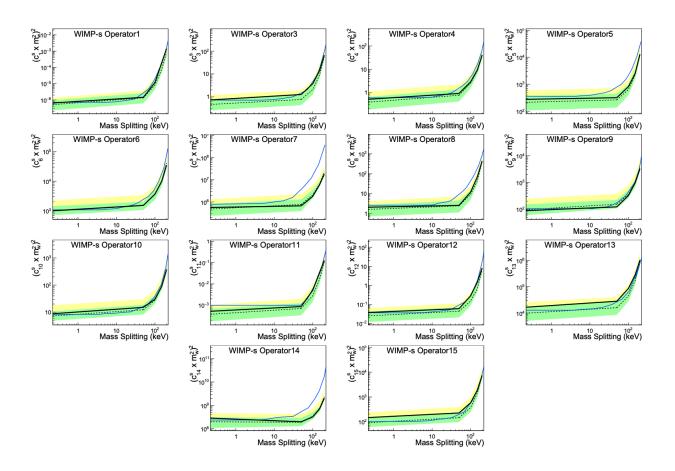

| 3.6 | Results from LUX's inelastic EFT analysis [46]. Limits on coupling strength for<br>each operator are shown. Solid black lines represent the limit, dashed black lines<br>indicate the expected limt, and blue lines show limits from XENON100, which<br>were also shown separately in Figure 3.3. A range of mass splittings from 50 to<br>200 keV are considered.                                                                                                                                                                                                                                                                                                                                            | 71 |

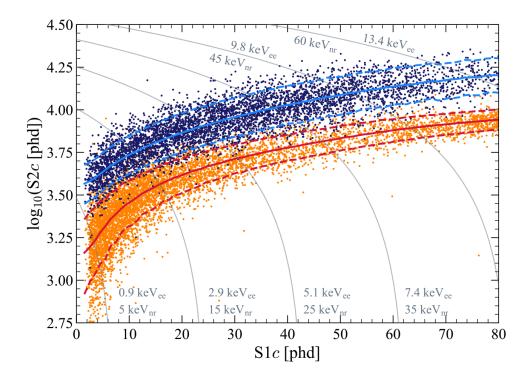

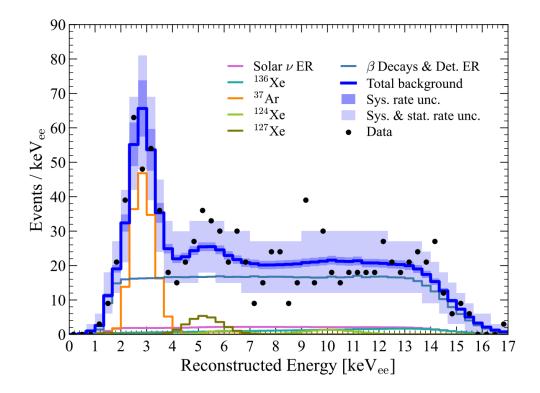

| 4.1 | Results from LZ's NR and ER band calibration campaign for SR1 are shown.<br>Calibration events in log10(S2c) vs. S1c for the tritium source are the dark<br>blue points (5343 events). The DD neutron source events are shown as orange<br>points (6324 events). Solid blue (red) lines indicate the median of the ER (NR)<br>simulated distributions, and the dotted lines indicate the 10% and 90% quantile<br>region. Thin grey lines show contours of constant nuclear recoil energy (keVnr)                                                                                                                                                                                                              | -0 |

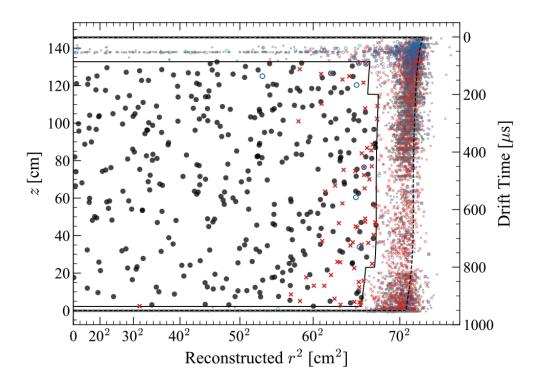

| 4.2 | and their equivalent electronic recoil energy (keVee) [41] Observed data in z versus r <sup>2</sup> space after all SR1 analysis cuts were applied, as discussed in the text. Black (grey) points show the data inside (outside) the FV. Red crosses and blue circles show events vetoed by a prompt LXe skin or OD signal, respectively. The solid line shows the FV definition, and the dashed line shows the extent of the active TPC. Field non-uniformities cause the reconstructed radial position of the active volume boundary to vary as a function of z. Events with drift time of approximately 50 µs are from recoils in the gas which produce S1 and S2 pulses with a fixed time separation [41] | 81 |

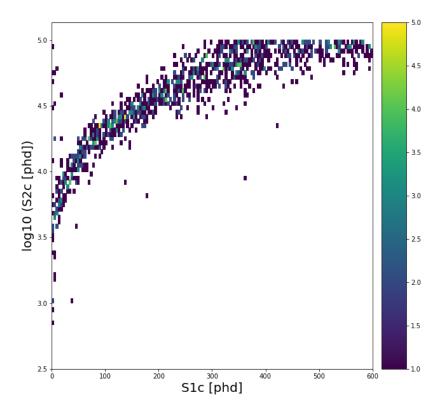

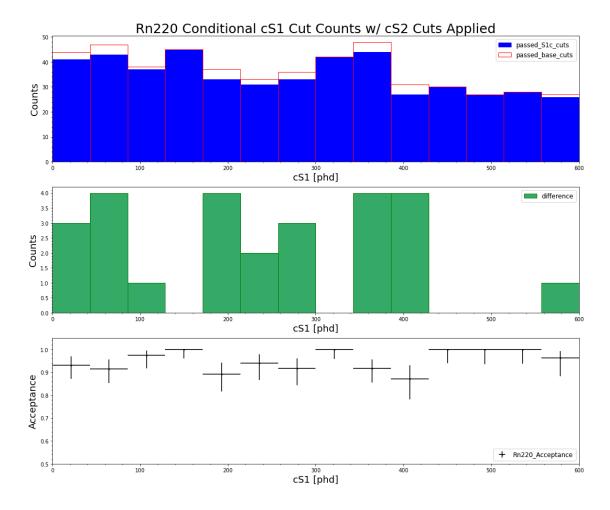

| 4.3 | A histogram of Rn220 skimmed events in log10(S2c) vs. S1c space. Although<br>there are limited statistics, a clear distribution of events across the entire extended<br>S1c ROI from 3 to 600 phd is seen. Similarly, a clear distribution of events across                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

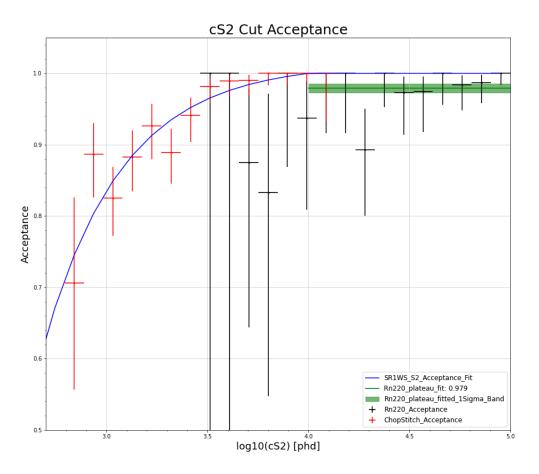

| 4.4 | high log10(S2c) values up to 5.0 are seen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 92 |

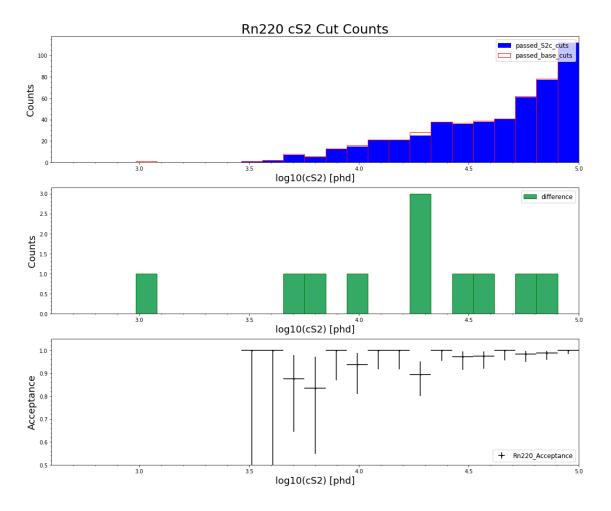

| 4.5 | extended region in S2c plus $1\sigma$ error bands are shown in green In the first row, in red, the original number of events in each log10(S2c) bin is shown. The remaining number of evts/bin is shown in blue after the S2-based cuts are applied. The second row shows the explicit number of events cut per bin. The final row re-plots the Rn220 acceptances from Figure 4.4. The dip in overall S2 acceptance in the plateau is from statistics limitations rather than a                                                                                                                                                                                                                               | 94 |

|     | true dip in the acceptance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 95 |

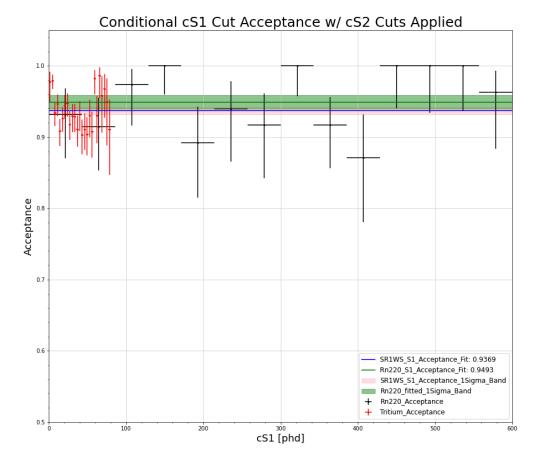

- 4.6 An overlay of the S1c-based cuts acceptance for the standard WIMP search ROI (using the tritium stitched data set) is shown in red. Rn220 calculated acceptances are shown in black for an extended S1c region. A constant value fit across the full energy range plus  $1\sigma$  error bands are shown in green for Rn220....

- 4.7 In the first row, in red, the original number of events in each S1c bin is shown. the remaining number of evts/bin is shown in blue after the S1-based cuts are applied. The second row shows the explicit number of events cut per bin. The final row re-plots the Rn220 acceptances from Figure 4.6. The first two Rn220 bins match well with the standard WIMP search S1 acceptance fit, validating the choice of Rn220 to evaluate S1-based cuts acceptance for an extended S1c ROI. 101

99

- 4.8 Evaluated S2-based trigger and S1 threshold cut acceptances as a function of nuclear recoil energy is shown in blue. In green, the SS and all S1c-  $+ \log 10(S2c)$ -based cuts acceptance is plotted. A final S1c and S2c standard WIMP search ROI cut is applied and the final NR acceptance curve is shown in black. The filled grev bands show the 1- $\sigma$  uncertainty for the final NR acceptance curve [41]. . . 103

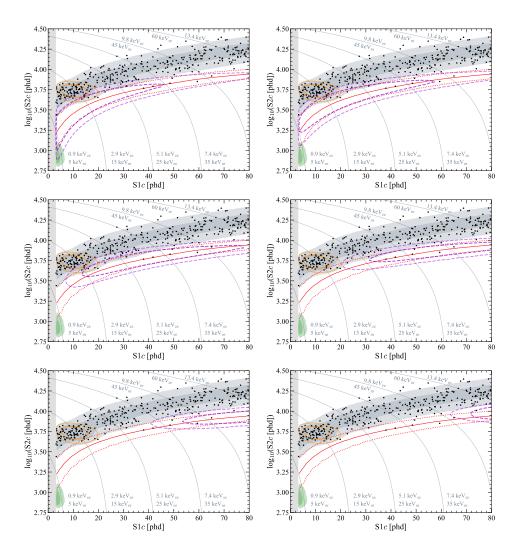

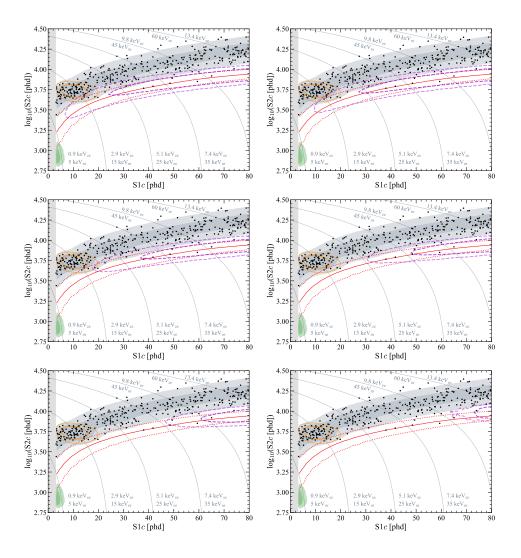

| 4.15 | Various parts of the input RooWorkspace for LZStats are shown for Operator 6. In purple are the 1- and 2- $\sigma$ contours for various mass splitting values going from 0 keV in the top left to 250 keV in the bottom right. The complete background model 1- and 2- $\sigma$ contours are shown in light and dark grey. The tuned NR hand madian and $00\%$ and $10\%$ substituting are shown in red. Also shown are the                                                             |            |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

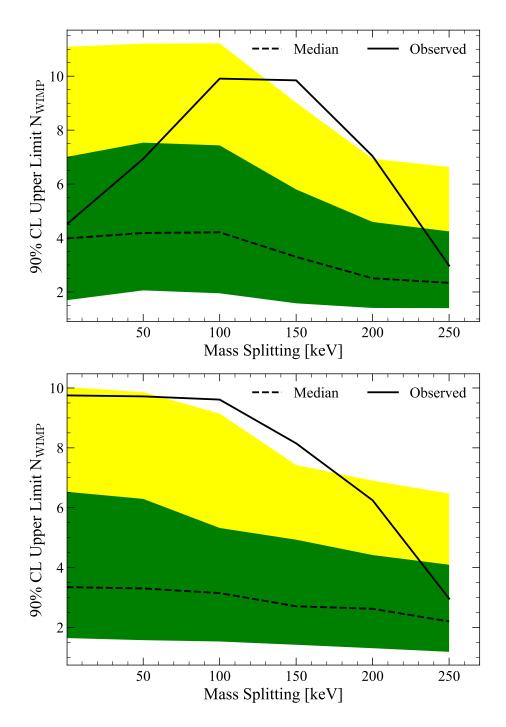

| 4.16 | band median and 90% and 10% quantiles are shown in red. Also shown are the individual 1- and 2- $\sigma$ contours for Ar-37 (orange) and B-8 (green)<br>The 90% CL upper limit on the POI, $\mu$ (the number of WIMP recoil events) as a function of mass-splitting value. Operator 1 is shown in the top figure and Operator 6 is shown in the bottom figure. The dotted line shows the expectation and the green and yellow bands show +/-1 and +2 $\sigma$ values per mass-splitting | 123        |

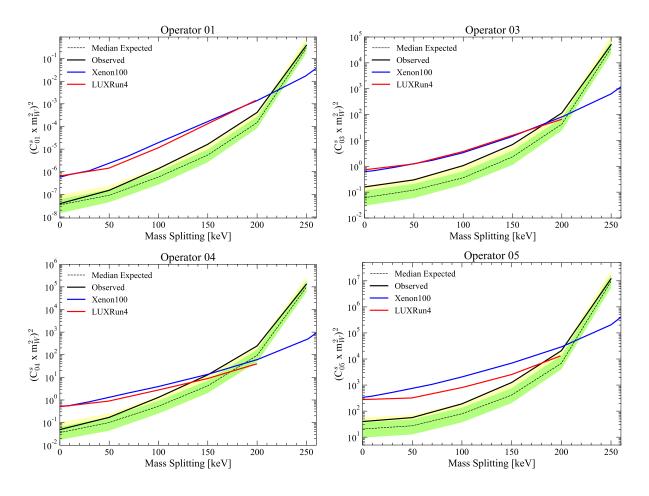

| 4.17 | term                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 125        |

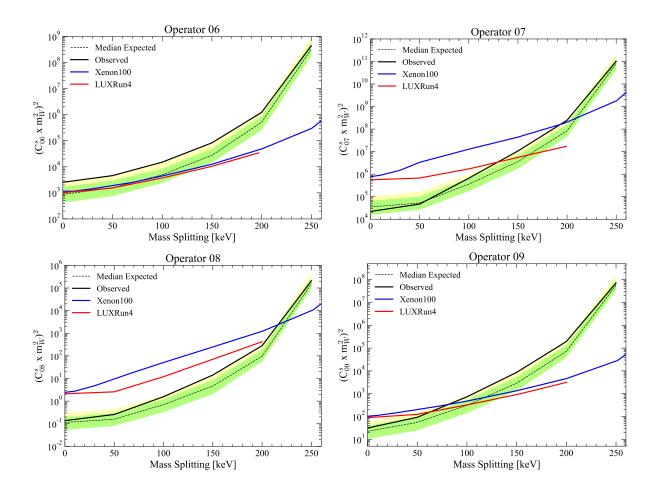

| 4.18 | are shown in blue and red, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 126        |

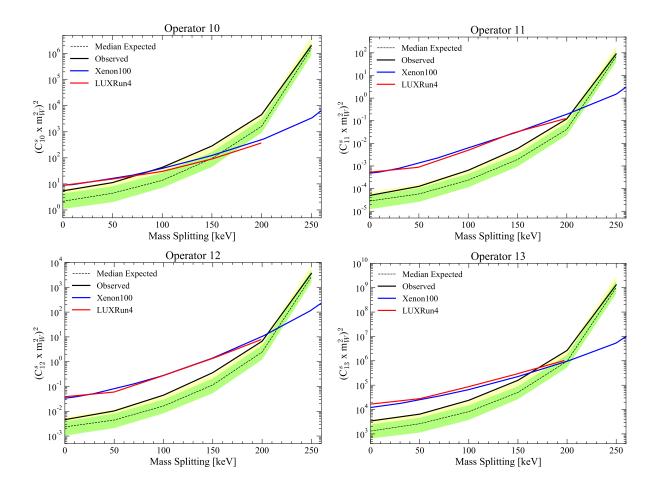

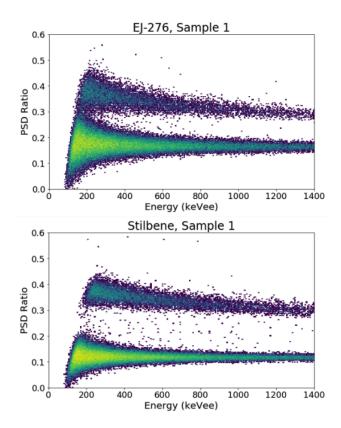

| 4.19 | coefficient is shown as a function of mass-splitting value for Operators 10-13. $+/-$ 1 and $+2 \sigma$ and the median expectation are also shown in green, yellow and the dotted black lines, respectively. XENON100 and LUX experimental limits are                                                                                                                                                                                                                                   | 127        |

| 4.20 | shown in blue and red, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 128<br>129 |

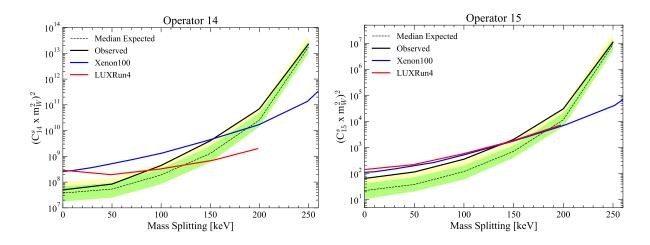

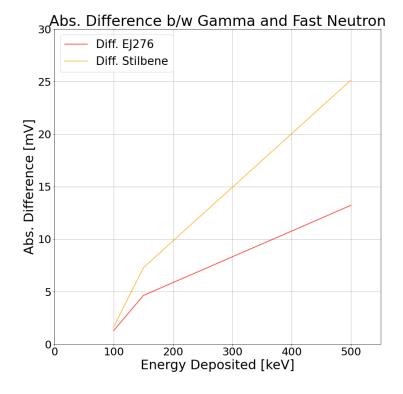

| 5.1  | From [76], one example of previous measurements of pulse shape differences be-<br>tween fast neutrons and gammas for Stilbene and EJ-276. The paper, however,<br>uses PMTs and not SiPMs for their study. Readout electronics and scintillator                                                                                                                                                                                                                                          |            |

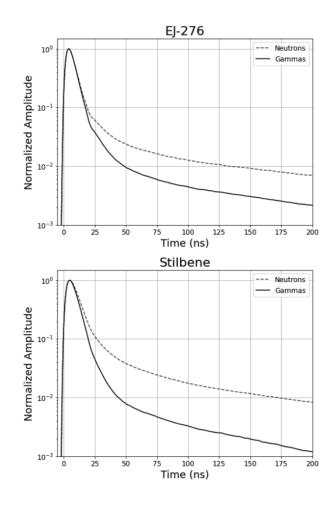

| 5.2  | geometry is also expected to affect pulse shapes                                                                                                                                                                                                                                                                                                                                                                                                                                        | 137<br>138 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 100        |

| 5.3  | From [76], the final figure of merit (FOM) values as a function of energy from a             |     |

|------|----------------------------------------------------------------------------------------------|-----|

|      | study into PSD capability of EJ276 and Stilbene (and other scintillators). The               |     |

|      | much better performance of Stilbene across all energies compared to EJ276 is                 | 100 |

| ~ .  | observed. The photo-sensors used were PMTs, not SiPMs.                                       | 139 |

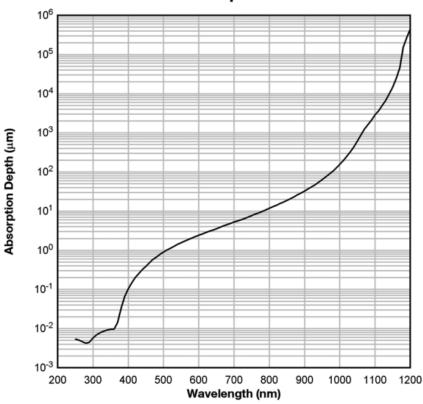

| 5.4  | From [77], the absorption length for various wavelengths of light in silicon.                | 141 |

| 5.5  | The avalanche and reset process for each SPAD that is connected in parallel to               |     |

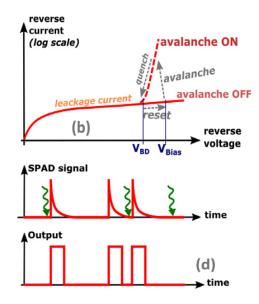

|      | form a complete SiPM cell, extracted from [78]                                               | 142 |

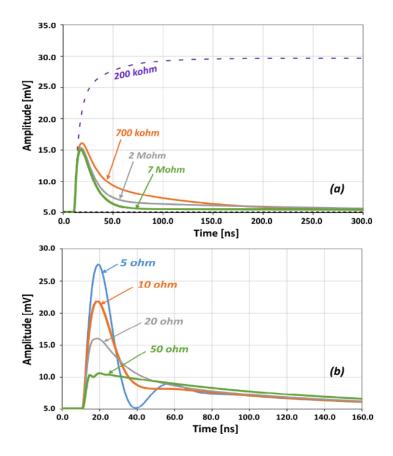

| 5.6  | Above, the effect of quenching resistor values on overall SiPM output pulse shape.           |     |

|      | Below, the effect of different front-end input impedances on SiPM pulse shape.               |     |

|      | Both plots are from [78]                                                                     | 144 |

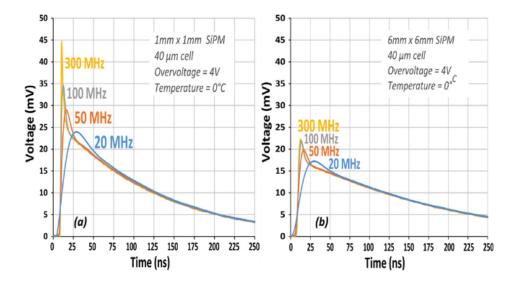

| 5.7  | From [78], the effect of front-end bandwidth (and SiPM sensor size) on the overall           |     |

|      | SiPM output pulse shape. Plot (a) describes the effect of front-end bandwidth                |     |

|      | for a 1mmx1mm SiPM with 40um microcell size and and plot (b) describes the                   |     |

|      | same but for a 6mmx6mm SiPM with the same microcell size                                     | 145 |

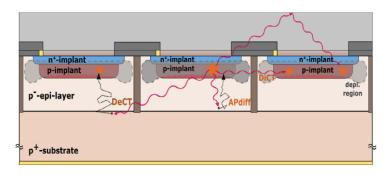

| 5.8  | From [78], a diagram showing how optical cross-talk and afterpulsing within a                |     |

|      | SiPM's microcells occur.                                                                     | 148 |

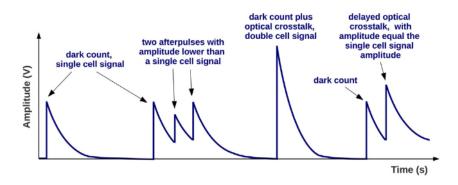

| 5.9  | From [78], SiPM output pulses from optical cross-talk and afterpulsing                       | 148 |

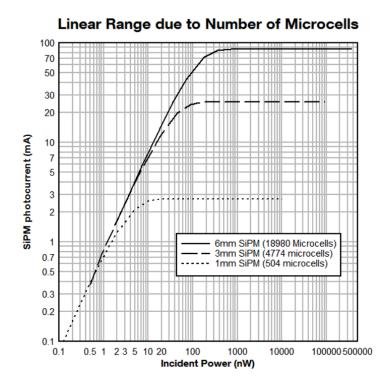

| 5.10 | From [77], the relationship between microcell size and linear response range of a            |     |

|      | SiPM                                                                                         | 150 |

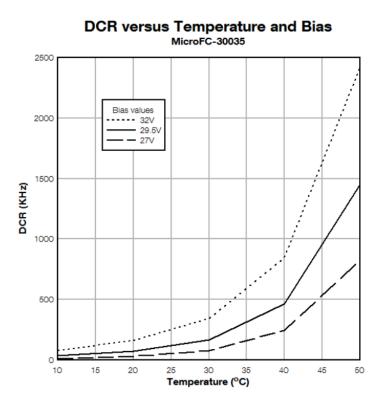

| 5.11 | From [77], the relationship between temperature and dark count rate in a SiPM.               | 152 |

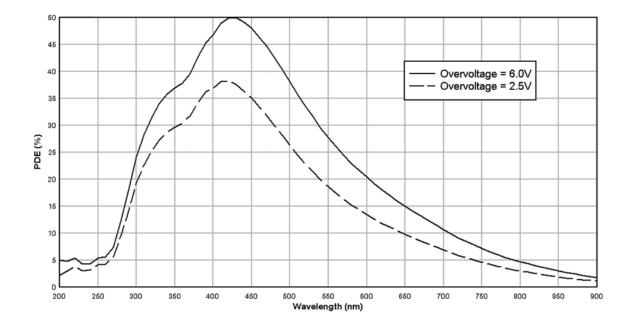

| 5.12 | From [80], the PDE vs. wavelength relationship for SensL J-series 6mmx6mm                    |     |

|      | (35um microcells) SiPMs at two different overvoltages                                        | 155 |

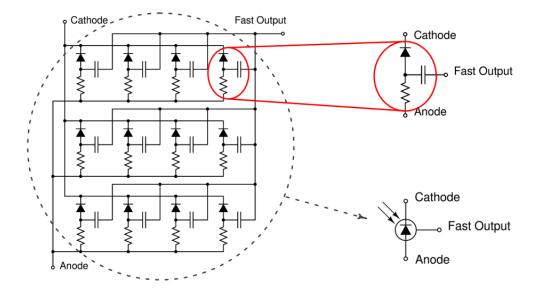

| 5.13 | A diagram of the substructure of a SensL SiPM, from [80]                                     | 156 |

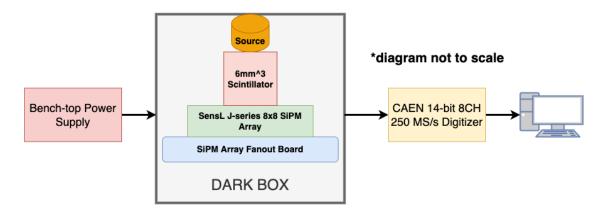

| 5.14 | A conceptual overview of the SiPM + Scintillator testbed setup. A focus was                  |     |

|      | made to keep the testbed as simple as possible in order to be able to study                  |     |

|      | inherent PSD capabilities of various scintillators coupled to SiPMs without effects          |     |

|      | of readout electronics.                                                                      | 157 |

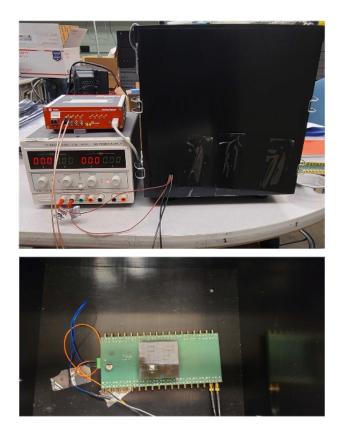

| 5.15 | Two photographs of the dark box design. A light maze was included as a way to                |     |

|      | offset the cables coming into the dark box and prevent light leakage. Clasps are             |     |

|      | included on the sides of the box as an additional precaution against light leakage.          |     |

|      | They clamp down on the two removable lids of the dark box                                    | 158 |

| 5.16 | Photographs showing all the major components of the $SiPM + Scintillator$ testbed            | 159 |

| 5.17 | A close up of the custom fanout boards designed for use in the SiPM + Scintillator           |     |

|      | characterization testbed. The board allows for directly plugging in a SensL J-               |     |

|      | series 8x8 SiPM array and SOUT and FOUT signals of selected channels are                     |     |

|      | fanned-out to respective SMB connectors. The green connector delivers bias to                |     |

|      | the SiPM array.                                                                              | 160 |

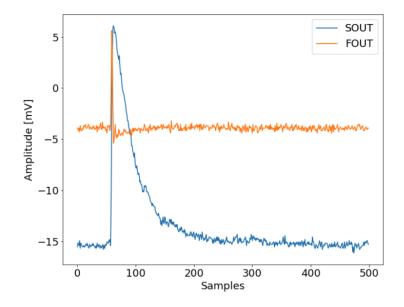

| 5.18 | Digitized (SOUT in blue and FOUT in orange) waveforms from the testbed are                   |     |

|      | plotted. The sampling rate of the 14-bit resolution CAEN digitizer used is $250 \text{MS/s}$ | 161 |

|      |                                                                                              |     |

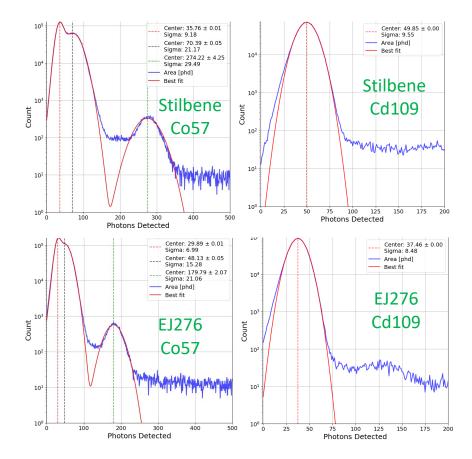

| 5.19        | The results from fitting known gamma peaks for Co-57 and Cd-109 sealed sources for data acquired from the testbed. Best fits are shown in orange and the centers    |     |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|             | each fitted peak are shown as dotted vertical lines.                                                                                                                | 165 |

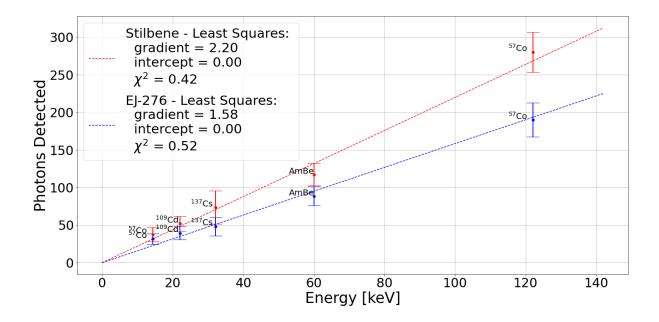

| 5.20        | •                                                                                                                                                                   |     |

|             | for both Stilbene and EJ-276 scintillators. A straight line was fit for each scintil-                                                                               |     |

|             | lator, respectively. Stilbene is measured to yield 2.20 phd/keV and EJ-276 yields                                                                                   |     |

|             | 1.58 phd/keV                                                                                                                                                        | 167 |

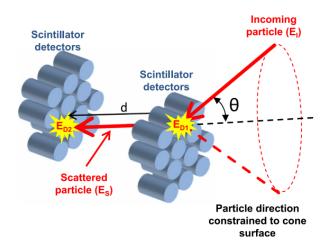

| 5.21        | A diagram showing the variables required for the reconstruction of the incident                                                                                     |     |

|             | abgle of a neutron in a general neutron scatter camera design [83]                                                                                                  | 168 |

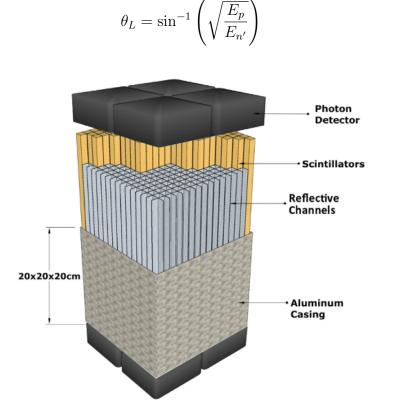

| 5.22        | From [82], an example of a segmented neutron camera design using plastic/organic                                                                                    |     |

|             | scintillator materials coupled to PMTs/SiPM photo-sensors.                                                                                                          | 170 |

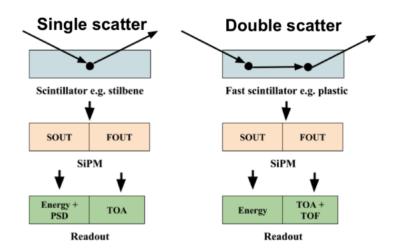

| 5.23        | A summary of the main signal outputs required for both single and double scatters                                                                                   |     |

|             | of fast neutrons within the camera volume for a neutron scatter camera. $\ldots$                                                                                    | 172 |

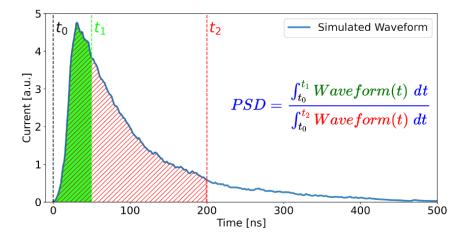

| 5.24        | A visual definition of PSD ratio as implemented in both versions of the chip                                                                                        | 174 |

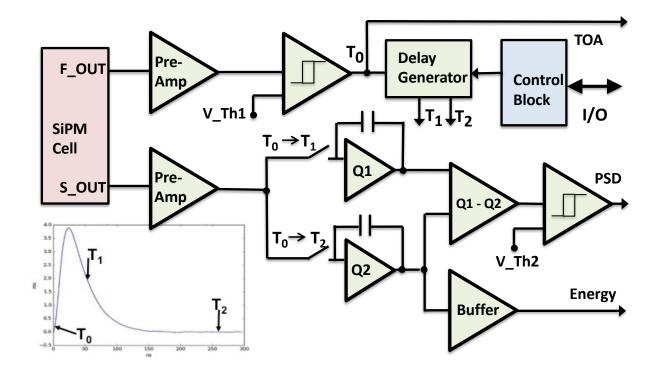

| 5.25        | A schematic overview of the main blocks of a single channel of the chip. $\ldots$ .                                                                                 | 177 |

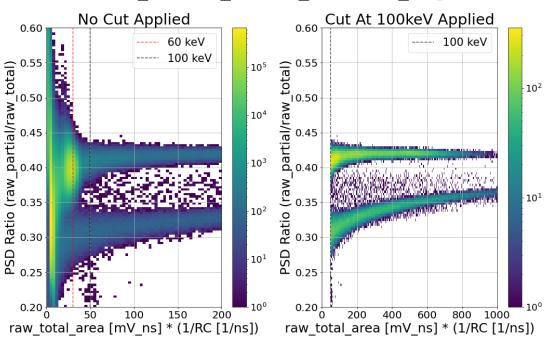

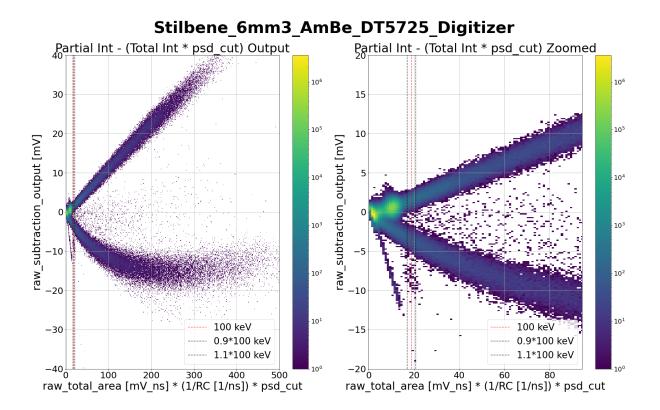

| 5.26        | PSD ratio versus raw total area scaled by the RC time constant of the integration                                                                                   |     |

|             | stage on chip for Stilbene is plotted for 30 million digitized AmBe events. In the                                                                                  |     |

|             | right-hand plot, a cut at 100keV was applied and only events passing this cut                                                                                       |     |

|             | (shown in the black dotted line) are plotted                                                                                                                        | 180 |

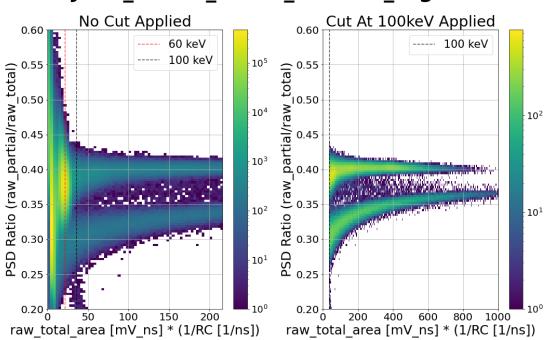

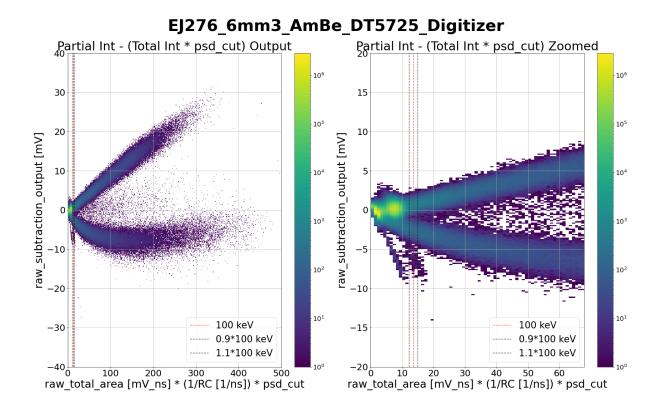

| 5.27        | PSD ratio versus raw total area scaled by the RC time constant of the integration                                                                                   |     |

|             | stage on chip for EJ-276 is plotted for 30 million digitized AmBe events. In the                                                                                    |     |

|             | right-hand plot, a cut at 100keV was applied and only events passing this cut                                                                                       |     |

|             | (shown in the black dotted line) are plotted                                                                                                                        | 182 |

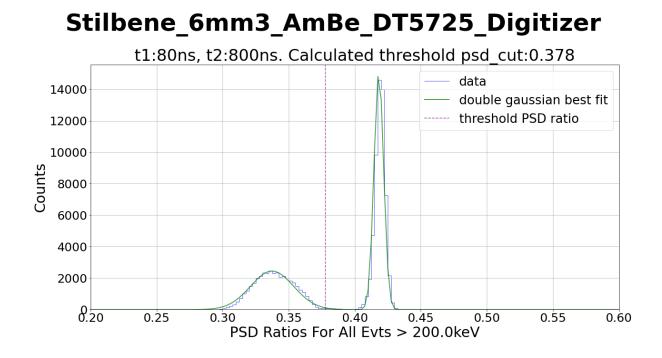

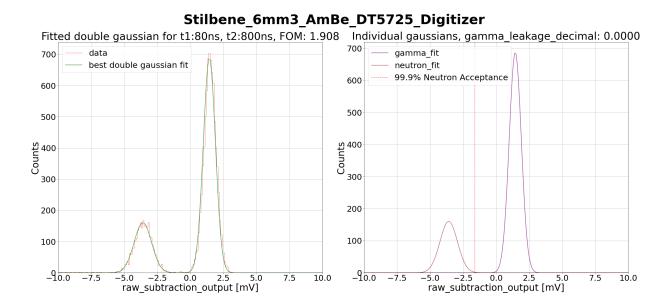

| 5.28        | After cutting on all events above 200keV equivalent total area, a double Gaussian                                                                                   |     |

|             | fit for the two bands was performed for Stilbene. The threshold PSD ratio (dotted                                                                                   |     |

|             | purple line) was taken to be the center between the two fitted Gaussian means                                                                                       | 104 |

| <b>F</b> 00 | for the feasibility study.                                                                                                                                          | 184 |

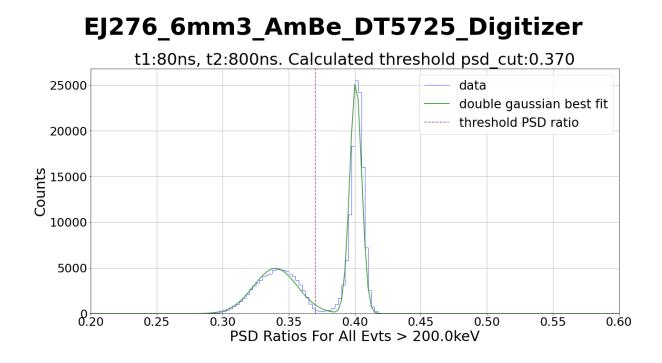

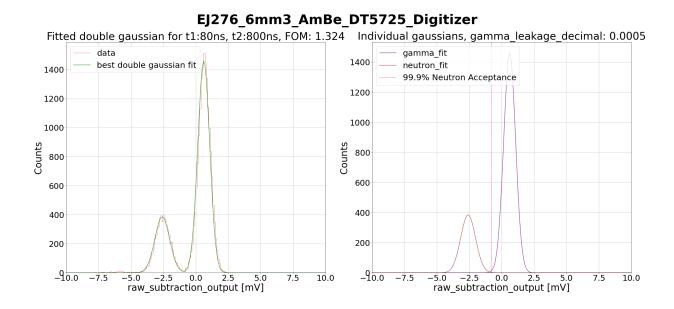

| 5.29        |                                                                                                                                                                     |     |

|             | fit for the two bands was performed for EJ276. The threshold PSD ratio (dotted                                                                                      |     |

|             | purple line) was taken to be the center between the two fitted Gaussian means                                                                                       | 105 |

| F 20        | for the feasibility study.                                                                                                                                          | 185 |

| 0.30        | Using the extracted threshold PSD ratio, the raw total area scaled by the thresh-<br>ald ratio is platted us, the new subtraction sutput value for Stillens. On the |     |

|             | old ratio is plotted vs. the raw subtraction output value for Stilbene. On the right, the plot is zoomed in to show a region around 100 keV. Setting a threshold    |     |

|             | value for the discriminator following the subtraction stage is equivalent to setting                                                                                |     |

|             | a threshold along the y-axis here                                                                                                                                   | 187 |

| 5 21        | Using the extracted threshold PSD ratio, the raw total area scaled by the thresh-                                                                                   | 107 |

| 0.01        | old ratio is plotted vs. the raw subtraction output value for EJ276. On the right,                                                                                  |     |

|             | the plot is zoomed in to show a region around 100 keV. Setting a threshold value                                                                                    |     |

|             | for the discriminator following the subtraction stage is equivalent to setting a                                                                                    |     |

|             | threshold along the y-axis here                                                                                                                                     | 188 |

|             |                                                                                                                                                                     | 100 |

| 5.32 | On the left, a 1D histogram of all AmBe events within $+/-10\%$ of 100keV for Stilbene. A double Gaussian was fit to this data and is overlayed in green. On               |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | the right, the separate neutron and gamma Gaussian fits as well as the 99.9%                                                                                               |     |

|      | neutron acceptance line are shown.                                                                                                                                         | 189 |

| 5.33 | On the left, a 1D histogram of all AmBe events within $+/-10\%$ of 100keV for                                                                                              |     |

|      | EJ276. A double Gaussian was fit to this data and is overlayed in green. On                                                                                                |     |

|      | the right, the separate neutron and gamma Gaussian fits as well as the 99.9%                                                                                               |     |

|      | neutron acceptance line are shown.                                                                                                                                         | 190 |

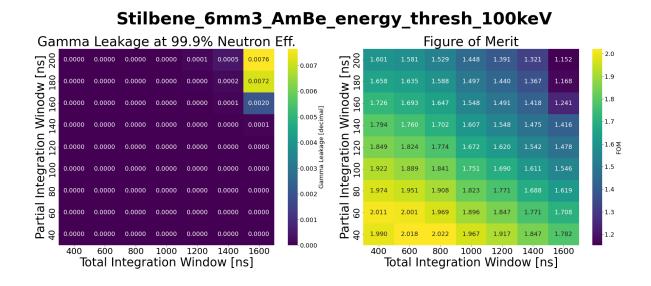

| 5.34 | Gamma leakage at 99.9% neutron efficiency for a range of partial and total inte-                                                                                           |     |

|      | gration windows is shown on the left for Stilbene. Figure of Merit values for the                                                                                          |     |

|      | same combinations of partial and total integration windows is shown on the right.                                                                                          | 193 |

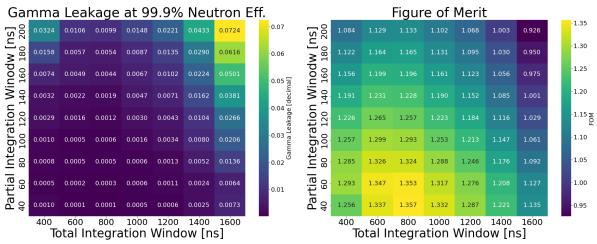

| 5.35 |                                                                                                                                                                            |     |

|      | gration windows is shown on the left for EJ276. Figure of Merit values for the                                                                                             |     |

|      | same combinations of partial and total integration windows is shown on the right.                                                                                          | 194 |

| 6.1  | An overview of PSD_CHIP_V1's one channel signal chain. Both the FOUT and                                                                                                   |     |

| 0.1  | SOUT signal chains are detailed, including which FOUT signals feed into the                                                                                                |     |

|      | SOUT signal chain. Most of the next chapter introduces and describes the various                                                                                           |     |

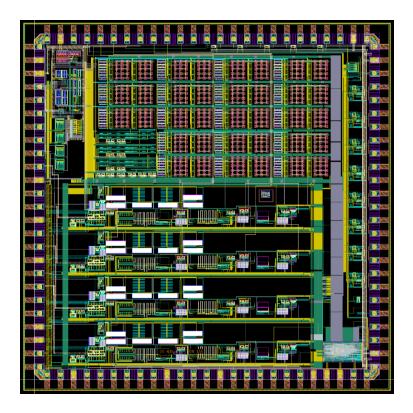

|      | blocks that form the complete one channel signal chain                                                                                                                     | 197 |

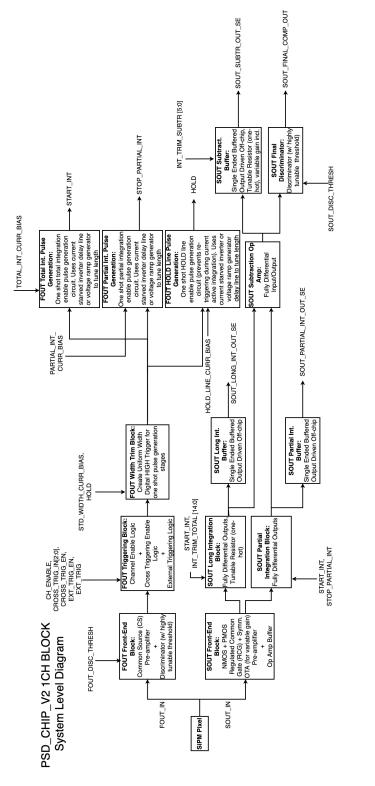

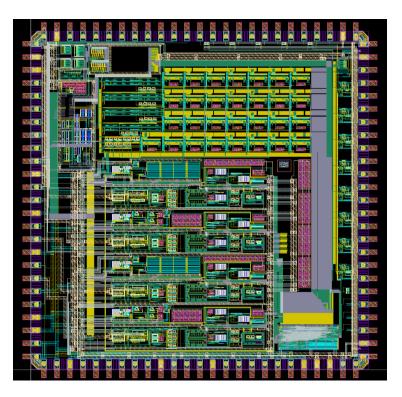

| 6.2  | A system level overview of the full PSD_CHIP_V2 design. Sizes of blocks in this                                                                                            |     |

|      | diagram are not indicative of the physical blocks' sizes on the chip.                                                                                                      | 198 |

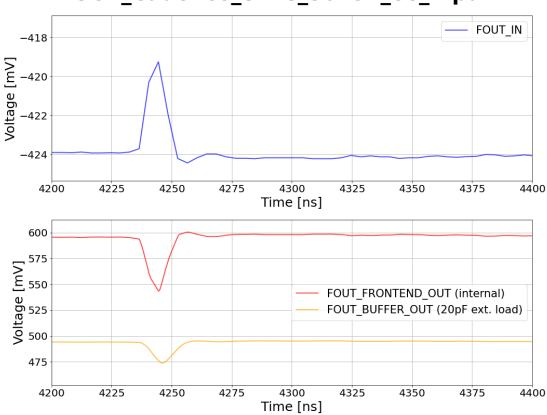

| 6.3  | A sample (50 keV <sub>ee</sub> , amplitude scaled down from a 500 keV <sub>ee</sub> pulse) fast neutron                                                                    |     |

|      | FOUT waveform acquired using the test bed was input to the FOUT signal chain                                                                                               |     |

|      | in a Cadence simulation (shown in blue). The output from the CS amplifier stage                                                                                            |     |

|      | is shown in red. The output post buffer with a 20 pF load is shown in orange.                                                                                              | 206 |

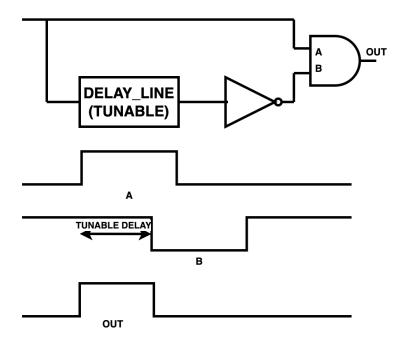

| 6.4  | The circuit implementation of digital pulse width trimming used on PSD_CHIP.                                                                                               |     |

|      | The programmable delay line block is implemented using a chain of current                                                                                                  |     |

|      | starved inverters (CSI). This circuit is one of two stages used to ensure a standard                                                                                       |     |

|      | width for generated T0 triggers before they are fed into the parallel integration                                                                                          |     |

|      | 0                                                                                                                                                                          | 209 |

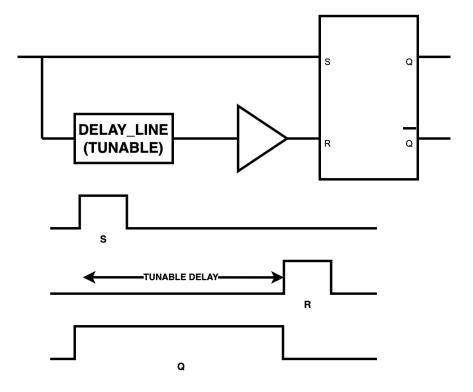

| 6.5  | The SR latch on-shot generator (with programmable delay) circuit design. The                                                                                               |     |

|      | delay line block is implemented through the use of a chain of current starved                                                                                              |     |

|      | inverters (CSI) on-chip. This circuit is the core of many parts of the FOUT digital                                                                                        |     |

|      | triggering logic. An appropriately selected length of CSIs in series generates the                                                                                         |     |

|      | partial, total, and HOLD enable pulses. It is also used as one of two stages to                                                                                            |     |

|      | implement a standard width for T0 before it is fed into the parallel integration                                                                                           | 011 |

| 66   | enable generation stages.                                                                                                                                                  | 211 |

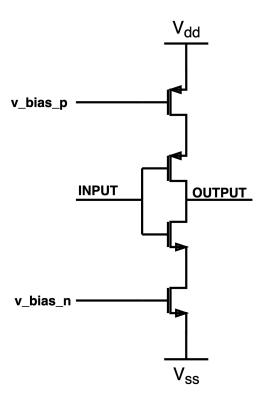

| 6.6  | A transistor level circuit of a current starved inverter. This inverter is exclusively<br>used as the building block for programmable delay lines in V1 of the chip. It is |     |

|      | used as the building block for programmable delay lines in V1 of the chip. It is also used in V2, but not exclusively                                                      | 214 |

|      | and used in $v_2$ , but not exclusively                                                                                                                                    | 414 |

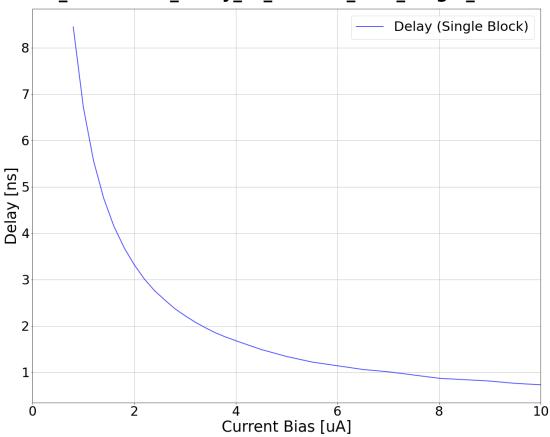

| 6.7  | The relationship between supplied bias current [uA] and the generated delay for         |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | a pair of current starved inverters                                                     | 216 |

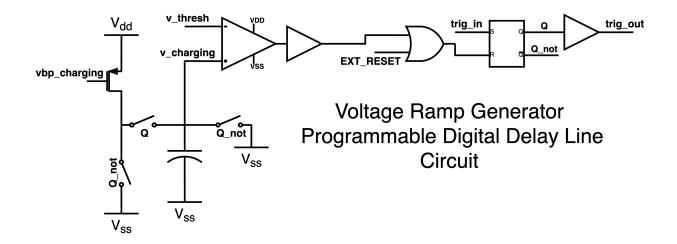

| 6.8  | A new programmable delay line circuit implemented in PSD_CHIP_V2. This                  |     |

|      | design at the base level is more complicated compared to CSI-based delay lines.         |     |

|      | However, the overall power and area savings are significant. Details are found in       |     |

|      | the text                                                                                | 217 |

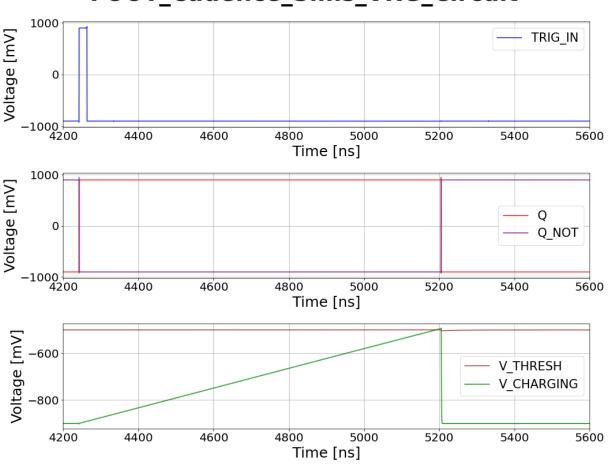

| 6.9  | A Cadence simulation of the VRG circuit. The different traces represent nodes           |     |

|      | in the VRG circuit (see Figure 6.8). See text for a thorough explanation                | 220 |

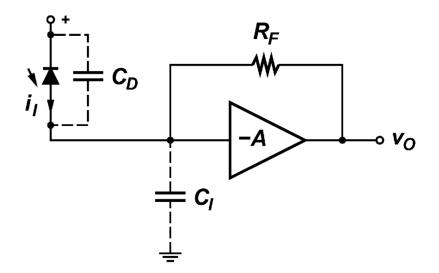

| 6.10 | A simplified block diagram of a transimpedance amplifier, from [88]. $C_D$ repre-       |     |

|      | sents the photodiode capacitance, $i_I$ the photodiode current, $C_I$ the input capac-  |     |

|      | itance of the amplifier and $R_F$ a feedback resistor that sets the overall gain of the |     |

|      | transimpedance amplifier. $v_O$ is the output node for the amplifier                    | 223 |

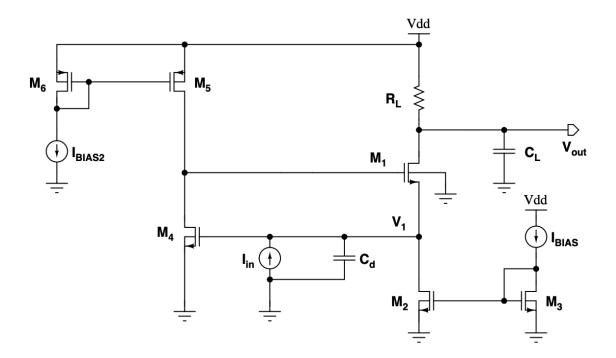

| 6.11 | A transistor level breakdown of the regulated common gate (RCG) amplifier, from         |     |

|      | [87]. This circuit is used for the SOUT front-end. Included in this diagram are         |     |

|      | the current mirror biasing and main capacitive elements at the input and output         |     |

|      | nodes that affect bandwidth and performance for this circuit.                           | 226 |

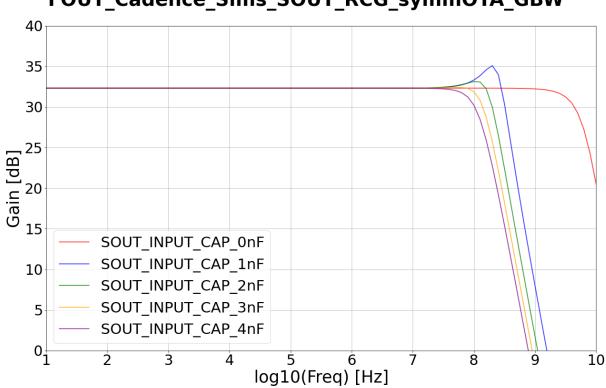

| 6.12 | Gain-bandwidth (GBW) plots for various input capacitances is shown. The sym-            |     |

|      | metrical OTA is not included in these simulations. A clear dependence between           |     |

|      | input capacitance and RCG bandwidth is observed                                         | 228 |

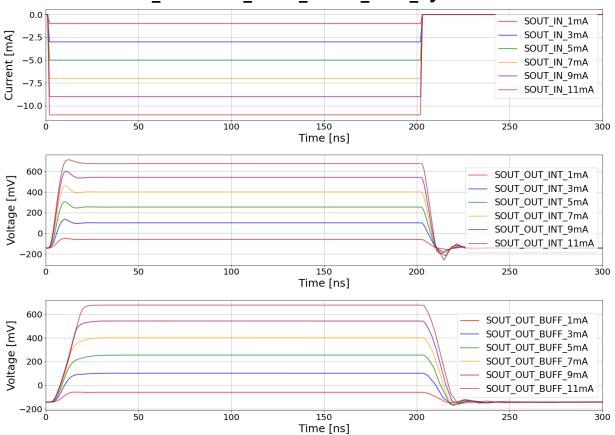

| 6.13 | A square wave input waveform with varying current amplitudes is used as a test          |     |

|      | input to the SOUT front-end (first row). The output waveform from the RCG +             |     |

|      | symmetrical OTA front-end (with the gain of the OTA set to unity) is shown in           |     |

|      | the second row. In the third row, the waveform post-buffer is shown. $\ldots$ .         | 229 |

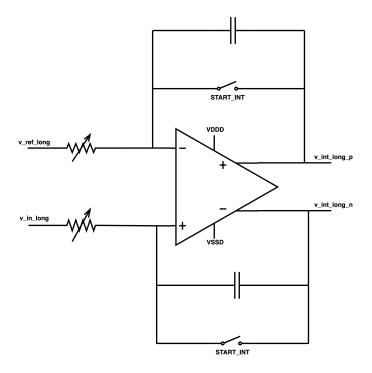

| 6.14 | A fully differential total integration stage implementation. The tunable resistor,      |     |

|      | as described in Chapter 5, is implemented in this stage and forms a core part of        |     |

|      | the real-time PSD design.                                                               | 231 |

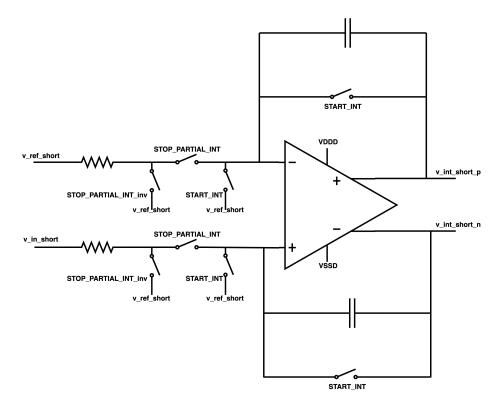

| 6.15 |                                                                                         |     |

|      | only fixed resistors and several series and feedback switches. The timing diagram       |     |

|      | for these switches is in Figure 6.16                                                    | 233 |

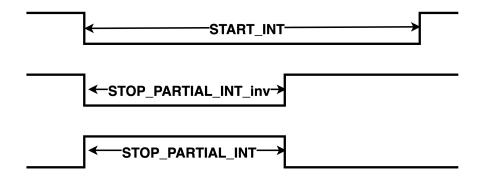

| 6.16 |                                                                                         |     |

|      | integration stages. The actual partial and total integration enable pulses are          |     |

|      | generated in the FOUT signal chain using either a current starved inverter (CSI)        |     |

|      | or voltage ramp generator (VRG) based design. They are then transformed in a            |     |

|      | manually implemented digital block into the versions seen in this diagram. The          |     |

|      | actual STOP_PARTIAL_INT digital testbus output is a "delayed" START_INT                 |     |