#### UNIVERSITY OF CALIFORNIA

Los Angeles

# Energy-Efficient VLSI Signal Processing for Wideband Spectrum Sensing in Cognitive Radios

A dissertation submitted in partial satisfaction

of the requirements for the degree

Doctor of Philosophy in Electrical Engineering

by

### **Tsung-Han Yu**

2013

© Copyright by

Tsung-Han Yu

2013

# Energy-Efficient VLSI Signal Processing for Wideband Spectrum Sensing in Cognitive Radios

by

#### Tsung-Han Yu

Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2013 Professor Dejan Marković, Co-chair Professor Danijela Čabrić, Co-chair

With the rapid increases in the number of wireless devices, fixed spectrum allocation has shown to be a major limitation to the evolution of wireless technologies. Cognitive radio (CR) allows opportunistic spectrum access by searching and utilizing temporally and spatially unused spectrum, provided that CR users do not cause interference to the primary users of the spectrum. Spectrum sensing over a wide bandwidth increases the probability of finding under-utilized spectrum for cognitive radios. However, the realization of wideband sensing is challenging because strong primary users introduce large dynamic range and spectral leakage to adjacent unused bands.

This work presents an algorithm-architecture co-design framework for wideband spectrum sensing. The suppression of spectral leakage is achieved by multitap-windowed FFT processing, which also enables reduced sensing time. The sensing time and detection threshold are adapted according to channel-specific spectral leakage, enabling reliable wideband detection within constrained sensing time. Power and area cost of the compute-intensive FFT block is minimized by using parallelism, radix factorization, and compact delay lines. A per-channel floating point data processing for large dynamic range signal is employed for power and area saving. A partial PSD estimation scheme that performs energy detection on only the band-of-interest further improves the energy efficiency. Two chips have been designed to demonstrate these concepts. These chips guarantee reliable weak signal detection with short sensing time, and outperform the prior work by at least 22x in power/bandwidth. Techniques developed in this dissertation enable energy-efficient chip implementation of advanced wideband signal processing for cognitive radios.

The dissertation of Tsung-Han Yu is approved.

Milos D. Ercegovać

Greg Pottie

Danijela Čabrić, Committee Co-chair

Dejan Marković, Committee Co-chair

University of California, Los Angeles

2013

To my family.

# TABLE OF CONTENTS

| 1 | Intr | duction                                                        |

|---|------|----------------------------------------------------------------|

|   | 1.1  | Cognitive Radios                                               |

|   | 1.2  | Spectrum Sensing                                               |

|   | 1.3  | Motivation for This Work                                       |

|   | 1.4  | Dissertation Outline                                           |

| 2 | Wid  | eband Spectrum Sensing in Cognitive Radios                     |

|   | 2.1  | Frequency-Domain Wideband Spectrum Sensing                     |

|   | 2.2  | Overview of Conventional Channelization Schemes                |

|   | 2.3  | Overview of Previous Work                                      |

|   | 2.4  | Summary                                                        |

| 3 | Wid  | eband Speccturm-Sensing Algorithms and Real-Time Testbed 17    |

|   | 3.1  | Wideband Spectrum-Sensing Design Problem                       |

|   |      | 3.1.1 System Model                                             |

|   |      | 3.1.2 Design Specification                                     |

|   |      | 3.1.3 Design Challenges                                        |

|   | 3.2  | Proposed Wideband Spectrum-Sensing Algorithms                  |

|   |      | 3.2.1 PSD Estimation Using Multitap-Windowed FFT Processing 25 |

|     | 3.2.2                                                          | Power Detector Matrix Model                                                                                                                                                                                                    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 3.2.3                                                          | Interfering Power Estimation                                                                                                                                                                                                   | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 3.2.4                                                          | Detection-Threshold and Sensing-Time Adaptations                                                                                                                                                                               | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.3 | Numer                                                          | ical Simulations                                                                                                                                                                                                               | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 3.3.1                                                          | Improvement in ROC                                                                                                                                                                                                             | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 3.3.2                                                          | Improvement in Sensing Time                                                                                                                                                                                                    | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

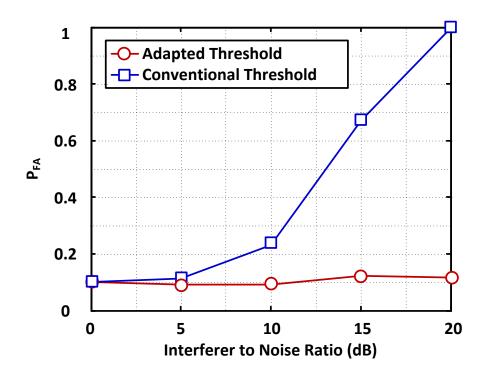

|     | 3.3.3                                                          | Improvement in False-Alarm Rate                                                                                                                                                                                                | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.4 | Propos                                                         | ed VLSI Architecture and Experimental Results                                                                                                                                                                                  | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 3.4.1                                                          | Proposed VLSI Architecture                                                                                                                                                                                                     | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 3.4.2                                                          | Fixed-Length vs. Reconfigurable FFT                                                                                                                                                                                            | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 3.4.3                                                          | Hardware Complexity                                                                                                                                                                                                            | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 3.4.4                                                          | Implementation on CR Testbed                                                                                                                                                                                                   | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 3.4.5                                                          | Experimental Results                                                                                                                                                                                                           | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.5 | Summa                                                          | ary                                                                                                                                                                                                                            | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Pow | er and A                                                       | Area Minimization of Reconfigurable FFT Processor                                                                                                                                                                              | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |                                                                |                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.1 | Overvi                                                         | ew of FFT Designs                                                                                                                                                                                                              | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.2 | FFT A                                                          | lgorithms and Architectures                                                                                                                                                                                                    | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 4.2.1                                                          | Radix-2-Butterfly Based Architecture                                                                                                                                                                                           | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 4.2.2                                                          | Reconfigurable Architecture                                                                                                                                                                                                    | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | <ul> <li>3.4</li> <li>3.5</li> <li>Pow</li> <li>4.1</li> </ul> | 3.2.3<br>3.2.4<br>3.3 Numer<br>3.3.1<br>3.3.2<br>3.3.3<br>3.4 Propos<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.5 Summa<br>Power and A<br>4.1 Overvi<br>4.2 FFT A<br>4.2.1 | 3.2.3       Interfering Power Estimation         3.2.4       Detection-Threshold and Sensing-Time Adaptations         3.3       Numerical Simulations         3.3.1       Improvement in ROC         3.3.2       Improvement in Sensing Time         3.3.3       Improvement in False-Alarm Rate         3.4       Proposed VLSI Architecture and Experimental Results         3.4.1       Proposed VLSI Architecture         3.4.2       Fixed-Length vs. Reconfigurable FFT         3.4.3       Hardware Complexity         3.4.4       Implementation on CR Testbed         3.4.5       Experimental Results         3.4.5       Experimental Results         3.4.6       Fired Area Minimization of Reconfigurable FFT Processor         4.1       Overview of FFT Designs         4.2       FFT Algorithms and Architectures         4.2.1       Radix-2-Butterfly Based Architecture |

|   | 4.3  | Power    | and Area Minimization                        | 61  |

|---|------|----------|----------------------------------------------|-----|

|   |      | 4.3.1    | Parallel Architecture with FFT Decomposition | 62  |

|   |      | 4.3.2    | Estimation of Area and Power                 | 64  |

|   |      | 4.3.3    | Mixed-Radix Implementation                   | 66  |

|   |      | 4.3.4    | Delay-Buffer Architecture and Memory Element | 70  |

|   |      | 4.3.5    | Area-Efficient Twiddle-Factor Generator      | 76  |

|   | 4.4  | Summ     | ary                                          | 77  |

| 5 | Chij | p 1: 200 | MS/s Wideband Spectrum Sensing Processor     | 78  |

|   | 5.1  | Desigr   | Challenges of Wideband Spectrum Sensing      | 78  |

|   | 5.2  | Archite  | ecture and Circuit Design                    | 80  |

|   |      | 5.2.1    | Multi-path Pipelined MW-FPD                  | 81  |

|   |      | 5.2.2    | Floating-point Signal Processing             | 84  |

|   |      | 5.2.3    | Processing Time Overhead Reduction           | 87  |

|   |      | 5.2.4    | Summary of Design Optimization               | 91  |

|   | 5.3  | Chip I   | mplementation                                | 93  |

|   |      | 5.3.1    | FPGA-aided Verification                      | 95  |

|   |      | 5.3.2    | Measurement Results                          | 97  |

|   |      | 5.3.3    | Performance Comparison                       | 99  |

|   | 5.4  | Summ     | ary                                          | 101 |

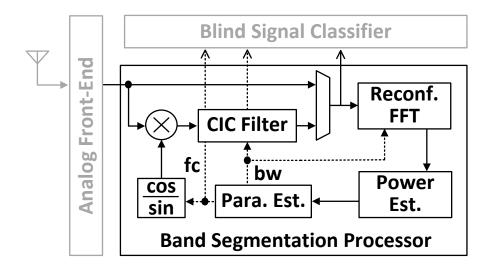

| 6  | Chij           | p 2: 500 | MS/s Wideband Band Segmentation Processor for Blind Signal |    |

|----|----------------|----------|------------------------------------------------------------|----|

| Cl | Classification |          |                                                            |    |

|    | 6.1            | Design   | Specifications                                             | 13 |

|    | 6.2            | Energy   | Minimization Methodology                                   | 14 |

|    |                | 6.2.1    | Partial PSD Estimation                                     | 15 |

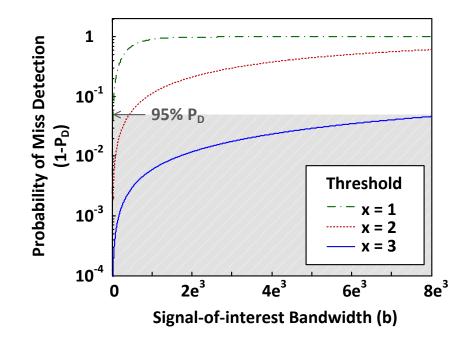

|    |                | 6.2.2    | Miss-detection Tolerant Signal Detection                   | 5  |

|    |                | 6.2.3    | Design Example                                             | 7  |

|    | 6.3            | Propos   | ed VLSI Architecture                                       | 9  |

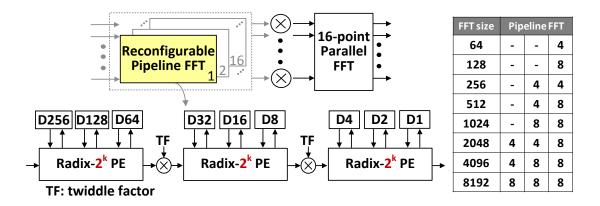

|    |                | 6.3.1    | Energy-Area Efficient Reconfigurable FFT                   | :0 |

|    |                | 6.3.2    | Energy Efficient CIC Filter                                | 21 |

|    |                | 6.3.3    | Summary of the Design Optimization                         | 5  |

|    | 6.4            | Chip I   | mplementation                                              | 27 |

|    |                | 6.4.1    | FPGA-aided Verification                                    | 27 |

|    |                | 6.4.2    | Measurement Results                                        | :9 |

|    |                | 6.4.3    | Performance Comparison                                     | 3  |

|    | 6.5            | Summ     | ary                                                        | 3  |

|    |                |          |                                                            |    |

| 7  | Con            | clusions | 5                                                          | 5  |

|    | 7.1            | Resear   | ch Contributions                                           | 6  |

|    | 7.2            | Future   | Work                                                       | 8  |

| References | .40 |

|------------|-----|

|------------|-----|

# LIST OF FIGURES

| 1.1 | Spectrum allocation of the United States                                      |

|-----|-------------------------------------------------------------------------------|

| 1.2 | Measurement of 0-6 GHz spectrum utilization at BWRC [4] 3                     |

| 1.3 | Interferer in-band power and spectral leakage                                 |

| 2.1 | Interferer in-band power and spectral leakage                                 |

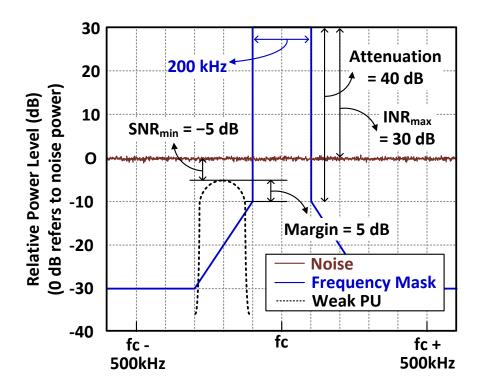

| 3.1 | Maximum tolerable INR. For a 200 kHz wireless microphone primary              |

|     | user, the maximum INR is constrained by 30 dB                                 |

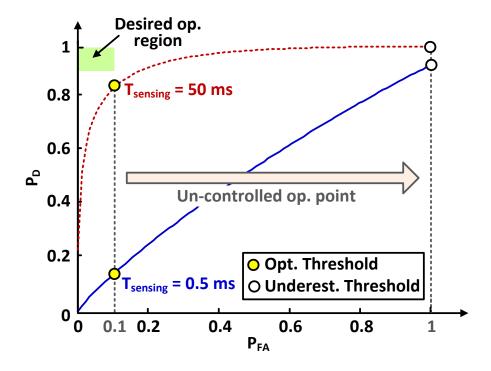

| 3.2 | Receiver operating characteristic of the conventional rectangular-windowed    |

|     | FFT power detector for sensing times of 0.5 ms (solid line) and 50 ms         |

|     | (dashed line). The strong adjacent-band interferers and the weak band-        |

|     | of-interest signal are 30-dB INR and -5-dB SNR, respectively 21               |

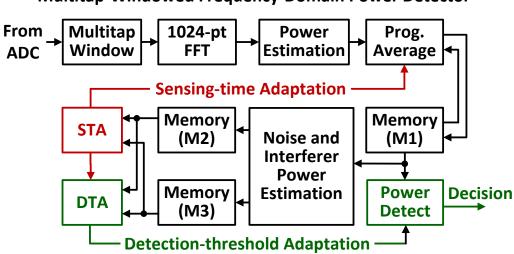

| 3.3 | Block diagram of the proposed wideband spectrum sensing proces-               |

|     | sor. The processor consists of a multitap-windowed frequency-domain           |

|     | power detector for PSD estimation, sensing-time adaptation for optimal        |

|     | sensing time, and detection-threshold adaptation for desired sensing rate. 24 |

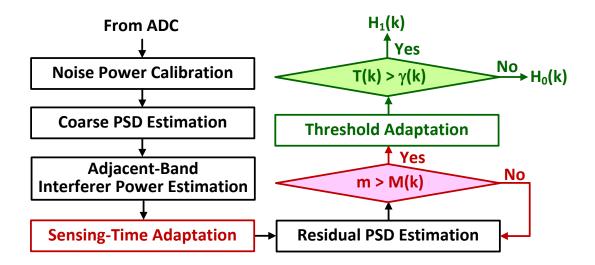

| 3.4 | Wideband spectrum sensing procedure                                           |

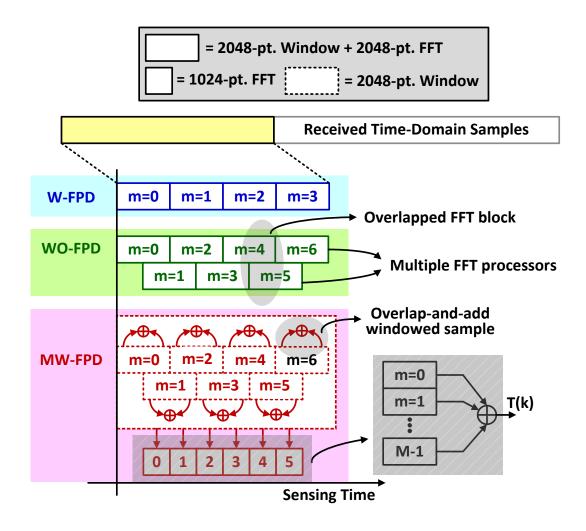

| 3.5 | Detection procedure for the windowed frequency-domain power detec- |

|-----|--------------------------------------------------------------------|

|     | tor (W-FPD), the windowed-overlapped frequency-domain power de-    |

|     | tector (WO-FPD), and the proposed multitap-windowed frequency do-  |

|     | main power detector (MW-FDP)                                       |

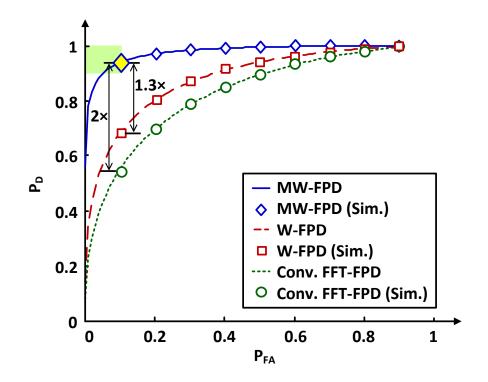

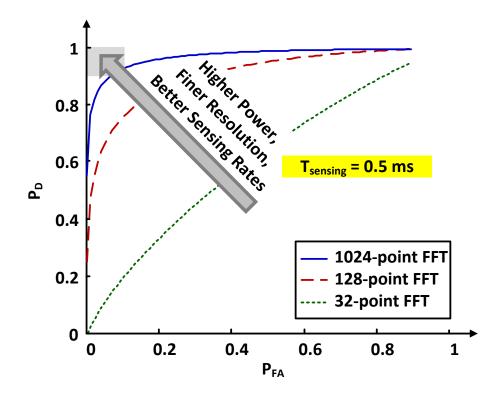

- 3.6 Receiver operating characteristic curves for different power detectors.The multitap-windowed frequency-domain power detector achieves the best detection rate.33

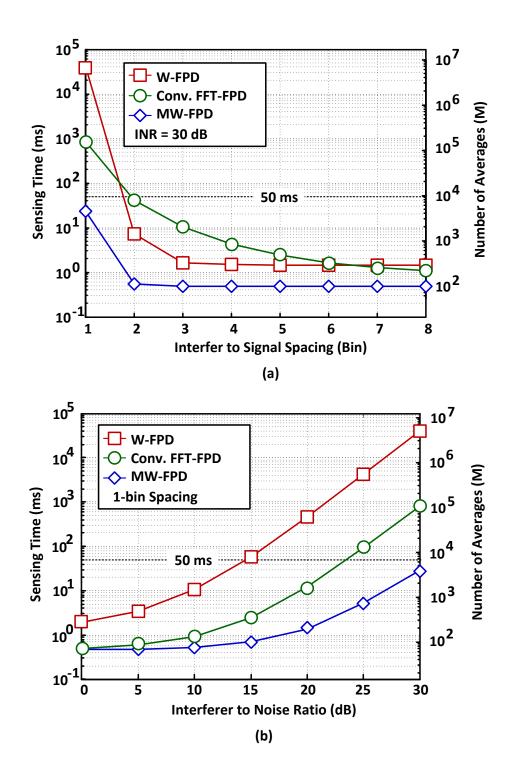

- 3.7 Required sensing time for conventional FFT power detector, windowed frequency-domain power detector, and multitap-windowed frequency-domain power detector as a function of interferer-to-signal spacing (a) and interferer-to-noise ratio (b). The proposed multitap-windowed power detector requires the least sensing time to reach a given detection rate. 34

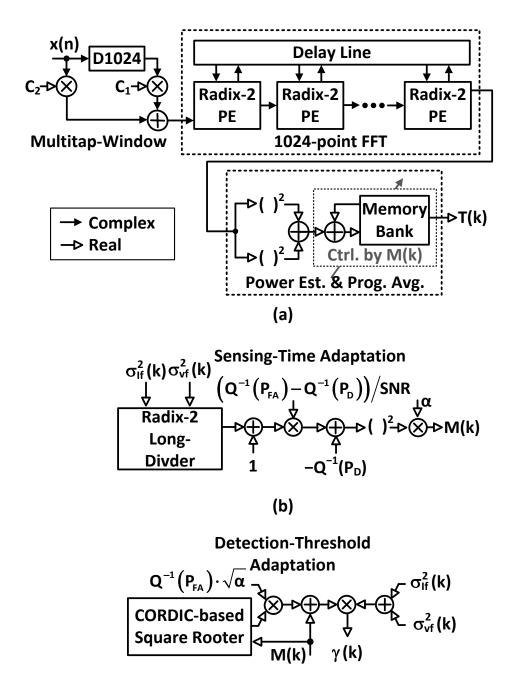

- 3.9 A VLSI architecture for the proposed spectrum sensing algorithms.(a) Multitap-windowed frequency-domain power detection block. (b)Sensing-time adaptation block. (c) Detection-threshold adaptation block. 40

- 3.10 Improvement in detection performance as a function of frequency resolution for a 6 MHz DTV signal. Larger FFT size with higher frequency resolution results in better sensing rates.

42

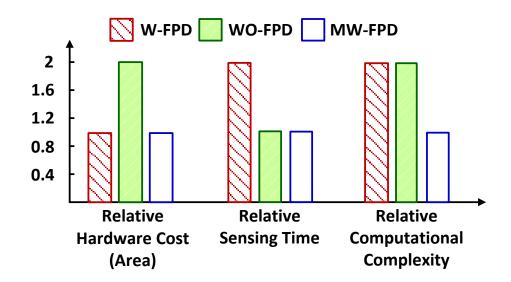

| 3.11 | Comparison of relative hardware cost, sensing time, and computation           |    |

|------|-------------------------------------------------------------------------------|----|

|      | complexity for W-FPD, WO-FPD, and MW-FDP                                      | 45 |

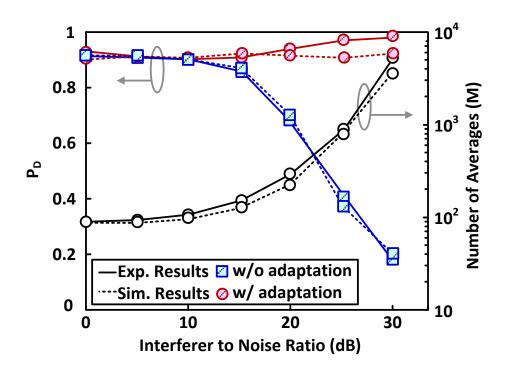

| 3.12 | $P_D$ and number of averages versus INR                                       | 48 |

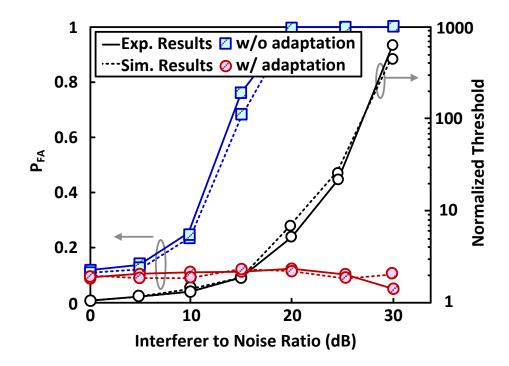

| 3.13 | $P_{FA}$ and detection threshold versus INR                                   | 48 |

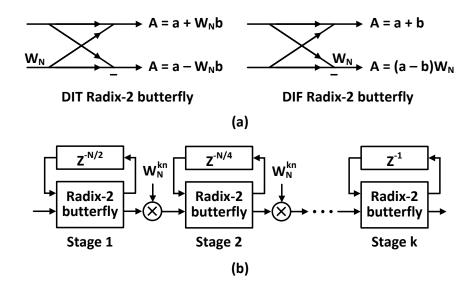

| 4.1  | (a) Signal flow graph of radix-2 butterfly for DIT and DIF structures.        |    |

|      | (b) Radix- $2^k$ single-path delay feedback (SDF) architecture. Output of     |    |

|      | stage k does not need twiddle-factor multiplication                           | 55 |

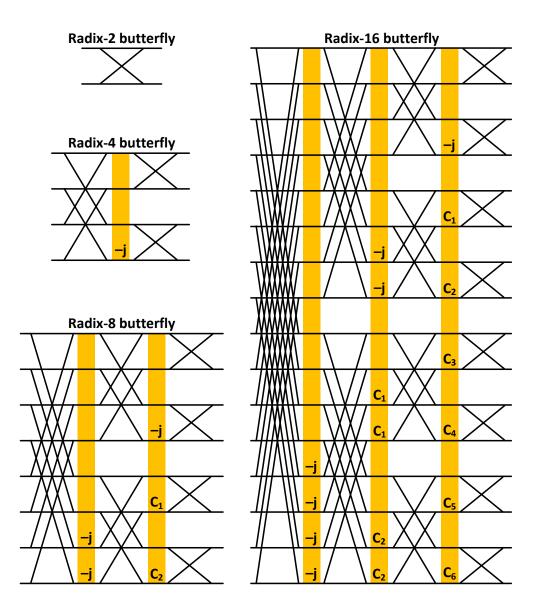

| 4.2  | Radix-2, radix- $2^2$ , radix- $2^3$ , and radix- $2^4$ butterfly operations  | 58 |

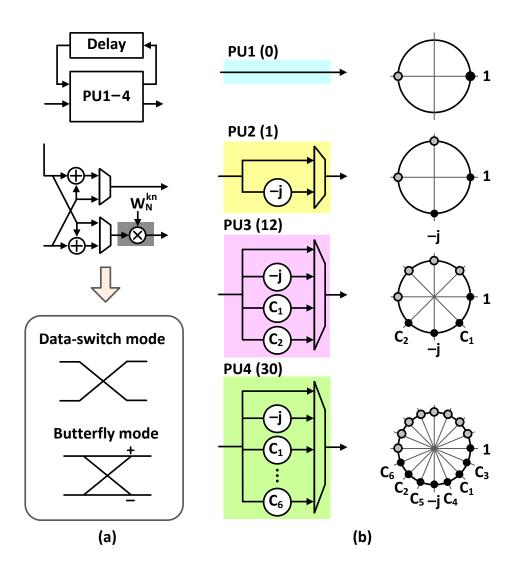

| 4.3  | Processing units (PUs) of a reconfigurable FFT processor that supports        |    |

|      | radix-2 to radix- $2^4$ factorizations. (a) The architecture and (b) the con- |    |

|      | stant multipliers of the PUs. The numbers in brackets next to each PU         |    |

|      | indicate relative cost (in terms of equivalent adders) of its constant mul-   |    |

|      | tiplier                                                                       | 60 |

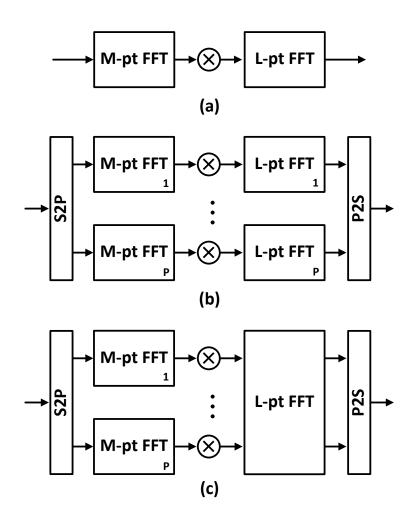

| 4.4  | (a) Reference N-point ( $N = M \times L$ ) FFT architecture. (b) Parallel ar- |    |

|      | chitecture. The level of parallelism = $P$ . (c) A significant reduction in   |    |

|      | complexity is achieved when $P = L$                                           | 63 |

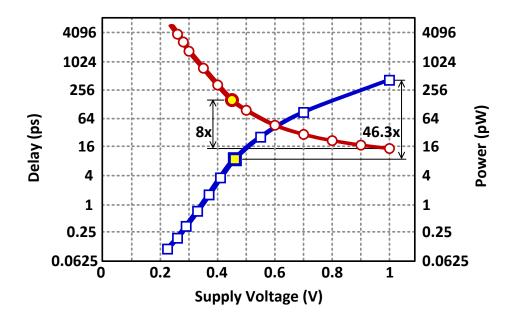

| 4.5  | Delay and energy vs. supply voltage for a FO-4 inverter in TSMC 65nm          |    |

|      | CMOS                                                                          | 65 |

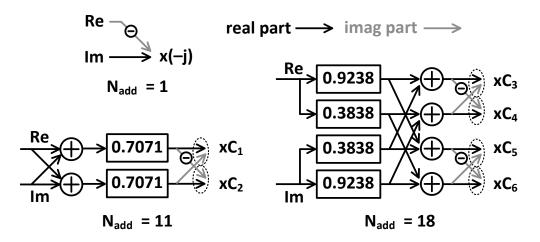

| 4.6  | Area-efficient implementation of constant multipliers                         | 67 |

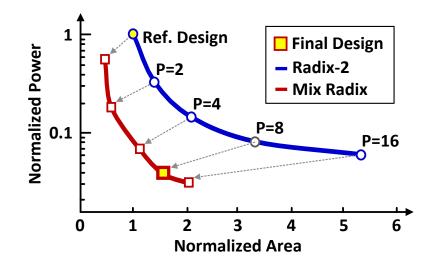

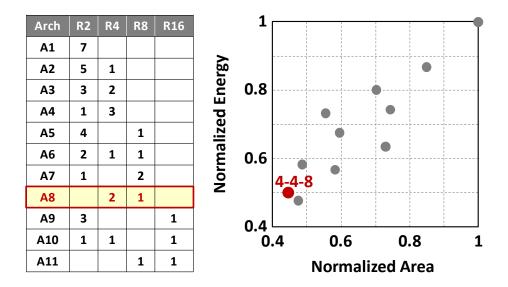

| Power and area minimization through FFT factorization and radix fac-          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| torization                                                                    | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Power and area for feasible radix factorizations of 128-point FFT. Ar-        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| chitecture A10 has the lowest power-area product                              | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

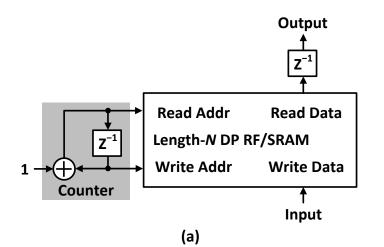

| (a) Dual-port RF-based delay buffer and (b) pointer-based DFF-based           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| delay buffer                                                                  | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

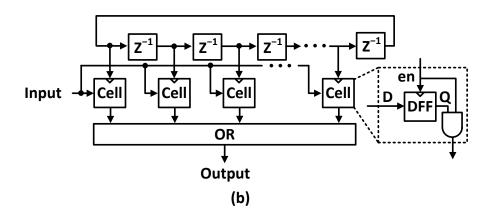

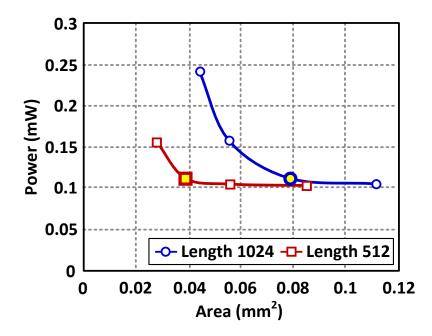

| Power-area product of delay buffers: D flip-flops (DFFs) are used for         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| delay lengths of 128 and 256, register files (RF) are used for delay          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| lengths of 512 and 1024                                                       | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Power-area tradeoff for feasible memory partitions. Partitions $2 \times 256$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| for length 512 and $4 \times 256$ for length 1024 delay buffers yield minimum |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| power-area product                                                            | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

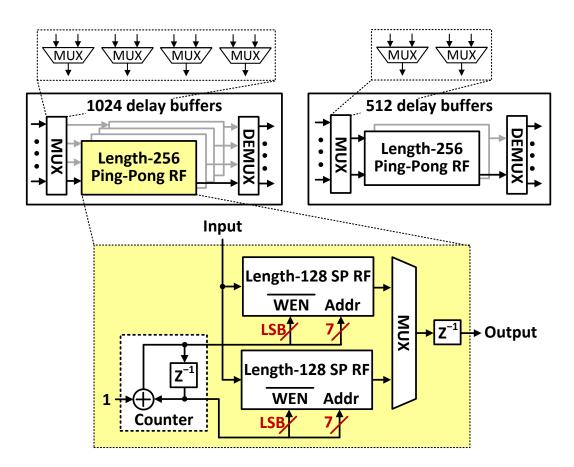

| Memory architecture for length 512 and 1024 delay buffers                     | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

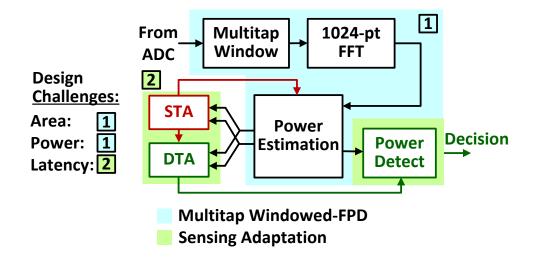

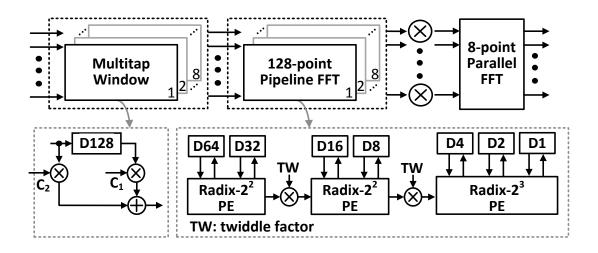

| Proposed wideband spectrum sensing processor. An FFT-based multi-             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| tap windowed frequency power detector estimates PSD, noise and inter-         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| fering power. Sensing-time adaptation (STA) and detection-threshold           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                               | torization.       Power and area for feasible radix factorizations of 128-point FFT. Ar-         chitecture A10 has the lowest power-area product.       .         (a) Dual-port RF-based delay buffer and (b) pointer-based DFF-based         delay buffer.       .         Power-area product of delay buffers: D flip-flops (DFFs) are used for         delay lengths of 128 and 256, register files (RF) are used for delay         lengths of 512 and 1024.         Power-area tradeoff for feasible memory partitions. Partitions 2 × 256         for length 512 and 4 × 256 for length 1024 delay buffers yield minimum         power-area product.         Memory architecture for length 512 and 1024 delay buffers.         Proposed wideband spectrum sensing processor. An FFT-based multi-         tap windowed frequency power detector estimates PSD, noise and inter- |

### adaptation (DTA) blocks adapt their parameters on a per-channel basis. . 80

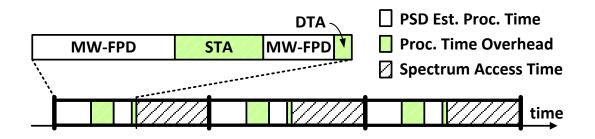

| 5.2 | Processing time for spectrum sensing consists of fixed time for MW-     |    |

|-----|-------------------------------------------------------------------------|----|

|     | FPD calculation and variable time for STA and DTA blocks. The MW-       |    |

|     | FPD determines the sensing rate performance. The overhead intro-        |    |

|     | duced by the STA and DTA blocks degrades the sensing-time efficiency    |    |

|     | and has to be minimized.                                                | 81 |

| 5.3 | Architecture of the frequency-domain power detector                     | 83 |

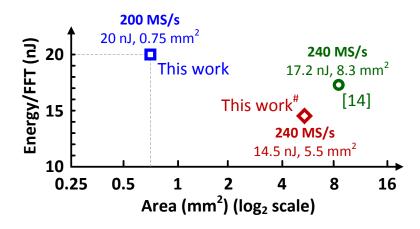

| 5.4 | Comparison of 1024-point FFTs. Our chip that minimizes power-area       |    |

|     | product is measured at 200 MS/s. At 240 MS/s, our fully synthesized (#  |    |

|     | indicates synthesis estimate) mix-radix design optimized for minimum    |    |

|     | energy achieves lower energy and lower area than the custom radix-4     |    |

|     | subthreshold design from [80]                                           | 83 |

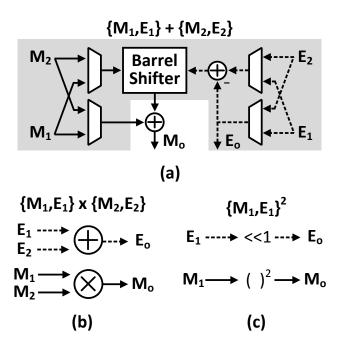

| 5.5 | Realization of floating-point operations: (a) addition, (b) multiplica- |    |

|     | tion, (c) squaring by using 2's complement operators. M1 and M2 in-     |    |

|     | dicate mantissas, E1 and E2 indicate exponents. Blocks in the shaded    |    |

|     | area in (a) perform the exponent matching                               | 86 |

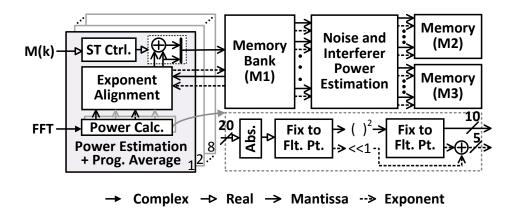

| 5.6 | Architecture of the power estimation block.                             | 87 |

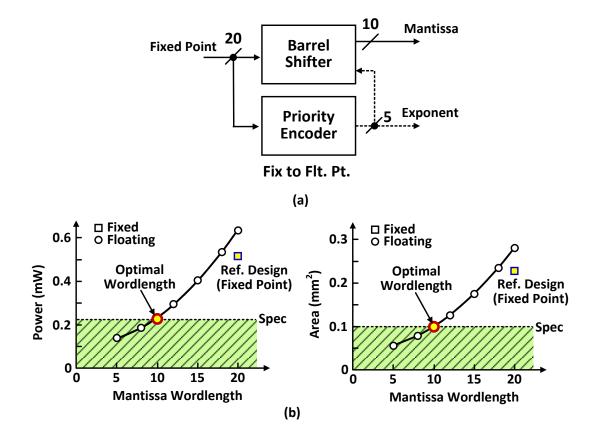

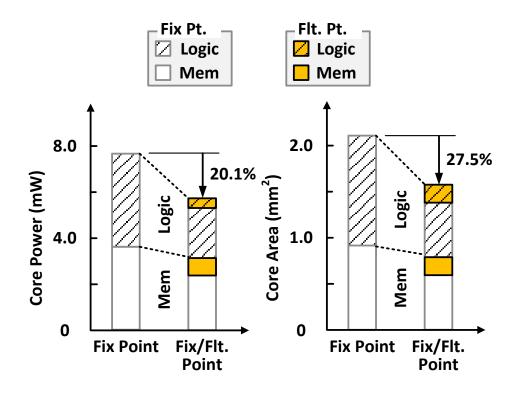

| 5.7 | (a) Architecture of fixed-point to floating-point conversion. The barrel |

|-----|--------------------------------------------------------------------------|

|     | shifter generates 10-bit mantissa, the priority encoder generates 5-bit  |

|     | exponent. (b) The plots of logic power and logic area of the power       |

|     | estimation block vs. mantissa wordlength show that the sensing per-      |

|     | formance spec is met with 10-bit mantissa. The floating-point format     |

|     | results in a 2x logic power reduction and a 2x logic area reduction as   |

|     | compared to the fixed-point reference design                             |

|     |                                                                          |

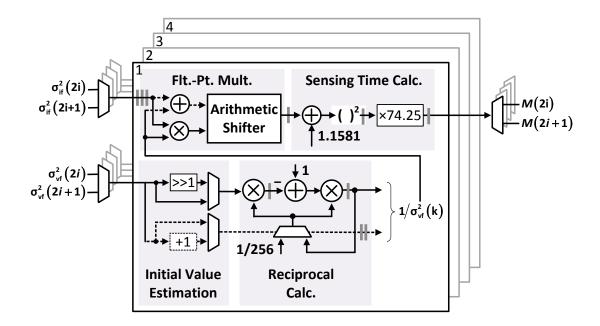

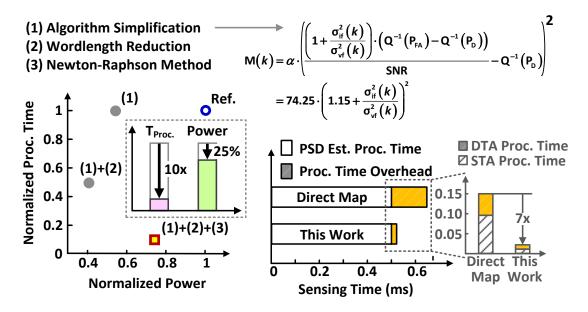

- 5.9 Architecture of the sensing-time-adaptation block. The initial-value estimation and the reciprocal calculation are performed using Newton-Raphson algorithm. Bounded sensing time allows for 10-bit output instead of full-precision 20-bit dictated by the input wordlength. . . . . 92

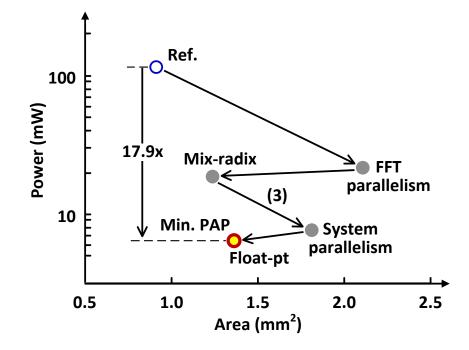

- 5.11 Summary of the optimization procedure. Parallelism with voltage scaling and radix factorization with power-area optimized delay lines are applied to the FFT block. Parallelism with voltage scaling is also applied at the system level. Floating-point signal processing with wordlength reduction is applied to STA and DTA blocks. An overall 17.9x reduction in power and 11.9x reduction in power-area product are achieved. 94

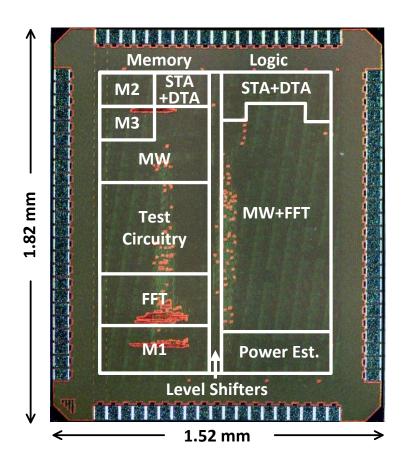

- 5.12 Chip micrograph of wideband spectrum sensing processor. . . . . . . . . 95

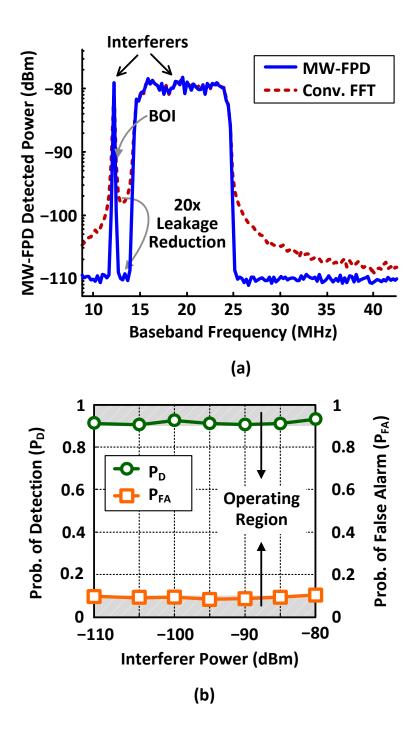

- 5.14 (a) Measured PSD estimated by MW-FPD. Two 30-dB interferers are present 2 bins away from the band of interest. The interfering power is suppressed by 20x using multitap windowing as compared to traditional FFT-based PSD estimation. (b) Measured  $P_D$  and  $P_{FA}$  as a function of adjacent-band interferer power ( $0 \le INR \le 30dB$ ) for SNR = -5 dB. STA and DTA blocks effectively maintain  $P_D \ge 0.9$  and  $P_{FA} \le 0.1$ . . . . 98

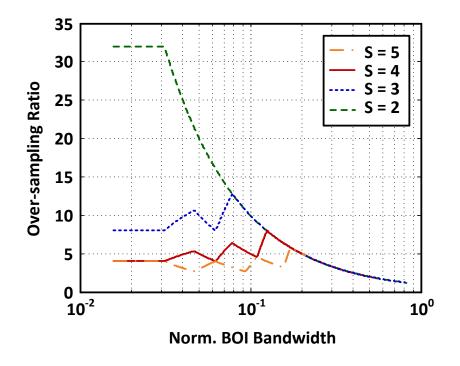

| 6.4  | Required up-sampling ratio with respect to different band-of-interest    |

|------|--------------------------------------------------------------------------|

|      | bandwidths and cascaded stages                                           |

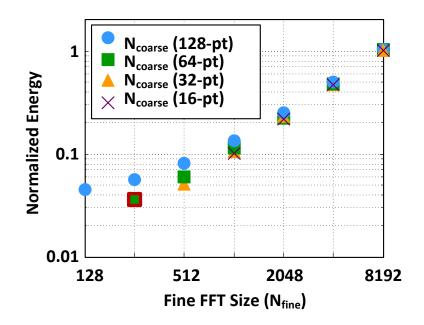

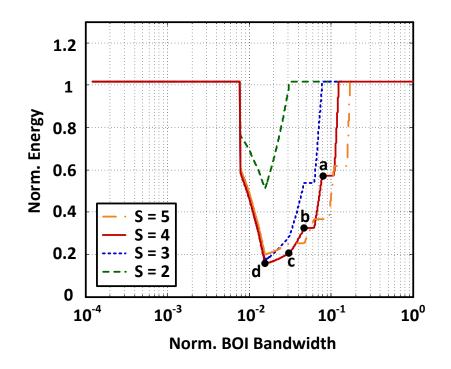

| 6.5  | Normalized energy with respect to band-of-interest bandwidth. Dif-       |

|      | ferent fine-sensing FFT configurations are shown: a) 4096-point, b)      |

|      | 2048-point, c) 1024-point, d) 512-point                                  |

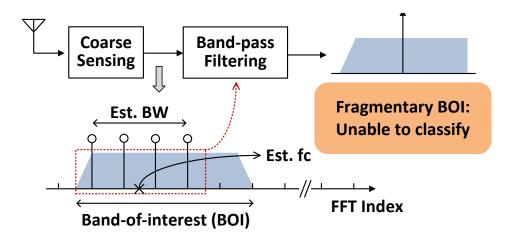

| 6.6  | Bandwidth and carrier frequency estimation by the binary decision re-    |

|      | sults. The underestimated bandwidth makes the DSP processor unable       |

|      | to classify the signals                                                  |

| 6.7  | The probability of having at most x consecutive zeros among b occu-      |

|      | pied channels                                                            |

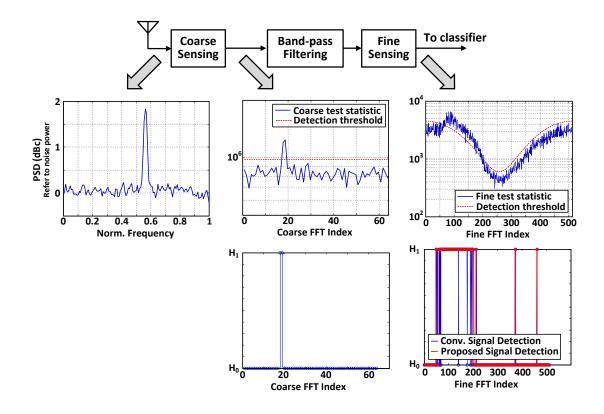

| 6.8  | A design example. (a) Power spectrum density of the wideband sce-        |

|      | nario. (b) Estimated PSD and the detection threshold of coarse sensing.  |

|      | (c) Binary decision result from coarse sensing. (c) Estimated PSD and    |

|      | the detection threshold of fine sensing. (e) Binary decision result from |

|      | fine sensing                                                             |

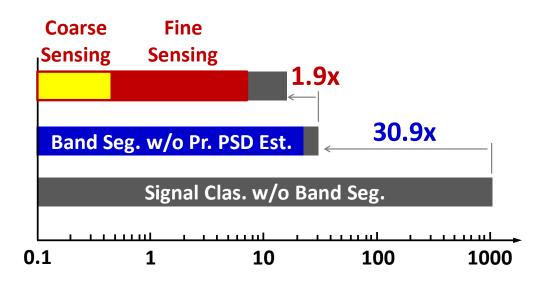

| 6.9  | Energy-efficient band segmentation, which consists of coarse sensing     |

|      | and fine sensing. Coarse sensing is to select band-of-interest, and fine |

|      | sensing is to channelize the selected band with finer resolution 120     |

| 6.10 | A multi-path pipelined reconfigurable FFT with optimal parallelism       |

|      | and radix-factorization                                                  |

| 6.11 | Comparison with the state-of-the-art FFTs                                |

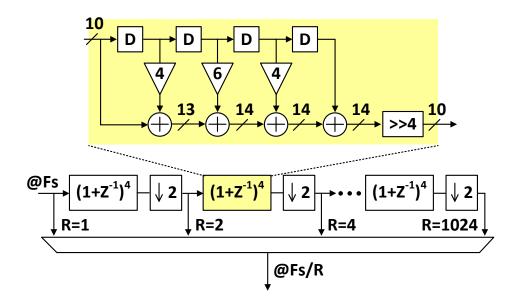

| 6.12 | 4 <sup>th</sup> -order feed-forward CIC filter, supporting down-sampling ratio up |

|------|-----------------------------------------------------------------------------------|

|      | to 1024, amenable to parallelism with smaller wordlength                          |

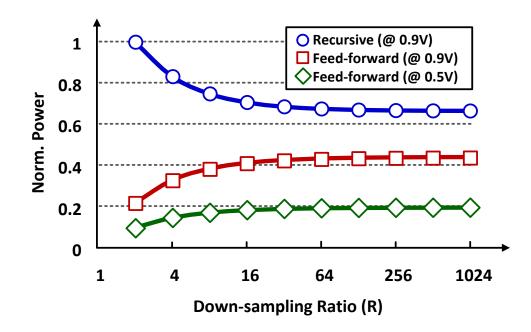

| 6.13 | Power saving from the feed-forward architecture                                   |

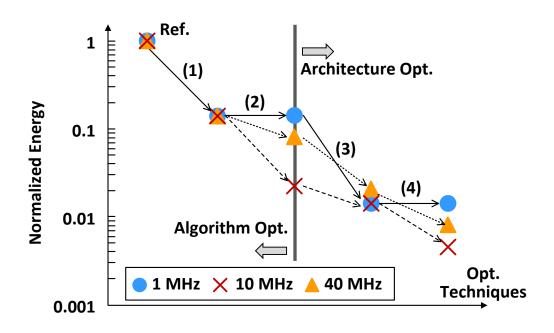

| 6.14 | Summary of design optimization for signal bandwidth of 1 MHz, 10MHz,              |

|      | and 40 MHz. Four techniques are used to improve energy efficiency. 1)             |

|      | Miss-detection tolerant signal detection. 2) Partial PSD estimation. 3)           |

|      | 16-way paralllelism and optimal radix factorization. 4) Feed-forward              |

|      | CIC filter architecture                                                           |

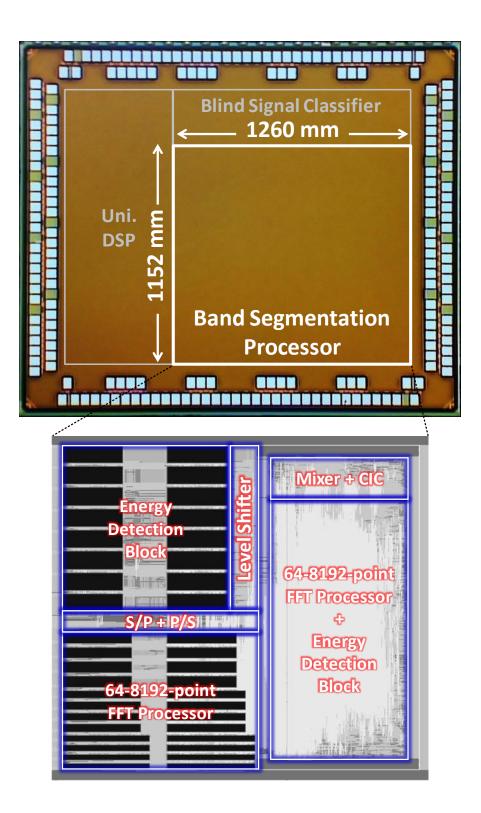

| 6.15 | Chip micrograph and the layout of the band segmentation processor 128             |

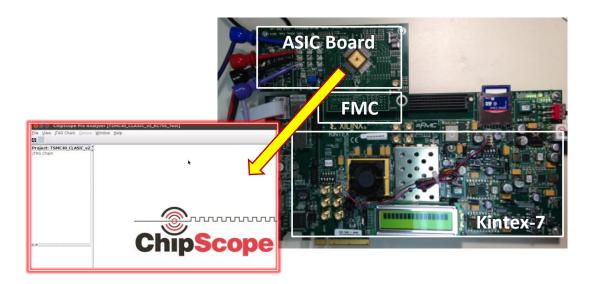

| 6.16 | FPGA-aided I/O verification. Test vectors are stored on the FPGA                  |

|      | board. The results are sampled and verified in real-time by using Xilinx          |

|      | ChipScope                                                                         |

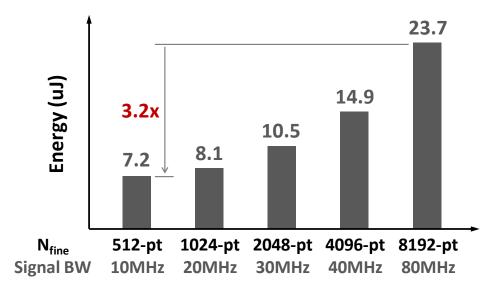

| 6.17 | Measured energy with respect to different signal bandwidths. A maxi-              |

|      | mum 3.2x saving in energy is achieved by using partial PSD estimation             |

|      | algorithms                                                                        |

| 6.18 | Measured energy with respect to different signal bandwidths. A maxi-              |

|      | mum 3.2x saving in energy is achieved by using partial PSD estimation             |

|      | algorithms                                                                        |

# LIST OF TABLES

| 3.1 | Wideband CR System Specification                                                                         |

|-----|----------------------------------------------------------------------------------------------------------|

| 3.2 | Hardware Complexity Estimates of W-PFD, WO-FPD, and MW-FPD . 44                                          |

| 3.3 | FPGA Hardware Resource Breakdown for MW-FPD                                                              |

| 3.4 | Comparison with State-of-the-Art Power-Detector ASICs                                                    |

| 4.1 | Radix Implementations of Radix-2, Radix-2 <sup>2</sup> , Radix-2 <sup>3</sup> , and Radix-2 <sup>4</sup> |

|     | Processing Elements                                                                                      |

| 4.2 | The Number of Equivalent Adders Required to Implement FFT 69                                             |

| 5.1 | Summary of Chip Features                                                                                 |

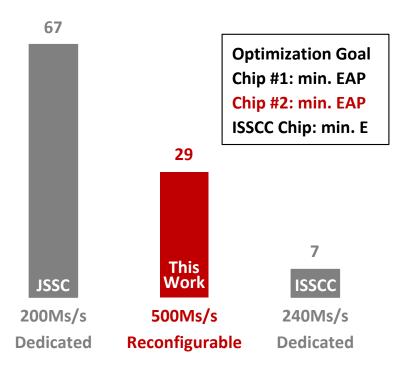

| 5.2 | Comparison with Prior Work                                                                               |

| 6.1 | Wideband CR System Specification                                                                         |

| 6.2 | Summary of Chip Features                                                                                 |

| 6.3 | Comparison with Prior Work                                                                               |

#### ACKNOWLEDGMENTS

My sincere gratitude goes to my advisors, Professor Dejan Marković and Professor Danijela Čabrić. Their stimulating guidance has sparked many ideas that carried my research. Dejan's constant drive for his students to succeed is truly exceptional, and I would not be typing this if it were not for him. The rightness and enthusiasm have been with me at every step along the way. Danijela's understanding and technical support has greatly transcended my knowledge about algorithm design. I am indebted to both of them for their faith in my research and their tolerance of my weaknesses. Their patient, trustful, and encouraging support has made me a better scholar and a better person. Professor Greg Pottie and Professor Milos D. Ercegovać provided thoughtful evaluation of my research proposal and review of this dissertation.

The multi-disciplinary, open minded setting of Parallel Data Architecture (PDA) Group and Cognitive Reconfigurable Embedded Systems (CORES) Lab created many opportunities to further develop my work in collaboration with others. Special gratitude goes to Chia-Hsiang Yang and Fang-Li Yuan. Chia-Hsiang has helped me get through pressures of graduate school and has been very supportive by sharing his wisdom and experience. I am thankful to Fang-Li for being a great roommate and for his support over year, and Fang-Li has been also a great friend since college. I am thankful to Oussama Sekkat for sharing the burden in setting up the BEE2 experiments. I am thankful to Henry Chen for sharing experience in using FPGA boards for ASIC test and debug. I am thankful to Paulo Isagani Urriza and Eric Rebeiz for doing wonderful jobs in DARPA CLASIC project. I am thankful to Chun-Hao Li for being a great lab mate and roommate. I am thankful to Cheng C. Wang for dividing suffering during the tape-out time. I am also thankful to my PDA lab mates Sina Basir-Kazeruni, Chaitali Biswas, Hariprasad Chandrakumar, Sarah Gibson , Vahagn Hokhikyan, Richard Dorrance, Vaibhav Karkare, Rashmi Nanda, Fengbo Ren, Dejan Rozgic, and Yuta Toriyama, and my CORES lab mates Wesam Gabran, Ali Shahed, Jason Tran, and Jun Wang for stimulating discussions and friendship.

Personal gratitude goes to Jung-Mao Lin and Santiago Rodriguez Parera for many inspiring technical discussions. I am indebted to their contributions in my very first paper. I appreciate working with Shang-Kee Ting and Zaid Towfic in DARPA HEALICS project.

This research was supported by the HEALICS/DARPA, CLASIC/DARPA programs and UCLA graduate fellowship.

Finally, and most importantly, I would like to express gratitude to my parents, my brother, and my dear fiancee. This work is a product of their endless love and continued support.

#### VITA

- 2001–2005 B.S. in Electrical Engineering, National Taiwan University, Taipei, Taiwan.

- 2005–2007 M.S. in Electronics Engineering, National Taiwan University, Taipei, Taiwan.

- 2008–2013 Research Assistant, Electrical Engineering Department, University of California, Los Angeles, California, USA.

#### PUBLICATIONS

T.-H. Yu, C.-H. Yang, D. Čabrić, and D. Marković, "A 7.4mW 200MS/s Wideband Spectrum Sensing Digital Baseband Processor for Cognitive Radios," *IEEE Journal of Solid-State Cicuits (JSSC)*, vol. 47, no. 9, pp. 2235-2245, Sep. 2012.

C.-H. Yang, T.-H. Yu, and D. Marković, "Power and Area Minimization of Reconfigurable FFT Processors: A 3GPP-LTE Example," *IEEE Journal of Solid-State Cicuits* (*JSSC*), vol. 47, no. 3, pp. 757-768, Mar. 2012.

T.-H. Yu, Oussama Sekkat, Santiago Rodriguez-Parera, D. Marković, and D. Čabrić, "A Wideband Spectrum-Sensing Processor with Adaptive Detection Threshold and Sensing Time," IEEE Transaction on Circuit and System-I (TCAS-I), vol. 58, no. 11, pp. 2765-2775, Nov. 2011.

T.-H. Yu, C.-H. Yang, D. Marković, and D. Čabrić, "An Energy-Efficient VLSI Architecture for Wideband Spectrum Sensing for Cognitive Radios," in *Proc. IEEE Global Telecommunications Conference (GLOBELCOM)*, Dec. 2011, pp. 1-6.

T.-H. Yu, C.-H. Yang, D. Čabrić, and D. Marković, "A 7.4mW 200MS/s Wideband Spectrum Sensing Digital Baseband Processor for Cognitive Radios," in *Proc. IEEE International Symposium on VLSI circuit (VLSI)*, June 2011, pp. 254-255.

T.-H. Yu, S. Rodriguez-Parera, D. Marković, and D. Čabrić, "Cognitive Radio Wideband Spectrum Sensing Using Multitap Windowing and Power Detection with Threshold Adaptation," in *Proc. IEEE International Conference on Communications (ICC)*, May 2010, pp. 1-6.

C.-H. Yang, T.-H. Yu, D. Marković, "A 5.8mW 3GPP-LTE Compliant 88 MIMO Sphere Decoder Chip with Soft-Outputs," in *Proc. IEEE International Symposium on VLSI circuit (VLSI)*, June 2010, pp. 209-210.

## **CHAPTER 1**

### Introduction

#### **1.1 Cognitive Radios**

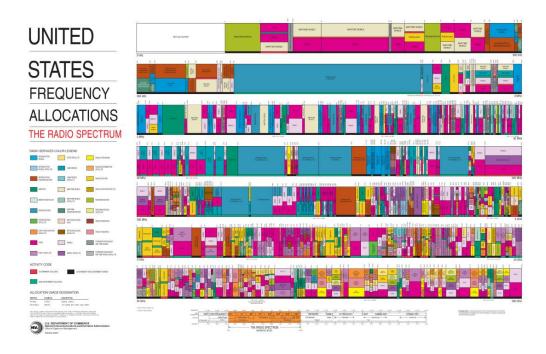

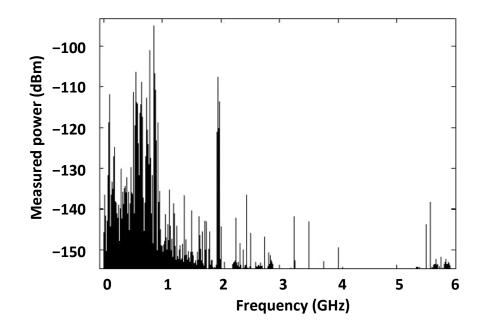

Wireless technology is rapidly proliferating into all aspects of daily life, and the demand for wireless connectivity is ever increasing. Higher and higher data rates are required for real-time and high-quality data transmission, with a rapid increase in the number of wireless devices. Till now, only specific users are allowed to access the wireless resources based on the spectrum polices. Figure 1.1 shows the spectrum allocation of the United States, where most of the radio spectrum is assigned to licensed users. This fixed spectrum allocation, however, does not guarantee the spectrum is efficiently utilized at all times. As indicated by numerous reports [1-4], the usage of the spectral resources is significantly under-utilized. A survey [1] reported in 2002 showed that, on average, only 2% of allocated spectrum in the United States is in use at any given moment. Another report [3], based on the measurement for the frequency bands below 3 GHz from January 2004 to August 2005, concluded that the averaged spectrum occupancy is only about 5.2%. Figure 1.2 [4], conducted by Berkeley Wireless Research Center (BWRC) over frequency bands from 0 to 6 GHz, illustrates the frequency bands

Figure 1.1: Spectrum allocation of the United States.

beyond 2 GHz are highly under-utilized.

Dynamic spectrum access with cognitive radios (CRs), introduced by Joseph Mitola III [5], is a promising solution to improve the efficiency of spectrum utilization. Cognitive radio is defined as a wireless communication system that is aware of its surrounding electromagnetic environment, has artificial intelligence to surveil the spectrum utilization, and finally adapts to the current environment to provide the most appropriate wireless services. Cognitive radios sense the electromagnetic environment to reliably detect the presence of legitimate users, which have higher priorities of spectrum usage, in order to avoid harmful interference and then utilize the remaining spectrum holes.

CR technology has been standardized in November 2004, the IEEE 802.22 Working

Figure 1.2: Measurement of 0-6 GHz spectrum utilization at BWRC [4].

Group (WG) [6]. The IEEE 802.22 WG allows the development of physical (PHY) and medium access control (MAC) layers for the use by license-exempt devices in TV bands. The 802.22 admits license-exempt devices to reuse vacant TV spectrum without introducing any harmful interference to primary users. The 802.22 has a leading and key role for facilitating the CR development and its outcome will serve as the basis for new and innovative research in this promising area.

#### **1.2 Spectrum Sensing**

The enabling technology for CR systems is spectrum sensing, in which the presence of primary users is detected in the band of interest to avoid harmful interference. The key requirement for spectrum sensing is reliable signal detection, with high sensitivity within a constrained sensing time. The high sensitivity requirement prevents a CR system from causing interference to the primary users [7-13]. The sensitivity improves by increasing the sensing time, but a long sensing time reduces the effective time for communication on an unused primary channel, thus reducing the CR throughput. On the other hand, a short sensing time enhances the throughput but increases the chance of unintended collisions. The constrained sensing time balances the tradeoff between CR throughput and unintended collisions.

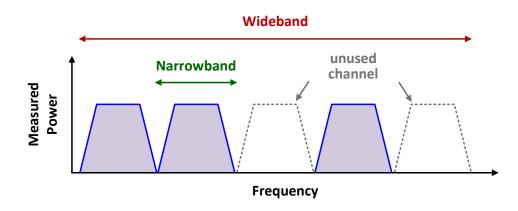

Wideband (> 100 MHz) sensing is a highly desirable feature of CR systems, since it allows for simultaneously sensing of multiple channels and thus increases the probability of finding available channel. Several algorithms have been proposed to resolve wideband spectrum sensing problem. Wideband sensing, however, imposes many design challenges at the physical layer [14-20]. The wideband front-end must have sufficient linearity to avoid mixing interferers into the band of interest [17-20]. The analogto-digital converter (ADC) requires high resolution to support large-dynamic-range signals and high sampling rate to adequately sample wideband spectrum [20]. In the digital baseband, the sensing processor needs to provide a reliable signal detection in a negative SNR regime while operating in real time [14-16]. The DSP baseband, therefore, must accommodate advanced signal processing algorithms within limited power and area. This dissertation focuses on development of a DSP baseband processor for wideband spectrum sensing.

Generally, the spectrum-sensing algorithms can be categorized into two types: energy (power) detection and feature detection.

Energy detection identifies the presence of signals by comparing the measured energy level to a threshold. The processing gain is proportional to the observation time T. Longer observation time improves the signal detection accuracy that enhance the detection performance. Energy detection is widely used for spectrum sensing because it is easy to implement and is able to detect noise level and interferers, without the knowledge of electromagnetic environment. However, several drawbacks of energy detection might diminish its implementation simplicity. First, the detection performance, false-alarm probability and detection probability, are highly susceptible to the changing noise level and the activity of interferers. The threshold used for energy detection needs to be decided carefully to keep a balance of false-alarm probability and detection probability. This problem becomes more serious in large-dynamic-range wideband spectrum sensing. Second, energy detection is unable to differentiate between modulated signals, noise, and interferers. Adaptive signal processing cannot be applied for cancelling the interferers. In addition, when the system is required to treat noise and other secondary users differently, more sophisticated signal processing algorithms need to be developed.

Feature detection identifies the channel occupancy by using the cyclostationary property of a modulated signal [21-25]. The cyclostationary property is commonly characterized by spectral correlation function [21-22]. Since only a modulated signal has a specific feature at a nonzero cyclic frequency, this feature can be used to differentiate background noise and modulated signals. In addition, different types of modulated signals (such as BPSK, QAM, FSK), even having the same power spectrum density function, have highly distinct spectral correlation functions. Thus, feature detection is able to distinguish modulated signals, noise, and interferers. Furthermore, signals with overlapping feature in their power spectrum have non-overlapping feature in their spectral correlation functions, indicating feature detection is able to differentiate overlapping signals as well. The computation complexity of feature detection, however, is much higher than energy detection [15]. As far as energy efficiency is concerned, feature detection is not feasible for real-time and low-cost implementation.

There are still other signal detection algorithms for wideband sensing, e.g. compressive spectrum sensing [26-32] or cooperative spectrum sensing [33-35]. Compressive sensing exploits spectrum scarcity and detects signals with sub-Nyquist sampling rates. Cooperative sensing improves detection performance by exploiting spatial diversity. [26-35] have shown these algorithms outperforming energy detection and feature detection. However, these algorithms are not applicable for low power implementation.

In this dissertation, we adopt energy detection with associated adaptation algorithms for reliable signal detection and energy-efficient implementation, making this design applicable to portable devices.

#### **1.3** Motivation for This Work

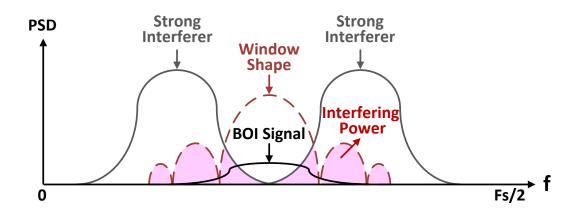

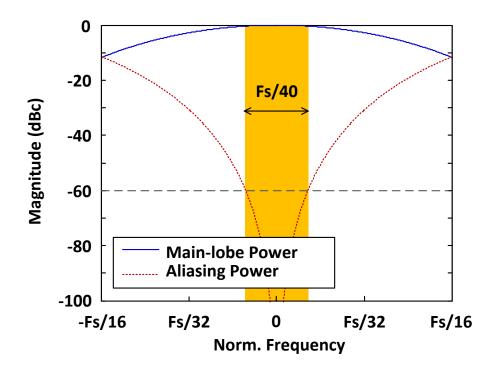

The major challenge of wideband spectrum sensing comes from the large-dynamicrange spectrum. Without notch filters for the detected spectrum, it is inevitable having both weak signals and strong blockers. The blockers might be strong primary users, or illegal or unexpected jammer. In the worst case, a weak signal with negative SNR, which is adjacent to two strong blockers, has to be detected. As shown in Fig. 1.3, under this scenario, an *interfering power* leaks into the band occupied by the weak signal. The interfering power comes from two sources. First, a modulated signals is shaped (by digital pulse-shaping and analog bandpass filters) in frequency according to a pre-defined frequency mask, which in reality is not a perfect brick-wall filter. As a result, the tail of the modulated signal spectrum might introduce significant interfering power in the adjacent band, provided that this modulated signal is very strong. Second, the time-domain received samples at the sensing processor are channelized with a non-ideal filter (e.g. FFT filterbank), which also causes spectral leakage. Both effects are represented by the shaded areas in Fig. 1.3. We call the combination of these two effects interfering power, which makes weak signal detection more difficult.

As energy detection is applied for wideband sensing, signal detection in real time is challenging because the detection performance is sensitive to the dynamic nature of electromagnetic environment. The threshold used for energy detection highly depends on the noise level and the activity of interferers. To accommodate the variation in background noise, an adaptive algorithm for the detection threshold needs to be designed. Also, with the presence of strong adjacent-band blockers, the detection threshold needs to be adapted to the channel condition. In addition to developing adaptive algorithms, the detection threshold needs to be channel-specific and adapted to real-time measured data.

Real-time and large-dynamic-range signal processing not only imposes challenges

Figure 1.3: Interferer in-band power and spectral leakage.