#### UNIVERSITY OF CALIFORNIA

## Los Angeles

General, Flexible and Unified Near-Data Computing

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

Zhengrong Wang

#### ABSTRACT OF THE DISSERTATION

General, Flexible and Unified Near-Data Computing

by

Zhengrong Wang

Doctor of Philosophy in Computer Science

University of California, Los Angeles, 2023

Professor Anthony John Nowatzki, Chair

Over the past decades, the memory hierarchy has increasingly become the bottleneck in general-purpose processors due to a widening gap between the growing demand for large data and the much slower scaling of conventional memory hierarchies. Therefore, conventional in-core computing suffers from increasingly expensive overheads such as excessive request messages, unnecessary data movement and coherence traffic, as well as limited off-chip bandwidth, to bring the data from memory to computing cores. To continue the performance and energy efficiency scaling, architects propose near-data computing (NDC) in which computations are offloaded to where the data is. However, existing NDC techniques fall short of providing generality and flexibility across different application domains, programming paradigms, computing substrates, which are crucial to the wide adoption of NDC.

Our key insight is that the critical missing cornerstone for general and flexible near-data computing is a novel rich-semantic memory abstraction. Unlike existing byte-grained load/store operations, the new interface should express a wide range of rich semantics such as the access pattern, reuse distance, near-data computations, etc. Such high-level information is essential for the system to promptly recognize the program's long-term behavior and

adjust accordingly to reach optimal states. More importantly, the new interface should be as transparent as possible to programmers with automatic compiler analysis and runtime library support. Based on this, we can fundamentally revolutionize the memory interface and co-optimize computation and data together.

This dissertation explores a new ISA interface - streams - to precisely capture the program's long-term memory and compute activities. Streams are incorporated into the program's functional semantics and are exposed to the entire system stack to guide various policies. Our evaluation and analysis suggest serval key findings. First, a set of useful and prevalent stream patterns cover a wide range of program behaviors and can be embedded into the program in a lightweight way while still maintaining the sequential ordering. Second, streams naturally decouple the address generation and computation from the core pipeline and can be offloaded as the basic unit for near-data computing. Third, by exposing high-level semantics to the system, we can unify different computing paradigms and codesign the software and data structure. Overall, this dissertation aims to enable a general and end-to-end near-data computing system that wipes out the boundary between computation and data – the computation is freely scheduled in the system near the data, and the data is carefully mapped to the memory resources to provide maximal locality and parallelism. Such data-computation orchestration is the key to continuing the performance and energy efficiency scaling.

The dissertation of Zhengrong Wang is approved.

Harry Guoqing Xu

Glenn D. Reinman

Todd D. Millstein

Anthony John Nowatzki, Committee Chair

University of California, Los Angeles 2023

To my parents...

## TABLE OF CONTENTS

| 1 | Intr                                          | roduction                         | 1                                |

|---|-----------------------------------------------|-----------------------------------|----------------------------------|

|   | 1.1                                           | Existing Near-Data Computing      | 3                                |

|   | 1.2                                           | Near-Stream Computing             | 9                                |

|   | 1.3                                           | Contributions                     | 10                               |

|   | 1.4                                           | Organization                      | 13                               |

| 2 | Stre                                          | eam Basics                        | 14                               |

|   | 2.1                                           | Stream Characterization           | 14                               |

|   | 2.2                                           | Decoupled-Stream ISA              | 18                               |

|   | 2.3                                           | Near-Stream Computing Abstraction | 24                               |

|   | 2.4                                           | Compiler Support                  | 27                               |

|   |                                               |                                   |                                  |

| 3 | Stre                                          | eam-Specialized Processors        | 32                               |

| 3 | <b>Stre</b> 3.1                               | eam-Specialized Processors        | <b>32</b>                        |

| 3 |                                               |                                   |                                  |

| 3 | 3.1                                           | Stream Specialization Overview    | 32                               |

| 3 | 3.1                                           | Stream Specialization Overview    | 32<br>35                         |

| 3 | 3.1<br>3.2<br>3.3                             | Stream Specialization Overview    | 32<br>35<br>39                   |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5               | Stream Specialization Overview    | 32<br>35<br>39<br>43             |

| 3 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5               | Stream Specialization Overview    | 32<br>35<br>39<br>43<br>45       |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | Stream Specialization Overview    | 32<br>35<br>39<br>43<br>45<br>51 |

|   | 4.2  | Stream Floating Design                        | 62  |

|---|------|-----------------------------------------------|-----|

|   | 4.3  | Coherence and Consistency                     | 70  |

|   | 4.4  | Methodology                                   | 73  |

|   | 4.5  | Evaluation                                    | 75  |

|   | 4.6  | Related Work                                  | 82  |

|   | 4.7  | Summary                                       | 84  |

| 5 | Nea  | ar-Stream Computing                           | 85  |

|   | 5.1  | Motivation and Overview                       | 85  |

|   | 5.2  | In-Core Near-Stream Computing                 | 95  |

|   | 5.3  | Near-Stream Computing                         | 97  |

|   | 5.4  | Synchronization-Free Optimization             | 105 |

|   | 5.5  | Methodology                                   | 106 |

|   | 5.6  | Evaluation                                    | 109 |

|   | 5.7  | Additional Related Work                       | 117 |

|   | 5.8  | Summary                                       | .19 |

| 6 | Affi | nity Alloc: Taming Not-So Near-Data Computing | 20  |

|   | 6.1  | Motivation and Overview                       | 21  |

|   | 6.2  | Affine Data Layout                            | 130 |

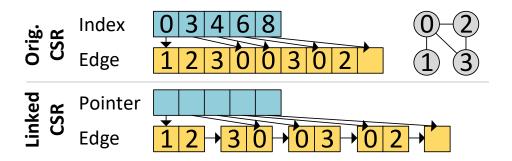

|   | 6.3  | Irregular Data Layout                         | 137 |

|   | 6.4  | Methodology                                   | L41 |

|   | 6.5  | Evaluation                                    | 143 |

|   | 6 6  | Discussion                                    | ırn |

|              | 6.7   | Related Work                 | 153 |

|--------------|-------|------------------------------|-----|

|              | 6.8   | Summary                      | 155 |

| 7            | In-/  | Near-Memory Computing Fusion | 156 |

|              | 7.1   | Background and Overview      | 157 |

|              | 7.2   | Infinity Stream Abstraction  | 163 |

|              | 7.3   | Runtime Support              | 172 |

|              | 7.4   | Microarchitecture Extensions | 179 |

|              | 7.5   | Implementation Limitations   | 184 |

|              | 7.6   | Methodology                  | 184 |

|              | 7.7   | Evaluation                   | 187 |

|              | 7.8   | Related Work                 | 195 |

|              | 7.9   | Summary                      | 197 |

| 8            | Con   | clusion                      | 198 |

| $\mathbf{A}$ | ND    | C Related Works              | 205 |

| В            | tDF   | G Optimization               | 210 |

| D,           | oforo | nces                         | 216 |

### LIST OF FIGURES

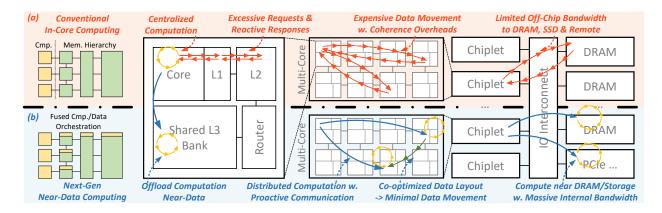

| 1.1  | Conventional In-Core (Top) vs. Future Near-Data Computing (Bottom)     | 3  |

|------|------------------------------------------------------------------------|----|

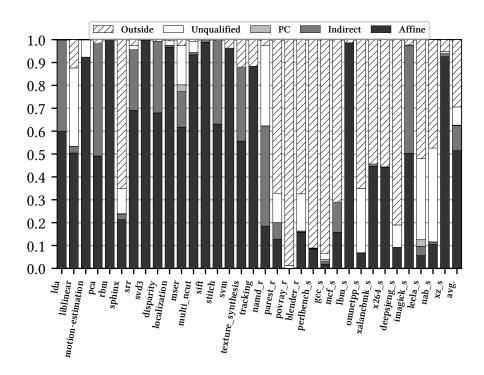

| 2.1  | Stream Breakdown (PC: Pointer-Chasing)                                 | 16 |

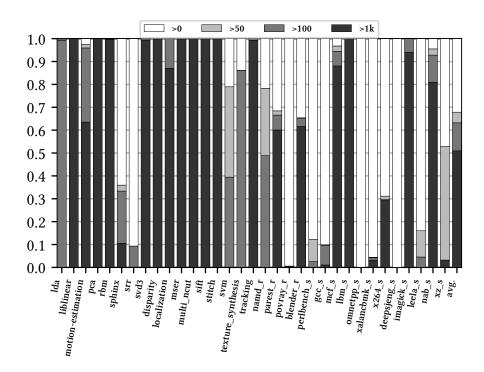

| 2.2  | Average Stream Length                                                  | 17 |

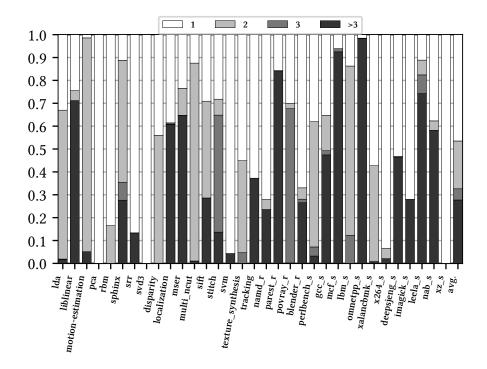

| 2.3  | Number of Control Paths                                                | 18 |

| 2.4  | Decoupled Stream ISA Examples                                          | 21 |

| 2.5  | Near-Stream Computing ISA Examples                                     | 25 |

| 2.6  | Decoupled Stream Assembly Example                                      | 29 |

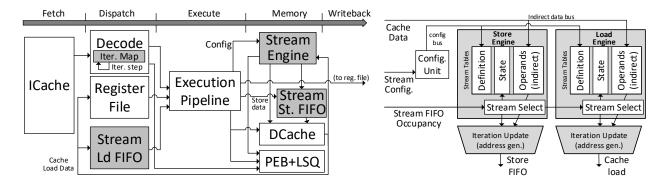

| 3.1  | Overview of Stream Specialization Paradigm vs Traditional Out-of-Order | 33 |

| 3.2  | Stream-specialized Pipeline                                            | 35 |

| 3.3  | Stream Engine                                                          | 35 |

| 3.4  | Iteration Map                                                          | 36 |

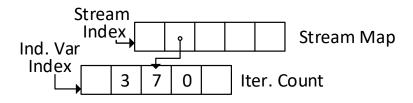

| 3.5  | State Transition for Cache Bypassing                                   | 42 |

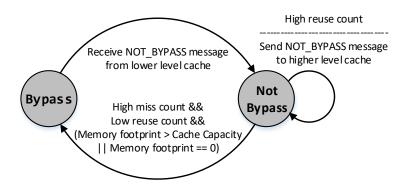

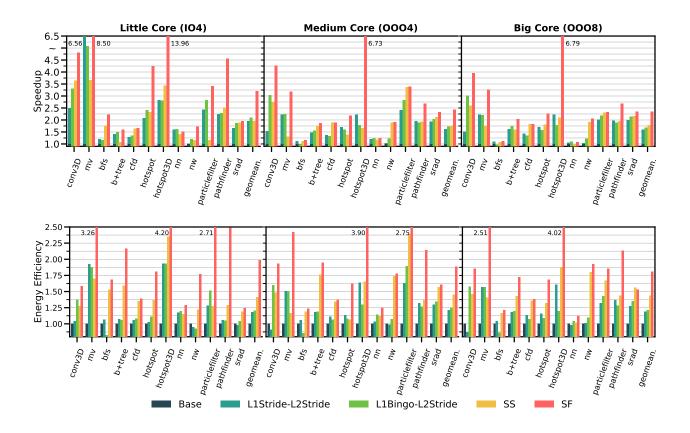

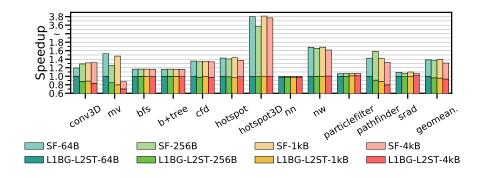

| 3.6  | Overall Speedup and Energy Efficiency                                  | 46 |

| 3.7  | Speedup of SSP-Non-Bind. vs. SSP-Semi-Bind                             | 47 |

| 3.8  | Dynamic Instructions in SSP-Semi-Bind                                  | 48 |

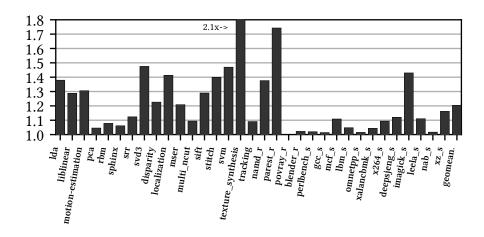

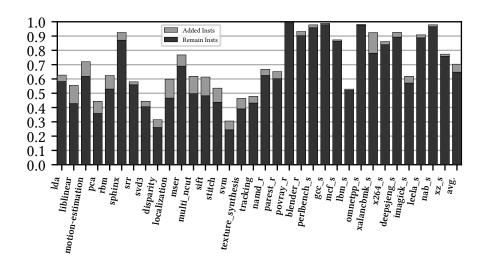

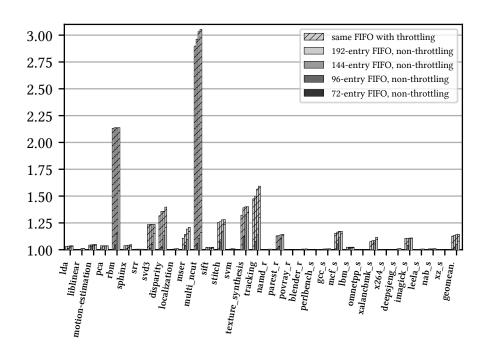

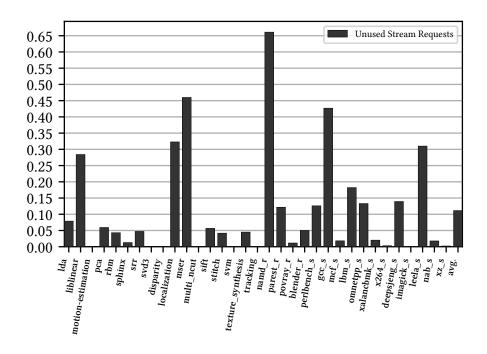

| 3.9  | Speedup with Dynamic Throttling                                        | 49 |

| 3.10 | Unused Stream Requests                                                 | 50 |

| 3.11 | Speedup with Cache Awareness                                           | 51 |

| 3.12 | Relative Speedup and Energy Efficiency for Various OOO Processors      | 52 |

| 4.1  | Overhead of Caching Data without Reuse                                 | 57 |

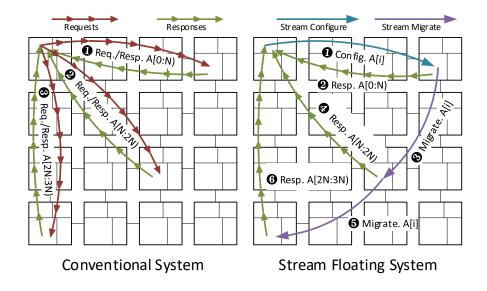

| 4.2  | Affine Floating Optimization                      | 59  |

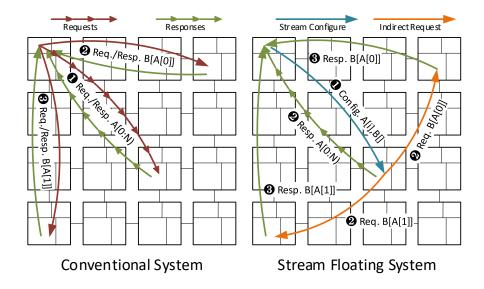

|------|---------------------------------------------------|-----|

| 4.3  | Indirect Floating Optimization                    | 60  |

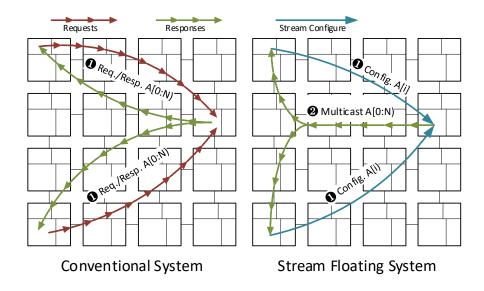

| 4.4  | Stream Confluence Optimization                    | 61  |

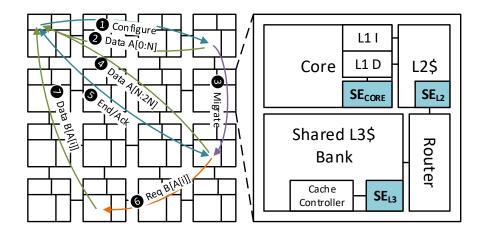

| 4.5  | Stream Floating Overview                          | 62  |

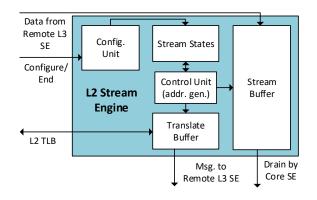

| 4.6  | L2 Stream Engine (SE <sub>L2</sub> )              | 63  |

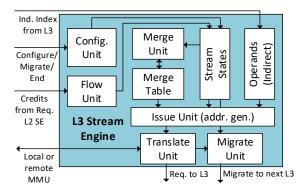

| 4.7  | L3 Stream Engine (SE <sub>L3</sub> )              | 63  |

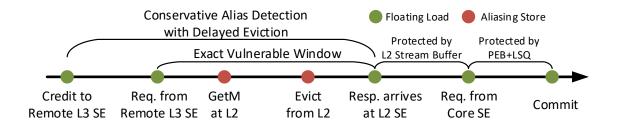

| 4.8  | Detecting Aliasing to Floating Stream Load        | 69  |

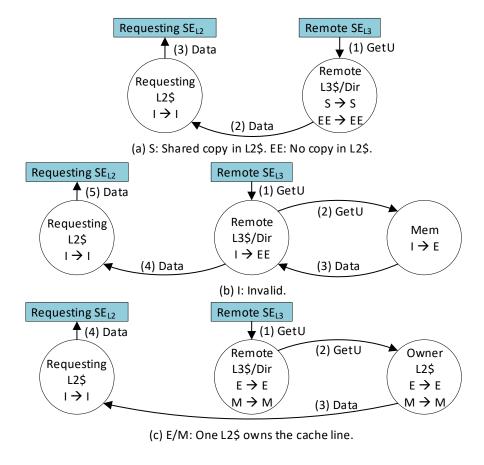

| 4.9  | Coherence Protocol Interaction                    | 70  |

| 4.10 | Overall Speedup and Energy Efficiency             | 76  |

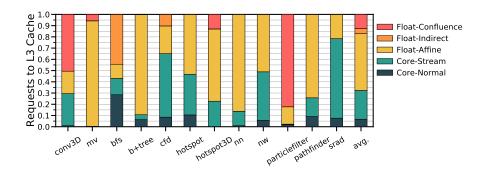

| 4.11 | Requests to L3 of SF-OOO8                         | 77  |

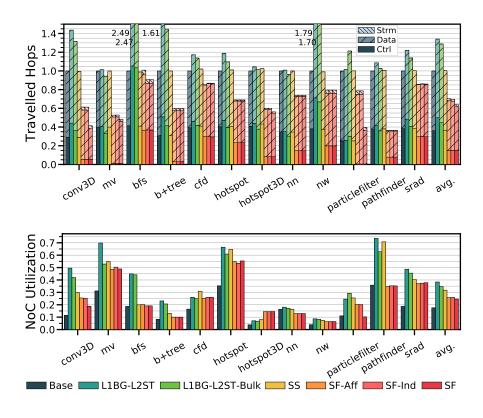

| 4.12 | OOO8 NoC Traffic and Utilization                  | 78  |

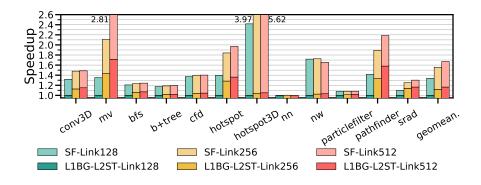

| 4.13 | SF vs. Bingo with 128, 256, 512-bit link (OOO8)   | 79  |

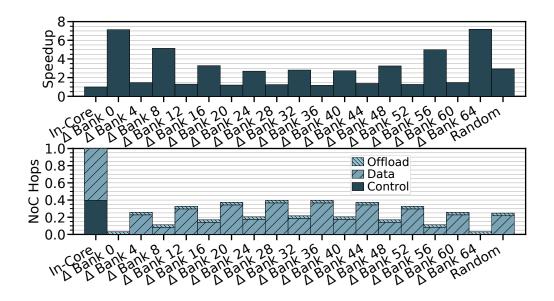

| 4.14 | Effect of NUCA Interleaving Granularity (OOO8)    | 80  |

| 4.15 | Core Scaling                                      | 81  |

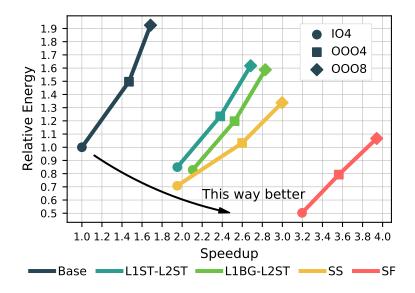

| 4.16 | Energy vs. Speedup for IO4, OOO4, OOO8            | 82  |

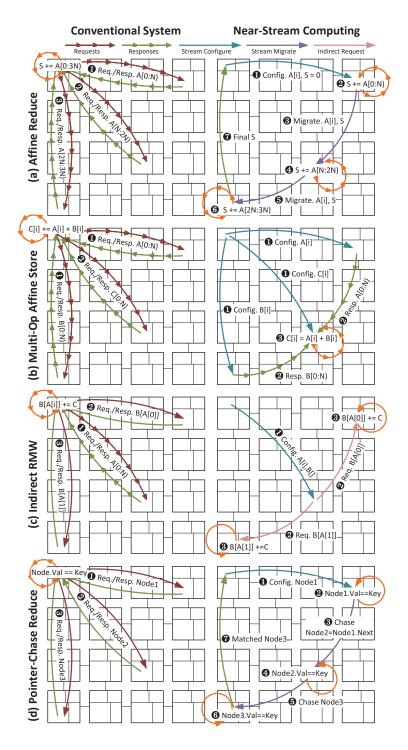

| 5.1  | Potential of Sub-Thread Near-Data (View in Color) | 89  |

| 5.2  | Near-Stream Computing Optimizations               | 90  |

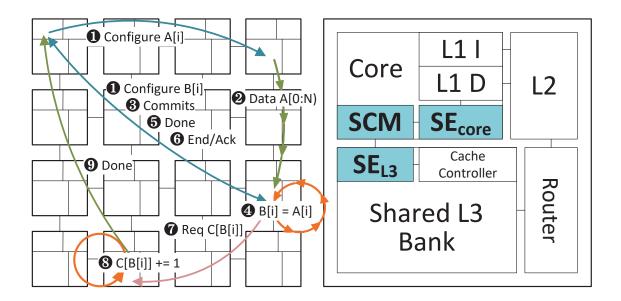

| 5.3  | In-Cache Near-Stream Computing Overview           | 97  |

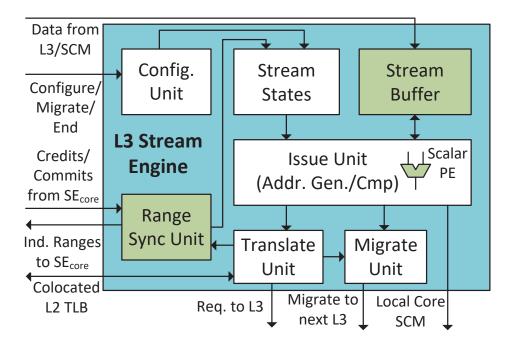

| 5.4  | L3 Stream Engine (SE <sub>L3</sub> )              | 98  |

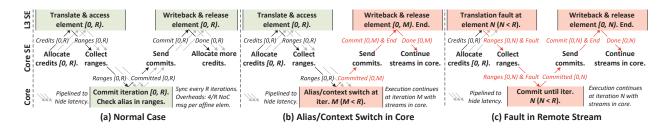

| 5.5  | Timeline of Range-Synchronization                 | 99  |

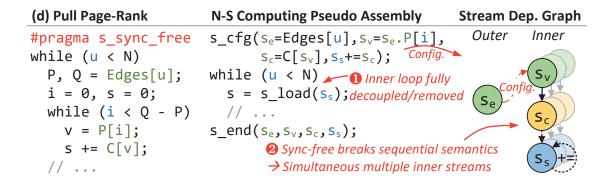

| 5.6  | Fully Decoupled Loop (Same Legend as Fig 2.5)     | 106 |

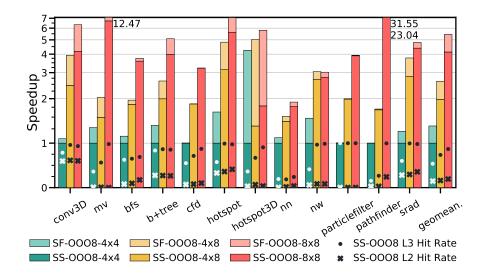

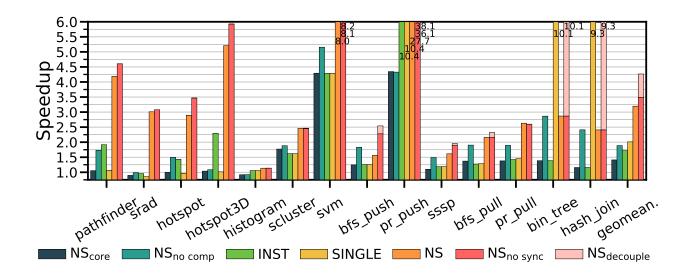

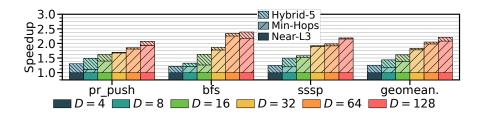

| 5.7  | Overall Speedup over Base OOO8 Core               | 110 |

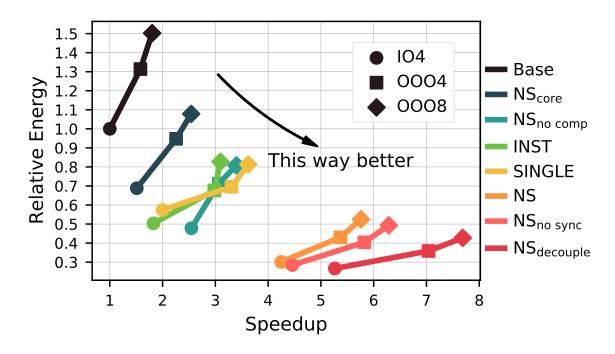

| 5.8  | Energy vs. Speedup for IO4, OOO4, OOO8            | 111 |

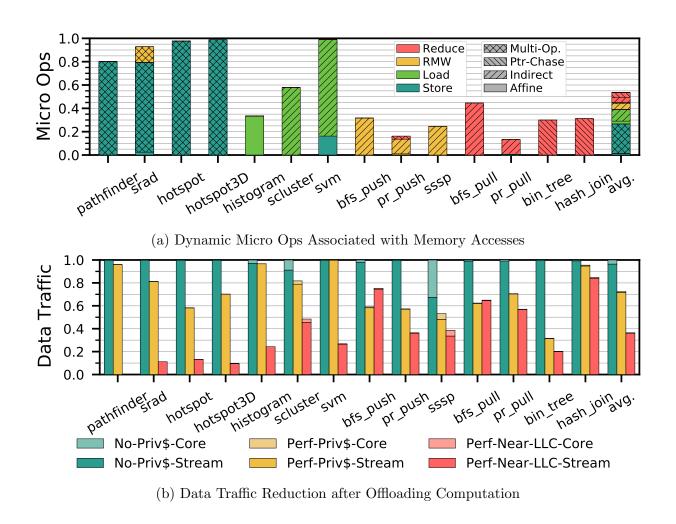

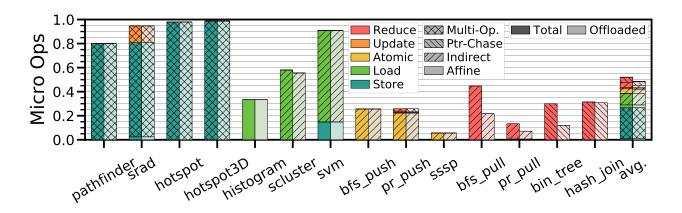

| 5.9  | Breakdown of Dynamic Micro Ops                              | 112 |

|------|-------------------------------------------------------------|-----|

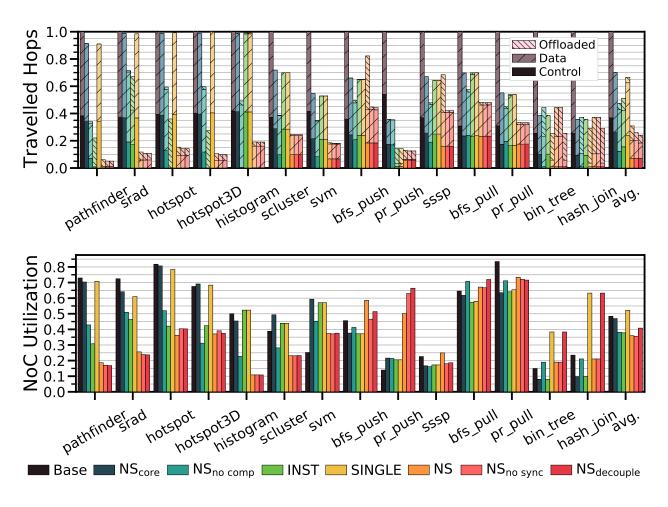

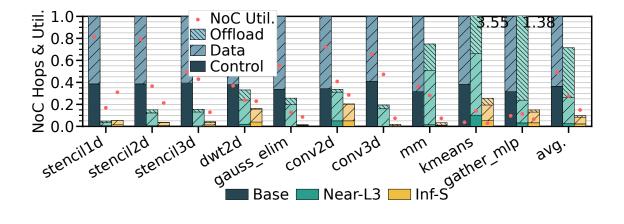

| 5.10 | OOO8 NoC Traffic (top) and Utilization (bottom)             | 113 |

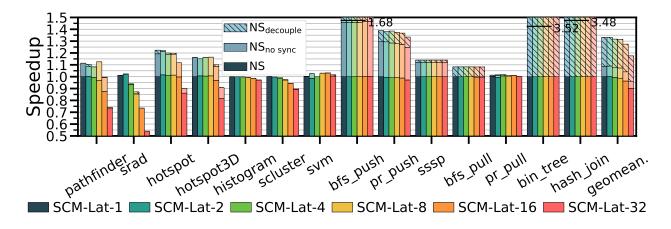

| 5.11 | NS, $NS_{no\ sync}$ , $NS_{decouple}$ with 1-32 SCM Latency | 114 |

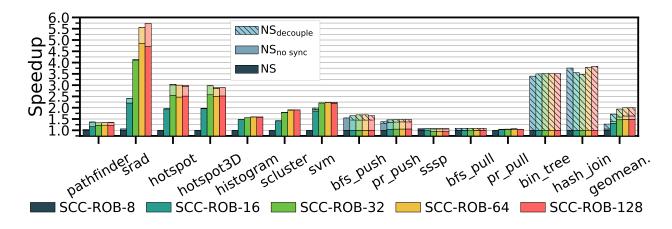

| 5.12 | Sensitivity to 8-128 SCC ROB-Entry                          | 115 |

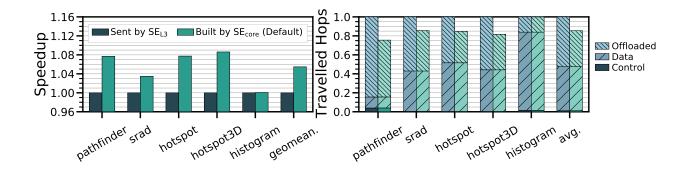

| 5.13 | Sensitivity to Affine Range Generation (NS)                 | 116 |

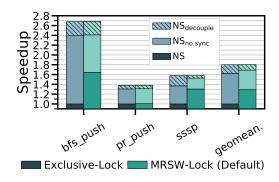

| 5.14 | Exclusive vs. MRSW                                          | 116 |

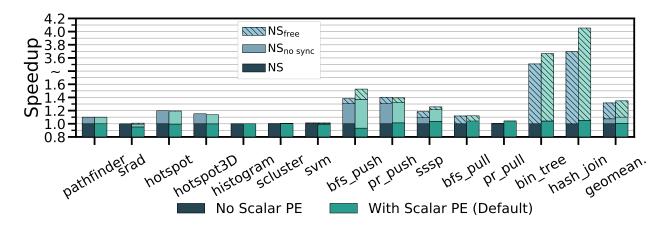

| 5.15 | Sensitivity to Scalar PE in $SE_{L3}$                       | 118 |

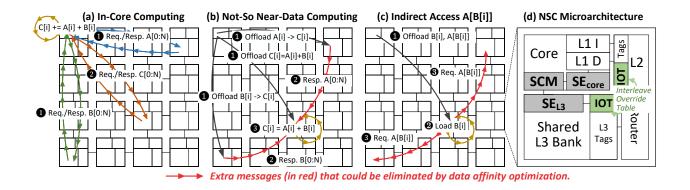

| 6.1  | Affinity Optimization Opportunities in NDC (View in Color)  | 121 |

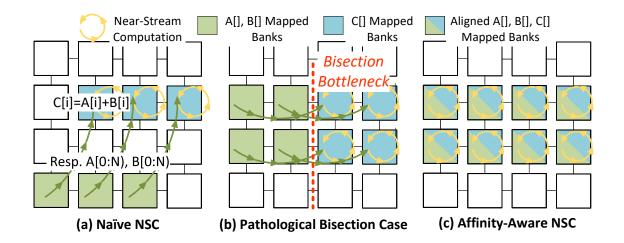

| 6.2  | Affine Data Layout for Vec Add                              | 124 |

| 6.3  | Impact of Affine Data Layout on Vec Add                     | 126 |

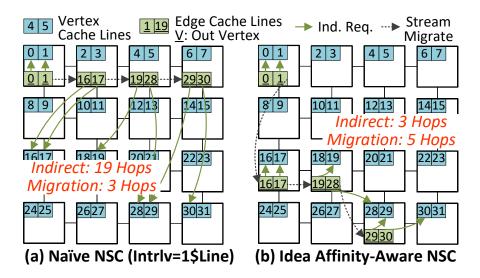

| 6.4  | Irregular Data Layout for Graph Edge List                   | 127 |

| 6.5  | Impact of Irregular Data Layout                             | 128 |

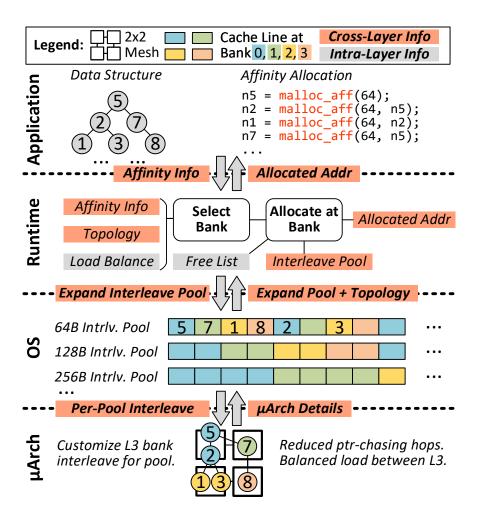

| 6.6  | Affinity Alloc Approach Overview                            | 129 |

| 6.7  | Affine Data Layout Optimizations                            | 133 |

| 6.8  | Distribute Partitions (Assume $P = X \times Y$ )            | 136 |

| 6.9  | Irregular Data Layout API                                   | 137 |

| 6.10 | Linked CSR Format                                           | 139 |

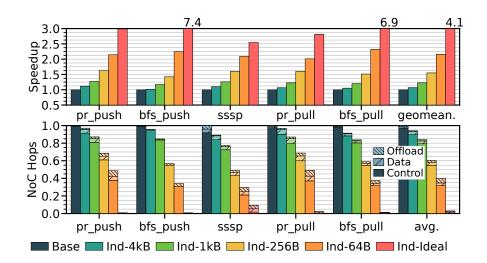

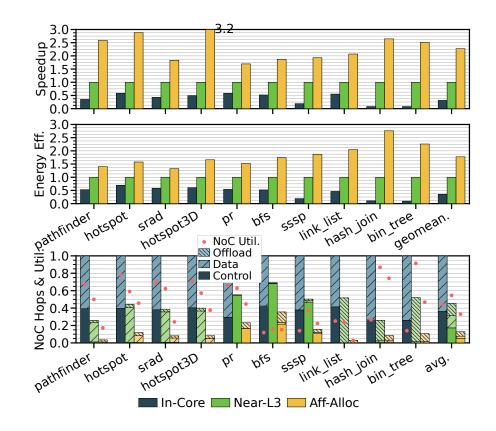

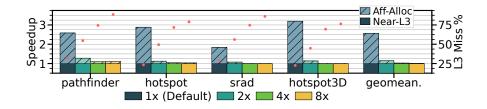

| 6.11 | Overall Performance and Traffic Reduction                   | 144 |

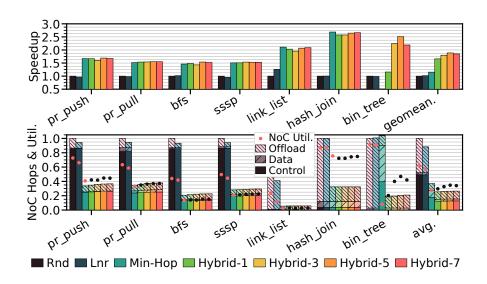

| 6.12 | Sensitivity on Irregular Layout Policies                    | 145 |

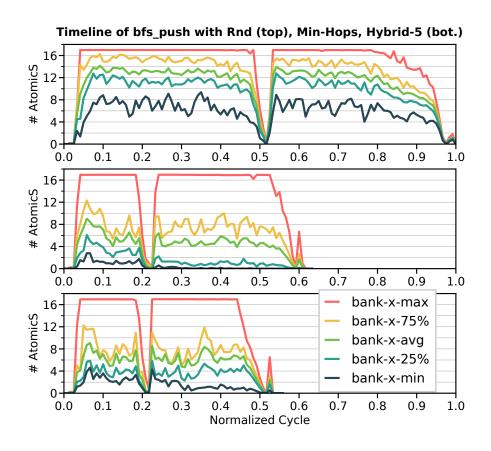

| 6.13 | Distribution of Atomic Stream in BFS-Push                   | 146 |

| 6.14 | Speedup of Affine Layout on Large Inputs                    | 147 |

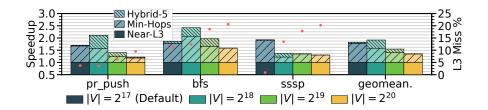

| 6.15 | Speedup of Linked CSR on Large Graphs                       | 147 |

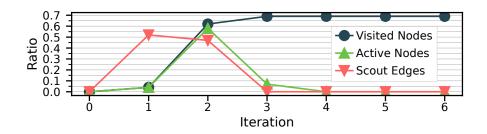

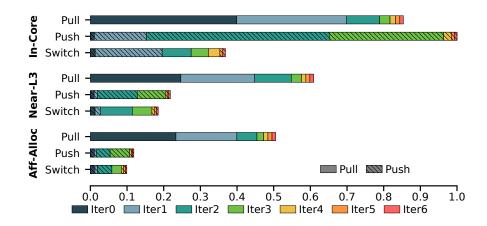

| 6.16 | BFS Iteration Characteristic                                | 149 |

| 6.17 | BFS Push vs. Pull Timeline                              | 150 |

|------|---------------------------------------------------------|-----|

| 6.18 | Speedup vs. Avg. Node Degree                            | 150 |

| 6.19 | Performance on Real World Graphs                        | 151 |

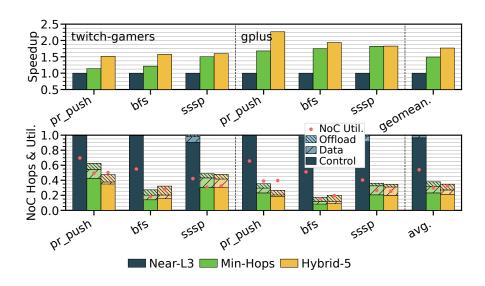

| 7.1  | Overview of In-Core/Near-Mem/In-Mem Computing Paradigms | 157 |

| 7.2  | Speedup of Different Paradigms (Fp32)                   | 160 |

| 7.3  | Infinity Stream Workflow Overview                       | 162 |

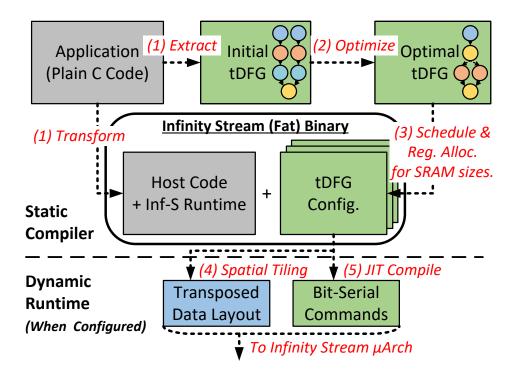

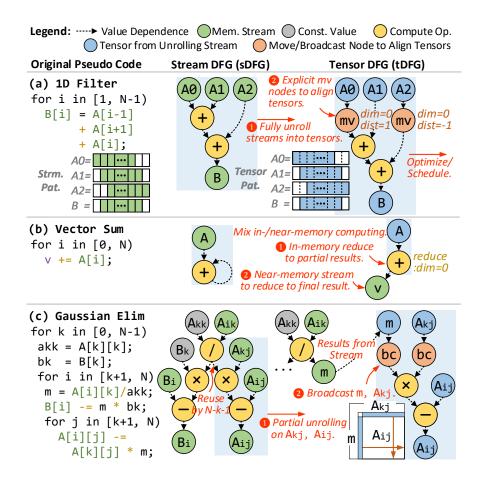

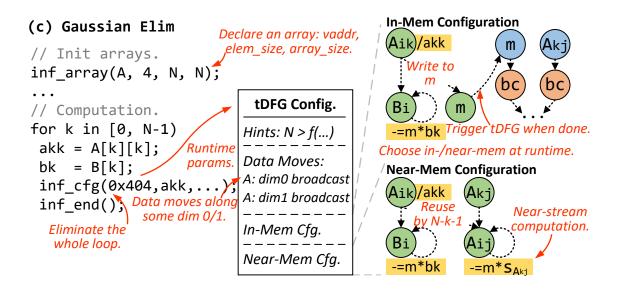

| 7.4  | Examples of Infinity Stream Abstractions                | 164 |

| 7.5  | tDFG Node Semantics                                     | 165 |

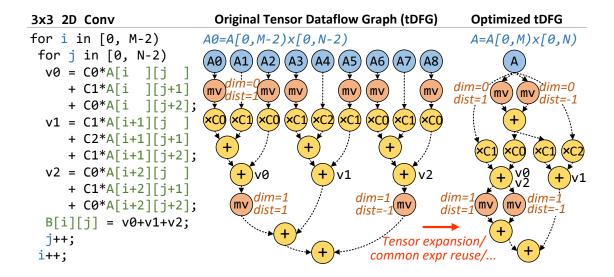

| 7.6  | Example of Optimized tDFG                               | 168 |

| 7.7  | Example of Compiled Infinity Stream Program             | 170 |

| 7.8  | Programming GEMM for Infinity Stream                    | 171 |

| 7.9  | Moving a Tensor in Tiled Layout (View in Color)         | 172 |

| 7.10 | Infinity Stream Microarchitecture                       | 180 |

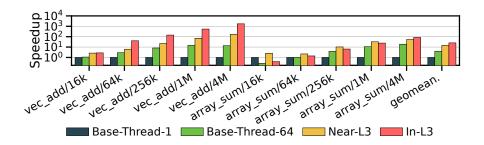

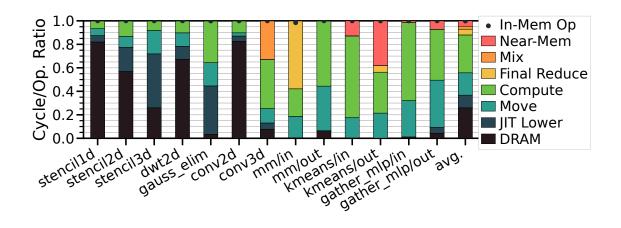

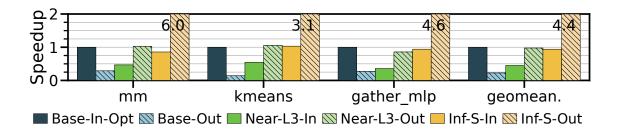

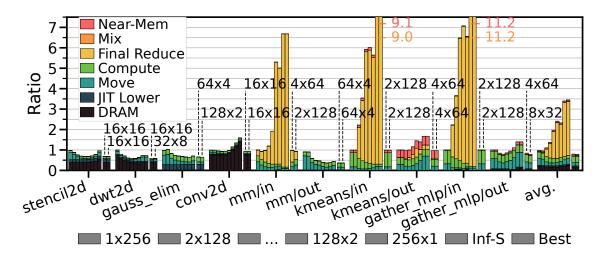

| 7.11 | Overall Speedup                                         | 187 |

| 7.12 | NoC Traffic Breakdown (Bar) and Util. (Dot)             | 188 |

| 7.13 | Inf-S Traffic Breakdown                                 | 188 |

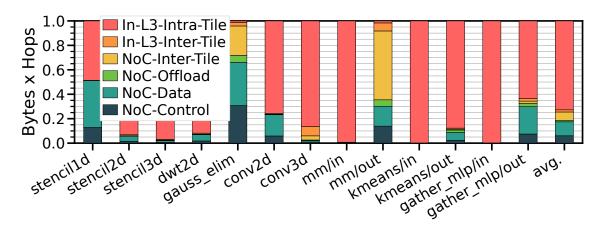

| 7.14 | Inf-S Cycle Breakdown                                   | 189 |

| 7.15 | Inner vs. Outer Product Dataflow                        | 190 |

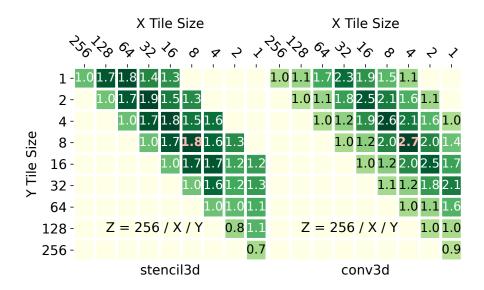

| 7.16 | Cycle Breakdown vs. 2D Tile Size                        | 190 |

| 7.17 | Inf-S Speedup vs. 3D Tile Size (Default as Bold)        | 191 |

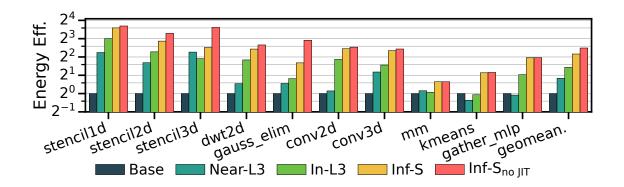

| 7.18 | Overall Energy Efficiency                               | 192 |

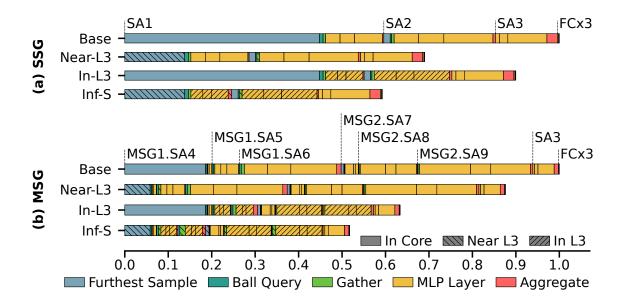

| 7.19 | Timeline of PointNet++ SSG/MSG Classifier               | 193 |

| B.1  | Example of Applying Rewrites                            | 213 |

## LIST OF TABLES

| 1.1 | Characterization of Representative Near-Data Approaches       | 5   |

|-----|---------------------------------------------------------------|-----|

| 1.2 | Dissertation Organization and Relation to Author's Prior Work | 13  |

| 3.1 | Fields of Stream Table                                        | 41  |

| 3.2 | Simulation Parameters for Baseline                            | 43  |

| 4.1 | Affine and Indirect Stream Configuration                      | 65  |

| 4.2 | Stream History Table                                          | 67  |

| 4.3 | System and Microarchitecture Parameters                       | 73  |

| 4.4 | Workload Datasets                                             | 74  |

| 5.1 | Capabilities of Sub-thread Near-data Approaches               | 92  |

| 5.2 | Address and Compute Patterns of Near-Data Works               | 94  |

| 5.3 | Capabilities of Stream ISA Works                              | 94  |

| 5.4 | Near-Stream Computing Configuration                           | 104 |

| 5.5 | System and Microarchitecture Parameters                       | 108 |

| 5.6 | Workloads (MO: Multi-Op)                                      | 109 |

| 6.1 | Interleave Override Table (IOT)                               | 132 |

| 6.2 | System and $\mu$ arch Parameters                              | 141 |

| 6.3 | Workloads Parameters                                          | 142 |

| 6.4 | Real World Graphs                                             | 151 |

| 7.1 | Layout Override Table (LOT)                                   | 181 |

| 7.2 | System and $\mu$ arch Parameters                              | 185 |

| 7.3 | Workloads (BC: Broadcast)                | 186 |

|-----|------------------------------------------|-----|

| 7.4 | PointNet++                               | 186 |

| 8.1 | Characterization of This Work            | 198 |

| A.1 | Characterization of Near-Data Approaches | 205 |

#### **ACKNOWLEDGMENTS**

I am profoundly grateful to Prof. Tony Nowatzki, my esteemed Ph.D. advisor, whose unwavering support and guidance have been the cornerstone of my academic journey. Our collaboration commenced in 2017 when I was a master's student, and under his mentorship, I have gained invaluable insights that have significantly shaped the trajectory of my research. His dedication, expertise, and encouragement have been instrumental in every step of this dissertation, and I owe much of its success to his profound influence. Without his steadfast assistance, none of this would have been possible.

I also extend my thanks to my committee members, Prof. Todd Millstein, Prof. Glenn Reinman, and Prof. Harry Xu. Their insights during my oral qualification exam and final defense significantly enriched my research, and I appreciate their valuable contributions.

I express my gratitude to an outstanding group of collaborators and lab mates who have played pivotal roles in shaping the diverse facets of this dissertation. Prof. Jason Lowe-Power from UC Davis provided invaluable insights into cache coherence and encouraged my work on gem5. Prof. Nathan Beckmann from CMU engaged in insightful discussions, enhancing my understanding of data affinity for near-data computing. Prof. Lizy John and Prof. Aman Arora offered essential guidance in the detailed modeling of in-memory computing hardware. Dr. Jayesh Gaur contributed significantly to discussions on CPU microarchitecture, while Prof. Jian Weng provided enjoyable insights into compilers and programming languages. Vidushi Dadu's expertise in irregular parallelism and Sihao Liu's patient guidance in hardware intricacies have been instrumental. Special thanks to Christopher Liu for his assistance and the creation of remarkable slides. Each of them has left an indelible mark on this dissertation, and I am deeply appreciative of their collaborative efforts.

A heartfelt thank you goes to my badminton partners, the steadfast companions who brought joy and camaraderie to these years. Dr. Xiaoyu Wu, Dr. Shuaihang Pan, Dr. Hao Liu, Dr. Kaiyuan Jin, Dr. Zizhao Zhang, Ziqing Luo, Jiayu Yi, Jiarui Wang, and Lu Cheng,

playing alongside you all was a source of solace during the challenges of the pandemic. Special appreciation to Alex, Andy, Arnold, Harry, Miranda, Yifan, Hallie, Carol, and Dr. Ke Huo for making every Tuesday/Thursday night over the past two years incredibly enjoyable. Xiaoyu, I could not have survived COVID-19 and these years without your help (including cold jokes). Hallie, your impeccable taste in songs added an extra layer of joy; best of luck with your DDS study. To each of you, I extend my wishes for the very best. Keep smashing both on and off the badminton court.

A special shoutout to my dear friends at UCLA, who added vibrant colors to my journey. Dr. Jie Wang, thank you for the exhilarating mountain hikes by Santa Monica Beach, creating cherished memories that will last a lifetime. Dr. Weikang Qiao and Dr. Bing Han, your delightful company and shared culinary adventures have made every meal an enjoyable experience. Congratulations on the arrival of Jojo, and I wish your growing family all the happiness. A heartfelt appreciation to Dr. Licheng Guo, the maestro behind the lens, for skillfully capturing our best moments and turning them into timeless treasures.

I also thank my friends around the world who have left indelible marks on my life. Dr. Zhanhao Su, your unwavering inspiration has been a driving force, urging me to aim high and persevere. Jiajian Kuang, you've been a lifesaver on countless gaming nights, turning each one into a memorable adventure. Hsien-yu Meng, thank you for your steadfast support during my Ph.D. application; I wish you all the best in your endeavors. Liqing Xu, you made Boston unforgettable with your insights and company. To Minjun Huang, your presence has enriched my life in too many ways to count. To the many other friends I've missed during these years of the pandemic, your absence has been felt.

To my dearest parents, Hongbing Wang and Jianhua Yi, words fall short of expressing my gratitude. I may not be the perfect son, but you, without a doubt, are the best parents in the world. Your unwavering love, support, and sacrifices have shaped me into the person I am today. Thank you for being my pillar of strength throughout this journey. I am endlessly fortunate to have you by my side.

# VITA

| 2012-2016 | Bachelor of Engineering, Department of Electronic Engineering, Tsinghua University, Beijing, China.                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2016–2018 | Master of Science, Department of Computer Science, UCLA. Designed a trace-based simulator using LLVM-IR.                                                                                               |

| 2019      | Published Stream-based Memory Access Specialization for General Purpose Processors in 2019 ACM/IEEE 46th Annual International Symposium on Computer Architecture (ISCA).                               |

| 2021      | Published Stream Floating: Enabling Proactive and Decentralized Cache<br>Optimizations in 2021 International Symposium on High-Performance<br>Computer Architecture (HPCA).                            |

| 2022      | Published Near-Stream Computing: General and Transparent Near-Cache Acceleration in 2022 International Symposium on High-Performance Computer Architecture (HPCA).                                     |

| 2022      | Teaching Assistant of CS 33, Spring Quarter, Department of Computer Science Department, UCLA.                                                                                                          |

| 2023      | Published Infinity Stream: Portable and Programmer-Friendly In-/Near-Memory Fusion in 2023 International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS). |

| 2023      | Published Affinity Alloc: Taming Not-So Near-Data Computing in 2023 ACM/IEEE 56th International Symposium on Microarchitecture (MI-CRO).                                                               |

# CHAPTER 1

### Introduction

For decades, conventional computer architectures followed the classical von Neumann model which draws a clear boundary between computation and data – centralized process units (e.g. cores in CPU/GPU) perform all the computation, with memory units (e.g. caches, DRAM) reacts to requests and serves the data. Such a compute-centric interface simplifies the design and works well as long as data movement is relatively cheap compared to performing the computation.

However, the landscape is fundamentally changed by an increasing gap between the rapidly growing demand for large data and the much slower scaling of conventional memory hierarchies. For example, ChatGPT requires ~14000× more parameters than its predecessor in 2017, while high-end GPUs used to train it only scale by 2.5× in memory capacity and 2.2× in memory bandwidth at the same time. To bridge this gap, modern systems also scale up the cache hierarchy to hold more data on-chip and serve the core's requests more timely. However, with the existing compute-centric interface, the cache hierarchy is inherently reactive and responsive, requiring complicated tiling schemes in the software as well as complex best-effort microarchitecture policies to predict the program behavior. Therefore, even with caches, conventional in-core computing still suffers from increasingly expensive overheads such as excessive request messages, unnecessary data movement and coherence traffic, as well as limited off-chip bandwidth, to bring the data from memory to computing cores. This calls for a fundamental redesign to revolutionize the memory interface and co-optimize computation and data together.

To mitigate such overheads, architects propose a variety of specialized architectures that carefully schedule computation near data and orchestrate data movements through efficient pipelines. This broad paradigm of near-data computing (NDC) covers an extremely large design space: near where (on-chip cache, DRAM, or storage), how to compute (small cores, reconfigurable arrays, or bit-serial logic using bit lines), how to program (domain-specific language or general compiler), as well as so many other aspects. Existing near-data computing techniques are limited to a subset of these design choices and often require manual programming using specific APIs, and hence insufficient to enable general, flexible and unified near-data computing.

**Key Question** How to build a NDC system in which *general* near-data computations can be *flexibly* scheduled to *all* available memory levels and computing substrates, with a *unified* programming and ISA abstraction and *automatic* analysis and optimization across the full system stack.

Our key insight is that such a general and flexible system is infeasible without a powerful unified abstraction to precisely capture and fuse the high-level memory access behaviors and compute patterns. This dissertation explores streams – general memory access patterns with near-stream computations – as a potential candidate. Streams inherently condense the essential information about memory accesses and near-data computations into a unified offloading basic unit, and unlock many opportunities to enable perfect prefetching, general and transparent near-data computing, automatic data layout optimization, etc.

The remainder of this chapter will focus on first introducing the background of near-data computing, and categorizing the huge design space and corresponding challenges to enable general, flexible and unified near-data computing. Then we introduce our approach to leverage streams as the fundamental near-data computing abstraction and how that presents a unique opportunity. Finally, we summarize our main contribution and the organization of this dissertation.

Figure 1.1: Conventional In-Core (Top) vs. Future Near-Data Computing (Bottom)

### 1.1 Existing Near-Data Computing

In this section, we first compare near-data computing with conventional in-core computing, then define the design space for near-data computing and the insufficiencies of existing neardata computing techniques.

In-Core Computing Fig 1.1 compares conventional in-core computing (top) and near-data computing (bottom) across various abstract levels of a multi-core system. In conventional in-core computing, all computations are centralized in the core, which incurs significant data movement and communication overheads to fetch and write back the data. For example, to perform a simple vector addition A[i]=B[i]+C[i], the core needs to fetch all three vectors and write back C[] even when there is no data reuse, as the computation is fixed in the core. These overheads are only going to be worse as modern systems continue to scale up in the number of cores and memory hierarchy levels, leading to longer data movement distance. Also, the growing demand for large data puts more pressure on the cache hierarchy to hold and reuse the working set, making it wasteful to move and cache the data.

Why Caches are Insufficient To mitigate these overheads, architects spend tremendous efforts to improve the cache hierarchy in terms of capacity and policies. For capacity, modern CPUs employ larger caches with more levels, e.g. 2MB private L2 cache and 2.7MB shared

L3 cache per core for Intel Xeon 4th Gen Sapphire Rapids. However, a more complex cache hierarchy requires a more complex tiling scheme to improve the data reuse, and is infeasible when the application has no reuse. On the other hand, architects also propose various microarchitecture policies to dynamically bypass certain cache levels, to replace unused cache lines, to prefetch future data, etc. However, these are all best-effort approaches to recovering the original high-level program semantics from the primitive memory interface that operates on individual cache lines, and are inefficient if the program's behaviors are too complicated or transient to be captured.

Fundamentally speaking, with the existing computing-centric interface, caches are inherently reactive and lack a holistic view of the program to proactively adjust to application phases. Even with an ideal cache that perfectly predicts the program's future behaviors, the data movements are inevitable due to the fixed in-core computing. Therefore, we need a fundamental redesign of the memory interface and hierarchy to address these challenges.

Near-Data Computing To overcome these overheads, near-data computing wipes out the boundary between computation and memory. As shown in Fig 1.1, the memory hierarchy is enhanced with computing capability at different levels, so that computation can be scheduled across the memory hierarchy near the data in on-chip caches, off-chip DRAM, or even near the storage. This replaces the superfluous requests and data movements with coarse-grained offloading messages and minimal data traffic to collect the operands. This is the key to continuing the scaling of performance and energy efficiency.

**Design Space** As Fig 1.1 suggests, near-data computing touches the entire system stack and forms a broad design space that includes at least the following dimensions. Table 1.1 characterizes a representative subset of recent near-data computing techniques. For a more comprehensive characterization, see Table A.1.

Table 1.1: Characterization of Representative Near-Data Approaches

| NDC Work               | Yr. | ABST.                 | Near Where        | Substrate  | Domain        | Program | Data Layout         |

|------------------------|-----|-----------------------|-------------------|------------|---------------|---------|---------------------|

| Goal                   |     | Unified               | All               | All        | General       | Trans.  | Automatic           |

| CDCS [1]               | '15 | Thread                | Core              | Local Core | General       | Trans.  | ${\rm Limited^1}$   |

| Dist-DA [2]            | '22 | DFG                   | LLC               | Core/CGRA  | General       | Trans.  | Oblivious           |

| Omni-Compute [3]       | '19 | Inst.                 | GPU LLC           | FU         | General       | Trans.  | Oblivious           |

| SnackNoC [4]           | '20 | Kernel                | NoC Router        | FU         | Regular       | API     | Scratchpad          |

| Fafnir [5]             | '21 | Kernel                | $\mathrm{DRAM}^2$ | FU         | Gather        | API     | Manual              |

| GenASM [6]             | '20 | Kernel                | DRAM              | ASIC       | Genomic       | API     | Scratchpad          |

| EMC [7]                | '16 | $\mu$ op Seq.         | DRAM              | FU         | Prefetching   | Trans.  | Oblivious           |

| To PIM or Not [8]      | '22 | Thread                | DDR Bank          | Core       | General       | Trans.  | ${\rm Oblivious^3}$ |

| MeNDA [9]              | '22 | Kernel                | DDR Rank          | ASIC       | Sparse $LA^4$ | API     | Manual              |

| Tesseract [10]         | '15 | Thread                | $_{\mathrm{HMC}}$ | Core       | Graph         | API     | Manual              |

| TOM [11]               | '16 | Thread                | $_{\mathrm{HMC}}$ | GPU Core   | General       | Trans.  | ${\rm Limited}^5$   |

| GPU-PIM [12]           | '16 | Thread                | $_{\mathrm{HMC}}$ | GPU Core   | General       | Trans.  | Oblivious           |

| ABNDP [13]             | '23 | Thread                | $_{\mathrm{HMC}}$ | Core       | General       | API     | ${\rm Oblivious}^6$ |

| PIM-Enabled Inst. [14] | '15 | Inst.                 | $_{\mathrm{HMC}}$ | FU         | General       | Trans.  | Oblivious           |

| IMPICA [15]            | '16 | Kernel                | $_{\mathrm{HMC}}$ | ASIC       | Ptr-Chasing   | API     | Oblivious           |

| Active Routing [16]    | '19 | Packet                | $_{\mathrm{HMC}}$ | FU         | Aggregation   | API     | Oblivious           |

| Gearbox [17]           | '22 | Kernel                | HMC Bank          | ASIC       | Sparse $LA^7$ | API     | Manual              |

| FANS [18]              | '21 | Kernel                | SSD               | FPGA       | Sorting       | API     | Manual              |

| ASSASIN [19]           | '22 | Kernel                | SSD               | ASIC       | $General^8$   | API     | Oblivious           |

| Neural Cache [20]      | '18 | Kernel                | In-LLC            | Bitline    | ML            | API     | Scratchpad          |

| Duality Cache [21]     | '19 | $\operatorname{SIMT}$ | In-LLC            | Bitline    | General       | Trans.  | Oblivious           |

| DUAL [22]              | '20 | Kernel                | In-DRAM           | Bitline    | Clustering    | API     | Manual              |

| Ambit [23]             | '17 | Inst.                 | In-HMC            | Bitline    | General       | API     | Scratchpad          |

<sup>&</sup>lt;sup>1</sup>Only at page granularity.

<sup>&</sup>lt;sup>2</sup>In interconnects of DDR ranks and channels.

<sup>&</sup>lt;sup>3</sup>Customized physical address layout in DRAM.

<sup>&</sup>lt;sup>4</sup>Sparse matrix transposition.

<sup>&</sup>lt;sup>5</sup>Specific to strided patterns on GPU.

$<sup>^6\</sup>mathrm{With}$  DRAM-based cache to capture locality.

$<sup>^7\</sup>mathrm{Sparse}$  linear algebra, mainly SpMV and SpMSpV.

<sup>&</sup>lt;sup>8</sup>Programs need to be transformed into streaming computing.

| SISA [24]         | '21 | Set                 | $\mathrm{Multi.^9}$    | $ m Multi.^{10}$        | Graph Mining                 | API    | Manual     |

|-------------------|-----|---------------------|------------------------|-------------------------|------------------------------|--------|------------|

| MLIMP [25]        | '22 | DFG                 | $ m Multi.^{11}$       | Multi.                  | $\mathrm{GEMM}/\mathrm{GNN}$ | API    | Scratchpad |

| NDC Compiler [26] | '21 | Inst.               | $ m Multi.^{12}$       | FU                      | General                      | Trans. | Oblivious  |

| Livia [27]        | '20 | ${\rm Kernel}^{13}$ | $\mathrm{Multi.^{14}}$ | ${\rm Core}/{\rm FPGA}$ | General                      | API    | Oblivious  |

• Offloading Location: There are two possible offloading dimensions for NDC: vertically across memory hierarchy levels, and horizontally among units within the same level Many works focus on the vertical approach near the controller of cache, DRAM, HMC, or SSD. Emerging technologies such as in-situ bitline operation turn the SRAM/DRAM arrays into massive vector units (labeled as In-X in Table 1.1). As for the horizontal dimension, many multi-core works targetting non-uniform memory accesses (NUMA) and non-uniform cache accesses (NUCA) do not offload computations from the core, but try to schedule and migrate computations horizontally among the cores to improve data locality (labeled as Core in Table 1.1). Notice that most vertical offloading approaches have a horizontal dimension within the offloaded level.

Most existing works focus on a single offloading location. However, depending on the application, different near-data computations may favor different offloading locations, and the optimal offloading level for a single near-data computation can also change depending on the input size and runtime behavior.

Goal: An ideal NDC system should intelligently schedule computations to a single or multiple efficient levels with minimal synchronization.

<sup>&</sup>lt;sup>9</sup>In-situ DRAM (SISA-PUM) and near DRAM controller (SISA-PNM).

<sup>&</sup>lt;sup>10</sup>In-situ DRAM bitline for SISA-PUM, and small in-order cores for SISA-PNM.

<sup>&</sup>lt;sup>11</sup>In-situ LLC, In-situ DRAM and ReRAM.

<sup>&</sup>lt;sup>12</sup>NoC routers, LLC controllers, DRAM controllers, inside DRAM.

<sup>&</sup>lt;sup>13</sup>Can only process a single cache line.

<sup>&</sup>lt;sup>14</sup>LLC controllers and DRAM controllers

• Computing Substrate: Besides the offloading location, different substrates to perform the near-data computation also present different tradeoffs. A small in-order core offers maximal generality but still incurs all the overheads of a general-purpose pipeline, e.g. instruction decoding, register reads and writes, etc. The opposite extreme is fix-function ASIC units, which are highly specialized for certain operations by sacrificing generality. Reconfigurable hardware like FPGA and CGRA, as well as tailored function units (FUs) that can be programmed to perform some predefined primitives, tries to balance programmability and efficiency. There are also many emerging computing substrates, e.g. bit-serial in-memory computing, resistive random-access memory (RRAM), non-volatile memory (NVMe), high-bandwidth memory (HBM), etc. All these techniques pose different tradeoffs.

Goal: An ideal NDC system should offload computations to the suitable computing substrate, or even split between them to combine their strengths.

• Application Domain: Many prior near-data computing techniques are limited to a specific application domain: graph processing, linear algebra, DNA sequencing, database acceleration, sorting, etc. These applications are usually memory intensive and can benefit the most from the improved memory bandwidth of near-data computing. Others try to target general computation by directly offloading an entire thread or providing a general programming interface. We argue that a general near-data computing system is more favorable in the future to handle more and more diverse applications and amortize the costs.

Goal: An ideal NDC system should be general enough to cover a wide range of application domains.

• Programming Model: Another key design choice is how to program such a complex near-data computing system, as much essential information is required to efficiently coordinate various system components. Some works simply program a low-level in-

terface, e.g. intrinsics or assembly instructions, while others provide special APIs in domain-specific or general-purpose languages. All these approaches require manually rewriting the program. Another approach is reusing a general-purpose language and automatically extracting near-data opportunities with minimal programmer hints. This significantly eases the overheads to adopt near-data computing on existing applications with less programmer intervention, but requires advanced compiler analysis and careful microarchitecture optimization to maintain consistency.

Goal: An ideal NDC system should remain almost transparent to the programmer without sacrificing performance.

• Data Layout: A common oversight in designing a near-computing system is data layout. Simply pushing computing into the memory hierarchy does not guarantee that computation is now closer to the data, especially when the computation accesses more than a single piece of data. For example, stencil workloads compute on multiple arrays, and graph workloads require indirect access to neighboring vertices. Without a suitable data layout, the required operands may be scattered far away from each other, and naïvely offloading computation near data may yield no data movement reduction or even hurt the performance. However, existing NDC work either relies on manual coarse-grained data partition, or is simply oblivious to the data layout and falls back to in-core computing when near-data computing is not profitable.

Goal: An ideal NDC system should automatically optimize data layout to improve data affinity.

On top of Table 1.1 lists the goal of an ideal near-data computing system. Unfortunately, existing NDC works fall short of reaching these goals. They are often limited to certain offloading location, computing substrate and application domain, requires enormous efforts to program, and are oblivious to data layout. We need a general, flexible and unified NDC system that fully realizes the potential of near-data computing.

### 1.2 Near-Stream Computing

A fundamental limitation of existing NDC techniques is that they still focus more on computing than data, i.e. they simply shift the conventional compute-centric view closer to the data, but lack of holistic data-centric view. The data is still treated as a small contiguous chunk identified by its address and size, and served by a memory subsystem reacting to individual memory requests. Such primitive memory abstraction completely misses diverse and rich memory behaviors. For example, do memory accesses follow a specific pattern such as linear, affine, or pointer-chasing? What is the computation performed on the fetched data? Are multiple data structures involved in the computation? If so, how should the system optimize their affinity? Without a rich semantic abstraction to efficiently capture this information, it is infeasible for near-data computing to reach the desired level of generality, flexibility and unification.

This dissertation replaces the primitive "data" abstraction with "stream" – a general abstraction with high-level data access patterns and near-data computations – to form a new paradigm called near-stream computing. For example, the above vector addition example C[i]=A[i]+B[i] can be represented as three streams: two load streams A[] and B[], and a store stream C[]. The addition can be associated with the store stream C[], forming a near-stream computation that is scheduled along with the stream. Specifically, near-stream computing presents the following unique opportunities.

- Streams capture broad access patterns, and computations consuming or producing stream data can be associated with the stream, forming near-stream computations. Moreover, streams still preserve the original sequential ordering, and can be automatically recognized by compiler analysis from general-purpose languages without sacrificing programmability or transparency.

- Streams and associated near-stream computations are inherently decouplable from the remainder of the program, making them a natural match for distributed near-data

computing. The embedded high-level access patterns also enable proactive and highly efficient data orchestration and synchronization between the core and offloaded streams across the entire memory hierarchy.

• The dependency relationship between streams and near-stream computations precisely represents the affinity relationship between data structures, enabling automatic data layout optimization to make near-data computations *truly* near the data.

Overall, near-stream computing fundamentally takes a data-centric view: it employs a unified data abstraction that captures general data movement and near-data computations (§2), orchestrates data and computation flexibly across the entire memory hierarchy (§3, §4, §5, §7), and automatically optimizes the data affinity to balance spatial locality and parallelism (§6).

#### 1.3 Contributions

This dissertation identifies streams as the fundamental near-data computing abstraction and explores many unique opportunities for near-stream computing. The potential impact of this is to enable general, flexible and unified near-data computing that eliminates communication bottlenecks without sacrificing programmability or transparency. The specific contributions are in terms of stream characterization/ISA extension, unified execution model/architecture design for near-stream computing, and automatic data layout optimization and data structure codesign for data affinity.

Stream Characterization and ISA Extension We characterize various stream patterns in a variety of representative workloads from simple strided linear accesses on an array, to complex data-dependent accesses such as irregular indirect pattern A[B[i]] and pointer-chasing p=p.next. Streams are prevalent, covering on average more than 60% memory accesses [28]. Based on these observations, we extend a general-purpose ISA (we use x86)

with stream abstraction to capture the high-level access pattern and potential near-data computations in the presence of control flow and indirect memory, This serves as the missing cornerstone of next-gen near-data computing. We also implement the automatic compiler analysis and transformation to directly recognize streams from plain-C programs.

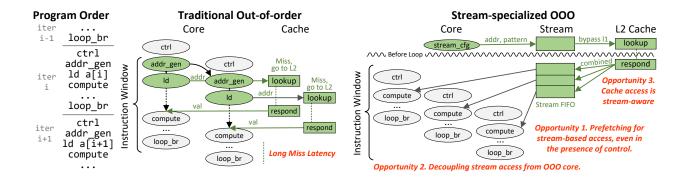

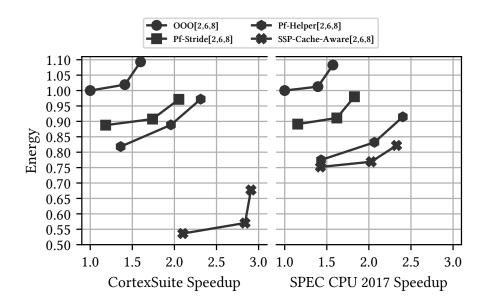

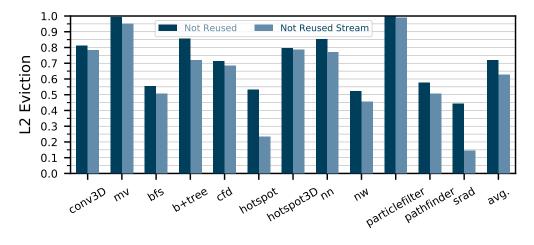

In-Core Stream Specialization With streams explicitly embedded in the ISA, we can leverage the inherent structure of streams to specialize the core pipeline, cache interface and cache policies. We find that streams can be decoupled, providing a semi-binding interface that does not require stream data to be consumed. Our stream-specialized microarchitecture benefits from stream-based prefetching, decoupling of address computation, and stream-awareness in prefetch throttling and cache bypassing. Broadly, this paradigm of encoding rich memory access semantics could open up new opportunities for specialization of access and communication at even higher levels within the cache and memory hierarchy.

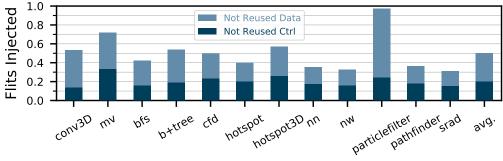

In-Cache Near-Stream Computing We then explore the idea of decoupling long-term access patterns, i.e. streams, with computations into on-chip caches. Instead of always bringing data to the core, computations are offloaded along with streams and are performed near the data. We propose microarchitecture extensions that can recognize near-stream computing opportunities and offload computations to remote cache banks while still maintaining the precise state with low overhead. It dramatically reduces the network traffic and improves core utilization, all without requiring programmer involvement. More importantly, this work breaks with the core-centric view and explores using memory streams as the basic unit for near-data scheduling. This hybrid approach is key to enabling high-performance and energy-efficient execution in future large-scale multi-core systems.

Software Co-Design for Data Layout We propose the first general and programmable framework that automatically optimizes data layout for any near-data computing technique. The idea is to capture the essential data affinity requirement, i.e. X should be close to Y, in a lightweight memory allocator interface. For example, when allocating the vectors A[N],

B[N] and C[N], the programmer can specify that they should be element-wise aligned for near-data computing. Another example is pointer-based data structures, e.g. linked lists, with the new node allocated closer to the previous one. Complemented by co-optimized data structures, runtime libraries, minimal OS extensions and microarchitecture tables, it achieves a clean layered design that systematically captures data affinity information and optimizes data layout throughout the system stack. Evaluated with critical dense scientific computing and irregular graph processing workloads, it achieves  $2.36 \times$  speedup and  $1.82 \times$  energy efficiency over a state-of-the-art near-data computing technique. More importantly, it also yields 75% traffic reduction, making near-data computations truly near the data.

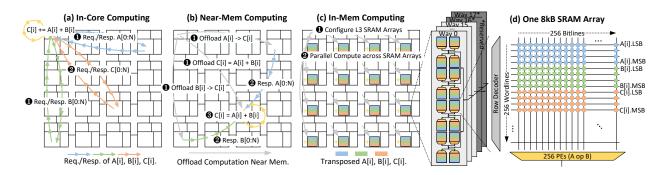

Fusing Near-Cache and In-Cache Computing While this new stream abstraction captures the essential program semantics, it remains neutral to the underlying hardware details. This makes it possible to apply it to improve the programmability and usability of other emerging computing paradigms, or even to fuse multiple paradigms. A particularly interesting case is bit-serial in-cache computing, in which each cache bitline is a vector lane, forming a massive vector unit (e.g. a 64MB L3 cache with 256x256 SRAM arrays has 2M vector lanes). Due to the massive parallelism, it is especially effective for large dense computations, e.g. matrix operations, but is not as efficient for irregular computations. Hence we need a hybrid paradigm.

Our stream abstraction captures essential program semantics to effectively fuse both paradigms. First, dense regular operations are often represented as computation involving multiple affine streams. By relaxing the sequential semantics of stream and allowing all stream elements to be processed in parallel, we can easily exploit the massive parallelism provided by in-cache computing without introducing another set of abstractions. Second, irregular sparse operations can still be handled as normal near-cache computing using irregular streams. We performed an end-to-end case study on the state-of-the-art point cloud application: PointNet++, in which the dense multi-layer perceptron (MLP) is handled by in-cache computing, while irregular operations, e.g. sampling centroids, gathering neighbor-

| Chap. | Topic                                | Author's Related Prior Work     |

|-------|--------------------------------------|---------------------------------|

| 2     | Stream Characterization and ISA      | ISCA 2019 [28], HPCA 2022 [31]  |

| 3     | In-Core Stream Specialization        | ISCA 2019 [28]                  |

| 4     | Stream-based Proactive Cache         | HPCA 2021 [32]                  |

| 5     | In-Cache Near-Stream Computing       | HPCA 2022 [31]                  |

| 6     | Automatic Data Affinity Optimization | MICRO 2023 [33]                 |

| 7     | In-/Near-Cache Computing Fusion      | ASPLOS 2023 [30], CAL 2022 [29] |

| 8     | Conclusion                           |                                 |

Table 1.2: Dissertation Organization and Relation to Author's Prior Work

ing vertices' feature vectors, are left as near-cache computing. This unifies two computing paradigms using a *single* abstraction, and achieves  $1.92\times$  speedup over the baseline, and  $1.20\times$  over the best of individual paradigm [29, 30]. This demonstrates the potential of a unified abstraction to fully unleash the benefit of data-computation orchestration.

# 1.4 Organization

Table 1.2 summarizes the organization of the dissertation and the author's related prior works. In the rest of this dissertation, we first introduce stream definition, stream characterization as well as the proposed stream ISA in Chapter 2. Following that, we discuss how to exploit streams and support in-core stream specialization in Chapter 3. Then we move on to how to leverage streams to enable proactive and decentralized cache optimizations (Chapter 4), and how to schedule computation along with streams (Chapter 5). Chapter 6 enables automatic software co-optimization for data affinity, and Chapter 7 leverages streams as the unified abstraction to fuse in-/near-memory computing. We conclude in Chapter 8.

# CHAPTER 2

### **Stream Basics**

In this chapter, we first define and characterize streams in representative applications to demonstrate that streams are suitable candidates for next-gen memory abstraction (§2.1). Then we move to explore how to embed streams in the ISA (§2.2) and extend them to cover near-data computing (§2.3). We also introduce necessary compiler support to automatically recognize streams and transform the program.

#### 2.1 Stream Characterization

A foundational question for a stream-specialized system is whether *programs* exhibit enough streaming behavior to take advantage of. We define four key questions:

Q1 - Coverage: Do streams cover program access?

**Q2 - Pattern:** What are their access patterns?

Q3 - Length: Are streams long enough to be meaningful?

**Q4 - Control:** Are they entangled with the core's control flow?

This section attempts to answer the above questions through a trace-based analysis of streams. The observations both justify our motivation and provide insights for the ISA and microarchitecture.

**Stream Definition** For this analysis, we empirically characterize patterns that may eventually be capturable by an instruction as streams. where the longest extent is defined as the entry and exit of the outermost containing loop.

**Desirable Properties** Extracting access patterns from memory streams and decoupling them from the von Neumann order of the program is key to achieving high performance and energy efficiency. However, certain memory streams are more amenable than others for specialization. In particular, certain properties are desirable, so we consider streams with these properties to be "qualified":

- Within an inlinable loop: This is because saving and restoring streams at functioncall boundaries would be more expensive than for a scalar register.

- Address is Control Independent: We intend to leave control decisions within the non-stream portion of the program, so that traditional speculative execution may take advantage. We disqualify control-dependent address computation, as supporting this would simultaneously eliminate the benefit of decoupling (close interaction with non-stream instructions), and make analysis for cache specialization more difficult.

- Affine Strides: This restriction keeps the hardware for streams trivial (an integer ALU is sufficient) and also enables simple analysis by cache hardware.

Three Clarifications First, these properties only need to hold up to some loop nesting level, because they can be considered to start at that level. Second, data-dependent streams (indirect and pointer-chasing) are still potentially quite profitable to target, as their addresses are still control independent. Third, it can still be profitable to target streams where not all elements of the stream's data are guaranteed to be used – i.e. the memory access can be control dependent. Note that the access being control dependent is orthogonal to the address being control dependent, and control-dependent access is not disqualified.

**Methodology** We profile SPEC CPU 2017 [34] to capture general application behavior, as well as CortexSuite [35, 36] to reflect the importance of data processing. To analyze the workloads, we use dynamic instrumentation and trace analysis. We exclude stack spilling accesses as it would inflate the number of affine stream accesses.

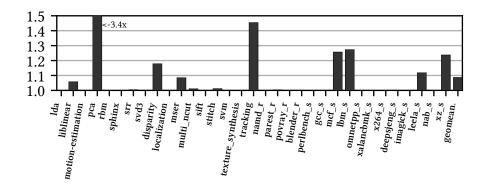

Figure 2.1: Stream Breakdown (PC: Pointer-Chasing)

Q1 and Q2: Coverage and Pattern Fig 2.1 shows the breakdown of dynamic memory accesses. Memory accesses outside of inlinable loops are labeled "outside". Depending on its access pattern, each qualified stream is further classified as affine, indirect or pointer-chasing (PC). On average, 51.49% dynamic memory accesses belong to affine streams, while 10.90% come from indirect streams and 0.3% from pointer-chasing streams. Although on average indirect streams contribute less than 12%, for some benchmarks more than 40% of stream accesses are indirect, e.g. namd\_r. These benchmarks require efficient support for dependence between streams to achieve high performance.

**Observation 1:** More than 60% of dynamic memory access instructions belongs to a stream with specializable properties.

**Observation 2:** Affine streams are the most common, while indirect streams are also common for some benchmarks.

Figure 2.2: Average Stream Length

Q3: Length Fig 2.2 shows the breakdown of stream accesses by the stream length. 51% of stream accesses belong to a stream of length at least 1000, and 62.1% come from streams with length at least 100. Notice that a stream of length N represents at least N loop iterations (greater if we consider the reuse of stream elements). Therefore, even a shorter stream may span across a long instruction window if the loop body is large.

**Observation 3:** Streams are generally long enough to convey meaningful patterns, while shorter streams are also common, requiring low initialization overhead.

Q4: Interaction with Control For general-purpose workloads, it is common for streams to coexist with the core's control flow. To characterize the degree of this interaction, Fig 2.3 shows the accumulated distribution of stream accesses, grouped by the number of control paths within the loop containing that static memory access instruction. Loops with 3 or more control paths contribute 27.7% of dynamic stream access.

Figure 2.3: Number of Control Paths

**Observation 4:** Because many stream accesses coexist with control flow, it is essential for the ISA to decouple control flow.

# 2.2 Decoupled-Stream ISA

In this section, we first make an argument for the requirements of a stream-specialized interface. We then define the decoupled-stream ISA informed by these requirements.

#### Stream ISA Requirements

In  $\S 2.1$ , we find that streams are common (> 50% of dynamic access), which is promising. However, some streams are shorter (37% less than 100 accesses), streams often have indirect access (about 11%), and streams often coexist with control flow (> 50% of stream accesses). Therefore, we argue that a decoupled-stream ISA interface should have five qualities:

- Integration-simplicity It should be lightweight and not require excessive core modification, while also efficiently conveying stream patterns to hardware with low overhead for short streams.

- **2** Generality It should be able to capture both regular and irregular (indirect, pointerchasing) memory access patterns.

- **3 Pattern-simplicity** The stream definition should be analyzable by hardware (for stream-aware cache policies).

- **4** Control under streaming It should enable control-dependent access, without interfering with the core speculation.

- **5 Abstract** It should not expose the underlying microarchitecture.

**Decoupled-stream ISA Approach** Streams are initialized through a configuration instruction that defines the pattern. To communicate with the core pipeline, each stream is assigned a pseudo-register, which is a register implicitly mapped to stream data. This means that instructions which consume/produce stream data remain unmodified, keeping the integration simple (req.1). Streams may specify other streams as dependences, which enables generality across irregular types (req.2). Streams are simple to analyze because there are only a handful of common patterns (req.3).

Streaming under control (req. 4) is possible because of how we update the meaning of each pseudo-register, i.e. the data item a pseudo-register corresponds to within the stream. Specifically, our approach is to add a "step" instruction to the core, which indicates the advancement of the stream from the core's perspective. This implies that data within the stream may be used multiple times, or even ignored if not needed depending on the core control flow.

Streams are general and ubiquitous, and therefore useful across subsequent ISA generations (req. 5). The only aspect of the microarchitecture exposed is the number of pseudoregisters, which represents the number of streams supported simultaneously.

### **Decoupled-Stream Concepts**

The following are the essential components of the ISA extensions:

- Streams: Streams are decoupled portions of the program which together generate memory accesses. They are explicitly constructed and deconstructed (stream\_cfg and stream\_end instructions), and their data can be accessed by traditional instructions through pseudo-registers.

- Stream Types and Dependence: There are two stream types: memory streams describe a memory access pattern; and induction streams define a repeating pattern of values. Memory streams are dependent on either 1. induction variable streams (affine access patterns), 2. other memory streams (indirect access patterns), or 3. themselves (pointer-chasing).

- Pseudo-registers and Stream Stepping: A pseudo-register is a register which refers to a stream's data. The meaning of the register, the position into the stream, is updated by a stream\_step instruction to the associated induction variable stream. In other words, a stream\_step advances the pseudo-register position of all dependent streams.

- Memory Semantics and Architecture State: Semantically, a load occurs at the point of the first use of a pseudo-register corresponding to a load stream after stepping or configuring, while a store happens at every write to a pseudo-register of a store stream. Pseudo-registers become part of the architecture state after their first use and are removed from the architecture state after stepping the corresponding induction variable stream.

- Pseudo-register Width: Pseudo-registers have a definable width, which determines the amount of data read by each step instruction. Instructions that access narrower portions of the register specify an offset.

#### Stream-ISA Extensions

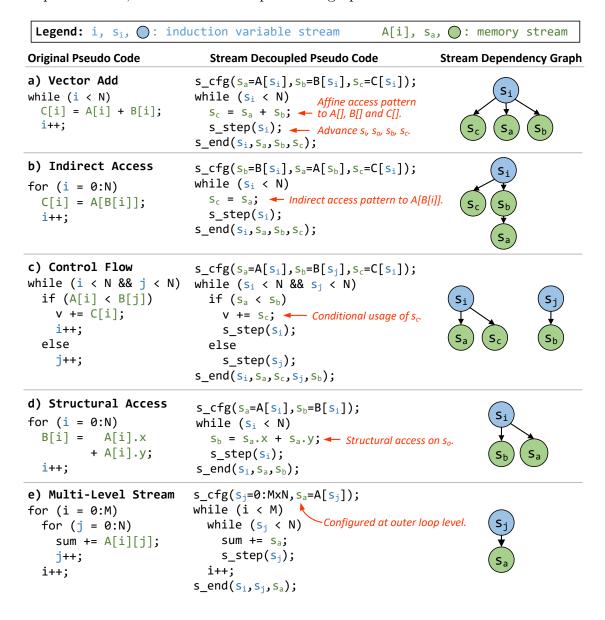

To explain the ISA intuitively, we describe its principles and potential through a series of examples that stress its different aspects. Fig 2.4 shows five examples, with the decoupled-stream pseudo code, and the stream dependence graph.

Figure 2.4: Decoupled Stream ISA Examples

Basic Operation – Fig 2.4(a) The example is a dense vector addition, using three affine streams. There are two load streams A[i], B[i] and a store stream C[i], which are all dependent on an induction variable stream i. Each stream is assigned a pseudo-register, which is used by the traditional instructions to interact with streams. Next, we explain the use of stream instructions.

s\_cfg: A s\_cfg instruction is inserted before entering the loop which uses the stream's data. It defines all of the streams within this loop level, including their type (induction/memory), pattern (stride, width, and optional length), dependences, and starting address<sup>1</sup>. This interface conveys stream information at a coarse granularity, using a stable interface.

In practice, after the configuration is complete, the hardware may begin fetching data ahead of the core's requests based on the program. Also, note that the stream's data never needs to be consumed, though an unused stream would occupy a pseudo-register.

s\_step: As described earlier, the s\_step instruction advances the pseudo-register position of the induction variable and dependent streams. In this example, stepping s\_i will also advance s\_a, s\_b and s\_c by one element. This highlights how the approach of implicitly stepping dependent streams avoids redundant step instructions.

An alternative decoupled ISA could have used a "destructive read" interface, where a read of a pseudo-register implicitly advances the state. This would have worked well in this example, eliminating the need for step instruction. However, this would not allow control-dependent access, as described shortly.

s\_end: The s\_end instruction deallocates a set of streams from the corresponding pseudoregisters. Generally, this happens after the loop in which the stream use occurred, but an explicit s\_end enables the termination of a stream to be data-dependent.

<sup>&</sup>lt;sup>1</sup>This can be implemented with a series of instructions for each stream. While this is shown abstractly in the figure, in our implementation, it is an instruction cache load of configuration data, interpreted by the hardware.

Indirect Memory Access – Fig 2.4(b) Indirect memory access is supported by making the address of one memory stream dependent on the value of another. In this example, s\_a is dependent on s\_b. We also refer to s\_b as the base stream of s\_a. Note that s\_a is also stepped with the s\_step of s\_i.

Control Flow – Fig 2.4(c) The s\_step interface enables the ISA to specify control-dependent access, meaning that a stream element may be used 0 times, once or many times. This example iterates over the elements of a[i] and b[j], but their relative ordering is data-dependent. This is implemented by conditionally stepping stream s\_i and s\_j depending on the outcome of the comparison. Having a s\_step instruction makes it trivial to support such a scenario, by simply replacing the increment instruction with a corresponding s\_step.

Notice that here not every element of s\_c will eventually be used. In a traditional ISA, such unused elements make it harder for the prefetcher to figure out the access pattern and prefetch for future elements. With the help of the compiler and the support of explicit control on when to step the stream, we effectively decouple the access pattern from the control flow. This also enables a new opportunity for the hardware, as now it knows the addresses and can speculate whether the stream element will be used and whether it should prefetch.

Coalescing Streams – Fig 2.4(d) In some situations, memory access patterns become more regular when coalescing from two static instructions. A common scenario is iterating through an array of structs, as shown in the example. Here the structural accesses on  $\mathbf{x}$  and  $\mathbf{y}$  fields can be coalesced into a single stream, where the pseudo-register width is now doubled. This reduces the total number of streams and also makes the access pattern contiguous.

To support this, the user of a pseudo-register may add an immediate offset parameter to specify the offset from the head of the pseudo-register<sup>2</sup>. In this example, s\_a.y has an offset of 4 bytes (assuming int32\_t data type).

<sup>&</sup>lt;sup>2</sup>In theory, this support could be added to the ISA by extending each instruction or adding a header byte to specify the offset. In our implementation, we add this information to the stream configuration.

Multi-Level Streams – Fig 2.4(e) It is sometimes advantageous to configure a stream at an outer loop level to increase the length. This example iterates over a 2D array and is transformed into a single memory stream. Because N is known and there is no conditional stepping, the affine access pattern can be determined before entering the outer loop. The induction variable  $\mathbf{i}$  is not specialized as a stream in this example, while the induction variable stream  $\mathbf{s}_{-\mathbf{j}}$  iterates from 0 to  $M \times N$ .

### Pattern Limitations and Speculation

The address patterns that we support are limited to those that are decouplable, i.e. determined at the point of configuration. There are two relevant caveats: 1. data may be conditionally used, and 2. the outermost dimension of the pattern can have an unknown length. This corresponds to the two forms of speculation that we allow for address patterns: that cache lines in the pattern are likely useful, and that streams are long enough that the overhead of loading a few extra items is acceptable.

This has implications for how many loop levels we can hoist up the configuration of a stream. If at a given outer level either the trip count of the inner loop becomes unknown, or the induction variable becomes conditionally stepped, then the decoupling invariant can no longer be maintained.

## 2.3 Near-Stream Computing Abstraction

Here we discuss extensions to decoupled stream ISAs [28] to associate streams with computation, as well as the compiler support.

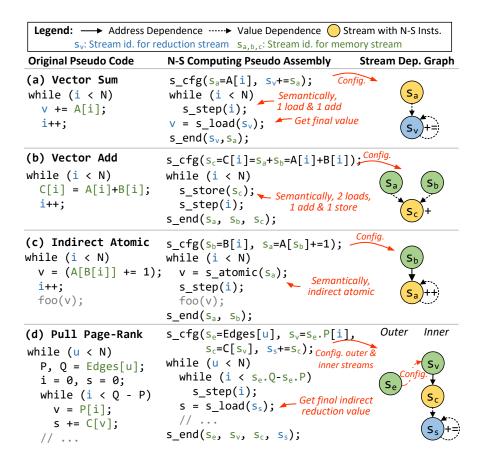

Figure 2.5: Near-Stream Computing ISA Examples

#### **Near-Stream Computing ISAs**

We extend streams to define co-located computation, or near-stream instructions. Many types of streams can have near-stream instructions: load streams (computing using loaded values), store streams (computing values to be stored), atomic streams (the atomic function is defined by the stream), and special reduction streams (computing using its previous result and loaded values). When there is a choice of associating an instruction with one or another stream, the compiler decides based on heuristics to optimize data traffic and reuse (see §2.4).

Besides the normal address dependence for the access pattern, streams with computation may also have value dependencies if they take other streams' data as their computation inputs. We define the user as the value-dependent stream and the provider as the value-base stream. Loop-invariant inputs are provided at configuration time. Streams cannot accept loop-variant core values, as it breaks the decoupling boundary.

Near-stream instructions are outlined in a separate function, with the pointer in the stream configuration. Computation is wrapped in a loop to facilitate pipelined execution of instances of the near-stream instructions. These functions have no memory access and are stackless. They use s\_load/store to communicate the stream inputs/result, and s\_step to advance to the next ready computing iteration. These instructions convey no shared memory semantics in this context and are only used for communication. This approach is general enough for the targeted workloads.

**Examples** Fig 2.5 shows four examples in the near-stream computing ISA, each demonstrating a specific feature.

Reduction - 2.5(a): A reduction stream  $s_v$  sums a load stream  $s_a$ .  $s_v$  has value dependencies on  $s_a$  and itself. The in-loop  $s_l$ oad is eliminated as the reduction is decoupled from the core. Instead, after exiting the loop, a  $s_l$ oad retrieves the final result.

Store - 2.5(b): A store stream  $s_c$  has two value dependencies on load streams  $s_a$  and  $s_b$ . The  $s\_store$  recieves both the address and stored value from the store stream  $s_c$ , and semantically it completes several near-stream operations: 2 loads, 1 addition and 1 store.

Atomic - 2.5(c): A s\_atomic instruction performs the atomic operation on the indirect stream address, and returns the new value, which is consumed by foo().

Nest - 2.5(d): To avoid frequent configuration of short inner loop streams, we extend the stream ISA [28] to allow nesting of stream configuration. The inner loop streams' configuration and trip count must only depend on outer stream or loop-invariant data. Each outer stream iteration instantiates a new inner loop stream. A conditional inner loop can also be nested, as long as the condition purely depends on outer streams; this is transformed into predication in the configuration.

### 2.4 Compiler Support

We implement compiler support to identify streams and transform the original program to decouple streams with near-stream computations. We implement the compiler transformations using LLVM IR [37]. Programs are transformed and compiled to an extended x86 backend with new stream instructions.

### Decoupled-Stream ISA

To support decoupled-stream ISA, there are three phases: recognizing stream candidates, selecting qualified candidates, and code generation.

Recognizing Stream Candidates The compiler treats every static memory access instruction in a loop as a candidate for a memory stream, and every  $\phi$  node in the loop entrant basic block as an induction variable stream.  $\phi$  nodes not in the loop entrant basic block represent other control-dependent values and are not considered as candidates. Starting from the candidate instruction, the compiler performs a backward search on its operands, gathering instructions until it encounters a loop-invariant, a constant, or another candidate instruction. It will also record dependencies between stream candidates.

Selecting Stream Candidates After finding the candidates, the compiler identifies all candidates qualified for stream decoupling. First, a candidate can only be qualified if it has a simple enough pattern to match the supported affine, indirect, and pointer-chasing patterns. Specifically, it can not contain any  $\phi$  node, which represents control-dependent address generation. Also, it should not contain any unsupported operations, e.g. floating point operations.

Second, the compiler checks the dependencies between streams. A trivial constraint is that if any of its base streams within the same loop level is unqualified, the stream is unqualified. A more sophisticated case is to handle multiple induction variables. To support

configuring streams in outer loops, if the address pattern limitations in 2.2 are satisfied, we remove the dependency on any outer loop induction variable so that the memory stream depends on only one innermost induction variable (the iteration domain is incorporated into the inner loop variable). If this is not possible, the stream becomes unqualified.

During this phase, the compiler coalesces affine streams with the same induction variable and small offsets between their elements. The compiler also drops some qualified streams if the total number of streams exceeds the maximum. The compiler prioritizes memory streams with no dependent streams to drop, as they are less likely on the critical path.

Similar to some prior work [38, 39, 40], we take a hardware/software codesign approach to memory aliasing. The compiler records which loads and stores may alias, so that non-aliasing streams can bypass the core's LSQ.

Code Generation During the code generation phase, the compiler first generates the stream configuration for the selected candidates. The configuration specifies 1. which pseudo-register to represent the stream; 2. the type of the stream (induction, load, store); 3. loop invariant values (stride, width); and 4. stream dependencies.

The compiler transforms the loop by 1. inserting stream\_cfg, stream\_step and stream\_end instructions; 2. replacing the operand of a user instruction with the corresponding pseudo register, along with the offset within the element (for a coalesced stream); 3. removing the memory access instruction for a memory stream, and possibly insert a dummy user instruction to ensure the original program order is preserved; and 4. if there are no other users, remove the address computation instructions.

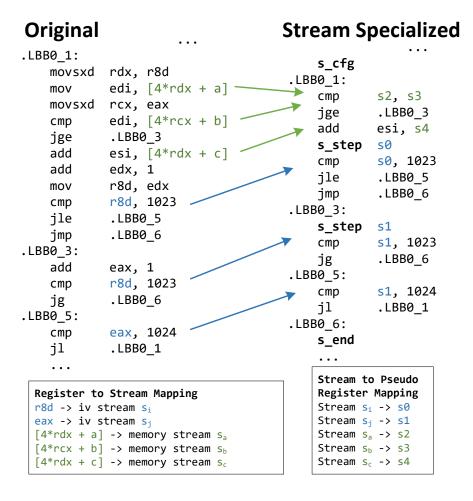

Fig 2.6 shows both the original and transformed X86 assembly code for example in Fig 2.4(c). The stream operands are replaced by the corresponding pseudo-registers.

Figure 2.6: Decoupled Stream Assembly Example

#### Support Near-Stream Computing

Ideally, we could formulate this as an optimization problem to find the best slicing between computations and streams. However, we find a heuristic-based approach is capable of handling the existing workloads. Specifically, the compiler tries to recognize load computation, store computation and reduction one by one:

**Load** For each load stream, the compiler performs a BFS on its user instructions, and checks if visited instructions form a closure, i.e. no outside users except the candidate final instruction. If so, and the final instruction has a smaller data type, the compiler slices out

the visited instructions, with the final instruction as the return value. The compiler iterates to find larger closures with fewer bits total in live outputs. Algorithm 1 covers the details.

**Store** Similar to loads, the compiler searches for instructions computing the stored value, and records a value dependence when encountering a load instruction (or its final instruction).

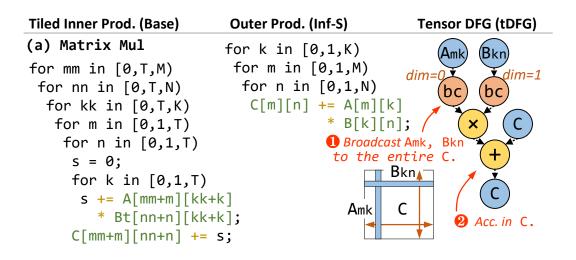

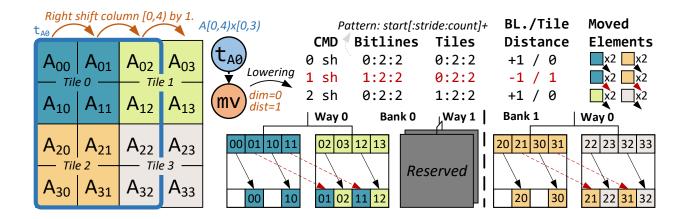

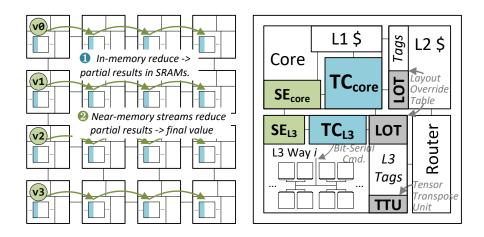

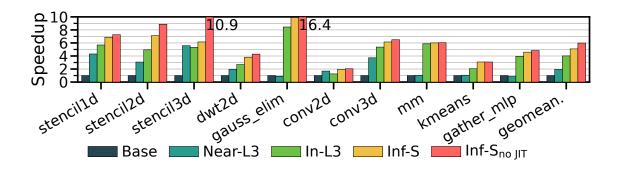

**Reduce** Reduction variables are typically represented as *phi* nodes in the loop entry basic block, and can be recognized by searching backward for computation instructions. The initial value for reduction is recorded either directly in the configuration (if constant) or as a live input at runtime.