## **UC Riverside**

### **UC Riverside Electronic Theses and Dissertations**

#### **Title**

Multi-Objective Design Automation for Microfluidic Capture Chips

### **Permalink**

https://escholarship.org/uc/item/3pp0d359

#### **Author**

Chen, Lisa

### **Publication Date**

2022

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA RIVERSIDE

Multi-Objective Design Automation for Microfluidic Capture Chips

A Thesis submitted in partial satisfaction of the requirements for the degree of

Master of Science

in

Computer Science

by

Lisa Chen

September 2022

#### Dissertation Committee:

Dr. Philip Brisk, Chairperson

Dr. William H. Grover

Dr. Manu Sriharan

University of California, Riverside

#### Acknowledgments

I am grateful to my advisor, Dr. Philip Brisk, without whose help and kind mentorship, I would not have been here. He has given me the opportunity to pursue a graduate degree, which is a first in my family, extended an all. I greatly appreciate his quick but extremely detailed emails to my many questions due to my being new to the graduate program and few to rely on to help me. I would also like to thank the rest of my committee, Dr. William Grover and Dr. Manu Sridharan, for their helpful guidance through this research. Overall, I am grateful for all the professors' efforts to make the research process as smooth and painless as possible, even during the middle of a pandemic.

Although there are many UCR staff out there that is extremely helpful and attentive to students' needs, I would like to especially thank Vanda Yamaguchi, the Graduate Student Services Supervisor. I know she is extremely busy with many graduate students to manage. Thank you for always somehow returning my emails in a timely manner and patience for my many questions throughout the years.

I also would like to thank my friends, both current and new, who have helped and supported me throughout the graduate degree process and switching to the Computer Science field. I especially want to thank Tania Kurbessoian, Xinxin Xie, William Lam, Justin Li, Frank Chen, Benson Chen, and Douglas Choi who have done a lot for me during the whole process. In the times I felt lost or the topics confusing, they have helped me even during their busy schedules or during their game nights outside of work. I also was able to lean on them for consultations and just someone to talk to when I felt lost or just wanted to relate to someone. I am eternally grateful and cherish our friendship.

To my parents and brother, I would like to thank them for their support and attempts for understanding my decision to choose to pursue a graduate program even after being in biological industry for over 5 years. It was definitely not an easy path, and they have supported my decision and me mentally and financially. The care packages, although sometimes excessive and unnecessary at times, were still welcomed as they came from the heart. Thank you very much for all the support in the best way you knew how, large amounts of food and random gadgets.

Campus Apartment Resident Association (CARA) has also been a tremendous help in giving me a place to live at cheaper rates while also providing a family of friends to give me support throughout the past year. Through the organization's aid, the journey is thankfully less stressful. I appreciate CARA for granting me this opportunity to be a part of their team.

I would like to thank the following generous fellowships and stipends which made this research possible:

- UCR for their Dean's Distinguished Fellowship

- The Department of Education for their Graduate Assistance in Areas of National Need (GAANN) Fellowship.

### This dissertation is dedicated to:

- My parents and brother for all the support in pursuing a graduate degree even though it was not particularly normal or something easy to understand for them.

- My friends and fiancé for helping me through the process of pursuing the graduate program and switching fields.

#### ABSTRACT OF THE THESIS

Multi-Objective Design Automation for Microfluidic Capture Chips

by

#### Lisa Chen

Master of Science, Graduate Program in Computer Science University of California, Riverside, September 2022 Dr. Philip Brisk, Chairperson

Microfluidic capture chips are useful for preparing or analyzing a wide range of different chemical, biological, and medical samples. A typical microfluidic capture chip contains features that capture certain targets (i.e. molecules, particles, cells) as they flow through the chip. However, creating optimal capture chip designs is difficult because of the inherent relationship between capture efficiency and flow resistance: as more capture features are added to the chip, the capture efficiency increases, but the additional features slow the flow of fluid through the chip. This thesis introduces the use of multi-objective optimization to generate capture chip designs that balance the trade-off between maximizing target capture efficiency and minimizing resistance to fluid flow. Design automation for this important class of microfluidic chips has not been attempted previously. Our approach automatically produces a Pareto Front of non-dominated chip designs in a reasonable amount of time, and most of these designs have comparable capture efficiency to hand-designed chips with far lower flow resistance. By choosing from the chip designs on the Pareto Front, a user

can obtain high capture efficiency without exceeding the flow resistance constraints of their application.

# Contents

| Li     | ist of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | X                 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Li     | ist of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xiv               |

| 1      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                 |

| 2      | Problem Formulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7                 |

| 3      | Capture Chip Design Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                |

| 4      | 4.1 NSGA-II Variable Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18<br>20<br>21    |

| 5      | Results 5.1 Generating capture chips with constant numbers of posts 5.2 Generating capture chips with larger numbers of posts 5.3 Generating capture chips with variable numbers of posts 5.4 Generating capture chips with different shaped posts 5.5 Runtime analysis 6.6 Runtime analysis 6.7 Runtime analysis 6.8 Runtime analysis 6.9 Runtime analysis 6.9 Runtime analysis 6.0 Runtime analysis | 21 22 27 28 34 37 |

| 6<br>7 | Related Work  Conclusion and Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40                |

| •      | ibliography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45                |

# List of Figures

| 1.1 | (a) A typical capture chip design consisting of a microfluidic channel filled with an array of circular posts. When a capture target (molecule, particle, cell, etc.) represented by a blue circle flows through the channel, it interacts with the posts and may eventually be captured by one. (b) When the channel is packed more densely with posts, the likelihood of a target interacting with a post and becoming trapped increases, but the paths for fluid to flow around                                                                                                                                                                                                                                              |   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|     | the posts grow more narrow; this can severely limit or even stop the flow of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

| 1.2 | fluid through the device and render it inoperable. *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | į |

|     | the channel to carry $\frac{1}{16}$ the flow $Q$ (if the pressure applied $\Delta P$ is unchanged) or require $16\times$ the pressure (if the flow rate is to be unchanged). This means that pressure and flow in a microfluidic device are far more sensitive to device design than voltage and current are in an electronic device. Consequently, just as voltage and current are essential aspects of electronic design optimization, pressure and flow $must$ be included in microfluidic design optimization. (The other variables in the equations are constants: $L = \text{length of the conductor or channel}$ , $\rho = \text{resistivity of the conductor}$ , and $\mu = \text{kinematic viscosity of the fluid.}$ ) | ( |

| 2.1 | The post shapes that are evaluated in this thesis. From left-to-right: circle,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

| 2.2 | (equilateral) triangle, square, pinwheel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ( |

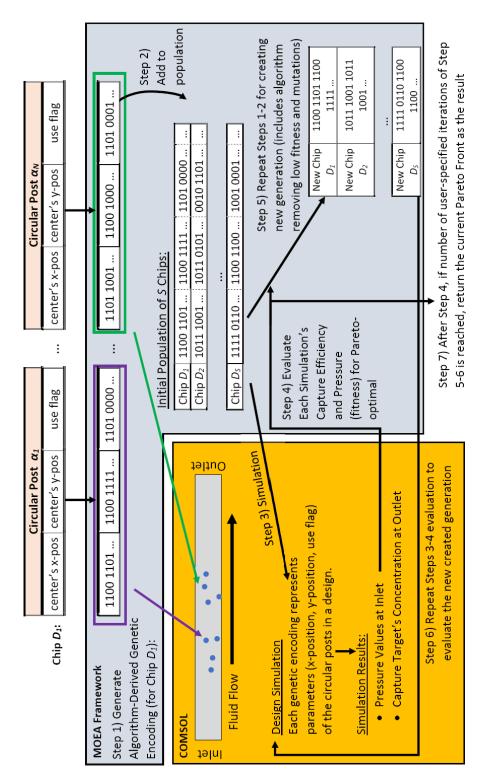

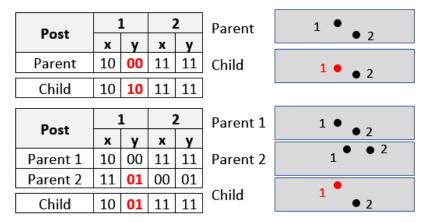

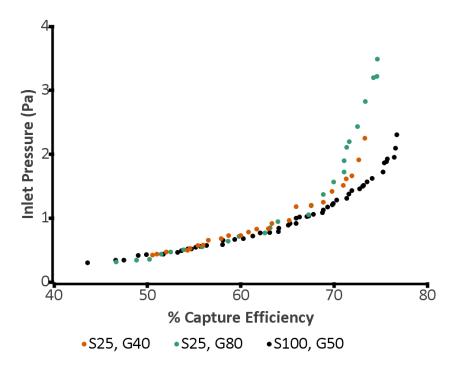

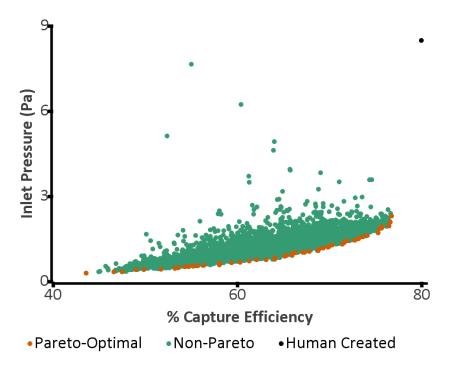

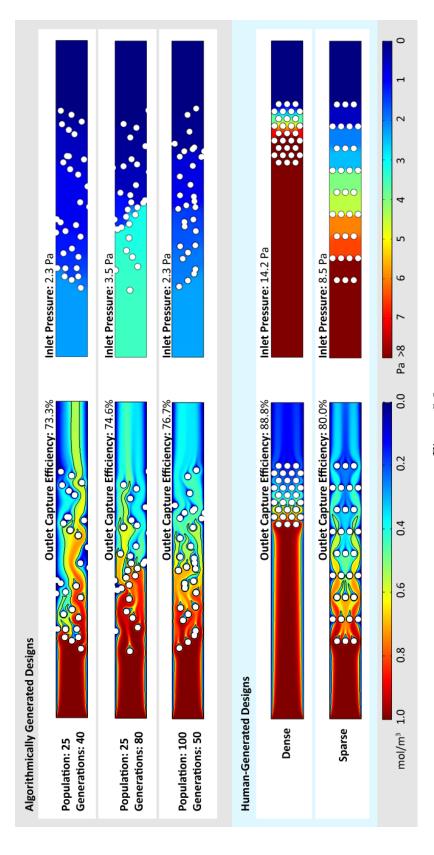

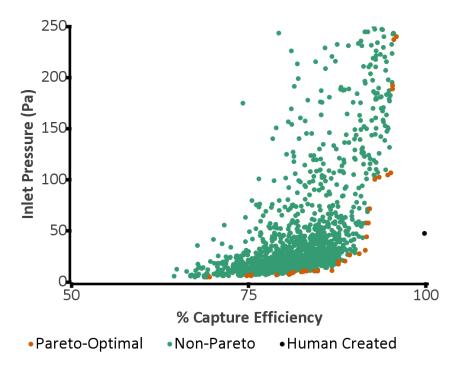

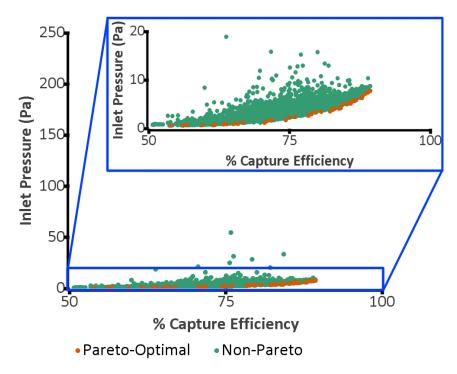

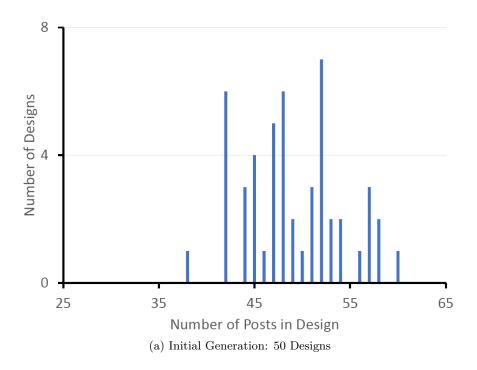

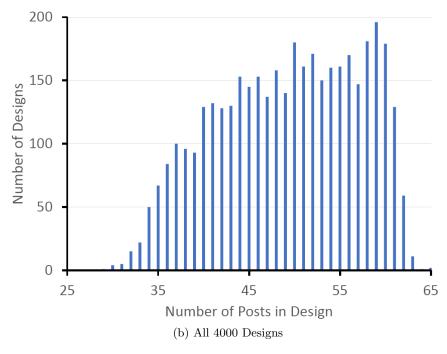

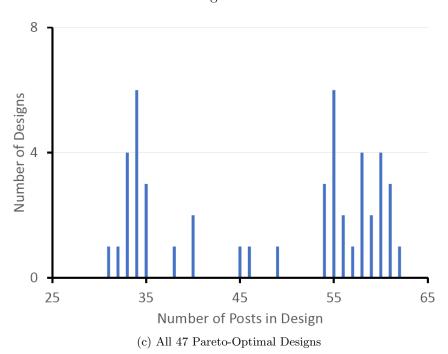

3.1 (Continued from previous page) Overview of our microfluidic capture chip design framework (configured for circular posts). The framework is implemented using NSGA-II, which is integrated into a larger open source Multi-Objective Evolutionary Algorithm (MOEA) framework [1], to enumerate chip designs and maintain a front of Pareto-optimal design points. NSGA-II/MOEA interfaces with finite-element simulation software (COM-SOL Multiphysics) which performs the simulation. For each chip, the simulation predicts the concentration of the capture target at each point in the chip (used to quantify how much of the target was captured by the chip) and the pressure that develops at the inlet (which is an indicator of fluid flow resistance as discussed in Figure 1.2). NSGA-II maintains and evolves a population of encoded chip designs (chromosomes) which encode post positions (genes). Each chip design enumerated by the NSGA-II procedure is simulated by COMSOL Multiphysics, and the results are transmitted back to NSGA-II to update the Pareto Front based on fitness. This whole process 14 A simplified example illustrating how uniform mutation (top) and uniform crossover (bottom) affect capture chip designs in our framework. Each variable is represented by a two-digit binary value (though in experiments, the binary values are much larger). For this example, we consider only the x and y coordinates of a circular post; to vary the number of posts (not shown), the Boolean flag for determining whether a post is used in the design will also have the same probability of being mutated as the x and y positions. For uniform mutation, each variable has an equal chance of being randomly mutated. For uniform crossover, each of the indices have equal probability of being swapped with another chip design of the same generation. . . . . . 15 Inlet pressure vs. capture efficiency for experiment runs with a constant number of posts (31) and different population sizes (S) and generation counts (G). The different experiments yielded similar results for designs that prioritize low flow resistance (lower-left corner). However, for designs that prioritize capture efficiency, the experiments with the largest total number of analyzed 23 Inlet pressure vs. capture efficiency for each capture chip design created during the experiment with 31 posts, population size S = 100, and generation count G=50, along with the result from the human-designed "Sparse" chip design shown in Figure 5.3. Non-Pareto chip design results with inlet pressures higher than 9 Pa are not shown. While the human-designed chip has a slightly higher capture efficiency than our computer-designed chips, it suffers 24 5.3 (Continued from previous page) Capture chip designs and simulation results for the designs with the highest capture efficiency from each of the three 31post experiments, along with results from the human-generated "Dense" and "Sparse" chips. For each design, two simulation results are shown. On the left is the predicted concentration of capture target at each location of fluid in the chip during operation. All chips receive the same high concentration of target (red; 1 mol/m<sup>3</sup>) flowing in from the left. As target is captured on the capture posts and channel walls, the concentration of target in the solution drops (indicated by a shift to orange, yellow, green, and blue). A chip with 100% capture efficiency would have no remaining target at the outlet (blue: 0 mol/m<sup>3</sup>). On the right is the predicted pressure at each location of fluid in the chip during operation. All chips have atmospheric pressure (0 Pa) at the outlet on the right. Designs with high resistance to fluid flow develop high pressures (red colors) at the inlet on the left, and designs with low resistance to fluid flow develop low pressures (blue colors) at the inlet on the left. These results show that our computer-generated designs have comparable capture efficiencies to human-generated designs, but with dramatically lower resistance to fluid flow. This gives our computer-generated 26 Inlet pressure vs. capture efficiency for each capture chip design created during the experiment with 100 posts, population size S=50, and generation count G = 40, along with the result from the human-designed 101-post chip shown in Figure 5.7. Non-Pareto chip design results with inlet pressures higher than 250 Pa are not shown. The results show that most of these 100post designs have extremely high resistance to fluid flow (100x higher than the 31-post designs shown in Figures 5.1–5.3); this renders these designs unsuitable for many applications and suggests that an optimal post count for 28 Inlet pressure vs. capture efficiency for capture chip designs created using a variable number of posts (up to 100), with population size S=50 and generation count G = 80. The axes are identical to Figure 5.4 for side-to-side comparison and 0-20 Pa data magnified for better visualization. Comparing this result to the constant 100-post results shows that allowing variable numbers of posts dramatically decreases the flow resistance of the resulting designs, with only a minimal decrease in maximum observed capture effi-29 Distribution of capture post counts in the designs from the variable-postcount experiment in Figure 5.5: (a) the initial generation with random numbers of posts per chip (50 chip designs), (b) all 4000 chip designs generated in the experiment, and (c) only the 47 Pareto-optimal chip designs from the experiment. The shapes of distributions (b) and (c) suggest that certain ranges of post counts per device are favored in optimal capture chip designs. 31

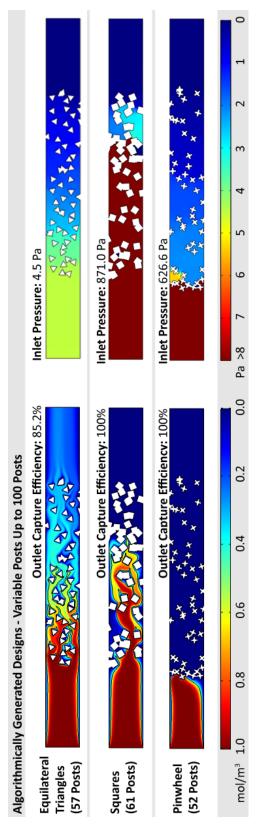

| 5.7 | Capture chip designs and simulation results for the designs with the highest capture efficiency from each of the experiments with variable numbers of |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | posts, along with results from the human-generated design with 101 posts.                                                                             |    |

|     | Capture efficiency (left) and inlet pressure (right) are as described in Fig-                                                                         |    |

|     | ure 5.3. These results show that our best computer-generated designs have                                                                             |    |

|     | comparable capture efficiency to the human-generated designs, but with six                                                                            |    |

|     | times lower flow resistance and almost half the number of posts                                                                                       | 33 |

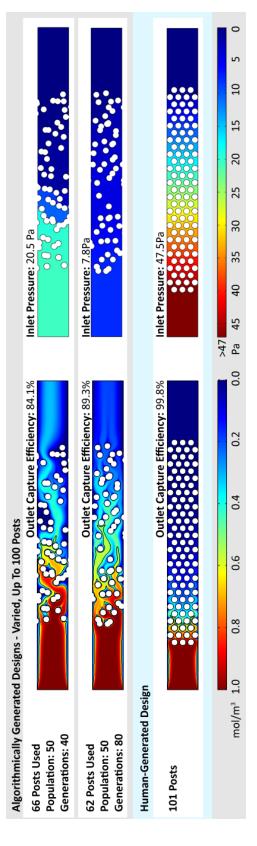

| 5.8 | Inlet pressure vs. capture efficiency for the Pareto Fronts for capture de-                                                                           | 00 |

| 0.0 | signs using different post shapes with up to 100 posts and totalling (a) 2000                                                                         |    |

|     | designs and (b) 4000 designs. 0-25 Pa data is also magnified for better visu-                                                                         |    |

|     | alization for comparison. The results show that circular posts is overall best                                                                        |    |

|     | in attaining lower inlet pressure and higher capture efficiency. Square and                                                                           |    |

|     | pinwheel posts are the only posts able to attain 100% capture efficiency but                                                                          |    |

|     | with extremely high inlet pressures                                                                                                                   | 35 |

| 5.9 | Simulation results for the highest-capture efficiency chip designs for trian-                                                                         | 00 |

| 0.0 | gular, square, and pinwheel-shaped posts, discovered during the 4000 design                                                                           |    |

|     | runs reported in Figure 5.8b. On the left is the predicted concentration of                                                                           |    |

|     | capture target at each location of fluid in the chip during operation. <b>On the</b>                                                                  |    |

|     | right is the predicted pressure at each location of fluid in the chip during                                                                          |    |

|     | operation. Although the triangular posts performed best among the three                                                                               |    |

|     | new shapes in terms of achieve high capture efficiency and low inlet pressure,                                                                        |    |

|     | the highest capture efficiency attained by triangular posts is still lower than                                                                       |    |

|     | the circular post design in Figure 5.7. Squares and pinwheels are able to                                                                             |    |

|     | obtain maximal capture efficiency, but the inlet pressures are likely to be too                                                                       |    |

|     |                                                                                                                                                       | 36 |

|     | large for practical use                                                                                                                               | 50 |

# List of Tables

| 4.1 | Defined parameters for COMSOL and NGSA-II                                      | 19 |

|-----|--------------------------------------------------------------------------------|----|

| 4.2 | Settings for post shapes for designs with variable post quantity. M is defined |    |

|     | as the number of NSGA-II variables while N is defined as the post quantity.    | 20 |

| 5.1 | Runtime Summary for Circular Post Designs                                      | 39 |

| 5.2 | Runtime Summary for $\leq 100$ Posts for Different Shapes                      | 39 |

## Chapter 1

# Introduction

Microfluidic chips have found important applications in a variety of fields, especially chemistry, biology, and healthcare. However, the process of designing a new microfluidic chip for a given application is slow, labor-intensive, and generally limited to researchers with expertise in the field. And while the design space of possible microfluidic devices is enormous, fabricating and testing each chip design is a laborious and time-consuming process. Consequently, most designers can only explore a handful of different device designs, and a researcher has no assurance that their final chip design is optimal or near-optimal for a particular purpose. Thus, there is a need to automate the process of generating new microfluidic chip designs for emerging applications.

This thesis focuses on the algorithmic design of *microfluidic capture chips*, an important class of microfluidic chips. Such chips typically contain tiny features whose surfaces provide locations where molecules, particles, cells, and other targets of interest can be trapped as they flow in fluid through the chip. Many capture chips use arrays of

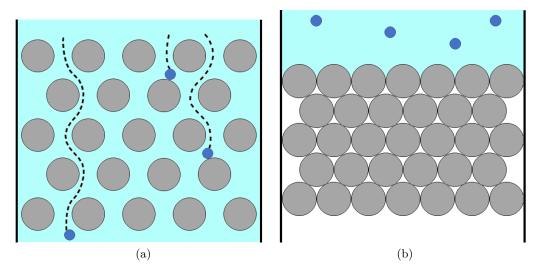

small posts, or pillars, for this purpose [2, 3, 4, 5, 6, 7]. For example, Sequist et al. [2] introduced a chip that utilized an staggered array fof 78,000  $\mu$ m-sized circular posts inside a microfluidic channel to capture circulating tumor cells (CTCs). This typical design is echoed in Figure 1.1a, in which fluid flows through a staggered array of circular posts inside a microfluidic channel. Previous work on design automation of microfluidic chips, summarized in Chapter 6, focused on chips with microvalves or performance-oriented metrics such as assay execution time without focusing on fluid physics [8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18]. This thesis employs a methodological approach to microfluidic design automation, similar in principle to previous work designing passive microfluidic mixers [19], but with objectives and constraints relevant to analyte capture, rather than mixing.

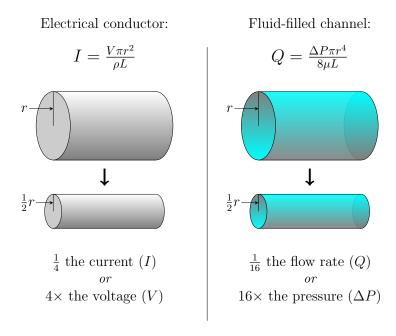

At first glance, it might seem trivial to design the optimal microfluidic capture chip: simply pack as many capture features into the chip as possible. Indeed, this strategy would maximize the likelihood that a given target encounters a capture feature and is successfully trapped in the chip. But this approach has a fatal flaw: packing a microfluidic channel full of capture features would significantly slow or even block the flow of fluid through the channel (Figure 1.1b). Increasing the resistance to fluid flow likewise increases the amount of time and/or pressure required to pump a given volume of fluid through the capture chip, as the fluid-carrying capacity of a fluid channel is proportional to the fourth power of the channel's radius (assuming a circular-cross-section channel for simplicity). For comparison, the electrical-current-carrying capacity of a wire is proportional to the second power of the wire's radius (see Figure 1.2). For this reason, reducing the channel area available for fluid flow by packing the channel with capture features can have an enormous impact on the

flow resistance of the channel, even more of an impact that our intuition from electronics might lead us to expect [20]. In other words, a chip with "perfect" capture efficiency may be practically useless if it takes hours or days (or dangerously high pressures) to pump a sample through it.

Conversely, it is trivial to reduce the flow resistance of a capture chip design—simply remove the capture features that are blocking the flow—but doing so will also reduce the capture efficiency of the device, possibly to the point that the device no longer serves its intended function.

Figure 1.1: (a) A typical capture chip design consisting of a microfluidic channel filled with an array of circular posts. When a capture target (molecule, particle, cell, etc.) represented by a blue circle flows through the channel, it interacts with the posts and may eventually be captured by one. (b) When the channel is packed more densely with posts, the likelihood of a target interacting with a post and becoming trapped increases, but the paths for fluid to flow around the posts grow more narrow; this can severely limit or even stop the flow of fluid through the device and render it inoperable.

Thus, the ideal capture chip design for a given application must balance target capture efficiency and fluid flow resistance. Balancing these two related, yet distinct, metrics within given specifications can be challenging, given existing arduous and time-consuming methodologies of designing, fabricating, and validating microfluidic chips by hand. We, therefore, aim to improve the process through the use of design automation and simulations of capture chip designs, going beyond the regular arrays seen in Figure 1.1 to consider designs not obvious to human designers.

The objective of this thesis is to algorithmically design microfluidic capture chips that balance the trade-off between target capture efficiency and fluid flow resistance. In doing so, this thesis makes the following contributions:

- We characterize the design space for microfluidic capture chips in terms of the placement and geometry of capture features inside a microfluidic channel (Chapter 2).

- We formulate the problem of microfluidic capture chip design as a multi-objective optimization problem (Chapter 3).

- We non-exhaustively explore the design space for microfulidic capture chips using the Non-dominated Sorting Genetic Algorithm II (NSGA-II) [21] (Chapter 3).

- We use finite element analysis simulation (COMSOL Multiphysics) to simulate both the capture efficiency and fluidic resistance of each design candidate (Chapter 3).

- We report successful runs of automated capture chip design generation using a fixed and varying number of capture features and varying the feature geometries (Chapter 5). Our key insights are:

- Varying the number of posts yields comparable capture efficiencies to chips generated using a fixed number of posts, but with dramatically lower resistance to fluid flow; and

- Circular-shaped posts tend to provide better overall performance in comparison to triangular, square, and pinwheel-shaped posts.

The thesis is organized as follows. Chapter 2 defines the problem formulation for microfluidic capture chip design. Chapter 3 introduces our framework for microfluidic capture chip design, emphasizing the design space to explore, its encoding for evolutionary multi-objective optimization, and our approach to evaluate each chip design using finite element analysis simulation. Chapter 4 summarizes the design of our experiments, including a number of relevant parameter settings and human-generated microfluidic chip designs that we use for comparison. Chapter 5 presents the results of our simulation experiments, leading to our conclusions outlined above. Chapter 6 relates our technical contribution to similar attempts to apply the principles of electronic design automation to the domain of microfluidics. Lastly, Chapter 7 concludes the thesis and outlines new directions for future work.

Figure 1.2: Comparing the effects of size reduction on electronic and fluidic systems. For an **electrical conductor** (like a wire, or a trace in an integrated circuit), Ohm's Law and Pouillet's Law state that halving the radius r of the conductor causes the conductor to carry  $\frac{1}{4}$  the current I (if the voltage applied V is unchanged) or require  $4\times$  the voltage (if the current is to be unchanged). However, for a **fluid-filled channel** (like those in microfluidic devices), the Hagen-Poiseuille Law dictates that halving the radius of the channel causes the channel to carry  $\frac{1}{16}$  the flow Q (if the pressure applied  $\Delta P$  is unchanged) or require  $16\times$  the pressure (if the flow rate is to be unchanged). This means that pressure and flow in a microfluidic device are far more sensitive to device design than voltage and current are in an electronic device. Consequently, just as voltage and current are essential aspects of electronic design optimization, pressure and flow must be included in microfluidic design optimization. (The other variables in the equations are constants: L = length of the conductor or channel,  $\rho = \text{resistivity}$  of the conductor, and  $\mu = \text{kinematic viscosity}$  of the fluid.)

## Chapter 2

## **Problem Formulation**

We define a microfluidic chip as a microfluidic channel containing zero or more features that can capture a free-flowing target (molecule, particle, cell, and so on) if it contacts the features. Most published capture devices use circular posts arranged in regular arrays, not because these are necessarily optimal, but because they are simple to design. To explore possible device designs that have not been considered before, we designed our framework to support multiple different post shapes (not just circles) and many different post arrangements (not just regular arrays). That being said, the range of possible capture chip designs is essentially infinite, so some design parameters must be constrained to make a study like ours feasible (for example, we did not consider chip designs that utilize two or more different post shapes in the same chip).

In this work, we constrain the design space to consider chips with four different post geometries shown in Figure 2.1: circular posts, square posts with a  $0-90^{\circ}$  rotation, equilateral triangle posts with a  $0-360^{\circ}$  rotation, and pinwheel-shaped posts with a  $0-90^{\circ}$

rotation. We also assume that all the posts in a given chip design have identical shapes and sizes; this is consistent with most published capture chip designs and allows us to have fewer changing variables and potentially faster convergence in our algorithm detailed later in Chapter 3.

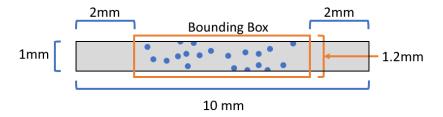

Figure 2.1: The post shapes that are evaluated in this thesis. From left-to-right: circle, (equilateral) triangle, square, pinwheel.

Figure 2.2 illustrates our assumptions about capture chip geometry and the restrictions that we impose on the design space. The designs are two-dimensional but are understood to represent a cross-section through a real three-dimensional channel (so, for example, each circular post actually represents a cylinder that spans from the floor to the ceiling of the channel). We assume that fluid flows from left to right through a 1-mm-wide channel; this channel width was chosen because it is representative of channel widths used in previous capture chips, wide enough to contain a reasonable number of capture posts and a reasonably high flow rate, and narrow enough that the flow inside the channel will be laminar (a Reynolds number  $Re \ll 2300$  [22]; see Chapter 3 for calculation details) as is typical in microfluidic chips. The total length of the channel is set to 10 mm; this value was chosen because the resulting channel is long enough to contain a large number of posts but short enough to be simulated using finite element analysis in a reasonable amount of

time. The algorithm is free to place capture posts within a 6 mm  $\times$  1.2 mm bounding box in the center of the channel as shown in Figure 2.2. The 2-mm-long sections of channel immediately before and after the bounding box are intentionally left free of capture posts to provide room for the "entrance length" [22], the distance required for the fluid flow profile to fully develop and no longer be influenced by the inlet and outlet boundaries. The capture posts are free to overlap with each other (thereby forming larger capture features with more complex shapes) and overlap with the channel wall (thereby extending the walls or narrowing the fluid channel). Finally, while these design parameters were chosen for the reasons noted above and are representative of many existing microfluidic capture chips, these parameters can also be easily changed if a user wishes to optimize a chip design that cannot fit within the constraints used in this study.

Figure 2.2: Capture chip design constraints used in this study. Fluid flows from left to right through a section of channel that is 1 mm wide and 10 mm long. The bounding box designates the region of the channel where the algorithm can place posts (in this example, 0.2 mm diameter circular posts).

We impose a maximum of N capture posts in our design and encode each post as a tuple  $\alpha_i = (x_i, y_i, \theta_i, b_i), 1 \le i \le N$ , where  $(x_i, y_i)$  is the coordinate of the post,  $\theta_i \in \mathbb{R}$  is the rotational angle, and  $b_i \in \{0,1\}$  determines presence or absence of each post, i.e.,

setting  $b_i$  to 0 removes post  $\alpha_i$  from the design. Chips with circular posts can omit  $\theta_i$ , and the number of posts can be fixed by removing  $b_i$  and treating all posts as present.

We explored a range of values for the number of posts N. The specific post counts we used in the study were largely chosen arbitrarily, but we intentionally limited ourselves to 100 posts as a trade-off between device complexity and simulation runtime:

- On one extreme, supporting devices with a massive number of posts (thousands or even millions) would be attractive because actual microfluidic capture devices sometimes use this many posts (e.g., [2]). However, performing finite-element simulation of these complex devices (the main time-consuming step in our technique) would take a prohibitively long amount of time.

- On the other extreme, simulating devices with only a handful of posts (say, 10 or fewer) would be attractive because these simulations can be performed quickly. However, having so few posts severely limits the range of possible device designs explored by our software and complicates comparisons with published results that use a larger number of posts.

In our experience, using 30 to 100 posts provided the needed "sweet spot" between device complexity and simulation runtime.

We characterize the performance of each microfluidic capture chip in terms of two objectives:

• Capture efficiency: the fraction of target molecules flowing into the chip that are successfully captured by the chip.

• Inlet pressure: the amount of pressure that develops at the inlet of the chip during operation (this is directly proportional to the flow resistance of the chip).

The next chapter formally defines these objectives.

## Chapter 3

# Capture Chip Design Framework

Figure 3.1 depicts the key aspects of the microfluidic capture chip design framework presented in this chapter. The search is driven by NSGA-II [21], a multi-objective optimizer. NSGA-II encodes each chip design as a binary chromosome  $D = \langle \alpha_1, \dots, \alpha_N \rangle$ , where  $\alpha_i = (x_i, y_i, \theta_i, b_i)$  represents the position, rotation, and existence of the  $i^{th}$  post. NSGA-II maintains a population size of S chromosomes,  $D_1, \dots, D_S$ .

During each generation, standard evolutionary procedures (see Figure 3.2) are applied to update the population. We applied uniform mutation and uniform crossover with mutation rates of 3/M, where M is the number of variables in the chromosome. Higher mutation rates increase population variability but tend to slow or otherwise limit the rate of convergence. The search terminates after a user-specified number of iterations.

<sup>&</sup>lt;sup>1</sup>To search for a chip design with N circular posts, the number of variables is M=3N, as each tuple  $\alpha_i$  has three fields, noting that  $\theta_i$  is not needed; to search for a chip design with N square, triangular, or pinwheel-shaped posts, the number of variables is M=4N.

Figure 3.1

chip, the simulation predicts the concentration of the capture target at each point in the chip (used to quantify how much of the target was captured by the chip) and the pressure that develops at the inlet (which is an indicator of fluid flow resistance as discussed in Figure 1.2). NSGA-II maintains and evolves a population of encoded chip designs (chromosomes) which encode post positions (genes). Each chip design enumerated by the NSGA-II procedure is simulated by COMSOL Multiphysics, and the results are transmitted back to NSGA-II to update the Pareto Front based on fitness. This whole process is repeated for a Figure 3.1: (Continued from previous page) Overview of our microfluidic capture chip design framework (configured for circular posts). The framework is implemented using NSGA-II, which is integrated into a larger open source Multi-Objective Evolutionary Algorithm (MOEA) framework [1], to enumerate chip designs and maintain a front of Pareto-optimal design points. NSGA-II/MOEA interfaces with finite-element simulation software (COMSOL Multiphysics) which performs the simulation. For each user-specified number of generations.

Figure 3.2: A simplified example illustrating how uniform mutation (top) and uniform crossover (bottom) affect capture chip designs in our framework. Each variable is represented by a two-digit binary value (though in experiments, the binary values are much larger). For this example, we consider only the x and y coordinates of a circular post; to vary the number of posts (not shown), the Boolean flag for determining whether a post is used in the design will also have the same probability of being mutated as the x and y positions. For uniform mutation, each variable has an equal chance of being randomly mutated. For uniform crossover, each of the indices have equal probability of being swapped with another chip design of the same generation.

We require at least 2 mm of spacing between the channel inlet and outlet and the center of each post; and we allow posts to intersect the channel walls as long as at least half of the post (e.g., determined by the radius r of a circular post) must reside within the channel:

$$x_c + 2 \le x_i \le x_c + L - 2 \tag{3.1}$$

$$y_c - r \le y_i \le y_c + W + r \tag{3.2}$$

Each chromosome  $D_j$  in the population is evaluated in terms of our two chosen objectives, capture efficiency  $E_j$  and inlet pressure  $P_j$ , denoted  $(E_j, P_j) \leftarrow F(D_j)$ , where

F is the evaluation function. We implemented F using finite element simulation software (COMSOL Multiphysics) to estimate  $(E_j, P_j)$  for each design that NSGA-II enumerates. COMSOL multiphysics generates a mesh and computes the target concentration and pressure at each point in the mesh.

Capture efficiency  $(E_j)$  characterizes the anticipated percentage of the target flowing in the fluid that each chip design will capture. Let  $C_{inlet}$  be the concentration of target molecules at the channel inlet, and  $c_k$ ,  $1 \le k \le K$  be the capture efficiencies computed by COMSOL Multiphysics at all K mesh points on the channel outlet. We define the capture efficiency  $E_j$  of design  $D_j$  as follows:

$$E_{j} = \frac{\sum_{k=1}^{K} C_{inlet} - c_{k}}{K} * \frac{100}{C_{inlet}}$$

(3.3)

Inlet pressure  $(P_j)$  is reported in units of Pascals (Pa). In our simulations, we set the linear fluid flow rate at the inlet to 1 mm/s and sample the pressure at the central mesh point at the inlet. A flow rate of 1 mm/s was chosen because it is representative of the flow rates commonly encountered in microfluidic chips. Additionally, this flow rate will result in laminar (not turbulent) flow inside the chip. This can be verified by estimating the Reynolds number Re for our capture chip using the formula

$$Re = \frac{u\rho L}{\mu} \tag{3.4}$$

where u is the fluid flow speed (0.001 m/s),  $\rho$  is the density of the fluid (1000 kg/m<sup>3</sup> for water), L is the diameter of the microfluidic channel (0.001 m), and  $\mu$  is the dynamic

viscosity of the fluid (0.001 kg/(m·s) [22]. The result, Re = 1, is much less than 2300; this confirms that the flow inside our capture chip will be laminar, as is usually the case in microfluidics.

Just as the electrical resistance of a resistor determines the voltage drop, the fluidic resistance of the capture chip determines the pressure drop. A capture chip design with a high(low) inlet pressure  $P_j$  therefore has high(low) resistance to fluid flow.

In multi-objective optimization, it is rare to find one design point that is optimal among all objectives. Chip design  $(E_j, P_j)$  dominates solution  $(E_k, P_k)$  if

$$(E_j > E_k \land P_j \le P_k) \lor (E_j \ge E_k \land P_j < P_k). \tag{3.5}$$

The Pareto Front of the search contains all chip designs enumerated by a run of NSGA-II that are not dominated by at least one other design. The user can then select any chip design from the Pareto Front based on her relative prioritization among the two objectives. This is not the Pareto Front for all possible capture chip designs, as the design space is too large to exhaustively enumerate.

## Chapter 4

# **Experiment Design and Setup**

We implemented our microfluidic capture chip design framework (Figure 3.1) using the COMSOL Multiphysics 5.5 and an open-source Java-based library that includes NSGA-II [1]. For each chip design enumerated by NSGA-II, we translated the design into COMSOL Multiphysics using its API to define shapes for the chip designs. We then simulated each chip design to obtain results for target capture and extracted the simulation result  $(E_j, P_j)$ , which we then returned to NSGA-II for evaluation; NSGA-II determined if the new design dominated any designs in the current Pareto front, and updated the Pareto front accordingly.

Table 4.1 summarizes the chip geometry, COMSOL, and NSGA-II parameters that we used in our simulations. Our first set of experiments looked at the impact of various parameter settings on chip designs using circular posts. Our second set of experiments compared chip designs featuring circular to the non-circular post alternatives, using a slightly different combination of parameters.

Table 4.1: Defined parameters for COMSOL and NGSA-II.

| Chip Geometry Parameters            |                                |  |  |

|-------------------------------------|--------------------------------|--|--|

| Channel Width                       | 1 mm                           |  |  |

| Channel Length                      | 10 mm                          |  |  |

| Post Quantity $(N)$                 | $\{31, 100, 0 \le N \le 100\}$ |  |  |

| COMSOL Settings                     |                                |  |  |

| Inlet Fluid Flow Rate               | $0.001 \; \text{m/s}$          |  |  |

| Inflow Concentration                | $1 \text{ mol/m}^3$            |  |  |

| Mesh Element Size                   | "Fine"                         |  |  |

| Fluid Setting                       | "Water"                        |  |  |

| NSGA-II Parameters (circular Posts) |                                |  |  |

| Population Size $(S)$               | {25, 50, 100}                  |  |  |

| Number of Generations $(G)$         | $\{40, 50, 80\}$               |  |  |

| Number of                           | 2N: Fixed number of posts      |  |  |

| NSGA-II Variables (M)               | 3N: Variable number of posts   |  |  |

| Mutation Rates                      | Uniform mutation: $3/M$        |  |  |

|                                     | Uniform crossover: $3/M$       |  |  |

| NSGA-II Parameter                   | rs (Non-circular Posts)        |  |  |

| Population Size $(S)$               | {50}                           |  |  |

| Number of Generations $(G)$         | {40,80}                        |  |  |

| Number of                           |                                |  |  |

| NSGA-II Variables (M)               | 4N: Variable number of posts   |  |  |

| Mutation Rates                      | Uniform mutation: $3/M$        |  |  |

|                                     | Uniform crossover: $3/M$       |  |  |

Table 4.2 summarizes the post geometries and parameters relating to rotation. Each pinwheel-shaped post consists of a small circle with four rectangular protrusions at 90° angles from one another. Square and triangular posts are rotated from their lower-left coordinate, while pinwheels are rotated from their center. Square and pinwheel posts rotate from 0-90° while triangular posts rotate from 0-360°.

All simulations were performed using an Intel Core i5-6600K CPU running at 3.50 GHz, with 32.0 GB RAM and running Windows 10 Education, OS Build 19042.985. We generated chip designs using exactly 31 posts, exactly 100 posts, and a variable number

of posts ranging from 0-100. All chip geometry parameters, except for the number and position of posts, were kept constant. COMSOL failed to simulate approximately 5% of the chip designs that we generated and yielded an error. When this occurred, we eschewed simulation and assigned a low fitness value. The computational overhead of dealing with these failures did not significantly impact the overall runtime.

Table 4.2: Settings for post shapes for designs with variable post quantity. M is defined as the number of NSGA-II variables while N is defined as the post quantity.

| Shape       | Dimensions                              | Rotation    | Rotation |

|-------------|-----------------------------------------|-------------|----------|

|             |                                         | Position    |          |

| Circle      | 0.1 mm radius                           | _           | _        |

| Square      | 0.2 mm length                           | Bottom-Left | 0 - 90°  |

| Equilateral | 0.2 mm sides                            | Bottom-Left | 0 - 360° |

| Triangle    |                                         |             |          |

| Pinwheel:   |                                         | Center      | 0 - 90°  |

| - Circle    | 0.05 mm radius                          |             |          |

| - Rectangle | $0.2 \text{ mm} \times 0.05 \text{ mm}$ |             |          |

## 4.1 NSGA-II Variable Encoding

Recall that each post is encoded as a tuple  $\alpha_i = (x_i, y_i, \theta_i, b_i)$ . We use RealVariables to represent real numbers for the  $(x_i, y_i)$  position of each post and the rotation  $\theta_i$  for non-circular posts. The  $b_i$  flags are also encoded as RealVariables to meet uniformity constraints imposed by the NSGA-II implementation (i.e., it does not allow us to specify a tuple comprised of three RealVariables and a Boolean). We encoded  $b_i$  to be a RealVariable in the range [0,1] and interpreted its value as 1 if  $b_i \geq 0.5$  and 0 otherwise.

### 4.2 COMSOL Implementation Details

Our chosen performance metrics, capture efficiency and inlet pressure, cannot be computed analytically for typical chip designs, so we estimate their values via simulation. To simulate a capture chip proposed by NSGA-II, COMSOL Multiphysics first constructs the chip geometry from rectangular and circular shapes and the generates a mesh for simulation. The Laminar Flow and Transport of a Diluted Species modules were used to establish the inlet flow rate and inflow target concentration of each chip design. All channel walls and post boundaries were marked as locations for fast irreversible surface reactions (surfaces where target molecules can be captured from the fluid). The API was also used to set other simulation parameters, including the physical properties of the fluid (water) and the granularity of the mesh used in finite-element analysis (finer mesh sizes tend to increase the accuracy of the simulation at the cost of longer simulation times). Finally, the API was used to execute the simulation and return the results to NSGA-II.

### 4.3 Human-Generated Designs

The first two human-generated chips are 31-post designs, named "Dense" and "Sparse" respectively. The "Dense" design packs the 31 posts into a small area; this a common design choice that aims for high capture efficiency at the cost of high resistance to fluid flow. The "Sparse" design spreads the posts out; this reduces the fluid flow resistance but also reduces the capture efficiency of the design. Finally, the third human-generated chip extends the "Dense" post spacing to fill the entire channel (101 posts); this design represents an attempt at manually maximizing the capture efficiency.

## Chapter 5

### Results

This chapter evaluates our capture chip design framework. The results demonstrate that our system can discover many non-obvious chip designs with a variety of trade-offs between capture efficiency and flow resistance, and that, for the most parts, circular posts perform better than the other three geometries that we considered.

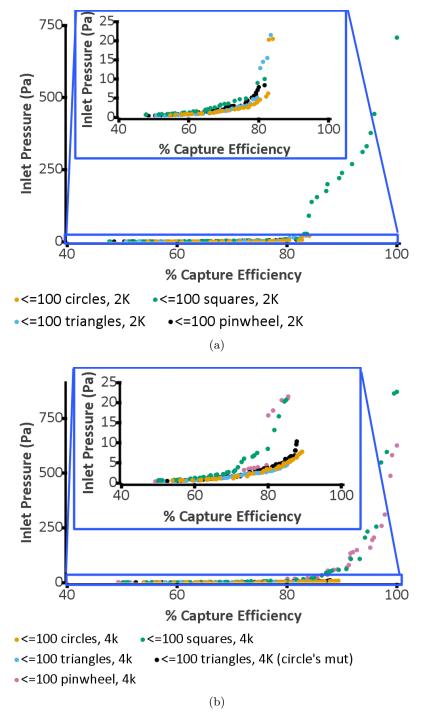

#### 5.1 Generating capture chips with constant numbers of posts

We first algorithmically generated capture chip designs with a constant number of posts (31 posts each) to mirror the number used in the human-generated design and explored different values of S (the population size) and G (the number of generations). The results shown in Figure 5.1 compare the capture chip designs generated using three NSGA-II configurations: 1) 1000 chip designs (S = 25, G = 40); 2) 2000 chip designs (S = 25, G = 80); and 3) 5000 chip designs (S = 100, G = 50). For each configuration, Figure 5.1 only reports the chip designs that were Pareto optimal with respect to those that were

Figure 5.1: Inlet pressure vs. capture efficiency for experiment runs with a constant number of posts (31) and different population sizes (S) and generation counts (G). The different experiments yielded similar results for designs that prioritize low flow resistance (lower-left corner). However, for designs that prioritize capture efficiency, the experiments with the largest total number of analyzed chips yielded the best designs (right side).

enumerated. For chip designs that prioritize minimizing flow resistance (inlet pressure) at the expense of decreased capture efficiency, all three experiments yielded comparable-quality designs (represented by the points in the lower-left region of Figure 5.1). However, for designs that prioritize maximizing capture efficiency at the expense of increased flow resistance, the different experiments yielded different results. Specifically, the experiment with the largest number of designs (S = 100 and G = 50) yielded chip designs with the same high capture efficiency as the other experiments, but with dramatically lower flow resistance. Between the 1000 chip designs and 2000 chip designs, the improvement is small for double the number of generations. This demonstrates that as the number of chips

simulated increases (via increasing the population size and/or the number of generations), the quality of chip designs on the Pareto Front tends to improve, especially at higher capture efficiencies.

Figure 5.2: Inlet pressure vs. capture efficiency for each capture chip design created during the experiment with 31 posts, population size S=100, and generation count G=50, along with the result from the human-designed "Sparse" chip design shown in Figure 5.3. Non-Pareto chip design results with inlet pressures higher than 9 Pa are not shown. While the human-designed chip has a slightly higher capture efficiency than our computer-designed chips, it suffers from significantly higher flow resistance.

Figure 5.2 plots the entire Pareto Front for the 5000 chip design run (S = 100, G = 50; green points) along with all the non-Pareto-optimal designs with inlet pressures lower than 9 Pa (green points). Also plotted is the result from the human-generated "Sparse" design with the same number of posts (black point in Figure 5.2). The results show that while the human-generated design has a slightly higher capture efficiency than the computer-

Figure 5.3

For each design, two simulation results are shown. On the left is the predicted concentration of capture target at each location of fluid in the chip during operation. All chips receive the same high concentration of target (red; 1 mol/m<sup>3</sup>) flowing in from the (blue; 0 mol/m<sup>3</sup>). On the right is the predicted pressure at each location of fluid in the chip during operation. All chips have atmospheric pressure (0 Pa) at the outlet on the right. Designs with high resistance to fluid flow develop high pressures Figure 5.3: (Continued from previous page) Capture chip designs and simulation results for the designs with the highest capture efficiency from each of the three 31-post experiments, along with results from the human-generated "Dense" and "Sparse" chips. left. As target is captured on the capture posts and channel walls, the concentration of target in the solution drops (indicated by a shift to orange, yellow, green, and blue). A chip with 100% capture efficiency would have no remaining target at the outlet (red colors) at the inlet on the left, and designs with low resistance to fluid flow develop low pressures (blue colors) at the inlet on the left. These results show that our computer-generated designs have comparable capture efficiencies to human-generated designs, but with dramatically lower resistance to fluid flow. This gives our computer-generated designs an advantage in many applications. generated designs, the human-generated design has a dramatically higher flow resistance. Based on these results, if a researcher is willing to accept a modest (3 percentage point) reduction in capture efficiency, they can reduce their resistance to fluid flow by 73% by switching from the human-generated design to one of the Pareto-optimal designs generated by our framework. The actual chip designs and COMSOL simulation results for the designs with the highest capture efficiency from each of the three experiments (along with results from the human-created "Dense" and "Sparse" designs) are shown in Figure 5.3.

#### 5.2 Generating capture chips with larger numbers of posts

Examination of the 31-post experiments in Figures 5.1–5.3 reveals that neither the computer-generated nor the human-generated designs had 100% capture efficiency. We hypothesized that the number of posts used in these experiments was too small for 100% capture efficiency, and more posts would be necessary for complete capture. To test this hypothesis, we performed an experiment using 100 posts (a  $3\times$  increase in the post count) with NSGA-II parameters S=50 and G=40 for a total of 2000 different designs.

The results from our 100-post experiment are shown in Figure 5.4. At first glance, these results look encouraging: the computer-generated results include designs on the Pareto-optimal front with 95% capture efficiency, which is higher than the 31-post designs. However, closer examination of Figure 5.4 shows that the flow resistance of the 100-post chips (up to 250 Pa) is dramatically higher than the 31-post chips (only up to 10 Pa, see Figure 5.2). And while the human-generated 101-post design does have near-100% capture efficiency, it also has around 5× higher flow resistance than the human-generated 31-post

Figure 5.4: Inlet pressure vs. capture efficiency for each capture chip design created during the experiment with 100 posts, population size S=50, and generation count G=40, along with the result from the human-designed 101-post chip shown in Figure 5.7. Non-Pareto chip design results with inlet pressures higher than 250 Pa are not shown. The results show that most of these 100-post designs have *extremely* high resistance to fluid flow (100x higher than the 31-post designs shown in Figures 5.1–5.3); this renders these designs unsuitable for many applications and suggests that an optimal post count for this device size lies between 31 and 100.

design described earlier. So while 100-post designs may be suitable for some applications that prioritize capture efficiency, their extremely high flow resistance makes them unsuitable for many other applications.

### 5.3 Generating capture chips with variable numbers of posts

The preceding experiments with 31- and 100-post capture chips show that the number of posts has a significant impact on capture chip performance: with too few posts

the flow resistance is favorable but the capture efficiency decreases, and with too many posts the capture efficiency improves but the flow resistance suffers. Consequently, in subsequent experiments we decided to allow the algorithm to choose the number of posts up to a user-specified maximum.

Figure 5.5: Inlet pressure vs. capture efficiency for capture chip designs created using a variable number of posts (up to 100), with population size S=50 and generation count G=80. The axes are identical to Figure 5.4 for side-to-side comparison and 0-20 Pa data magnified for better visualization. Comparing this result to the constant 100-post results shows that allowing variable numbers of posts dramatically decreases the flow resistance of the resulting designs, with only a minimal decrease in maximum observed capture efficiency.

In these experiments, the maximum number of posts was defined as 100 to align with the previous 100-post experiment, and tests were conducted with population size S = 50, and generation count G = 40 (2000 chips total) or G = 80 (4000 chips total). The plot of inlet pressure vs. capture efficiency for the G = 80 run is shown in Figure 5.5.

Comparing these results with the previous 100-post results in Figure 5.4, we see that the designs with variable numbers of posts have comparable capture efficiencies but dramatically lower resistance to fluid flow. This combination is advantageous in most applications.

To understand why the variable-post designs had such low resistance to fluid flow, we examined the number of posts chosen by the algorithm in each of these designs. For all 4000 designs considered by the algorithm, the number of posts per design ranged from 29 to 65, with an average of 49 posts (Figure 5.5b). The results for the 47 Pareto-optimal designs were similar, ranging from 31 to 62 posts with an average of 48 posts (Figure 5.6c). With around half as many posts as the 100-post designs, the variable-post designs have lower resistance to fluid flow while still providing high capture efficiency.

Figure 5.5

Figure 5.6: Distribution of capture post counts in the designs from the variable-post-count experiment in Figure 5.5: (a) the initial generation with random numbers of posts per chip (50 chip designs), (b) all 4000 chip designs generated in the experiment, and (c) only the 47 Pareto-optimal chip designs from the experiment. The shapes of distributions (b) and (c) suggest that certain ranges of post counts per device are favored in optimal capture chip designs.

The shape of the post-count distribution in our variable-post results also offers interesting insights into the algorithm's search for optimal designs. Since each device in the first generation has up to 100 posts but each post has a 50% probability of being present, the first generation has a normal (or Gaussian) distribution of post counts centered around 50 posts, as shown in Figure 5.6a). If the algorithm's design search was unguided, this symmetric distribution centered on 50 posts might be expected to endure in subsequent generations. However, that is not the case: Figure 5.5b shows that among all 4000 chip designs examined by the algorithm, the distribution of posts per design is asymmetric, with 59 being the most common number of posts. The extremes of the post count distribution are also different: on the high end, a sudden drop around 63 posts per design means that very few chips with more than 63 posts were considered by the algorithm; and on the low end, a longer and more gradual decline to 30 posts indicates the minimum number of posts considered by the algorithm. The distribution of Pareto-optimal post counts in Figure 5.6c shows that most optimal chip designs had either relatively large numbers of posts (54 to 62 posts per chip) or relatively small numbers of posts (31 to 40 posts per chip), and surprisingly few optimal designs had intermediate numbers of posts per chip. This almostbimodal distribution of posts per chip in the Pareto-optimal designs could indicate that two different types of designs have emerged that are both optimal but use different numbers of posts, an idea we intend to explore in future work.

Figure 5.7 shows actual chip designs from the variable-post-count experiments. The design with the highest capture efficiency was obtained using a population size S = 50 and generation count G = 80; it has a capture efficiency of 89.3%, which is only 10 percent-

designs have comparable capture efficiency to the human-generated designs, but with six times lower flow resistance and almost Figure 5.7: Capture chip designs and simulation results for the designs with the highest capture efficiency from each of the experiments with variable numbers of posts, along with results from the human-generated design with 101 posts. Capture efficiency (left) and inlet pressure (right) are as described in Figure 5.3. These results show that our best computer-generated half the number of posts.

age points lower than the human-generated design that uses nearly twice as many posts. Additionally, the human-generated design has over six times the inlet pressure of our computergenerated design. This combination of very high capture efficiency with very low flow resistance means that our computer-generated designs can outperform human-generated designs in many applications.

#### 5.4 Generating capture chips with different shaped posts

The previous experiments exclusively considered microfluidic capture chips with circular post geometries; the set of experiments reported here serves to confirm the choice of circular posts compared to posts having square, triangular, and pinwheel-shaped geometries. It is worth noting that circular, square, and triangular posts are convex, while pinwheel-shaped posts feature multiple cavities. All experiments reported here were performed using a variable number of 0-100 posts, as this setting performed better than fixing the number of posts in our previous experiments. We performed two different runs: one where we generated 2000 chip designs (S = 50, G = 40) and another where we generated 4000 chip designs (S = 50, G = 80).