# UC Irvine UC Irvine Electronic Theses and Dissertations

## Title

Innovative Solid-State Bonding Designs and Techniques for High Power Electronic and Laser Diode Packaging

Permalink https://escholarship.org/uc/item/3rh3r09z

Author Chen, Yi-Ling

**Publication Date** 2016

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, IRVINE

Innovative Solid-State Bonding Designs and Techniques for High Power Electronic and Laser Diode Packaging

DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

in Engineering

by

Yi-Ling Chen

Dissertation Committee: Professor Chin C. Lee, Chair Professor James C. Earthman Professor Frank G. Shi

2016

Chapter 4 © IEEE Chapter 5 © 2015 Springer All other materials © 2016 Yi-Ling Chen

## **DEDICATION**

То

my dear family

For supporting, understanding, and encouraging me to believe in myself, all of you help me make it possible to complete this dissertation.

# TABLE OF CONTENTS

| List of Figure  | S                                                    | vi   |

|-----------------|------------------------------------------------------|------|

| List of Tables  |                                                      | xi   |

| Acknowledge     | ment                                                 | xii  |

| Curriculum V    | itae                                                 | xiii |

| Publications    |                                                      | xiv  |

| Abstract of the | e Dissertation                                       | xvi  |

| Chapter 1       | Introduction                                         | 1    |

| 1.1             | Electronic Packaging                                 | 1    |

| 1.2             | The Die Attach Materials                             | 3    |

| 1.3             | Challenges for High Temperature Die Attach Materials | 6    |

| 1.4             | Techniques for High Temperature Die Attach Materials | 8    |

| 1.5             | Dissertation Outline                                 | 10   |

| 1.6             | References                                           | 13   |

| Chapter 2       | Review of Solid-State Bonding Principle              | 18   |

| 2.1             | Introduction                                         | 18   |

| 2.2             | Parameters in solid-state bonding                    | 19   |

| 2.3             | The Quantum Theory of Solid-state Atomic Bonding     | 21   |

| 2.4             | References                                           | 23   |

| Chapter 3       | Experimental Setup and Techniques                    | 25   |

| 3.1             | Material Fabrication                                 | 25   |

|                 | 3.1.1 Wafer Cleaning Procedures                      | 26   |

|                 | 3.1.2 Electron Beam Evaporation                      | 27   |

|                 | 3.1.3 Electroplating                                 | 29   |

|                 | 3.1.4 Photolithography                               | 30   |

|                 | 3.1.5 Etching                                        | 32   |

| 3.2       | Vacuum Furnace and Bonding Setup                                 | 34 |

|-----------|------------------------------------------------------------------|----|

| 3.3       | Characterization Techniques                                      | 37 |

|           | 3.3.1 X-Ray Diffraction (XRD)                                    | 37 |

|           | 3.3.2 Scanning Electron Microscope (SEM)/Energy Dispersive       |    |

|           | X-ray Spectroscopy (EDX)                                         | 40 |

|           | 3.3.3 Dektak 3 Surface Profilometer                              | 43 |

| 3.4       | References                                                       | 44 |

| Chapter 4 | Strength of solid-state silver bonding between copper Structures | 46 |

| 4.1       | Introduction                                                     | 46 |

| 4.2       | Experimental design and procedures                               | 47 |

| 4.3       | Experimental results and discussion                              | 48 |

| 4.4       | Summary                                                          | 55 |

| 4.5       | References                                                       | 55 |

| Chapter 5 | Silver-Assisted Copper Wire Bonding Using Solid-State            |    |

|           | Processes                                                        | 57 |

| 5.1       | Introduction                                                     | 57 |

| 5.2       | Experimental Design and Procedure                                | 59 |

| 5.3       | Experimental Results and Discussion                              | 63 |

| 5.4       | Summary and Outlook                                              | 77 |

| 5.5       | References                                                       | 78 |

| Chapter 6 | Solid-State Bonding of Copper Chips to Copper Substrate Using    |    |

|           | Silver with Cavities                                             | 84 |

| 6.1       | Introduction                                                     | 84 |

| 6.2       | Experimental Design and Procedure                                | 86 |

|           | 6.1.1 Fabrication steps of Ag layer with the annealing step      | 87 |

|           | 6.1.2 Fabrication steps of Ag layer with cavities                | 88 |

| 6.3       | Experimental Results and Discussion                               | 91  |

|-----------|-------------------------------------------------------------------|-----|

|           | 6.3.1 The bonding design of Ag layer with the annealing step      | 91  |

|           | 6.3.2 The bonding design of Ag layer with cavities                | 99  |

| 6.4       | Summary                                                           | 106 |

| 6.5       | References                                                        | 108 |

| Chapter 7 | Solid-State Bonding of Silicon Chips Directly on Copper           |     |

|           | Substrates With Trenches                                          | 113 |

| 7.1       | Introduction                                                      | 113 |

| 7.2       | Experimental Design and Procedure                                 | 114 |

| 7.3       | Experimental Results and Discussion                               | 119 |

| 7.4       | Summary                                                           | 124 |

| 7.5       | References                                                        | 125 |

| Chapter 8 | Design and Fabrication of Silver Solid Solution Layers on Silicon |     |

|           | and Silicon Carbide Chips and Subsequent Solid-State Bonding      |     |

|           | to Cu Substrate                                                   | 127 |

| 8.1       | Introduction-Si Chip                                              | 127 |

| 8.2       | Experimental Design and Procedure-Si Chip                         | 129 |

| 8.3       | Experimental Results and Discussion-Si Chip                       | 132 |

|           | 8.3.1 Phase diagram and intermetallics                            | 132 |

|           | 8.3.2 Structure design I:                                         |     |

|           | Si/Cr/Au/Ag/In/Ag without initial annealing on the bottom Ag      |     |

|           | layer & with following 2-step annealing in air                    | 134 |

|           | 8.3.3 Structure design II:                                        |     |

|           | Si/Cr/Au/Ag/In/Ag without initial annealing on the bottom Ag      |     |

|           | layer & with extension time of following 2-step annealing in      |     |

|           | air                                                               | 136 |

|           |                                                                   |     |

8.3.1 Structure design III:

|         |     | Si/Cr/Au/Ag/In/Ag with initial annealing on the bottom Ag    |     |

|---------|-----|--------------------------------------------------------------|-----|

|         |     | layer & with extension time of following 2-step annealing in |     |

|         |     | vacuum                                                       | 138 |

|         | 8.4 | Conclusions-Si Chip                                          | 140 |

|         | 8.5 | Experimental Design and Procedure-SiC Chip                   | 141 |

|         | 8.6 | Experimental Results and Discussion-SiC Chip                 | 144 |

|         | 8.7 | Conclusions-SiC Chip                                         | 149 |

|         | 8.8 | References                                                   | 151 |

| Chapter | r 9 | Conclusions                                                  | 154 |

|         | 9.1 | Silver Joints and Patterned Silver Joints                    | 154 |

|         | 9.2 | Silver-Assisted Copper Wire Bonding                          | 156 |

|         | 9.3 | Silicon Chips Directly Bond to Pattered Copper Substrate     | 157 |

|         | 9.4 | Silver-Indium Joints                                         | 158 |

# LIST OF FIGURES

|           | -                                                                                                                                                                                                                                                                             | 8- |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 1.1  | Basic electronic package functions                                                                                                                                                                                                                                            | 1  |

| Fig. 1.2  | A simple packaging device                                                                                                                                                                                                                                                     | 3  |

| Fig. 2.1  | A simple solid-state bonding process (a) Two dissimilar metal<br>surfaces are ready for the bonding experiment, (b) The intimate<br>contact is created, and (c) The bond is achieved                                                                                          | 20 |

| Fig. 3.1  | Temescal CHA-600S/CV-8 (UC-Irvine INRF)                                                                                                                                                                                                                                       | 28 |

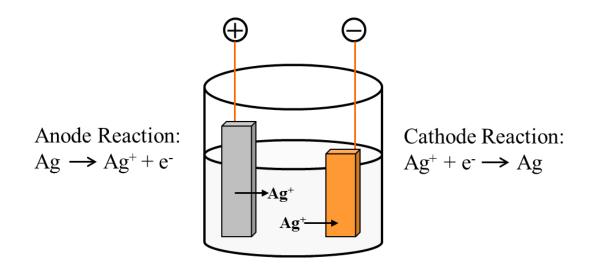

| Fig. 3.2  | Silver electroplating: Anode is a Ag plate. Cathode is a Cu substrate                                                                                                                                                                                                         | 29 |

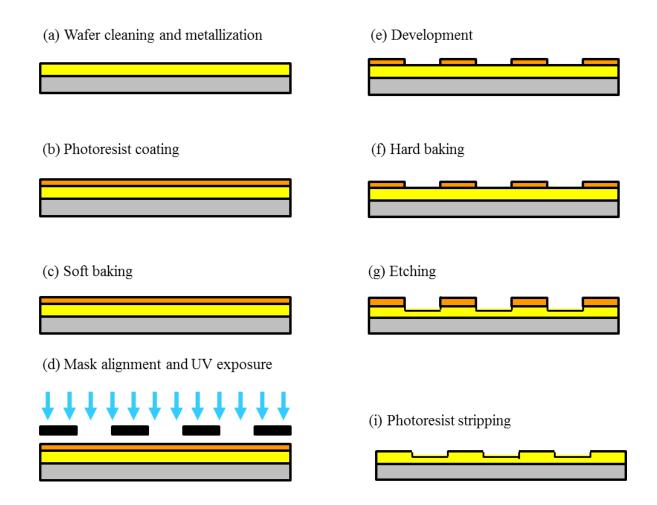

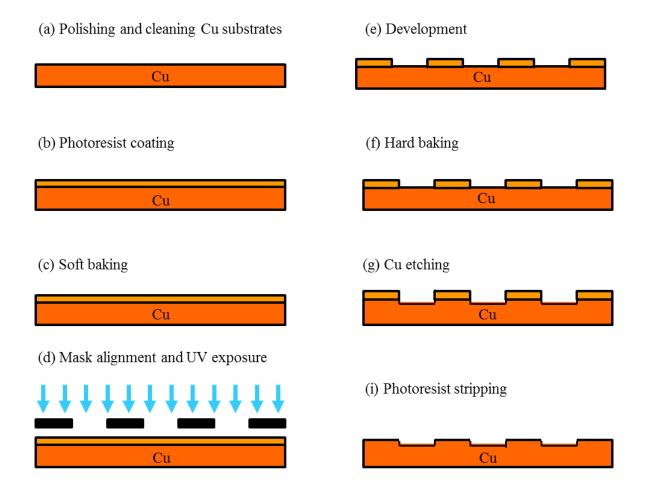

| Fig. 3.3  | An example of a typical sequence of lithographic processing steps<br>(a) Wafer cleaning and metallization, (b) Photoresist coating, (c)<br>Soft baking, (d) Mask alignment and UV exposure, (e)<br>Development, (f)Hard baking, (g) Etching, and (i) Photoresist<br>stripping | 31 |

| Fig. 3.4  | Karl Suss MA6 Mask Aligner (UC-Irvine INRF)                                                                                                                                                                                                                                   | 32 |

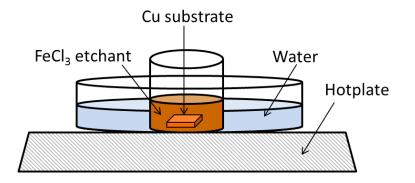

| Fig. 3.5  | Warm up the FeCl3 etchant in the hot water bath                                                                                                                                                                                                                               | 33 |

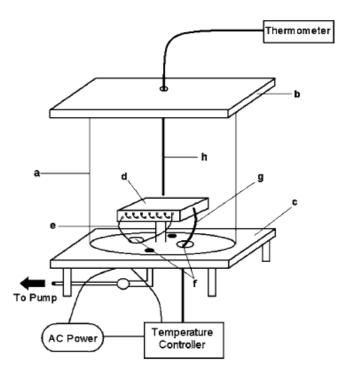

| Fig. 3.6  | Schematic of the vacuum furnace showing key components: (a) quartz cylinder, (b) upper stainless plate, (c) base plate, (d) graphite platform, (e) heating wire, (f) electrical feedthroughs, (g) platform thermocouple, and (h) sample thermocouple                          | 35 |

| Fig. 3.7  | Rigaku SmartLab X-ray Diffractomete (UC-Irvine Calit2)                                                                                                                                                                                                                        | 38 |

| Fig. 3.8  | Philips XL-30 FEG SEM with EDX system (UC-Irvine LEXI)                                                                                                                                                                                                                        | 40 |

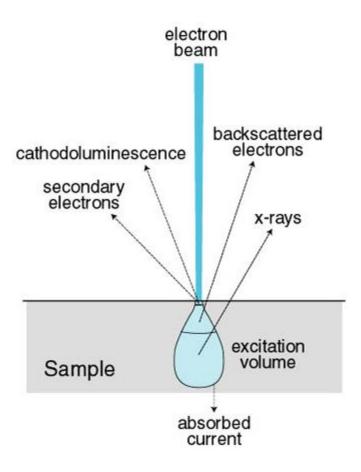

| Fig. 3.9  | The interaction volume and the signals produced by the interaction<br>between the electron beam and specimen (Electron Microscope<br>Laboratory, Northern Arizona University)                                                                                                 | 41 |

| Fig. 3.10 | Dektak 3 Surface Profilometer (UC-Irvine INRF)                                                                                                                                                                                                                                | 43 |

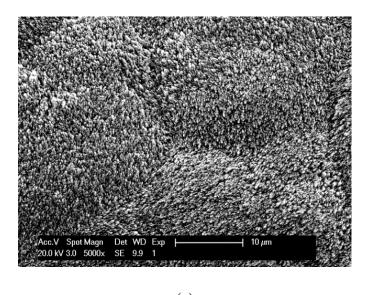

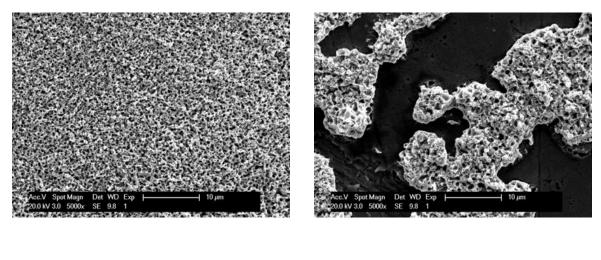

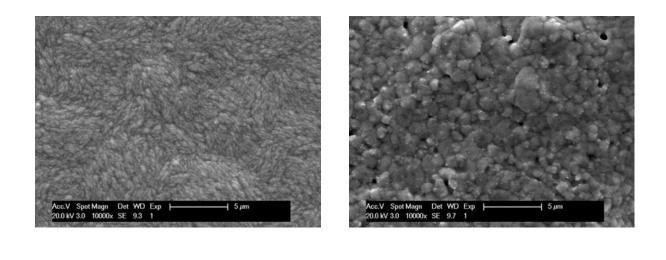

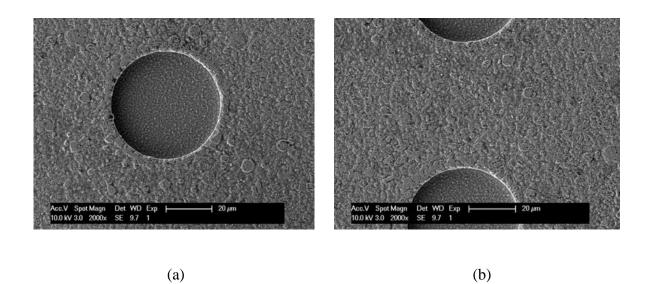

| Fig. 4.1  | SEM images of Ag surface morphologies on Cu substrates (a) non-<br>annealed Ag microstructures and (b) annealed Ag microstructures<br>at 400 °C for 5 h                                                                                                                       | 49 |

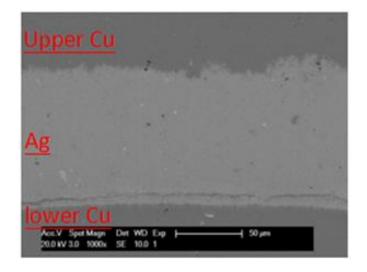

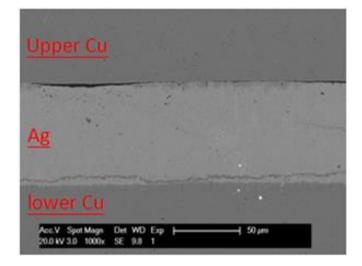

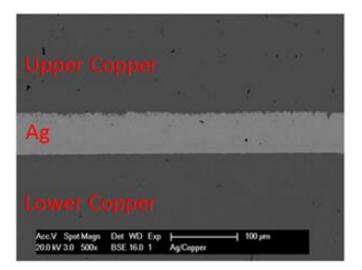

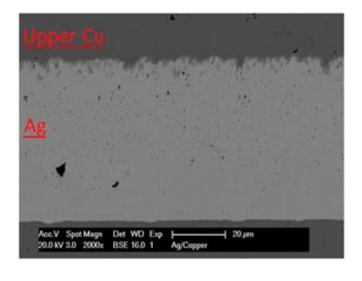

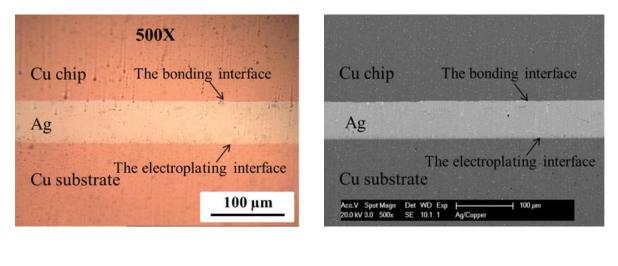

| Fig. 4.2 | Cross-sectional SEM images of the bonded sample at 250 °C with static pressure 1000 psi (a) Cu/Ag/Cu structures and (b) Cu/Ag/Cu structures include gaps and voids                                                                                                                                                                                                                                                                                                                                                               | 50 |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

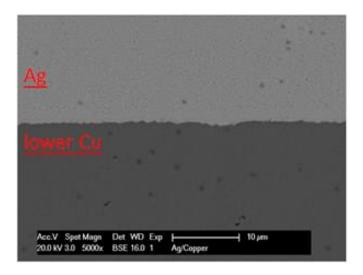

| Fig. 4.3 | Cross-sectional SEM images of the bonded sample at 300 °C with static pressure 1000 psi (a) Ag/Cu structure, (b) Cu/Ag/Cu structure and (c) Cu/Ag structure                                                                                                                                                                                                                                                                                                                                                                      | 53 |

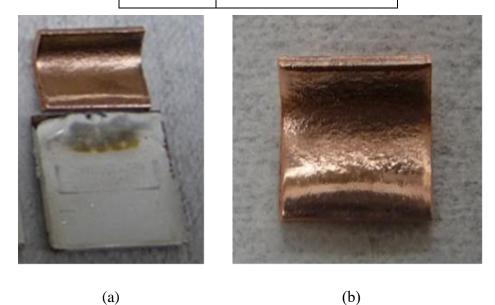

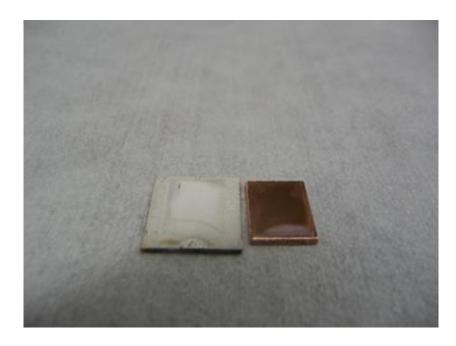

| Fig. 4.4 | The Cu chip and the Cu substrate after the shear test. (a) The Cu ship and the Cu substrate of bonded sample 6 after the shear test and (b) The Cu chip of bonded sample 6 after the shear test. The tool wedge bent the Cu chip and the breaking force is 90.16 kg. It shows the bonding structure is strong                                                                                                                                                                                                                    | 54 |

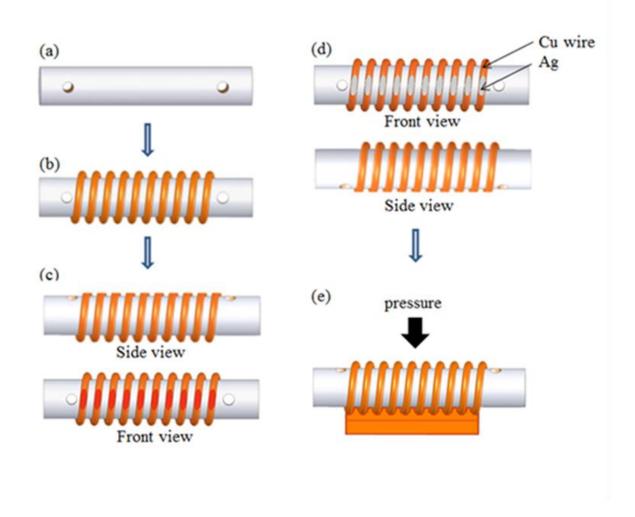

| Fig. 5.1 | Fabrication steps to bond flat surfaces of a Cu coil on a Si chip or Cu substrate using solid-state bonding process: (a) 12.7 mm (0.5 inch) diameter MACRO core with groove, (b) winding 1 mm Cu wire on the groove and coating the assembly with lacquer, (c) machining the coil to produce flat surfaces on the wire, (d) electroplating 50 $\mu$ m Ag on the flat surfaces of Cu wire, removing lacquer, and annealing at 350 °C for 5 h, (e) solid-state bonding at 300 °C with 6.89 MPa in 1.33 × 10-5 MPa vacuum for 3 min | 61 |

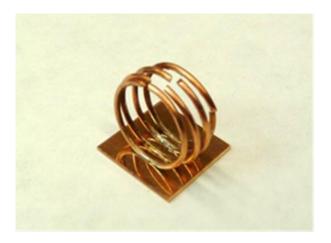

| Fig. 5.2 | The Cu coils bonded on Cu substrate after each turn was cut open<br>and the MACOR winding core was removed                                                                                                                                                                                                                                                                                                                                                                                                                       | 63 |

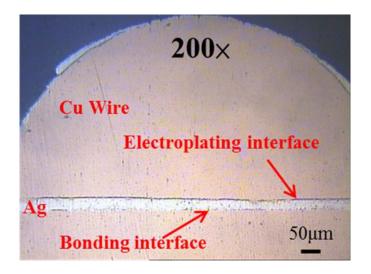

| Fig. 5.3 | Optical microscopy images of an Ag-plated Cu wire annealed at 400 °C for 5 h and then bonded to Cu substrate at 300 °C with 6.89 MPa pressure                                                                                                                                                                                                                                                                                                                                                                                    | 64 |

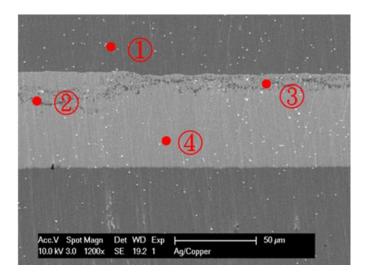

| Fig. 5.4 | The SEM image includes a black band inside the Ag layer and EDX data demonstrate that it is a Cu diffusion band inside the Ag layer                                                                                                                                                                                                                                                                                                                                                                                              | 64 |

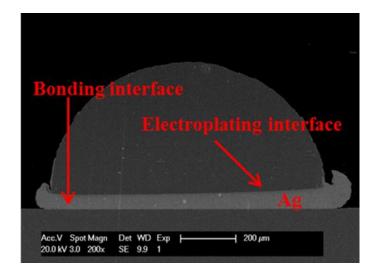

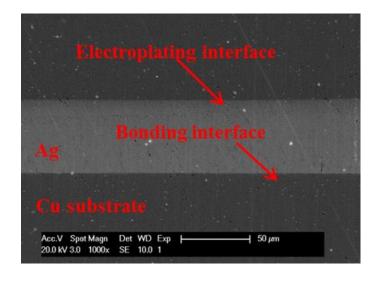

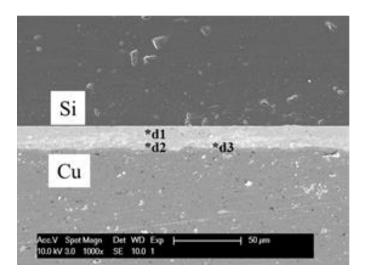

| Fig. 5.5 | Cross-section SEM images of a typical wire bond annealed at 350 °C for 5 h and then bonded at 300 °C with 6.89 MPa pressure: (a) low magnification (200×), (b) high magnification (1000×)                                                                                                                                                                                                                                                                                                                                        | 65 |

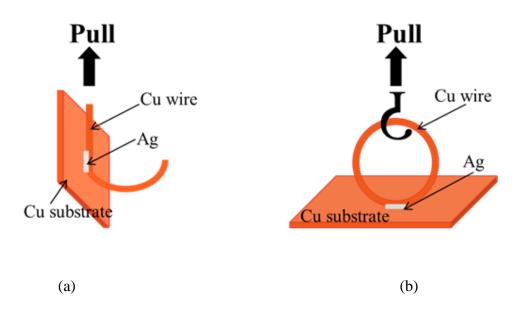

| Fig. 5.6 | Two pull tests: (a) In-plane pull test and (b) Vertical pull test                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67 |

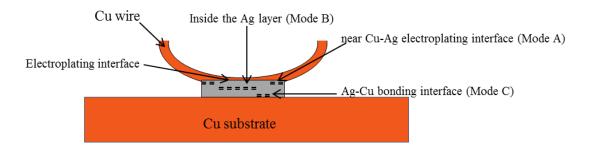

| Fig. 5.7 | A cross-sectional sketch showing three fracture modes: A, B, and C. Mode A is not exactly on the Cu-Ag electroplating interface, but inside Ag and near the interface                                                                                                                                                                                                                                                                                                                                                            | 69 |

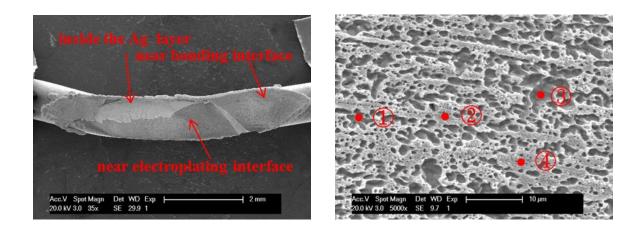

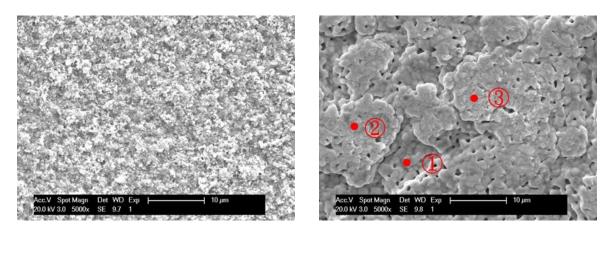

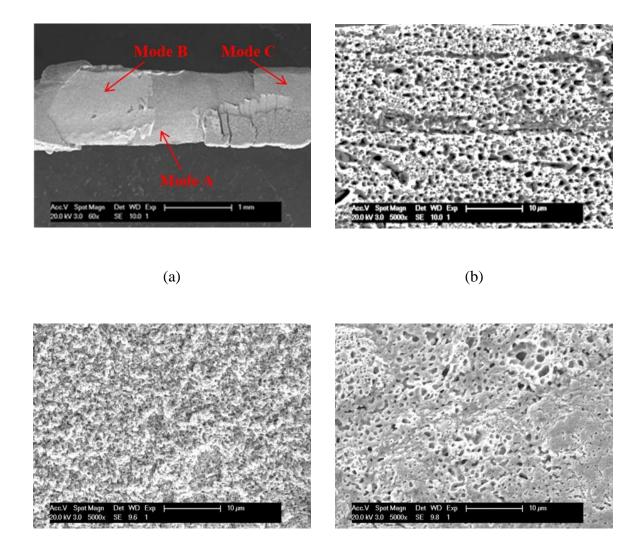

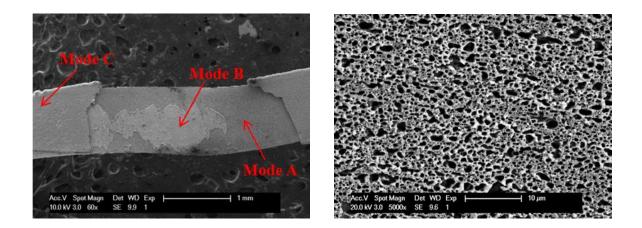

| Fig. 5.8 | Fig. 5.8 SEM images of the bonding region of sample 3 in Table 5.2 after Cu wire being pulled off the Cu substrate: (a) the entire bonding region, (b) mode A: fracture near Cu-Ag electroplating                                                                                                                                                                                                                                                                                                                                |    |

|           | interface, (c) mode B: fracture surface inside Ag layer, and (d) mode C: fracture on Ag-Cu bonding interface                                                                                                                                                                                 | 70 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

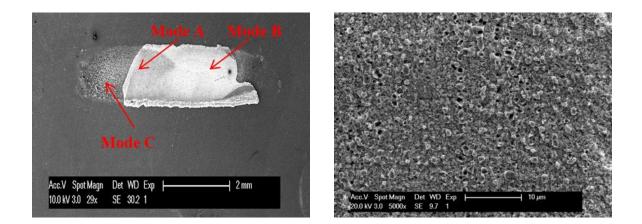

| Fig. 5.9  | SEM images of wire bond residue of sample 3 on Cu substrate<br>after pull test: (a) the entire bonding region, (b) mode A: fracture<br>near Cu-Ag electroplating interface, (c) mode B: fracture surface<br>inside Ag layer, and (d) mode C: fracture on Ag-Cu bonding<br>interface          | 73 |

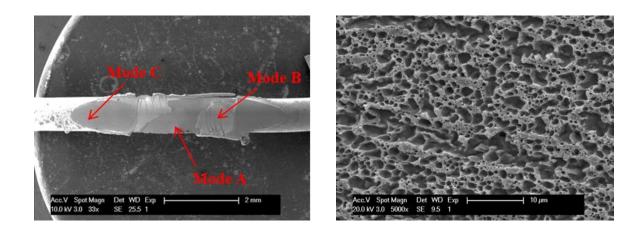

| Fig. 5.10 | SEM image of the Cu wire bond sample 4 which is bonded to Cu substrate after vertical pull test: (a) the entire bonding region, (b) mode A: fracture near Cu-Ag electroplating interface, (c) mode B: fracture surface inside Ag layer, and (d) mode C: fracture on Ag-Cu bonding interface. | 74 |

| Fig. 5.11 | SEM image of the Cu wire bond sample 7 which is bonded to Si chip after in-plane pull test: (a) the entire bonding region, (b) mode A: fracture near Cu-Ag electroplating interface, (c) mode B: fracture surface inside Ag layer, and (d) mode C: fracture on Ag-Si bonding inter           | 75 |

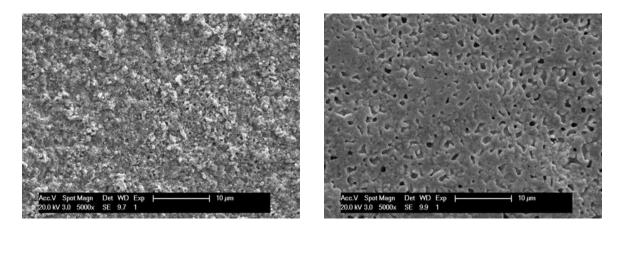

| Fig. 5.12 | SEM image of the Cu wire bond sample 9 which is bonded to Si chip after vertical pull test: (a) the entire bonding region, (b) mode A: fracture near Cu-Ag electroplating interface, (c) mode B: fracture surface inside Ag layer, and (d) mode C: fracture on Ag-Si bonding interface       | 76 |

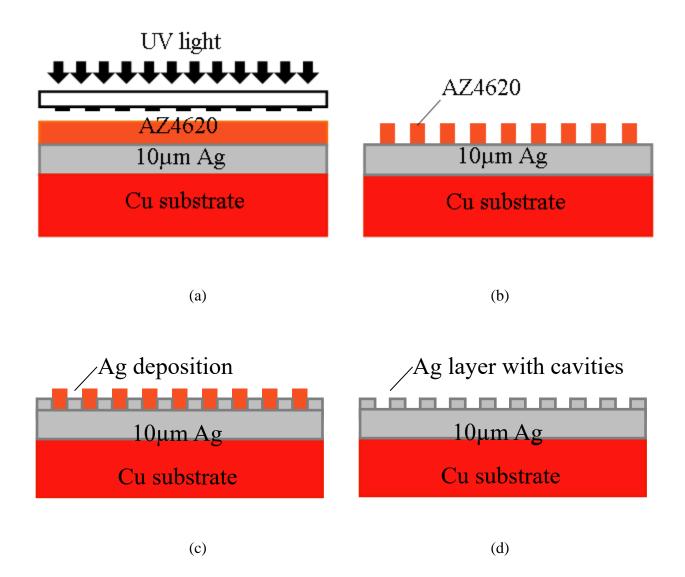

| Fig. 6.1  | Fabrication steps of Ag layer with cavities: (a) Photoresist coating<br>on Cu substrate with Ag layer and UV exposure through a<br>photomask, (b) Photoresist development, (c) Electroplating Ag on<br>the Cu substrate, and (d) Ag layer with cavities after photoresist<br>stripping       | 90 |

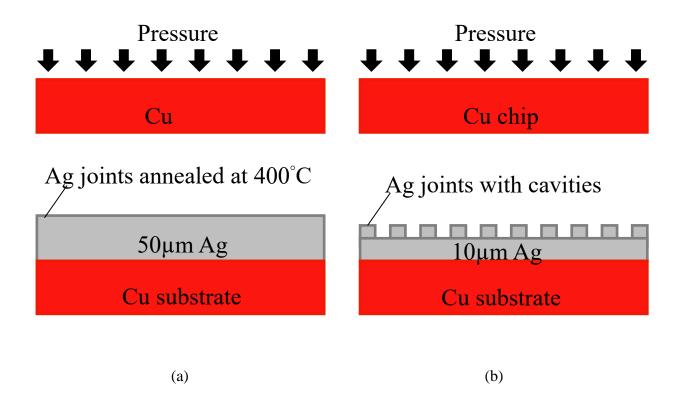

| Fig. 6.2  | The bonding mechanism for two designs: (a) Ag layer with the annealing step, and (b) Ag layer with cavities                                                                                                                                                                                  | 91 |

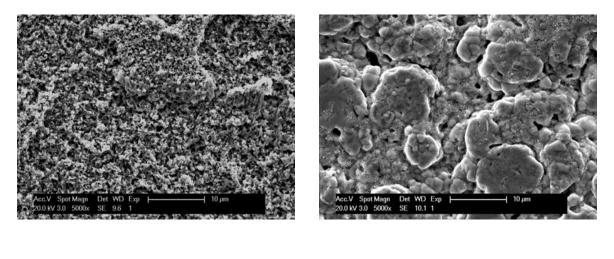

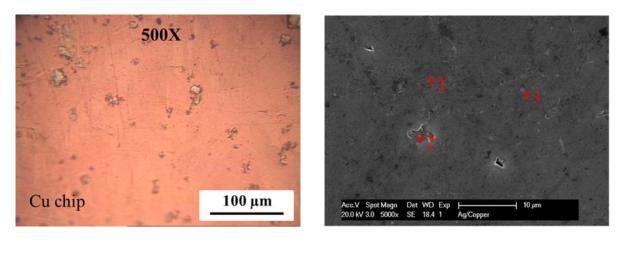

| Fig. 6.3  | SEM images of Ag morphologies on Cu substrates: (a) Ag layer was not annealed, and (b) Ag layer was annealed at 400 °C for 5 h to grow grains                                                                                                                                                | 92 |

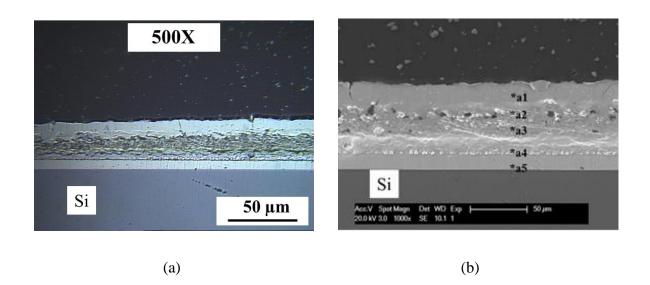

| Fig. 6.4  | Cross-section images of a bonded sample used 50 $\mu$ m Ag joints with annealing step: (a) optical microscopic image, and (b) SEM image                                                                                                                                                      | 93 |

| Fig. 6.5  | The photo of sample #1 after the shear test                                                                                                                                                                                                                                                  | 94 |

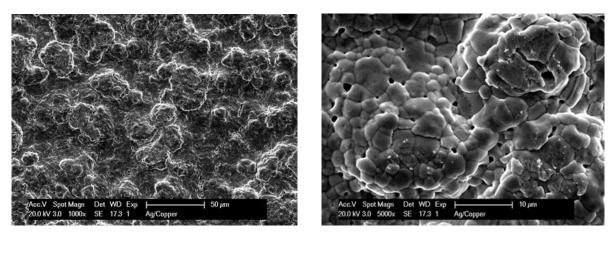

| Fig. 6.6  | SEM images of the Ag layer on Cu substrate of sample #5 after shear test: (a) $1,000 \times$ magnification showing Ag surface being                                                                                                                                                          |    |

|           | flattened on some regions, and (b) $5,000 \times$ magnification zooming<br>in three hill-tops that were clearly flattened during the solid-state<br>bonding process                                                                                                                                                                                                              | 97  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 6.7  | Images of Cu chip that was sheared off sample #5: (a) Optical microscopic image of Cu chip showing Ag traces, and (b) SEM image of Cu chip with Ag traces and EDX analysis locations                                                                                                                                                                                             | 98  |

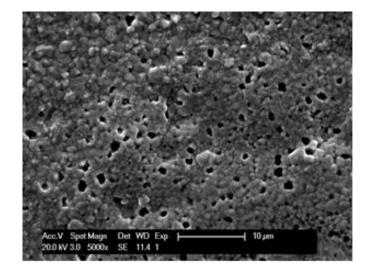

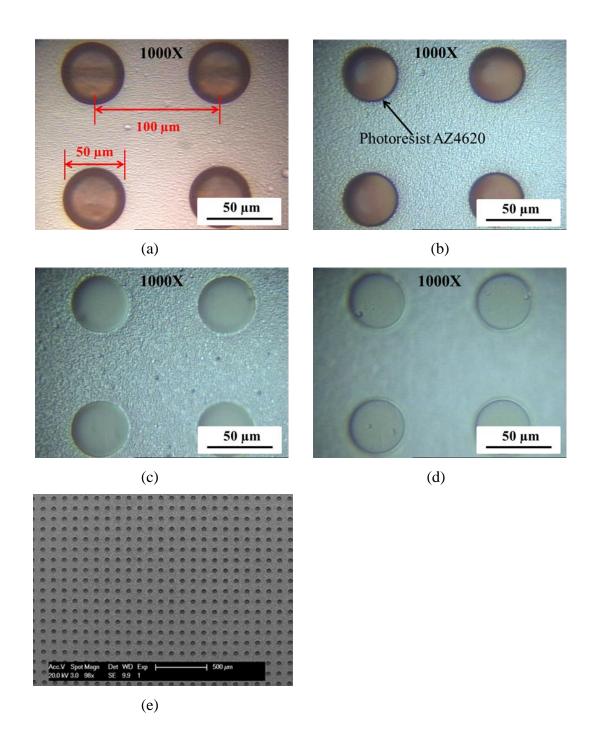

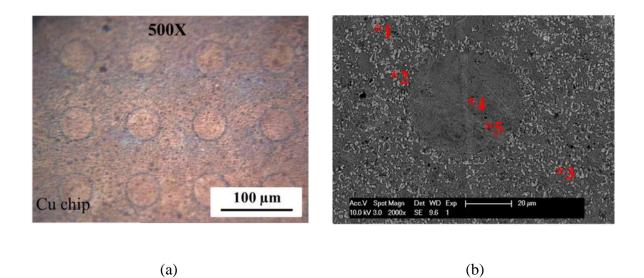

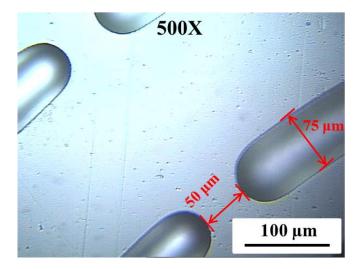

| Fig. 6.8  | Images of fabricating steps: (a) photoresist with columns with 50 $\mu$ m in diameter and 100 $\mu$ m pitch made on 10 $\mu$ m Ag layer on a Cu substrate, (b) after electroplating 5 $\mu$ m thick Ag, (c) after removing photoresist, (d) focusing on the cavity bottoms to ensure that photoresist was removed completely, and (e) Ag layer with an array of 50 × 50 cavities | 101 |

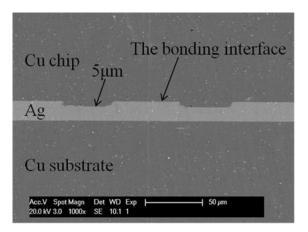

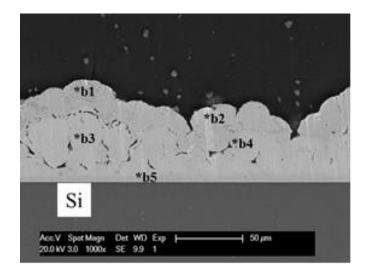

| Fig. 6.9  | Cross-section SEM image of a sample of Cu chip bonded on Ag layer with cavities plated on a Cu substrate                                                                                                                                                                                                                                                                         | 102 |

| Fig. 6.10 | Close-up SEM image of a single cavity                                                                                                                                                                                                                                                                                                                                            | 102 |

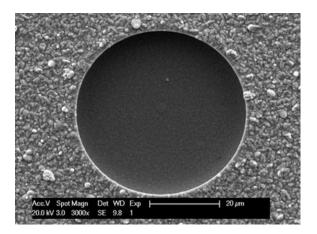

| Fig. 6.11 | SEM images of Ag layer with cavities on Cu substrate that was<br>sheared off sample #8: (a) Ag material near the cavities was<br>flattened, and (b) Ag surface between cavities was flattened                                                                                                                                                                                    | 104 |

| Fig. 6.12 | Images of Cu chip that was sheared off sample #8: (a) The optical microscopic image shows that Ag traces reminded bonded on the Cu chip, and (b) The SEM image shows that Ag traces on the Cu chip with EDX analysis locations                                                                                                                                                   | 106 |

| Fig. 7.1  | The major steps of fabricating the pattern on Cu substrate (a)<br>Polishing and cleaning the Cu substrates, (b) Photoresist coating, (c)<br>Soft baking, (d) Mask alignment and UV exposure, (e)<br>Development, (f) Hard baking, (g) Cu etching, and (i) Photoresist<br>stripping                                                                                               | 116 |

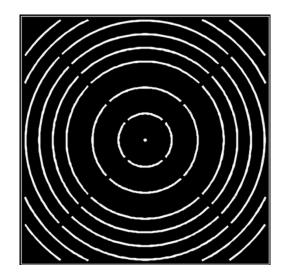

| Fig. 7.2  | The pattern of photomask                                                                                                                                                                                                                                                                                                                                                         | 117 |

| Fig. 7.3  | The optical microscopic image of Cu substrate after the Cu etching process                                                                                                                                                                                                                                                                                                       | 120 |

| Fig. 7.4  | The optical microscopic image of Cu substrate after the Ag electroplating process                                                                                                                                                                                                                                                                                                | 120 |

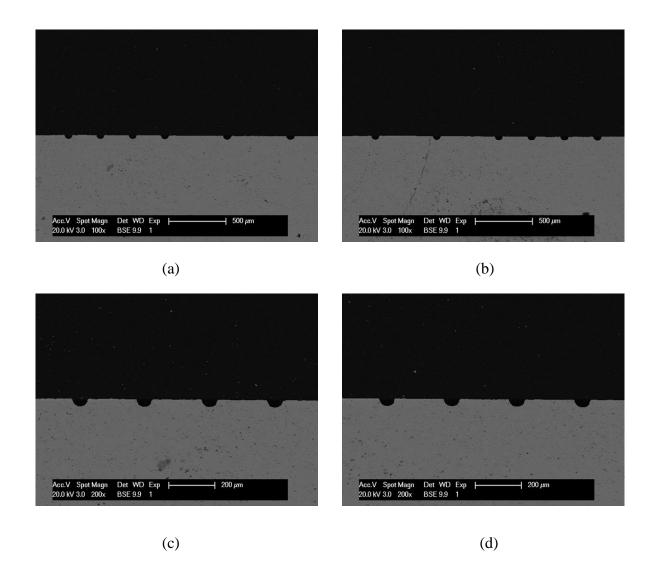

| Fig. 7.5  | The cross-sectional SEM image with trenches before the solid-state<br>bonding process (a) The left side of trenches at $100 \times$ magnification,<br>(b) The right side of trenches at $100 \times$ magnification, (c) The left<br>side of trenches at $200 \times$ magnification, and (d) The right side of<br>trenches at $200 \times$ magnification                          | 121 |

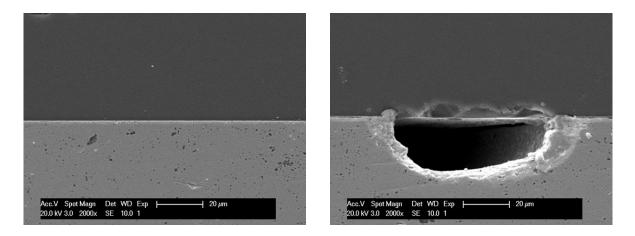

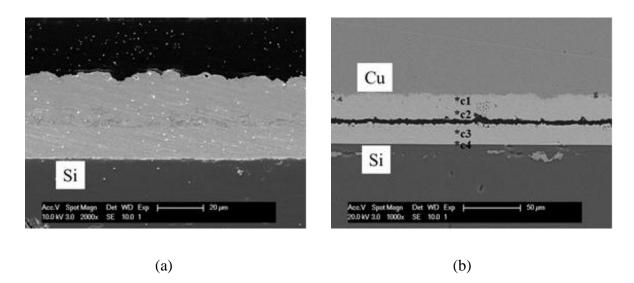

| Fig. 7.6  | The cross-sectional SEM image of a bonded sample (a) A bonded region without trenches at $2000 \times$ magnification (b) A bonded region with a trench at $2000 \times$ magnification | 122 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

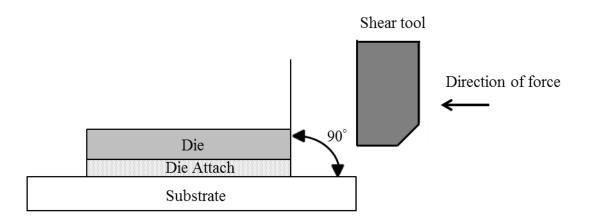

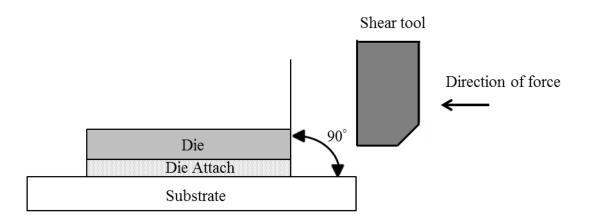

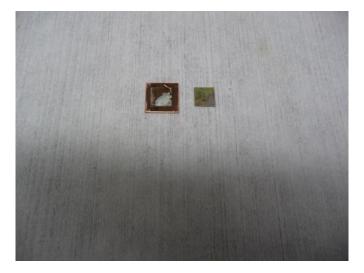

| Fig. 7.7  | Die shear test                                                                                                                                                                        | 124 |

| Fig. 7.8  | The broken Si chip still bonded to the Cu substrate after the simple shear test                                                                                                       | 124 |

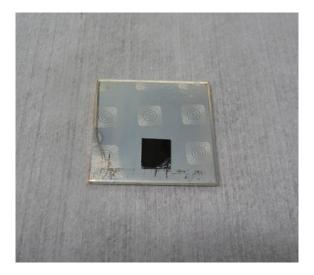

| Fig. 8.1  | Cross-sectional OM image of Ag layer after electroplating 50 min                                                                                                                      | 130 |

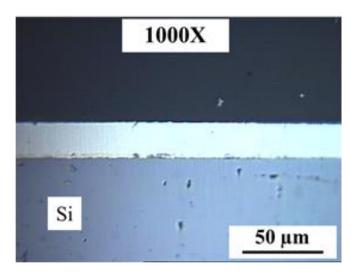

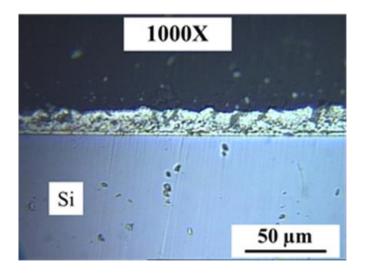

| Fig. 8.2  | Cross-sectional OM image of In layer after electroplating 30 min                                                                                                                      | 130 |

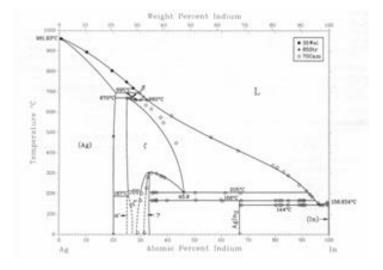

| Fig. 8.3  | Ag-In phase diagram                                                                                                                                                                   | 132 |

| Fig. 8.4  | Cross-sectional images of Ag-In binary system after two weeks at room temperature (a) OM image (b) SEM image                                                                          | 133 |

| Fig. 8.5  | For design I, cross-sectional SEM image of Ag-In binary system when the annealing process is completed                                                                                | 135 |

| Fig. 8.6  | For design II, cross-sectional SEM image of Ag-In binary system<br>(a) before the solid-state bonding process (b) after the solid-state<br>bonding process                            | 137 |

| Fig. 8.7  | For design III, cross-sectional SEM image of Ag-In binary system, before the solid-state bonding process                                                                              | 139 |

| Fig. 8.8  | For design III, cross-sectional SEM image of Ag-In binary system, after the solid-state bonding process                                                                               | 139 |

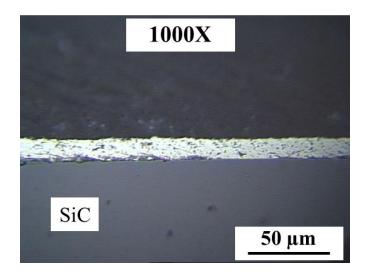

| Fig. 8.9  | The cross-sectional OM image of Ag-In binary system, after the 2-<br>step annealing process                                                                                           | 145 |

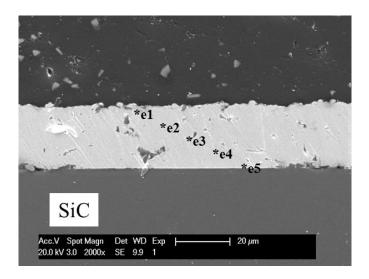

| Fig. 8.10 | The cross-sectional SEM image of Ag-In binary system with EDX analysis, after the 2-step annealing process                                                                            | 146 |

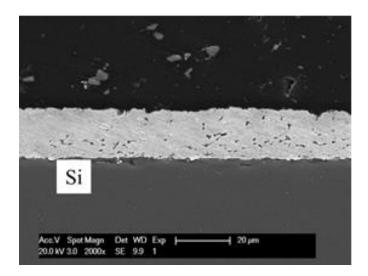

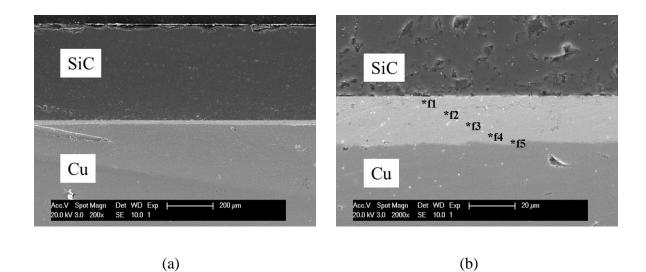

| Fig. 8.11 | The cross-sectional SEM image of Ag-In binary system (a) $200 \times$ magnification (b) $2000 \times$ magnification                                                                   | 147 |

| Fig. 8.12 | Die shear test                                                                                                                                                                        | 148 |

| Fig. 8.13 | The bonded sample was sheared off                                                                                                                                                     | 149 |

## LIST OF TABLES

|           |                                                                                                          | Page |

|-----------|----------------------------------------------------------------------------------------------------------|------|

| Table 1.1 | ITRS Single-chip Package Technology Requirements                                                         | 2    |

| Table 1.2 | The popular die attach materials with melting and operating temperatures                                 | 4    |

| Table 1.3 | Some properties of popular die attach materials                                                          | 7    |

| Table 1.4 | Four major steps for oxidation-free fluxless soldering technnique                                        | 8    |

| Table 3.1 | Materials and its applications                                                                           | 25   |

| Table 4.1 | The shear test results of six samples                                                                    | 54   |

| Table 5.1 | EDX data on Fig. 5.4 showing the Cu diffusion into Ag                                                    | 65   |

| Table 5.2 | Pull test breaking forces of Cu wire-bonds made on Cu substrates                                         | 68   |

| Table 5.3 | Pull test breaking forces of Cu wire-bonds made on Cu substrates                                         | 68   |

| Table 5.4 | EDX data on Fig. 5.8(b) showing mode A fracture surface of sample 3 after in-plane pull test             | 71   |

| Table 5.5 | EDX data on Fig. 5.8(d) showing mode C fracture surface of sample 3 after in-plane pull test             | 71   |

| Table 6.1 | Shear test results of five samples of Cu chip bonded to Ag layer with the annealing step on Cu substrate | 95   |

| Table 6.2 | EDX data on the Cu chip that was sheared off sample #5                                                   | 97   |

| Table 6.3 | Shear test results of five samples of Cu chip bonded to Ag layer with cavities on Cu substrate           | 103  |

| Table 6.4 | EDX data on the Cu chip that was sheared off sample #8                                                   | 105  |

| Table 7.1 | The designed pattern for the Cu etching process                                                          | 117  |

| Table 7.2 | Typical CTE values of the materials                                                                      | 122  |

| Table 8.1 | EDX analysis data on the cross-section of Ag-In binary system after two weeks at room temperature        | 133  |

| Table 8.2 | For design I, EDX analysis data on the cross-section of Ag-In binary system when the annealing process is completed | 135 |

|-----------|---------------------------------------------------------------------------------------------------------------------|-----|

| Table 8.3 | For design II, EDX analysis data on the cross-section of Ag-In binary system after the solid-state bonding process  | 137 |

| Table 8.4 | For design III, EDX analysis data on the cross-section of Ag-In binary system after the solid-state bonding process | 140 |

| Table 8.5 | EDX analysis data on the cross-section of Ag-In binary system after the 2-step annealing process                    | 146 |

| Table 8.6 | EDX analysis data on the cross-section of Ag-In binary system after the solid-state bonding process                 | 147 |

#### ACKNOWLEDGMENTS

I would like to express my deepest gratitude to Dr. Chin C. Lee, my advisor, who has equipped me with an invaluable training for science research in these years. This dissertation would never have been possible without his kind support, active encouragement, and clear instruction. I regard it as a great privilege, honor, and pleasure to work under his guidance.

I would like to thank Professor James Earthman and Professor Frank G. Shi for serving on my dissertation committee and enriching my work with their insights at various stages of this study.

I would like to extend my gratefulness to Professor Farghalli Mohamed, Professor G. P. Lee, and Professor Payam Heydari for their valuable suggestions on my research.

I am also grateful to Mr. Yongjun Huo, Dr. Yuan-Yun Wu, Dr. Shou-Jen Hsu, Dr. Rongwei Mao, Mr. Jiaqi Wu, Mr. Shao-Wei Fu, INRF and LEXI staffs.

Researching leading to this dissertation was supported by II-VI Foundation.

# **CURRICULUM VITAE**

# **Yi-Ling Chen**

| 2002      | Bachelor of Engineering                                   |

|-----------|-----------------------------------------------------------|

|           | Department of Chemical and Materials Engineering          |

|           | Tamkang University, New Taipei, Taiwan                    |

| 2002-2004 | Research Assistant                                        |

|           | Department of Materials Science and Engineering           |

|           | National Central University, Taoyuan, Taiwan              |

| 2004      | Master of Engineering,                                    |

|           | Department of Chemical and Materials Engineering,         |

|           | National Central University, Taoyuan, Taiwan              |

| 2004-2006 | Thin Film Engineer                                        |

|           | Taiwan Semiconductor Manufacturing Company (TSMC)         |

|           | Hsinchu, Taiwan                                           |

| 2012-2016 | Graduate Student Researcher                               |

|           | Materials & Manufacturing Technology                      |

|           | Department of Electrical Engineering and Computer Science |

|           | University of California at Irvine, Irvine, CA, USA       |

| 2015      | Teaching Assistant                                        |

|           | Department of Electrical Engineering and Computer Science |

|           | Course: Electrical Engineering Analysis                   |

|           | University of California at Irvine, Irvine, CA, US        |

| 2016      | Doctor of Philosophy in Engineering                       |

|           | Materials & Manufacturing Technology                      |

|           | University of California at Irvine, Irvine, CA, US        |

## PUBLICATIONS

#### Journal Articles

- 1. Y. L. Chen, and C. C. Lee, "Novel silver solid-state bonding designs between two copper structures", under review

- 2. Y. Huo, S. W. Fu, Y. L. Chen, and C. C. Lee, "A reaction study of sulfur vapor with silver and silver-indium solid solution as a tarnishing test method", under review

- 3. Y. Y. Wu, Y L. Chen, and C. C. Lee, "Solid state bonding of silicon chips to copper substrates using silver with cavities", Journal of Materials Science: Materials in Electronics, vol. 27, pp. 3347-3354, Dec. 2015

- 4. Y. L. Chen, Y. Y. Wu, and C. C. Lee, "A solid-state bonding technique of large copper wires for high power devices operating at high temperature", Journal of Materials Science: Materials in Electronics, vol. 26, pp. 3521-3529, Mar. 2015

#### Published Conference Proceedings and Conference Presentations

- 1. Y. L. Chen, Y. Huo, and C. C. Lee, "Design and fabrication of silver solid solution layer on silicon and its solid-state bonding applications" in IEEE 66<sup>th</sup> Electronic Components and Technology Conference (ECTC), 2016, accepted

- Y. L. Chen, Y. Y. Wu, and C. C. Lee, "Silver-assisted copper wire bonding using solid-state processes," in IEEE 64<sup>th</sup> Electronic Components and Technology Conference (ECTC), 2014, pp. 1529-1532

- 3. Y. L. Chen, Y. Y. Wu, and C. C. Lee, "Solid-state silver bonding design with microstructure to reduce material flow distance and stresses," in II VI Foundation Conference, 2014

- 4. Y. L. Chen and C. C. Lee, "Strength of solid-state silver bonding between copper," in IEEE 63<sup>rd</sup> Electronic Components and Technology Conference (ECTC), 2013, pp. 1773-1776

#### **ABSTRACT OF THE DISSERTATION**

Innovative Solid-State Bonding Designs and Techniques for High power Electronic and Laser

**Diode Packaging**

by

Ying-Ling Chen Doctor of Philosophy in Engineering University of California, Irvine, 2016

Professor Chin C. Lee, Chair

Rapid evolution of electronics industry has made the adoption of high performance chips more urgent. In fact, those chips cannot be used unless high temperature die attach materials and methods are available. The conventional die attach methods typically require a processing temperature 20-30 °C above the melting temperature of bonding material, which melts and reacts with to-be–bonded parts to form the bonding joint. For high temperature applications (> 400 °C), the processing temperature will sharply increase along with the increased melting temperature to reach the molten phase. However, such high processing temperature will damage nearly all electronic components. To respond to such challenge, the metal bonding is considered to be a possible solution.

In this dissertation, the solid-state bonding technique is employed for various bonding designs by electroplating Ag-based and In-based systems as bonding media. No molten phase or flux is involved. For most cases, the bonding conditions are conducted at 300 °C with 6.89 MPa (1,000 psi) pressure for a dwell time of 3 min in vacuum. The bonding time, 3 min, is constrained by the furnace. It is worth mentioning that this pressure is less than 10% of what is

used in industrial thermo-compression processes.

To begin with, silver (Ag) was chosen as a bonding medium because of its exceptional properties and reasonable price. There are two designs for the Ag layer. For the first design, the 50 µm Ag layer plated on the copper (Cu) substrate is initially annealed at 400 °C for 5 h to increase Ag grain sizes, thereby making it easier to deform during bonding. For the second design, the 10 µm Ag layer is plated on the substrate and followed another 5 µm Ag with cavities. The fundamental concept is to release the thermal induced stress by creating cavities in the Ag layer to allow easier plastic deformation for the bonding medium. The resulting Ag layers are then bonded to the Cu chips. For both designs, all samples are bonded well and pass MIL-STD-883J method 2019.9. The Ag layer is also applied to the Cu wire bonding. To overcome Cu oxidation issue, the bonding surface on the 1 mm Cu wire is plated a 50 µm Ag layer. An annealing step is followed to facilitate the Ag layer easier to deform and conform to the Cu or Si bonding surfaces. In-plane pull test and vertical pull test are performed to measure the breaking force of the wire bonds. For wire-bonds made on the Cu substrate, the breaking forces on inplane pull test are greater than 20 kg. The breaking forces on vertical pull test are approximately one-half of in-plane pull test results. For wire-bonds made on Si chip, breaking forces are approximately 80% of those made on Cu substrate.

Next, the novel method is to bond the Si chips to Cu substrates directly. This structure design can provide low-resistance paths for electricity and heat. There is no specific joint used in between. The basic concept is to provide room for Cu and Si to deform without restriction by producing trenches inside the Cu substrate. When the bond between two surfaces is formed, the trenches inside the Cu substrate could release the part of thermal stress from the coefficient of thermal expansion CTE mismatch. Therefore, the bond could deal with the large CTE mismatch

between Si (3 ppm/°C) and Cu (17 ppm/°C). The cross-sectional images show that the Si chips are well bonded to the Cu substrates without visible voids and cracks. After the bonding process, the simple shear tests are conducted to evaluate the bond strength, while the Si chips are all broken first. It demonstrates that the bond is stronger than the Si chip itself.

Finally, the Ag-rich Ag-In solid solution layers have successfully developed on Si and silicon carbide (SiC) chips. Ag has definite advantages among metals, but it still has its own weaknesses, which can actually or potentially lead to failure. That is Ag can be tarnished not only when exposed to certain corrosive gases such as hydrogen sulfide or sulfur gas but also under normal atmospheric conditions for a long period of time. Ag-In solid solution is further studied while Ag-In binary system has been demonstrated with an exceptional anti-tarnish property. To fabricate the single phase Ag-In solid solution, the Ag/In/Ag multilayers are electroplated on the chips. Importantly, the bottom Ag layer is initially annealed at 350 °C to increase its grain sizes and to reduce grain boundaries, inasmuch as the reaction rate between Ag and In is subject to the microstructure of Ag layer. The In/Ag layers are followed to be plated onto Si chip. To decompose AgIn<sub>2</sub> and Ag<sub>2</sub>In, the two-step annealing process is then performed in a vacuum environment at 180 °C and 350 °C, respectively. After the bonding process, the compositions of resulting joints are measured by SEM/EDX, which is a homogeneous Ag-rich Ag-In solid solution.

In this study, five different bonding designs are reported. All bonds made between the chips and the substrates are fabricated at relatively low processing temperatures. The bonding structures are designed to be used for high operating temperatures. The results are encouraging. These novel methods may bring a chance for those who need die-attach materials for high performance electronic devices under severe environmental conditions in industries.

## **Chapter One**

# Introduction

### **1.1** Electronic Packaging

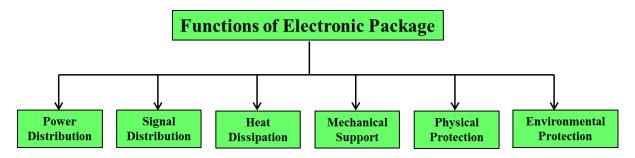

In electronics manufacturing, electronic packaging is the bridge that interconnects the integrated circuits (ICs) and other components into a system level interconnection to form electronic devices. The functions of packaging mainly include power distribution, signal distribution, heat dissipation, mechanical support, physical protection, and environmental protection [1-2], as shown in Fig 1.1. Importantly, the improper packaging of IC could seriously limit device performance and degrade reliability. Electronic packaging materials and techniques in fact play a key role for electronic systems with excellent performance. Therefore, the rapid development of electronics industry has led to active research for advanced packaging technology.

Fig. 1.1 Basic electronic package functions

| Year of Production              |                                       | 2016          | 2018          | 2020          | 2022          | 2024          | 2026          |

|---------------------------------|---------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Low-end,<br>Low cost<br>package | Cost<br>(Cents/Pin)                   | 0.20-<br>0.32 | 0.20-<br>0.29 | 0.20-<br>0.26 | 0.19-<br>0.25 | 0.19-<br>0.25 | 0.17-<br>0.25 |

|                                 | Power Density<br>(W/mm <sup>2</sup> ) | 0.5/40        | 0.5/40        | 0.5/40        | 0.5/40        | 0.5/40        | 0.5/40        |

|                                 | Pin Count<br>(Maximum)                | 100           | 100           | 100           | 100           | 100           | 100           |

|                                 | Performance:<br>On Chip (MHz)         | 50            | 50            | 50            | 50            | 50            | 50            |

| High<br>Performance             | Cost (Cents/Pin)                      | 1.15          | 1.04          | 0.94          | 0.85          | 0.77          | 0.73          |

|                                 | Power Density<br>(W/mm <sup>2</sup> ) | 0.70          | 0.80          | 0.90          | 1.00          | 1.10          | 1.20          |

|                                 | Pin Count<br>(Maximum)                | 6501          | 7167          | 7902          | 8712          | 9148          | 9605          |

|                                 | Performance:<br>On Chip (GHz)         | 9.18          | 10.65         | 12.36         | 14.34         | 15.41         | 16.18         |

Table 1.1 ITRS Single-chip Package Technology Requirements

The International Technology Roadmap for Semiconductors (ITRS) is one of the best sources for acquiring requirements of assembly and packaging based on continuing development of IC [3]. Table 1.1 lists some of the ITRS projections such cost, power density, pin count and operating frequency onto a single-chip packaging for low cost and high performance product categories. The data presented clearly indicates that high temperature, high power, and high frequency applications will increase along with increased functionality. In order to address the common needs of high performance devices, the die attach materials are first reviewed to meet basic requirements to be operable at high temperatures. In what follows, challenges and techniques for high temperature die attach materials are then discussed. The dissertation outline is given at last.

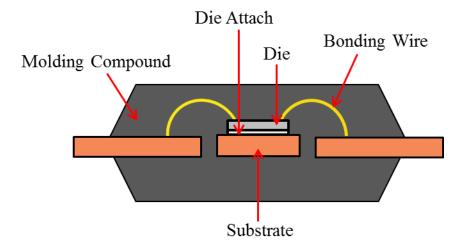

#### **1.2** The Die Attach Materials

Die attach materials are used to bond the chip (die) and the substrate. Fig. 1.2 portrays a simple packaging device. The popular bonding materials are solder alloys (eutectic and soft solders), polymer-based electrically conductive adhesives (ECAs), and silver (Ag) based pastes (Ag-glass and sintered nano-Ag pastes) [4-7]. Table 1.2 presents some bonding materials studied

Fig. 1.2 A simple packaging device

Table 1.2 The popular die attach materials with melting and operating temperatures.

| Die-attach materials                             | Melting Temperature (°C)            | *Operating Temperature (°C)  |  |  |

|--------------------------------------------------|-------------------------------------|------------------------------|--|--|

| Sn63Pb37                                         | 183                                 | 92                           |  |  |

| Sn96.5Ag3Cu0.5                                   | 217                                 | 119                          |  |  |

| Au80Sn20                                         | 280                                 | 170                          |  |  |

| Pb95.5Ag2.5Sn2                                   | 300                                 | 185                          |  |  |

| Au88Ge12                                         | 356                                 | 230                          |  |  |

| Au97Si3                                          | 363                                 | 236                          |  |  |

| Elecolit® 327<br>(ECA)                           | 120-150<br>(Processing temperature) | 275<br>(Literature review)   |  |  |

| Sintered280nano-Ag paste(Processing temperation) |                                     | < 600<br>(Literature review) |  |  |

| Ag                                               | 961                                 | 715                          |  |  |

from literatures, including their melting temperatures and their operating temperatures which are calculated by homologous temperature of 80 % [8-12]. From the Table 1.2, the lead-tin eutectic solder, lead-free solder, and gold-tin eutectic cannot sustain temperatures higher than 170 °C [13]. Even in the case of high lead lead-tin solder, the operating temperature is only 185 °C. The maximum operating temperature of gold (Au) based solders is approximately 240 °C; nevertheless, the cost is extremely high due to high percentage of Au [14]. In addition to the

solder alloys mentioned above, some of ECAs used in commercial devices, fail at temperature near 275 °C. Regardless of the category of the die attach materials, the relatively low melting temperatures of those materials is considered to be a serious issue, thereby preventing them from being employed as a possible solution for high temperature applications. For high temperature electronic modules incorporating silicon carbide (SiC) and gallium nitride-based (GaN) devices, a new bonding medium for high temperature applications is the nano-Ag paste [15]. After sintering, the paste can be turned into pure silver and then would be able to handle high operating temperature. The sintering process often requires relatively high temperature and pressure to obtain significant densification and create the joint [16-17]. The resulting Ag joints cannot be made pore-free. A major concern with pores involves the loss of thermal conductivity.

Rapid evolution of electronics industry has made the adoption of high performance chips more urgent. In fact, those chips cannot be used unless high temperature die attach materials are available. The development of high temperature bonding material not only is a technological challenge for achieving better performance, but also a critical step for possible new generation of the electronic products.

### **1.3** Challenges for High Temperature Die Attach Materials

There are two major issues for high temperature die attach materials. Firstly, the high operating temperature bonding joint has to be achieved without the high processing temperature. The conventional die attach method typically requires a processing temperature 20-30 °C above the melting temperature of bonding material. During the molten phase, the bonding material melts and reacts with to-be–bonded parts to form the bonding joint. For high temperature applications (> 500 °C), the processing temperature will sharply increase along with the increased melting temperature to reach the molten phase. However, such high processing temperature will damage nearly all electronic components. Clearly, increased operating temperature is required, but increased processing temperature is not desirable.

Secondly, high temperature electronic devices demand efficient thermal management. The most important thermal properties are coefficient of thermal expansion (CTE) and thermal conductivity. The concern of high temperature die attach materials is the difference of CTE between chips and substrates, for example, Si chips (3 ppm/°C) and Cu substrates (17 ppm/°C). This pair creates large CTE mismatch and results in thermal stress after the die attach process. A suitable die attach material must be able to deal with severe CTE mismatch. In addition, thermal dissipation is another concern. For example, the heat generated in the laser diode is dissipated by attaching a heat sink. The die attach material must ensure an efficient heat transfer through the thermal interface, since their performance decreases drastically with increasing chip temperature [18-20].

To overcome these challenges, it is very essential to select the proper die attach material which has excellent properties, high melting temperature and low processing temperature. Table 1.3 lists some properties of popular die attach materials. From the Table 1.3, Ag is a possible solution as it has high melting temperature, excellent ductility, low yield strength, and superior electrical and thermal conductivity. The difficulty is how to find a method to form Ag joints at low temperature with low pressure.

| Properties                                           | Cu     | Ag     | Au     | Sn    | Sn3.5Ag     |

|------------------------------------------------------|--------|--------|--------|-------|-------------|

| Melting temperature (°C)                             | 1,083  | 961    | 1,063  | 231   | 221         |

| Density (gm/cc)                                      | 8.94   | 10.5   | 19.3   | 7.29  | 7.4         |

| Thermal conductivity (watt/cm-K)                     | 3.862  | 4.075  | 3.151  | 0.665 | 0.78        |

| Electrical conductivity $(x10^{5}/\Omega\text{-cm})$ | 5.88   | 6.25   | 4.17   | 0.87  | 0.812       |

| CTE (ppm/°C)                                         | 16.4   | 18.6   | 14.2   | 22.2  | 30.2        |

| Yield strength (psi)                                 | 10,000 | 1,000  | 250    | 1,300 | 3,600       |

| Ultimate tensile strength (psi)                      | 32,000 | 21,000 | 17,000 | 2,000 | 5,000~7,000 |

| Young's modulus (x10 <sup>6</sup> psi)               | 19.2   | 11.8   | 11.2   | 6.89  | 7.8         |

| Elongation at break (%)                              | 51     | 50     | 50     | 50~80 | 37          |

| Hardness (Brinell)                                   | 37     | 25     | 18.5   | 3.7   | 14.8        |

Table 1.3 Some properties of popular die attach materials

### **1.4** Techniques for High Temperature Die Attach Materials

In the case of soldering process, the flux mainly react with metal oxides such as CuO and SnO. Once the metal oxides are removed by fluxing actions, the fresh solder and base metals can contact intimately to form solder joints. Simultaneously, flux residues are generated, which are known to cause voids and remain corrosive. It could say that flux residues not only are accompanied, but also lead to degrade the performance of device. Consequently, the use of flux is prohibited for many applications. Even if it is allowed, the assembled parts need to be cleaned to remove all flux residues. The fluxless process, thus, becomes very critical to improve reliability in the advanced electronic packaging.

| T-1.1. 1 / E        |            | ſ         | 1. 1 f      | £11        | 1 1       | A 1             |

|---------------------|------------|-----------|-------------|------------|-----------|-----------------|

| Table 1.4 Four m    | alor steps | tor oxid  | lation-free | THIXIESS   | soldering | technnique      |

| 10010 1111 0001 111 | ajor stops | 101 0/110 |             | 1100111000 | bolaoling | ce e mining a e |

| Step | Process                     | Approach                              |

|------|-----------------------------|---------------------------------------|

| 1    | Solder fabrication          | Electroplating or Vacuum deposition   |

| 2    | A capping layer over solder | Ag or Au                              |

| 3    | Bonding environment         | Vacuum or Inert gas or H <sub>2</sub> |

| 4    | Dealing with capping layer  | Dissolution                           |

Our group has developed an oxidation-free fluxless soldering technique to produce high temperature joints at low processing temperature since 1995 [21-23]. There are four major steps necessary to accomplish the fluxless bonding, as show in Table 1.4. First, solder materials should be fabricated in an oxidation-free environment such as vacuum deposition or electroplating method. Second, there should be a thin capping layer, usually Au or Ag layer, on the solder materials to protect inner solders from oxidation when solders are exposed to air. Third, the bonding process should be performed in vacuum, inert gas, or H<sub>2</sub> environment to inhibit oxidation. Finally, during the reflow process, this thin capping layer should become a part of joints and the fresh solders can react with base metals to form IMCs. This technique has been applied to develop various fluxless processes such as on Sn-Au, Sn-Cu, Sn-Ag, Sn-Bi, Sn-In, In-Au, In-Cu, In-Ag binary systems and In-Pb-Au ternary system [22-28]. The results are encouraged. However, this fluxless bonding technique is not feasible to form Ag joints due to its high melting temperature.

Among all possible metallic bonding materials for electronic packaging, Ag is a promising choice in terms of excellent physical, chemical, thermal, electrical, and mechanical properties. However, Ag does not melt until 952 °C. Obviously, taking the advantage of Ag is desirable, but increasing processing temperature is not desirable. To respond to this challenge, our group has successfully developed a solid-state atomic bonding technique to bond Ag to Au,

Ag, and Cu, respectively, at a temperature much lower than its melting point [29-32]. This is a solid-state bonding process without molten phases. No flux is used. The bonding is performed at 300 °C with 1,000 psi (6.9 MPa) pressure in 0.1 torr vacuum for a few minutes. The 300 °C bonding temperature makes Ag deform more easily to conform to the bonding chip's surface profile. The pressure is less than 1/10 of what used in industrial thermo-compression processes [33-36].

The fundamental concept of solid-state atomic bonding refers to the atomic interaction between solid material A and solid material B when A atoms and B atoms are brought within atomic range. On the interface, bonding between materials A and B will occur where A atoms and B atoms can share outer electrons. The ability to share outer electrons mainly depends on the electronic configurations. The bonding theory based on quantum mechanics was recently reported [37].

### **1.5 Dissertation Outline**

This thesis is composed of 9 chapters, including the present one, and their content is concisely presented below:

Chapter 2 briefly reviews the solid-state bonding technology based on its bonding

mechanism and the three major parameters, including temperature, pressure, and time. The bonding can be accomplished within a reasonable time by choosing appropriate temperature and pressure values. The quantum theory of solid-state atomic bonding is further reported.

Chapter 3 is to report the materials, apparatus, fabrication processes, bonding furnace setup, and characterization analysis.

Chapter 4 is to present that a 50 µm Ag layer is used as a bonding medium between two Cu pieces. That is initially annealed at 400 °C for 5 h to increase Ag grain sizes, thereby making it easier to deform during bonding. The solid-state bonding process is performed at 300 °C with 6.89 MPa (1000 psi) static pressure for 3 min. The shear test results of 6 samples all pass MIL-STD-883J method 2019.9.

Chapter 5 is to present a novel method for advanced Cu wire bonding. The 1 mm Cu wires is cut a flat surface and then electroplated a 50 µm Ag layer. The Cu wires bond to Cu and Si chips, respectively. The bonding conditions are at 300 °C with 6.89 MPa (1,000 psi) for 3 min. For wire-bonds made on Cu substrate, in-plane pull test measured a breaking of force 20.7 to 23.7 kg, comparable to the 22.5 kg breaking force of the Cu wire itself. Breaking forces on vertical pull test are about one-half of in-plane pull test results. For wire-bonds made on Si chip, breaking forces are about 80% of those made on Cu substrate.

Chapter 6 is to present that a patterned Ag layer is used as a bonding medium between

two Cu pieces. With this design, the flow distance is not set by the chip size. That is determined by the pattern on the Ag bonding layer. Additionally, the patterned cavities could release the thermal induced stress by creating cavities in the Ag layer to allow easier plastic deformation for the bonding medium. The bonding conditions are the same as the Ag joints without cavities. The shear test results of 5 samples all pass MIL-STD-883J method 2019.9.

Chapter 7 is to present a novel design that Si chips have successfully bonded to Cu substrates directly. The Cu substrates are etched to produce the trench pattern, followed by thin layer of Ag (1 µm) to prevent Cu from oxidation. Si chips are deposited with thin Cr (30nm) and Au (100nm). The Si chip is placed over Cu substrate and bonded at 300°C with 6.89 MPa (1000 psi) for 3 min using the solid-state bonding process in vacuum. The simple shear tests are conducted to evaluate the bond strength, while the Si chips are all broken first.

Chapter 8 is to present that designs and fabrications of Ag-In solid solution layers on Si and SiC chips and subsequent solid-state bonding to Cu substrate. The Ag/In/Ag multilayers are electroplated on the chips. The initial annealing step carried out in between is to increase its grain sizes and to reduce grain boundaries, inasmuch as the reaction rate between Ag and In is subject to the microstructure of Ag layer. A two-step annealing process is followed in a vacuum environment at 180 °C and 350 °C, respectively. The SEM/EDX analysis studies the composition of bonding joints, which displays the single phase Ag-In solid solution. The simple shear tests are conducted to evaluate the bond strength. After the test, the half Ag-In solid solution joints are still bonded on the Cu substrates. It could say that the bond is strong not weak.

Finally, chapter 9 is given to point out important conclusions in this dissertation.

### 1.6 References

- R. R. Tummala, E. J. Rymaszewski, and A. G. Klopfenstein., Microelectronics Packaging Handbook, New York: Van Nostrand Reinhold, pp.1-63, 1989

- R. R. Tummala, Fundamentals of Microsystems Packaging, New York: McGraw- Hill, pp.1-41, 2001

- International Technology Roadmap for Semiconductors, 2011 Ed, Assembly and Packaging, 2011, http://www.itrs2.net/itrs-reports.html

- D. D. Lu and C. P. Wong, "Recent advances in developing high performance isotropic conductive adhesives," Journal of Adhesion Science and Technology, vol. 22, pp. 835-851, 2008

- Y. Li, K. S. Moon, and C. P. Wong, "Monolayer-protected silver nano-particle-based anisotropic conductive adhesives: enhancement of electrical and thermal properties," Journal of Electronic Materials, vol. 34, pp. 1573-1578, 2005

- H. Dong, K. S. Moon, and C. P. Wong, "Molecular dynamics study of nanosilver particles for low-temperature lead-free interconnect applications," Journal of Electronic Materials, vol. 34, pp. 40-45, 2005.

- 7. K. Moon, C. Rockett, C. Kretz, W. F. Burgoyne, and C. P. Wong, "Improvement of adhesion

and electrical properties of reworkable thermoplastic conductive adhesives," Journal of Adhesion Science and Technology, vol. 17, pp. 1785-1799, 2003.

- E. H. Amalu and N. N. Ekere, "Damage of lead-free solder joints in flip chip assemblies subjected to high-temperature thermal cycling," Computational Materials Science, vol. 65, pp. 470-484, 2012.

- 9. T.W. Giants, "Aging effects on the electrical properties of silver-filled epoxy adhesives," Journal of Adhesion Science and Technology, vol. 12, pp. 593-613, 1998.

- 10. D. Lu, D. WONG, and C. P. WONG, "Properties of conductive adhesives based on different curing agents," Journal of Electronics Manufacturing, vol. 9, pp. 241-248, 1999.

- P. O. Quintero and F. P. McCluskey, "Temperature cycling reliability of high-temperature lead-free die-attach technologies," IEEE Transactions on Device and Materials Reliability, vol. 11, pp. 531-539, 2011.

- R. Kisiel and Z. Szczepanski, "Die-attach solution for SiC power devices," Microelectronics Reliability, vol. 49, pp. 627-629, 2009.

- 13. K. Suganuma, "Advances in lead-free electronics soldering," Current opinion in Solid State and Material Science, vol. 5, pp. 55-64, 2001.

- 14. T. A. Tollefsen, A. Larsson, O. M. Lovvik, and K. E. Aasmundtveit, "High temperature interconnect and die attachment technology: Au-Sn SLID bonding," IEEE Transactions on Components, Packaging, and Manufacturing Technology, vol. 3, pp. 904-914, 2013.

- L. Coppolal, D. Huff, F. Wang, R. Burgos, and D. Borovevich, "Survey on high-temperature packaging materials for SiC-based power electronics modules," IEEE Power Electronics Specialists Conference (PESC), pp. 2234-2240, 2007.

- 16. Z. Zhang and G. Q. Lu, "Pressure-assisted low-temperature sintering of silver paste as an alternative die-attach solutions to solder reflow," IEEE Transactions on Components,

Packaging, and Manufacturing Technology, vol. 25, pp. 279-283, 2002.

- 17. J.G. Bai, J. N. Calata, and G. Q. Lu, "Processing and characterization of nanosilver pastes for die-attaching SiC devices," IEEE Transactions on Components, Packaging, and Manufacturing Technology, vol. 30, pp. 241-245, 2007.

- T. M. Alander, P. A. Heino, and E. O. Ristolainen, "Analysis of substrates for single emitter laser diodes," Journal of Electronics Packaging, vol. 125, pp. 313-318, 2003.

- C. Chaminade, E. Fogarassy, and D. Boisselier, "Diode laser soldering using a lead-free filler material for electronic packaging structures," Applied Surface Science, vol. 252, pp. 4406-4410, 2006.

- K. E. Goodson, K. Kurabayashi, and R. F. W. Pease, "Improved heat sinking for laser-diode arrays using microchannels in CVD diamond," IEEE Transactions on Components, Packaging, and Manufacturing Technology, vol. 20, pp. 104-109, 1997.

- 21. K. M. Chu, J. S. Lee, H. S. Cho, H. H. Park, and D. Y. Jeon, "A fluxless flip-chip bonding for VCSEL arrays using silver-coated indium solder bumps," IEEE Trans. Electronics Packaging Manufacturing, vol. 27, pp. 246-253, 2004.

- G. Matijasevic, Y. C. Chen, and C. C. Lee, "Copper-tin multilayer composite solder for fluxless processing," International J. of Microcircuits and Electronic Packaging, vol. 17, pp. 108-117, 1994.

- R. W. Chuang, D. Kim, J. Park, and C. C. Lee, "A fluxless process of producing tin-rich gold-tin joints in air," IEEE Trans. Components and Packaging Technology, vol. 27, pp. 177-181, 2004.

- C. C. Lee, C. Wang, and G. Matijasevic, "A new bonding technology using gold and tin multilayer composite structures," IEEE Trans. Components, Hybrids and Manufacturing Technology, vol. 14, pp. 407-412, 1991.

- C. C. Lee, C. Wang, and G. Matijasevic, "Gold-indium alloy bonding below the eutectic temperature," IEEE Trans. Components, Hybrids and Manufacturing Technology, vol. 16, pp. 331-316, 1993.

- 26. C. C. Lee and Y. C. Chen, "Indium-copper multilayer composite for fluxless oxidation-free bonding," Thin Solid Film, vol. 283, pp. 243-246, 1996.

- 27. Y. C. Chen, W. W. So, and C. C. Lee, "A fluxless bonding technology using indium-silver multilayer composites" IEEE Trans. Components, Packaging, and Manufacturing Technology-Part A, vol. 20, pp. 46-51, 1997.

- J. Kim and C. Lee, "Fluxless Sn-Ag bonding in vacuum using electroplated layers," Materials Science and Engineering A, vol. 448, pp. 348-.50, 2007.

- W. P. Lin, C. H. Sha, P. J. Wang, and C. C. Lee, "Microstructures of silver films plated on different substrates and annealed at different conditions," Proc. IEEE Electronic Components and Technology Conference (ECTC), pp. 1782-1786, 2011.

- C. H. Sha, P. J. Wang, W. P. Lin, and C. C. Lee, "Solid state bonding of silver foils to metalized alumina substrates at 260 °C," Journal of Electronic Packaging, vol. 133, pp. 041007-1-041007-3, 2011.

- 31. C. H. Sha and C. C. Lee, "Low temperature solid state gold bonding of Si chips to alumina substrates," Journal of Electronic Packaging, vol. 133, pp. 021003-1-021003-5, 2011.

- 32. C. H. Sha and C. C. Lee, "Low-temperature solid-state silver bonding of silicon chips to alumina substrates," IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 1, pp. 1983-1987, 2011.

- 33. S. Das, A. N. Tiwari, and A. R. Kulkarni, "Thermo-Compression Bonding of Alumina Ceramics to Metal," *Journal of Material Science*, vol. 39, pp. 3345-3355, 2004.

- 34. S. Pozder, A. Jain, R. Chatterjee, Z. Huang, R. E. Jones, and E. Acosta et al., "3-D die-to-

wafer Cu/Sn microconnects formed simultaneously with an adhesive dielectric bond using thermal compression bonding," International Interconnect Technology Conference (IITC), pp. 48-50, 2008.

- C. H. Tsau, S. M. Spearing, and M. A. Schmidt, "Characterization of wafer-level thermalcompression bonds," Journal of Microelectromechanical Systems, vol. 13, pp. 963-971, 2014.

- 36. S. Chen, W. Li, and X. Liu, "Calculation of rolling pressure distribution and force based on improved Karman equation for hot strip mill," International Journal of Mechanical Sciences, vol. 89, pp. 256-263, 2014.

- 37. C. C. Lee and L. Cheng, "The quantum theory of solid-state atomic bonding," Proc. IEEE Electronic Components and Technology Conference (ECTC), pp. 1335-1341, 2014.

## **Chapter Two**

## **Review of Solid-State Bonding Principle**

#### 2.1 Introduction

Solid-state bonding refers to the bonding process at temperatures below the melting temperatures of the bonding materials. No liquid or gaseous state is involved. Examples of vapor-phase bonding are sputtering and chemical vapor deposition processes [1]. Examples of molten-phase bonding are soldering and welding processes. The popular processes for achieving solid-state bonding are thermo-compression and diffusion bonding. Solid-state bonding is carried out at relatively lower temperature compared with molten-phase and vapor-phase bonding, which makes surface roughness difficult to overcome. Accordingly, the bonding between solids may be hard to occur.

The term diffusion bonding is often regarded as solid-state bonding [2]. It may cause confusion with respect to solid-state bonding and thermal-compression bonding. Brief definitions are given in this section. For the bonding mechanism, both diffusion and thermos-compression bonding are affiliated to solid-state bonding. Diffusion bonding requires a considerable amount of time for the atoms to interact with each other, and thus they can achieve the bond. On the contrary, thermal-compression bonding can be achieved within a short period of time. In this dissertation, we are more interested in using solid-state bonding process to form a robust bond within a few tens of seconds.

## 2.2 Parameters in solid-state bonding

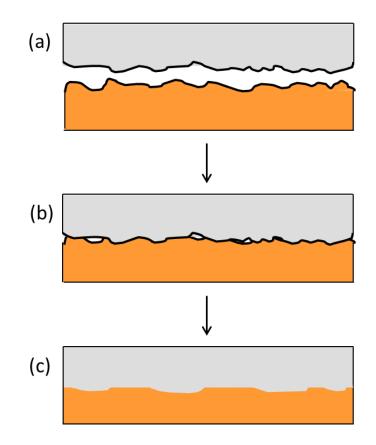

There are three major parameters of the solid-state bonding, temperature, pressure, and time, which are closely interrelated [3-4]. The role of these parameters is to achieve the intimate contact between the surfaces to be bonded, and thus the interaction can occur. Therefore, the bonding can be accomplished within a reasonable time by choosing appropriate temperature and pressure values. Fig. 2.1 depicts a simple solid-state bonding process. First, two dissimilar metallic surfaces are cleaned and ready to perform the bonding experiment, as shown in Fig. 2.1 (a). Second, both pressure and heat can be applied to create intimate contact between the surfaces to be bonded, as shown in Fig. 2.1 (b). During the creation of intimate contact, metals may undergo plastic deformation to conform the surface roughness. Next, the interaction can be activated. Finally, the bond is achieved, as shown in Fig. 2.1 (c). Ideally, no voids and gaps can be observed.

Fig. 2.1 A simple solid-state bonding process (a) Two dissimilar metal surfaces are ready for the bonding experiment, (b) The intimate contact is created, and (c) The bond is achieved

An important purpose of this dissertation is to determine the solid-state bonding conditions that can be applied to various metal combinations. One way to increase the percentage of bonding is to increase the pressure, which can greatly reduce the influence of surface roughness. But any pressure higher than 1,000 psi is not acceptable in our applications. The concern is that such high pressure may damage the chips to be bonded. On the other hand, high temperatures can provide a high rate of interaction, however, which may also result in the high defect densities on the chips. Our objective is looking for other ways to improve the bonding strength without increasing the pressure or the temperature. Some novel designs are reported in the following chapters.

#### 2.3 The Quantum Theory of Solid-state Atomic Bonding

Numerous experiments have been performed to show the possibility to achieve a robust bond using solid-state bonding process [5]. Neither principle nor theory at the atomic level has been reported. How is solid-state bonding possible?

Fundamentally, it is possible only if materials A and B can be brought within atomic distance. Over the past few years, we have proposed the solid-state atomic bonding principle as follows: "As A atoms and B atoms are brought within atomic distance, there is the interaction between them. On the atomic interface, if A atoms and B atoms can share outer electrons, bonding between materials A and B will occur. The ability of materials A and B to share outer electrons depends on their electronic configurations. Diffusion of A and B atoms alone does not guarantee bonding if A and B atoms do not want to share electrons. A and B atoms may share electrons to form  $A_xB_y$  compound. The  $A_xB_y$  compound may or may not bond with A or B atoms, depending on whether they are willing to share electrons." Our experimental bonding results have indicated that this bonding principle is correct [6-8]. At present, the ability to share

electrons is determined by the experimental data. The broader questions are: "how do we determine whether A atoms and B atoms would share electrons and how closely they require to be brought together to achieve bonding?" We searched the literature and could not find any publications in this subject. The fundamental mechanism and principle of solid-state bonding were seldom reported.