# **UC Berkeley**

# **UC Berkeley Electronic Theses and Dissertations**

### **Title**

Agile Design of Generator-Based Signal Processing Hardware

### **Permalink**

https://escholarship.org/uc/item/3sr4x8md

### **Author**

Wang, Angie

## **Publication Date**

2018

Peer reviewed|Thesis/dissertation

# Agile Design of Generator-Based Signal Processing Hardware

by

### Angie Wang

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolić, Chair Professor Vladimir Stojanović Professor Aaron Parsons

Spring 2018

# Agile Design of Generator-Based Signal Processing Hardware

Copyright 2018 by Angie Wang

#### Abstract

Agile Design of Generator-Based Signal Processing Hardware

by

Angie Wang

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Chair

Custom, application-specific implementations of digital signal processing (DSP) systems offer high performance and high energy efficiency, but require significant design and verification effort. Fast Fourier transform (FFT) processors with a broad range of performance requirements are needed for many modern-day signal processing applications, ranging from medical imaging and machine learning to communication and radio astronomy. Certain applications, including modern-day wireless communications, require runtime reconfigurability across a multitude of mixed-radix FFT sizes, high throughput, low latency, and lower power. Convolutional neural networks use multi-dimensional FFTs with stringent requirements on quantization bounds. Despite sharing underlying algorithms and hardware constructs, FFT designs are often difficult to reuse on a per-application or even per-platform basis, leading to redeveloping and reverifying conceptually similar instances. Hardware generators are attractive solutions for effectively balancing fine-grained control of implementation details with simple, rapidly retargetable hardware descriptions, but the existing FFT generators do not support key features like runtime reconfigurability or more general mixed-radix FFTs, limiting their applicability.

This thesis presents ACED (A Chisel Environment for DSP), a library extension to the Chisel hardware construction language and the FIRRTL (Flexible Intermediate Representation for RTL) compiler specifically created to simplify the development of hardware DSP generators. ACED allows DSP designs to be specified at a higher level of abstraction, making it easier to add new features as they become necessary. Optimization and specialization are handled via platform-specific compiler passes that promote generator reusability. The ACED library has been used to create a parameterizable memory-based, runtime-reconfigurable  $2^n 3^m 5^k 7^l$  FFT generator to support next-generation wireless systems prototyping. The generator uses a conflict-free, in-place, multi-bank SRAM design, and exploits the duality of decimation-in-frequency and decimation-in-time FFTs to support continuous data flow with  $\sim 2N$  memory. The hardware itself is templated so that Chisel/Scala code can be written to add additional functionality, and users pass parameters to the hardware template via a "firmware" block. This is the essence of the Chisel DSP generator methodology.

The FFT generator has been proven via a 0.37-mm<sup>2</sup> LTE/Wi-Fi compatible FFT RISC-V accelerator instance with measured performance and area comparable to state-of-the-art. To demonstrate the use case of the FFT generator in a larger systems context, a low-power signal acquisition front end capable of sensing frequency-sparse signals in a 1.89-GHz bandwidth with a resolution of 175 kHz in real time has also been prototyped in a 16-nm process. The spectral analysis chip relies on mixed-radix FFTs and reconstruction via the fast Fourier aliasing-based sparse transform (FFAST) algorithm to recover signals in compressed form from a subsampled input. This thesis presents new tools and design methodologies to rapidly design DSP hardware generators—with a particular focus on FFTs—for use in emerging applications such as spectrum sensing for cognitive radio, RADAR, and more.

# Contents

| $\mathbf{C}_{\mathbf{c}}$ | onten                            | its                     |                                                                                                     | i                     |

|---------------------------|----------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------|-----------------------|

| $\mathbf{Li}$             | st of                            | Figur                   | es                                                                                                  | iv                    |

| $\mathbf{Li}$             | st of                            | Table                   | S                                                                                                   | xi                    |

| 1                         | Intr<br>1.1<br>1.2<br>1.3<br>1.4 | FFTs:<br>Backg<br>Agile | ion: Agile DSP Hardware Generation. Why the Need?  A Motivating Example for Hardware DSP Generators | 1<br>1<br>3<br>7<br>9 |

| 2                         | A R                              | untim                   | e-Reconfigurable, Mixed-Radix Hardware FFT Generator                                                | 10                    |

|                           | 2.1                              | Overv                   | iew                                                                                                 | 10                    |

|                           | 2.2                              | Comp                    | uting the Discrete Fourier Transform via FFTs                                                       | 10                    |

|                           |                                  | 2.2.1                   | Cooley-Tukey FFT                                                                                    | 11                    |

|                           |                                  |                         | 2.2.1.1 Decimation-in-Frequency FFT                                                                 | 11                    |

|                           |                                  |                         | 2.2.1.2 Decimation-in-Time FFT and DIF $\leftrightarrow$ DIT Duality                                | 14                    |

|                           |                                  |                         | 2.2.1.3 Generalizing the CTA Index Mapping: Digit Reversal                                          | 16                    |

|                           |                                  |                         | 2.2.1.4 CTA Twiddle Multiplication                                                                  | 18                    |

|                           |                                  | 2.2.2                   | Generalized Index Mapping                                                                           | 19                    |

|                           |                                  |                         | 2.2.2.1 Case A: $gcd(N_1, N_2) \neq 1$                                                              | 20                    |

|                           |                                  |                         | 2.2.2.2 Case B: $gcd(N_1, N_2) = 1 \dots \dots \dots \dots \dots \dots$                             | 20                    |

|                           |                                  | 2.2.3                   | Prime-Factor Algorithm                                                                              | 20                    |

|                           |                                  | 2.2.4                   | A Generalized Mixed-Radix Algorithm                                                                 | 23                    |

|                           |                                  | 2.2.5                   | Combining the CTA and PFA                                                                           | 24                    |

|                           | 2.3                              | Input                   | Output Index Vector Generator                                                                       | 26                    |

|                           | 2.4                              | Memo                    | ry-Based Architecture with Conflict-Free Calculation Scheduling                                     | 30                    |

|                           |                                  | 2.4.1                   | Pipelined vs. Memory-Based Architectures                                                            | 30                    |

|                           |                                  | 2.4.2                   | Computation Clock Cycles                                                                            | 32                    |

|                           |                                  | 2.4.3                   | Butterfly Scheduling and Calculation Control Logic                                                  | 34                    |

|                           |                                  |                         | 2.4.3.1 Computation with a Single Iterating Butterfly                                               | 34                    |

|          |               | 2.4.3.2 Computation with Multiple Parallel Butterflies           | 30 |

|----------|---------------|------------------------------------------------------------------|----|

|          | 2.5           | Twiddle Address Generation                                       | 41 |

|          | 2.6           | Butterfly Construction                                           | 42 |

|          |               | 2.6.1 Using the Cooley-Tukey Algorithm                           | 42 |

|          |               | 2.6.2 Winograd's (Short) Fourier Transform Algorithm             | 44 |

|          |               |                                                                  | 44 |

|          |               | 2.6.2.2 Rader's DFT Algorithm                                    | 45 |

|          |               | 2.6.2.3 Winograd's Short Convolution Algorithm                   | 47 |

|          |               |                                                                  | 48 |

|          |               | 2.6.2.3.2 2-Point Convolution Example                            | 49 |

|          |               | 2.6.2.4 3-Point WFTA Butterfly Derivation and N-Point WFTA Equa- |    |

|          |               | tions                                                            | 50 |

|          |               | 2.6.3 Reconfigurable WFTA Butterfly                              | 54 |

|          |               | 2.6.4 The Complete Processing Element                            | 58 |

|          | 2.7           | Generating FFT Instances from a Hardware Template                | 59 |

|          |               |                                                                  | 62 |

|          | 2.8           | •                                                                | 63 |

|          |               |                                                                  | 64 |

|          |               |                                                                  | 66 |

|          |               | 2.8.3 Summary                                                    | 68 |

|          |               |                                                                  |    |

| <b>3</b> | $\mathbf{AC}$ | ED: A Hardware Library for Generating DSP Systems                | 71 |

|          | 3.1           | Introduction                                                     | 71 |

|          | 3.2           | $\circ$                                                          | 73 |

|          |               |                                                                  | 73 |

|          |               |                                                                  | 73 |

|          |               | 3.2.3 Tools for Hardware Generation                              | 74 |

|          |               | ( ) 0 0                                                          | 74 |

|          | 3.3           |                                                                  | 75 |

|          |               | 1 01                                                             | 76 |

|          |               | V I                                                              | 77 |

|          |               | 3.3.1.2 An FIR Filter Generator Example:                         | 78 |

|          |               | 3.3.2 Unified Systems Modeling and Verification                  | 79 |

|          |               | 3.3.3 Interval-Based Arithmetic and Bitwidth Reduction           | 83 |

|          |               | 3.3.3.1 Static Interval Optimization                             | 83 |

|          |               | 3.3.3.2 Dynamic Interval Optimization via Hardware Profiling     | 85 |

|          | 3.4           | Bitwidth Optimization Results                                    | 86 |

|          | 3.5           | ACED Summary                                                     | 89 |

|          |               |                                                                  |    |

| 4        |               | Real-Time, Analog/Digital Co-Designed 1.89-GHz Bandwidth, 175-   | 0- |

|          |               | ı ı                                                              | 91 |

|          | 4.1           | Introduction                                                     | 91 |

|    | 4.2   |                                                       | 93<br>93 |

|----|-------|-------------------------------------------------------|----------|

|    |       |                                                       | 97       |

|    |       | 4.2.2.1 Problem Setup                                 | 97       |

|    |       | 4.2.2.2 FFAST Peeling Decoding                        | 98       |

|    |       | 4.2.2.3 Singleton Estimator                           | 00       |

|    |       | 4.2.2.4 Theoretical Limits via Simulation Results     | )3       |

|    | 4.3   | Implementation Details                                | )5       |

|    |       | 4.3.1 Analog Frontend                                 | )5       |

|    |       | 4.3.2 Sub-FFTs                                        | )8       |

|    |       | 4.3.3 Singleton Estimation and Peeling Reconstruction | )9       |

|    |       | 4.3.3.1 Calculating $x \mod n$                        | .3       |

|    |       | 4.3.3.2 CORDIC                                        | .3       |

|    |       | 4.3.4 Rocket Processor                                | 4        |

|    | 4.4   | Measurement Results                                   | .5       |

|    | 4.5   | Chip Summary                                          | 24       |

| 5  | Con   | nclusions 12                                          | 28       |

|    | 5.1   | Summary of Contributions                              | 28       |

|    | 5.2   | Future Work                                           |          |

| Bi | bliog | graphy 13                                             | 31       |

# List of Figures

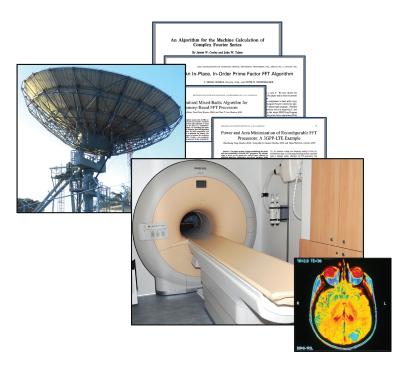

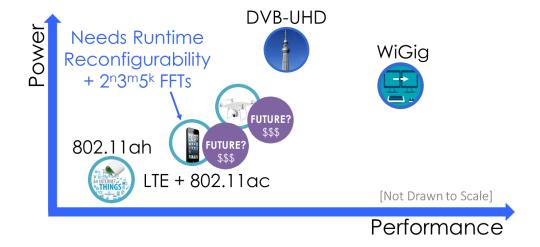

| 1.1<br>1.2 | Seminal FFT papers and applications relying on FFTs. [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

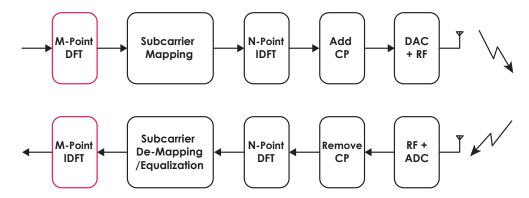

| 1.3        | OFDM transmitter and receiver. The additional DFT/IDFT blocks in pink are required for single-carrier frequency-division multiple access (SC-FDMA), used                                                                                                                                                                                                                                                                                                                                                                                               |        |

| 1.4        | by LTE [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3<br>6 |

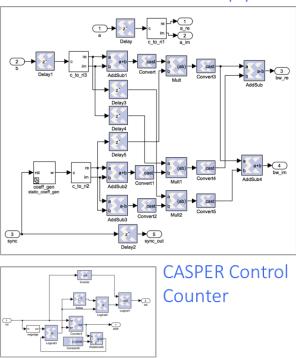

| 1.5        | In the approach highlighted in this thesis, hardware generators consist of a user-facing interface that allows users to input design constraints (e.g., FFT sizes). These constraints are then used by "firmware" to determine optimal hardware allocation. Calculated parameters are fed into a hardware template to generate synthesizable Verilog. A similar mechanism is used to automatically generate tests associated with a parameterized hardware instance. Scientific libraries built for Scala can be directly used at each generator layer | 8      |

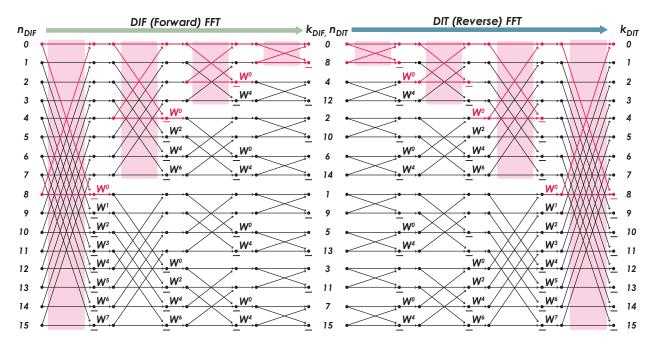

| 2.1        | $N=16$ , radix-2 DIF (a) and DIT (b) CTA signal-flow graphs [34]. One butterfly "group" (containing $N/2^i$ butterflies for the DIF FFT) in each of the four $N/2^{i-1}$ , $i \in [1,4]$ decomposition stages is highlighted. The number of butterfly groups in the <i>i</i> th stage is given by $2^{i-1}$ . Different butterfly groups within the same stage                                                                                                                                                                                         | 10     |

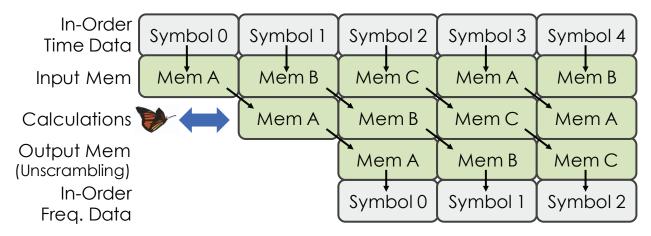

| 2.2        | share the same twiddle factors. Example radix-2 DFT butterflies are in pink $N$ -point DIF FFT memory access timing to support continuous data flow with $3N$ memory. Memories A-C are simultaneously accessed. One symbol contains                                                                                                                                                                                                                                                                                                                    | 12     |

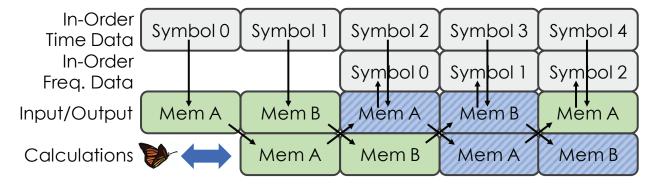

| 2.3        | N data samples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14     |

|            | alternates every $2a$ th cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16     |

| 2.4        | N=16, radix-4 DIF (forward) and DIT (reverse) CTA signal-flow graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17     |

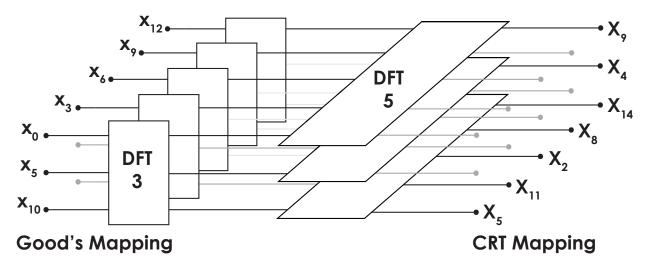

| 2.5        | N = 15 1D-to-2D PFA mapping [35]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22     |

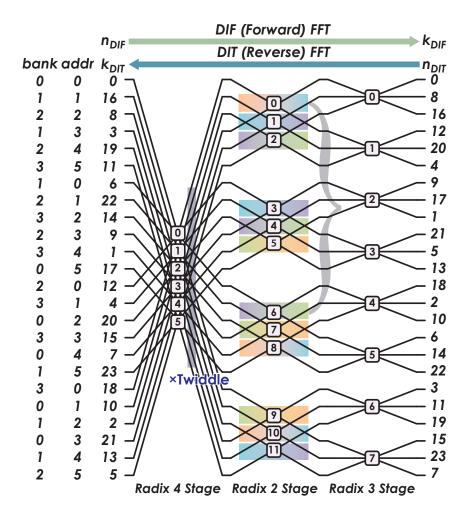

| 2.6        | FFT $N=24$ signal flow graph. Forward and reverse decompositions mirror each other. Calculations can be performed in-place, but $n_{DIF}$ , $k_{DIF}$ input/output orders are scrambled relative to each other. The <i>i</i> th calculation stage requires $N/r_i$ butterfly operations, where $r_i$ is the radix associated with stage <i>i</i> . Colors in the radix-2 stage represent different memory banks needed at each butterfly iteration. As an example, butterflies 0 & 6 use non-conflicting banks. This will |          |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

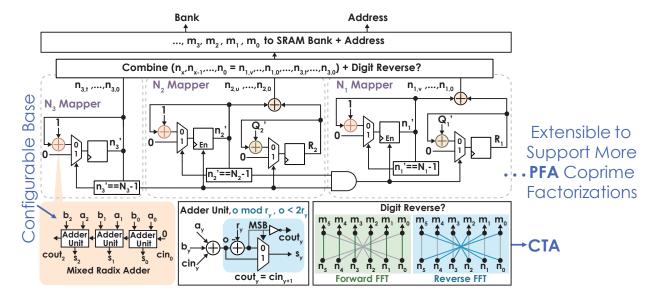

| 2.7        | be described further in Section 2.4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26       |

|            | adders, as required. $n'_2$ increments when $n'_3$ wraps. $n'_1$ increments when $n'_3, n'_2$ wrap. $R_{x<3}$ wraps when the corresponding $n'_x$ increments. The mixed-radix digits of the $N_x$ mapper outputs are combined into one index vector. Banks and                                                                                                                                                                                                                                                            | 20       |

| 0.0        | addresses are obtained from the $n_x$ values via (2.104) and (2.109)                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30       |

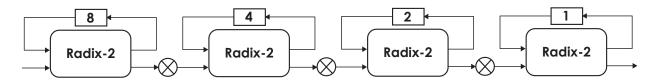

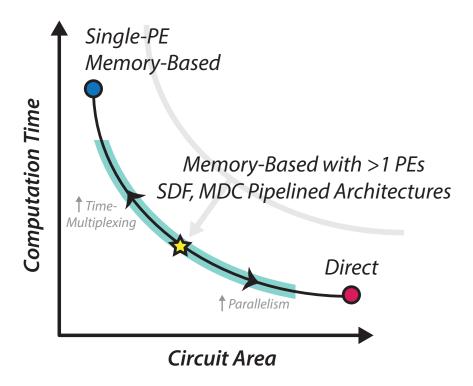

| 2.8<br>2.9 | High-level diagram of a memory-based architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31<br>31 |

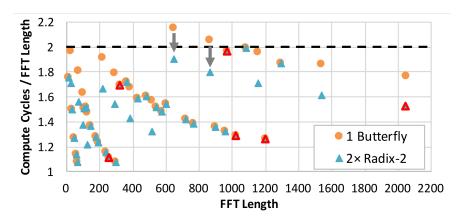

| 2.10       | Area/throughput trade-offs for different FFT architectures. Given a throughput constraint (e.g., continuous data flow), the optimal number of parallel butterflies                                                                                                                                                                                                                                                                                                                                                        | 31       |

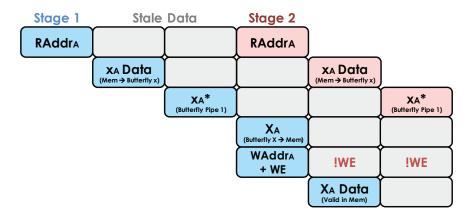

| 2.11       | should be used. However, this complicates conflict-free scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32       |

|            | pipeline delay of one. There is an additional one cycle latency from read address to valid data from the SRAM. Stale data should not be written to memory, necessitating that the write enable be disabled. The SRAM logic is implemented such that if a computation block requires data from an address that is currently being written to, the new data is automatically routed to the output, although                                                                                                                 |          |

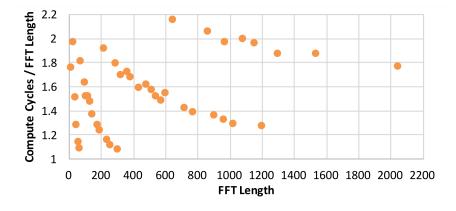

| 2.12       | it takes an extra cycle to actually write to memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33       |

| 2.13       | the number of computation clock cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33       |

|            | for FFT lengths highlighted in red                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34       |

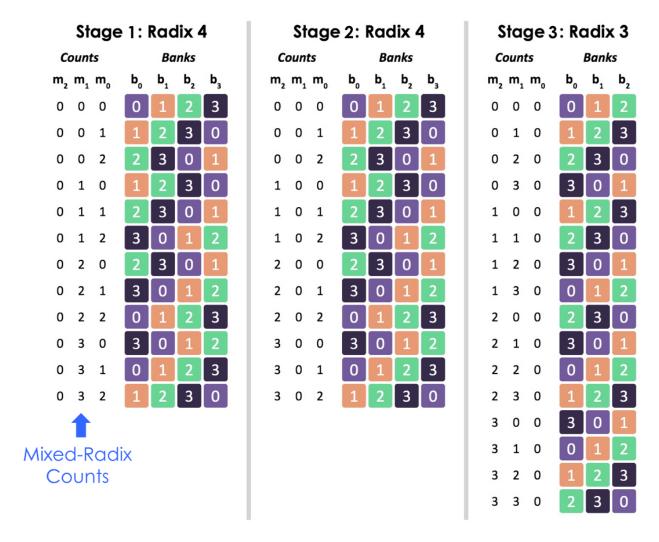

| 2.14       | N=48 calculation scheduling. Banks are individually color-coded to illustrate                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

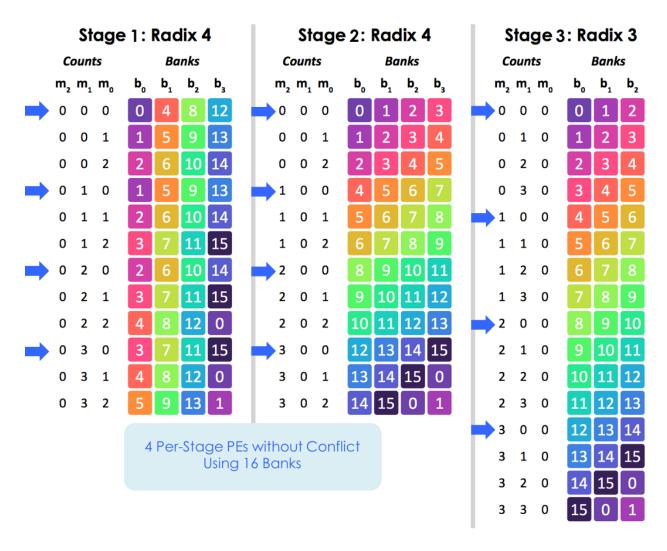

| 2.15       | that, on a per-PE basis, all operands come from different memory banks $N=48$ calculation scheduling so that 4 butterflies can be parallelized. Arrows indicate butterflies that are associated with operands from non-conflicting banks.                                                                                                                                                                                                                                                                                 | 38       |

| 2.16       | These butterflies are not consecutive and need to be re-ordered $N=48$ calculation scheduling so that 4 butterflies can be parallelized, with                                                                                                                                                                                                                                                                                                                                                                             | 39       |

| a - =      | butterfly re-ordering to group conflict-free sets.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40       |

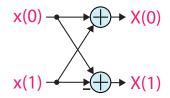

| 2.17       | Radix-2 butterfly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42       |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

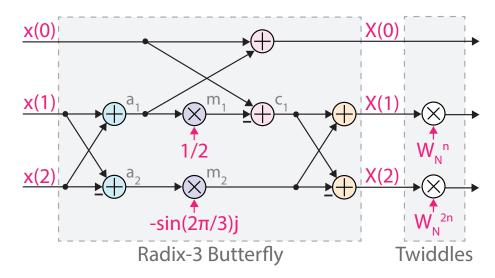

| 2.18 | Radix-3 butterfly with two non-trivial, complex twiddle multiplications at the                       |    |

|------|------------------------------------------------------------------------------------------------------|----|

| 0.40 | output (DIF)                                                                                         | 43 |

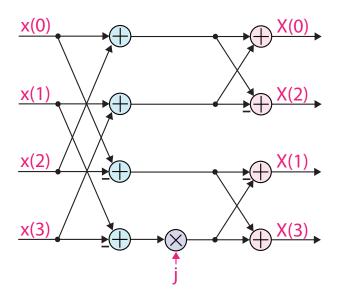

|      | Radix-4 butterfly                                                                                    | 52 |

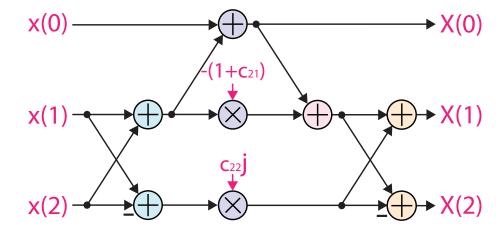

|      | Radix-3 butterfly with rearranged operations for easier integration                                  | 54 |

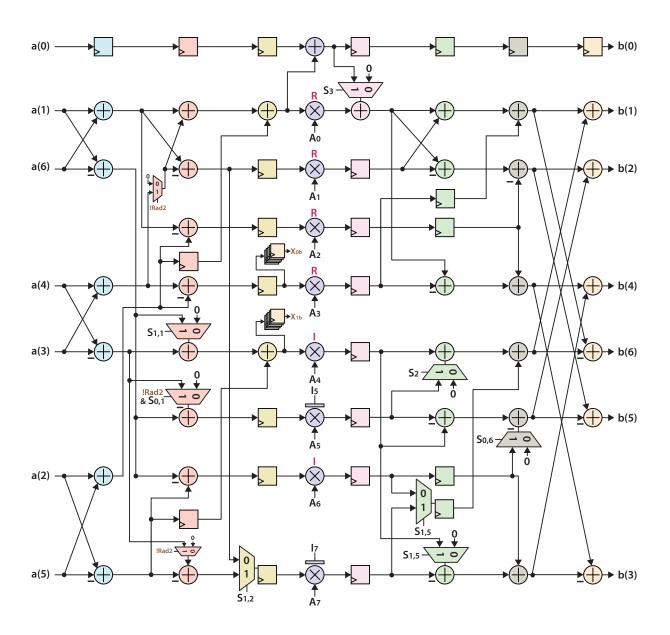

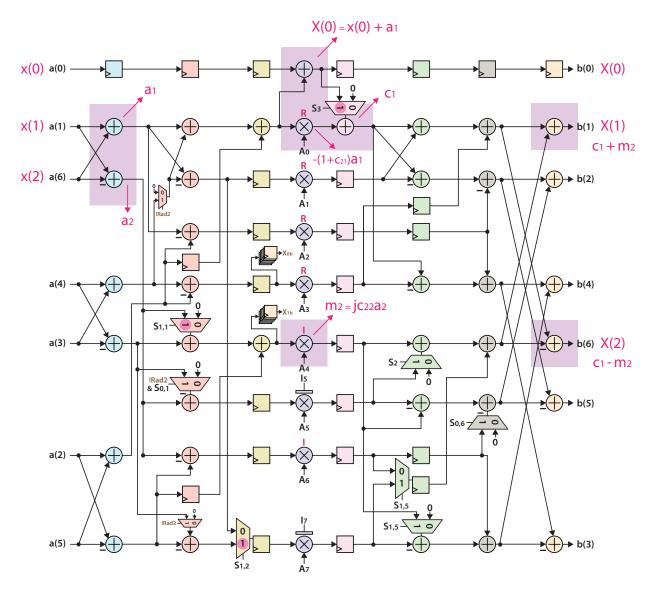

| 2.21 | Reconfigurable radix- $2\times2/3/4/5/7$ butterfly with operator reuse [20], [28]. Con-              |    |

|      | trol signals and outputs in brown are for supporting 2 radix-2 butterflies simul-                    |    |

|      | taneously. Each colored stage can be programmatically pipelined. Two internal                        |    |

|      | multipliers are reconfigured for multiplication by real or imaginary constants de-                   |    |

|      | pending on the current radix. The other multipliers interpret associated constants                   |    |

|      | as real (R) or imaginary (I), without reconfigurability                                              | 55 |

|      | Butterfly configured (at runtime) for radix-3 operation                                              | 57 |

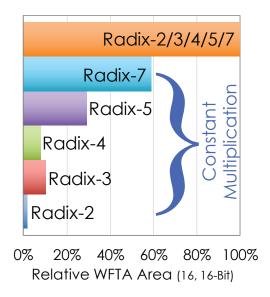

| 2.23 | Relative area of generated butterflies using a 28nm process. Synthesis results were                  |    |

|      | obtained from Design Compiler. Constant multiplication requires fewer resources.                     |    |

|      | Supporting reconfigurability across radix- $2/3/4/5/7$ requires 70% more area than                   |    |

|      | that of a static radix-7 butterfly                                                                   | 58 |

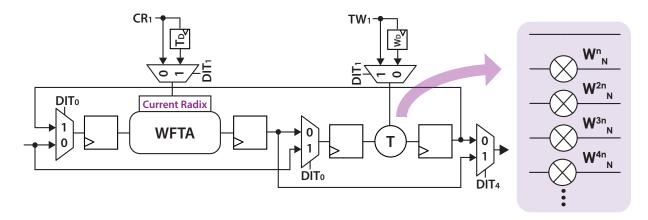

| 2.24 | Reconfigurable processing element for DIF/DIT consisting of a runtime-reconfigurable                 | le |

|      | butterfly and twiddle multipliers. Pipeline delays across the data paths need to                     |    |

|      | be matched in both the DIF and DIT cases                                                             | 59 |

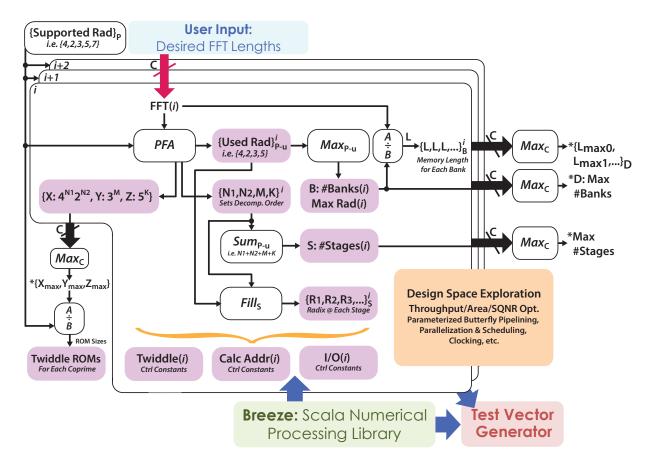

| 2.25 | Firmware component of the FFT generator. It calculates constants for LUT                             |    |

|      | generation as well as optimized hardware parameters. It is also used for test                        |    |

|      | vector generation                                                                                    | 60 |

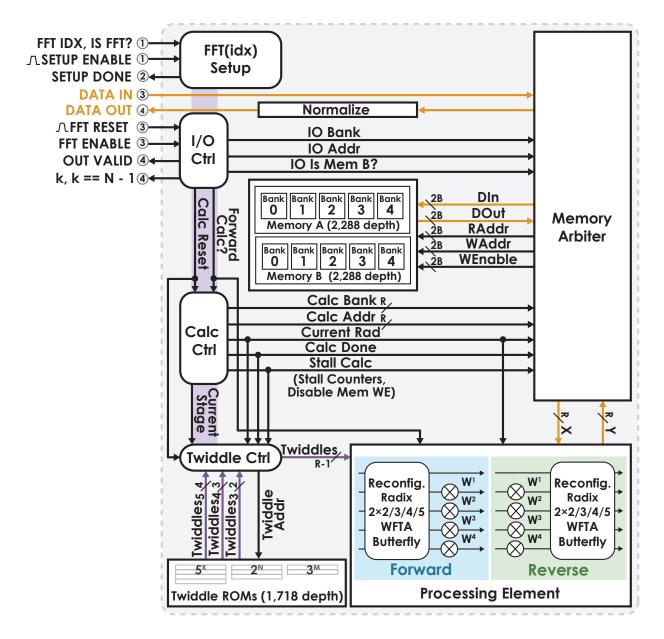

| 2.26 | Hardware template consisting of LUTs for reconfiguration + twiddles and con-                         |    |

|      | figurable blocks controlling data flow between IO, SRAMs, and PE(s). The com-                        |    |

|      | plexity of memory-based designs is primarily in the control logic                                    | 61 |

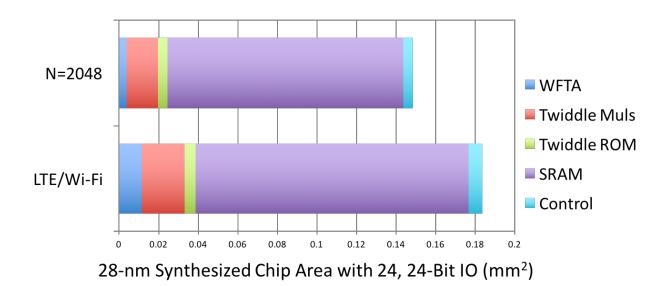

|      | Post-synthesis (cell) area breakdown                                                                 | 62 |

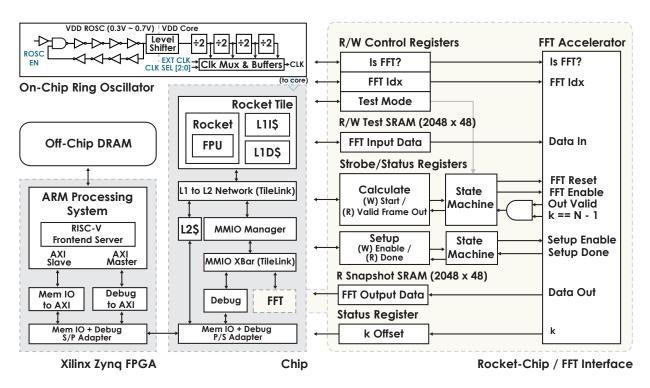

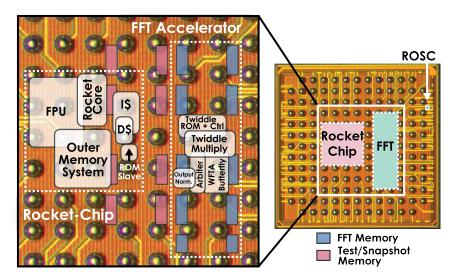

|      | Rocket-Chip + FFT system, with snapshot memory                                                       | 64 |

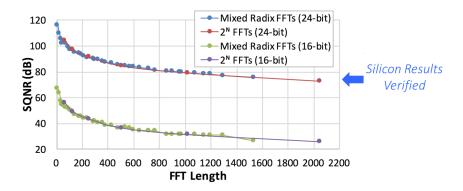

|      | Fixed-point SQNR (vs. floating-point) for different FFT lengths and bitwidths.                       | 65 |

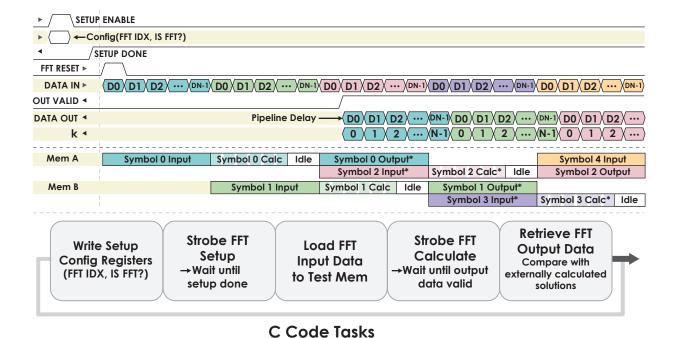

| 2.30 | FFT timing for runtime configuration and continuous input/output, along with                         |    |

|      | the C task sequence for chip verification. Ping-pong memory timing is shown with                     |    |

|      | alternating forward and reverse* decompositions. Calculation idle/stall periods                      |    |

|      | are marked in white                                                                                  | 65 |

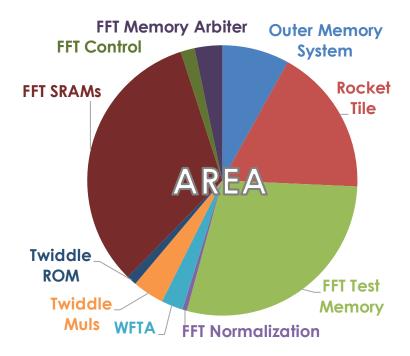

|      | Gate area breakdown (0.24mm <sup>2</sup> total)                                                      | 66 |

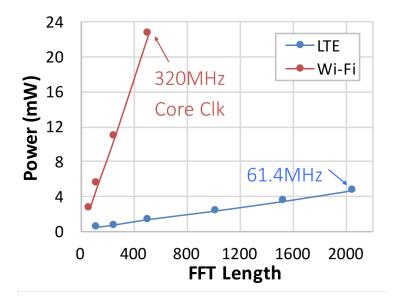

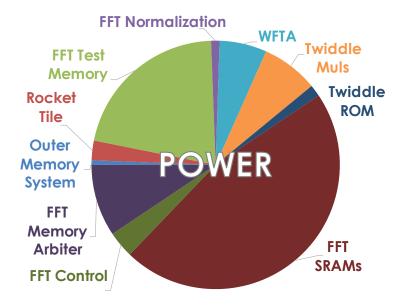

|      | Total (FFT + Rocket) measured power at 570mV for LTE/Wi-Fi                                           | 67 |

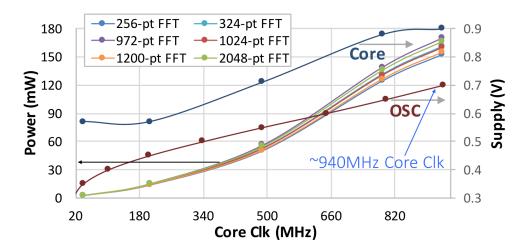

| 2.33 | Total power required for various FFTs and corresponding supply voltages used                         |    |

|      | at different core frequencies (ring oscillator frequency / 8)                                        | 67 |

| 2.34 | Primetime post-synthesis power breakdown for a 2048-point FFT at 520MHz and                          |    |

|      | 0.72V core supply                                                                                    | 68 |

| 2.35 | Die photo. The total active area is 1.28mm <sup>2</sup> . The FFT occupies 0.37mm <sup>2</sup> . The |    |

|      | active area can be significantly smaller with improved floor planning                                | 69 |

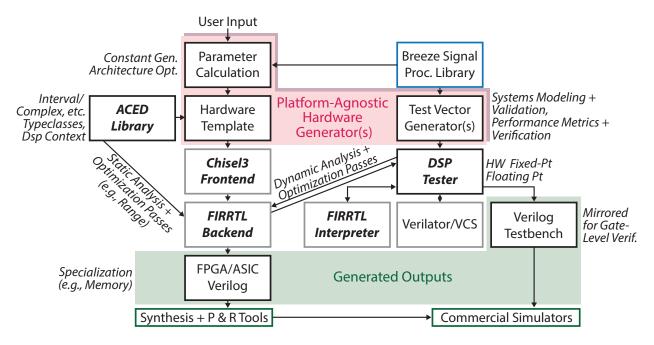

| 3.1  | ACED hardware generator design environment                                                           | 75 |

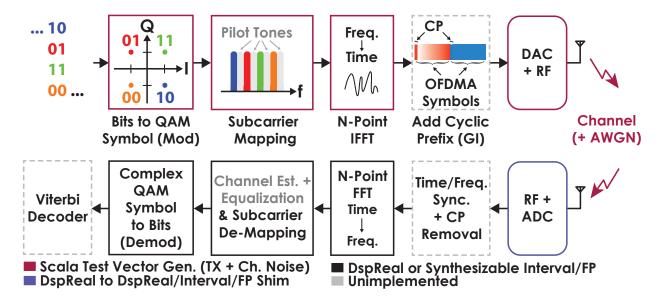

| 3.2  | A system model of an OFDM transmitter/receiver pair with an additive white Gaussian noise channel. At the transmitter, each set of $b$ data bits is represented as a point on a complex $(I/Q)$ constellation diagram and mapped onto a subcarrier |          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | in the frequency domain. The time-domain waveform is cyclically extended to                                                                                                                                                                        |          |

|      | improve robustness against multipath interference and turn the channel response                                                                                                                                                                    |          |

|      | into a cyclic convolution, allowing for single-tap equalization at the receiver. Then                                                                                                                                                              |          |

|      | it is up-converted in the analog domain and transmitted over the antenna. The                                                                                                                                                                      |          |

|      | receiver undoes channel effects and the steps used by the transmitter, corrects                                                                                                                                                                    |          |

|      | for any timing and frequency mismatches between itself and the transmitter, and                                                                                                                                                                    |          |

|      | tries to recover the data from its noise-corrupted input                                                                                                                                                                                           | 80       |

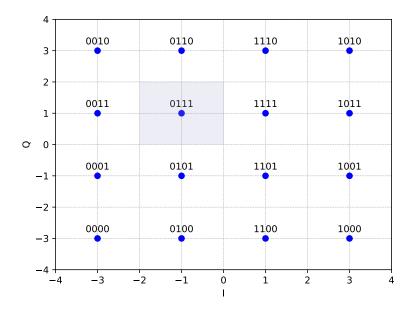

| 3.3  | 16-QAM constellation diagram. A sequence of 4 bits is converted to a complex                                                                                                                                                                       |          |

|      | symbol whose real and imaginary components taken on a value of -3, -1, 1, or 3.                                                                                                                                                                    |          |

|      | Gray codes are used so that adjacent symbols only differ by one bit, reducing bit                                                                                                                                                                  |          |

|      | errors. Upon demodulation, noisy inputs located at regions adjacent to a symbol                                                                                                                                                                    | 01       |

| 9.4  | are mapped to that symbol, e.g., all inputs in the blue box are mapped to 0b0111.                                                                                                                                                                  | 81       |

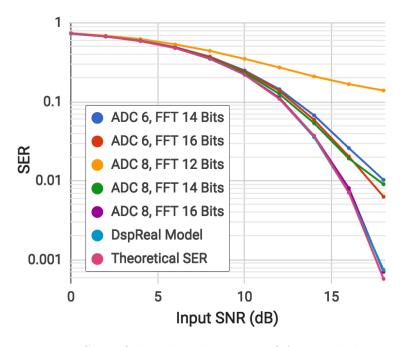

| 3.4  | SER vs. input SNR @ baseband using 16-QAM modulation and an $N = 128$                                                                                                                                                                              |          |

|      | FFT. ADC quantization and FFT output bits are indicated for each I and Q channel. The SER is very sensitive to FFT output bitwidths below 16 bits                                                                                                  | 82       |

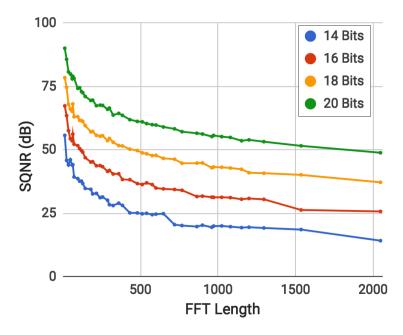

| 3.5  | SQNR vs. FFT length for different output I/Q bitwidths                                                                                                                                                                                             | 82       |

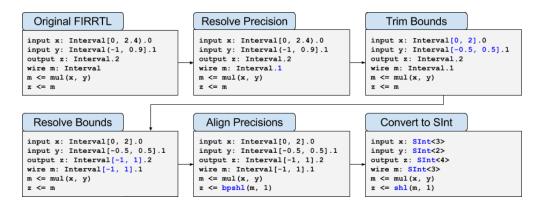

| 3.6  | A demonstration of transformations which infer precisions and bounds of <i>Interval</i>                                                                                                                                                            | 02       |

| 0.0  | circuit elements that are then converted to signed integer types                                                                                                                                                                                   | 85       |

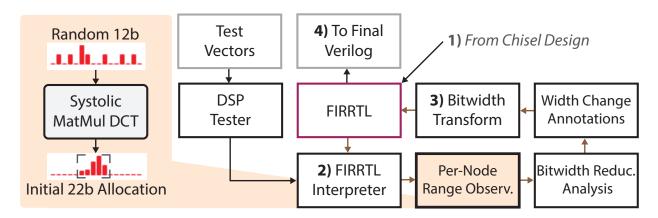

| 3.7  | Bitwidth optimization procedure using the FIRRTL Interpreter for dynamic range                                                                                                                                                                     |          |

|      | analysis. Utilization is reported visually to help build design intuition                                                                                                                                                                          | 85       |

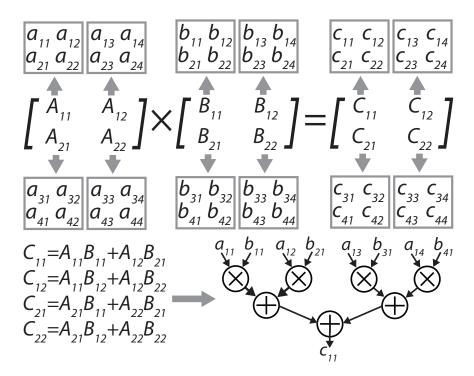

| 3.8  | a) Divide + conquer MatMul. <i>Intervals</i> are automatically propagated                                                                                                                                                                          | 86       |

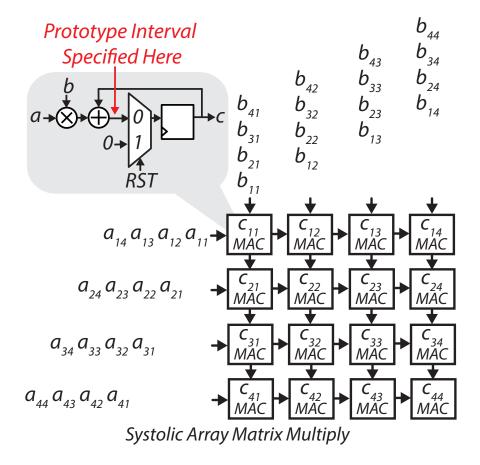

| 3.9  | Systolic array MatMul. Prototype <i>Intervals</i> from loop unrolling must be supplied.                                                                                                                                                            | 87       |

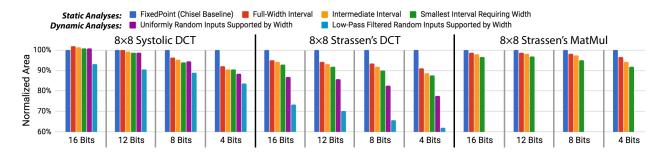

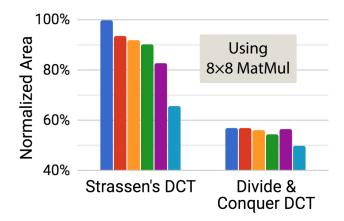

| 3.10 | Area comparison using FixedPoint bitwidth propagation (Chisel baseline) vs.                                                                                                                                                                        |          |

|      | ACED Interval range optimization (with equivalent input bitwidths). Static and                                                                                                                                                                     |          |

|      | dynamic range analyses can automatically reduce area down to 62%, with zero                                                                                                                                                                        |          |

|      | (static) or minimal (dynamic) performance penalties using representative test                                                                                                                                                                      |          |

|      | vectors and input conditions. Constant coefficients are built into DCT-specific                                                                                                                                                                    |          |

|      | MatMul circuits. Area is calculated post-synthesis and includes the cell + esti-                                                                                                                                                                   | 00       |

| 3.11 | mated net area                                                                                                                                                                                                                                     | 88<br>88 |

| 5.11 | Relative areas for 6-bit divide + conquer & Strassen's Matividi DC1s                                                                                                                                                                               | 00       |

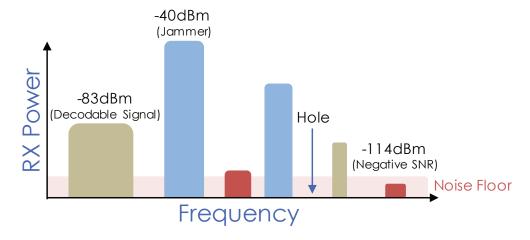

| 4.1  | Cartoon representation of the RF spectrum                                                                                                                                                                                                          | 92       |

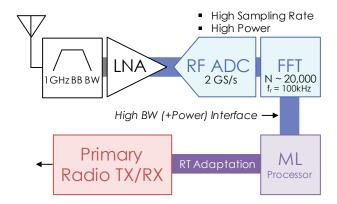

| 4.2  | Nyquist-rate wideband sensing requires a high-sample-rate and, therefore, high-                                                                                                                                                                    |          |

|      | power ADC. Because the $n = 21,600$ FFT (with computational complexity                                                                                                                                                                             |          |

|      | $\mathcal{O}(n \log n)$ ) outputs a significant amount of raw, real-time data, the interface                                                                                                                                                       | റാ       |

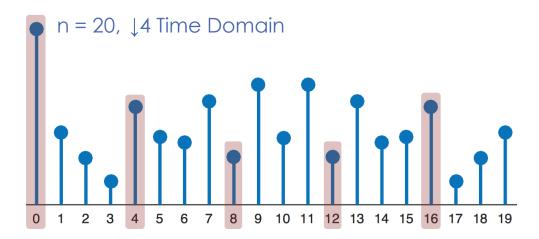

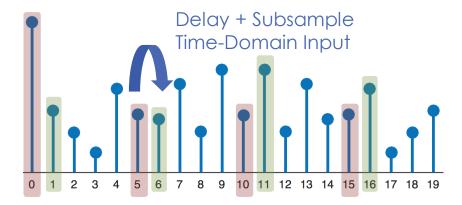

| 4.3  | between it and any subsequent processor must be high bandwidth and high power. $n = 20$ time-domain sequence, subsampled by 4 in pink                                                                                                              | 92<br>94 |

| 1.0  | n = 20 time domain sequence, subsampled by 4 in plant                                                                                                                                                                                              | JŦ       |

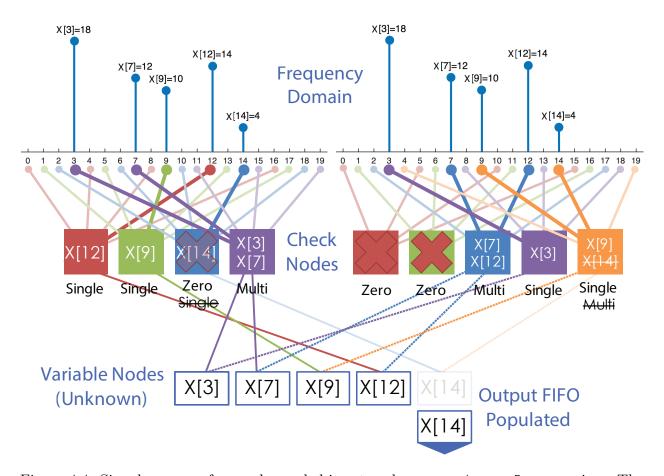

| 4.4  | Signal recovery from subsampled inputs, where $n_1 = 4$ , $n_2 = 5$ are coprime. The $j = 14$ signal recovered from the blue singleton bin in stage 1 is peeled off (i.e., |      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | subtracted) from the associated multiton bin in stage 2 (orange, determined by                                                                                             |      |

|      | $j \equiv a_2 \mod n_2$ , such that the multiton bin becomes a recoverable singleton bin                                                                                   |      |

|      | on the next peeling iteration. Zeroton bins, which can be determined via simple                                                                                            |      |

|      | thresholding, are not included in the graph, because they are already known                                                                                                | 95   |

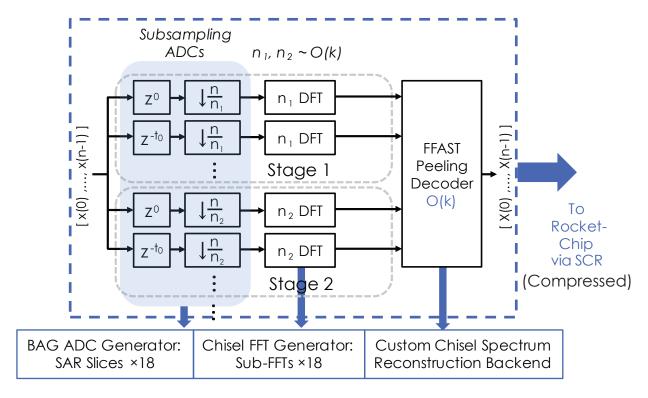

| 4.5  | High-level FFAST architecture, consisting of frontend subsampling, sub-FFTs,                                                                                               |      |

| 4.6  | and a peeling reconstruction backend                                                                                                                                       | 96   |

|      | singletons from multitons                                                                                                                                                  | 97   |

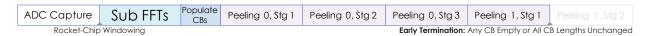

| 4.7  | Signal acquisition and analysis stages                                                                                                                                     | 97   |

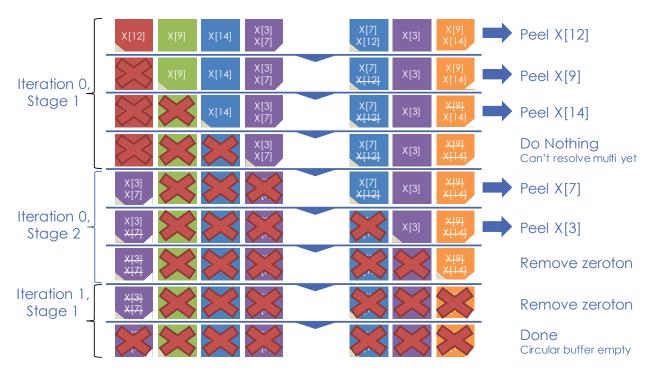

| 4.8  | Peeling using circular buffers. Read pointers (brown) are updated for each $b$ read.                                                                                       |      |

|      | When a zeroton or singleton bin is discovered, b is removed from the corresponding                                                                                         |      |

|      | circular buffer. Write pointers (white) are updated when subsampled bins are                                                                                               |      |

|      | determined to be unresolvable multitons. In such a case, bin $b$ is replaced back                                                                                          |      |

|      | into the circular buffer                                                                                                                                                   | 100  |

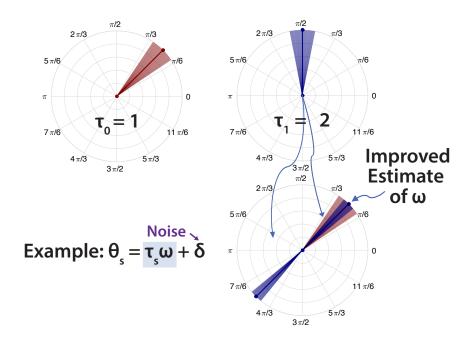

| 4.9  | Successive refinement of the $\omega$ estimate for $\tau_s = 2^s$ [84]                                                                                                     | 103  |

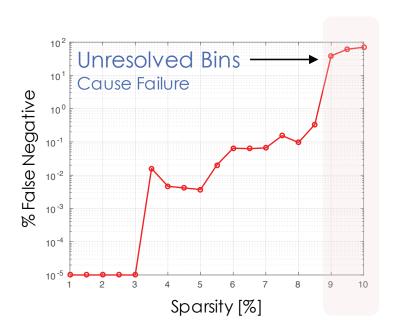

| 4.10 | Percentage of false negatives vs. input sparsity                                                                                                                           | 104  |

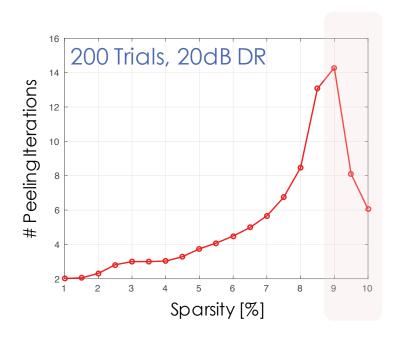

|      | Peeling iterations required to decode the frequency spectrum as a function of                                                                                              |      |

|      | input sparsity                                                                                                                                                             | 104  |

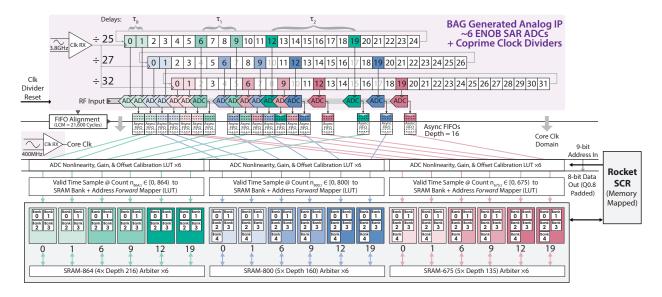

| 4.12 | Analog frontend with shift-register-based clock dividers that generate (non-50%                                                                                            |      |

|      | duty cycle) 151.2MHz, 140MHz, and 118.125MHz subsampling clocks with unit                                                                                                  |      |

|      | delays of 0, 1, 6, 9, 12, and 19 from a 3.78GHz source. Data from associated                                                                                               |      |

|      | 9-wire, < radix-2, SAR ADC slices are time-synchronized and stored in memory                                                                                               |      |

|      | using 8 bits, following capacitor mismatch, offset, and gain correction                                                                                                    | 105  |

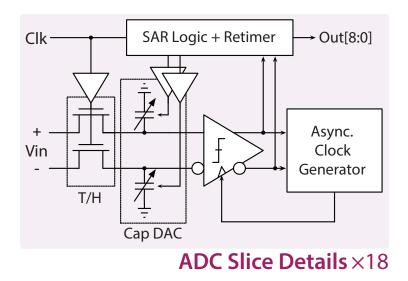

| 4.13 | Asynchronous SAR ADC slice [86]                                                                                                                                            | 106  |

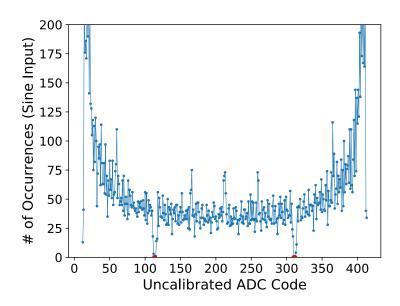

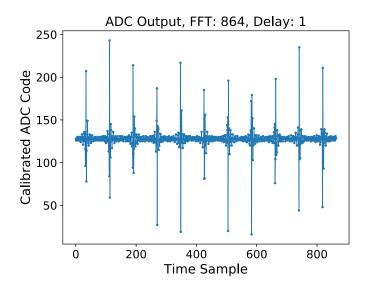

|      | Missing raw ADC output codes due to using < radix-2 for the 3 MSBs                                                                                                         | 106  |

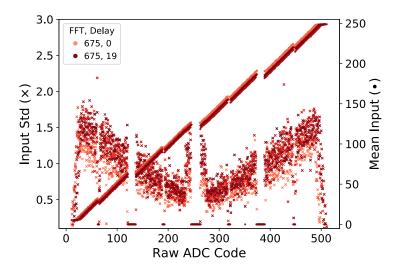

| 4.15 | Fitted input (and its standard deviation) vs. raw ADC code. Missing codes are                                                                                              |      |

|      | due to < radix-2 capacitor weights. Gain and offset mismatches across different                                                                                            |      |

|      | ADC slices are evident. A 0.875MHz sine input and a 3.78GHz input clock were                                                                                               |      |

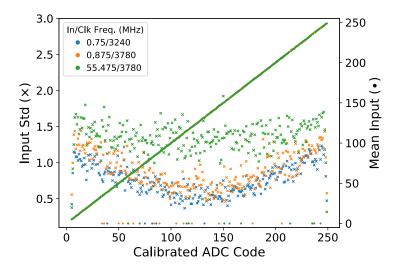

|      | used for calibration.                                                                                                                                                      | 107  |

| 4.16 | Fitted input (and its standard deviation) vs. calibrated ADC code after the LUT.                                                                                           |      |

|      | The post-processed data is 8 bits wide, and missing codes are mostly eliminated.                                                                                           | 107  |

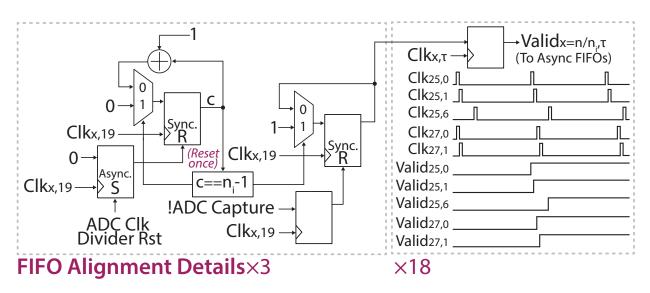

|      | ADC-to-core FIFO alignment circuit (aligned every 21,600 ADC clock cycles).                                                                                                | 108  |

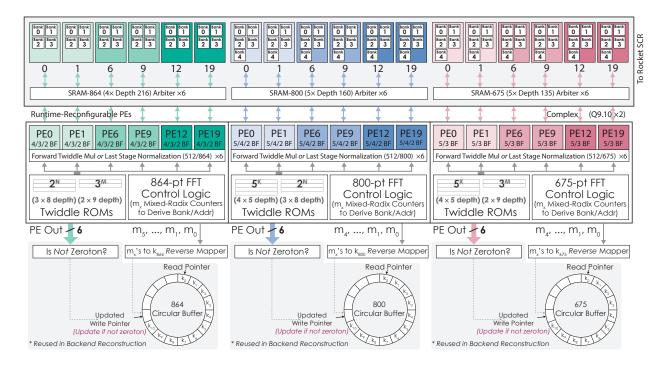

| 4.18 | Sub-FFT DSP blocks with shared control logic and runtime-reconfigurable but-                                                                                               |      |

|      | terflies. Abusing notation, $k_{n_i}$ corresponds to the current sub-FFT bin $b$ , and the                                                                                 | 4.00 |

| 4.10 | $m$ in $k_m$ represents the position that the bin is stored in the circular buffer                                                                                         | 109  |

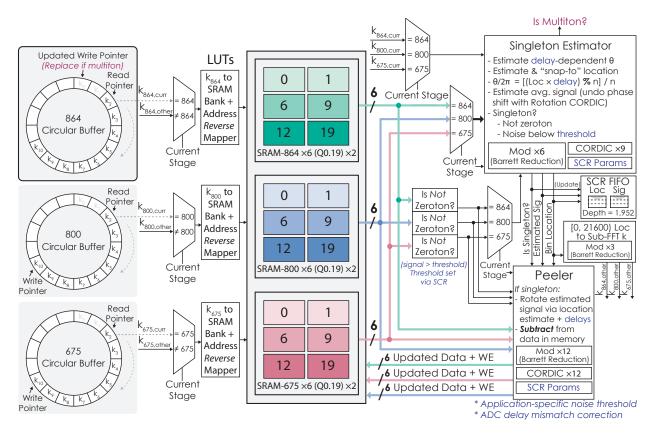

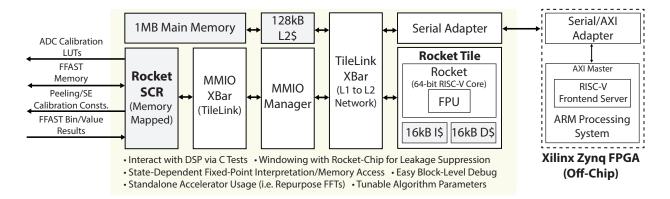

| 4.19 | Peeling reconstruction backend with a singleton estimator. Abusing notation,                                                                                               |      |

|      | $k_{n_i}$ corresponds to the current sub-FFT bin b, and the m in $k_m$ represents the                                                                                      | 110  |

| 4.00 | position that the bin is stored in the circular buffer                                                                                                                     | 110  |

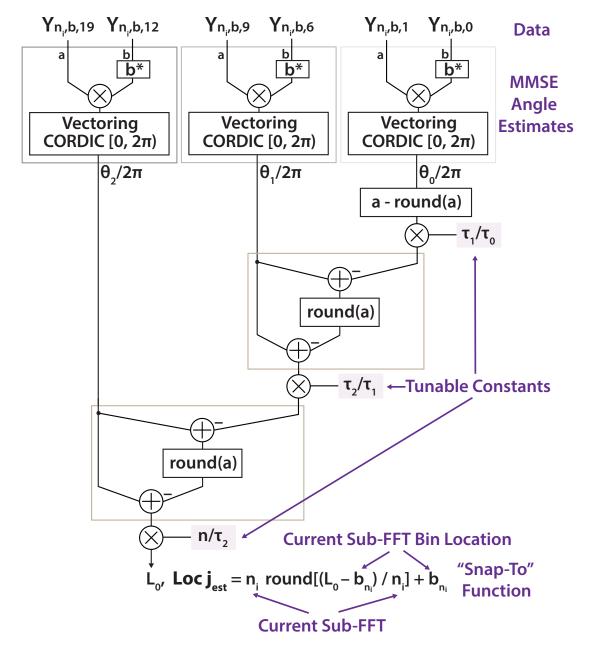

| 4.20 | Successive approximation used to improve the signal location estimate from the                                                                                             | 111  |

|      | angle deltas (obtained via CORDIC [87]) of delayed input samples                                                                                                           | 111  |

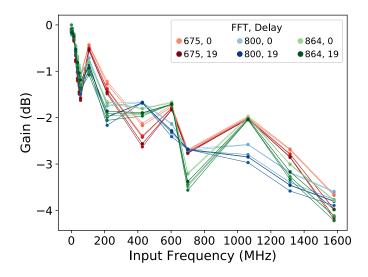

| 4.21 | Gains across different ADC slices and input frequencies @ 3.78GHz ADC input clock. This plot gives a designer perspective on bandwidth mismatch between |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | lanes. Gains are not monotonically decreasing with higher input frequency, since                                                                        |     |

|      | they are not completely determined by the input samplers' bandwidths, and sig-                                                                          |     |

|      | nals above individual subsampling frequencies are folded down                                                                                           | 112 |

| 4 22 | Actual delay offsets across different ADC slices and input frequencies @ 3.78GHz                                                                        | 112 |

| 4.22 | ADC input clock. Delay calibration is required, as DC lane-to-lane skew shifts                                                                          |     |

|      | the delays away from ideal. The analog layout does not need to be optimized to                                                                          |     |

|      | minimize skew, as the amount of skew can be determined after chip fabrication                                                                           |     |

|      | and delay-related control registers used by the singleton estimator can be updated                                                                      |     |

|      | from their nominal values                                                                                                                               | 112 |

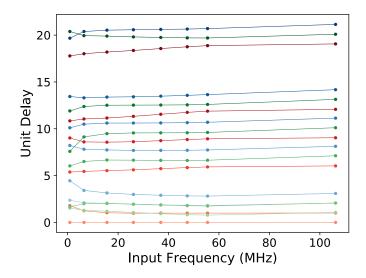

| 4 23 | The Rocket RISC-V processor & Xilinx Zynq FPGA testing setup                                                                                            | 115 |

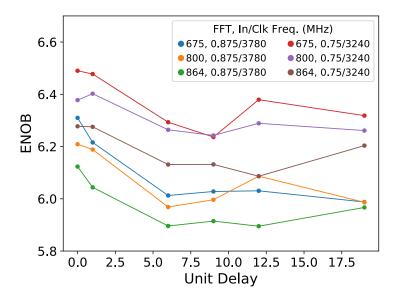

|      | Ideal ENOB comparison between 3.24GHz and 3.78GHz clocks. Unit delays are                                                                               | 110 |

| 1.21 | ideal                                                                                                                                                   | 116 |

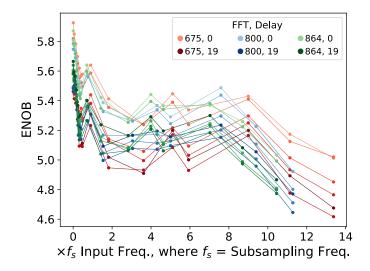

| 4.25 | ENOBs calibrated at different input frequencies (with a 3.78GHz clock) for differ-                                                                      | 11( |

| 1.20 | ent ADC slices. ENOBs are higher at lower delay offsets due to the corresponding                                                                        |     |

|      | ADCs' closer proximity to the voltage reference, resulting in less noise. Phase                                                                         |     |

|      | imbalance is tuned during testing                                                                                                                       | 116 |

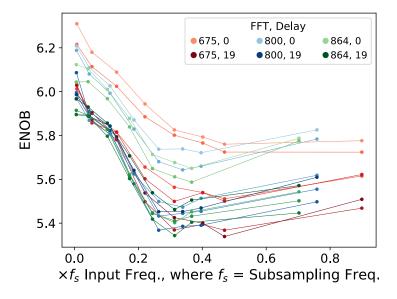

| 4.26 | ENOBs @ 3.78GHz clock using calibration parameters taken with a 0.875MHz                                                                                |     |

|      | input. Phase imbalance was tuned during testing. SNDR is input-frequency                                                                                |     |

|      | dependent and optimized at 0.875MHz                                                                                                                     | 117 |

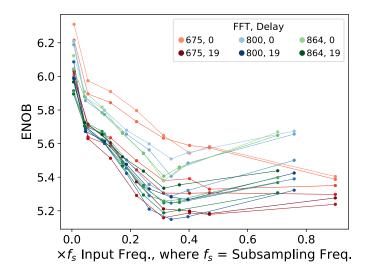

| 4.27 | ENOBs @ 3.78GHz clock using calibration parameters taken with a 15.575MHz                                                                               |     |

|      | input. Phase imbalance was tuned during testing. SNDR is input-frequency                                                                                |     |

|      | dependent and optimized at 15.575MHz                                                                                                                    | 117 |

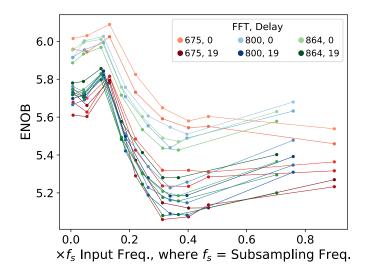

| 4.28 | ENOBs @ 3.78GHz clock using calibration parameters taken with a 0.875MHz                                                                                |     |

|      | input. A balun with $\sim 5^{\circ}$ of phase imbalance is used to measure SNDR at higher                                                               |     |

|      | input frequencies                                                                                                                                       | 118 |

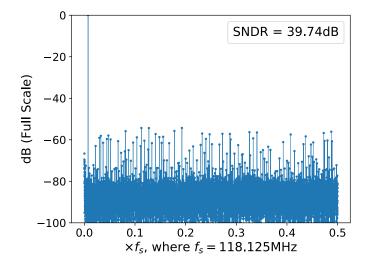

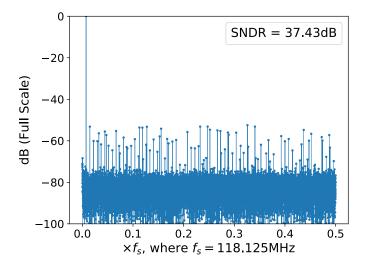

| 4.29 | Frequency spectrum at a sub-ADC output (0.875MHz input). Tuning the differ-                                                                             |     |

|      | ential P and N phase imbalance reduces HD2                                                                                                              | 119 |

| 4.30 | 1 ( 1 )                                                                                                                                                 |     |

|      | the external balun's phase imbalance degrades SNDR                                                                                                      | 119 |

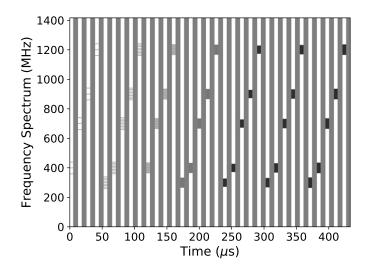

| 4.31 | Recovered spectra over time for 3- to 37-tone (dense) vector signal generator in-                                                                       |     |

|      | puts. The input tones are spread out across an approximately 80MHz bandwidth                                                                            |     |

|      | and have center frequencies ranging from 300MHz to 1.2GHz. Gray vertical re-                                                                            |     |

|      | gions indicate time spent on analysis, when the ADC input is not observed. A                                                                            |     |

| 4.00 | full signal acquisition and analysis cycle takes $13.3\mu s.$                                                                                           | 120 |

| 4.32 | 37 tones (corresponding to 0.35% sparsity) are generated from a vector signal                                                                           |     |

|      | generator, centered at 700MHz, with a 1.925MHz spacing. The time-domain                                                                                 | 101 |

| 4 99 | waveform is subsampled 25× in the stage corresponding to an 864-point FFT.                                                                              | 121 |

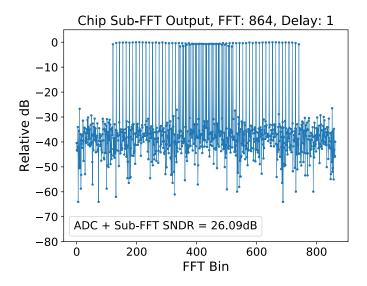

| 4.33 | Subsampled frequency domain result at the output of the 864-point FFT. Tones                                                                            | 101 |

|      | have been folded down to different locations due to subsampling                                                                                         | 121 |

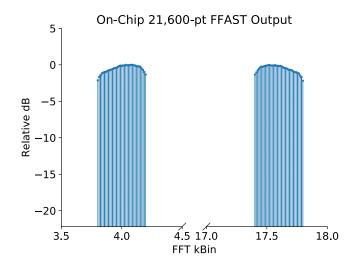

| 4.34 | FFAST is able to reconstruct 100% of the spectrum in $13.3\mu s$ (including signal       |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | capture and analysis). The data is compressed to 0.48%, including 15-bit bin             |     |

|      | locations.                                                                               | 122 |

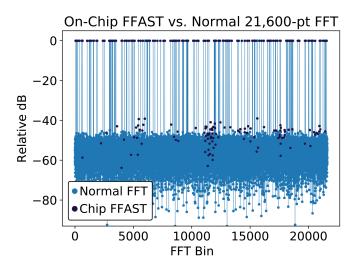

| 4.35 | FFAST vs. normal FFT for C test vectors with 33.5dB SNR and 0.79% sparsity.              |     |

|      | Reconstruction with $0\%$ false negatives and $0.5\%$ false positives                    | 123 |

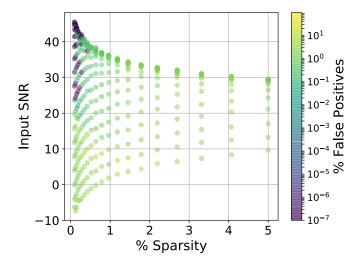

| 4.36 | False positive rates. False positives remain below $5\%$ for sparsities $< 5.0\%$ . With |     |

|      | respect to the number of false positives, FFAST supports input $SNRs > 8.4dB$            |     |

|      | for less populated spectra                                                               | 123 |

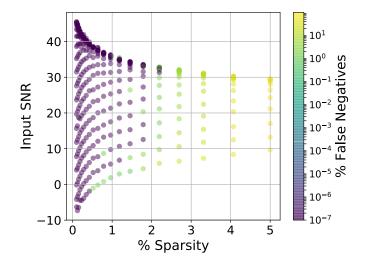

| 4.37 | False negative rates. False negatives (worst case) remain below 5% for sparsities        |     |

|      | < 2.7%. With respect to the number of false negatives, FFAST supports input              |     |

|      | SNRs > 9.7dB for less populated spectra                                                  | 124 |

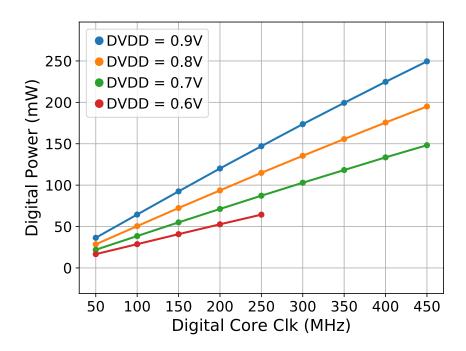

| 4.38 | Power vs. frequency/supply with an FFAST workload                                        | 124 |

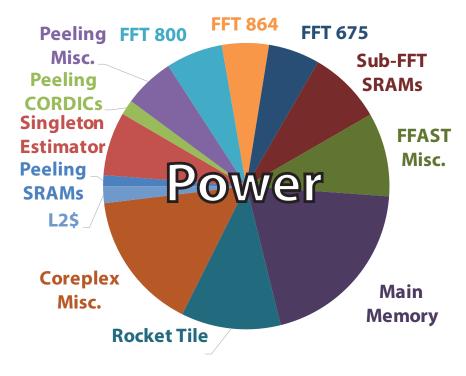

| 4.39 | Post-place-and-route power breakdown simulated with representative test vectors.         | 125 |

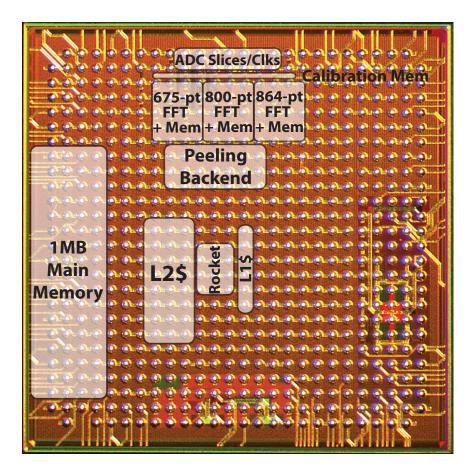

| 4.40 | Die photo                                                                                | 127 |

# List of Tables

| 1.1  | Wi-Fi 802.11ac FFT requirements. The symbol duration is $3.2\mu$ s with an additional 800ng grand interval. FFT computation can be performed across a total |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | tional 800ns guard interval. FFT computation can be performed across a total                                                                                | ç  |

| 1.2  | of $4\mu$ s                                                                                                                                                 | 5  |

| 1.3  | $2^n 3^m 5^k$ FFT sizes required for LTE SC-FDMA precoding                                                                                                  |    |

| 1.4  | Generated FFT configurations from Spiral for fixed $N=2,048.$                                                                                               | 4  |

| 1.5  | Areas of focus for hardware FFT optimizations in recent literature. Genesis2 data is pre-stored in memory. <sup>1</sup>                                     | Ę  |

|      | data is pre-stored in memory.                                                                                                                               | -  |

| 2.1  | n, k index mappings for radix-2 and radix-4 $N=16$ FFTs                                                                                                     | 16 |

| 2.2  | n, k index mappings for radix-2 and radix-4/2 $N=8$ FFTs                                                                                                    | 17 |

| 2.3  | n, k index mappings for $N = 15$ FFTs                                                                                                                       | 22 |

| 2.4  | Comparison of radix-2 memory-based vs. SDF FFTs                                                                                                             | 31 |

| 2.5  | Radix-3 SFG equations. 6 additions and 2 constant multiplications (one imple-                                                                               |    |

|      | mented as a shift operation) are required                                                                                                                   | 42 |

| 2.6  | Radix-3 constants                                                                                                                                           | 43 |

| 2.7  | Primitive roots of $N$ [45]                                                                                                                                 | 45 |

| 2.8  | Factorizations of $x^n - 1$ into irreducible polynomials [48]                                                                                               | 48 |

| 2.9  | Radix-5 SFG equations [51], [52]. 17 additions and 5 constant multiplications                                                                               |    |

|      | (one implemented as a shift operation) are required                                                                                                         | 51 |

|      | Radix-5 constants, where $u = 2\pi/5$ [20]                                                                                                                  | 52 |

| 2.11 | Radix-4 SFG equations [51]. 8 additions and 1 simple constant multiplication are                                                                            |    |

|      | required                                                                                                                                                    | 52 |

| 2.12 | Radix-7 SFG equations [51]. 36 additions and 8 constant multiplications are                                                                                 |    |

|      | required                                                                                                                                                    | 53 |

|      | Radix-7 constants, where $u = 2\pi/7$ [20]                                                                                                                  | 53 |

| 2.14 | Butterfly input/output mappings, i.e., $x_i \to a_j$ and $b_k \to X_l$ . * are required for                                                                 |    |

|      | simultaneous operation of two radix-2 butterflies                                                                                                           | 56 |

| 2.15 | Mux selects used by the reconfigurable butterfly. $I_i$ control signals determine                                                                           |    |

|      | whether multiplication is by an imaginary (1) or real (0) constant. * are required                                                                          |    |

|      | for two radix-2 butterflies                                                                                                                                 | 56 |

| 2.16       | Reconfigurable WFTA multiplication constants. Multiplication by 0, 1, or -1 can be bypassed or replaced with simpler operations                                                                                                                                                                                                                                                                                                         | 56         |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2.17       | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                   | 50         |

|            | I/O unscrambling in [41]                                                                                                                                                                                                                                                                                                                                                                                                                | 63         |

| 2.18       | Resource comparison for reconfigurable LTE/Wi-Fi FFTs. Comparison numbers are taken from [19]. * represents the ratio of calculation to IO clock rates to support continuous data flow. Note that $2N$ is achievable with our generator for                                                                                                                                                                                             |            |

| 0.40       | specific FFT lengths, but for LTE/Wi-Fi, we require $2.23N_{max}$ memory                                                                                                                                                                                                                                                                                                                                                                | 63         |

| 2.19       | Comparison with other LTE-compatible FFTs. $^a$ LTE, $^b$ Wi-Fi, $^c$ including Rocket $+$ snapshot memory, $^d$ unscrambling memory is not reported.                                                                                                                                                                                                                                                                                   | 70         |

| 3.1        | A subset of corresponding constraint expressions for each supported FIRRTL primitive operation. Listed operation arguments are FIRRTL interval-typed expressions $(x, y)$ , a constant integer $C$ , or an unsigned-typed $(UInt)$ expression $u$ . The argument subscripts refer to the lower bound, upper bound, precision, or width of the expression (e.g., $x_l$ , $x_u$ , $x_p$ , or $x_w$ , respectively). Constraint expression | 0.4        |

| 3.2        | sions are: $+, -, *, \max$ , min, and floor Static range optimization times (s) for designs using 16-bit $FixedPoint$ and full-                                                                                                                                                                                                                                                                                                         | 84         |

| 3.3        | width <i>Interval</i> inputs                                                                                                                                                                                                                                                                                                                                                                                                            | 89         |

|            | optimization                                                                                                                                                                                                                                                                                                                                                                                                                            | 89         |

| 4.1<br>4.2 | Fourier relationships                                                                                                                                                                                                                                                                                                                                                                                                                   | 95         |

| 4.3        | 1 0, 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                | 126<br>127 |

## Acknowledgments

First, I would like to thank my advisor and dissertation chair Professor Borivoje Nikolić for his guidance and support during my PhD. He believed in me at times when I had lost confidence in myself, and gave me the encouragement necessary to keep chugging along, in the face of adversity and, sometimes, extremely stressful deadlines. I would also like to thank Professor Vladimir Stojanović and Professor Aaron Parsons for being on my dissertation committee. Professor Parsons agreed with my last-minute request, and Professor Stojanović provided me with valuable guidance when I was proposing my dissertation topic. I'm also grateful to Professor Paul Wright for serving on my qualifying examination committee.

I pivoted midway through my PhD; when I first started, I had intended to become a domain expert in analog/RF, despite knowing full well that digital systems design came to me a lot more naturally. Luckily, Bora had domain expertise in both areas, so transitioning was extremely easy. My dissertation work was motivated by a special topics class on signal processing hardware taught by Bora and Dr. Sriram Sundararajan. Although DSP systems architecture is a fairly mature field, we realized that there is actually much to be done in this space to increase designer productivity and facilitate the development of next-generation wireless systems.

During my PhD, I was able to leverage and adapt the Chisel hardware construction language created by Professor Jonathan Bachrach—who I must also thank for being on my qualifying examination committee—and his students to develop some pretty exciting DSP systems. I'm grateful for the opportunity to collaborate with Adam Izraelevitz (who happens to be amazing at project management—crucial to the success of large projects), Chick Markley, and Paul Rigge on the ACED library for hardware DSP generation in Chisel. More generally, I'm grateful for the feedback I received from Paul, Chris Yarp, and Stephen Twigg (who are walking bodies of DSP/Chisel knowledge) that impacted various design choices and research directions. I had a lot of fun learning about and implementing the FFAST algorithm developed by Professor Kannan Ramchandran's group and am grateful for the various fruitful discussions I was able to have with him and his student, Orhan Ocal. The associated chip required a significant amount of analog (and analog generator) expertise, particularly from students in Elad Alon's group—Jaeduk Han and Zhongkai Wang. I'd like to give a special shout out to Stevo Bailey and Woorham Bae, without whom the FFAST chip would not have gone out in time. In much the same way, I'd like to thank Brian Richards, who worked tirelessly with me to get a 16nm FinFET flow setup at BWRC for the first time. Furthermore, I'd like to thank Howie Mao, James Dunn, Eric Chang, Amy Whitcombe, and David Biancolin for their help in various aspects of the testing process and Nandish Mehta for providing valuable advice on the digital design flow at crazy hours in the morning.

I would like to thank Professor Elad Alon for being the principal investigator on the DARPA CRAFT project and for providing guidance on system architecture. My PhD was funded by the National Science Foundation's Graduate Research Fellowship Program, DARPA through the CRAFT program, and Intel through the Intel Science and Technology Center for Agile Hardware. My research was made possible through the BWRC, ASPIRE,

and ADEPT labs at Berkeley. I would also like to thank Professor Ali Niknejad and his student Nai-Chung Kuo for their advice when I was working on RF frontends. I'm grateful to Bill Dally for his feedback on my work at the ASPIRE retreats. It really helped to keep things in perspective and motivate me to continue.