# UC Irvine UC Irvine Previously Published Works

### Title

A Fully-Integrated  $1\mu W/Channel \mbox{ Dual-Mode Neural Data Acquisition System for Implantable Brain-Machine Interfaces}$

**Permalink** https://escholarship.org/uc/item/3v80093w

### **Authors**

Malekzadeh-Arasteh, Omid Pu, Haoran Danesh, Ahmad Reza <u>et al.</u>

### **Publication Date**

2021-11-01

### DOI

10.1109/embc46164.2021.9630058

### **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>

Peer reviewed

## A Fully-Integrated $1\mu$ W/Channel Dual-Mode Neural Data Acquisition System for Implantable Brain-Machine Interfaces

Omid Malekzadeh-Arasteh<sup>1</sup>, Haoran Pu<sup>1</sup>, Ahmad Reza Danesh<sup>1</sup>, Jeffrey Lim<sup>2</sup>, Po T. Wang<sup>2</sup>, Charles Y. Liu<sup>3</sup>, An H. Do<sup>4</sup>, Zoran Nenadic<sup>2</sup>, and Payam Heydari<sup>1</sup>

Abstract— This paper presents an ultra-low power mixedsignal neural data acquisition (MSN-DAQ) system that enables a novel low-power hybrid-domain neural decoding architecture for implantable brain-machine interfaces with high channel count. Implemented in 180nm CMOS technology, the 32channel custom chip operates at 1V supply voltage and achieves excellent performance including 1.07 $\mu$ W/channel, 2.37/5.62 NEF/PEF and 88dB common-mode rejection ratio (CMRR) with significant back-end power-saving advantage compared to prior works. The fabricated prototype was further evaluated with in-vivo human tests at bedside, and its performance closely follows that of a commercial recording system.

#### I. INTRODUCTION

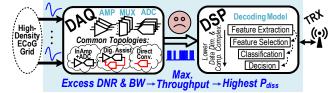

Restoration of neurological functions impaired by spinal cord injury necessitates implantable brain-machine interfaces (BMIs), capable of neural signal acquisition, processing, and wireless connectivity to external base-station and endeffectors. While electrocorticography (ECoG)-based BMIs provide superior signal stability, electrode longevity and spatial resolution/area coverage for accurate decoding of neural activity, the overall power dissipation needs to be minimized to allow prolonged battery life which is a critical aspect of biomedical implants. Existing neural decoding architecture for implantable BMIs is primarily based on conventional power-hungry brain signal acquisition and processing approaches, which are ill-suited for high channelcount systems [1]. Shown in Fig. 1, a standalone data acquisition (DAQ) captures neural signals of varying amplitudes across a wide range of frequencies (near DC up to 1 kHz) and provides digitized samples to a back-end processor for decoding purposes. However, the relevant physiological neural information, such as movement intentions, is typically encoded within a fraction of frequency range (e.g., high- $\gamma$  band) whose content requires significantly less dynamic range and bandwidth compared to the raw neural signal. As such, conventional DAQ is bound to operate with an excess dynamic range and bandwidth that result in an unduly high data throughput, placing a significant power and computing burden on digital signal processor (DSP). Recent works do not address this prominent data-processing power bottleneck for massive channel-count systems, including several neural recording architectures based on capacitively-coupled

Supported by National Science Foundation (Award #1646275)

<sup>1</sup> Dept. of Electrical Engineering and Computer Science, University of California, Irvine (UCI), Irvine, CA 92697, USA {omalekza, haoranp1,ahmadred,payam}@uci.edu

<sup>2</sup> Dept. of Biomedical Engineering, UCI, Irvine, CA 92697, USA {limj4,ptwang,znenadic}@uci.edu

<sup>3</sup> Dept. of Neurological Surgery, University of Southern California, Los Angeles, CA 90033 cliu@usc.edu

<sup>4</sup> Dept. of Neurology, UCI, Irvine, CA 92697, USA and@uci.edu

Existing Neural Decoding Architecture for Implantable BMIs

Low-Power Hybrid-Domain Neural Decoding Arch. for Implantable BMIs

Fig. 1. Conventional and proposed neural decoding architectures for high channel-count implantable brain-machine interfaces.

InAmp+ADC [2], DC-coupled digitally-assisted amplifier [3] and direct conversion (time-based [4], delta-sigma [5]) schemes.

Inspired by our work in [6], the proposed mixed-signal neural DAQ (MSN-DAQ) enables a novel low-power hybriddomain neural decoding architecture for implantable BMIs by adopting dual-mode acquisition that is intended for distinct use in training and decoding procedures, with the latter accounting for the majority of operation time. In training mode, raw neural signals are collected by MSN-DAQ during a set of clinical trials and transmitted to an external basestation where decoder training takes place offline [7], [8]. While training helps improve decoding accuracy and provides a means of calibration and validation, it primarily involves data collection with increased bit-resolution and sampling rate, further justifying the dual-mode acquisition. Once the decoder's performance is optimized, identified features and their corresponding weights are computed in a lookup table to be transferred to DSP and subsequently applied to the channel-specific programmable weights on MSN-DAQ, marking the transition to decoding mode. Similar to [6], feature extraction is performed in analog domain using the stored weights, which facilitates the digitization with minimum required bit-resolution and sampling rate. Hence, the DSP power dissipation is significantly relaxed. Furthermore, no computationally-expensive algorithm needs to be executed on DSP for decoding in this proposed framework, and therefore, the back-end's complexity overhead remains relatively low with increasing number of channels, a highly desired attribute for real-time operation in implantable BMIs with multiple functionalities.

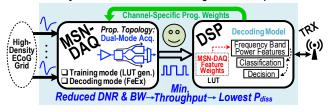

Fig. 2. System architecture of the mixed-signal neural data acquisition (MSN-DAQ) chip and a micrograph of its fabricated prototype.

The rest of this paper is organized as follows: Section II describes the proposed MSN-DAQ system and its circuit implementation. Experimental results including electrical and in-vivo measurements are presented in Section III, followed by concluding remarks in Section IV.

#### II. PROPOSED MIXED-SIGNAL NEURAL DAQ

Fig. 2 shows the top-level system block diagram of MSN-DAQ. The main modules include a 32-element dualmode front-end array with register banks to store channelspecific programmable weights, mixed-signal back-end consisting dual-mode multiplexer (DM-MUX), programmable gain amplifiers (PGAs), analog-to-digital converters (ADCs) with distinct bit-resolution and bandwidth requirements for training and decoding modes, and a digital core. Other onchip blocks include serial peripheral interface (SPI), bias circuitry for global current generation, digitally-controlled ultra-low-level current banks and analog/digital input-output (I/O) modules.

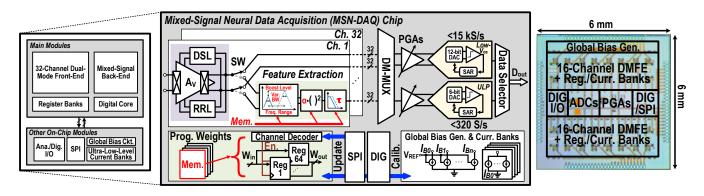

#### A. Dual-Mode Front-End and Analog Interface Circuits

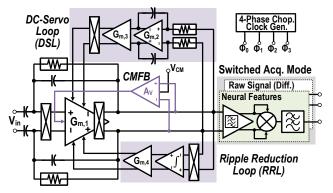

The dual-mode front-end includes a newly-added lownoise, folded-cascode chopper-stabilized amplifier array. Shown in Fig. 3 is the closed-loop amplifier incorporating two auxiliary loops across the output and folding nodes: (a) DC servo loop to further attenuate low-frequency signals and minimize the output offset, and (b) ripple reduction loop to minimize chopping ripples introduced by up-modulated voltage offset of the input stage,  $G_{m,1}$ . Given that the chopping mechanism eliminates the mismatch effect of transistors, high common-mode rejection ratio (CMRR) can be achieved. To further improve CMRR, input capacitors were adequately sized to reduce mismatch and the common-mode to commonmode attenuation was notably increased by using an inputinjecting common-mode feedback (CMFB) network, which remarkably improves the source impedance by an additional loop gain factor.

Depending on acquisition mode, raw neural signal or extracted neural features are time-multiplexed and further amplified by the respective PGA. Since raw signals contain higher dynamic range and bandwidth, the required settling time prior to digitization is significantly shortened. A higher unity gain-bandwidth product required in training mode is achieved by increasing the transconductance, resulting in higher power consumption in this mode. Conversely, neural

Fig. 3. Schematic details of dual-mode front-end, incorporating DC-servo loop, ripple reduction loop and common-mode feedback.

features do not suffer from this problem, and thus, the PGA consumes significantly less power in decoding mode.

#### B. Successive Approximation Register ADCs

To meet the stringent power requirements of neural data acquisition, successive approximation register (SAR) ADC is chosen. Shown in Fig. 4, the differential 12-bit SAR-ADC includes a V<sub>CM</sub>-based binary-weighted capacitive digital-toanalog converter (DAC) array, a multi-stage offset-canceling comparator and a compact modular non-redundant SAR logic and control with minimum circuit overhead. The digitization begins with top-plate sampling of the amplified differential input signal, followed by the energy-efficient bit-cycling that is accomplished by  $V_{CM}$ -based switching scheme. To satisfy the required resolution, a combination of circuit and layout techniques have been utilized. Most notably, the comparator employs three-stage pre-amplification with output offset cancellation (OOS) to minimize the input-referred voltage offset and the kickback noise introduced by the regenerative latch. Moreover, twisted differential signaling is applied between the DAC and the comparator to suppress common-mode noise (Fig. 4). To implement the SAR algorithm, a compact modular digital circuity based on non-redundant logic is used. Illustrated in Fig. 4, the entire SAR logic consists of only 12 MUXed D-flipflops and 11 OR gates. Moreover, a unique control circuitry (shaded in light blue) - consisting of only 1 D-flipflop, 1 inverter and 2 AND gates for each bit - is implemented to accommodate the  $V_{CM}$ -based switching procedure. The working principle is as follows: Initially, each D-flipflop in the control circuitry is reset by  $CK_{S/H}$  during

Fig. 4. Schematic details of SAR-ADC, highlighting the digital logic and control circuitry for  $V_{CM}$ -based capacitive DAC.

the sample and hold operation. Thus, all  $S_3$  switches are enabled in the capacitive DAC, connecting the bottom plate of each capacitor to the common-mode voltage  $(V_{cm})$ . Next, SAR logic produces a leftward-propagating pulse that is sequentially captured by each stage in the shift register. Each in-between interval lasts for one clock period of  $CK_{SAR}$ and represents a comparison window. During each interval, one bit is resolved at a time and the result is stored in the corresponding MUXed D-flipflop. Starting with the most significant bit, the direction of binary search is determined by the stored value at the end of each comparison window. Given the inherent sequential operation of SAR algorithm within comparison windows, each control D-flipflop detects the transition instances and generate the necessary control signals by a simple combinational circuit. Depending on the outcome, the appropriate DAC switch  $(S_1 \text{ or } S_2)$  is activated at the beginning of each comparison window immediately after  $S_3$  is turned off. The detection and control signal generation continue until all bits have been resolved, and a new conversion takes place.

#### **III. EXPERIMENTAL RESULTS**

#### A. Electrical Measurements

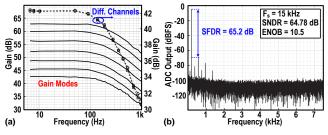

MSN-DAQ chip achieves a measured 42.5-dB minimum closed-loop gain, 1.03  $\mu V_{rms}$  input-referred noise (2-200 Hz), 2.37 noise efficiency factor (NEF), 5.62 power efficiency factor (PEF) at 1V supply voltage, and 88-dB average CMRR for a maximum 10mVpp interference within 50-160 Hz range. Fig. 5(a) shows the measured frequency response of MSN-DAQ across 3 neighboring channels and different gain modes for one channel. Based on measured FFT of the 12-bit SAR-ADC output for 193.17-Hz tone (i.e., upper edge of the frequency band) at maximum sampling rate of 15kHz, the ENOB, SFDR, and SNDR are 10.5, 65.2 dB, 64.78 dB, respectively, as depicted in Fig. 5(b).

#### B. Biomedical testing and in-vivo measurements

To further validate MSN-DAQ operation within a clinical context, neural recordings were carried out on an epileptic patient with implanted ECoG grids. The study was approved by the Institutional Review Board of the Rancho Los Amigos National Rehabilitation Center and the University of

Fig. 5. (a) MSN-DAQ measured frequency response and (b) ADC measured output power spectrum.

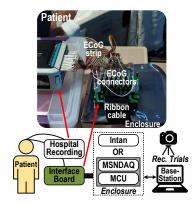

Fig. 6. Hospital experiment setup, including the custom chip (MSN-DAQ) and commercial system (Intan).

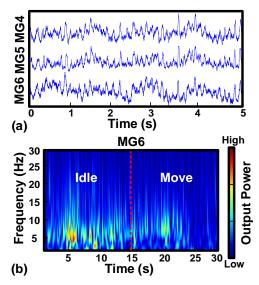

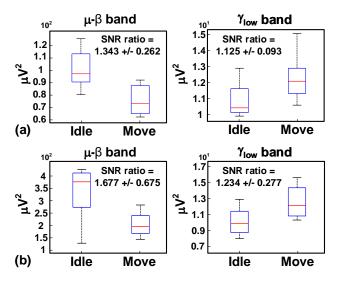

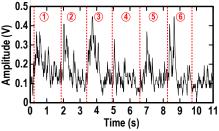

California, Irvine. Fig. 6 illustrates the experiment setup with connections between the implanted ECoG girds and the recording systems, including hospital clinical acquisition (i.e., Natus® Quantum<sup>TM</sup>) and MSN-DAQ placed in a shielding enclosure. A similar setup was reproduced for the commercial Intan recording system (RHD2000), substituting Intan for MSN-DAQ to allow comparison with the custom chip. The raw neural data were acquired from 32 anteriorly placed electrodes over M1 (MG1-32) for ten 14-second idle periods and ten 14-seconds move periods during a hip flexion task. Fig. 7(a) shows a sample of acquired timeseries data from three electrodes over the motor leg area that exhibited behavioral modulation. Fig. 7(b) show the spectrogram demonstrating  $\mu$ - $\beta$  power modulations for a pair of idle/move trials. After further statistical analysis of all the recorded trials, the power for idle and move states within each frequency band were plotted for both MSN-DAQ and Intan recording systems - as depicted in Fig. 8 which exhibit similar distinguishable difference. Given that placement of ECoG grid was dictated by the patient's clinical needs, the highly-localized gamma activity correlated to hip flexion appeared to be less prominent, particularly for high- $\gamma$ band which did not attain the expected distinguishable SNR range that have been previously observed in our prior works. Thus, the extracted high- $\gamma$  features in decoding mode did not contain meaningful information regarding idle/move states. Nevertheless, to validate the operation in decoding mode, ECoG data containing high- $\gamma$  modulations from previous hospital experiments were fed to MSN-DAO by a highresolution waveform generator. The extracted power envelope from an ECoG channel exhibiting high- $\gamma$  modulation in response to an upper extremity movement task is shown in Fig. 9.

Fig. 7. (a) ECoG time-series sample data from motor grid (MG) electrodes and (b) spectrogram of raw ECoG from MG6, acquired by MSN-DAQ.

Fig. 8. Box plots showing signal-to-noise power ratio (SNR) between idle and move states from (a) MSN-DAQ and (b) Intan recording system.

#### IV. CONCLUSION

A dual-mode mixed-signal neural data acquisition was presented. The 180nm CMOS chip enables a novel lowpower hybrid-domain neural decoding architecture for implantable brain-machine interfaces that could achieve significant power-saving in high-channel count systems. In addition to electrical measurements, the prototype has been validated in a hospital setting with real-time human ECoG recording. A comparison with the most relevant prior works in Table I shows that the proposed MSN-DAQ achieves excellent CMRR and noise performance at lowest power consumption per channel.

#### ACKNOWLEDGMENT

The authors would like to thank Tower Semiconductor for chip fabrication and Rhode & Schwarz and Keysight Technologies for providing measurement equipment.

Fig. 9. Extracted high- $\gamma$  features in decoding mode, exhibiting power modulations during six consecutive elbow flexion and extension periods.

TABLE I Performance Comparison

|                     | JSSC'15<br>[3] | TBCAS'18<br>[9] | JSSC'19<br>[4] | TBCAS'20<br>[10] | This<br>Work |

|---------------------|----------------|-----------------|----------------|------------------|--------------|

| Tech. (nm)          | 65             | 180             | 180            | 65               | 180          |

| Supply (V)          | 0.5            | 1.8             | 1.2            | 0.5, 2.5         | 1            |

| Channel             | 64             | 16              | 4              | 64               | 32           |

| Power/Ch. $(\mu W)$ | 2.3            | 3.26            | 3.9            | 2.98             | 1.07         |

| BW (Hz)             | 1-500          | 0.59-117        | 200            | 1-1k             | 2-200        |

| IRN $(\mu V_{rms})$ | 1.23           | 2.02            | 1.3            | 1.66             | 1.03         |

| NEF                 | 3.7            | 3.36            | 4.9            | 2.21             | 2.37         |

| PEF                 | 6.9            | 20.32           | 28.81          | -                | 5.62         |

| CMRR (dB)           | 88             | 67.1            | >75            | 76               | 88           |

| ADC Res.            | 15             | 10              | -              | 16               | 12           |

| ENOB                | -              | 7.8             | 13.2           | 15.7             | 10.5         |

#### REFERENCES

- [1] N. Even-Chen, D. G. Muratore, S. D. Stavisky, L. R. Hochberg, J. M. Henderson, B. Murmann, and K. V. Shenoy, "Power-saving design opportunities for wireless intracortical brain-computer interfaces," *Nature Biomedical Engineering*, vol. 4, pp. 984–996, 2020.

- [2] D. Han, Y. Zheng, R. Rajkumar, G. S. Dawe, and M. Je, "A 0.45 V 100-channel neural-recording IC with sub-μw/channel consumption in 0.18μm CMOS," *IEEE Trans. Biomed. Circuits Syst.*, vol. 7, pp. 735– 746, 2013.

- [3] R. Muller, S. Gambini, and J. M. Rabaey, "A 0.013 mm<sup>2</sup>, 5 μW, dccoupled neural signal acquisition IC with 0.5 V supply," *IEEE J. Solid-State Circuits*, vol. 47, pp. 232–243, 2011.

- [4] H. Jeon, J.-S. Bang, Y. Jung, I. Choi, and M. Je, "A high DR, dccoupled, time-based neural-recording IC with degeneration R-DAC for bidirectional neural interface," *IEEE J. Solid-State Circuits*, vol. 54, no. 10, pp. 2658–2670, 2019.

- [5] H. Chandrakumar and D. Marković, "A 15.2-ENOB 5-kHz BW 4.5-μW chopped CT ΔΣ-adc for artifact-tolerant neural recording front ends," *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3470–3483, 2018.

- [6] O. Malekzadeh-Arasteh, H. Pu, J. Lim, C. Y. Liu, A. H. Do, Z. Nenadic, and P. Heydari, "An energy-efficient CMOS dual-mode array architecture for high-density ECoG-based brain-machine interfaces," *IEEE Trans. Biomed. Circuits Syst.*, vol. 14, no. 2, pp. 332–342, 2020.

- [7] P. T. Wang, E. Camacho, M. Wang, Y. Li, S. J. Shaw, M. Armacost, H. Gong, D. Kramer, B. Lee, R. A. Andersen *et al.*, "A benchtop system to assess the feasibility of a fully independent and implantable brainmachine interface," *J. Neural Eng.*, vol. 16, no. 6, p. 066043, 2019.

- [8] P. T. Wang, C. E. King, C. M. McCrimmon, J. J. Lin, M. Sazgar, F. P. Hsu, S. J. Shaw, D. E. Millet, L. A. Chui, C. Y. Liu *et al.*, "Comparison of decoding resolution of standard and high-density electrocorticogram electrodes," *J. Neural Eng*, vol. 13, no. 2, p. 026016, 2016.

- [9] C.-Y. Wu, C.-H. Cheng, and Z.-X. Chen, "A 16-channel CMOS chopper-stabilized analog front-end ECoG acquisition circuit for a closed-loop epileptic seizure control system," *IEEE Trans. Biomed. Circuits Syst.*, vol. 12, no. 3, pp. 543–553, 2018.

- [10] J. P. Uehlin, W. A. Smith, V. R. Pamula, S. I. Perlmutter, J. C. Rudell, and V. S. Sathe, "A 0.0023 mm<sup>2</sup>/ch. delta-encoded, time-division multiplexed mixed-signal ECoG recording architecture with stimulus artifact suppression," *IEEE Trans. Biomed. Circuits Syst.*, vol. 14, no. 2, pp. 319–331, 2020.