# UC Irvine UC Irvine Electronic Theses and Dissertations

## Title

Cost-Efficient Approximate Log Multipliers for Convolutional Neural Networks

Permalink https://escholarship.org/uc/item/3w4980x3

**Author** Kim, Min Soo

Publication Date 2020

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA, IRVINE

Cost-Efficient Approximate Log Multipliers for Convolutional Neural Networks

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Electrical and Computer Engineering

by

Min Soo Kim

Dissertation Committee: Professor Nader Bagherzadeh, Chair Professor Jean-Luc Gaudiot Professor Rainer Dömer

$\bigodot$  2020 Min Soo Kim

# DEDICATION

To my lovely wife and daughter, Bora and Grace

# TABLE OF CONTENTS

|        |         |                                                                                                             | Page    |

|--------|---------|-------------------------------------------------------------------------------------------------------------|---------|

| LIST ( | OF FIG  | GURES                                                                                                       | v       |

| LIST ( | OF TA   | BLES                                                                                                        | vii     |

| LIST ( | OF AL   | GORITHMS                                                                                                    | viii    |

| ACKN   | [OWL]   | EDGMENTS                                                                                                    | ix      |

| VITA   |         |                                                                                                             | x       |

| ABST   | RACT    | OF THE DISSERTATION                                                                                         | xii     |

| Chapte | er 1: I | ntroduction                                                                                                 | 1       |

|        |         | Design of Cost-Efficient Approximate Log Multipliers                                                        | 6       |

| 2.1    |         | ell Log Multiplier                                                                                          |         |

|        | 2.1.1   | Mitchell's Algorithm                                                                                        |         |

|        | 2.1.2   | Proposed Design                                                                                             |         |

|        | 2.1.3   | Implementation Complexity                                                                                   |         |

|        | 2.1.4   | Synthesis Results                                                                                           |         |

| 2.2    |         | ated Mitchell Log Multiplier, Mitch- $w$                                                                    |         |

|        | 2.2.1   | Proposed Design                                                                                             |         |

|        | 2.2.2   | Error Study of Truncation                                                                                   |         |

|        | 2.2.3   | Handling Negative Numbers with One's Complement (C1)                                                        |         |

|        | 2.2.4   | Error Study of C1 Sign Handling                                                                             |         |

|        | 2.2.5   | Making Mitch- $w$ Unbiased $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |         |

|        | 2.2.6   | Synthesis Results                                                                                           |         |

|        | 2.2.7   | Cost Comparison against Bfloat16                                                                            |         |

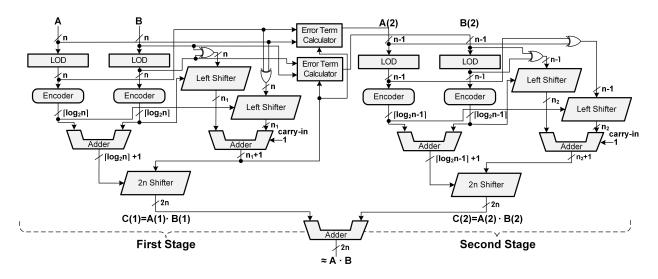

| 2.3    |         | ated Iterative Log Multiplier                                                                               |         |

|        | 2.3.1   | Preliminaries                                                                                               |         |

|        | 2.3.2   | Proposed Design                                                                                             |         |

|        | 2.3.3   | Error Study                                                                                                 | . 45    |

|        | 2.3.4   | Synthesis Results                                                                                           | . 45    |

| Chapto |         | Effects of Approximate Multiplication on Convolutional Neura<br>Networks                                    | l<br>48 |

| 3.1     | Introduction to Convolutional Neural Networks                      |                  |  |  |  |  |  |  |  |

|---------|--------------------------------------------------------------------|------------------|--|--|--|--|--|--|--|

| 3.2     | Approximate Multiplication for CNN Inferences                      |                  |  |  |  |  |  |  |  |

| 3.3     | Related Works                                                      |                  |  |  |  |  |  |  |  |

| 3.4     | Accumulated Error in Convolution and Fully Connected Layers 57     |                  |  |  |  |  |  |  |  |

| 3.5     | Effects of Batch Normalization on Very Deep Neural Networks        | 63               |  |  |  |  |  |  |  |

| 3.6     | Experiments with Simple Networks                                   | 65               |  |  |  |  |  |  |  |

|         | 3.6.1 Setup                                                        | 65               |  |  |  |  |  |  |  |

|         | 3.6.2 Network Dependency of Quantization                           | 67               |  |  |  |  |  |  |  |

|         | 3.6.3 Impact on CNN Performance                                    | 71               |  |  |  |  |  |  |  |

|         | 3.6.4 Evaluation of the Truncation Parameter                       | 77               |  |  |  |  |  |  |  |

|         | 3.6.5 Evaluation of the Unbiased Designs                           | 77               |  |  |  |  |  |  |  |

|         | 3.6.6 Evaluation of the C1 Sign Handling                           | 79               |  |  |  |  |  |  |  |

|         | 3.6.7 Comparison against Other Approximate Multipliers on CNNs     | 81               |  |  |  |  |  |  |  |

|         | 3.6.8 Verification with More Images                                | 84               |  |  |  |  |  |  |  |

| 3.7     | Experiments with Very Deep Neural Networks                         | 85               |  |  |  |  |  |  |  |

|         | 3.7.1 Setup                                                        | 86               |  |  |  |  |  |  |  |

|         | 3.7.2 Impact on CNN Performance and Variance of Accumulated Error  | 87               |  |  |  |  |  |  |  |

|         | 3.7.3 Effects of Batch Normalization                               | 90               |  |  |  |  |  |  |  |

| Chapte  | er 4: Integrating Approximate Multipliers into an FPGA Accelerator | 93               |  |  |  |  |  |  |  |

| 4.1     | Design of the Convolutional Core                                   | 94               |  |  |  |  |  |  |  |

| 4.2     | Reduced Mitchell Log Multiplier                                    |                  |  |  |  |  |  |  |  |

| 4.3     | Experimental Results                                               | 97               |  |  |  |  |  |  |  |

| Chapte  | Chapter 5: Conclusions 99                                          |                  |  |  |  |  |  |  |  |

| Bibliog | graphy                                                             | Bibliography 101 |  |  |  |  |  |  |  |

# LIST OF FIGURES

## Page

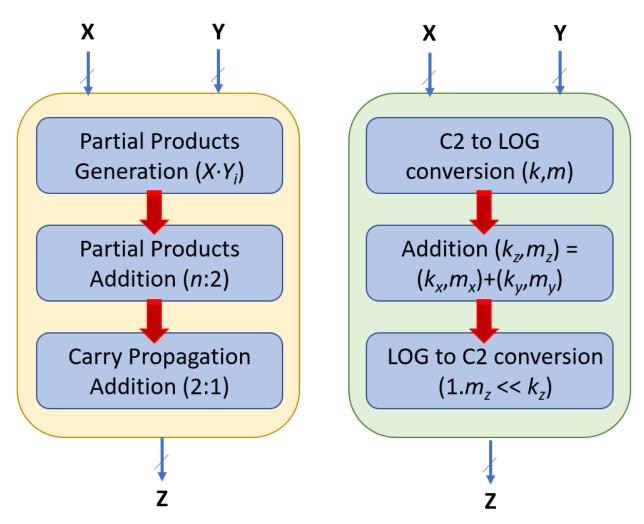

| 1.1  | Difference between (a) the conventional fixed-point multiplication and (b) the approximate log multiplication.                                                        | 4   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

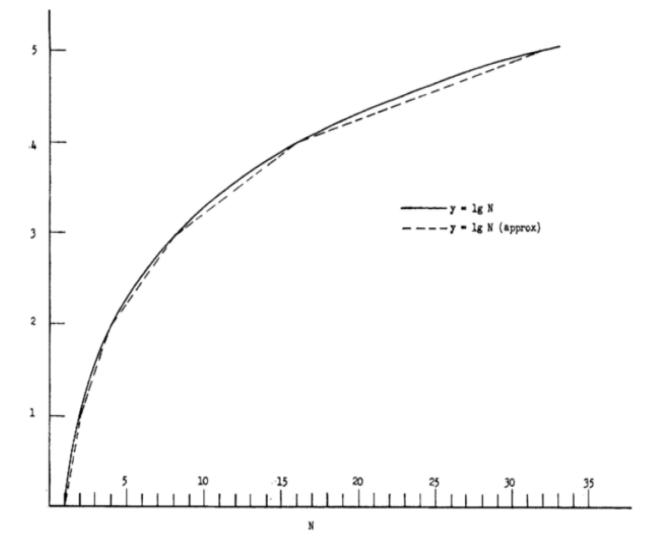

| 2.1  | Approximate logarithm from Mitchell's Algorithm, compared against logarithm                                                                                           | 8   |

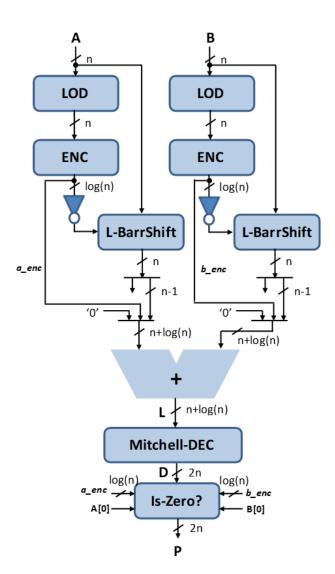

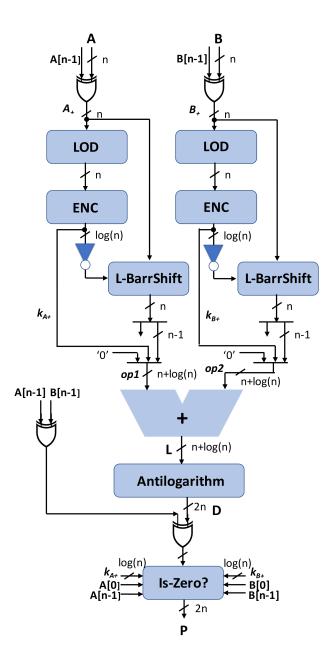

| 2.2  | Mitchell Logarithmic Multiplier according to Algorithm 1                                                                                                              | 10  |

| 2.3  | 4-bit leading one detector                                                                                                                                            | 12  |

| 2.4  | Mitchell Decoder                                                                                                                                                      | 13  |

| 2.5  | Is-Zero block structure: performs both zero detection and correct result generation                                                                                   | 15  |

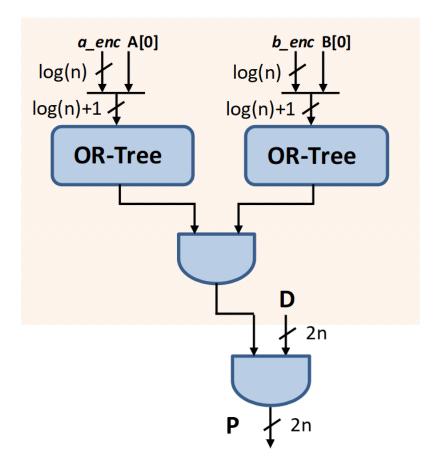

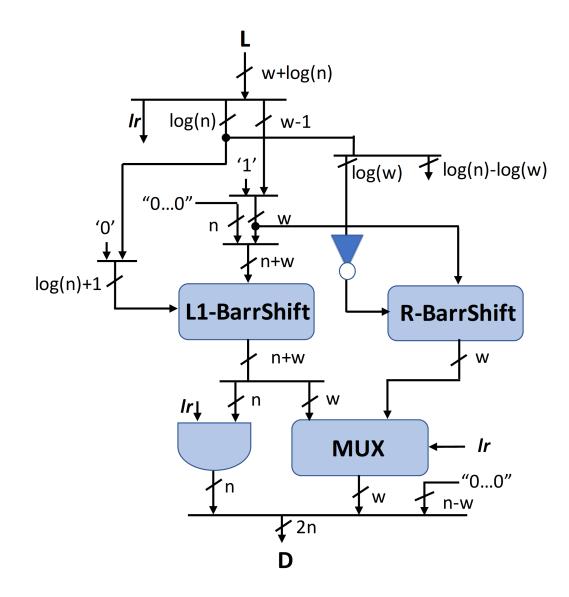

| 2.6  | Truncated Mitchell Log Multiplier, Mitch- $w$                                                                                                                         | 19  |

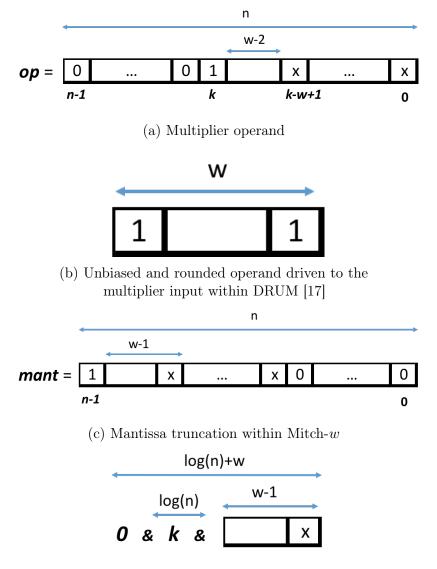

| 2.7  | Operands truncation methods                                                                                                                                           | 21  |

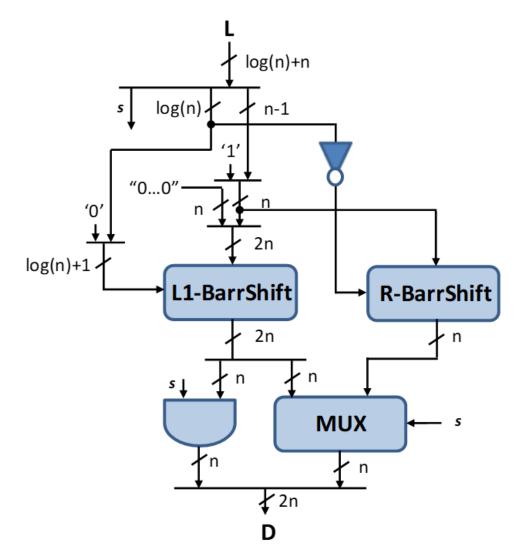

| 2.8  | Customizable Antilogarithm block                                                                                                                                      | 22  |

| 2.9  | Mitch- $w$ with C1 negative number handling $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                 | 27  |

| 2.10 | Structure of the proposed two-stage logarithmic multiplier                                                                                                            | 44  |

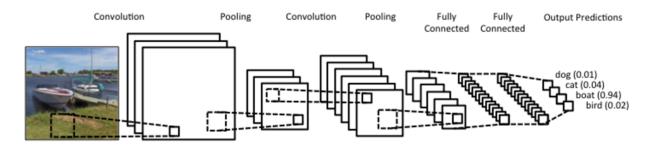

| 3.1  | An example of a simple CNN                                                                                                                                            | 49  |

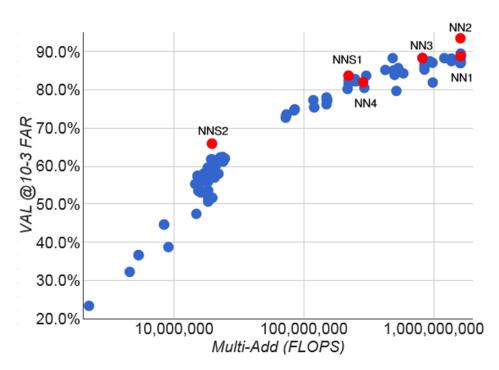

| 3.2  | The correlation between the accuracy and size of CNNs [59] $\ldots \ldots \ldots$                                                                                     | 49  |

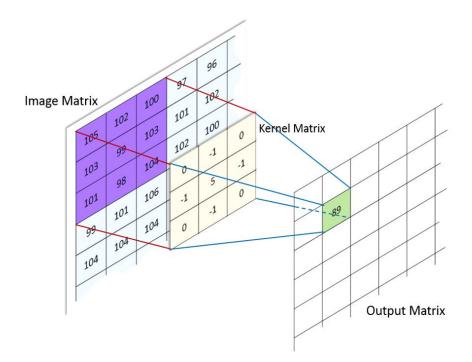

| 3.3  | An example of convolution operation                                                                                                                                   | 50  |

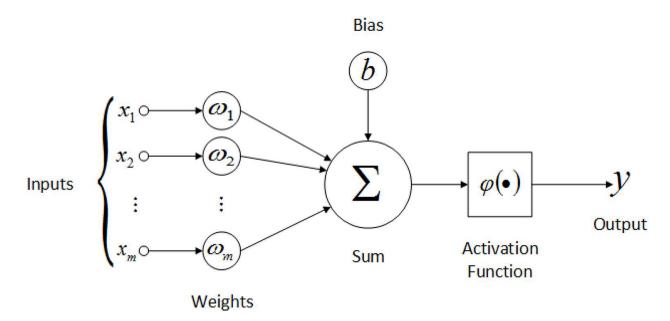

| 3.4  | A neuron in a fully connected layer                                                                                                                                   | 51  |

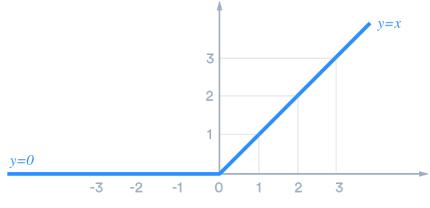

| 3.5  | ReLU activation                                                                                                                                                       | 52  |

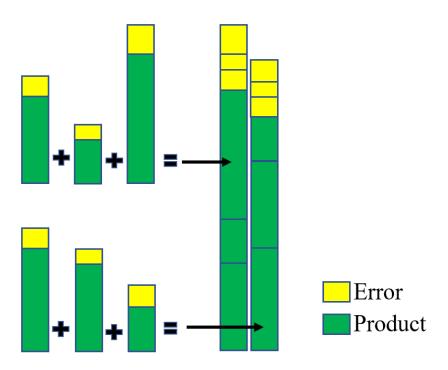

| 3.6  | The accumulation of many products with varying amount of error converges                                                                                              |     |

|      | the combined errors to a mean value.                                                                                                                                  | 59  |

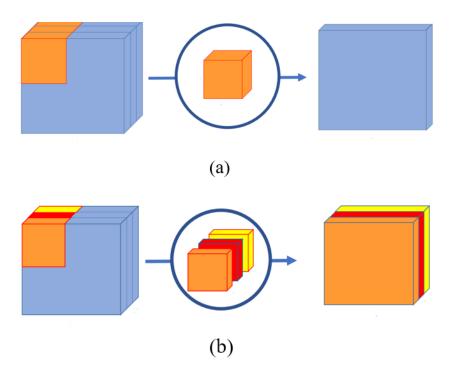

| 3.7  | (a) Conventional Convolution (b) Depthwise Convolution                                                                                                                | 61  |

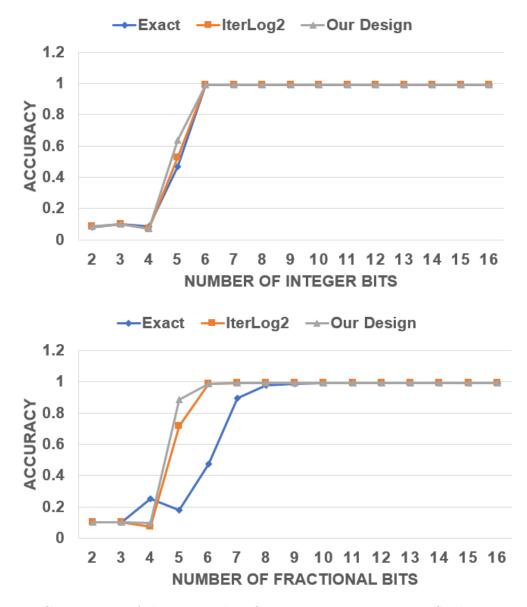

| 3.8  | Comparison of the Top-1 classification accuracies on MNIST between the                                                                                                | 0.0 |

| 2.0  | multipliers, with varying number of integer and fractional fixed-point bits.                                                                                          | 69  |

| 3.9  | Comparison of the Top-1 classification accuracies on CIFAR-10 between the                                                                                             | -   |

| 0.10 | multipliers, with varying number of integer and fractional fixed-point bits.                                                                                          | 70  |

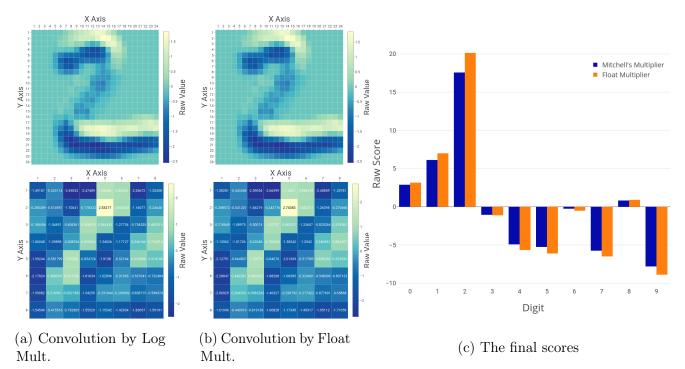

| 3.10 | The convolution outputs and the final raw scores of a sample inference from                                                                                           | 70  |

| 0.11 | LeNet                                                                                                                                                                 | 72  |

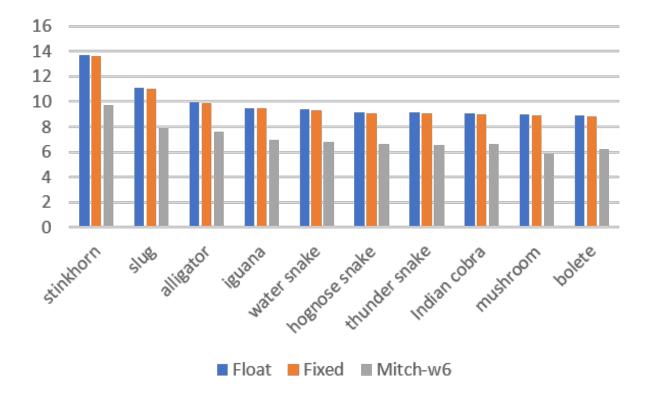

| 3.11 | Top 10 scores of a sample AlexNet inference, sorted by the highest floating-point                                                                                     | 7 4 |

| 0 10 | raw scores                                                                                                                                                            | 74  |

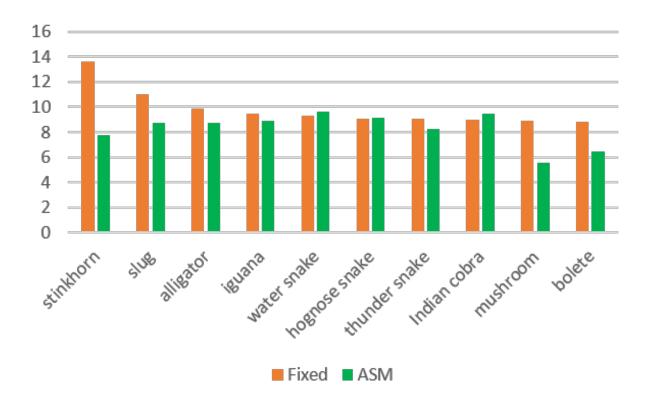

| 3.12 | The final raw scores of the sample inference from AlexNet with the ASM                                                                                                | 70  |

| 0 10 | multiplier                                                                                                                                                            | 76  |

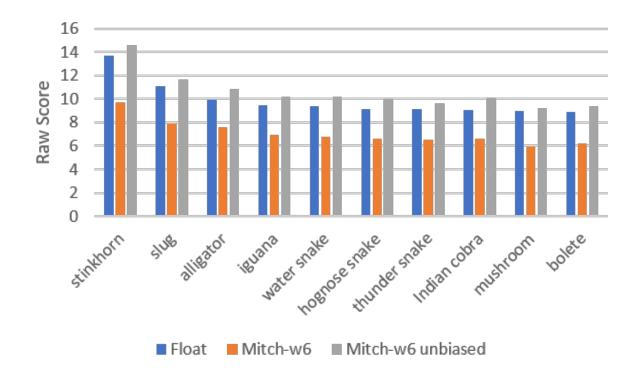

|      | The final scores of the sample inference from AlexNet with the unbiased Mitch- $w$<br>The final scores for the C2 and C1 size handling from the sample information of | 78  |

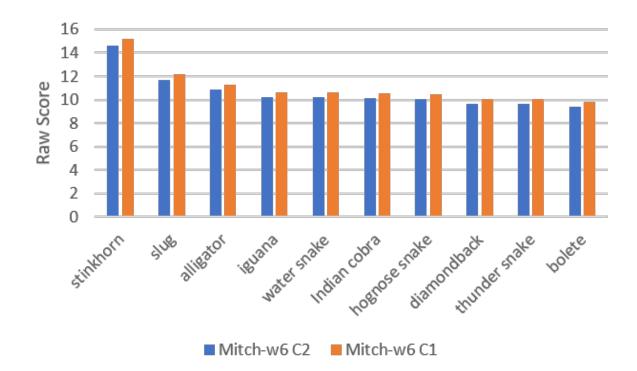

| ა.14 | The final scores for the C2 and C1 sign handling from the sample inference of AlexNet                                                                                 | 82  |

|      | AlexNet                                                                                                                                                               | 04  |

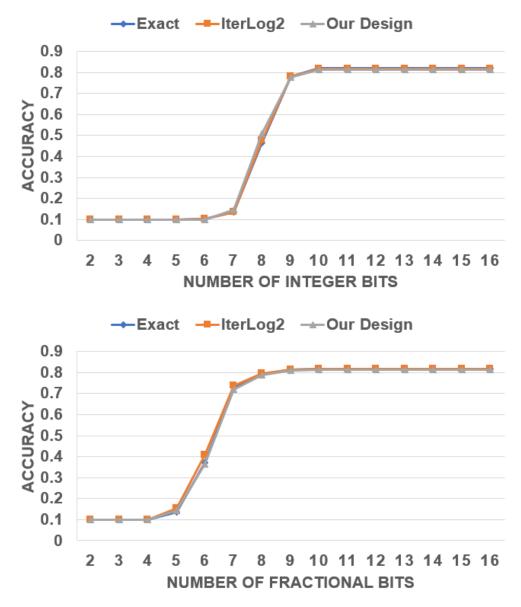

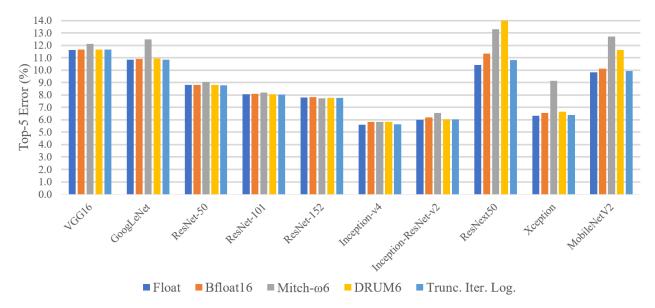

| 3.15 | Comparison of Top-5 errors between the FP32 reference and the approximate |    |

|------|---------------------------------------------------------------------------|----|

|      | multipliers                                                               | 88 |

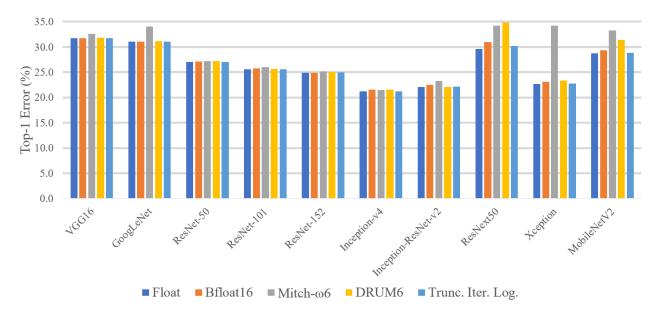

| 3.16 | Comparison of Top-1 errors between the FP32 reference and the approximate |    |

|      | multipliers                                                               | 89 |

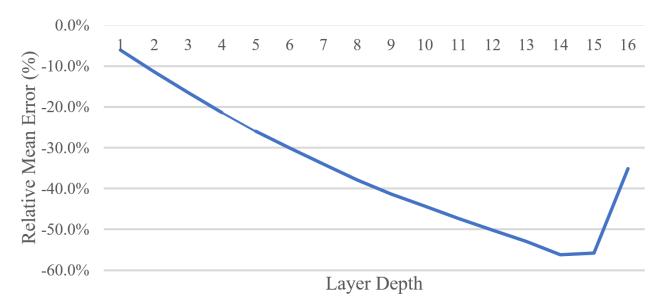

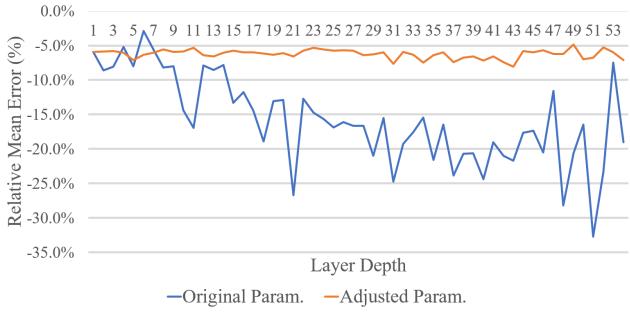

| 3.17 | Accumulation of mean error on VGG16                                       | 90 |

| 3.18 | Effect of batch normalization on ResNet-50                                | 91 |

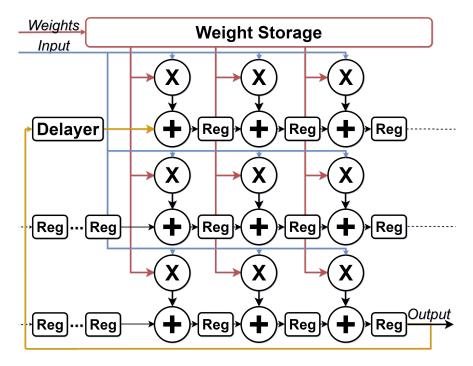

| 11   | The convolution core of 2-2 Filton Cigo                                   | 05 |

| 4.1  | The convolution core of 3x3 Filter Size                                   | 95 |

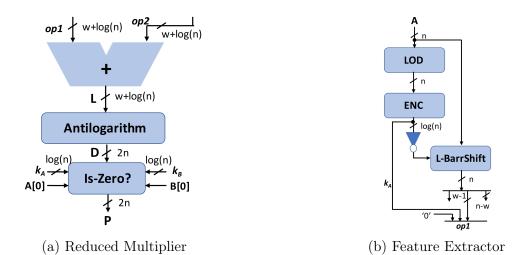

| 4.2  | Reduced Truncated Approximate Log Multiplier, RMitch- $w$                 | 96 |

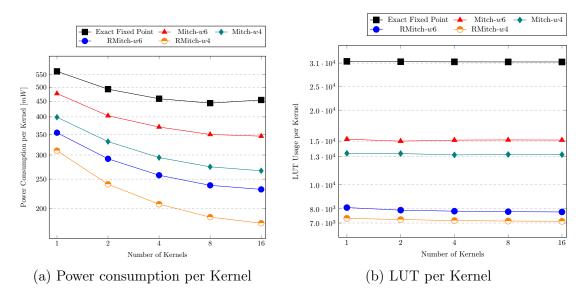

| 4.3  | Scalability of the convolution core by number of kernels                  | 97 |

# LIST OF TABLES

## Page

| 2.1          | Complexity Comparison                                                                                                                              | 14       |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2          | Comparison of power and area after synthesis                                                                                                       | 17       |

| 2.3          | Truth table for determining whether an operand is zero or not                                                                                      | 28       |

| 2.4          | Comparison of the synthesis results of Mitch- $w$ designs $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                      | 38       |

| 2.5          | Synthesis results of the unbiased designs. Energy savings are calculated with respect to the exact multiplier                                      | 39       |

| 2.6          | Synthesis results of the signed designs. Energy savings are calculated with                                                                        | 00       |

|              | respect to the exact multiplier                                                                                                                    | 39       |

| 2.7          | Hardware costs of FP32, bfloat16, and Mitch- $w$ 6 MAC $\ldots$                                                                                    | 41       |

| 2.8          | Summary of relative errors                                                                                                                         | 46       |

| 2.9          | Comparison of relative errors and costs                                                                                                            | 46       |

| 3.1          | The network descriptions of target CNNs                                                                                                            | 67       |

| 3.2          | Top-1 accuracies for LeNet and cuda-convnet                                                                                                        | 71       |

| 3.3          | Top-1 and Top-5 accuracies for AlexNet                                                                                                             | 73       |

| 3.4          | Top-1 and Top-5 accuracies of AlexNet with the Mitch- $w$ design with varying $w$                                                                  | 77       |

| 3.5          | Effect of unbiased error on Top-5 accuracy for AlexNet                                                                                             | 78       |

| $3.6 \\ 3.7$ | Effect of the C1 approximation on Top-5 accuracy for AlexNet                                                                                       | 79       |

| 3.8          | and C1 sign handling                                                                                                                               | 80       |

| 3.9          | and C1 sign handling                                                                                                                               | 81       |

|              | Mitch- <i>w</i> multipliers are unbiased and consider the C1 transform for negative                                                                | 09       |

| 9 10         | numbers                                                                                                                                            | 83       |

| 3.10<br>3.11 | Top-1 and Top-5 accuracies of the different approximate multipliers on AlexNet<br>The AlexNet accuracies with the entire ILSVRC2012 validation set | 83<br>85 |

| 0.11         | Pre-trained CNN models used for the experiments                                                                                                    | 86       |

|              | •                                                                                                                                                  | 89       |

|              | Measured variance of accumulated error with Mitch- $w6$                                                                                            | 89<br>91 |

| 4.1          | Comparison of the synthesis results for the LeNet accelerator                                                                                      | 98       |

# LIST OF ALGORITHMS

|   |                                                      |  |  |       |  |  | F | Page |

|---|------------------------------------------------------|--|--|-------|--|--|---|------|

| 1 | Digital Logic Implementation of Mitchell's Algorithm |  |  | •     |  |  |   | 9    |

| 2 | Truncated Mitchell Log Multiplier (Mitch- $w$ )      |  |  | <br>• |  |  |   | 20   |

# ACKNOWLEDGMENTS

I would like to express my sincere gratitude to those who have helped me complete this dissertation. First and foremost, I would like to thank my advisor, Professor Nader Bagherzadeh, and my partner Alberto Del Barrio who has closely worked with me throughout this project. Also, it has been a pleasure to work with Professor Hyunjin Kim, Professor Román Hermida, Leonardo Oliveira and the colleagues in Advanced Computer Architecture Group (ACAG). I have learned much by working with the great minds, and this dissertation was simply not possible without their guidance, support, and contributions.

I am also grateful to my committee members, Professor Jean-Luc Gaudiot and Professor Rainer Dömer, for their valuable comments, kind support and encouragements.

I express special thanks to Vladimir Alves and the people at NGD Systems, Inc. for offering me an internship position at the company. Working there for many quarters has been a great learning experience, and the position has been the primary source of funding for the Ph.D. study. I also thank the Center for Pervasive Communications and Computing at UCI for the funding assistance.

I thank my parents and my family for their endless support. I also thank my friends at UCI and Bethel Church for the priceless memories together. Lastly and above all, I thank and praise my God for I can do nothing without Him.

# VITA

## Min Soo Kim

#### EDUCATION

| <b>Doctor of Philosophy in Electrical and Computer Engineering</b> | <b>2020</b>        |

|--------------------------------------------------------------------|--------------------|

| University of California, Irvine                                   | Irvine, California |

| Master of Science in Electrical and Computer Engineering           | <b>2011</b>        |

| University of California, Irvine                                   | Irvine, California |

| Bachelor of Applied Science in Engineering Science                 | <b>2008</b>        |

| University of Toronto                                              | Toronto, Canada    |

#### **RESEARCH EXPERIENCE**

**Graduate Student Researcher** University of California, Irvine

**Internship in Engineering** NGD Systems, Inc.

**Research Intern** Microsoft Research

**Research Engineer** Silicon Works Co., Ltd.

**Graduate Student Researcher** University of California, Irvine

#### TEACHING EXPERIENCE

Teaching Assistant Introduction to Digital Systems, Introduction to Digital Logic Laboratory, Oragnization of Digital Computers Laboratory, University of California, Irvine **2015–2020** *Irvine, California*

**2017 - 2020** *Irvine, California*

Summer 2018 Redmond, Washington

**2011–2014** Daejeon, South Korea

> **2009–2011** *Irvine, California*

> > 2017 - 2018

Irvine, California

## **REFEREED JOURNAL PUBLICATIONS**

| Min Soo Kim, Alberto A. Del Bario, Leonardo Tavares Oliveira,<br>Román Hermida and Nader Bagherzadeh, "Efficient Mitchell's<br>Approximate Log Multipliers for Convolutional Neural<br>Networks"<br>IEEE Transactions on Computers                                                                                  | May 2019                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| REFEREED CONFERENCE PUBLICATIONS                                                                                                                                                                                                                                                                                    |                             |

| HyunJin Kim, <b>Min Soo Kim</b> , Alberto A. Del Bario and Nader<br>Bagherzadeh, <b>"A Cost-Efficient Iterative Truncated Log-</b><br><b>arithmic Multiplication for Convolutional Neural Net-</b><br><b>works"</b><br>IEEE Symposium on Computer Arithmetic                                                        | June 2019                   |

| Leonardo Tavares Oliveira, <b>Min Soo Kim</b> , Alberto A. Del<br>Barrio, Nader Bagherzadeh and Ricardo Menotti, <b>"Design<br/>of Power-Efficient FPGA Convolutional Cores with Ap-<br/>proximate Log Multiplier"<br/>European Symposium on Artificial Neural Networks</b> , Computational Int<br>Machine Learning | April 2019<br>elligence and |

| Min Soo Kim, Alberto A. Del Barrio, Román Hermida<br>and Nader Bagherzadeh, "Low-power Implementation of<br>Mitchell's Approximate Logarithmic Multiplication for<br>Convolutional Neural Networks"<br>Asia and South Pacific Design Automation Conference                                                          | January 2018                |

## AWARDS

| Hyundai Motor Group Scholarship                              | 2019 |

|--------------------------------------------------------------|------|

| The Governor Generals Academic Medal, Bronze                 | 2004 |

| Da Vinci Scholar from Leonardo da Vinci National Competition | 2004 |

## ABSTRACT OF THE DISSERTATION

Cost-Efficient Approximate Log Multipliers for Convolutional Neural Networks

by

Min Soo Kim

Doctor of Philosophy in Electrical and Computer Engineering University of California, Irvine, 2020 Professor Nader Bagherzadeh, Chair

The breakthroughs in multi-layer convolutional neural networks (CNNs) have caused significant progress in the applications of image classification and recognition. The size of CNNs has continuously increased to improve their prediction capabilities on various applications, and it has become increasingly costly to perform the required computations. In particular, CNNs involve a large number of multiply-accumulate (MAC) operations, and it is important to minimize the cost of multiplication as it requires most computational resources.

This dissertation proposes cost-efficient approximate log multipliers, optimized for performing CNN inferences. Approximate multipliers have reduced hardware costs compared to the conventional multipliers but produce products that are not exact. The proposed multipliers are based on Mitchell's Log Multiplication that converts multiplications to additions by taking approximate logarithm. Various design techniques are applied to Mitchell Log Multiplier, including fully-parallel LOD, efficient shift amount calculation, and exact zero computation. Additionally, the truncation of the operands is studied to create the customizable log multiplier that further reduces energy consumption. This dissertation also proposes using the one's complements to handle negative numbers to significantly reduce the associated costs while having minimal impact on CNN performances. The viability of the proposed designs is supported by the detailed formal analysis as well as the experimental results on CNNs. The proposed customizable design at w=8 saves up to 88% energy compared to the exact fixed-point multiplier at 32 bits with just a performance degradation of 0.2% on AlexNet for the ImageNet ILSVRC2012 dataset.

The effects of approximate multiplication are analyzed when performing inferences on deep CNNs, to provide a deeper understanding of why CNN inferences are resilient against the errors in multiplication. The analysis identifies the critical factors in the convolution, fully-connected, and batch normalization layers that allow more accurate CNN predictions despite the errors from approximate multiplication. The same factors also provide an arithmetic explanation of why bfloat16 multiplication performs well on CNNs. The experiments with deep network architectures, such as ResNet and Inception-v4, show that the approximate multipliers can produce predictions that are nearly as accurate as the FP32 references, while saving significant amount of energy compared to the bfloat16 arithmetic.

Lastly, a convolution core that utilizes the approximate log multiplier is designed to significantly reduce the power consumption of FPGA accelerators. The core also exploits FPGA reconfigurability as well as the parallelism and input sharing opportunities in convolution to minimize the hardware costs. The simulation results show reductions up to 78.19% of LUT usage and 60.54% of power consumption compared to the core that uses exact fixed-point multipliers, while maintaining comparable accuracy on the LeNet for MNIST dataset.

# Chapter 1

# Introduction

For the past several years, the techniques employing Machine Learning allowed significant breakthroughs in many applications, and convolutional neural networks (CNNs) have been widely successful in advancing the field of computer vision. From the milestone network LeNet for the handwritten digit recognition [38], CNNs have been continually studied and improved to perform well even for the large-scale image classification. The CNNs developed in this progress, such as AlexNet and GoogLeNet [33, 63], showed the trend where the amount of computations augmented as the number of layers increased for better accuracy. With such a large and growing number of computations, as well as the rising application of Machine Learning techniques to many areas, it is vital to develop efficient processing hardware units for CNNs. For deep learning to have revolutionary impacts on the real-world applications, their computational costs must meet the timing, energy, monetary, and other design constraints of the deployed services. Many approaches have been studied to reduce the computational costs at all levels of software and hardware, from advances in network architectures [63, 7] down to electronics where even memory devices are extensively researched [62, 60].

One distinction to make in neural network computation is the training versus inference

computations. Training teaches neural networks to develop the classification capabilities through the gradient-based backpropagation algorithms performed on a large amount of supplied data. These algorithms involve delicate computations of gradient values and are performed with floating-point units. The DaDianNao project [5] studied applying fixed point arithmetic to training and found that training required much more precision than inference. Hence, it is difficult to apply approximate computing to the training of CNNs. Although training requires more computations when compared to inference, it is still important to reduce the cost of inference as much as possible, because it is the inference that is usually subject to more strict real-world design constraints. The training phase may be performed offline in advance, and the trained network models may be approximated when they are deployed to perform inferences, to meet the design constraints and reduce the cost of services.

Many hardware-based approaches have shown significant improvements for the computational costs of CNN inferences, but there are two limitations commonly found in these works. Some techniques are computationally expensive in order to optimize their methods for each network model, or to retrain networks to compensate the performance degradation from their methods [35, 70]. Also, many techniques such as [55] are only effective for small networks and cannot scale to deeper CNNs, as they report much worse performance results when tested for deeper networks. In the past it had been shown that small number of bits are sufficient for small CNNs and many techniques relied on aggressive quantization, but more complex networks require more bits to properly represent the amount of information [37].

One promising hardware-based approach is the application of approximate multiplication to CNN inferences. The convolution layers in CNNs consist of a large number of multiplyaccumulate (MAC) operations, and they take up the majority of computations for CNN inferences [54]. The MAC operations are ultimately performed in the hardware circuits, and it is important to minimize the cost of these circuits to perform more computations with the same amount of resources. For MAC operations, multiplications are more complex than additions and consume most resources. The proposed methodology is to minimize the cost of multiplication by replacing the conventional multipliers with approximate multipliers. Unlike aggressive quantization that trades off numeric precision, approximate multipliers trade off arithmetic accuracy that is less dependent on the network models, making them better suited for deeper CNNs. The approach does not involve any optimization to a target network model or require additional processing of the network models, allowing easy adaptation into the ASIC and FPGA accelerators.

Approximate multipliers are significantly cheaper compared to the exact multipliers, but they introduce errors in the results. There are many different types of approximate multipliers, with various costs and error characteristics. Some designs use the electronic properties [6] and some approximate by intentionally flipping bits in the logic [13], while others use algorithms to approximate multiplication [58]. Several previous research papers have shown that it is possible to apply approximate multiplication to the inference stage of neural networks after training with exact arithmetic [45, 58, 50, 13]. Such techniques usually demonstrated small drops in performance but had significant reduction in resources. The resource reduction, especially the power savings, would be beneficial for embedded systems and datacenters, as emphasized by the efforts from Google to create a custom TPU processor for Machine Learning on its datacenters [24].

The logarithmic multiplier based on Mitchell's Algorithm [47] is a promising approximate multiplier for neural network computation. Figure 1.1 shows the difference between the conventional fixed-point multiplier and the log multiplier. This multiplier converts multiplications into additions by taking approximate logarithm. This algorithm is well known to have a significant benefit in area and power savings while maintaining a reasonably low error rate. Many research such as [4, 46, 1, 42] have recognized its benefits and attempted to improve it since the original proposal [47]. The original algorithm has a worst case relative error that is proven to be as low as 11.1%, and this property is potentially important in

Figure 1.1: Difference between (a) the conventional fixed-point multiplication and (b) the approximate log multiplication.

neural networks that emulate firing of neurons. A large worst-case error would have a greater chance of incorrectly firing a neuron, which would lead to a larger probability of incorrect classification. Another important benefit of the log multiplication is the consistent error characteristics, which allows for consistent observation of the effects across various CNN instances. In this dissertation, the consistent observation enabled the in-depth analysis of the effects of approximate multiplication on CNN inferences.

The following contributions are made in this dissertation toward the study of approximate multiplication for CNN inferences. Firstly, cost-efficient approximate multipliers based on Mitchell's Algorithm are presented in Chapter 2. We present an efficient implementation of Mitchell's Algorithm and apply various techniques to create customizable designs that can reduce significant amount of resources compared to exact multiplication. The effects of the proposed log multipliers on CNN inferences are studied in Chapter 3. Various experiments on CNN models support the conclusion that the proposed designs are suitable for CNN inferences, and the analysis also provide the theoretical understanding of the effects of approximate multiplication and why CNNs are resilient against the errors in multiplication. A convolution core design that utilizes the proposed multipliers is presented in Chapter 4. The convolution core design provides the opportunities for resource sharing between multiple instances of the log multipliers, and consumes significantly less power and LUT resources for a CNN accelerator on FPGA. Lastly, the conclusion of this dissertation is presented in Chapter 5.

# Chapter 2

# Design of Cost-Efficient Approximate Log Multipliers

This chapter describes the proposed approximate log multipliers optimized for CNN inferences. The multipliers are based on Mitchell's Algorithm [47], and various techniques are applied to minimize their hardware costs while maintaining reasonable accuracies on CNN inferences.

# 2.1 Mitchell Log Multiplier

The Mitchell's log multiplication algorithm and the proposed implementation is described in this section. The original paper on Mitchell's Algorithm [47] does not specify any digital circuit implementation, so a low-cost implementation is created and optimized through various techniques. The implementation is the basis from which the other proposed designs are derived, and its development as well as the performance on CNNs were published in [29].

#### 2.1.1 Mitchell's Algorithm

The first approach to logarithmic multipliers was presented by J. Mitchell in 1962 [47]. The logarithmic multiplication of two numbers  $A \cdot B$  requires converting them to logarithm, then adding both logarithms and finally computing the antilogarithm of the result.

Equation 2.1 represents Z, an n-bit number.

$$Z = \sum_{i=0}^{n-1} 2^{i} z_{i} = 2^{k} \left( 1 + \sum_{i=j}^{k-1} 2^{i-k} z_{i} \right), \quad k \ge j \ge 0.$$

(2.1)

where k is the position corresponding to the leading one,  $z_i$  is a bit value at the  $i^{th}$  position, and j depends on the number's precision. Then, the logarithm with the basis 2 of Z is expressed by Equation 2.2.

$$\log_2(Z) = \log_2\left(2^k \left(1 + \sum_{i=j}^{k-1} 2^{i-k} z_i\right)\right) = \log_2\left(2^k (1+x)\right) = k + \log_2(1+x)$$

(2.2)

Then, the expression  $\log_2(1 + x)$  is approximated with x, as  $\forall x \in [0, 1]$  both expressions provide close results. Figure 2.1 shows the resulting approximate logarithm compared against exact logarithm. The original work provided the mathematical analysis of the error and proved that the maximum error was -11.1% relative to the exact product [47]. In other words, the magnitude of the product from Mitchell's Algorithm will be relatively smaller than that of the exact product, from 0% up to 11.1%. The Mitchell Log Multiplier cannot produce a product that has a bigger magnitude than the exact product.

Figure 2.1: Approximate logarithm from Mitchell's Algorithm, compared against logarithm

#### Algorithm 1 Digital Logic Implementation of Mitchell's Algorithm Require: A, B: *n*-bits **Ensure:** P: 2n-bits $\triangleright$ P is an approximate product $\triangleright$ Logarithm $h_A \leftarrow LOD(A), h_B \leftarrow LOD(B)$ $k_A \leftarrow ENC(h_A), k_B \leftarrow ENC(h_B)$ $x_A \leftarrow A \ll (n - k_A - 1), x_B \leftarrow B \ll (n - k_B - 1)$ $\triangleright$ Addition in the LNS domain $op1 \leftarrow 0' \& k_A \& x_A[n-2..0]$ $op2 \leftarrow 0' \& k_B \& x_B[n-2..0]$ $L \leftarrow op1 + op2$ $\triangleright$ Antilogarithm $charac \leftarrow L[n + \log_2(n) - 1..n - 1]$ $lr \leftarrow charac[\log_2(n)]$ $m \leftarrow 1' \& L[n-2..0]$ if lr = 1' then $\triangleright$ Large characteristic $shamtL \leftarrow ('0' \& charac[\log_2(n) - 1..0]) + 1$ $D \leftarrow m \ll shamtL$ else $\triangleright$ Small characteristic $shamtR \leftarrow n - charac[\log_2(n) - 1..0] - 1$ $D \leftarrow m >> shamtR$ end if $\triangleright$ Check if the result should be zero if $A = 0 \lor B = 0$ then $P \leftarrow 0$ else $P \leftarrow D$ end if

## 2.1.2 Proposed Design

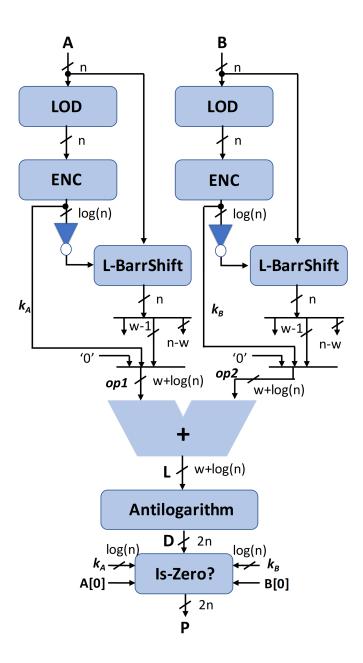

The proposed implementation is detailed by Algorithm 1. Figure 2.2 shows the design of our logarithmic multiplier. It must be noted that & stands for the concatenation symbol and x[b..a] represents the bits that range from positions b to a belonging to signal x.

The first step is implemented through the Leading One Detectors (LOD) and the Encoders (ENC). It must be noted that the LOD module produces a one-hot representation of the leading one. Hence, the encoder is composed of just a set of OR gates, instead of the priority encoder employed in [4, 45]. Our LOD module leverages the implementation provided in

Figure 2.2: Mitchell Logarithmic Multiplier according to Algorithm 1

[4, 45], where the proposed 4-bits LOD blocks can be modeled with Equations 2.3 and 2.4.

$$h_j = z_j \cdot m_j, \qquad 0 \le j \le 4 \tag{2.3}$$

$$m_{j} = \begin{cases} 1, & j = 3\\ \hline z_{j+1} \cdot m_{j+1}, & 0 \le j \le 3 \end{cases}$$

(2.4)

where  $h_j$  is the  $j^t h$  bit belonging to the hot one representation (H) of the leading one in Z. Expanding Equation 2.4 for a generic bitwidth n, it would be possible to obtain the expression given in Equation 2.5.

$$m_j = z_j \cdot \overline{\sum_{i=j+1}^{n-1} z_i} \tag{2.5}$$

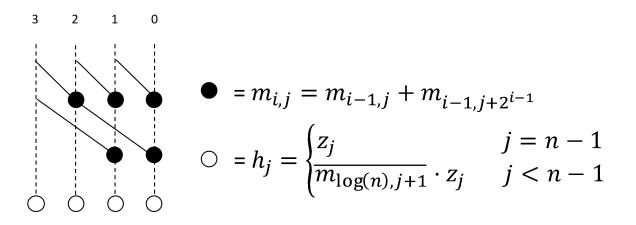

Using Equation 2.5 and constructing an or-tree in the same fashion as the Kogge-Stone adder [31] calculates the carry-in signals of an addition, it is possible to obtain Equations 2.6 and 2.7, which model our fully parallel LOD.

$$m_{i,j} = \begin{cases} z_j, & i = 0 \\ m_{i-1,j}, & i > 0, (n-1-j) < 2^{i-1} \\ m_{i-1,j} + m_{i-1,j+2^{i-1}}, & i > 0, (n-1-j) \ge 2^{i-1} \\ \forall i, 0 \le i \le \log(n), \forall j, 0 \le j < n \end{cases}$$

$$h_j = \begin{cases} z_j, & j = n-1 \\ \hline (m_{\log(n),j+1}) \cdot z_j, & j < n-1 \end{cases}$$

$$(2.7)$$

$\overline{(m_{log(n),j+1})}$  is a signal that indicates whether or not there is a '0's chain at the left of  $z_j$ ,  $h_j$  is the  $j^{th}$  bit belonging to the one-hot representation (H) of the leading one in Z. As an

example, a 4-bit LOD block is shown in Figure 2.3.

Figure 2.3: 4-bit leading one detector

Finally, Equation 2.8 gives the value of  $e_i$ , if it is the  $i^{th}$  bit of the encoded value E.

$$e_i = \sum_{j=0}^{n-1} h_j, \qquad \forall i, 0 \le i \le \log(n)$$

(2.8)

In order to compute the mantissas  $x_A$  and  $x_B$ , the shift amount is computed utilizing one's complement arithmetic, as  $n-k_i-1$  is equivalent to  $not(k_i)$  when n is a power of 2. Afterwards two left barrel shifters generate the mantissas, which concatenated with the corresponding characteristics compose the two operands added to compute L.

Afterwards, the result L needs to be decoded. Figure 2.4 depicts the structure of our Mitchell Decoder. In Antilogarithm of Algorithm 1, two cases are distinguished depending on the most significant bit of L (labelled as lr), which is also the most significant bit of the characteristic of L. If lr='1', the mantissa of L must be shifted at least n positions to the left. That is why a 2n-bit left barrel shifter is employed for such purpose. It must be noted that when this left shifter is being used, the shift amount *shamtL* is always increased by 1. Hence, this shifter has been customized to always shift one extra position to the left. In this way an addition is avoided at zero cost. On the other hand, when lr='0', its mantissa must be shifted to the

Figure 2.4: Mitchell Decoder

|         | LOD              | ENC      | SHT                                 | ADD                   | Zero    |

|---------|------------------|----------|-------------------------------------|-----------------------|---------|

| [4, 45] | 4-bit blocks [1] | Priority | 2 Left (n)                          | $1 (2n), 2 (\log(n))$ | _       |

| Ours    | Parallel         | Or-tree  | 2 Left (n), 1 Right (n), 1 Left(2n) | $1~(\log(n)+n)$       | Or-tree |

Table 2.1: Complexity Comparison

left by n-1 positions at most, which is equivalent to shift to the right by shamtR. shamtR is also efficiently calculated by employing one's complement arithmetic. As can be observed, the right barrel shifter bitwidth is just n-bits. Thus, while the least significant bits of D must be selected using a multiplexer (MUX), the most significant ones can be obtained through an AND gate with the most significant bit of L.

When any of the operands is zero, the result P must be zero. It has been demonstrated by Mrazek et al. in [50] that it is important to produce the accurate zero result when one of the operands is zero, and we implemented a zero detection unit to correctly handle it. In order to implement it, we leverage the following property: if an operand is zero, the value provided by ENC is zero and the least significant bit of the operand is '0'. This is shown in Figure 2.5 and the logic within the darkened area produces valid results just after the encoded values of the one-hot representations are computed.

#### 2.1.3 Implementation Complexity

Table 2.1 contains a detailed summary of the complexity between our proposal and the one presented in [4, 45]. It must be noted that the latter is an iterative design that combines several basic blocks (BBs) to obtain different accuracies. Thus, the data shown in the table corresponds with just one BB, while our Mitchell's multiplier data correspond with the whole multiplier.

As shown in Table 2.1, the leading one detection(LOD) stage is different. While the LOD

Figure 2.5: Is-Zero block structure: performs both zero detection and correct result generation

implementations in [4, 45, 1] are based on 4-bit blocks interconnected through carry signals, our implementation is fully parallel and therefore faster. Second, as our LOD produces a one-hot representation, the encoding phase (ENC) is realized through OR-trees instead of complex priority encoders. In terms of shifters (SHT) our proposal requires more instances of these resources, but less adders (ADD). It must be noted that in both SHT and ADD columns the size of every resource is specified among parentheses, as they vary depending on the multiplier implementation. Finally, our proposal includes a zero detection unit based on the encoded signals, whose bit width is log(n), which is simpler than employing two n-bit comparators with zero.

#### 2.1.4 Synthesis Results

To evaluate the power and area benefits of the proposed design, we performed synthesis using Synopsys Design Compiler and compared it against the synthesis results of the exact fixed-point multiplier and the 2-stage iterative logarithmic multiplier. The exact multiplier is automatically synthesized by Design Compiler from the simple Verilog multiplication, and the 2-stage iterative logarithmic multiplier presented in [3] was modified to remove all pipeline registers and add the zero detection unit. We used a 32nm digital standard cell library from Synopsys, and repeated the synthesis for 8, 16, and 32 bits. The synthesis was performed with "Ultra" effort at the clock frequency of 250 MHz, because we wanted to see the maximum power savings without being constrained by the timing. The 2-stage iterative multiplier at 32 bits was time constrained and had an increased area, but we did not adjust the clock speed of the experiment because of the inefficiency of the design. We also compared the referenced error rates of these multipliers.

Table 2.2 shows the synthesis results of the multipliers to compare their power and area. Although our optimized design has the worst error rate, it is significantly smaller and consumes

|                      |       | N=8      |           | N=16  |          |           | N=32  |          |           |  |  |  |

|----------------------|-------|----------|-----------|-------|----------|-----------|-------|----------|-----------|--|--|--|

|                      | Exact | Proposed | Iter. Log | Exact | Proposed | Iter. Log | Exact | Proposed | Iter. Log |  |  |  |

| Mean Err. (%)        | 0     | -3.77    | -0.83     | 0     | -3.83    | -0.99     | 0     | -3.87    | N/A       |  |  |  |

| Worst Case Error (%) | 0     | -11.11   | -6.25     | 0     | -11.11   | -6.25     | 0     | -11.11   | -6.25     |  |  |  |

| Cell Area $(um^2)$   | 403   | 312      | 872       | 1681  | 909      | 2189      | 6409  | 2161     | 7220      |  |  |  |

| Critical Path (ns)   | 1.07  | 1.13     | 1.75      | 2.23  | 2.31     | 3.77      | 3.78  | 3.70     | 4.00      |  |  |  |

| Total Power $(mW)$   | 0.269 | 0.197    | 0.544     | 1.240 | 0.549    | 1.310     | 6.02  | 1.41     | 4.64      |  |  |  |

| Power Saving (%)     | —     | 26.8     | -102.2    | -     | 55.7     | -5.6      | —     | 76.6     | 22.9      |  |  |  |

Table 2.2: Comparison of power and area after synthesis

less power than the other multipliers. The critical path length of the proposed design is comparable to that of the exact multiplier and clearly shorter than the critical path of the iterative design. Our logarithmic multipliers show better reduction of power and area as the number of bits increases, thus possessing better scalability. Compared to the exact fixed-point multiplier, it saves up to 76.6% of power at 32 bits and shows a clear saving of 26.8% even at 8 bits. The proposed design achieves larger power and area savings compared to the 2-stage iterative multiplier that had been applied to the neural networks in [45]. In fact, the iterative multiplier design seems inefficient and consumes more power and area than the exact multiplier at 8 and 16 bits. We divided the 2-stage iterative logarithmic multiplier to create the 1-stage multiplier without the error correction, but it was still larger than our proposed design and consumed 0.689 mW at 16 bits, while having the worst case relative error of 25% [4]. It must be noted that the authors of [45] had a different aim than ours. They focused on pipelining the iterative design and compared it against the matrix multiplier in Xilinx Spartan 3 FPGA. Nevertheless, in this dark silicon era where we are limited primarily by power, our proposed logarithmic multiplier suits better than the state-of-the-art for CNN inferences.

## 2.2 Truncated Mitchell Log Multiplier, Mitch-w

While the Mitchell Log Multiplier is very cost-efficient, it is possible to further approximate it by truncating mantissa bits. The LODs locate the leading ones and most significant portions of the input operands so that truncating the operands after taking logarithm enables performing reasonably accurate multiplication, while significantly reducing the hardware cost of the multiplier. The design of Mitch-w multipliers and their performances on CNNs were published in [30].

#### 2.2.1 Proposed Design

Our proposal is detailed by Algorithm 2 and Figure 2.6. It must be noted that & stands for the concatenation symbol and x[b..a] represents the bits that range from positions b to a belonging to signal x. This design will hereafter be referred to as Mitch-w.

The main difference with respect to the Mitchell multiplier in Section 2.1 is the introduction of the parameter w. This parameter indicates that only the most significant w bits of the operand will be taken into account. As the leading one is encoded into the characteristic, this means that only the most significant w - 1 mantissa bits are considered to be added. Some approaches in literature [17, 58] have shown that under the paradigm of approximate computing, the most significant part of a value may be sufficient to provide an acceptable approach. Figure 2.7 shows the truncation schemes presented at [17] and ours. Figures 2.7a and 2.7b illustrate how [17] unbiases and truncates an operand using w bits, namely: the leading one located at the  $k^{th}$  position, w - 2 bits, and an extra '1' for approximating the least significant part. This operand will be driven to a wxw multiplier then. On the other hand, Figures 2.7c and 2.7d describe the resulting mantissa after left-shifting the operand, and how the w - 1 most significant bits (excluding the leading one) are used in combination

Figure 2.6: Truncated Mitchell Log Multiplier, Mitch-w

| Algorithm 2 Truncated Mitchell Log Multiplier (Mit                                    | ch-w)                                        |

|---------------------------------------------------------------------------------------|----------------------------------------------|

| <b>Require:</b> A, B: <i>n</i> -bits, $w \in [0, n-1]$                                |                                              |

| Ensure: P: 2n-bits                                                                    | $\triangleright$ P is an approximate product |

|                                                                                       | $\triangleright$ Logarithm                   |

| $h_A \leftarrow LOD(A), h_B \leftarrow LOD(B)$                                        |                                              |

| $k_A \leftarrow ENC(h_A), k_B \leftarrow ENC(h_B)$                                    |                                              |

| $x_A \leftarrow A \ll (n - k_A - 1), x_B \leftarrow B \ll (n - k_B - 1)$              |                                              |

|                                                                                       | $\triangleright$ Addition in the LNS domain  |

| $op1 \leftarrow 0' \& k_A \& x_A[n-2n-w]$                                             |                                              |

| $op2 \leftarrow 0' \& k_B \& x_B[n-2n-w]$                                             |                                              |

| $L \leftarrow op1 + op2$                                                              |                                              |

|                                                                                       | $\triangleright$ Antilogarithm               |

| $charac \leftarrow L[w + \log_2(n) - 1w - 1]$                                         |                                              |

| $lr \leftarrow charac[\log_2(n)]$                                                     |                                              |

| $m \leftarrow 1' \& L[w - 20]$<br>if $lr = 1'$ then                                   | . I anno al ano atomistic                    |

|                                                                                       | $\triangleright$ Large characteristic        |

| $shamtL \leftarrow ('0' \& charac[\log_2(n) - 10]) + 1$<br>$D \leftarrow m << shamtL$ |                                              |

| $D \leftarrow m << shame{L}$ else                                                     | ▷ Small characteristic                       |

| $shamtR \leftarrow n - charac[\log_2(n) - 10] - 1$                                    |                                              |

| $D \leftarrow m >> shamtR[\log_2(n) \log_2(n) - \log_2(w)]$                           |                                              |

| end if                                                                                |                                              |

|                                                                                       | ▷ Check if the result should be zero         |

| if $A = 0 \lor B = 0$ then                                                            |                                              |

| $P \leftarrow 0$                                                                      |                                              |

| else                                                                                  |                                              |

| $P \leftarrow D$                                                                      |                                              |

| end if                                                                                |                                              |

with the characteristic k to compose the operand that will be driven to the adder within the logarithmic multiplier. These differences ultimately stem from the fact that our designs perform the truncation in the approximate logarithmic domain while the authors in [17] operate in the linear domain.

The use of the aforementioned truncated summands implies using a customized antilogarithm block. The design of this module is shown in Figure 2.8. As observed, utilization of the wparameter has a large impact on power and area of this block. The original left barrel shifter shown in Section 2.1 decreases its size from 2n to n + w, while the right barrel shifter and the multiplexer decrease their sizes from n to w. Reducing the size of these blocks has a positive

(d) Operand driven to the adder input of Mitch-w

Figure 2.7: Operands truncation methods

impact on power and area, but at the expense of losing some accuracy.

Figure 2.8: Customizable Antilogarithm block

# 2.2.2 Error Study of Truncation

In this subsection, an analysis on the use of the truncated logarithmic multiplier is presented. This error  $(E_D)$  is the one produced at the output of the antilogarithm block, as truncating some bits on the operand mantissas does not affect the zero-checking block. Thus, it must be noted that the error with respect to a conventional Mitchell Log Multiplier is first produced when truncating the operands.

$$\widehat{m} = m/2^{n-1} < 1 , (2.9)$$

$$y_A = x_A \wedge (2^{n-1} - 1) \tag{2.10}$$

$$y_B = x_B \wedge (2^{n-1} - 1) \tag{2.11}$$

$$y'_{A} = x_{A} \wedge (2^{n-1} - 2^{n-w}) > y_{A} - 2^{n-w} , \qquad (2.12)$$

$$y'_B = x_B \wedge (2^{n-1} - 2^{n-w}) > y_B - 2^{n-w} , \qquad (2.13)$$

$$y_L = (y_A + y_B) \wedge (2^{n-1} - 1) , \qquad (2.14)$$

$$y'_L = (y'_A + y'_B) \wedge (2^{n-1} - 1) , \qquad (2.15)$$

$$k_L = k_A + k_B + \left( \left( (y_A + y_B) \land (2^{n-1}) \right) >> (n-1) \right) , \qquad (2.16)$$

$$k'_{L} = k_{A} + k_{B} + \left( \left( \left( y'_{A} + y'_{B} \right) \land (2^{n-1}) \right) \right) >> (n-1) \right) , \qquad (2.17)$$

$$L = k_A * 2^{n-1} + y_A + k_B * 2^{n-1} + y_B$$

(2.18)

$$=k_L * 2^{n-1} + y_L$$

,

$$L' = k_A * 2^{n-1} + y'_A + k_B * 2^{n-1} + y'_B$$

=  $k'_L * 2^{n-1} + y'_L$ , (2.19)

$$D = antilog(L) = 2^{k_L} * (1 + \widehat{y_L}) , \qquad (2.20)$$

$$D' = antilog(L') = 2^{k'_L} * (1 + \widehat{y'_L}) .$$

(2.21)

First, according to Equation 2.9 let us define  $\hat{m}$  as the normalized version of a generic mantissa m, so  $\hat{m}$  will always be  $\in [0,1)$ . Let  $x_A$  and  $x_B$  be the mantissas as defined in Algorithm 2, i.e. after left shifting. And let  $y_A$  and  $y_B$  be the mantissas after removing the leading one, i.e. the most significant bit, as Equations 2.10 and 2.11 indicate. And let  $y'_A$  and  $y'_B$  be the truncated version of those, as Equations 2.12 and 2.13 point, respectively. Let us define L

and L' as Equations 2.18 and 2.19 indicate, respectively.

It must be noted that  $k_L$  and  $k'_L$  do not necessarily match, as if  $y_L \neq y'_L$ , the carry-out propagating towards the characteristic part of L and L' may be different too. Then, the error  $E_D$  performed when computing D' with respect to D in Algorithm 2 is as pointed by Equation 2.22.

$$E_D = D - D' = 2^{k_L} * (1 + \widehat{y_L}) - 2^{k'_L} * (1 + \widehat{y'_L})$$

=  $2^{k_L} * ((1 + \widehat{y_L}) - 2^{k'_L - k_L} * (1 + \widehat{y'_L}))$ . (2.22)

As  $k_L \ge k'_L$ , because L' comes from the truncated operands, two cases may happen then: either  $k_L = k'_L$ , or  $k_L > k'_L$ . If  $k_L = k'_L$ , then both  $y_L$  and  $y'_L$  propagate, or do not propagate, a carry-out to the characteristic parts  $k_L$  and  $k'_L$ , respectively. Then,  $y_L = y_A + y_B - carry$ ,  $y'_L = y'_A + y'_B - carry'$ , and Equation 2.23 holds.

$$E_D = 2^{k_L} * \left( (1 + \widehat{y_L}) - (1 + \widehat{y'_L}) \right)$$

=  $2^{k_L} * (\widehat{y_L} - \widehat{y'_L})$

=  $2^{k_L} * (\widehat{y_A} - \widehat{y'_A} + \widehat{y_B} - \widehat{y'_B})$

<  $2^{k_L} * (2^{-w+1} + 2^{-w+1}) = 2^{k_L - w + 2}$ . (2.23)

It must be noted that as Equation 2.12 indicates,  $y_A - y'_A$  is lower than  $2^{n-w}$ , and then  $\widehat{y}_A - \widehat{y'_A}$  is lower than  $2^{-w+1}$ . Analogously for Equation 2.13. On the other hand, if  $k_L > k'_L$ , then  $k_L = k'_L + 1$ . As the only difference between L and L' is a carry-out being propagated to the non-truncated part, there can only be one unit of difference in the characteristic part of L. Furthermore, if in L such carry propagation exists, while in L' does not,  $\widehat{y'_L}$  will be composed of just '1's, and  $\widehat{y}_L$  will be transformed into a chain of '0's. Under these conditions,

Equation 2.24 holds.

$$E_D = 2^{k_L} * \left( (1 + \widehat{y_L}) - 2^{k'_L - k_L} * (1 + \widehat{y'_L}) \right)$$

=  $2^{k_L} * \left( 1 - (1 + \widehat{y'_L})/2 \right)$

=  $2^{k_L} * \left( 1 - (1 + \sum_{i=n-w+1}^{n-1} 2^{i-n})/2 \right)$

=  $2^{k_L} * \left( 1 - (1 + 1 - 2^{-w+1})/2 \right)$

=  $2^{k_L} * (2^{-w}) = 2^{k_L - w}$ . (2.24)

Thus,  $E_D$  is never larger than  $2^{k_L-w+2}$ . Or, in relative terms, it is  $2^{k_L-w+2}/(2^{k_L} * (1+\widehat{y_L})) = 2^{-w+2}/(1+\widehat{y_L})$ . In order to finally bound the error, in the worst case  $\widehat{y_L} = 0$ , so it can be concluded that the relative error, with respect to the conventional logarithmic multiplier, is always lower than  $2^{-w+2}$ . Hence, the shorter the w, the larger the error as expected.

# 2.2.3 Handling Negative Numbers with One's Complement (C1)

In this subsection, a proposal for handling the negative values will be described. The CNNs often involve negative weights and require the arithmetic of signed numbers. One problem with the prior design in Section 2.1 was that it did not handle signed numbers naturally, and required the 2's complements sign conversion (hereafter referred to as C2) before and after the design so that the inputs to the log multiplier are always positive. Each operand went through C2 if it was negative, and the output result also went through C2 depending on the expected output sign determined by the input signs. The inability to process signed numbers is found in many approximate multipliers, and the ones based on locating the leading one in the operands all suffer the same problem because the leading one is always placed at the leftmost bit for the negative numbers. The previous approaches either had assumed the sign-magnitude representation of signed numbers [45] or inserted C2 before and after their

designs as we did [17, 58]. None of the prior works had evaluated the associated costs to fully investigate the issue.

Our proposal consists of leveraging the approximate computing scenario introduced by the CNNs. In this way, both inputs of the multiplier will be in two's complement. In this format there are several well-known facts:

- If X ∈ Z, then C2(X) = C1(X)+1. Thus, if a number is negative, it can be approached with its one's complement (hereafter referred to as C1) at the expense of introducing an error of one *unit in the last place* (ulp).

- In C2, the sign of a number is given by the most significant bit (MSB). Thus, if  $X \ge 0$  the MSB is '0', and on the contrary if X < 0, the MSB is '1'.

The proposed design is shown in Figure 2.9. As observed, first both operands are XOR-ed with their sign bit in order to convert the negative numbers into the positive domain by using the C1 transform. Consequently, the sign of the result will be the logical XOR between the operand signs. If such bit is '1', then the result provided by the antilogarithm block must be XOR-ed to produce a negative result. In this case, the zero handling is performed differently in comparison with the Mitchell multiplier in Section 2.1, although a similar idea is followed: the result is not zero if both operands are not zero. Let  $k_{O+}$  be the characteristic of an operand O after being converted to the positive domain. And let  $msb_O$  (i.e. sign) and  $lsb_O$  be the most and least significant bits of an operand O. Then, the conditions under which an operand is not zero are given by Table 2.3.

- If  $k_{O+} > 0$ , this means that the operand is not zero (cases 4 to 7).

- If  $k_{O+} = 0$  and the operand is negative  $(msb_O = 1)$ , the operand is not zero (cases 2 and 3).

Figure 2.9: Mitch-w with C1 negative number handling

| $k_{O+} > 0$ | $msb_O$ | $lsb_O$ | $notZero_O$ |

|--------------|---------|---------|-------------|

| 0            | 0       | 0       | 0           |

| 0            | 0       | 1       | 1           |

| 0            | 1       | 0       | 1           |

| 0            | 1       | 1       | 1           |

| 1            | 0       | 0       | 1           |

| 1            | 0       | 1       | 1           |

| 1            | 1       | 0       | 1           |

| 1            | 1       | 1       | 1           |

Table 2.3: Truth table for determining whether an operand is zero or not

• If  $k_{O+} = 0$  and the operand is positive  $(msb_O = 0)$ , the operand is not zero if  $lsb_O$  is 1 (case 1), and zero otherwise (case 0).

Therefore, the condition under which the result is not zero is as Equation 2.25 indicates.

$$notZero_D = notZero_A \wedge notZero_B$$

$$= (k_{A+} > 0 \lor msb_A \lor lsb_A) \wedge (k_{B+} > 0 \lor msb_B \lor lsb_B) .$$

$$(2.25)$$

# 2.2.4 Error Study of C1 Sign Handling

The error produced by our approach when A and B have different signs and when A and B are negative is generally low. Intuitively, there is only 1 unit of difference between computing C1 or C2 of an operand. In this section, the error introduced by the proposed scheme to handle negative numbers will be studied in detail. Provided that the operands are not zero, the error occurs at the output of the antilogarithm block. Four cases may arise depending on the sign of both operands A and B. If both are positive, there is no error in comparison to the conventional logarithmic multiplier.

# A and B possess different sign

Without loss of generality, let us suppose that A < 0 and  $B \ge 0$ . If  $A \ge 0$  and B < 0, the analysis is analogous. In this scenario, let us define the variables indicated by Equations 2.26 to 2.34.

$$y_L = (y_{C2(A)} + y_B) \land (2^{n-1} - 1) , \qquad (2.26)$$

$$y'_{L} = (y_{C1(A)} + y_{B}) \land (2^{n-1} - 1) , \qquad (2.27)$$

$$k_L = k_{C2(A)} + k_B + \left( \left( \left( y_{C2(A)} + y_B \right) \land (2^{n-1}) \right) \right) >> (n-1) \right),$$

(2.28)

$$k'_{L} = k_{C1(A)} + k_{B} + \left( \left( \left( y_{C1(A)} + y_{B} \right) \land (2^{n-1}) \right) \right) >> (n-1) \right),$$

(2.29)

$$L = k_{C2(A)} * 2^{n-1} + y_{C2(A)} + k_B * 2^{n-1} + y_B$$

=  $k_L * 2^{n-1} + y_L$ , (2.30)

$$L' = k_{C1(A)} * 2^{n-1} + y_{C1(A)} + k_B * 2^{n-1} + y_B$$

=  $k_L * 2^{n-1} + y'_L$ , (2.31)

$$P = C2(2^{k_L} * (1 + \widehat{y_L})) = C2(U) , \qquad (2.32)$$

$$P'_{Neg1} = C1(2^{k'_L} * (1 + \widehat{y'_L})) = C1(V) , \qquad (2.33)$$

$$E_{Neg1} = P - P'_{Neg1} . (2.34)$$

$$E_{Neg1} = P' - P'_{Neg1} = C2(U) - C1(V)$$

=  $C2(U) - (C2(V) - 2^{-n+1}) = V - U + 2^{-n+1}$

=  $2^{k'_L} * (1 + \widehat{y'_L}) - 2^{k_L} * (1 + \widehat{y_L}) + 2^{-n+1}$

=  $2^{k_L} * (2^{k'_L - k_L} * (1 + \widehat{y'_L}) - (1 + \widehat{y_L})) + 2^{-n+1}$ . (2.35)

As in the prior theorem, two cases arise:  $k_L = k'_L$  and  $k_L > k'_L = k_L - 1$ . If  $k_L = k'_L$ , then by definition of two's and one's complement  $k_{C2(A)} \ge k_{C1(A)}$ . If  $k_{C2(A)} = k_{C1(A)}$  and  $k_{C2(B)} = k_{C1(B)}$ , the logical AND in the definition of  $y_L$  and  $y_{L'}$  has no effect and then Equation 2.36 holds. If  $k_{C2(B)} > k_{C1(B)}$ , the situation will be analogous as described by Equation 2.40.

$$E_{Neg1} = 2^{k_L} * \left( \left( 1 + \widehat{y'_L} \right) - \left( 1 + \widehat{y_L} \right) \right) + 2^{-n+1}$$

=  $2^{k_L} * \left( \widehat{y'_{C1(A)}} - \widehat{y'_{C2(A)}} + \widehat{y_B} - \widehat{y_B} \right) + 2^{-n+1}$

=  $2^{k_L} * \left( \widehat{y'_{C1(A)}} - \widehat{y'_{C2(A)}} \right) + 2^{-n+1}$ . (2.36)

The difference between  $\widehat{y_{C2(A)}}$  and  $\widehat{y_{C1(A)}}$  is as studied in Equations 2.37 and 2.38, where the logical AND of Equations 2.26 and 2.27 has no effect.

$$y_{C2(A)} - y_{C1(A)} = (C2(A) << \neg (k_{C2(A)})) \land (2^{n-1} - 1) - (C1(A) << \neg (k_{C1(A)})) \land (2^{n-1} - 1) = (C2(A) - C1(A)) << n - k_{C1(A)} - 1 = 2^{n-k_{C1(A)}-1} ,$$

$$\widehat{y_{C2(A)}} - \widehat{y_{C1(A)}} = 2^{n-k_{C1(A)}-1}/2^{n-1} = 2^{-k_{C1(A)}} .$$

(2.38)

Introducing Equation 2.37 into Equation 2.36 it is possible to get Equation 2.39.

$$E_{Neg1} = 2^{k_L} * (-2^{-k_{C1(A)}}) + 2^{-n+1} \approx -2^{k_L - k_{C1(A)}} .$$

(2.39)

In this case, the relative error is  $(-2^{k_L-k_{C1(A)}})/(2^{k_L}*(1+\widehat{y_L})) > -1/2^{k_{C1(A)}}$ .

If  $k_{C2(A)} = k_{C1(A)} + 1$ , then C2(A) is a power of two and  $y_{C2(A)} = 0$ , and  $y_L$  does not propagate any carry. Thus the logical AND of its definition has no effect. On the other hand, if  $k_L = k'_L$ , then  $k_{C2(B)} = k_{C1(B)}$  and  $y'_L$  must propagate to compensate  $k_{C2(A)} = k_{C1(A)} + 1$ , i.e.  $y'_L = y_{C1(A)} + y_B - 1$ . In this scenario, Equation 2.40 holds.

$$E_{Neg1} = 2^{k_L} * \left( (1 + \widehat{y_{C1(A)}} + \widehat{y_B} - 1)/2 - (1 + \widehat{y_B}) \right) + 2^{-n+1}$$

$$< 2^{k_L} * \left( (\widehat{y_{C1(A)}} + \widehat{y_B}) - (1 + \widehat{y_B}) \right) + 2^{-n+1}$$

$$\approx 2^{k_L} * \left( \widehat{y_{C1(A)}} - 1 \right) .$$

(2.40)

Therefore, the relative error is  $(2^{k_L} * (\widehat{y_{C1(A)}} - 1))/(2^{k_L} * (1 + \widehat{y_L})) = (\widehat{y_{C1(A)}} - 1)/(1 + \widehat{y_L}) \to 0$ . As C2(A) is a power of two,  $y_{C2(A)}=0$  and consequently  $y_{C1(A)}$  will possess several '1's in the most significant positions. For instance, consider n=8 bits, A=-64, C2(A)=64 and then  $k_{C2(A)}=6$ ,  $y_{C2(A)}=0$  and  $\widehat{y_{C2(A)}}=0$ . On the other hand, C1(A)=63,  $k_{C1(A)}=5$ ,  $y_{C1(A)}=120=11111000b$  and  $\widehat{y_{C1(A)}}=0.9375$ .

If  $A \ge 0$  and B < 0, similar expressions can be obtained.

#### A and B are negative

In the scenario where A < 0 and B < 0, let us define the variables indicated by Equations 2.41 to 2.49.

$$y_L = (y_{C2(A)} + y_{C2(B)}) \land (2^{n-1} - 1) , \qquad (2.41)$$

$$y'_{L} = (y_{C1(A)} + y_{C1(B)}) \land (2^{n-1} - 1) , \qquad (2.42)$$

$$k_L = k_{C2(A)} + k_{C2(B)} \tag{2.43}$$

+

$$\left(\left(\left(y_{C2(A)} + y_{C2(B)}\right) \land (2^{n-1})\right) >> (n-1)\right)$$

,

$$k'_{L} = k_{C1(A)} + k_{C1(B)} + (((y_{C1(A)} + y_{C1(B)}) \land (2^{n-1})) >> (n-1)), \qquad (2.44)$$

$$L = k_{C2(A)} * 2^{n-1} + y_{C2(A)} + k_{C2(B)} * 2^{n-1} + y_{C2(B)}$$

=  $k_L * 2^{n-1} + y_L$ , (2.45)

$$L' = k_{C1(A)} * 2^{n-1} + y_{C1(A)} + k_{C1(B)} * 2^{n-1} + y_{C1(B)}$$

=  $k_L * 2^{n-1} + y'_L$ , (2.46)

$$P = 2^{k_L} * (1 + \widehat{y_L}) , \qquad (2.47)$$

$$P'_{Neg2} = 2^{k'_L} * (1 + \widehat{y'_L}) , \qquad (2.48)$$

$$E_{Neg2} = P - P'_{Neg2} = 2^{k_L} * \left( (1 + \widehat{y_L}) - 2^{k'_L - k_L} * (1 + \widehat{y'_L}) \right) .$$

(2.49)

Again, two possible scenarios arise: either  $k_L = k'_L$ , or  $k_L > k'_L$ . If  $k_L = k'_L$ , then by definition of two's and one's complement  $k_{C2(A)} \ge k_{C1(A)}$  and  $k_{C2(B)} \ge k_{C1(B)}$ . If  $k_{C2(A)} = k_{C1(A)}$  and  $k_{C2(B)} = k_{C1(B)}$ , then the logical AND in Equations 2.41 and 2.42 have no effect and applying Equation 2.38 it is possible to prove that Equation 2.50 holds.

$$E_{Neg2} = 2^{k_L} * \left( \widehat{y_{C2(A)}} - \widehat{y_{C1(A)}} + \widehat{y_{C2(B)}} - \widehat{y_{C1(B)}} \right)$$

=  $2^{k_L} * \left( 2^{-k_{C1(A)}} + 2^{-k_{C1(B)}} \right).$  (2.50)

In this case, the relative error would be  $2^{k_L} * (2^{-k_{C1(A)}} + 2^{-k_{C1(B)}})/(2^{k_L} * (1 + \widehat{y_L})) < 2^{-k_{C1(A)}} + 2^{-k_{C1(B)}}.$

If  $k_L = k'_L$  and  $k_{C2(A)} > k_{C1(A)} = k_{C2(A)} - 1$ , then C2(A) is a power of two and then  $y_{C2(A)} = 0$ . In this scenario,  $k_{C2(B)} = k_{C1(B)}$ , as otherwise  $(k_{C2(A)} + k_{C2(B)}) - (k_{C1(A)} + k_{C1(B)}) = 2$ , and this cannot be compensated by a carry out propagated from  $y'_L$  to  $k'_L$ . On the other hand, a difference of just 1 can be compensated if  $y'_L$  propagates, and then  $\widehat{y'_L} = \widehat{y_{C1(A)}} + \widehat{y_{C1(B)}} - 1$ . Thus, Equation 2.51 holds.

$$E_{Neg2} = 2^{k_L} * \left( (1 + \widehat{y_{C2(B)}}) - (1 + \widehat{y_{C1(A)}} + \widehat{y_{C1(B)}} - 1) \right)$$

=  $2^{k_L} * \left( 1 - \widehat{y_{C1(A)}} + 2^{-k_{C1(B)}} \right) < 2^{k_L - k_{C1(B)}}$ . (2.51)

It must be noted that if C2(A) is a power of 2, then C1(A) and consequently  $y_{C1(A)}$  will possess several '1's in the most significant positions. Thus,  $(1 - \widehat{y_{C1(A)}}) \rightarrow 0$ . Hence, the relative error is around  $2^{k_L - k_{C1(B)}}/(2^{k_L} * (1 + \widehat{y_L})) < 2^{-k_{C1(B)}}$ . A similar expression can be found if  $k_L = k'_L$  and  $k_{C2(B)} > k_{C1(B)} = k_{C2(B)} - 1$ .

If  $k_L > k'_L$ , several scenarios may happen depending on the relation between  $k_{C2(A)}$  and  $k_{C1(A)}$ , and  $k_{C2(B)}$  and  $k_{C1(B)}$ . If  $k_{C2(A)} = k_{C1(A)}$  and  $k_{C2(B)} = k_{C1(B)}$ , then  $y_L$  propagates a carry-out while  $y'_L$  does not. Thus,  $\widehat{y_L} = \widehat{y_{C2(A)}} + \widehat{y_{C2(B)}} - 1$ ,  $k_L = k'_L + 1$  and Equation 2.52

holds.

$$E_{Neg2} = 2^{k_L} * \left( \left( 1 + \widehat{y_{C2(A)}} + \widehat{y_{C2(B)}} - 1 \right) - \left( 1 + \widehat{y_{C1(A)}} + \widehat{y_{C1(B)}} \right) / 2 \right) \right)$$

$$= 2^{k_L} * \left( 2^{-k_{C1(A)}} + 2^{-k_{C1(B)}} - 1 / 2 \right)$$

$$< 2^{k_L} * \left( 2^{-k_{C1(A)}} + 2^{-k_{C1(B)}} \right) .$$

(2.52)

In this case again the relative error is lower than  $2^{-k_{C1(A)}} + 2^{-k_{C1(B)}}$ . If  $k_L > k'_L$ ,  $k_{C2(A)} > k_{C1(A)} = k_{C2(A)} - 1$  and  $k_{C2(B)} = k_{C1(B)}$ , then  $y_{C2(A)}$  is zero, so  $y_L$  does not propagate a carry-out and neither does  $y'_L$ , otherwise  $k_L = k'_L$ . Thus,  $k_L = k'_L + 1$ . Hence, the logical AND in Equations 2.41 and 2.42 has no effect and Equation 2.53 holds.

$$E_{Neg2} = 2^{k_L} * \left( (1 + \widehat{y_{C2(B)}}) - (1 + \widehat{y_{C1(A)}} + \widehat{y_{C1(B)}})/2) \right)$$

$$= 2^{k_L - 1} * \left( 1 + 2 * \widehat{y_{C2(B)}} - \widehat{y_{C1(B)}} - \widehat{y_{C1(A)}} \right)$$

$$< 2^{k_L - 1} * \left( 1 + \widehat{y_{C2(B)}} - \widehat{y_{C1(B)}} - \widehat{y_{C1(A)}} \right)$$

$$= 2^{k_L - 1} * \left( 1 + 2^{-k_{C1(B)}} - \widehat{y_{C1(A)}} \right)$$

$$\approx 2^{k_L - k_{C1(B)} - 1} .$$

(2.53)

In this case the relative error is lower than  $(2^{k_L-k_{C1(B)}-1})/(2^{k_L}*(1+\widehat{y_L})) < 2^{-k_{C1(B)}-1}$ . If  $k_{C2(B)} > k_{C1(B)} = k_{C2(B)} - 1$  and  $k_{C2(A)} = k_{C1(A)}$ , an analogous expression can be found.

The last case to be studied is  $k_L > k'_L$ ,  $k_{C2(A)} > k_{C1(A)} = k_{C2(A)} - 1$  and  $k_{C2(B)} > k_{C1(B)} = k_{C2(B)} - 1$ . In this scenario, C2(A) and C2(B) are power of two, so  $y_{C2(A)}$ ,  $y_{C2(B)}$  and  $y_L$  are zero, while  $y_{C1(A)}$  and  $y_{C1(B)}$  will have several '1's in the most significant positions (at least

one) so  $y'_L$  will propagate a carry-out to  $k'_L$  and then  $k_L = k'_L + 1$ . Thus,  $\widehat{y'_L} = \widehat{y_{C1(A)}} + \widehat{y_{C1(B)}} - 1$ and Equation 2.54 holds.

$$E_{Neg2} = 2^{k_L} * \left(1 - \left(1 + \widehat{y_{C1(A)}} + \widehat{y_{C1(B)}} - 1\right)/2\right)\right)$$

=  $2^{k_L} * \left(1 - \left(\widehat{y_{C1(A)}} + \widehat{y_{C1(B)}}\right)/2\right)\right).$  (2.54)

For the same reasons as in Section 2.2.4,  $y_{C1(A)}$  and  $y_{C1(B)}$  will have several '1's in the most significant positions and will be close to 1. Thus,  $(\widehat{y_{C1(A)}} + \widehat{y_{C1(B)}})/2 \rightarrow 1$ , and then the error shown in Equation 2.54 will tend to zero, and so will do the relative error.

#### Corner cases

Despite the generally low error when employing the one's complement, there are some special cases that need careful attention. In the prior proofs it has been considered that, without loss of generality, when C2(A) is a power of two, then  $y_{C2(A)}$  is 0 and consequently C1(A) and  $y_{C1(A)}$  will possess several '1's in the most significant positions. This is valid but for two special cases, namely: -1 and -2.

Following Figure 2.9, it is possible to observe that when A = -1,  $C1(A) = A_+ = 0$ ,  $k_{C1(A)} = k_{A_+} = 0$  and op1 = 0. Hence, multiplying by -1 works as adding the neutral element in the LNS domain. It must be noted, that according to Table 2.3 the result will not be converted to zero, despite the fact that  $A_+ = 0$ . Furthermore, if B = -1 and consequently op2 = 0, the antilogarithm will produce D = 1 anyway.

When A = -2,  $C1(A) = A_{+} = 1$ ,  $k_{C1(A)} = k_{A+} = 0$  and op1 = 0 and  $y_{C1(A)} = 0$ . Hence, a similar situation arises, but with the drawback of producing a larger error, as we are actually multiplying by -2. Once again, if B = -1 or B = -2, the result given by the antilogarithm

will be D = 1.

This situation is different when we have larger power of two numbers, because  $k_{A+} > 0$  and there will be at least a MSB equal to '1' in  $y_{C1(A)}$ . For instance, A = -4,  $C1(A) = A_+ = 3$ ,  $k_{A+} = 1$  and  $y_{C1(A)} = 2^{n-2}$ , i.e.  $\widehat{y_{C1(A)}} = 0.5$ .

#### Error interpretation