## UC Berkeley UC Berkeley Electronic Theses and Dissertations

#### Title

Specification Mining: New Formalisms, Algorithms and Applications

#### Permalink

https://escholarship.org/uc/item/4027r49r

## Author

Li, Wenchao

# Publication Date 2013

Peer reviewed|Thesis/dissertation

### Specification Mining: New Formalisms, Algorithms and Applications

by

Wenchao Li

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

$\mathrm{in}$

#### Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Sanjit A. Seshia, Chair Professor Andreas Kuehlmann Professor Francesco Borrelli

Fall 2013

#### Specification Mining: New Formalisms, Algorithms and Applications

Copyright 2013 by Wenchao Li

#### Abstract

#### Specification Mining: New Formalisms, Algorithms and Applications

by

#### Wenchao Li

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

#### University of California, Berkeley

#### Professor Sanjit A. Seshia, Chair

Specification is the first and arguably the most important step for formal verification and correct-by-construction synthesis. These tasks require understanding precisely a design's intended behavior, and thus are only effective if the specification is created right. For example, much of the challenge in bug finding lies in finding the specification that mechanized tools can use to find bugs. It is extremely difficult to manually create a complete suite of goodquality formal specifications, especially given the enormous scale and complexity of designs today. Many real-world experiences indicate that poor or the lack of sufficient specifications can easily lead to misses of critical bugs, and in turn design re-spins and time-to-market slips.

This dissertation presents research that mitigates this manual and error-prone process through automation. The overarching theme is specification mining – the process of inferring likely specifications by observing a design's behaviors. We explore formalisms and algorithms to mine specifications from different sources, and demonstrate that the mined specifications are useful if not essential for a variety of applications such as verification, diagnosis and synthesis. The first part of the dissertation presents two approaches to mine specifications dynamically from simulation or execution traces. The first approach offers a simple but effective template-based remedy to the aforementioned problem. The second approach presents a novel formalism of specification mining based on the notion of sparse coding, which can learn latent structures in an unsupervised setting, and thus are not restricted by predefined templates. Additionally, we show that the mined specifications from both approaches can be used to localize bugs effectively.

In the second part of the dissertation, we study the problem of synthesis from temporal logic specifications. This synthesis approach offers an attractive proposition – one can automatically construct a functionally correct system from its behavioral description. The downside, however, is that it completely relies on the user to not only specify the intended behaviors of the system but also the assumptions on the environment. The latter is especially tricky in practice as environment assumptions are often implicit knowledge and seldom documented. We propose a framework that learns assumptions from the counterstrategies of an unrealizable specification to systematically guide it towards realizability. We further show that, the proposed counterstrategy-guided assumption mining approach enables the automatic synthesis of a new class of semi-autonomous controllers, called human-in-the-loop (HuIL) controllers. A crucial component of such a controller is an advisory that determines when to switch control from the autonomous controller to the human operator. We formalize the criteria that characterize a HuIL controller, by taking into account of human factors such as response time, and describe how to construct the advisory using assumption mining.

Human inputs are still critical in specification. In the last part of this dissertation, we describe two efforts on broadening the scope of specification mining with creative use of human inputs. The first is the design of a crowdsourced specification mining game called CrowdMine. The main idea of CrowdMine is to transform a design's traces into images and leverage the human ability to recognize patterns in images to assist the process of mining specifications. The second effort examines the feasibility of converting natural language specifications to formal specifications, with a focus on how specification mining encapsulated in a natural language processing (NLP) layer may assist non-expert users of formal methods at the requirement stage of a design.

To my family.

# Contents

| C  | Contents |         |                                                                                                             |   |   | ii   |

|----|----------|---------|-------------------------------------------------------------------------------------------------------------|---|---|------|

| Li | st of    | Figure  | es                                                                                                          |   |   | vi   |

| Li | st of    | Tables  | S                                                                                                           |   |   | viii |

| 1  | Intr     | oducti  | ion                                                                                                         |   |   | 1    |

|    | 1.1      | Thesis  | s Statement                                                                                                 |   |   | 3    |

|    | 1.2      | Thesis  | $s$ Contributions $\ldots$ |   |   | 4    |

|    |          | 1.2.1   | New Formalisms                                                                                              | • |   | 4    |

|    |          | 1.2.2   | New Algorithms                                                                                              | • |   | 5    |

|    |          | 1.2.3   | New Applications                                                                                            | • |   | 6    |

|    |          | 1.2.4   | Broadening the Scope of Specification Mining                                                                | • |   | 7    |

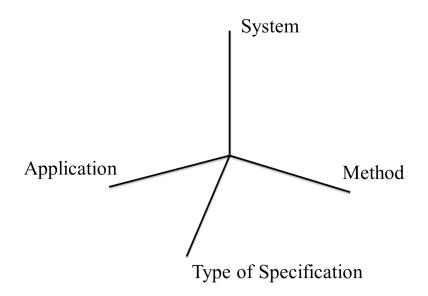

|    | 1.3      | Relate  | ed Work                                                                                                     | • |   | 8    |

|    |          | 1.3.1   | System                                                                                                      | • |   | 8    |

|    |          | 1.3.2   | Type of Specification                                                                                       | • |   | 9    |

|    |          | 1.3.3   | Method                                                                                                      | • |   | 11   |

|    |          | 1.3.4   | Application                                                                                                 | • |   | 12   |

|    | 1.4      | Thesis  | Organization                                                                                                | • | • | 13   |

| 2  | Pre      | liminar | ries                                                                                                        |   |   | 15   |

|    | 2.1      | Notati  | ion                                                                                                         |   |   | 15   |

|    | 2.2      | Autom   | nata                                                                                                        |   |   | 16   |

|    |          | 2.2.1   | Büchi Automaton                                                                                             |   |   | 16   |

|    |          | 2.2.2   | Finite-State Transducers                                                                                    |   |   | 16   |

|    | 2.3      | Linear  | r Temporal Logic                                                                                            | • |   | 17   |

|    |          | 2.3.1   | Syntax and Semantics                                                                                        |   |   | 17   |

|    |          | 2.3.2   | Satisfiability and Realizability                                                                            |   |   | 18   |

|    | 2.4      | Specifi | ication Mining with Templates                                                                               | • |   | 19   |

| ~ |                                               | quirement Generation and Error Localization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 |                                               | ckground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 3.1                                           | Formalism and Notations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |                                               | 3.1.1 Transition System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 2.0                                           | 3.1.2 Traces and Subtraces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 3.2                                           | Running Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4 |                                               | ecification Mining for Digital Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 4.1                                           | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 4.2                                           | Preliminaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |                                               | 4.2.1 Notations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 4.0                                           | 4.2.2 Specification Templates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 4.3                                           | Mining Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                                               | 4.3.1 Mining from Delta Traces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                               | 4.3.2 Merging Simple Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                               | 4.3.3 Specification Ranking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 4.4                                           | Error Localization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 4.5                                           | Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                               | 4.5.1 Benchmarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                                               | 4.5.2 Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 1.0                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 4.6                                           | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 |                                               | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 |                                               | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | A S                                           | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | <b>A S</b><br>5.1                             | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | <b>A S</b><br>5.1                             | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | <b>A S</b><br>5.1                             | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | <b>A S</b><br>5.1<br>5.2                      | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | <b>A S</b> 5.1 5.2 5.3                        | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | <b>A S</b> 5.1 5.2 5.3                        | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | <b>A S</b> 5.1 5.2 5.3                        | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | <b>A S</b> 5.1 5.2 5.3                        | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | <b>A S</b> 5.1 5.2 5.3 5.4                    | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | <b>A S</b> 5.1 5.2 5.3 5.4                    | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | <b>A S</b> 5.1 5.2 5.3 5.4                    | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | <b>A S</b> 5.1 5.2 5.3 5.4                    | Summary and Discussion         Sparse Coding Framework for Specification Mining         Introduction         Background         5.2.1         Traces and Matrices         5.2.2         Bipartite Graphs         Specification Formalism – Basis Subtraces         Algorithm: Sparsity-Constrained Biclique Cover         5.4.1         Formulation as a Sparse Coding Problem         5.4.2         Solving the Sparse Coding Problem         5.4.3         Example Illustration         Application to Error Localization         5.5.1         Problem Definition         5.5.2         Localization by Construction                                                                                                                                                                                                                                                                                                                                   |

| 5 | <b>A S</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Summary and DiscussionSparse Coding Framework for Specification MiningIntroductionBackground5.2.1 Traces and Matrices5.2.2 Bipartite GraphsSpecification Formalism – Basis SubtracesAlgorithm: Sparsity-Constrained Biclique Cover5.4.1 Formulation as a Sparse Coding Problem5.4.2 Solving the Sparse Coding Problem5.4.3 Example Illustration5.5.1 Problem Definition5.5.2 Localization by Construction5.5.3 Example Illustration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5 | <b>A S</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Summary and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | <b>A S</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Summary and Discussion         Sparse Coding Framework for Specification Mining         Introduction         Background         5.2.1         Traces and Matrices         5.2.2         Bipartite Graphs         Specification Formalism – Basis Subtraces         Algorithm: Sparsity-Constrained Biclique Cover         5.4.1         Formulation as a Sparse Coding Problem         5.4.2         Solving the Sparse Coding Problem         5.4.3         Example Illustration         Application to Error Localization         5.5.1         Problem Definition         5.5.2         Localization by Construction         5.5.3         Example Illustration         Aspelication to Error Localization         5.5.1         Troblem Definition         5.5.3         Example Illustration         Station by Construction         5.5.3         Example Illustration         Station by Construction         5.6.1         Theoretical Guarantees |

iii

|    | 5.8 | 5.7.2    Bug Localization    6      Summary    6           |

|----|-----|------------------------------------------------------------|

| 6  | Cro | wdsourced Specification Mining 6                           |

| Ŭ  | 6.1 | Introduction                                               |

|    | 6.2 | CrowdMine – Game Design                                    |

|    | 0.2 | 6.2.1 CrowdMine1: An Open-Loop Design                      |

|    |     | 6.2.2 CrowdMine2: A Closed-Loop Design                     |

|    | 6.3 | Discussion                                                 |

| II | Ass | sumption Mining for LTL Synthesis 72                       |

| 7  | Bac | kground 73                                                 |

|    | 7.1 | Synthesis from $GR(1)$ Specifications                      |

|    |     | 7.1.1 Generalized Reactivity (1) Specifications            |

|    |     | 7.1.2 Games and Strategies                                 |

|    |     | 7.1.3 Counterstrategy Graph                                |

|    | 7.2 | Related Work                                               |

| 8  | Min | ing Environment Assumptions 80                             |

|    | 8.1 | Solution Overview                                          |

|    | 8.2 | Version-Space Learning with Templates                      |

|    | 8.3 | Experimental Results                                       |

|    |     | 8.3.1 AMBA AHB Bus Protocol                                |

|    |     | 8.3.2 Generalized Buffer                                   |

|    |     | 8.3.3 Robotic Vehicle Controller                           |

|    | 8.4 | Summary                                                    |

| 9  | Hur | nan-in-the-Loop Controller Synthesis 92                    |

|    | 9.1 | Introduction                                               |

|    | 9.2 | Motivating Example                                         |

|    | 9.3 | Human-in-the-Loop Controller                               |

|    |     | 9.3.1 Agents as Automata 9                                 |

|    |     | 9.3.2 Criteria for Human-in-the-loop Controllers           |

|    | 9.4 | Controller Synthesis                                       |

|    |     | 9.4.1 Weighted Counterstrategy Graph                       |

|    |     | 9.4.2 Counterstrategy-Guided Synthesis of HuIL Controllers |

|    |     | 9.4.3 Switching from Human Operator to Auto-Controller     |

|    | 9.5 | Experimental Results                                       |

|    |     | 9.5.1 Car-Following                                        |

|    |     | 9.5.2 Gridworld Hallway                                    |

| 9.6    | 6 Additional Related Work                                              | 107 |

|--------|------------------------------------------------------------------------|-----|

| 9.7    |                                                                        | 108 |

|        | ining Assumptions from Natural Language Specifications                 | 109 |

|        | .1 Related Work in NLP                                                 | 110 |

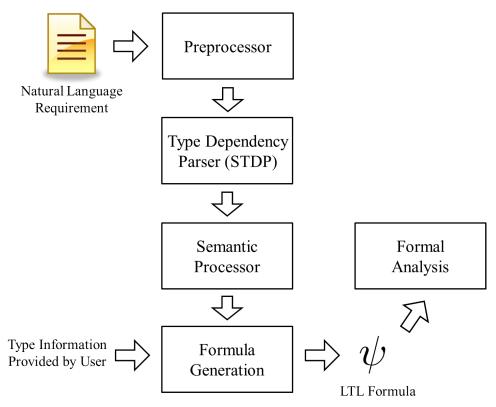

| 10     | .2 Natural Language to LTL Formula                                     | 111 |

|        | 10.2.1 Preprocessor $\ldots$                                           | 111 |

|        | 10.2.2 Stanford Type Dependency Parser (STDP)                          | 112 |

|        | 10.2.3 Semantic Processor                                              | 113 |

|        | 10.2.4 Formula Generation                                              | 115 |

| 10     | .3 Case Study                                                          | 117 |

| 10     | .4 Summary                                                             | 121 |

| 11 C   | analysian and Estuna Wark                                              | 122 |

|        | onclusion and Future Work                                              |     |

|        | .1 Closing Remarks                                                     | 122 |

| 11     | .2 Future Work                                                         | 123 |

|        | 11.2.1 Combining Sparse Coding and Automata-Based Specification Mining | 123 |

|        | 11.2.2 Compositional Analysis                                          | 123 |

|        | Assumption Mining for Verification                                     | 124 |

|        | Contract-Based Synthesis                                               | 124 |

|        | 11.2.3 Improving Sparse Coding                                         | 125 |

|        | 11.2.4 Other Application Domains                                       | 125 |

| Biblio | ography                                                                | 126 |

# List of Figures

| $\begin{array}{c} 1.1 \\ 1.2 \end{array}$                   | Thesis overview                                                                                                                                                                                                                                                                                                                                      | 4<br>8                                             |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

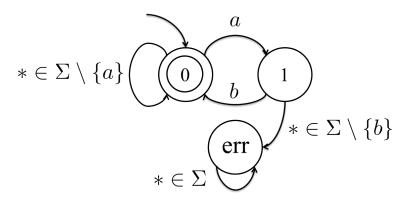

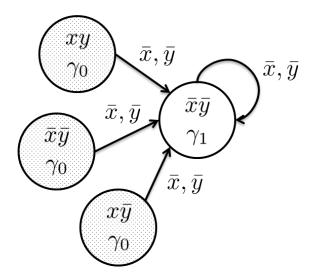

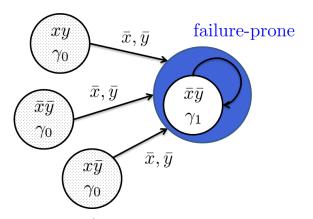

| 2.1                                                         | Monitor for $\mathbf{G} \ (a \to \mathbf{X} \ b)$                                                                                                                                                                                                                                                                                                    | 19                                                 |

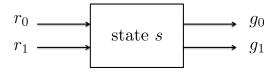

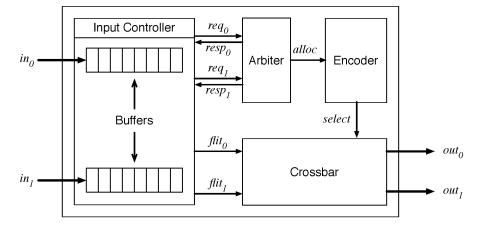

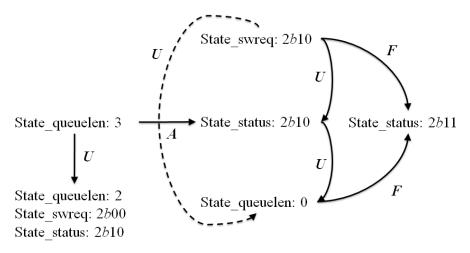

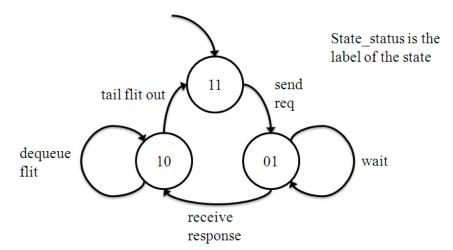

| $3.1 \\ 3.2$                                                | A two-port arbiter design                                                                                                                                                                                                                                                                                                                            | 23<br>23                                           |

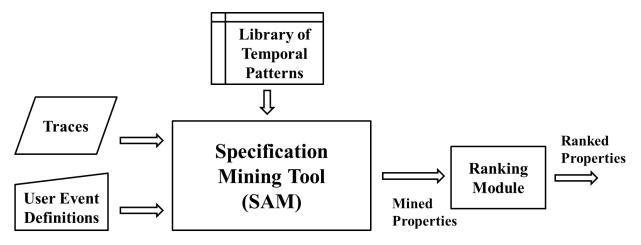

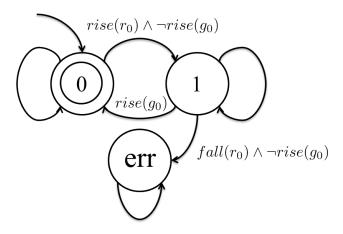

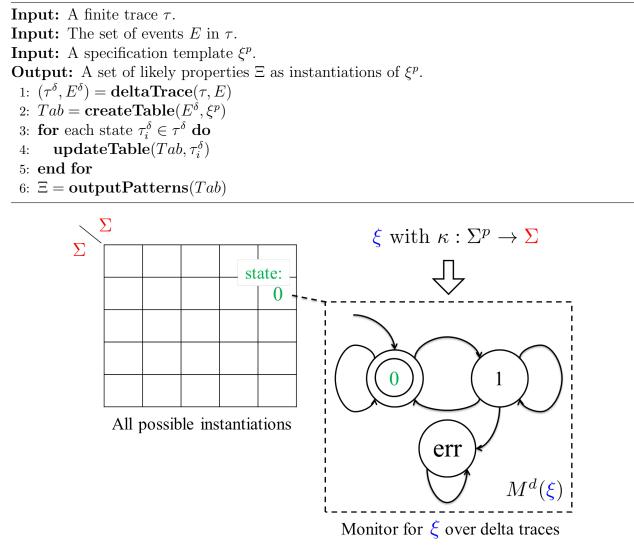

| 4.1<br>4.2<br>4.3                                           | High-level architecture of the proposed specification mining tool SAM Equivalent delta trace of the trace shown in Figure 3.2                                                                                                                                                                                                                        | 26<br>29                                           |

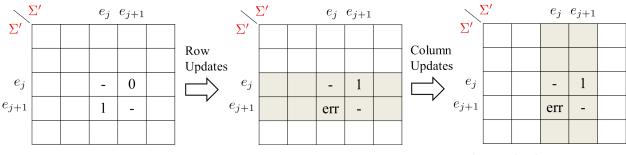

| 4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9                      | ton is deterministic)                                                                                                                                                                                                                                                                                                                                | 30<br>31<br>32<br>35<br>38<br>39<br>39             |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9 | Bipartite graph $G_D$ .Biclique edge cover $Cov$ .A subtrace as superimposition of two basis subtraces.A normal trace of a 2-port round-robin arbiterThree basis subtraces computed via sparse coding.Subtrace correctness characterization using basis subtraces.Bit flip on $g_1$ at cycle 97.Error subtrace as identified.Two error explanations. | 46<br>47<br>50<br>53<br>54<br>55<br>57<br>58<br>58 |

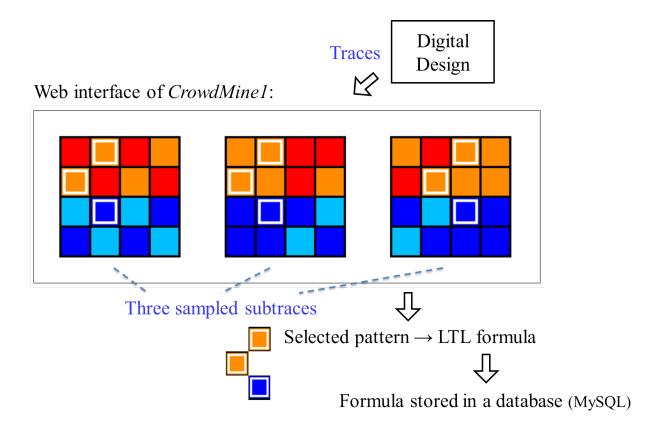

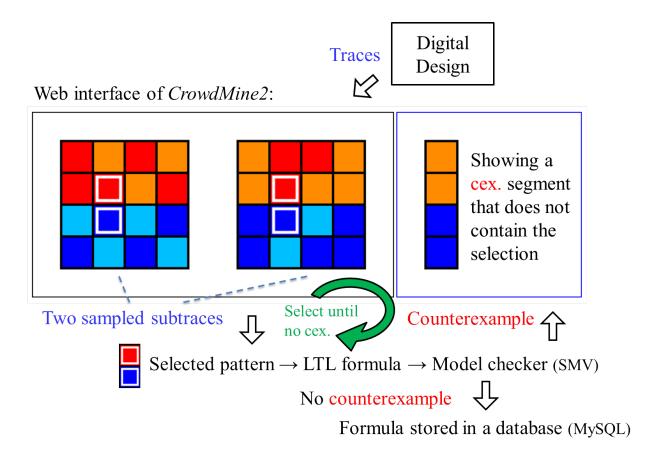

| $6.1 \\ 6.2 \\ 6.3$                                         | Overview of CrowdMine1.Top ranked patterns obtained in CrowdMine1.Overview of CrowdMine2                                                                                                                                                                                                                                                             | 66<br>67<br>68                                     |

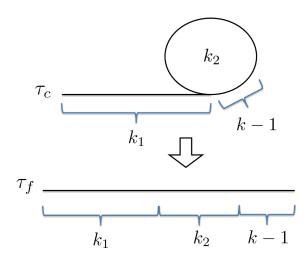

| 6.4        | Finding contradicting subtraces in a counterexample.                                                            | 69  |

|------------|-----------------------------------------------------------------------------------------------------------------|-----|

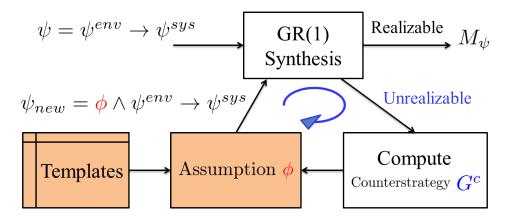

| 8.1        | Counterstrategy-guided synthesis enabled by assumption mining (the highlighted portions are our contributions). | 82  |

| 8.2<br>8.3 | Counterstrategy graph $G^c$ for unrealizable specification $\psi$                                               | 84  |

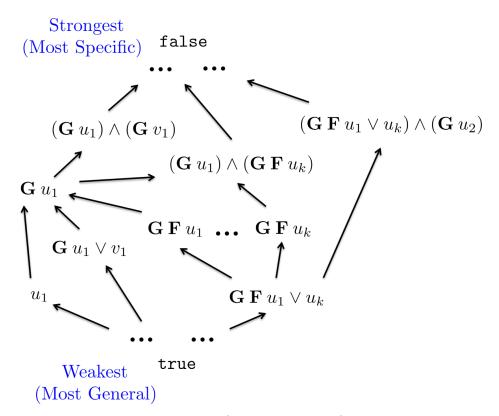

|            | to the most specific hypothesis.                                                                                | 86  |

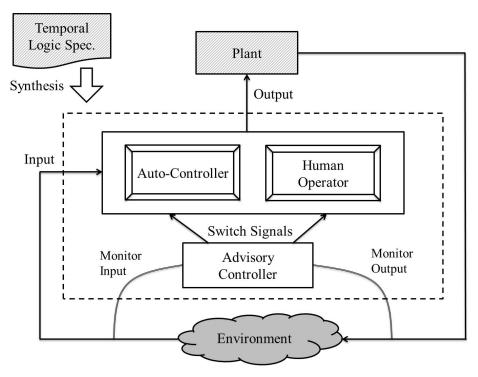

| 9.1        | Human-in-the-Loop Controller: Component Overview and Synthesis from Speci-<br>fication                          | 94  |

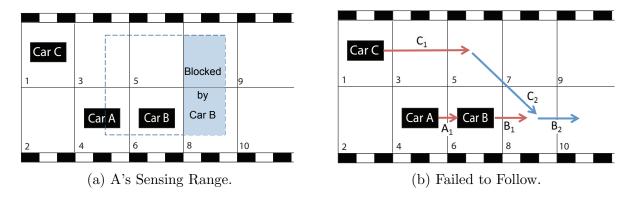

| 9.2        | Controller Synthesis – Car A Following Car B                                                                    | 94  |

| 9.3        | Condensed graph $\hat{G}^c$ for $G^c$ (Figure 8.2) after contracting all SCCs.                                  | 99  |

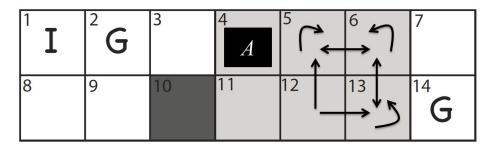

| 9.4        | Gridworld hallway example.                                                                                      | 105 |

| 9.5        | Illustration of $\phi$ : arrows indicate all possible movements of car <i>B</i> from the current                |     |

|            | position to the next position.                                                                                  | 107 |

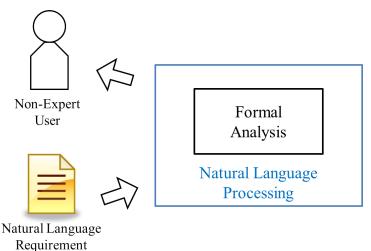

| 10.1       | Non-expert user uses formal methods to analyze problems in a design document,                                   |     |

|            | facilitated by a NLP layer                                                                                      | 110 |

|            | Workflow: $NL \rightarrow LTL \rightarrow$ formal analysis                                                      | 112 |

|            | Dependencies generated using STDP                                                                               | 113 |

|            | Predicate graph after the application of type rules.                                                            | 115 |

| 10.5       | Transition of Regulator_Mode based on Requirement 13 and 15                                                     | 121 |

# List of Tables

| 2.2  | Mathematical Notations15Abbreviations16Semantics of LTL16  |

|------|------------------------------------------------------------|

| 4.1  | Performance results on generation of likely specifications |

| 4.2  | Bug localization results on the CMP router                 |

| 10.1 | Formula Translation Rules                                  |

| 10.2 | Isolette requirements in English                           |

#### Acknowledgments

This dissertation would not have been possible without the help of many people over the years. First and foremost, I would like to thank my advisor, Sanjit A. Seshia, for his guidance and support. His contagious enthusiasm, intense motivation and determination, and seemingly limitless patience, have set an example that I can only hope to imitate. I am truly grateful to have had the opportunity to work and learn under his mentorship.

I would also like to thank Prof. Andreas Kuehlmann and Prof. Francesco Borrelli for reviewing my dissertation and giving me invaluable feedback. I would also like thank Prof. Rastislav Bodík for chairing my qualifying exam committee. They have given me much critical and constructive feedback that helped shape this thesis.

I am also thankful to my internship mentors at Microsoft Research, Redmond and SRI International, Menlo Park: Dr. Alessandro Forin, Dr. Natarajan Shankar and Dr. Shalini Ghosh. Some of the ideas on specification mining were first developed while I was working as an intern with Dr. Alessandro Forin during the summer of 2008, in Microsoft Research, Redmond. He is always very resourceful and has given me much help and advice. I am thankful to Dr. Natarajan Shankar, Dr. Shalini Ghosh and other amazing researchers at SRI International for the intriguing conversations, insightful feedback, and overall the fun and productive times at Menlo Park. Dr. Shalini Ghosh really spearheaded the work on converting natural language requirements to their formal representations. Her inputs were critical to the development of the work on connecting natural language processing to specification mining. I would also like to thank Dr. Natarajan Shankar for his continual encouragement and guidance. His expertise deeply impresses me, and if anyone asks about my role models, Shankar would definitely be one of them. I am also grateful to my other collaborators: Lili Dworkin, Dorsa Sadigh, Daniel Elenius, Prof. Somesh Jha and Prof. S. Shankar Sastry. Some of the work done in this dissertation could not have been possible without their assistance and guidance. I would also like to thank Prof. Orna Kupferman who visits Berkeley regularly in the summers, during which we have had many fruitful discussions. Her depth of knowledge and rigor in approach exemplify the meaning of a world-class researcher. She is, without a doubt, a constant source of my inspiration.

During my tenure as a graduate student at Berkeley, I also had the opportunity to work alongside some of the most talented and creative people colleagues and friends. The list include, but not limited to: Daniel Holcomb, Bryan Brady, Susmit Jha, Jia Zou, Chenjie Gu, Hao Zhang, Qi Zhu, Yang Yang, Haibo Zeng, Wei Zheng, Qiliang Xu, Yenhao Chen, Liangpeng Guo, Chung-Wei Lin, Alberto Puggelli, Pierluigi Nuzzo, Mehdi Maasoumy, Xuening Sun, Tobias Welp, Baruch Sterin, Sayak Ray, Aadithya Karthik, Prateek Bhanshali, Luigi Di Guglielmo, Alexandre Donze, Rüdiger Ehlers, Indranil Saha, Rohit Sinha, Dorsa Sadigh, Jonathan Kotker, Zach Wasson, Wei Yang Tan, Garvit Juniwal, Nishant Totla, Ankush Desai and Daniel Fremont.

Last but not least, I would like to thank my family, for their unadulterated and unconditional love and support. My parents are always supportive of my choices, and many times at their own sacrifices. Without them, I would not have been able to achieve my goals. My wife, Nuo, has worked alongside with me also as a Ph.D. student in Electrical Engineering and Computer Sciences at UC Berkeley. She is the most loving and caring person I know. Her wonderful smile brightens my every day at Berkeley.

# Chapter 1 Introduction

We live in a world of ubiquitous computing. From home appliances, to smart phones, to cars, we constantly engage and interact with computing devices. It has been projected that there will be over 1,000 embedded devices per person by 2015 [Joh08]. However, a problem that arises from ubiquitous computing is the potential proliferation of bugs, where even tiny bugs can result in large-scale failures, e.g., a single bit error brought down all Amazon S3 servers in July 20, 2008 [Tea08]. The stakes are even higher for safety-critical systems, such as pacemakers, auto-pilot systems and automotive control systems, where a failure may result not only in financial losses but also loss of human lives.

The proliferation of computing devices, shrinking of semiconductor fabrication process nodes, as well as increase in design complexity are making the already challenging problem of providing assurance for these devices an even more daunting task. In fact, the dominant problem faced by engineers today lies not in creating *new* designs, but in creating them *correctly. Verification* and *correct-by-construction synthesis*<sup>1</sup> are two main approaches for providing such assurances. In [Ses12], the author has identified *the lack of good-quality specifications* as one of the major problems that still plagues these two fields. We elaborate on this below.

#### Verification:

Design and verification engineers now have an arsenal of tools that they can apply to verify computing systems. However, despite decades of efforts, especially in automation, the cost of verification is steadily rising. It has been estimated that verification and validation makes up about 60-70 percent of the total development cost of a processor or a system-on-a-chip (SoC) design [BAM03]. According to International Business Strategies, the cost of verification and validation makes up addition will soon completely dwarf the rest of the overall design cost as technology scales

<sup>&</sup>lt;sup>1</sup>The term "synthesis" here refers to the synthesis of formal artifacts from high-level specifications, such as those given in temporal logic, as opposed to "logic synthesis" (turning a register transfer level (RTL) description into its gate-level implementation), or "high-level synthesis" (e.g., create a RTL description from a C or SystemC description), which are more commonly used in the electronic design automation (EDA) community.

beyond 45 nm [San].

The first and a fundamental step of every verification process is *specification*. Specification at large is the process of determining the requirements of the target design and *formalizing* them mathematically. It is important to note that the effectiveness of many mechanized procedures, such as assertion-based verification [Sto02] and model checking [CGP00], relies heavily on an engineer being able to create correct and complete specifications of a design.

Consider the classic example of an elevator controller design. The first and foremost step is to determine and define the intended behaviors of the elevator. These behaviors are supposed to capture *precisely* how the elevator should operate. For instance, the door should remain closed *until* the elevator reaches the target floor. Temporal logic, such as Linear Temporal Logic (LTL) [Pnu77] which has been assimilated into industry standards (IEEE 1850 Standard for Property Specification Language) [EF06], can be used to *formalize* this requirement, as shown below.

$$\psi = \mathbf{G} \text{ (elevator\_moves} \rightarrow \text{(door\_closed U reaches\_target\_floor))}$$

(1.1)

We review the syntax and semantics of LTL in Section 2.3. In general, this kind of property, which describes temporal behaviors of a system, is commonly known as *temporal property*. These properties, as opposed to *single-state assertions*, which describe constraints at a single state of a circuit or program, are intended to capture the evolution and relationship among behaviors of multiple states in time. Therefore, they are typically more tricky to write and formalize correctly. According to a report from IBM Haifa, roughly 30% of the formulas were created incorrectly during the first formal verification runs of a new hardware design [BBDER97]. In this dissertation, we propose *mining* likely formal specifications from traces of a design as a way to mitigate this problem. The mined specifications allow an engineer to better understand the design, verify its correctness, and manage possible evolutional changes. We explore novel formalisms of specification and present a suite of algorithms for mining meaningful specifications from traces.

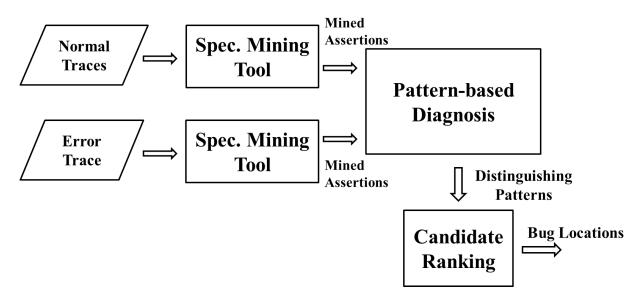

The practical effectiveness of verification, especially formal verification, lies much in its ability to find bugs. Hence, much of the challenge in finding bugs in fact lies in *finding the specification* that mechanized tools can use to find bugs. Mined specifications, which are only behaviors exhibited in traces (of a possibly buggy design), cannot be used directly as targets for further (formal) verification until they are validated by a human engineer. In this dissertation, we present a novel bug localization technique that leverages mined specifications but is not limited by this restriction.

#### Synthesis:

The majority of a design process is in fact expensive iterations of verification and debug. Wouldn't it be nice if we can start with the requirements and then have a way to automatically generate a design that satisfies these requirements? Temporal logic synthesis [PR89], the proposition of automatically synthesizing an implementation from its temporal logic specification, offers an attractive solution to this problem. However, it faces the same problem as in verification – its complete reliance on having good-quality specifications.

In this dissertation, we demonstrate that specification mining can also be valuable in addressing the specification challenge in temporal logic synthesis. Specifically, we focus on the problem of missing environment assumptions, which is a common cause of a specification being unrealizable (see Section 2.3.2 for a precise definition of unrealizability) due to the difficulty of capturing the environmental model (e.g., as a result of implicit knowledge, third-party IP and simply poor documentation), and propose a novel algorithm based on analyzing how the environment should not behave in order for the system to satisfy its specification. Our work is motivated, in part, by the recent advance in temporal logic synthesis, which does not only result in more efficient algorithms [PPS06b], but also demonstrates its applicability to a spectrum of domains, ranging from digital circuits [BGJ<sup>+</sup>07a, BGJ<sup>+</sup>07b], to aircraft electric power system [XTM12], to mission planning for autonomous robots [KGFP07, Won10], to industrial automation [CGR<sup>+</sup>12].

#### **1.1** Thesis Statement

In this dissertation, we explore the following thesis:

Temporal specifications can be mined systematically from example behaviors of a design and its environment, and can be used to automate tedious tasks in verification and synthesis such as bug localization and finding missing assumptions.

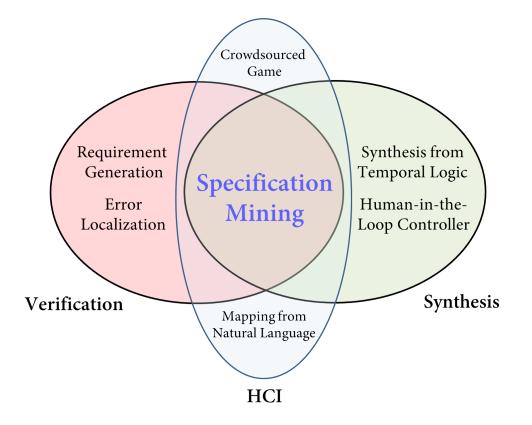

This thesis takes the position that the manual and error-prone process of writing formal specifications can be mitigated by specification mining – an automatic procedure that infers likely specifications by analyzing a design's behaviors. We show that specification mining is not only useful for requirement generation (i.e. finding candidate formal specifications that a designer may miss), but also applicable to a variety of other applications. Figure 1.1 illustrates the composition of this thesis.

The central theme of the thesis is specification mining. We present a collection of novel formalisms and techniques that are tailored for a variety of different applications. This thesis is the first to propose the use of mined specifications for bug localization in reactive systems, such as digital circuits. We study two topics at large – verification and synthesis. In verification, we show that relevant and meaningful specifications can be mined dynamically by observing traces of a digital design, and are useful also for bug localization. In synthesis, we study the topic of synthesis from temporal logic specifications and focus on the problem of finding missing environment assumptions. We show that, by analyzing the counterstrategy of an unrealizable specification towards realizability. In addition, this *counterstrategy-guided synthesis* approach enables the automatic construction of a new class of semi-autonomous controller, called human-in-the-loop (HuIL) controllers. Lastly, this thesis makes an effort to broaden the scope of specification mining, by proposing creative uses of human computer interaction (HCI). Specifically, we present a crowdsourced specification

Figure 1.1: Thesis overview

mining game called CrowdMine that can be played even by young children but effectively infers likely properties behind the scene. Our second effort in this direction is motivated by the fact that much documentation is still written in natural language (NL) today. We examine the feasibility of automatically deriving formal specifications from NL sentences, and demonstrate that this process can be tightly integrated with our assumption mining framework to assist non-expert users of formal methods to debug design requirements.

#### 1.2 Thesis Contributions

The contributions of this thesis are four-fold.

#### 1.2.1 New Formalisms

There has been extensive work on specification formalisms. These formalisms can be generally put into two categories: (1) automata-based [Muk96, Rus12] or (2) logic based (e.g., CTL [CES86], LTL [Pnu77], PSL [EF06]), and often with a tight connection between members of the two categories (e.g., two formalisms describe the same formal language).

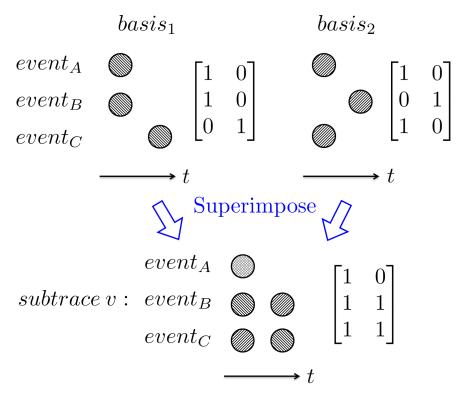

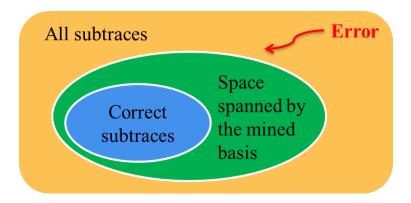

In this thesis, we explore a different direction, inspired by the notion of a sparse code [OF97]. In comparison, in the automata-theoretic view of specification, an automaton (or an equivalent logic formula) characterizes a set of traces with the condition that it accepts each trace in this set (or each trace satisfies the logic formula). In our sparse-coding formalism, we offer a "linear algebra" view of specification. Instead of using an automaton, we propose to use a basis to characterize a set of traces. Similar to the notion of a vector space, we consider a finite-length subtrace (see the definition of a subtrace in Section 3.1.2) as a k dimensional Boolean vector, where k is the number of Boolean signals present in the trace. Hence, any finite trace can be viewed as a collection of such subtraces of the same dimension, and we can characterize a design in terms of the set of subtraces it can produce. With this observation, we propose the use of "basis subtraces" as a specification formalism. These basis subtraces, just like basis vectors in linear algebra, span a k-dimensional subspace ( $\subset \mathbb{B}^k$ ) including all possible k-dimensional behaviors that can be exhibited from the design under analysis. Particularly, we use a linear combination analog in the Boolean domain, where multiplication is interpreted as the Boolean conjunction and addition is interpreted as the Boolean disjunction. In Chapter 5, we elaborate on this formalism in detail, and show the specification mining problem is equivalent to computing a basis that spans the observed traces.

#### 1.2.2 New Algorithms

In a dynamic specification mining framework, where specifications are mined from observations of the design under analysis, the problem of specification mining is closely related to the problem of runtime verification. In runtime verification, traces of a design are tested against one or more patterns usually in the form of monitors. In specification mining, traces are examined to deriving a set of patterns that the traces satisfy<sup>2</sup>, which presumably also capture some aspects of the underlying design.

By prescribing to a set of templates, which determine the form these patterns take, one can construct *instantiations* of these templates so that they can be checked against the traces. Many existing algorithms follow this strategy (see [LKLH11] for a compilation of techniques). In Chapter 4, we also use this strategy but adapt it in a way that it is efficient for digital circuits. Specifically, two main challenges for porting this strategy to circuits are addressed by the new algorithm -(1) many concurrent signals in a circuit; (2) traces can easily be millions or even billions cycles long.

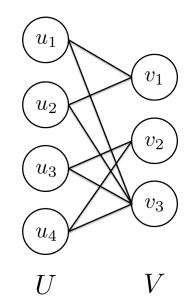

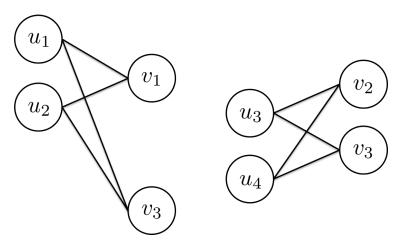

Using predefined templates can be restrictive. In Chapter 5, we leverage the new sparse coding-based specification formalism, which does not use hard-coded templates and only parameterize a specification by the length of a subtrace, and describe a graph-theoretic algorithm for computing a basis from traces. The key novelty of this algorithm is a connection from computing a basis from Boolean traces to finding a biclique edge cover for a bipartite graph. We describe this algorithm in detail in Chapter 5.

<sup>&</sup>lt;sup>2</sup>The term "satisfy" is used a in loose sense here.

In Part II of the thesis, we present the first counterstrategy-guided assumption mining algorithm that systematically guides an unrealizable specification towards realizability. Similar to counterexample-guided abstraction refinement in verification, our algorithm iteratively refines the environment model by adding an assumption that eliminates certain moves by the environment that contribute to the specification being unrealizable. This technique also extends the existing methods for finding specifications, which often focus on desired behaviors exhibited in traces of a design in traces – (1) it derives assumptions from *counteracting* behaviors that prevents the target design from fulfilling certain objectives; (2) it examines a new form of evidence – counterstrategies (represented as a graph) as opposed to traces. In Chapter 9 of the thesis, we further show that, by adapting this algorithm suitably, we can synthesize a new class of semi-autonomous controllers that incorporates constraints representing the interaction with a human operator.

#### **1.2.3** New Applications

Specification mining has been used to address a number of challenges in verification, such as assisting in program understanding [CJK07], bug finding [ECH+01, WN05], bug classification [LCH+09] and meeting coverage goals [LSTV12]. In this thesis, we expand this envelope further and demonstrate novel applications of specification mining both in verification and synthesis. We list these applications below.

#### Bug Localization in Reactive Systems, such as Digital Circuits:

A mined specification, if validated that it matches design intent, can be used as a target for verification. However, not all mined specifications are real specifications, since their validity is only supported by the given evidence (e.g., traces). Thus, we cannot use them directly in verification or to do find bugs until they are validated by a third party (e.g, a human designer).

In this thesis, we make the observation that, by finding likely temporal properties that certain signals hold in different locations and at different time points of traces of a circuit, we can effectively *localize* bugs *both in space and in time* given correct and erroneous traces of the circuit<sup>3</sup>. An additional advantage of this approach is that we need not even care about the problem that the correct traces may also be produced by the same buggy design. In Chapter 4, we demonstrate that this approach enables effective bug localization for a variety of bugs in hardware, including transient bugs.

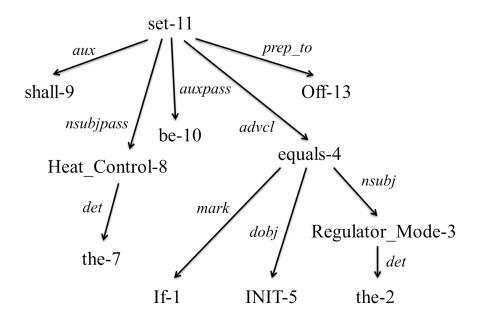

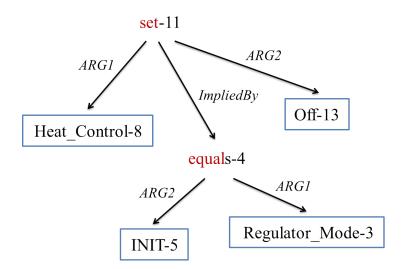

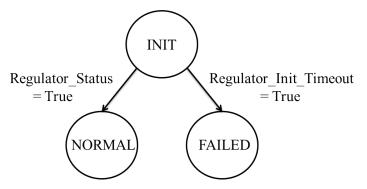

#### **Temporal Logic Synthesis:**