# **UC Irvine**

# **UC Irvine Electronic Theses and Dissertations**

### **Title**

The Art of Voltage Boosting Part I: Boosting Switched Capacitor Converter Part II: Hybrid Boosting Converters

### **Permalink**

https://escholarship.org/uc/item/41f2488f

# **Author**

Wu, Bin

### **Publication Date**

2016

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, IRVINE

# The Art of Voltage Boosting

**Part I: Boosting Switched Capacitor Converter**

**Part II: Hybrid Boosting Converters**

### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in Electrical Engineering

by

Bin Wu

Dissertation Committee: Professor Keyue Smedley, Chair Professor Nader Bagherzadeh Professor Michael Green

# **TABLE OF CONTENTS**

|           |                                                        | Page  |

|-----------|--------------------------------------------------------|-------|

| LIST OF   | CABLES                                                 | xiv   |

| ACKNOW    | LEDGMENTS                                              | xvi   |

| CURRICU   | LUM VITAE                                              | xviii |

| ABSTRAC   | T OF THE DISSETTATION                                  | xxi   |

| Chapter 1 | Introduction                                           | 1     |

| 1.1       | Objective                                              | 1     |

| 1.2       | Background                                             | 2     |

| 1.2       | 1 Switched capacitor voltage boosting technology       | 5     |

| 1.2       | 2 Inductor based voltage boosting technology           | 9     |

| 1.3       | Outline of the thesis                                  | 17    |

| Part I T  | wo-switch Boosting Switched Capacitor Converter        | 19    |

| Chapter 2 | Introduction of Switched Capacitor Converter           | 20    |

| 2.1       | Development of switched capacitor converter            | 21    |

| 2.1       | 1 Topology                                             | 21    |

| 2.1       | 2 Modeling                                             | 23    |

| 2.1       | 3 Control Technique                                    | 29    |

| 2.2       | Development in Part I of this dissertation             | 32    |

| Chapter 3 | Topology Development of TBSC and Operational Principle | 34    |

| 3.1       | TBSC family Derivation                                 | 34    |

| 3.2       | Operational principle of TBSC                          | 37    |

| 3.2       | 1 2X TBSC                                              | 37    |

| 3       | .2.2 | 3X TBSC                                                     | 39 |

|---------|------|-------------------------------------------------------------|----|

| 3       | .2.3 | High-order TBSC                                             | 43 |

| 3.3     | Ex   | tensions for bi-direction and step-down conversion          | 45 |

| 3       | .3.1 | Bidirectional TBSC                                          | 45 |

| 3       | .3.2 | Buck-mode (Step down) TBSC                                  | 46 |

| 3.4     | Su   | ımmary                                                      | 47 |

| Chapter | 4    | Modeling of TBSC                                            | 48 |

| 4.1     | M    | odeling of 2X TBSC                                          | 48 |

| 4.2     | M    | odeling of 3X TBSC                                          | 51 |

| 4       | .2.1 | Complex coupling Loop                                       | 53 |

| 4       | .2.2 | Accurate Steady State Model Derivation of 3X TBSC           | 54 |

| 4       | .2.3 | Peak Current Analysis of 3X TBSC                            | 58 |

| 4       | .2.4 | Small Signal Model of 3X TBSC                               | 60 |

| 4.3     | Su   | ımmary                                                      | 63 |

| Chapter | 5    | Performance Analysis of TBSC                                | 64 |

| 5.1     | Co   | omparison with Previous Step-up SC Converters               | 64 |

| 5       | .1.1 | Component Count                                             | 64 |

| 5       | .1.2 | Component Stress                                            | 65 |

| 5.2     | Οι   | utput voltage ripple analysis of TBSC                       | 66 |

| 5.3     | Su   | ımmary                                                      | 68 |

| Chapter | 6    | Simulation and Experimental Results of 3X TBSC              | 69 |

| 6.1     | Si   | mulation verification of CT model and peak current analysis | 69 |

| 6.2     | Ex   | perimental verification                                     | 70 |

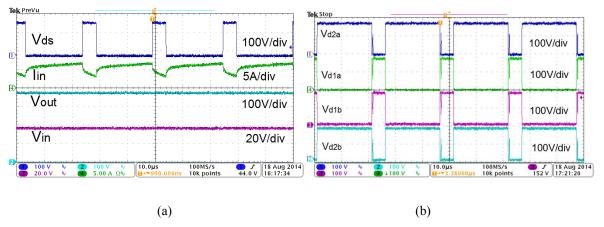

| 6.2.1       | Duty cycle and frequency modulation verification                | 71        |

|-------------|-----------------------------------------------------------------|-----------|

| 6.2.2       | Efficiency testing and high efficiency design consideration     | 75        |

| 6.2.3       | Soft rising input current                                       | 77        |

| 6.2.4       | Ripple cancelation                                              | 78        |

| 6.2.5       | Close loop operation under load step condition                  | 79        |

| 6.2.6       | Summary                                                         | 80        |

| Chapter 7   | Accurate Modeling Technique of Switched Capacitor Convert       | er 81     |

| 7.1 Ch      | arge-Balance Transient-Calculation (CT) Modeling Method         | 81        |

| 7.1.1       | State Space Average (SSA) Modeling                              | 82        |

| 7.1.2       | Charge-balance Transient-Calculation Modeling                   | 83        |

| 7.1.3       | Comparison of SSA Model and CT Model                            | 86        |

| 7.1.4       | Model evaluation based equivalent output impedance              | 88        |

| 7.2 En      | hanced CT Modeling Method                                       | 91        |

| 7.2.1       | Modeling of Interleaved simple dual-phase SC converter          | 92        |

| 7.2.2       | Modeling of Non-interleaved simple dual-phase SC converter      | 98        |

| 7.2.3       | Comparative analysis of interleaved and non-interleaved SC conv | erter 102 |

| 7.2.4       | Model comparison for Unity Gain SC Converter                    | 104       |

| 7.2.5       | Accuracy constraint analysis of enhanced CT modeling method     | 107       |

| 7.2.6       | Simulation and experimental verification                        | 109       |

| 7.3 Su      | mmary                                                           | 112       |

| Part II Hyb | rid Boosting Converters (HBC)                                   | 114       |

| Chapter 8   | Introduction of hybrid converters                               | 115       |

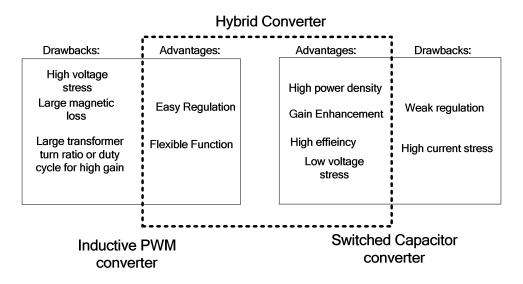

| 8.1 De      | efinition of hybrid converters                                  | 115       |

| 8.2      | N      | Merits of hybrid converters                                      | 117 |

|----------|--------|------------------------------------------------------------------|-----|

| 8.3      | Г      | Development in Part II of this dissertation                      | 118 |

| Chapter  | . 9    | Topology Development of HBC and Operational Principle            | 119 |

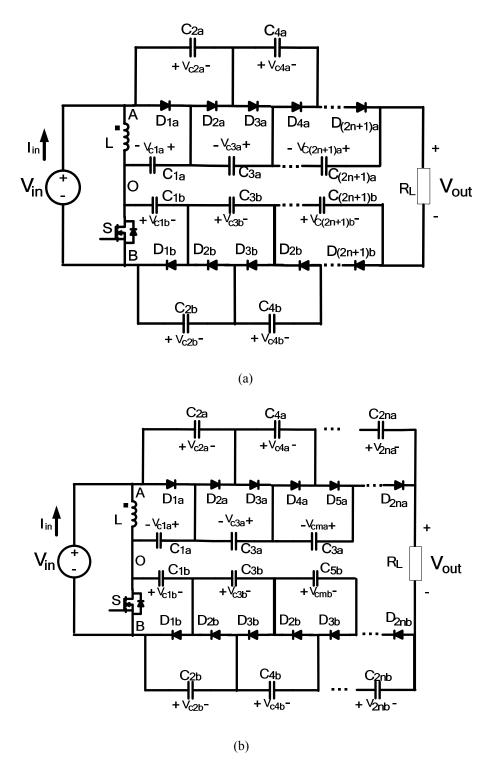

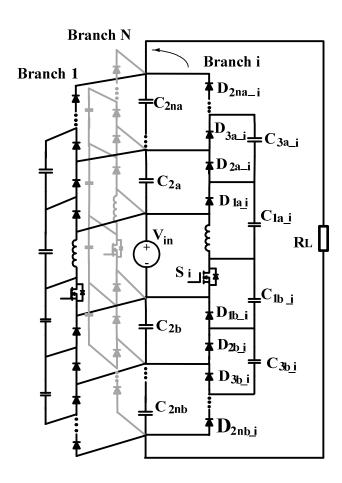

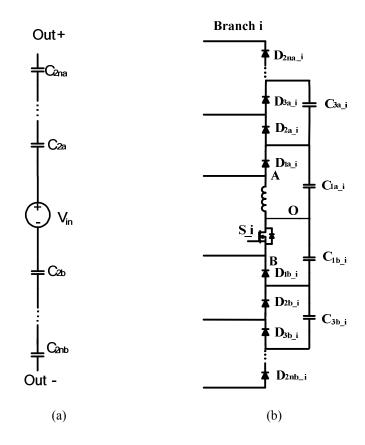

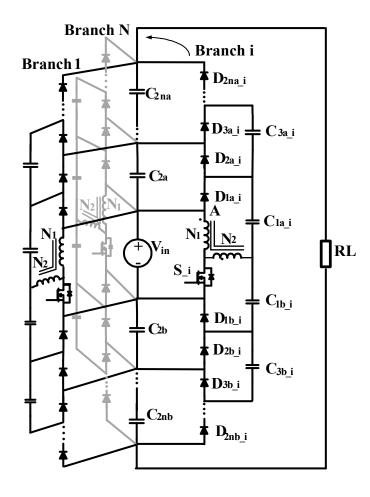

| 9.1      | Г      | Derivation of HBC family                                         | 119 |

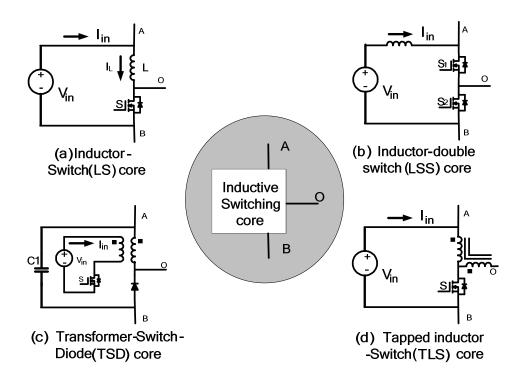

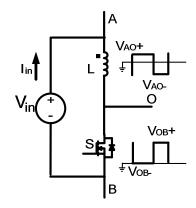

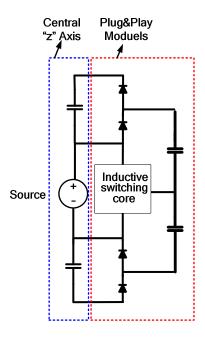

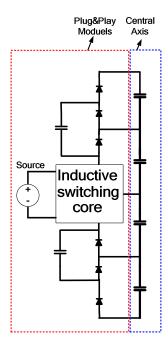

| Ģ        | 9.1.1  | Inductive Switching Core (ISC) Development                       | 120 |

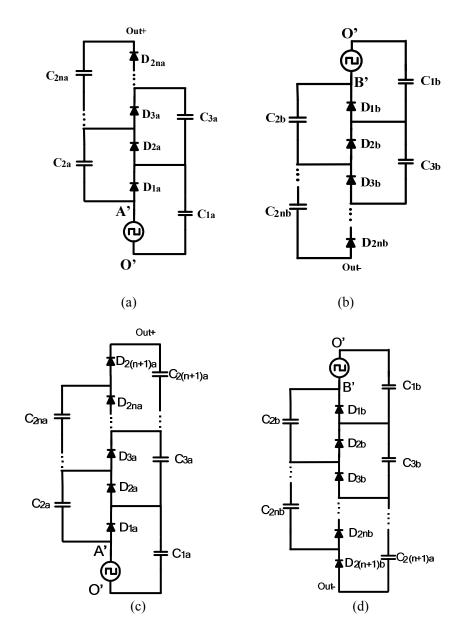

| Ģ        | 9.1.2  | Bipolar Voltage Multiplier Analysis                              | 122 |

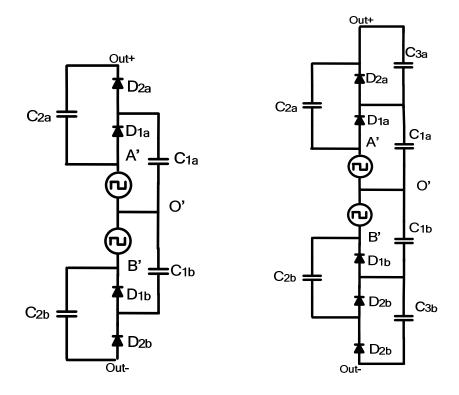

| 9.2      | В      | Basic HBC                                                        | 124 |

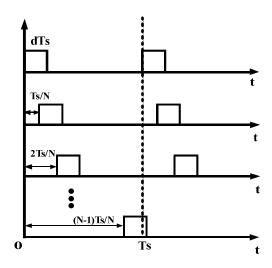

| 9.3      | S      | ymmetrical HBC                                                   | 128 |

| 9.4      | Is     | solated HBC                                                      | 133 |

| 9.5      | Т      | Capped HBC                                                       | 136 |

| 9.6      | S      | ummary                                                           | 141 |

| Chapter  | 10     | Analysis and Design of Basic HBC for Renewable Energy            |     |

| Applicat | tions  | 142                                                              |     |

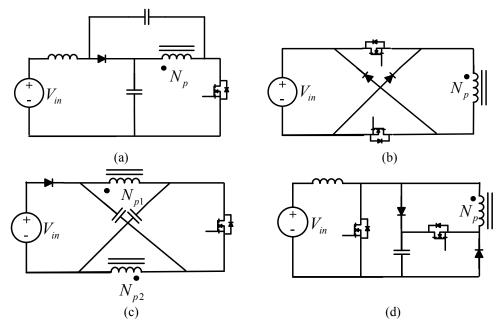

| 10.      | 1 A    | review of topology category of "Switch+Inductor+Diode-capacitor" | 142 |

| 10.      | 2 6    | General HBC topology and its operational principle               | 145 |

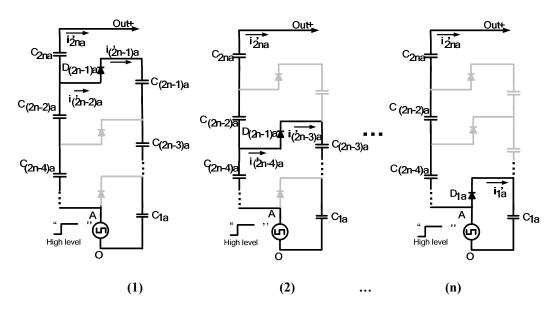

| 1        | 10.2.1 | Analysis of general BVM                                          | 147 |

| 1        | 10.2.2 | 2 Steady state analysis of general basic HBC                     | 154 |

| 10.      | 3 C    | Converter Performance Analysis                                   | 161 |

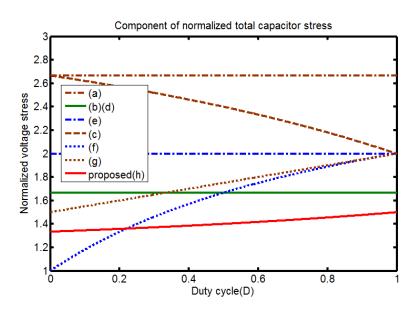

| 1        | 10.3.1 | Component stress analysis                                        | 161 |

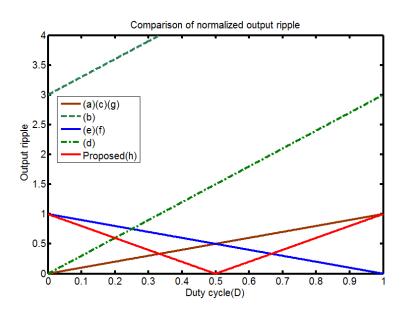

| 1        | 10.3.2 | 2 Voltage ripple analysis                                        | 164 |

| 1        | 10.3.3 | Comparison of Basic HBC with previous converters                 | 166 |

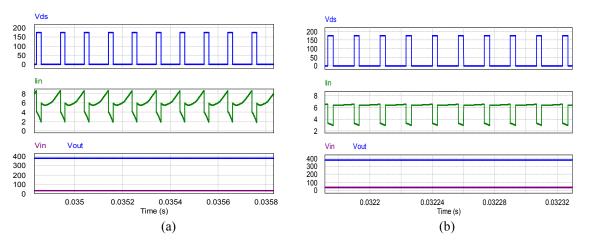

| 10.      | 4 S    | imulation and Experimental Verification                          | 170 |

| 10.      | 5 S    | ummary                                                           | 175 |

| Chapter 11 | A new Design of lossless Snubber for high efficiency Isolated HBC1      | 76  |

|------------|-------------------------------------------------------------------------|-----|

| 11.1       | A review of topology category of "Switch+Transformer+Didoe-capacitor" 1 | 76  |

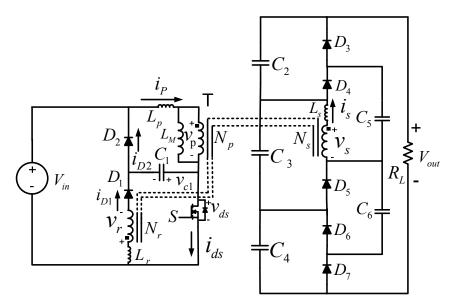

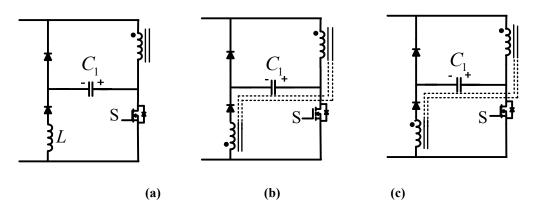

| 11.2       | Operational Principal of Isolated HBC with Lossless Snubber             | 79  |

| 11.2       | 2.1 CCM operation of Isolated HBC                                       | 80  |

| 11.2       | 2.2 DCM operation of Isolated HBC                                       | 89  |

| 11.3       | Circuit Design Analysis                                                 | 89  |

| 11.4       | Experimental Verification 1                                             | 97  |

| 11.5       | Summary                                                                 | :00 |

| Chapter 12 | Extension Circuits based on HBC                                         | 01  |

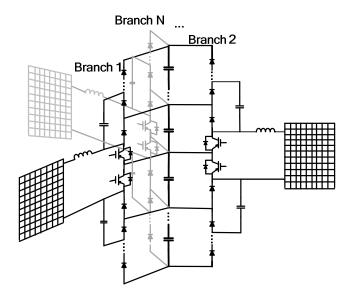

| 12.1       | Paralleling technology of HBC                                           | :01 |

| 12.        | 1.1 Single-source paralleling technology (3D DC-DC converter)           | :01 |

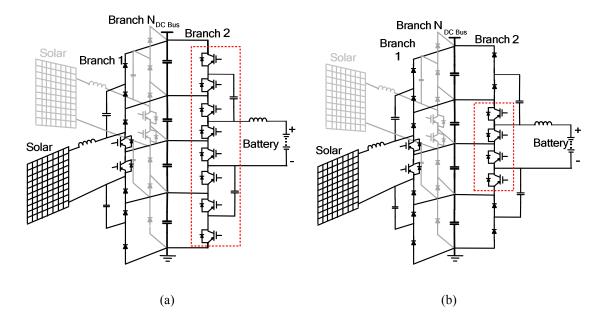

| 12.        | 1.2 Multi-source paralleling technology                                 | 10  |

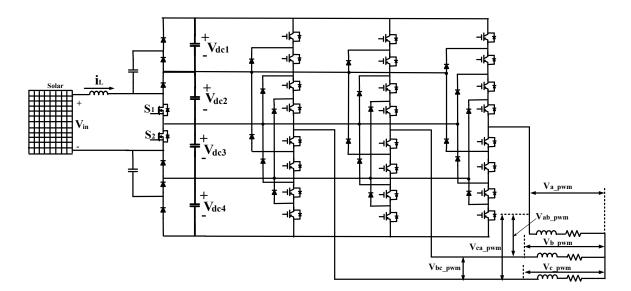

| 12.2       | Inverter based on HBC                                                   | :12 |

| 12.2       | 2.1 Micro-inverter                                                      | :12 |

| 12.2       | 2.2 Multilevel Inverter                                                 | 16  |

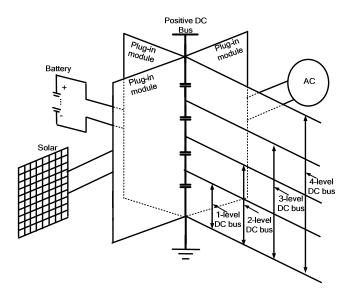

| 12.3       | Multi-bus DC micro-grid based on HBC                                    | 17  |

| 12.4       | Summary                                                                 | 19  |

| Chapter 13 | Conclusions and future work2                                            | 21  |

| References | 226                                                                     |     |

# LIST OF FIGURES

|                                                                      | Page |

|----------------------------------------------------------------------|------|

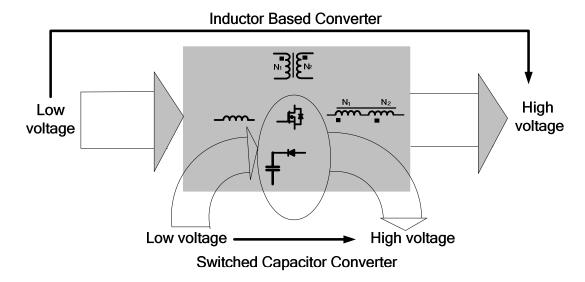

| Figure 1.1 Voltage Boosting Technology                               | 3    |

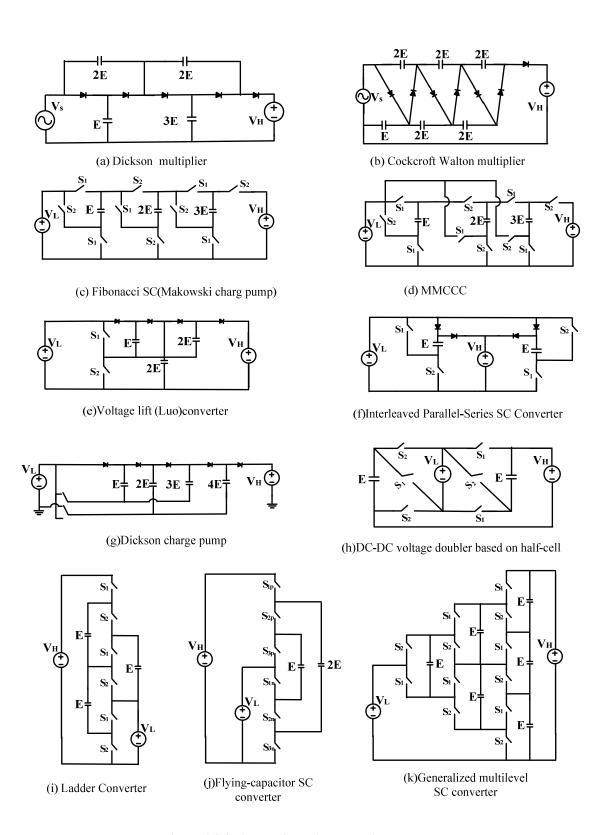

| Figure 1.2 Switched Capacitor Boosting Technology                    | 4    |

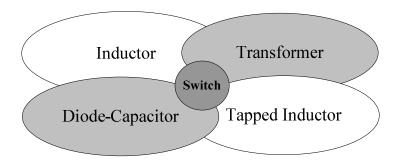

| Figure 1.3 Inductor based voltage gain boosting elements             | 10   |

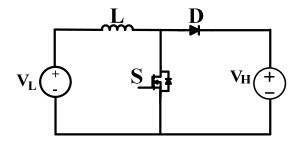

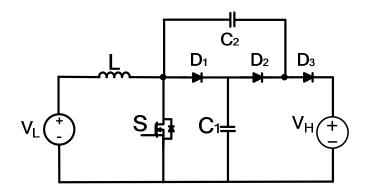

| Figure 1.4 Switch+Inductor topology                                  | 10   |

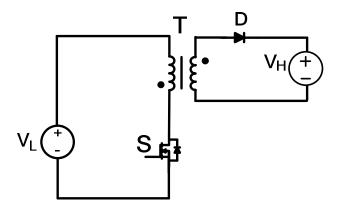

| Figure 1.5 Switch+ Transformer topology                              | 11   |

| Figure 1.6 Switch+Tapped-inductor topology                           | 12   |

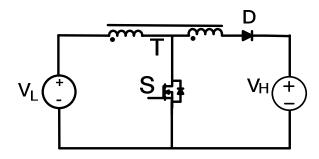

| Figure 1.7 Switch+inductor+diode-capacitor topology                  | 13   |

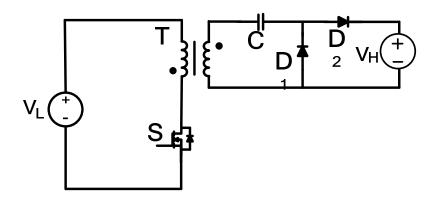

| Figure 1.8 Switch+Transformer+Diode-capacitor topology               | 13   |

| Figure 1.9 Switch+Tapped-inductor+Diode-capacitor topology           | 14   |

| Figure 1.10 Switch+Inductor+Transformer+Diode-capacitor topology     | 15   |

| Figure 1.11 Switch+Inductor+Tapped-inductor+Diode-capacitor topology | 15   |

| Figure 2.1 Equivalent circuit of SCC for steady state model.         | 24   |

| Figure 2.2 Simple SC blocks for steady state model analysis.         | 25   |

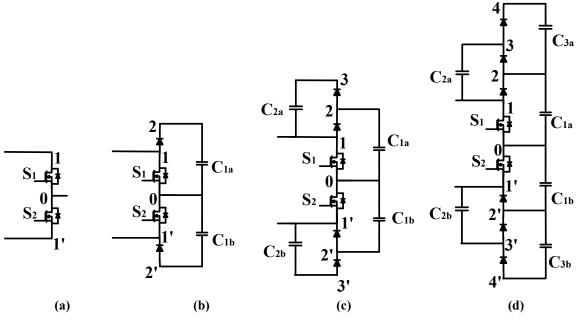

| Figure 3.1 The proposed TBSC family                                  | 35   |

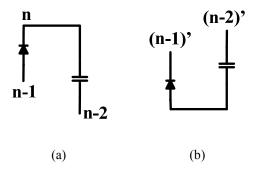

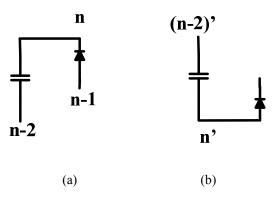

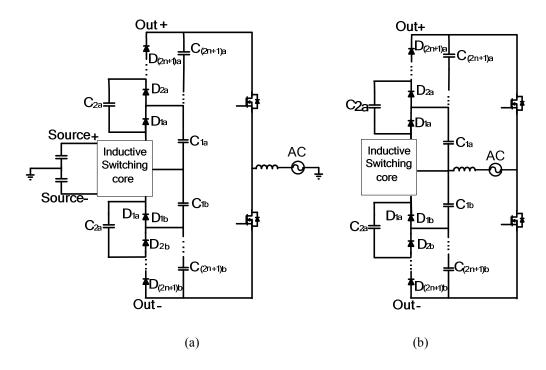

| Figure 3.2 Gain-extension network (n=2, 4, 6) (a) Top (b) Bottom     | 35   |

| Figure 3.3 Gain extension network (n=3, 5, 7) (a) Top (b) Bottom     | 36   |

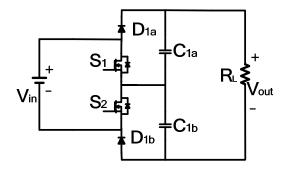

| Figure 3.4 Topology of 2X TBSC.                                      | 37   |

| Figure 3.5 Driving signals and key waveforms of 2X TBSC              | 38   |

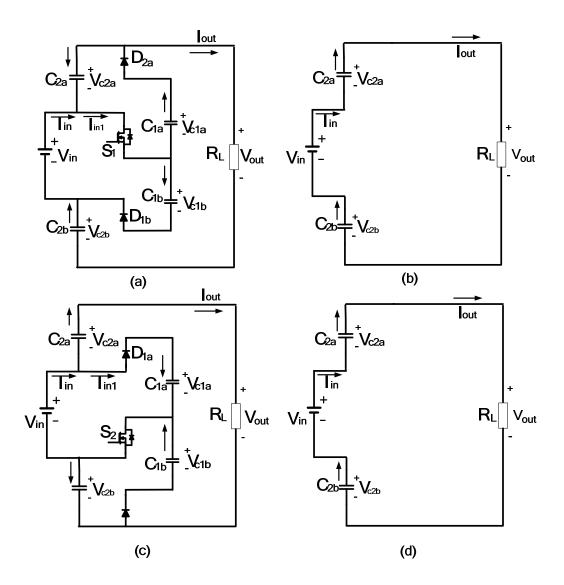

| Figure 3.6 Operation states of 2X TBSC                               | 38   |

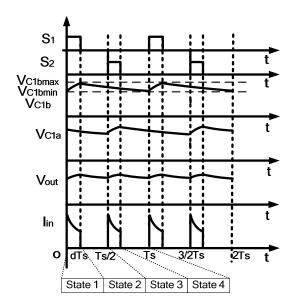

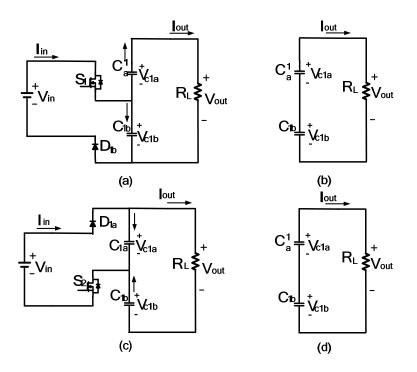

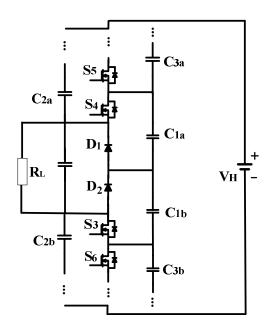

| Figure 3.7. Topology of 3X TBSC                                      | 40   |

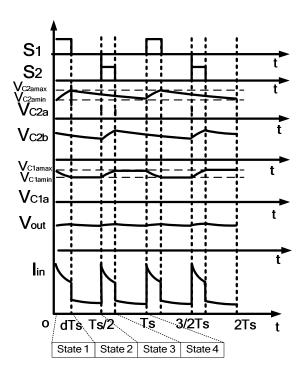

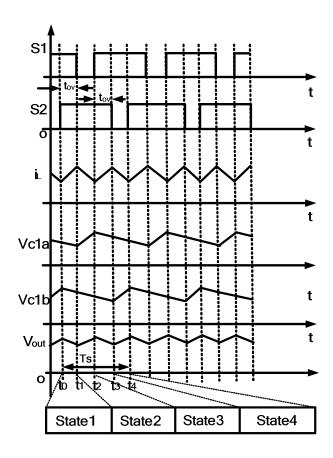

| Figure 3.8 Driving signals and key waveforms of 3X TBSC                                           | .41 |

|---------------------------------------------------------------------------------------------------|-----|

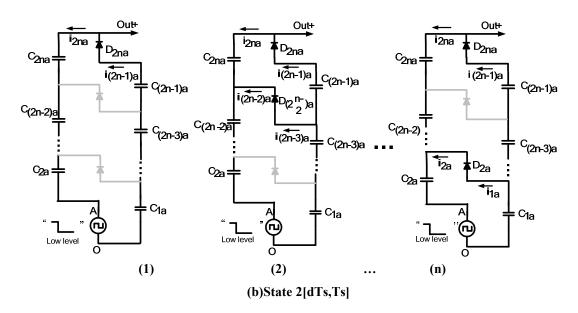

| Figure 3.9 Operation states of 3X TBSC                                                            | .42 |

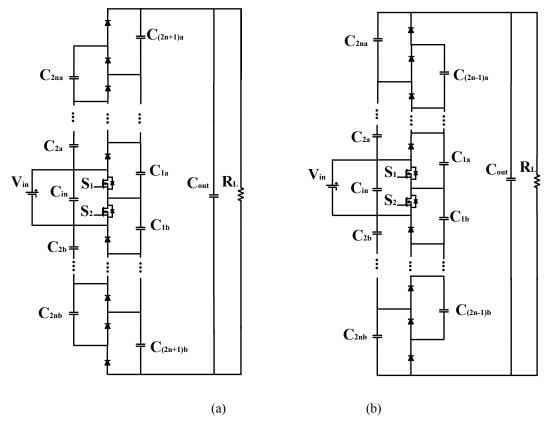

| Figure 3.10. Topology of high-order TBSC (a) Even-order (b) Odd-order                             | .44 |

| Figure 3.11 Extensions of TBSC for Bi-directional application                                     | .45 |

| Figure 3.12 Extensions of TBSC for Step-down application.                                         | .46 |

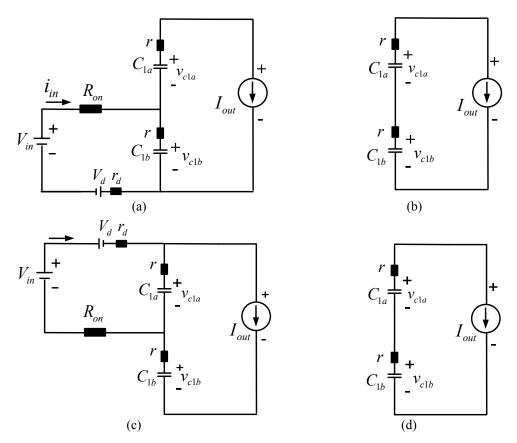

| Figure 4.1 Equivalent circuits of different states for 2X SC converter                            | .49 |

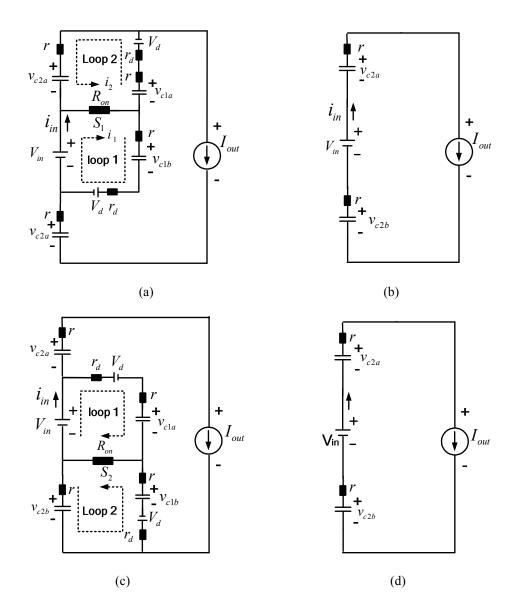

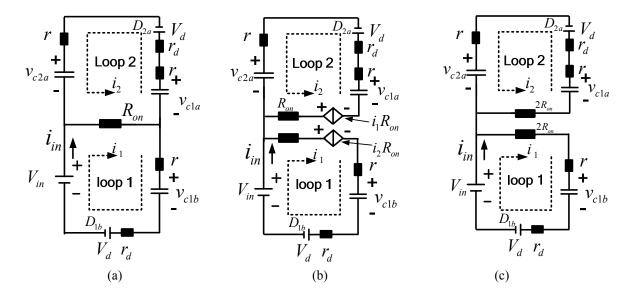

| Figure 4.2 Equivalent circuits in different modes for 3X TBSC converter                           | .52 |

| Figure 4.3 Loop decoupling procedure                                                              | .53 |

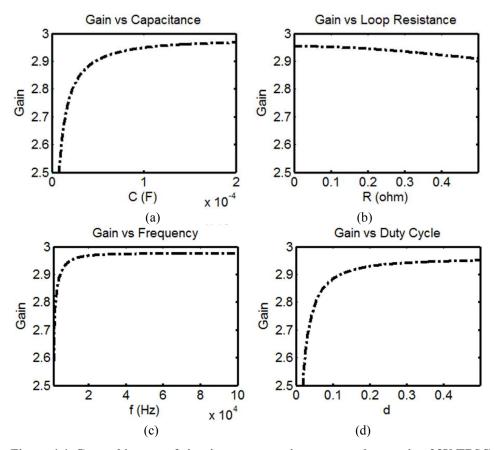

| Figure 4.4 General impact of circuit parameters impact on voltage gain of 3X TBSC                 | .56 |

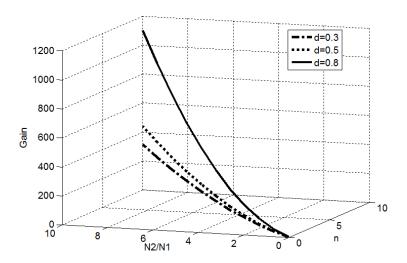

| Figure 4.5 3X TBSC voltage gain as function of frequency and duty cycle                           | .57 |

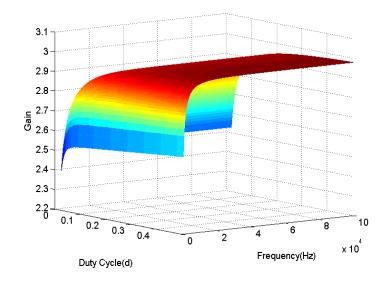

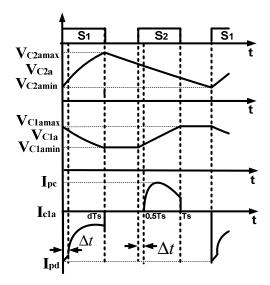

| Figure 4.6 Transient voltages of capacitor $C_{1a}$ , $C_{2a}$ and transient current of $C_{1a}$  | .59 |

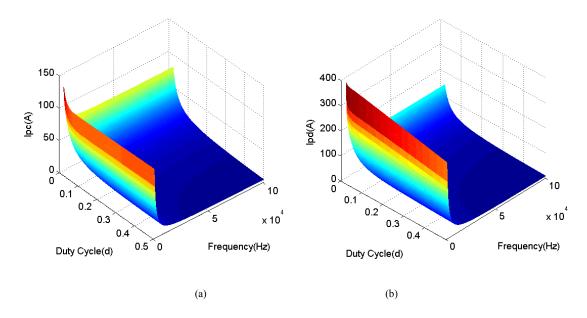

| Figure 4.7 Peak current as function of frequency and duty cycle                                   | .60 |

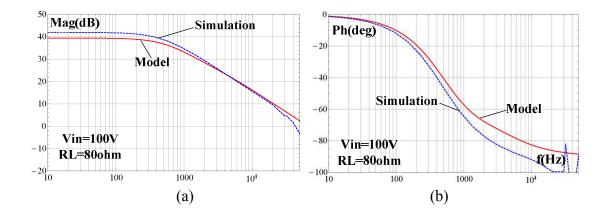

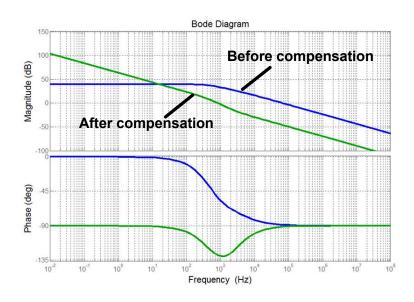

| Figure 4.8. Comparison between model (solid, red) and PSIM simulation (dashed, blue)              | .61 |

| Figure 4.9 T. Loop gain Bode plot comparison before and after compensation                        | .62 |

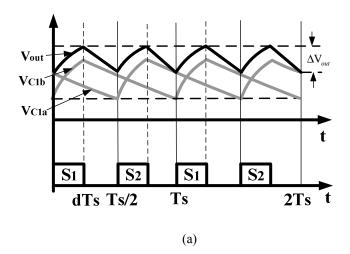

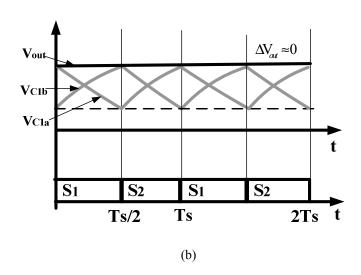

| Figure 5.1 Relationship of $\Delta V_{cla}$ , $\Delta V_{clb}$ $\Delta V_{out}$                   | .67 |

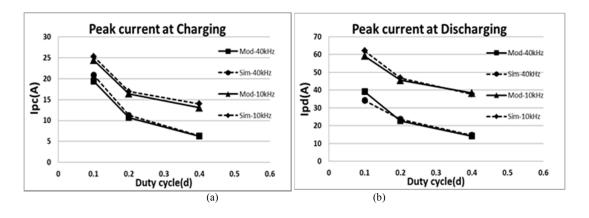

| Figure 6.1 Comparison of peak current model with simulation                                       | .69 |

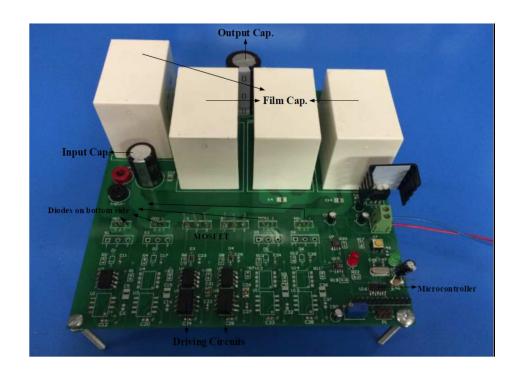

| Figure 6.2 Experimental prototype of 1kW 3X TBS                                                   | .71 |

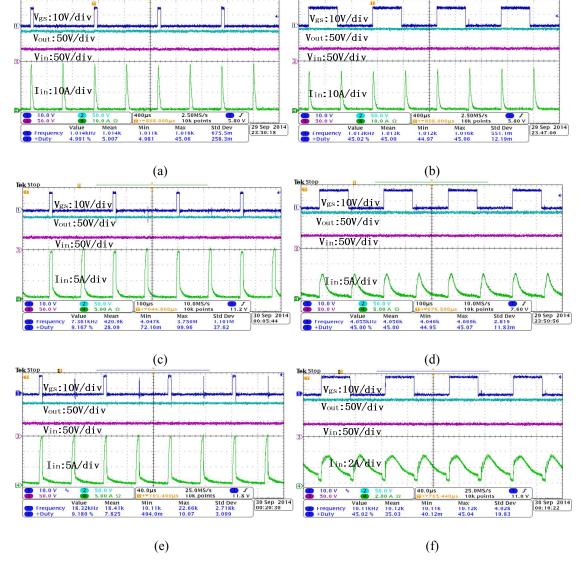

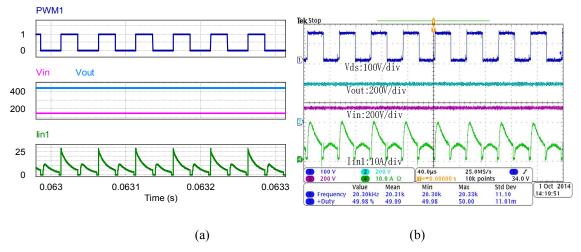

| Figure 6.3 Waveforms of V <sub>gs1</sub> , V <sub>in</sub> , V <sub>out</sub> and I <sub>in</sub> | .73 |

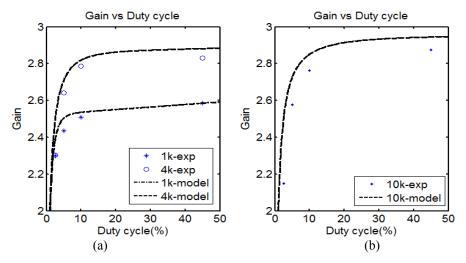

| Figure 6.4 Comparison of duty cycle modulation between experiment and model                       | .74 |

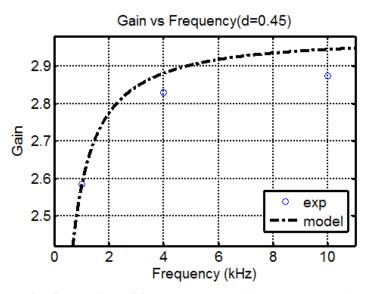

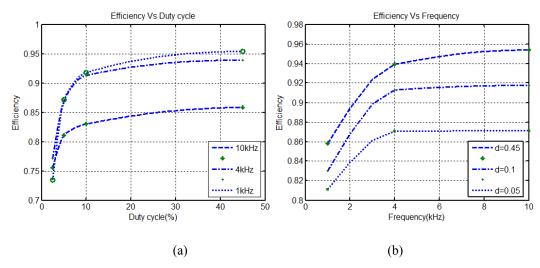

| Figure 6.5 Comparison of frequency modulation between experiment and model                        | .74 |

| Figure 6.6 Relationship between duty cycle and frequency under fixed load                         | .75 |

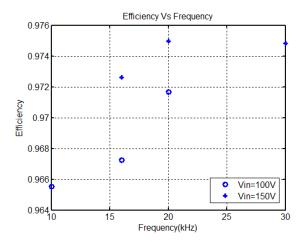

| Figure 6.7Effeiciency V.S. Frequency under input voltage of 100V and 150V                         | .76 |

| Figure 6.8 Waveforms of $V_{gs1}$ , $V_{in}$ , $V_{out}$ and $I_{in1}$ under fs=20kHz, d=0.45viii | .78 |

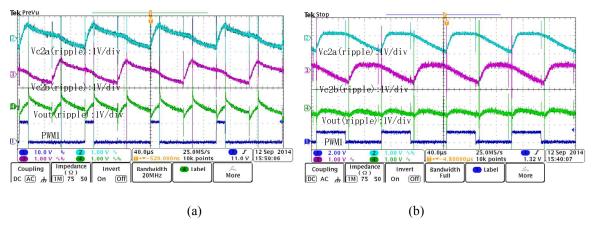

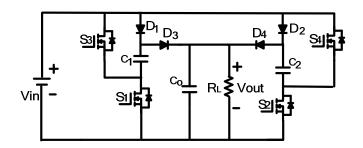

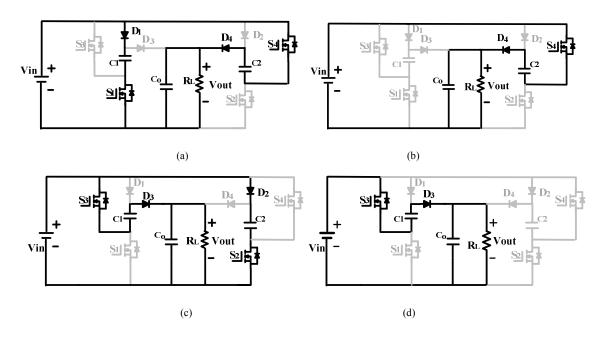

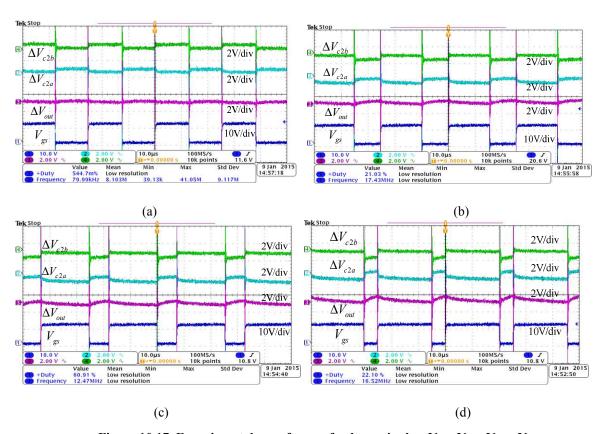

| Figure 6.9 Experimental result of ripple cancelation (a)d=0.25 (b)d=0.45                                                  | 79  |

|---------------------------------------------------------------------------------------------------------------------------|-----|

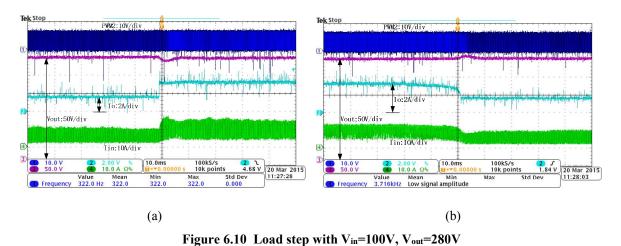

| Figure 6.10 Load step with V <sub>in</sub> =100V, V <sub>out</sub> =280V                                                  | 79  |

| Figure 7.1 A voltage doubler topology proposed in [19]                                                                    | 82  |

| Figure 7.2 Operation modes of voltage doubler topology proposed in [19]                                                   | 84  |

| Figure 7.3 Transient waveforms based on CT modeling method                                                                | 84  |

| Figure 7.4. Duty cycle regulation curves with different control parameters                                                | 87  |

| Figure 7.5 Model of an idealized SCC                                                                                      | 89  |

| Figure 7.6 Comparison of CT model and AC model with simulation results                                                    | 90  |

| Figure 7.7 Simple dual-phase SC converter                                                                                 | 92  |

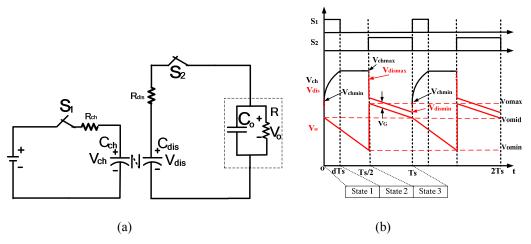

| Figure 7.8 Interleaved type I dual-phase SC converter(a)Topology (b) Waveforms                                            | 93  |

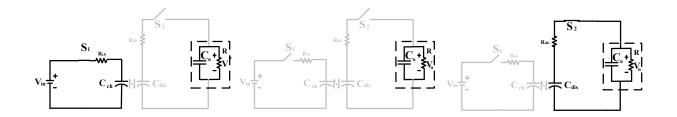

| Figure 7.9 Operational states of Interleaved type I dual-phase SC converter                                               | 94  |

| Figure 7.10 Circuit states of type I dual-phase SC converter at discharging phase                                         | 95  |

| Figure 7.11 Interleaved type I single-phase SC converter (a) Topology (b) Waveform                                        | 98  |

| Figure 7.12 Operational states of None-interleaved type I dual-phase SC converter                                         | 99  |

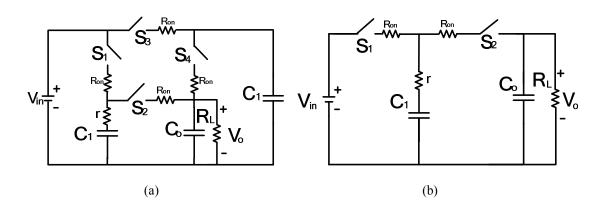

| Figure 7.13 Unity gain SC Converter                                                                                       | 104 |

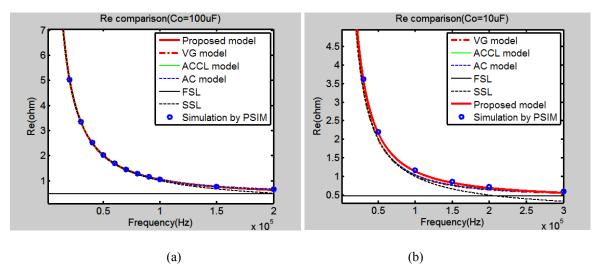

| Figure 7.14 Output impedance comparison for single-branch unity gain SC converter.                                        | 106 |

| Figure 7.15 Discharging phase with consideration of ESR of Co.                                                            | 108 |

| Figure 7.16 Voltage Waveforms of Capacitor C <sub>1</sub> , C <sub>0</sub> and Control signals                            | 110 |

| Figure 7.17 Voltage Waveforms of Capacitor C <sub>1</sub> , C <sub>o</sub> ,V <sub>gs1</sub> , V <sub>gs2</sub> at d=0.1  | 111 |

| Figure 7.18 Voltage Waveforms of Capacitor C <sub>1</sub> , C <sub>o</sub> , V <sub>gs1</sub> , V <sub>gs2</sub> at d=0.4 | 111 |

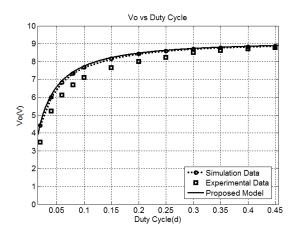

| Figure 7.19 Model, simulation and experiment comparison at V <sub>in</sub> =10V, f <sub>s</sub> =100kHz                   | 112 |

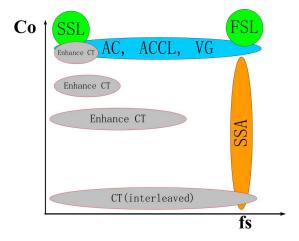

| Figure 7.20 Application guideline for steady state model of SC converter                                                  | 113 |

| Figure 8.1 Concept of Hybrid Converter                                                                                    | 116 |

| Figure 8.2 Merits of Hybrid Converter                                         | 117    |

|-------------------------------------------------------------------------------|--------|

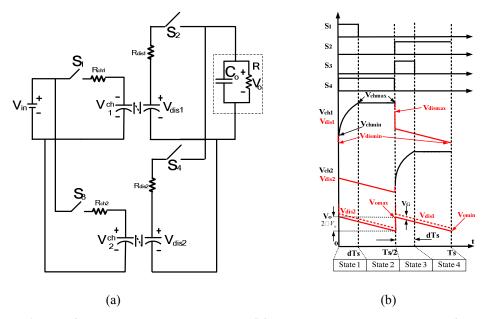

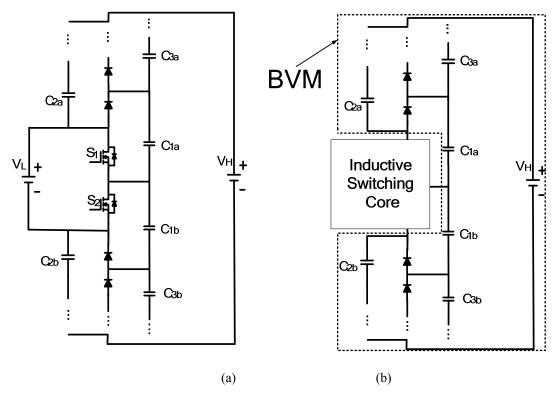

| Figure 9.1 Topology development from TBSC to HBC                              | 120    |

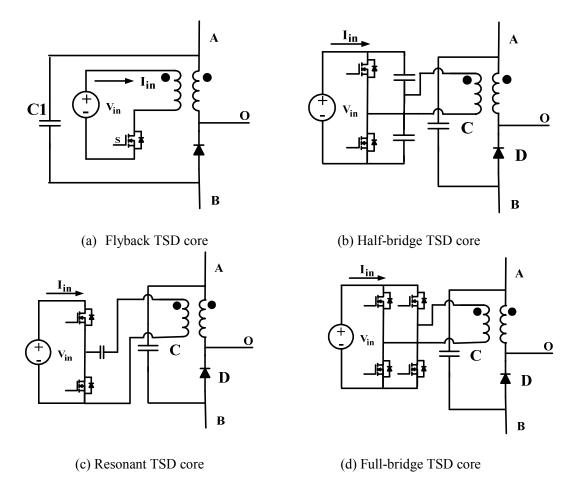

| Figure 9.2 Inductive switching cores: LS, LSS, TSD, and TLS                   | 121    |

| Figure 9.3 The positive branch and negative branch of BVM                     | 123    |

| Figure 9.4 Example BVMs (a) second-order BVM (b) third-order BVM              | 124    |

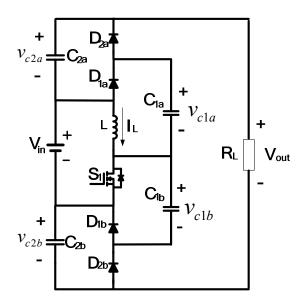

| Figure 9.5 Second-order Basic HBC                                             | 125    |

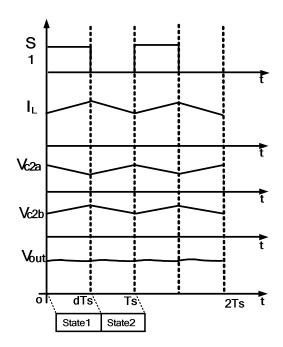

| Figure 9.6 Key circuit waveforms of second-order basic HBC                    | 125    |

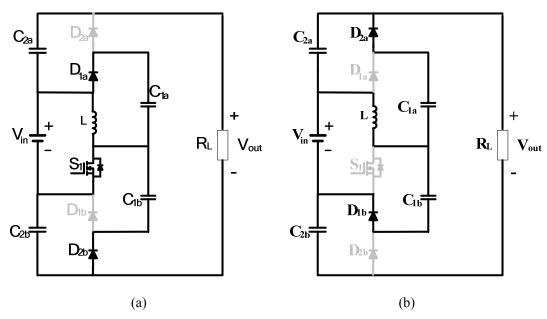

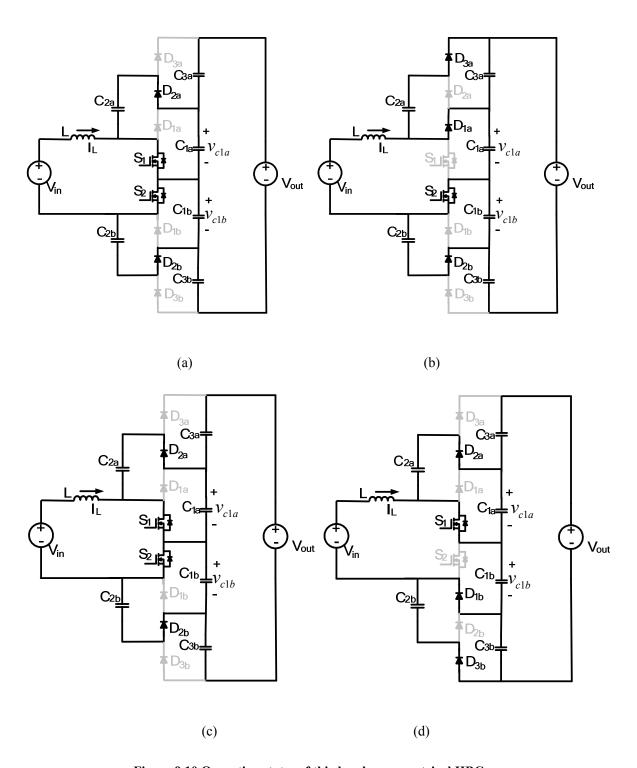

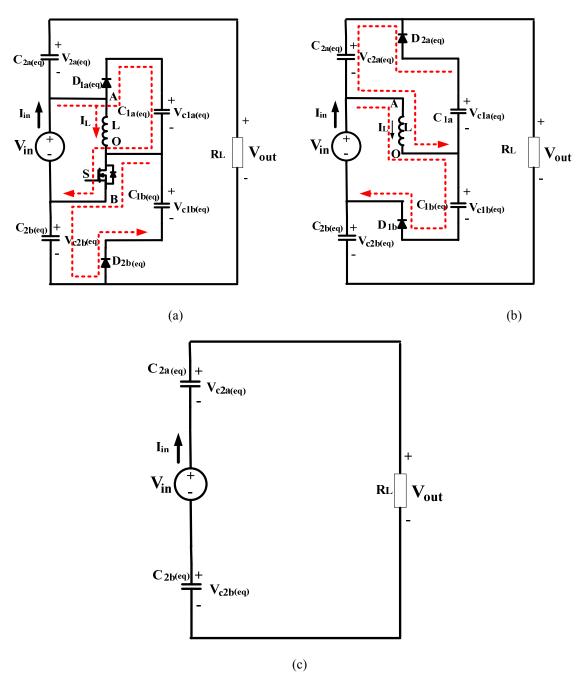

| Figure 9.7 CCM operation modes of second-order Basic HBC                      | 126    |

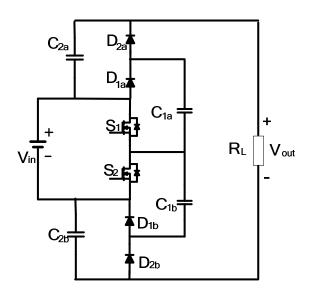

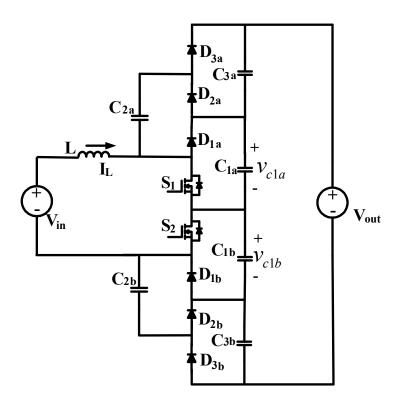

| Figure 9.8 Third-order symmetrical HBC                                        | 128    |

| Figure 9.9 Overlaping interleaved PWM signal                                  | 129    |

| Figure 9.10 Operation states of third-order symmetrical HBC                   | 131    |

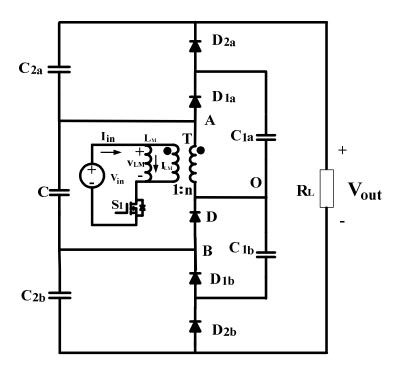

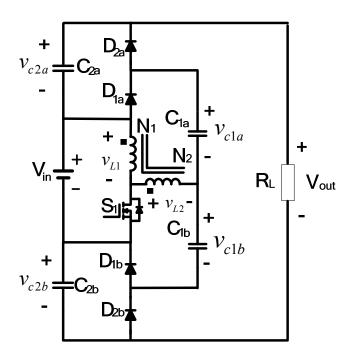

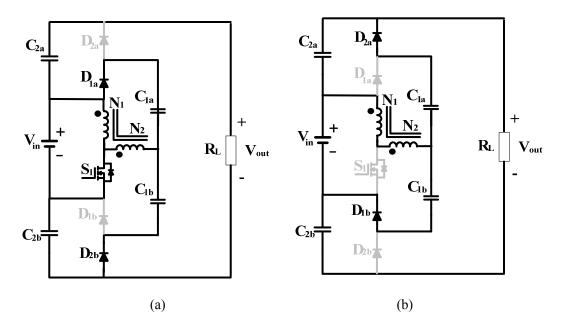

| Figure 9.11 Second-order Isolated HBC                                         | 133    |

| Figure 9.12 CCM operation states of second-order Isolated HBC                 | 134    |

| Figure 9.13 Different configurations of TSD cores for Isolated HBC            | 136    |

| Figure 9.14 Second-order Tapped HBC                                           | 137    |

| Figure 9.15 CCM operational states of second-order Tapped HBC                 | 138    |

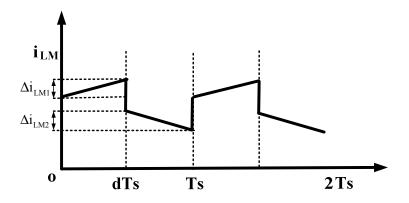

| Figure 9.16 Magnetizing current with different mac                            | 139    |

| Figure 10.1 High-gain DC-DC converters with single-switch and single-inductor | 143    |

| Figure 10.2 Proposed General HBC topology (a) Odd-order HBC (b) Even-order HI | 3C 146 |

| Figure 10.3 LS inductive switching core                                       | 147    |

| Figure 10.4 Operation States of even-order BVM positive branch                | 148    |

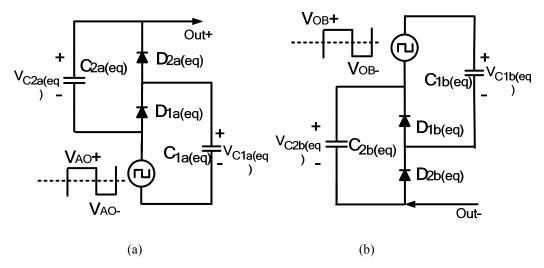

| Figure 10.5 Equivalent circuit of even-order BVM                              | 150    |

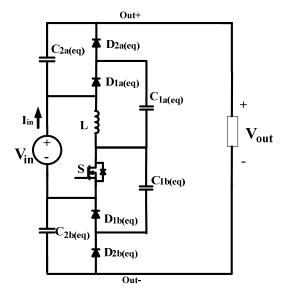

| Figure 10.6 Equivalent circuit of general even-order Basic HBC                | 154    |

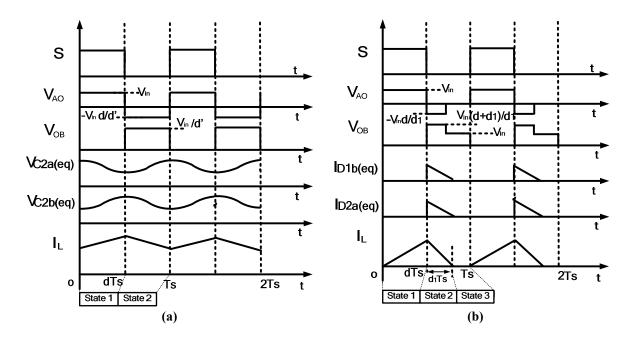

| Figure 10.7 Key waveforms of even-order HBC                                                                                      | 155 |

|----------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 10.8 Three operation states of Basic even-order HBC                                                                       | 156 |

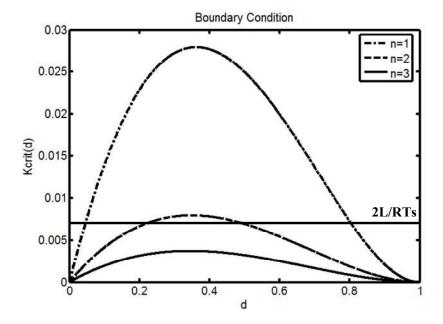

| Figure 10.9 $K_{crit}(d)$ with variation of n                                                                                    | 161 |

| Figure 10.10 Current waveforms of Diodes and Switch                                                                              | 163 |

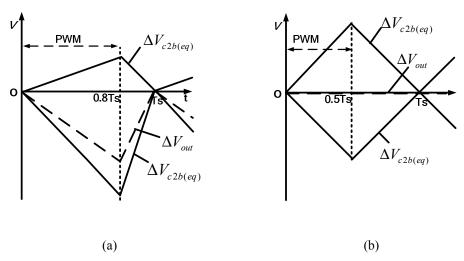

| Figure 10.11 Voltage ripple cancellation with different duty cycle                                                               | 165 |

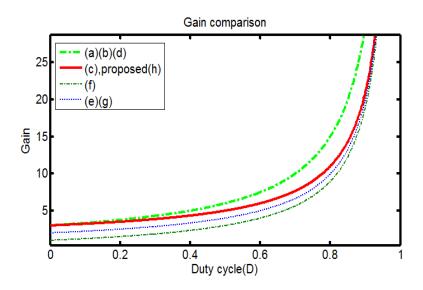

| Figure 10.12 Comparison of voltage gain                                                                                          | 167 |

| Figure 10.13 Comparison of total normalized capacitor voltage stress                                                             | 169 |

| Figure 10.14 Comparison of normalized output ripple                                                                              | 170 |

| Figure 10.15 Simulation waveforms of $V_{ds}$ , $I_{in}$ , $V_{out}$ , $V_{in}$                                                  | 171 |

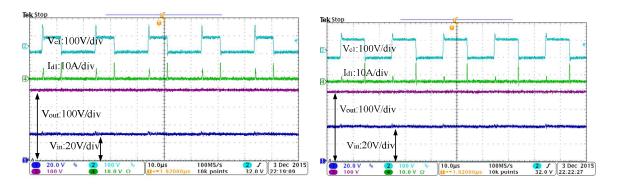

| Figure 10.16 Experimental waveforms                                                                                              | 172 |

| Figure 10.17 Experimental waveforms of voltage ripples: V <sub>c2a</sub> , V <sub>c2b</sub> , V <sub>out</sub> , V <sub>gs</sub> | 173 |

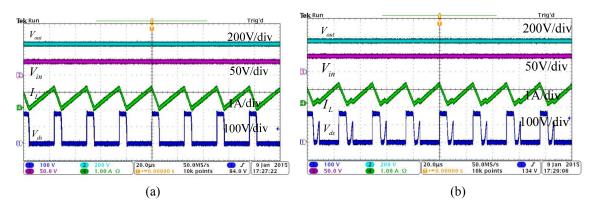

| Figure 10.18 Experimental waveforms of V <sub>out</sub> , V <sub>in</sub> , I <sub>L</sub> and V <sub>ds</sub>                   | 174 |

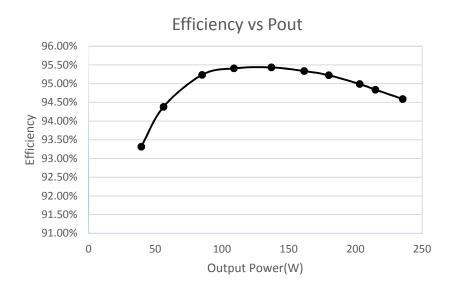

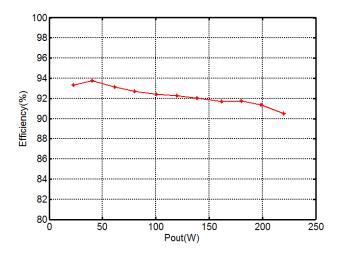

| Figure 10.19 Efficiency curve with load variation (Vin=35V,Vout=380V)                                                            | 174 |

| Figure 11.1 Primary side configurations for high-gain isolated DC-DC converters                                                  | 177 |

| Figure 11.2 Secondary side configurations for high-gain isolated DC-DC converters                                                | 177 |

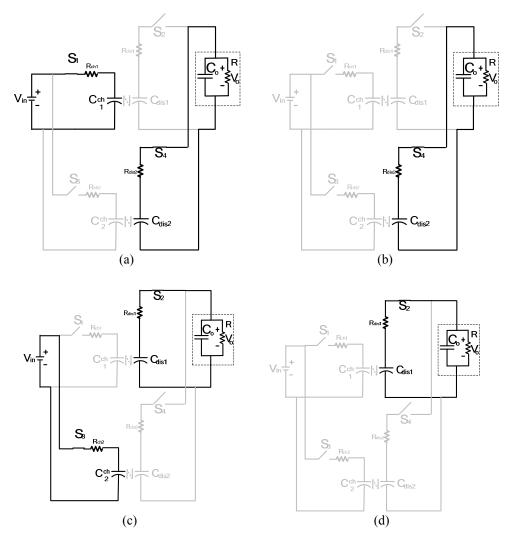

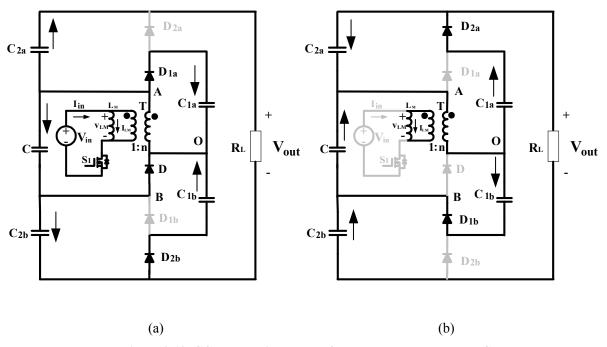

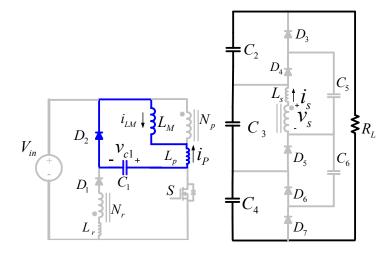

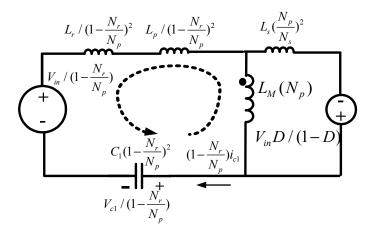

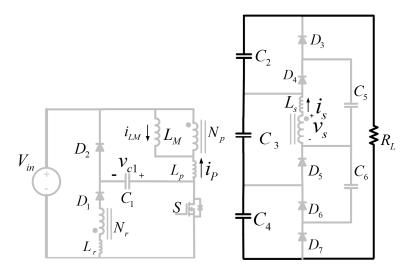

| Figure 11.3 Isolated HBC with energy regenerative snubber                                                                        | 179 |

| Figure 11.4 Energy regenerative snubber configurations                                                                           | 180 |

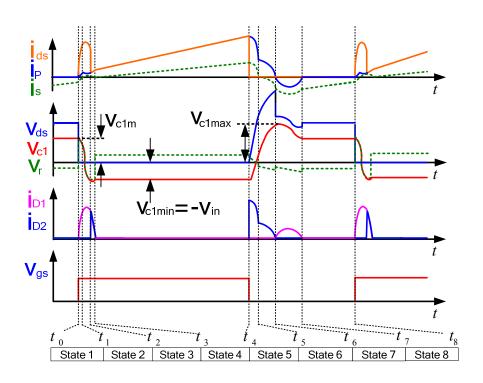

| Figure 11.5 Key waveforms under CCM operation condition                                                                          | 181 |

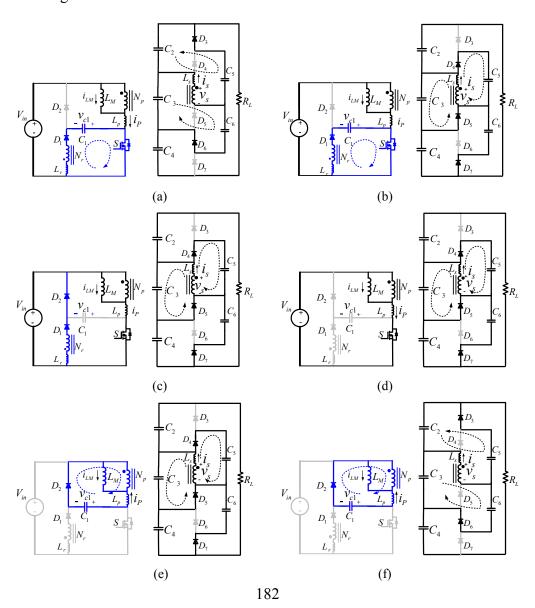

| Figure 11.6 Operational states under CCM condition (a) State 1~ (h) State 8                                                      | 183 |

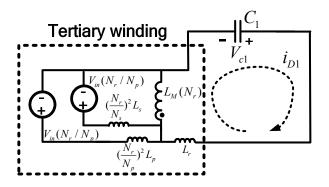

| Figure 11.7 Equivalent circuit of resonant tank of State 2                                                                       | 183 |

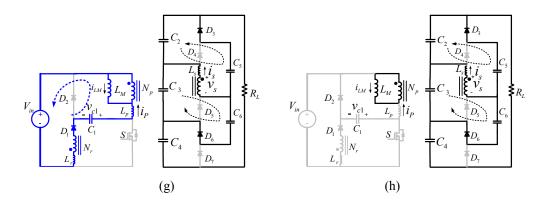

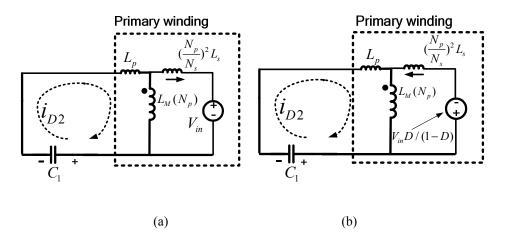

| Figure 11.8 Equivalent circuit of resonant tank                                                                                  | 184 |

| Figure 11.9 Intermediate state before state 6 under $V_{c1}(t_5) < V_{in}D/(1-D)$ condition                                      | 187 |

| Figure 11.10 Equivalent circuit of resonant tank at state 7                                                                    | 187 |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 11.11 Final state under DCM condition                                                                                   | 189 |

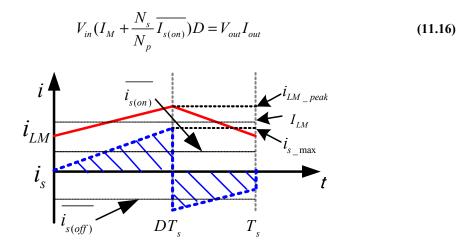

| Figure 11.12 Ideal waveforms of magnetizing current and secondary winding current.                                             | 191 |

| Figure 11.13 Desirable waveform of resonant capacitor C <sub>1</sub> .                                                         | 193 |

| Figure 11.14 Design of resonant capacitor C <sub>1</sub>                                                                       | 195 |

| Figure 11.15 Prototype with measurement set-up                                                                                 | 197 |

| Figure 11.16 Circuit Resonation states validation waveforms: Vgs, Vc1, Vr, Vs                                                  | 198 |

| Figure 11.17 Soft Switching waveforms from top to bottom V <sub>gs</sub> , V <sub>c1</sub> , V <sub>ds</sub> , I <sub>ds</sub> | 199 |

| Figure 11.18 Steady state waveforms from top to bottom $V_{c1}$ , $I_{d1}$ , $V_{out}$ , $V_{in}$                              | 199 |

| Figure 11.19 Efficiency curve under fixed gain Vin=35V, Vout=400V                                                              | 200 |

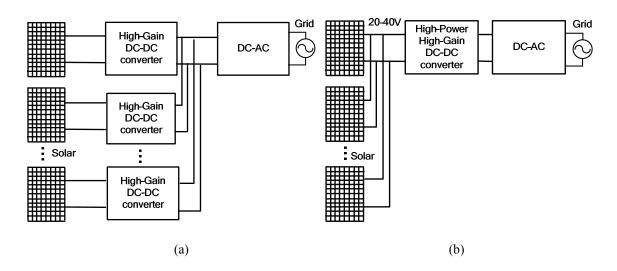

| Figure 12.1 Two-stage solar system.                                                                                            | 202 |

| Figure 12.2 3D DC-DC extension of HBC                                                                                          | 203 |

| Figure 12.3 3D 2n <sup>th</sup> -order Basic HBC                                                                               | 205 |

| Figure 12.4 3D Basic HBC                                                                                                       | 206 |

| Figure 12.5 Control signal for the 3D Basic HBC                                                                                | 207 |

| Figure 12.6 3D 2n <sup>th</sup> -order Tapped HBC                                                                              | 208 |

| Figure 12.7 Voltage gain of 2n <sup>th</sup> -order Tapped-inductor HBC                                                        | 209 |

| Figure 12.8 Multi-source paralleling of HBC                                                                                    | 210 |

| Figure 12.9 Multi-source paralleling solar system with Symmetrical HBC                                                         | 211 |

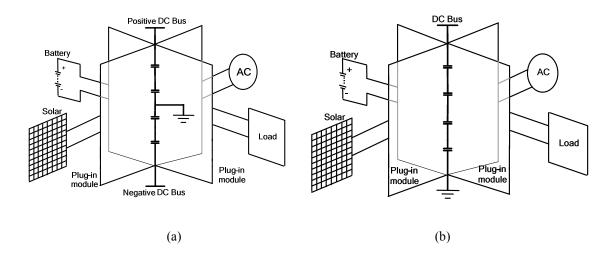

| Figure 12.10 Multi-source paralleling system with storage                                                                      | 212 |

| Figure 12.11 Half-bridge micro-inverter based on HBC                                                                           | 213 |

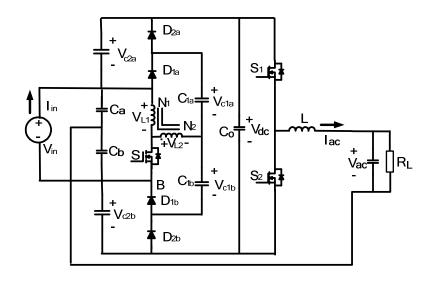

| Figure 12.12 Second-order Tapped HBC micro-inverter                                                                            | 214 |

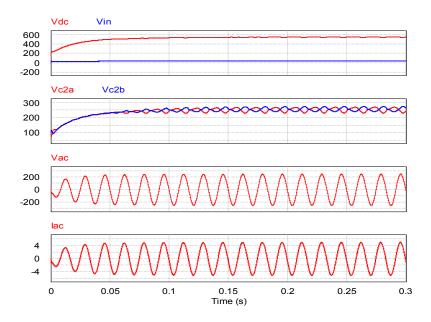

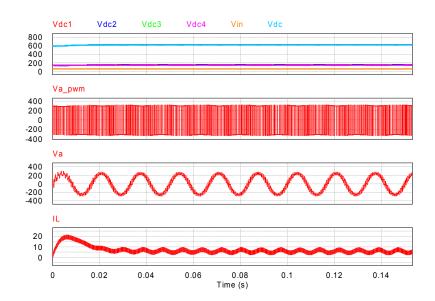

| Figure 12.13 Simulation waveforms of Second-order Tapped HBC micro-inverter                                                    | 214 |

| Figure 12.14 Second-order half-bridge symmetrical HBC micro-inverter              | 215 |

|-----------------------------------------------------------------------------------|-----|

| Figure 12.15 Simulation waveforms of third-order Symmetrical HBC micro-inverter   | 215 |

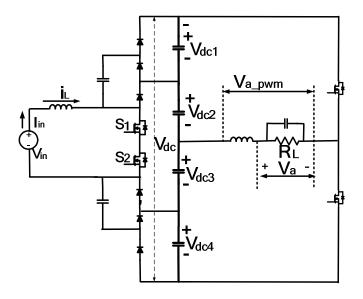

| Figure 12.16 Third-order Symmetrical HBC Multilevel inverter                      | 216 |

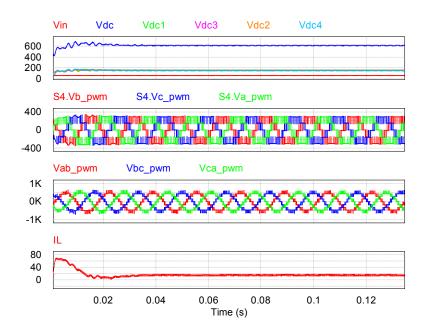

| Figure 12.17 Simulation waveforms of third-order Symmetrical HBC Multilevel inver | ter |

|                                                                                   | 217 |

| Figure 12.18 Multi-bus DC micro-grid system                                       | 218 |

| Figure 12.19 Grounding solutions for Multi-bus DC micro-grid system               | 219 |

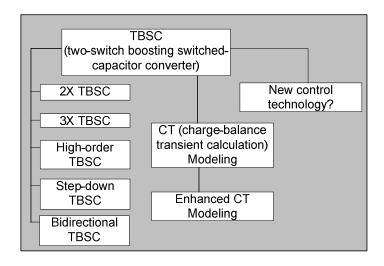

| Figure 13.1 Developed and future work of Part I                                   | 223 |

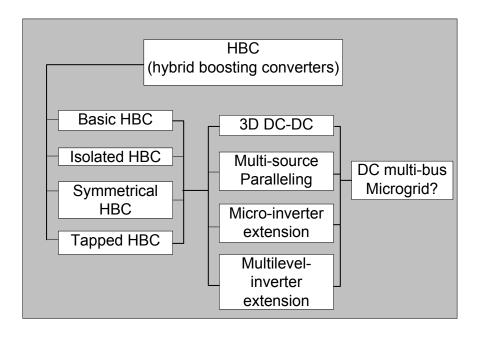

| Figure 13.2 Developed and future work of Part II                                  | 225 |

# LIST OF TABLES

| Page                                                                                |

|-------------------------------------------------------------------------------------|

| Table 1.1 Comparison of switched capacitor boosting topologies                      |

| Table 1.2 Combination of inductor based boosting topologies                         |

| Table 2.1 Comparison of SCC, inductor-based converter and LDO                       |

| Table 2.2 Comparison of surveyed steady state modeling methods for SC converter29   |

| Table 4.1 Circuit Parameters of 1kW 3X TBSC                                         |

| Table 5.1 Components Number Comparison                                              |

| Table 5.2 Components Stress Comparison                                              |

| Table 6.1 Verification of Steady State Model                                        |

| Table 6.2 Parameters of the 3X TBSC Prototypes                                      |

| Table 6.3 Parameter control for modulation testing                                  |

| Table 7.1 Circuit and Control parameters for model comparison                       |

| Table 7.2 Comparison of output impedance based on different Molding method89        |

| Table 7.3 Proposed modeling Method for modeling Simple dual-phase SC converter103   |

| Table 7.4 Comparison of Output impedance calculation for unity gain SC converter105 |

| Table 7.5 Parameter list for model comparison                                       |

| Table 7.6 Circuit parameters of unity gain SC converter                             |

| Table 9.1 Comparison of inductive switching cores                                   |

| Table 10.1 Components Stress                                                        |

| Table 10.2 Comparison of proposed second-order HBC with other converters167         |

| Table 10.3 Comparison of Normalized Capacitor Voltage Stress for Converters168      |

| Table 10.4 P  | arameter Selected for prototype design                          | 170 |

|---------------|-----------------------------------------------------------------|-----|

| Table 11.1 P  | arameters of example Design                                     | 195 |

| Table 11.2 C  | Component Design of Snubber Circuit                             | 196 |

| Table 11.3 Ci | ircuit Components list                                          | 197 |

| Table 12.1 3  | D DC-DC converter extension options                             | 204 |

| Table 12.2 Co | omponent count of 2n <sup>th</sup> -order N-branch 3D Basic HBC | 207 |

### **ACKNOWLEDGMENTS**

I'm writing this acknowledgement on Morning, Aril 10, 2016, Irvine, California, which is a cloudy morning. At this moment, recalling my four and half years' study in UC Irvine, all up and downs in my research and final achievements upon graduation, I cannot suppress my excitement to express my deepest gratitude to my dear advisor, Keyue Smedely, who offer me the chance to pursuit my PhD's degree in US and led me to the true way of becoming a scientist. Without her cultivation, both in personality and research methodology, my giant progress cannot be possible. It's her who changed my life and shed me the bright light into the future. There will never be enough words to express my acknowledgement to this.

Moreover, I would also like to express my sincere appreciation to professor Singer Sigmund, who served as co-advisor in my BSF project, Professor Michel Green, who not only served in my defense committee but also gave generous help during faculty position hunting, manager Ken Yang from Broadcom, who treated me nicely during internship and provided me with great recommendation upon graduation, Professor Alexander Abramovitz, who encouraged me a lot during difficult times in research, and Professor Yinyong Zhao, who showed me his treasurable research philosophy and inspired me the road to success.

It's my honor to spend my PhD life in the great UCI power electronics lab, with a group of talented and helpful people. They are graduated PhDs: Dr. In-Wha Jeong, Dr. Liang Zhou, and Dr. Marco Tedde, Dr. Arash, Dr. Roozbeh Naderi, and current PhD Students: Shouxiang Li, Ling jiang, Yifei Zheng, Daniel Gebbran. Moreover, my gratitude goes to all visiting scholars and students, Dr. Jia Yao, Dr. Ben Zhao, Kang Xiang Li. Florian, and Prof. Enyuan dong. All of their help and company are appreciated. Without their encouragement and help, I can't reach where I am.

I also want to acknowledge University of California, Irvine and the EECS department for all the financial support, which enables me to go over my PhD study.

Finally, special thanks are granted to my family, my parents, Lizhi Wu and Qiliang Wu, who supported me and encouraged me whatever I encountered in my life, my wife and son, who provided me a really supportive and warm family to make me focused on research, and my wife's parents, who devoted a lot of time, money and energy to take care of my family during my hard times.

# **CURRICULUM VITAE**

# Bin Wu

# **Education Background**

| 2004.9-2008.6 | B.S. in Electrical Engineering  Zhejiang University, Hangzhou, China                                        |

|---------------|-------------------------------------------------------------------------------------------------------------|

| 2008.9-2011.6 | M.S. in Electrical Engineering  Xi'an Jiao tong University, Xi'an, China                                    |

| 2011.9-2016.3 | Ph.D. in Electrical and Computer Engineering University of California-Irvine, CA, US Advisor: Keyue Smedley |

# **Working Experience**

| Summer 2008 | Internship: Assistant Electrical Engineer <b>PHILIPS</b> , Global Research Center (Shanghai), China      |

|-------------|----------------------------------------------------------------------------------------------------------|

| Winter 2010 | Internship: Assistant Electrical Engineer  General Electric (GE), "Appliance and Lighting", Xi'an, China |

| Summer 2011 | Internship: Assistant Electrical Engineer <b>Silergy</b> , Headquarter, Hangzhou, China                  |

| Summer 2013 | Internship: Assistant Electrical Engineer <b>Broadcom,</b> PMU group, Headquarter, CA, US                |

# **Teaching Experience**

| Fall 2013   | Class TA for <b>Introduction to control theory</b> (Undergraduate Course) |

|-------------|---------------------------------------------------------------------------|

| Winter 2013 | Lab TA for <b>Industrial and power Electronics</b> (Graduate Course)      |

| Winter 2014 | Lab TA for <b>Industrial and power Electronics</b> (Graduate Course)      |

| Fall 2015   | Class TA for <b>Senior Project design A</b> (Undergraduate Course)        |

| Winter 2015 | Class TA for <b>Senior Project design B</b> (Undergraduate Course)        |

#### **Publications**

### Journal Papers:

- [1] **B. Wu**, S. Li, K. Ma Smedley, and S. Singer, "A Family of Two-Switch Boosting Switched-Capacitor Converters," IEEE Trans. Power Electron., vol. 30, no. 10, pp. 5413–5424, Oct. 2015.(IF:6.008)

- [2] **B. Wu**, S. Li, Y. Liu, and K. Ma Smedley, "A New Hybrid Boosting Converter for Renewable Energy Applications," IEEE Trans. Power Electron., vol. 31, no. 2, pp. 1203–1215, Feb. 2016. (IF:6.008)

- [3] **B. Wu**, S. Li, K. M. Smedley, and S. Singer, "Analysis of High-Power Switched-Capacitor Converter Regulation Based on Charge-Balance Transient-Calculation Method," IEEE Trans. Power Electron., vol. 31, no. 5, pp. 3482–3494, May 2016. (IF:6.008)

- [4] **Wu, B.**; Naderi, R, Smedley, K. "A Modified Buck-Boost DMPPT Tracker with Improved Tracking Accuracy" submitted to IET power electronics (Accepted) (IF:1.683)

- [5] **Wu, B**.; Li, S.; Smedley, K. "A new Single-switch Isolated Hybrid Boosting Converter with Bipolar Voltage Multiplier" submitted to IEEE Transactions on Industrial Electronics (Accepted) (IF:6.498)

- [6] **Wu, B.**; Smedley, K. and S. Singer, "Comparative Analysis of Steady-State Models for Switched Capacitor Converter" submitted to IEEE Transactions on Power Electronics (Accepted) (IF:6.008)

# **Conference Papers:**

- [7] **B. Wu** and K. Smedley, "A new Isolated Hybrid Boosting Converter," in 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), 2015, pp. 28–34

- [8] **B. Wu**, S. Keyue, and S. Sigmond, "A new 3X interleaved bidirectional switched capacitor converter," in 2014 IEEE Applied Power Electronics Conference and Exposition APEC 2014, 2014, pp. 1433–1439.

- [9] **B. Wu**, S. Li, and S. Keyue, "A new hybrid boosting converter," in 2014 IEEE Energy Conversion Congress and Exposition (ECCE), 2014, pp. 3349–3354.

- [10] **B. Wu** and S. Keyue, "A current control MPPT method in high power solar energy conversion system," in 2014 IEEE Applied Power Electronics Conference and Exposition APEC 2014, 2014, no. 1, pp. 3021–3025.

- [11] **B. Wu**, S. Keyue, and S. Sigmond, "A Unified Switched Capacitor Converter," in Conference Proceedings IEEE Applied Power Electronics Conference and Exposition APEC, 2014, pp. 1433–1439.

- [12] Singer S, Beck Y, **Bin Wu**, et al. Suitability of capacitive converters to photovoltaic systems [C]//Electrical and Electronics Engineers in Israel (IEEEI), 2014 IEEE 28th Convention of. IEEE, 2014: 1-5.

- [13]S. Li, **B. Wu**, K. Smedley, and S. Sigmond, "Analysis and Design of a 1-kW 3X Interleaved Switched-Capacitor DC-DC Converter," in Energy Conversion Congress and Exposition (ECCE), 2014 IEEE, 2014, pp. 1692–1698.

#### **Patents:**

- [14] **Bin Wu**, Keyue Smedley, Sigmond Singer, Two-switch switched-capacitor converters, Issued number: US20150263612 A1, Issued date: 2015.9.17

- [15] **Wu, B.**; Smedley, K. "A family of hibird boosting converters" (Pending)

# ABSTRACT OF THE DISSETTATION

### The Art of Voltage Boosting

Part I: Boosting Switched Capacitor Converter

**Part II: Hybrid Boosting Converters**

By

Bin Wu

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Irvine 2016

Professor Keyue M. Smedley, Chair

Voltage boosting is required in many energy conversion applications, ranging from front-end solar energy system to Medium-Voltage DC (MVDC)-grid system, and from headlamp ballast of automobile to fuel cell powered system. This dissertation is dedicated to the development of voltage boosting technology. New circuits were found both in switched capacitor converters and inductor-based power converters.

# Part I

Switched Capacitor Converter (SCC) is a special branch of power electronics converters which is composed of capacitors and switches without the participation of inductors/transformers. It potentially has lower electromagnetic interference (EMI), lighter weight, lower cost, higher energy density, and the promise for full integration.

xxi

In this part, a family of "Two-switch Boosting Switched-capacitor Converters (TBSC)" is introduced, which distinguishes itself from the prior arts by its symmetrical interleaved operation, reduced output ripple, low yet even voltage stress on components, and systematic expandability. Along with the topologies, a modeling technique based on charge-balance transient-calculation is formulated, which provokes the converter regulation method through duty cycle and frequency adjustment. The design guideline for high efficient TBSC is provided and regulation under high power condition is explored.

In addition, an enhanced accurate modeling technique considering the output capacitor effect is developed for simple two-phase SC converters.

#### Part II

Built upon the momentum of the "Two-switch Boosting Switched-capacitor Converters (TBSC)" circuit structure, another family of Hybrid Boosting Converters (HBC) is developed, featuring wide regulation range, symmetrical configuration, low component voltage stress, small output voltage ripple, and expandable structure. It integrates the inductive switching cores of various functionalities and control strategies with Bipolar Voltage Multiplier (BVM), resulting in the new breed of hybrid converters: Hybrid Boosting Converters (HBC). The proposed HBC family includes the basic HBC, symmetrical HBC, Isolated HBC, and tapped inductor HBC, all of which are analyzed in details and design considerations are provided.

In addition, the 3D DC-DC converter concept for high power application, inverter configuration and DC micro-grid based on HBC converters are developed.

The proposed HBCs are applicable in many areas such HID lamp driver, X-ray system, ion pumps, front-end photovoltaic energy system, and energy storage systems.

# **Chapter 1** Introduction

# 1.1 Objective

In the past, most DC-DC converters were for step-down applications since most consumer electronic products draw energy from Power Grid, whose voltage level is much higher than the load DC voltage. A typical grid interfaced power electronics system is comprised of a front-end stage as a voltage rectifier and a second stage as a step-down DC-DC converter. The first stage performs the function of rectifying the AC voltage to a relatively high DC voltage, either actively or passively, while the second stage converts the high DC voltage to a much lower DC voltage. Step-down DC-DC topologies such as fly-back, LLC, push-pull converter for second stage were extensively investigated both in academia and industry, aiming at higher efficiency, lower cost, increased power density and improved reliability.

In contrast, voltage boosting technologies, which are also an important subset of DC-DC power electronics conversion technology, were less developed due to fewer applications found decades ago. In recent years, power electronics technology has been experiencing a booming development, with applications ranging from mili-watt energy scavenger to tens of megawatt wind power system. Voltage step-up technology is playing an increasingly important role in modern power electronics industry. The Uninterruptible Power Supply (UPS) system, serving as the back-up power system for critical load such as factories and hospitals, demands high step-up converter to boost the 48V telecom power supply voltage to 380V for inverter application[1]. The two-stage PV system requires a

front-end stage to be high-gain DC-DC converter to step up voltage from 20~40V to 400V, due to low terminal voltage of single solar panel. The offshore wind farm with an internal Medium Voltage DC (MVDC) grid calls for a high power high gain DC-DC converter to interface between the rectifier output at 1~6kV with MVDC bus at 30~60kV[2]. The automobile HID headlamp driver requires a DC voltage about 100V which should be boosted from the 12V battery voltage. Moreover, the state of art voltage booting technology has also been found widely used in X ray power supply system, modern electrical vehicle system, and fuel cell powered systems, where different specific requirements may be required, such as isolated or non-isolated, regulated or non-regulated, low gain or ultra-high gain, single-direction or bidirectional.

The objective of this dissertation is to explore voltage boosting technologies. Switched capacitor converter known as a network composed of only capacitors and switches has the advantages of easy integration, high power density, low EMI and lower cost. While for inductor-based converters, as it employ the magnetic components such as inductor, transformer or tapped-inductor, has an apparent advantage of easiness in voltage regulation. This dissertation focuses on voltage boosting technology both in switched capacitor and inductor based converter fields. New topologies were discovered together with modeling techniques and control methods.

# 1.2 Background

Voltage boosting technology in the power electronics field can be regarded as an input source connected with a collection of voltage boosting elements, resulting in an increased output voltage. Apart from the active switch, other adopted components include diode, capacitor, inductor, tapped inductor and transformer. A concept description graph of voltage boosting technology can be presented shown as Figure 1.1. According to the figure, when the component network doesn't involve magnetic components, it can be defined as boosting switched capacitor converter. Otherwise it is an inductor based boosting converter.

Figure 1.1 Voltage Boosting Technology

A comprehensive review of voltage boosting technology in switched capacitor converter and inductor based converter are provided in following two subsections.

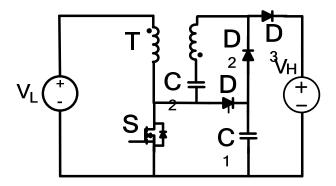

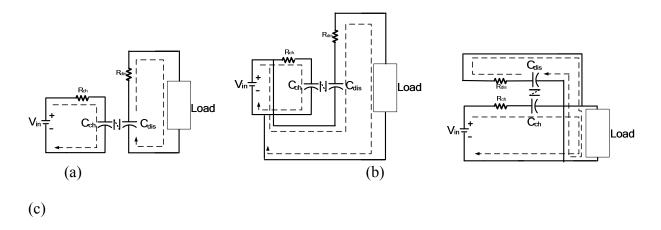

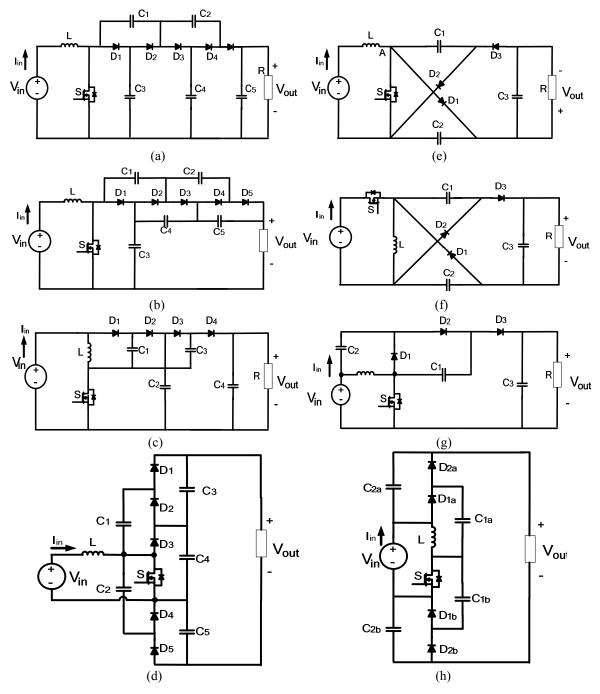

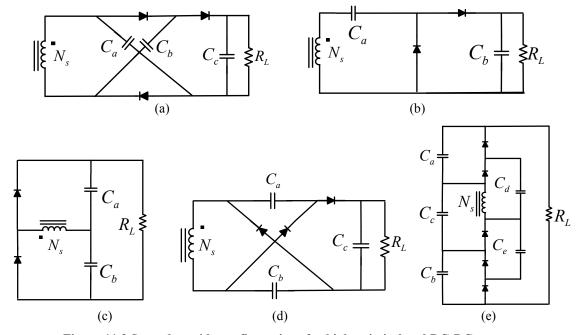

Figure 1.2 Switched Capacitor Boosting Technology

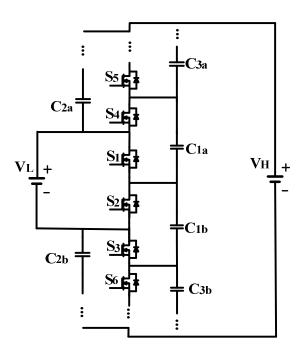

# 1.2.1 Switched capacitor voltage boosting technology

In the past, many step-up switched capacitor converters have been reported. Typical topologies are listed in Figure 1.2 and discussed in this section. The DC low voltage side has input source of  $V_L$  whose amplitude is "E". In the low voltage side is AC input, low annotated as  $V_s$ , it's amplitude is also assumed "E". Therefore, all the associated capacitors voltage stress can be clearly identified by "E" or multiples of "E" in Figure 1.2. The voltage at high voltage side is annotated as  $V_H$ . Moreover, the switches  $S_1$  and  $S_2$  are usually operating under duty cycle of 0.5 in complimentary manner. In regulation case, the switch controlling charging state can operate under Pulse Width Modulation (PWM) mode. Each converter is briefly introduced as below:

# (1) Dickson Multiplier

Voltage multiplier was initially created to rectify and boost the alternating voltage to a high DC voltage, which has been used in X-ray tube power supplies[3]–[5]. The famous Dickon Multiplier is shown as Figure 1.2(a)[6]. The disadvantage of this multiplier is its uneven voltage stress of flying capacitors. Hence, this multiplier is not widely used.

#### (2) Cockcroft Walton multiplier

In contrast, the Cockcroft Walton multiplier has evenly distributed voltage across the flying capacitors, thus the component stress is low. This voltage multiplier has been widely used in very high gain applications, as shown in Figure 1.2(b). Isolated version and variations based on this multiplier has been comprehensively investigated[7], [8]. Small signal model is derived in [9]. However, due to its non-interleaving nature, large flying capacitors are needed to suppress the output voltage ripple.

### (3) Fibonacci SC converter

Fibonacci switched capacitor converter is known as the topology that has the maximum attainable gain for a given number of capacitors[10], shown as Figure 1.2(c). It is a good candidate to increase the voltage gain with minimized die area. But it is demonstrated that the equivalent output resistance increases rapidly as the gain increases[11].

# (4) MMCCC

The Multilevel Modular Capacitor Clamped DC-DC Converter (MMCCC) is a two phase modular switched capacitor converter[12], shown as Figure 1.2(d). It is expect to improve the conversion efficiency due to current flow path is optimized. But the high switch count and the increased capacitor stresses with increment of conversion ratio can post challenges on components selection, size, and cost[13].

# (5) Voltage-lift Converter

The voltage lift technology has many variations[14]–[18], one of which is switched capacitor converter. A 3-lift circuit is shown as Figure 1.2(e). It has some similarities with the principle of Dickson charge pump but has less switches and smaller gain boosting capability. It can be a good candidate when tradeoff between switch number and voltage gain is required. But it also suffers from unbalanced capacitor stress issue and large output voltage ripple.

### (6) The interleaved Parallel-Series SC converter

Figure 1.2(f) gives an interleaved Parallel-Series voltage doubler topology[19]. Other step-up topologies with different gain but similar configurations are investigated in [20]–[23]. The similarity of these converters is that the paralleling phase is controlled to regulate the output voltage, which determines the charging time of flying capacitors. Moreover,

interleaved branch is adopted to minimize the output filter capacitor and input current ripple. An apparent disadvantage of these topologies is the significant components count adopted to achieve a moderate gain.

### (7) Dickson Charge Pump

Dickson Charge Pump is a well know charge pump and is being used in many voltage step up applications[24], shown as Figure 1.2(g). Compare with Fibonacci SC converter, it shows better performance in high gain situation, as equivalent output impedance is comparatively lower[11]. However, similar to voltage lift SC converter, it suffers from uneven capacitor stress and large output ripple.

### (8) DC-DC voltage doubler based on half-cell

The DC-DC voltage doubler based on half-cell shown in Figure 1.2(h) is proposed in [25]. It introduces the interleaving operation to achieve smaller output ripple and input current stress. But the structure is not easy to expand while maintaining symmetrical configuration and the switch count is still large to achieve a given voltage gain.

### (9) Ladder converter

Ladder converter shown as Figure 1.2(i) is well known for its capability of elevating an input voltage like a ladder. All flying capacitors and switches are equally stressed and the control is easy with two simple complementary control signals. The structure is flexible for expansion. But due to asymmetrical configuration, the component current stress is still large as well as output ripple.

# (10)Flying Capacitor SC converter

The flying capacitor SC converter is employed in the electrical vehicle systems [26].A four-level dc-dc flying capacitor SC converter is shown as Figure 1.2(j). It apparently has a

reduced the flying capacitor number compared with other topologies in Figure 1.2 having same voltage gain. But it has an increased the component stress and calls for larger flying capacitor and filter capacitor to handle the voltage ripples. Moreover, the control complexity is increased because more operational stages found during a switching period.

# (11) SC converter based on generalized multi-level converter

The SC converter shown in Figure 1.2(k) is also adopted in (42/14V) automotive system in [27]. The voltage conversion principle is straightforward with only two simple complementary control signals. The components stress is also balanced and minimized. But the large component count may prevent it from wide applications.

A summarizing table of listed topologies is provided as Table 1.1.

Table 1.1 Comparison of switched capacitor boosting topologies

| Figure 1.2 | Gain(V <sub>H</sub> ) | Flying<br>Capacitors | Switch/<br>Diode | Comment Voltage<br>Stress | Output Voltage<br>Ripples |

|------------|-----------------------|----------------------|------------------|---------------------------|---------------------------|

| (a)        | 5E                    | 4                    | 5                | large/uneven              | Large                     |

| (b)        | 7E                    | 6                    | 7                | Low/even                  | Large                     |

| (c)        | 5E                    | 3                    | 10               | large/uneven              | Large                     |

| (d)        | 4E                    | 3                    | 10               | large/uneven              | Large                     |

| (e)        | 3E                    | 3                    | 6                | large/uneven              | Large                     |

| (f)        | 2E                    | 2                    | 8                | Low/even                  | Small                     |

| (g)        | 5E                    | 4                    | 9                | large/uneven              | Large                     |

| (h)        | 2E                    | 2                    | 6                | Low/even                  | Small                     |

| (i)        | 3E                    | 3                    | 6                | Low/even                  | Large                     |

| (j)        | 3E                    | 2                    | 6                | large/uneven              | Large                     |

| (k)        | 3E                    | 6                    | 12               | Low/even                  | Small                     |

It is not easy to pick a best topology among the listed topologies. Rather, it's more meaningful for designers to understand tradeoffs for specific applications. Different topologies may have some merits in certain aspects but suffer from problems in other

perspectives. The comparison table shown in 1.1 gives a general guideline for the trade-off considerations

Part I of this dissertation is dedicated to provide some switched capacitor step-up solutions with small active switch count, low and even component stress, and small output voltage ripple, which is essential to reduce the cost and improve power density of SC converter.

# 1.2.2 Inductor based voltage boosting technology

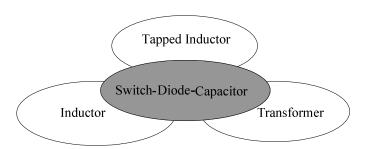

On the contrary of switched capacitor converter, the inductor based voltage boosting topology has at least one magnetic component participating in the voltage conversion process. The magnetic components can serve as an energy storage element or transformer for mere voltage level escalation. Most inductor-based voltage-boosting topologies can be illustrated as some combinations in Figure 1.3. It should be noted that in some places, if a transformer is designed to store energy in its magnetizing inductance while release it in other operational stages, it is called "coupled inductor or tapped inductor", regardless weather it provides isolation or not. Nevertheless, in this dissertation, to clarify topology based on configurations, transformer is defined based on whether it provides the galvanic isolation or not. If it doesn't provide galvanic isolation for the converter, it is defined as tapped inductor. Otherwise, it is defined as transformer.

Figure 1.3 Inductor based voltage gain boosting elements

Figure 1.3 shows that the switch is the central element of a voltage boosting converter; a combination with four other major voltage boosting elements yields countless new topologies. Reviewing all the topologies is a tedious work. Therefore, they are briefly discussed based on the combination categories as below:

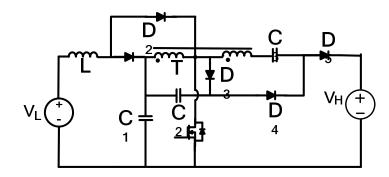

### (1) Switch+Inductor

Figure 1.4 Switch+Inductor topology

The basic inductor based voltage boosting topology is the traditional boost converter, shown as Figure 1.4. It consists only switch and inductor elements because the diode and output capacitor serve as rectifier and filter instead of implementing voltage lift functionality. The boost converter is well suited to step up voltage less than four times as it has very low efficiency at a higher gain, in which case the extreme duty cycle has to be used and serious diode reverse recovery loss occurs. Moreover, the gain drops when duty

cycle becomes closer to one due to parasitic parameters of the circuit. Therefore, in order to further increase the voltage gain while maintain high efficiency, new topologies must be created.

#### (2) Switch+Transformer

A simple way to increase voltage level is using the principle of magnetic coupling. Figure 1.5 shows a conventional fly-back topology. It was commonly used in step-down DC-DC applications previously with step-down transformer. However, it also can be used to step up voltage when more turns at secondary side is used compared with primary side. Therefore, it is considered as voltage boosting technology with combination of switch and transformer. However, the issue associated with this approach is that when the voltage gain is increased, the primary side current will increase accordingly, leading to increased loss of leakage energy and aggregated voltage spike problem.

Figure 1.5 Switch+ Transformer topology

A new topology based on this combination was proposed in [28], which took use of the third winding of transformer and the primary-parallel secondary-series structure, substantially extended the voltage gain. There are many merits created by this structure but the major concern is the challenges posted by production of three-winding transformers.

# (3) Switch+Tapped-inductor

Another voltage gain boosting element is tapped inductor. The tapped boost converter is a well-known converter which employs the tapped inductor to extend the gain of boost converter, shown as Figure 1.6. Detail analysis of this converter is given in [29]. The problem with this topology is similar to the fly-back converter. The leakage energy loss may limit the conversion efficiency when the gain increases.

Figure 1.6 Switch+Tapped-inductor topology

### (4) Switch+Inductor+Diode-Capacitor

Diode-capacitor structure is also a gain enhancement solution which can avoid dealing with issues cause by magnetic coupling method. A typical topology is shown in Figure 1.7, proposed in [30]. The diode-capacitor structures basically serve as voltage duplicators which are able to effectively enhance the voltage gain while maintaining high efficiency. But the capacitor number with high voltage ratings can increase the cost and volume of converter. Moreover, the output voltage ripple needs to be mitigated to reduce output filter size.

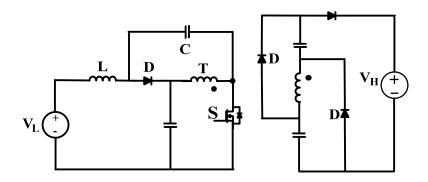

Figure 1.7 Switch+inductor+diode-capacitor topology

#### (5) Switch+Transformer+Diode-Capacitor

A typical topology that implements the idea of combining switch, transformer and diode-capacitor is given in Figure 1.8, reported in [31]. In such case, the desirable voltage gain can be achieved either by adjusting transformer turn ratio or diode-capacitor stage, leading to a more flexible gain design. But the leakage of transformer needs to be taken care of and the component stress is high.

Figure 1.8 Switch+Transformer+Diode-capacitor topology

#### (6) Switch+Tapped-Inductor+Diode-Capacitor

A more advanced combination of two gain boosting elements is integrating tapped inductor with diode-capacitor stages, while handling leakage energy simultaneously. This

solution usually leads to more sophisticated operational process, but many topologies with high gain and high efficiency were created, at the price of increased components count. An example topology is show as Figure 1.9, proposed in [32]. The main reason for high efficiency achieved by these topologies is that it recycles the leakage energy of tapped inductor and creates soft-switching condition for the main switch. But due to more complicated circuit structure and increased component count, they are more suitable for low power applications. Moreover, large filter capacitors are normally required at the output.

Figure 1.9 Switch+Tapped-inductor+Diode-capacitor topology

#### (7) Switch+Inductor+Transformer+Diode-Capacitor

With a further increased the complexity of combination (5), an extra inductor is added in some topologies, a sample circuit is given in Figure 1.10, developed in [33]. The benefit brought by the new inductor includes continuous input current and enhanced voltage gain boosted by the inductor. But due to the power processing path gets longer, the loss dissipated in circuit path may increase.

Figure 1.10 Switch+Inductor+Transformer+Diode-capacitor topology

#### (8) Switch+Inductor+Tapped-inductor+Diode-Capacitor

To amend the pulsating input current problem of the combination (6), an input inductor also can be incorporated in such circuits[34], shown as Figure 1.11. This combination has similar complexity level as the combination (7), which has employed three voltage boosting elements in the final circuit. The voltage gain was greatly enhanced. But compared to non-isolated structures, the efficiency has no superiority. Another topology implementing this combination was proposed in [35], where soft switching for main switch was created and more promising efficiency was derived. But complicate circuit design and increased component stress post the cost challenge for commercializing.

Figure 1.11 Switch+Inductor+Tapped-inductor+Diode-capacitor topology

In summary, the art of inductor-based boosting technology can be very sophisticated with numerous possibilities provided by the increase of participated boosting elements. It is a constant pursuit among the researchers to find circuit structures with minimum components, best efficiency, while achieving maximum gain. The challenges are discussed in above discussions. Many papers compared a proposed topology with some previous papers only in terms of voltage gain, but under different combination categories, which may not be appropriate. Such comparison may have disregarded the drawbacks brought by the high gain obtained, such as increased components count, component stress or deteriorated efficiency.

Therefore, a more proper comparison shall be performed within the same combination categories as referred to apple to apple comparison. For example, when the continuous input current or galvanic isolation is indispensable in some applications, such conditions should be default for all the converters in the comparison. The difference should be the cost, power density, and efficiency of two topologies with similar gain boosting capability, crossing combination categories. In this way, superior topology can be finally selected for specific applications.

Table 1.2 Combination of inductor based boosting topologies

| Combinations<br>Elements | 1    | 2    | 3             | 4                                      | 5                       | 6             | 7                      | 8                                |

|--------------------------|------|------|---------------|----------------------------------------|-------------------------|---------------|------------------------|----------------------------------|

| A. Switch                | *    | *    | *             | *                                      | *                       | *             | *                      | *                                |

| B. Inductor              | *    |      |               | *                                      |                         |               | *                      | *                                |

| C. Transformer           |      | *    |               |                                        | *                       |               | *                      |                                  |

| D. Tapped inductor       |      |      | *             |                                        |                         | *             |                        | *                                |

| E. Diode-Capacitor       |      |      |               | *                                      | *                       | *             | *                      | <b>*</b>                         |

| References               | [36] | [28] | [29],<br>[37] | [1], [15],<br>[16], [30],<br>[38]–[60] | [5], [31],<br>[61]–[68] | [69]–<br>[86] | [33],<br>[87]–<br>[96] | [34],<br>[35],<br>[97]–<br>[105] |

The combination categories are summarized in Table 1.2, with associated references given for further investigation.

In this dissertation, a family of inductor based converter, which is composed by a Bipolar Voltage Multiplier (BVM) and different inductive switching cores, is proposed. They can be classified to different categories in Table 1.2. Their superiority among the topologies in the same category is analyzed and demonstrated.

#### 1.3 Outline of the thesis

This dissertation is composed of two parts. The first part reports the invention related to the voltage boosting switched capacitor topologies: the Two-switch Boosting Switched Capacitor Converter (TBSC). The second part reports the discoveries of new inductor-based converters: the Hybrid boosting Converters. Each part is presented with theoretical analysis and experimental demonstrations.

#### Part I:

The general introduction and development of switched capacitor converter is given in Chapter 2, with the topology, modeling and control technique reviewed respectively. The new development in this Part is outlined. In Chapter 3, the topology evolvement of TBSC family and its operation principal are introduced by case study of 2X TBSC and 3X TBSC. The new modeling method for TBSC is presented in Chapter 4. The performance investigation of TBSC and comparison with some previous topologies are carried out in Chapter 5. The simulation and experimental verification of proposed theory are provided in Chapter 6. The generalized Charge-balance Transient-Calculation (CT) modeling method

suitable for interleaved SC converter and enhance CT modeling method considering output capacitance are extensively studied in Chapter 7. They are both compared with many recently developed modeling methods.

#### Part II:

In part II, the introduction of hybrid converter is given in Chapter 9 and the new development in Part II is outlined. The topology development of Hybrid Boosting Converters (HBC) family is introduced in Chapter 10, which is inspired by TBSC family. The operational principles of each family member are briefly introduced. In Chapter 11, the based members of HBC family, basic HBC, is fully investigated. It is compared with other topologies in the same category defined by previous section. Experimental results are provided to verify the proposed theory. In Chapter 12, another member of HBC family, isolated HBC, is fully explored with a new design method of lossless snubber circuit proposed to cope with the leakage problem of transformer. The performance comparison with other work and experimental verification are provided. In Chapter 13, many potential new circuit configurations and applications are developed based proposed HBC converter. The simulation results are provided to verify the feasibility of these configurations.

# Part I Two-switch Boosting Switched Capacitor Converter

# **Chapter 2 Introduction of Switched Capacitor**

# Converter

Switched Capacitor Converter (SCC) is an important subset of power electronics converters, which is composed of capacitors and switches without the participation of inductors/transformers. It potentially has lower Electro Magnetic Interference (EMI), lighter weight, lower cost, higher energy density, and the promise for full integration[106], [107]. A comprehensive comparison of switched capacitor converter, inductor based converter, and Low Voltage Dropout (LDO) is summarized in Table 2.1.

Table 2.1 Comparison of SCC, inductor-based converter and LDO

| Comparison       | Switched capacitor converter | Inductor based converter | LDO                   |  |

|------------------|------------------------------|--------------------------|-----------------------|--|

| Concept topology | S1 Ron S2 Ron Ceq ESR        | S Ron L                  | S S                   |  |

| EMI emission     | Low                          | High                     | Very low              |  |

| Cost             | Low                          | High                     | Very low              |  |

| Volume           | small                        | large                    | Very small            |  |

| Weight           | light                        | heavy                    | light                 |  |

| Integration      | full                         | partial                  | full                  |  |

| input current    | impulsive                    | peak limited             | continues             |  |

| regulation       | poor                         | good                     | poor                  |  |

| Power density    | high                         | medium or low            | high                  |  |

| efficiency       | Suffer intrinsic loss        | good                     | Suffer resistive loss |  |

| Gain flexibility | Step up/step down            | Step up/step down        | Step down             |  |

| Dynamic          | Fast                         | Medium                   | Slow                  |  |

According to Table 2.1, the unique merits that switched capacitor converter can bring to future portable devices is small size, high power density, flexible gain choice and fast

response equipped by appropriate control scheme. Due to these unique characteristics, it becomes increasingly important to investigate the topology, modeling and control of switched capacitor converters.

In this chapter, the general development of switched capacitor converter in past decades is briefly reviewed in section 2.1. The previous research outcomes focused on topology, modeling, and control of switched capacitor converter are briefly discussed. The new development and contributions in this part are outlined in section 2.2.

## 2.1 Development of switched capacitor converter

#### 2.1.1 Topology

Before 1990s, switched capacitor converter was primary in the form of voltage multiplier where diodes were usually driven by sinusoidal source[3]. After 1990s, switch mode Switched Capacitor Converter (SCC) attracted more attentions from power electronics community. A number of new topologies based on two-branch interleaving operation were proposed and verified with discrete semiconductor components prototype in power electronics labs[19], [20], [23], [108]–[110]. They were basically based on the idea of parallel-series configuration. Most of these topologies relied on controlling the time of charging phase to regulate the output voltage. These converters showed high power density and small output ripple. In the meantime, the CMOS level circuit design on simple switched capacitor converter began at the end of 1990s[111], [112]. In 1999, the simple switched capacitor product LM2660 with voltage doubling and inverting functions was released by National Semiconductor. In 2002, regulated SC converter with wide input

voltage range Max5008 was created by Maxim. In 2006, improved version of voltage inverting and doubling SC converter TL7660 was announced by TI. All these commercialized SC converters were focused on low power, simple topology by utilizing off-chip surface mounted capacitors. Compare with inductor-based converter, significant improvement was achieved in converter size by getting rid of inductor. Thereafter, researchers intended to integrate increased number of switches to formulate more complicate switched capacitor converters, such as charge pump[113] and structure variable SC converters[114].

In recent years, along with the advance of semiconductor industry, full integration of capacitors have become more realistic, which triggered a new round of enthusiasm to pursuit full integrated SC converter with further reduced convert size and improved power density. Many industrial and academic research institutions such as IBM, Intel, TI and UC Berkeley have built chip level full integrated SC converters in laboratory using different capacitor integration technologies [115]–[121]. Normally, structure variable scheme was adopted for SC converter to increase regulation range. Moreover, great efforts have been reported to optimize the design[122] and improve power density[123] of full integrated switched capacitor converter.

On the other hand, the application of switched capacitor converters on high power field was found in automobile system in 2000s, where topology using multilevel DC-DC structure were adopted[27], [124]. Article [125] reported a unregulated 1kW SC DC-DC converter for 42V automobile system with peak efficiency of 98%. In order to mitigate pulsating current and reduce capacitor size, resonant inductor was introduced to turn the SCC to Resonant Switched Capacitor Converter(RSCC) [126]. Some merits in efficiency

improvement under high power condition were confirmed. Article [127] uses the stray inductance in circuit to operate the resonant switched capacitor converter at 55kw. Article [128] and [2] proposed a new resonant SCC based on utilization of stray inductance or air core inductor, in which case careful selection of switching frequency is necessary. The regulation of high power switched capacitor becomes a challenge due to possible high component stress. Recently, some more switched capacitor topologies for DC-AC, AC-DC and AC-AC conversion have been reported[45], [128]–[131].

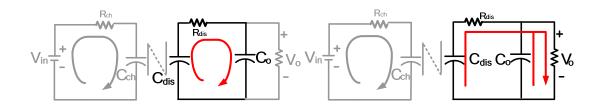

#### 2.1.2 Modeling

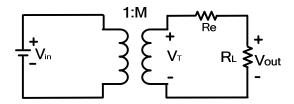

Modeling technique of switched capacitor converter is essential to understand the performance of SCC. In 1990s, the traditional state-space averaging method was adapted to model the switched capacitor converter for steady state model analysis [19], [132], [133]. This model is general for inductor based power converter modeling and it found its way for switching capacitor converter modeling with satisfactory results under high frequency and large flying capacitance condition. Modified state-space averaging method was introduced to address the nonlinear property of switched capacitor but does not provide the frequency regulation characteristic either [134], [135]. In recent years, many new modeling techniques were developed to study the physical insights of switched capacitor converter from different aspects [136]–[153]. A widely referred equivalent circuit for steady state model of SC converter is showed in Figure 2.1. Instead of deriving the steady state conversion ratio of a switched capacitor converter directly, calculation of equivalent output impedance R<sub>e</sub> was explored.

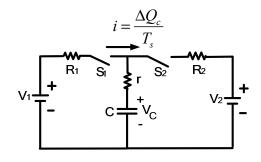

Figure 2.1 Equivalent circuit of SCC for steady state model

Based on the equivalent circuit, V<sub>T</sub> is defined as target voltage, which is determined by the topology of switched capacitor converter. Regulation of equivalent transformer turn ratio M typically requires a large number of switches and capacitors to reconfigure circuit topology [114], [120], [154], [155]. Once M is fixed, lower equivalent R<sub>e</sub> leads to higher conversion efficiency. Consequently, to derive an elegant expression of R<sub>e</sub> becomes objective of many researchers for steady state modeling.

Previously, most expressions of R<sub>e</sub> were derived based on analysis of a simplified SC block [136]–[146], as shown in Figure 2.2. Firm input and output voltage were usually assumed in the charging or discharging loops. The intermediate capacitor C serves as a storage element which delivers charge and energy by manipulation of switches S<sub>1</sub> and S<sub>2</sub>. More sophisticated converters were considered composition of multiple building blocks equivalent to this basic structure [137]. Typically, the output filter capacitor effect was neglected, which raises the difficulty for output voltage ripple control.

Figure 2.2 Simple SC blocks for steady state model analysis.

The recently developed steady state modeling techniques are reviewed as follows:

#### (1) Average current base method

In [136], [137], an average current based steady state model was proposed based in Figure 2.2. It assumes the intermediate capacitor voltage varied from  $V_{c1}$  to  $V_{c2}$  during discharging state. According to charge balance, the average current passing from  $V_1$  to  $V_2$  was found and denoted as i. The equivalent resistance between  $V_1$  and  $V_2$  was expressed as:

$$R_{eq} = \frac{V_1 - V_2}{i} = \frac{1}{fC} \frac{e^{\frac{(D_1 T_1 + D_2 T_1)}{\tau_1} - 1}}{e^{\frac{D_1 T_1}{\tau_1}} - 1)(e^{\frac{D_2 T_1}{\tau_1}} - 1)}$$

(2.1)

where  $D_1$  and  $D_2$  are duty cycle of charging and discharging state,  $\tau_1$  and  $\tau_2$  are time constant of charging and discharging loops.

Equation (2.1) provides a unified form of the output impedance showing overall impact from circuit parameters on steady state of the unity gain SC converter, including the switching frequency, duty cycle, resistive elements and flying capacitance. But the method is based on the assumption of firm input voltage  $V_1$  and output voltage  $V_2$  sources. It is general but may not be accurate when limited output filter capacitance is considered.

#### (2) Average-current-base conduction loss method

Another general method based on average-current conduction loss calculation was proposed in [142]–[144]. This method divided a switching period into switching phases according to the operational modes. For each phase, equivalent RC sub-circuits were found

and power loss caused by each sub-circuit was calculated to match with a corresponding equivalent output resistor R<sub>ei</sub>. Then the total output impedance can be accumulated as:

$$R_e = \sum_{i=1}^{m} k_i^2 \frac{1}{2f_s C_i} \frac{1 + e^{-\beta_i}}{1 - e^{-\beta_i}}$$

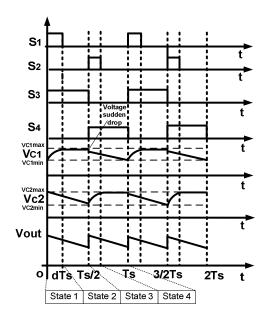

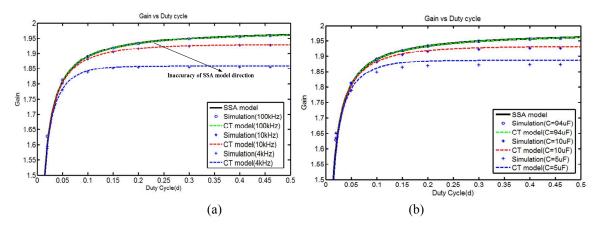

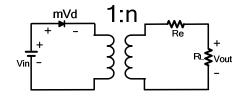

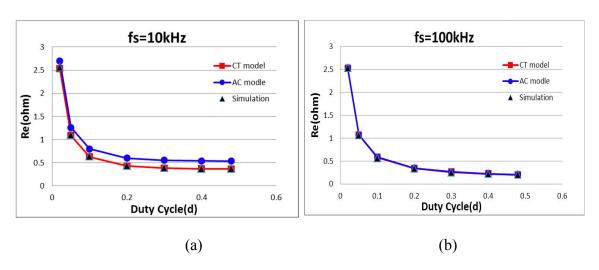

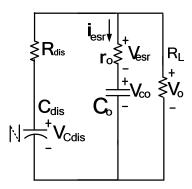

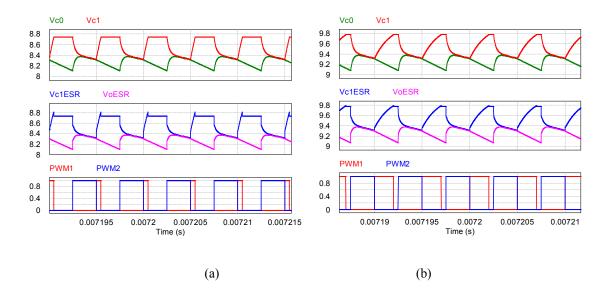

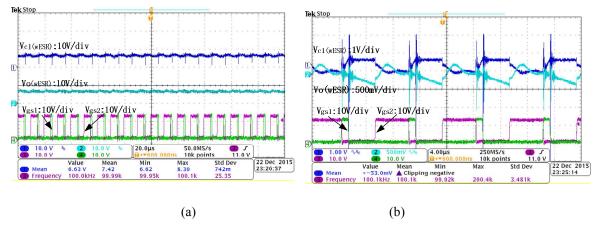

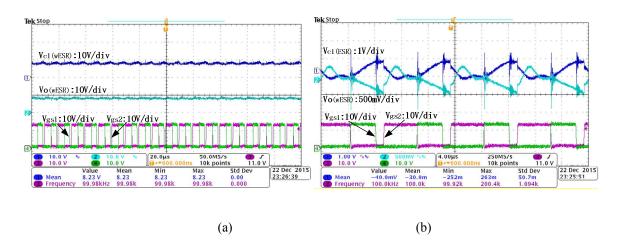

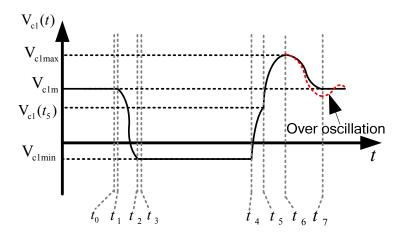

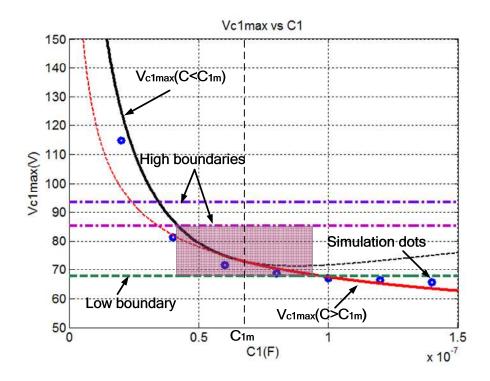

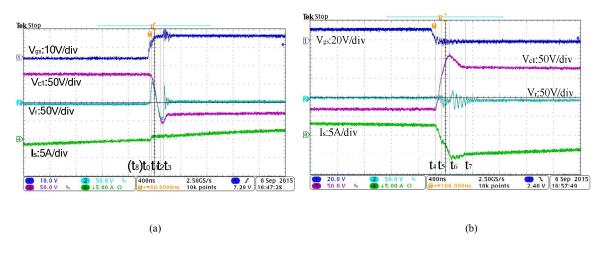

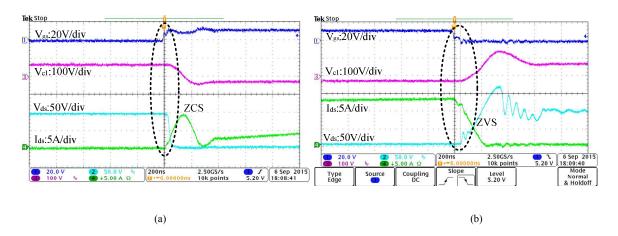

(2.2)