# **UC San Diego**

# **Technical Reports**

### **Title**

Maintaining Safe Memory for Security, Debugging, and Multi-threading

### **Permalink**

https://escholarship.org/uc/item/4269b7n8

### **Author**

Chuang, Weihaw

### **Publication Date**

2006-12-09

Peer reviewed

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

Maintaining Safe Memory for Security, Debugging, and Multi-threading

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

ir

Computer Science (Computer Engineering)

by

Weihaw Chuang

Committee in charge:

Brad Calder, Chair Jeanne Ferrante Ranjit Jhala Andrew Kahng Chandra Krintz

Copyright

Weihaw Chuang, 2006

All rights reserved.

| The dissertation of Weihaw Chuang is approved, and it    |

|----------------------------------------------------------|

| is acceptable in quality and form for publication on mi- |

| crofilm:                                                 |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

|                                                          |

| Chair                                                    |

University of California, San Diego

2006

For my parents, brother, and relatives who made this possible.

# TABLE OF CONTENTS

| Dedication Page  Table of Contents  List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| List of Tables  Acknowledgments  Vita and Publications  Abstract  Introduction  A. The Importance of Software Bugs  B. Sources of Software Failure  C. Silicon Fabrication Trends  D. Goals of Thesis  II Software Check Optimization  A. Motivation for Memory Checks  1. Bounds Security Exploits  2. C and C++ Code Base  B. Implementation of Bounds Check  1. Representing Bounds Information  C. Software Memory Check Related Work  1. Bounds Checking and Their Alternatives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Acknowledgments  Vita and Publications  Abstract  Introduction  A. The Importance of Software Bugs  B. Sources of Software Failure  C. Silicon Fabrication Trends  D. Goals of Thesis  II Software Check Optimization  A. Motivation for Memory Checks  1. Bounds Security Exploits  2. C and C++ Code Base  B. Implementation of Bounds Check  1. Representing Bounds Information  C. Software Memory Check Related Work  1. Bounds Checking and Their Alternatives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Vita and Publications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| I Introduction A. The Importance of Software Bugs B. Sources of Software Failure C. Silicon Fabrication Trends D. Goals of Thesis  II Software Check Optimization A. Motivation for Memory Checks 1. Bounds Security Exploits 2. C and C++ Code Base B. Implementation of Bounds Check 1. Representing Bounds Information C. Software Memory Check Related Work 1. Bounds Checking and Their Alternatives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A. The Importance of Software Bugs B. Sources of Software Failure C. Silicon Fabrication Trends D. Goals of Thesis  II Software Check Optimization A. Motivation for Memory Checks 1. Bounds Security Exploits 2. C and C++ Code Base B. Implementation of Bounds Check 1. Representing Bounds Information C. Software Memory Check Related Work 1. Bounds Checking and Their Alternatives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A. Motivation for Memory Checks  1. Bounds Security Exploits  2. C and C++ Code Base  B. Implementation of Bounds Check  1. Representing Bounds Information  C. Software Memory Check Related Work  1. Bounds Checking and Their Alternatives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2. Compiler Optimization 3. Comparison 4. Hardware Proposals for Security 5. Hardware Support for Debugging D. Performance Analysis of Bounds Checking 1. Performance Profiling 2. Bounds Tools 3. Bounds Code-Generation for Directly-Associated Meta-Data 4. Generating Bounds Information from Type Information and Code Generation  Code Generation  2. Compiler Optimization  3. Comparison  4. Generation  5. Hardware Proposals for Security  5. Hardware Support for Debugging  6. Security  6. Security  7. Security  7. Security  8. Security  9. Security  9 |

|       |            | 5. Performance Analysis                                       |

|-------|------------|---------------------------------------------------------------|

|       | Ε.         | Data Layout                                                   |

|       |            | 1. Methodology                                                |

|       |            | 2. Meta-Data Overhead                                         |

|       |            | 3. Storing Meta-Data for Bounds and Dangling Pointer Checks 4 |

|       |            | 4. Meta-Data Checking Overhead                                |

|       | F.         | Eliminating Unneeded Checks by Taint-Based Analysis 49        |

|       |            | 1. Interface Analysis Example                                 |

|       |            | 2. Interface Analysis Algorithm                               |

|       |            | 3. Aliasing Properties                                        |

|       |            | 4. Memory Writer Algorithm                                    |

|       |            | 5. Implementation Details 5                                   |

|       |            | 6. Network External Interface Results                         |

|       |            | 7. All External Interface Results                             |

|       | G.         | Hardware Acceleration                                         |

|       |            | 1. Motivation for Meta Checker Instruction 62                 |

|       |            | 2. Overview of Meta Data Check Architecture Extensions 63     |

|       |            | 3. Meta-Check Instruction                                     |

|       |            | 4. Using the Meta-Check Instruction 60                        |

|       |            | 5. Hardware support for Meta-Check Instruction 69             |

|       |            | 6. Performance Result                                         |

|       | Η.         | Summary                                                       |

|       | I.         | Acknowledgement                                               |

| T T T | <b>T</b>   |                                                               |

| III   |            | ansactional Memory                                            |

|       | Α.         | Introduction to Transactional Memory                          |

|       |            | 1. Race-Conditions                                            |

|       | ъ          | 2. Lock Synchronization and Transaction                       |

|       | В.         | Transaction Software Model                                    |

|       |            | 1. Transactional Memories Programming Model                   |

|       |            | 2. Details of Transactional Memory Programming Model 90       |

|       |            | 3. Related Model: Thread-Level-Speculation (TLS)              |

|       |            | 4. Transactified Examples                                     |

|       | C          | 5. Programming Models Comparison                              |

|       | <b>C</b> . | Transactional Memory Related Work                             |

|       |            | 1. Early Database Systems                                     |

|       |            | 2. Hardware Transactional Memory (HTM)                        |

|       |            | V ( )                                                         |

|       |            | 7                                                             |

|       |            | 5. VTM                                                        |

|       |            | o. Imcad-bever-opeculation (IDo)                              |

|    | D. Paged Transactional Memory (PTM)          |

|----|----------------------------------------------|

|    | 1. Structures                                |

|    | 2. Implementation                            |

|    | E. Evaluation                                |

|    | 1. Simulation Platform                       |

|    | 2. Characterizing Transactional Applications |

|    | 3. PTM Performance Comparisons               |

|    | F. Conclusion                                |

|    | G. Acknowledgement                           |

| IV | Conclusion and Future Work                   |

|    | A. Future Direction                          |

|    | 1. Software Safety Checks                    |

|    | 2. Transactional Memory                      |

|    | Bibliography                                 |

# LIST OF FIGURES

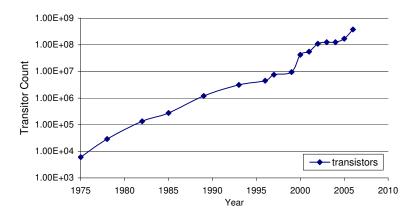

| 1.1   | Moore's Law: doubling of transistor per chip every 18-24 months on Intel Microprocessors |    |

|-------|------------------------------------------------------------------------------------------|----|

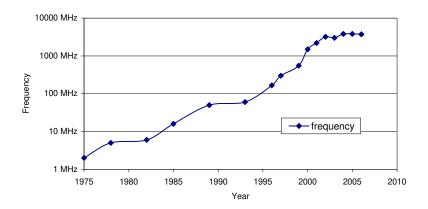

| I.2   | Frequency doubled until 2003 on Intel Microprocessors                                    | 8  |

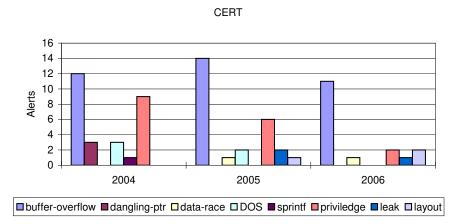

| II.1  | Cert Alerts 2004-2006                                                                    | 15 |

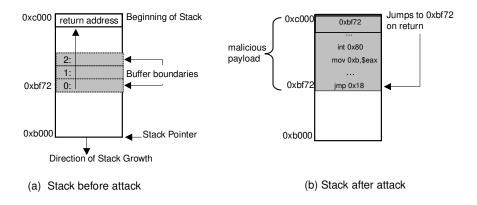

| II.2  | Stack Smashing example                                                                   | 16 |

| II.3  | Psuedo-Code of Bound Check                                                               | 20 |

| II.4  | Bounds Check Meta-Data representation                                                    | 21 |

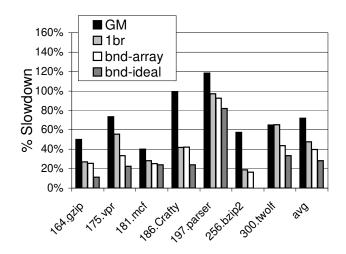

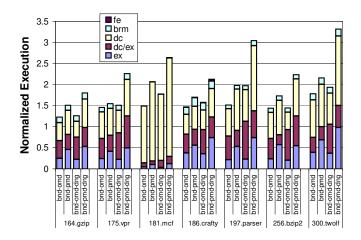

| II.5  | Run-time overhead of bounds checking (AMD Athlon)                                        | 38 |

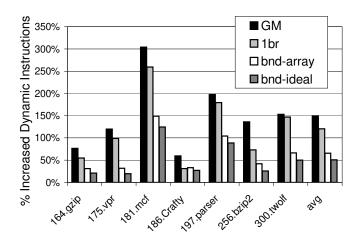

| II.6  | Increased dynamic instructions due to bounds checking                                    | 38 |

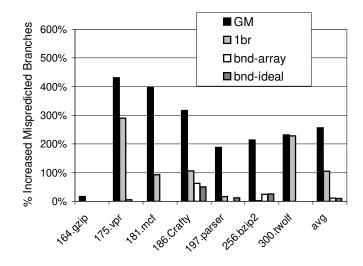

| II.7  | Increased branch misprediction                                                           | 40 |

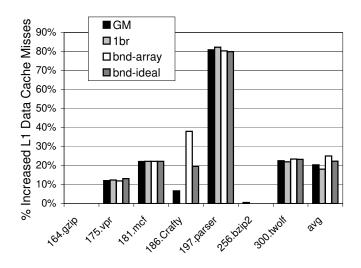

| II.8  | Increased Level One Data cache misses                                                    | 40 |

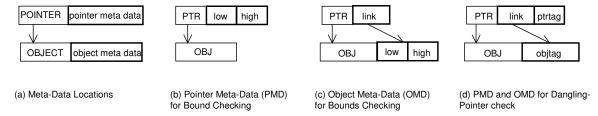

| II.9  | Meta-data Representations                                                                | 41 |

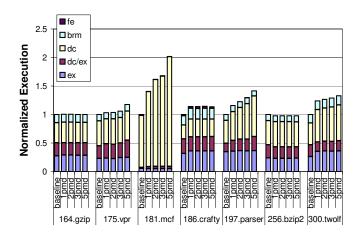

| II.10 | Pointer Meta-Data Overhead                                                               | 45 |

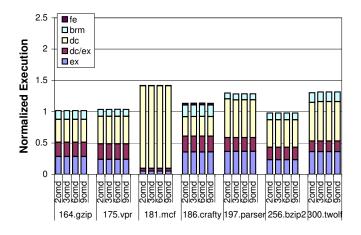

| II.11 | Object Meta-Data Overhead                                                                | 45 |

| II.12 | 2 OMD Software Check Implementations                                                     |    |

| II.13 | Bounds Micro-op Expansion                                                                | 47 |

| II.14 | Bounds and combined Dangling Pointer and Bounds check overhead                           |    |

| II.15 | Tainted Code Example                                                                     | 51 |

| II.16 | Algorithm for interface optimization                                                     | 53 |

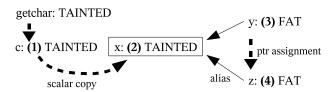

| II.17 | TAINTED flow code for Figure II.18                                                       | 56 |

| II.18 | TAINTED flow via scalar assignment and aliasing                                          | 56 |

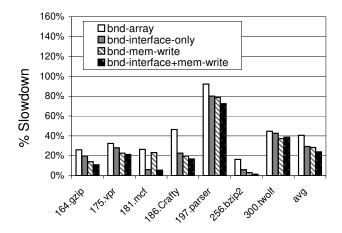

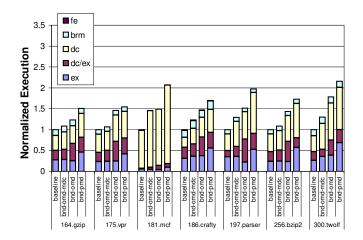

| II.19 | Performance advantage of interface and memory-writer optimizations                       | 61 |

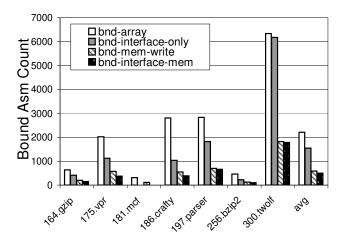

| 11.20 | Reduction in the number of static bound instruction in the binary.                                               | 61  |

|-------|------------------------------------------------------------------------------------------------------------------|-----|

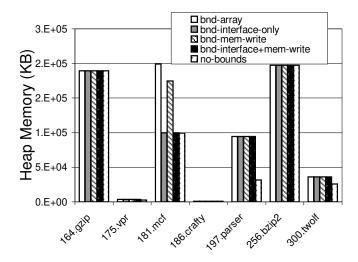

| II.21 | Comparison of heap size overhead in KB                                                                           |     |

| II.22 | Example meta-check instructions for dangling pointer and bounds checking                                         | 67  |

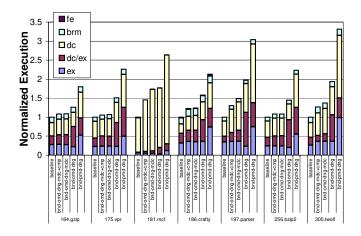

| II.23 | Performance Overhead of Bounds Checking using meta-check instruction and MDC hardware                            | 75  |

| II.24 | Performance Overhead of Dangling-Pointer Checking using meta-check instruction and MDC hardware                  | 76  |

| III.1 | Pseudo-code illustrating Lock Synchronization                                                                    | 88  |

| III.2 | Pseudo-code for overlimit that illustrates deadlock                                                              | 88  |

| III.3 | Pseudo-code of credit card example using transactions synchronization                                            | 104 |

| III.4 | Transactified loop example- Ordered transactions protect against loop carried dependency                         | 105 |

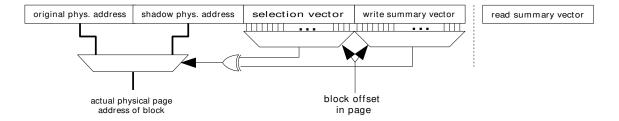

| III.5 | PTM Structures                                                                                                   | 126 |

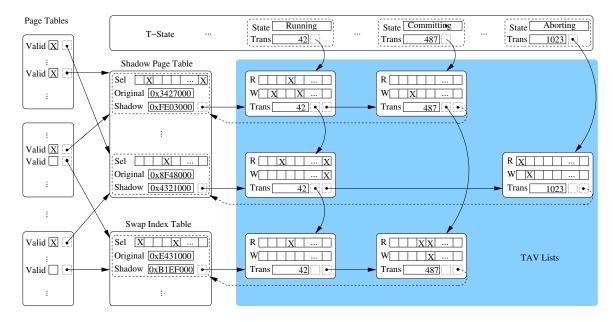

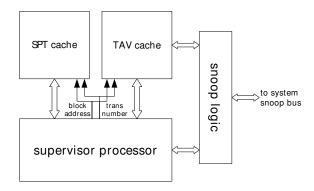

| III.6 | I.6 The Virtual Transaction Supervisor (VTS) has a memory backed cache holding the SPT entries and the TAV nodes |     |

| III.7 | SPT cache entry                                                                                                  | 141 |

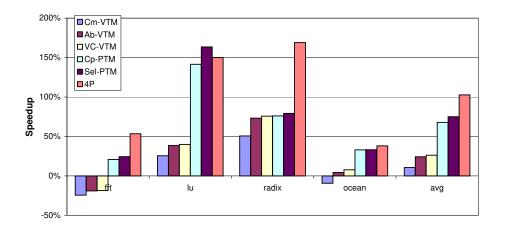

| III.8 | Comparing TM speedup for lock-based multi-threading, (base) VTM, Victim-Cache VTM, Copy-PTM and Select-PTM       | 155 |

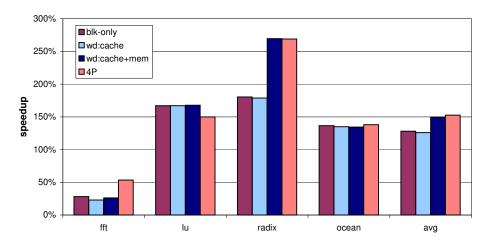

| III.9 | Advantage of conflict detection at the word granularity                                                          | 155 |

# LIST OF TABLES

| 1.1   | Causes of data-corrupting bug in MVS bug reports                                                      | 4   |

|-------|-------------------------------------------------------------------------------------------------------|-----|

| I.2   | Causes of severe non-memory corrupting failure that prevents automatic MVS reboot and system recovery | 5   |

| II.1  | Distribution of open source projects by languages                                                     | 18  |

| II.2  | Comparison of prior techniques                                                                        | 27  |

| II.3  | Coverage for UIUC AccMon benchmarks                                                                   | 34  |

| II.4  | Simulation model based on the AMD Athlon                                                              | 43  |

| II.5  | Meta-Data Check Table (MDCT)                                                                          | 70  |

| II.6  | Meta-Data Register Map (MDRM)                                                                         | 70  |

| III.1 | Comparing Safety and Convenience of Transactional Memory<br>Programming Models                        |     |

| III.2 | Comparing Conflict Detection Actions of Parallel Programming Models Without and With Ordering         | 108 |

| III.3 | TM vs TLS and Locks                                                                                   | 109 |

| III.4 | Transactional memory execution behavior for loop regions in the SPLASH-2 programs                     | 152 |

### ACKNOWLEDGMENTS

I would like to acknowledge Prof. Brad Calder for his support as my advisor for these six years. I would also like extend my deep appreciation to my co-authors and acknowledge their hard work: Satish Narayanasamy, Dr. Osvaldo Colavin, Prof. Jeanne Ferrante, Prof. Ranjit Jhala, Dr. Gilles Pokam, Jack Sampson, Michael Van Biesbrouck, and Ganesh Venkatesh.

Section II.F contains materials to appear in "Bounds Checking with Taint-Based Analysis", in 2007 International Conference on High Performance Embedded Architectures and Compilers (HiPEAC 2007), W. Chuang, S. Narayanasamy, R. Jhala and B Calder. The dissertation author was the primary investigator and author of this paper.

Sections III.D, and III.E contain material to appear in "Unbounded Page-Based Transactional Memory", in *Proceedings of 12th International Conference on Architectural Support for Programming Languages and Operating System (ASPLOS XII)*, W. Chuang, S. Narayanasamy, G. Venkatesh, J. Sampson, M. Van Biesbrouck, G. Pokam, O. Colavin and B. Calder. The dissertation author was the primary investigator and author of this paper.

#### VITA

| nology |

|--------|

| nolo   |

1995–2000 Intel Corporation

2000–2006 Research Assistant, University of California, San Diego

2006 Doctor of Philosophy, University of California, San Diego

#### **PUBLICATIONS**

- W. Chuang, S. Narayanasamy, R. Jhala and B Calder, "Bounds Checking with Taint-Based Analysis", to appear in 2007 International Conference on High Performance Embedded Architectures and Compilers (HiPEAC 2007), Ghent, Belgium, January 2007.

- W. Chuang, S. Narayanasamy, G. Venkatesh, J. Sampson, M.V. Biesbrouck, G. Pokam, O. Colavin and B. Calder. "Unbounded Page-Based Transactional Memory", to appear in *Proceedings of 12th International Conference on Architectural Support for Programming Languages and Operating System (ASPLOS XII)*, October 2006.

- W.K. Chen, S. Bhansali, T.M. Chilimbi, X.G. Gao and W. Chuang, "Profile-guided proactive garbage collection for locality optimization", In *Proceedings of the ACM SIGPLAN 2006 Conference on Programming Language Design and Implementation (PLDI06)*, Ottawa, Ontario, Canada, June 2006.

- W. Chuang, B. Calder, and J. Ferrante, "Phi Predication for Light Weight If-Conversion", In *Proceedings of International Symposium on Code Generation and Optimization (CGO)*, March 2003.

- W. Chuang and B. Calder, "Predicate Predicate Prediction for Efficient Out-of-order Execution", In *Proceedings of the 16th Annual ACM International Conference on Supercomputing (ICS03)*, June 2003.

- L. Carter, W. Chuang and B. Calder, "An EPIC Processor with Pending Functional Units", In *High Performance Computing*, 4th International Symposium (ISHPC 2002), May 2002.

### ABSTRACT OF THE DISSERTATION

Maintaining Safe Memory for Security, Debugging, and Multi-threading

by

#### Weihaw Chuang

Doctor of Philosophy in

Computer Science (Computer Engineering)

University of California, San Diego, 2006

Brad Calder, Chair

As transistor budgets grow enabling chip multi-core processors, adding hardware support to ensure the correctness and security of programs will be just as important, for the average user, as adding another core. The goal of our research is to develop hardware support for software checks and for multi-threaded synchronization that protects memory from corruption. This is the source of a significant number of bugs and security issues. We want efficient low-overhead run-time performance of these checks and synchronization so that it can be left on all of the time, even in production code releases.

Bounds checking protects pointer and array accesses. It is the process of keeping track of the address boundaries for objects, and checking that the loads and stores do not stray outside bounds. It can serve two purposes: it can assist debugging by precisely capturing invalid memory accesses, and it can guarantee protection against buffer overflow attacks. Unfortunately, the high performance overhead of runtime bounds checking has prevented its inclusion in most released software. In this thesis, we analyze the sources of bounds checking overhead.

We then consider hardware/software enhancements: the effect merging the check into a single instruction, software optimizations based on potential for overflow to eliminate checks, and changes to meta-data layout to limit copying overhead.

Transactional Memories enable programmers to greatly simplify multithreaded code by eliminating lock synchronization and its attending deadlock and livelock problems. Unlike locks they also enable speculative concurrent execution through the critical section. Specialized transactional memory can also aid concurrent programming models by providing determinism only when needed at run-time. A key limitation of past transactional memory proposals are that they have a finite memory capacity. Virtualized transactional memory (unbounded in space and time) are desirable, as they can increase the scope of transactions' use, and thereby further simplify a programmer's job. In this thesis, we introduce Page-based Transactional Memory to support unbounded transactions. We combine transaction bookkeeping with the virtual memory system to support fast transaction conflict detection, commit, abort, and to maintain transactions' speculative data.

# Ι

# Introduction

# I.A The Importance of Software Bugs

Software safety is a paramount concern for developers and end users, because billions of dollars are lost, and lives are at risk when software fails. A NIST study estimated that \$59.5 billion (2002) was lost due to software failure in the United States alone (0.6% Gross Domestic Product) [75]. One of the most famous case of software failure was caused by a data race condition in the Therac-25, a radiation medical device, resulting in five deaths [51]. Consequently a great deal of software development effort is spent avoiding software failure. Beizer [8] estimates that between 30% to 90% of software development cost is devoted to testing.

Broken applications do not fully describe the cost of these software failures. Malicious hackers exploit software bugs to steal personal, and financial information from computers, or to perform other nefarious activities. Computer viruses and Internet worms use software bugs to inject malicious code on a host computer to commit Internet crimes like launching denial-of-service attacks, installing back doors [56, 77] or keystroke loggers, or scanning for information like credit cards. Worms and viruses characteristically use that malicious code

to repropagate themselves, frequently overwhelming the ability of host and/or networks to handle normal workloads. Much like the organic viral epidemics, computer worms and viruses propagate at a rapid rate across the Internet reaching all corners of the globe. Just one of these worm attacks, "Code-Red" on 19 July 2001, infected 359,000 computers in fourteen hours that hosted the Microsoft Corporation "Internet Information Service" (IIS) server. The entire "Code-Red" epidemic has been estimated to cost the US \$2.6 billion dollars [89]. Another IIS server worm called the "Witty Worm" in 2004 has the notoriety of being the first worm to intentionally delete data on the host machine [78]. Desktop machines are vulnerable too. A 2004 study found that an unpatched Windows XP SP1 connected to the Internet would be exploited by worms in less than four minutes [6].

Computer software has become more meaningful to the general public because they now touch everyday life by providing instant information from around the world and automating many common tasks like banking, maintaining contact lists and doing taxes. When computers fail, many more people are now affected. In the 1980's and 1990's, there was a large new demographic of non-technical computer users because of the reduction in cost of ownership of personal computers from transistor scaling which is commonly known as Moore's Law. This user base expects appliance like reliability from their computer, yet is unable or unwilling to manually patch their computer software when a bug is found [56], creating new demands on the computer vendors. Inter-networking of computers was also enabled by transistor scaling, allowing the rapid dissemination of knowledge, and unfortunately enabling the spread of worms and viruses as well. Microsoft faced both greater user expectations and new Internet based attacks, with the "Code-Red" worm exploits on their IIS server, and many other worm exploits on different software products. Bill Gates in a 2002 memo [26]

stated that Microsoft software needed to attain the reliability level of utility services such as water or electric, because their customers expected this reliability, especially because of earlier security breaches from worm attacks that shook their customers' trust. That memo launched Microsoft's Trustworthy Computing campaign, instituting more rigorous code development processes, automatic software updates, and other initiatives to root out exploits. This cost the company \$100 million dollars for just 2002-2003 [55]. The Internet played a critical role with the "Code-Red" worm attack: Knowledge enabling the IIS exploit was posted on the World-Wide-Web in 18 June 2001 [56, 77], and shortly by 12 July the first worm appeared. Like all worms it infected its host, then used the Internet as the transmission medium to re-propagate itself to other machines.

### I.B Sources of Software Failure

Identifying the sources of these software failures is important to us as we seek to prevent them. Sullivan and Chillarege [85, 13] analyzed the failures on a rigorously tested and deployed IBM mainframe MVS operating system. Sullivan and Chillarege classified the type of failure, its triggers, and the consequence to the customer. They found that memory overwriting bugs are more likely to cause a high priority bug report to be generated by a ratio of three-to-one than the general population of bug reports, even though memory corruption comprise just 15%-25% of that population. Memory corrupting bugs often allows the program to continue for some time (Byzantine failure) that potentially corrupts data and obscures the bug's identity, instead of stopping immediately at the point of failure. Another class of severe bugs overwrites the MVS recovery mechanism; it is discussed after the memory corruption bugs.

The causes of these memory corruption bugs are listed in Table I.1. Over half of the data-corrupting failures are directly due to memory mismanagement.

Table I.1: Causes of data-corrupting bug in MVS bug reports

| Bug type                  | % of bugs |

|---------------------------|-----------|

| Buffer overflow           | 20%       |

| Use of deallocated memory | 19%       |

| Use of corrupt pointers   | 13%       |

| Unknown                   | 13%       |

| Type mismatch             | 12%       |

| Synchronization           | 8%        |

| Register Reused           | 7%        |

| Uninitialized Ptr         | 5%        |

| Undefined State           | 4%        |

Buffer-overflow accesses data outside its allocated region typically when an array index or pointers, exceeds the bounds. This either returns the incorrect value or corrupts nearby data. The second most prevalent bug is use of deallocated memory, which is also commonly known as the dangling pointers. In this case there exist two or more pointers with different uses of the same memory, caused by one pointer seeing the original use of the memory, and another pointer seeing memory that's been been freed once and been reallocated to it. The third bug occurs when a buffer overflow overwrites a pointer, that causes that pointer to reference the wrong location. The fifth set of bugs is due to memory corruption caused by multi-threaded synchronization problems such as race conditions. Here different ordering of thread execution causes different results in an unexpected way. Other types of concurrency problems can occur without having to corrupt memory as well.

Sullivan and Chillarege also classify the regular population of software failures that includes the memory corruption bugs described above, and all other bugs. The most severe non-memory corrupting errors prevent the MVS operating system from automatically recovering from failure, thus decreasing system availability. This strikes at the primary reason for having the MVS mainframe

Table I.2: Causes of severe non-memory corrupting failure that prevents automatic MVS reboot and system recovery.

| Bug type        | % of bugs |

|-----------------|-----------|

| Deadlock        | 58%       |

| Synchronization | 22%       |

| Undefined State | 4%        |

| Copying Overrun | 4%        |

| Data Error      | 3%        |

| Unknown         | 3%        |

system marketed for high availability. Non-recoverable errors occur at a rate of 6.3% of the regular bug report population. Of these, the two largest causes are from deadlocks(58%) and synchronization (22%) errors, as given in Figure I.2, caused by multi-threaded concurrency bugs. Sullivan and Chillarege summarize that the three main causes of severe failure are memory corruption, concurrency and administrative errors.

The Sullivan and Chillarege's study succinctly provides the central motivation for this thesis. It covers two different areas of software bugs- memory corruption and concurrency bugs- that share the property that they have severe consequences and are difficult to isolate and repair in the field. However, there are techniques to avoid these bugs by systematically checking for failure conditions, though costly in terms of performance. Our approach is to provide hardware techniques that accelerate these checks to avoid the overhead.

### I.C Silicon Fabrication Trends

In this section we look at silicon fabrication trends that enable special purpose hardware for software safety checks and error prevention. These trends also suggest future programming models will need to be multi-threaded cognizant, as multiprocessors become the dominant means of improving performance.

Understanding the future trend of microprocessors comes in part from looking at the recent silicon semiconductor trends, and looking at the likely technology available to designers and manufacturers in that future time frame. Historic transistor scaling has caused the number of transistors per chip to increase at an exponential rate for the past three decades, doubling every 18 to 24 months, which famously is known as "Moore's law". Intel's microprocessors roadmap demonstrates this trend and is provided in Figure I.1. Gordon Moore, with visibility into the technology at Intel, has stated in 2005 that this trend will definitely continue for at least two more process generations but perhaps as long as twenty more years until silicon lithography reach limits when dimensions are the size of individual atoms [22]. While there are many barriers to further progress with transistor scaling, the historic trend is that the technologists have managed to find solutions, allowing Moore's Law to continue. This history is recorded in past International Technology Roadmap for Semiconductors (ITRS) [42] for future design and manufacturing direction. All previous ITRS "red bricks" where no technology is known to solve a particular problem, have been knocked off successfully<sup>1</sup>.

While the number of transistors increases at a rapid rate and will do so into the future, translating that to performance has hit several obstacles. Microprocessor designers have historically found that performance could be derived from microarchitectural improvements and from frequency improvements. But taking Intel's roadmap as example, since 2004 this model has not kept us with the earlier 1.5 to 1.7X performance increase per processor generation. Microarchitectural improvements through instruction level parallel techniques has reached the

$<sup>^1</sup>$ Photolithographic technology limitations is perhaps the most famous of these "red-bricks". One example occurred at the 248nm wavelength of deep ultraviolet that the industry thought would limit feature sizes at around  $0.25\mu$ . Engineers succeeded in using optical correction techniques, and later introduced 193nm wavelength lithographic tools previously thought impractical, to overcome this limitation.

Figure I.1: Moore's Law: doubling of transistor per chip every 18-24 months on Intel Microprocessors

point of diminishing returns [64], due to scaling limitations of hardware structures. Increasing the instruction level parallelism enlarges the size of microprocessor structures increasing the power consumption and propagation delay of wires through them. For example register files, cache ports, and reorder buffers have a quadratic area growth rate of the number inputs with at best linear improvements in performance. There are other areas of microarchitectural improvements that scale better such as L3 caches that reduce overall memory latency, or vector processing units that increase parallelism without needing data bypassing. A second means to improving microarchitectural performance is to scale up the frequency of microprocessors. Historically Intel's microprocessor's clock rate approximately doubled every process generation, matching Moore's law (hence frequency used to be a corollary law). Of this 2X, half the increase comes from transistor scaling of 1.4X per generation, while the other half comes from reducing the logic depth per pipestage at about 1.4X [46]. However frequency speedup has encountered two barriers. First switching power overhead is proportional to frequency, and microprocessor design hit the "power wall" [67] in dramatic fashion in 2004, where an Intel microprocessor successor for the first time did not increase the

Figure I.2: Frequency doubled until 2003 on Intel Microprocessors

frequency over the earlier version. This is seen in Figure I.2. Since then Intel has not increased processor frequency beyond 3.8GHz though some smaller rate of increase is expected in the future. The second barrier is that there is diminishing returns as one partitions logic into more pipestages, due to clock jitter and sequential circuit overhead. Further frequency improvements will likely be limited to transistor scaling effects, leavened by power concerns.

One solution to performance scaling problems is to consider multicores on a single chip, as has been done by Intel and others. Figure I.1 graphs the transistor count of the largest Intel general purpose processor chips of a given year, and year 2006 already has a dual core chip. This Intel Smithfield chip has 376 million transistors using 65nm process node technology. Contrast that chip with its ancestor, the 1997 single core Intel Klamath chip with 7.5 million transistors at  $0.35\mu$ m that already has all of the significant high-performance features like out-of-order execution, two-level branch predictor, multiple execution units, and multiple levels (two) of cache, of its larger relative. Intel expects to release sometime this year, the Montecito server chip with an even larger 1.76 billion transistors. One can see that current chip budgets already support having several high performance general-purpose cores on a single chip, even when using larger

caches. Alternatively one might consider specialized functions such as security and debug because there is such a abundance of transistors now.

Because fine grain parallelism finds diminishing returns while simultaneously there are many chip level procesor cores, using coarse-grain task or thread parallelism becomes preferable. The Chip Multiprocessors (CMP) [64, 46] are loosely coupled using cache coherence to communicate between the cores, where each runs separate threads. Combining the threads to solve a single task requires coordination between the threads that is error-prone as the Sullivan and Chillarege data demonstrates. Also such multi-threaded programs only provide useful speedup if the partitioned work can be done in parallel, that is work independent of one another. If data dependencies, that normally cause ordered execution, is only present part of the time, most parallelization techniques must be conservative and prevent potentially unsafe parallel partitioning. Our work will later demonstrate a solution to both problems.

Duplicating cores is not the only solution. These extra transistors enables specialization of functional units to improve performance in ways that general purpose processors are not able to. This was explored in the context of cryptographic Application-Specific-Processors by Wu et.al. [94] where certain bit manipulations were done much more efficiently in custom hardware, and several specialized processors were run in parallel, to assist a general purpose processor. Because of the overhead of software checks, we seek to create specialized functional units for software security later that reduce the overhead of software checks.

### I.D Goals of Thesis

Software bugs are program behavior that are unexpected from what the software designer intended, which malicious hackers can often exploit on Internet connected computers to remotely execute code or deny services. One common bug often exploited is called a buffer overflow. In this thesis we examine why such a simple bug is so frequently targeted to the detriment of so many systems. We then examine a simple but powerful software technique called bounds checking to defeat it. It comes with performance caveats that are addressed by this work.

Buffer overflow is a kind of memory bug caused by writing or reading beyond the bounds of allocated memory. Reading beyond the bounds may leak information. Writing past the bounds causes memory corruptions that often manifests itself non-deterministically because the bad data may not used hence observed by the program till long past the point of overwrite. Bounds checking forces non-deterministic data corruption to become deterministic, by immediately detecting if the buffer bounds have been exceeded, and before any memory is written. Dangling-pointers is another memory corruption bug, but less frequently seen. It occurs when memory has been freed, but is still used, leading to two different overlaid uses of that memory. When both write that memory, they will corrupt each others memory image. Protecting against both bugs is considered to be sufficient protection against the most important cases of memory corruptions by some [5].

We improve the performance of memory checks that prevent data corruption by software optimization and hardware acceleration:

- Identifying performance overheads of software memory checks through hardware performance counters and simulation. The causes of overhead are extra instruction execution, data-copying overhead, and branch mispredictions.

- Optimizing the organization of data association with the software checks.

We found that associating the meta-data with the object rather than pointer reduces copying costs.

- Eliminate unnecessary checks outside the scope of code needing security

checks for dangerous data. We developed an interprocedural type-based analysis to discover code that touches safe and unsafe data.

Provide a modified Instruction Set Architecture and hardware datapath to efficiently accelerate software checks. This eliminates unnecessary meta-data loads and reducing instruction fetch requirements.

A second trend we examine is multi-threaded programming for Chip Multi-Processors (CMP). Semiconductor scaling provides far in excess of transistors than needed for a single general purpose CPU core, consequently many CPU design companies will provide multiple cores on a chip. These multicores could be used to accelerate single program performance by splitting it apart into multiple threads, and executing the threads concurrently on the CMP cores. This multithreaded program needs to share data across threads, requiring coordination of the data updates to maintain the original single threaded execution behavior. Lack of coordination amongst shared data typically results in non-deterministic execution called a race condition, and is often considered a software bug. We examine a technique called Transactional Memory (TM) that eliminates race conditions yet allows for parallelism.

We propose multi-threaded execution models for multi-core systems that avoid data-races and deadlocks by using Transactional-Memories. Memory maybe speculatively modified in parallel, but data conflicts detected between different threads force serial execution of the threads that avoids. One of the main limitations of prior techniques handling what happens when their speculative state no longer fits in cache due capacity constraints or when the thread must be context switched out.

• Propose a virtualized Hardware Transactional Memory model called Page-Transactional-Memory (PTM) that enables execution on general purpose computers, that is cached, multi-user systems. This backs the transactional state in virtual memory using additional hardware assistance, allowing that state to overflow the cache, context-switched out or saved to disk. PTM features faster aborts and commits than all prior virtualized transaction work, by eliminating the need to copy data.

• Provide the first performance results for an important prior Transactional Memory technique called VTM

# $\mathbf{II}$

# Software Check Optimization

### II.A Motivation for Memory Checks

Buffer overflow attacks are still the most common internet exploit, and if current trends hold without intervention, it will remain so into the future. The common form of buffer overflow attack takes advantage of program bugs that allow writes of malicious data past the allocated memory boundary, such that the adversary can execute code of their choosing. Figure II.1 reports the number of CERT Security Alerts caused by different software bugs for 2004, 2005 and 2006. CERT Alerts are significant because they represent a security danger to the national computer infrastructure due to an exploit (e.g. worm, virus) or the potential for one. There are many categories: Buffer-overflow accounts for the majority at 55%, 50% and 73% for those respective years. The following two paragraphs describe the other bugs denoted by *italics*. Virtually all of these buffer overflow alert carry the warning that they allow remote code execution. Earlier CERT Security Advisory statistics before 2004 are found in [88], and have the same proportions of buffer overflow exploits to total, with variation year-toyear. Despite increased industry vigilance due to worm outbreaks in 2001, buffer overflow attacks still remain the most dangerous and common exploit.

Two other types of bugs found in the 2004-2006 CERT Alerts are important for this thesis; the rest we contrast to justify their exclusion. First dangling-pointers have three CERT Alerts reports in 2004. These are caused by bugs where memory is freed by one pointer, and still used by another pointer causing memory corruption. Second there are data-race alerts reported one each in 2005 and 2006, caused by unsynchronized memory update in multi-threaded execution. Both have the potential for memory corruption which allows execution of remote code.

The rest of the bugs are beyond the scope of this thesis for a number of provided reasons. The second largest category of CERT Alert exploits is privilege escalation (23.9%) caused by the improper use of commands, such as active X controls, or Internet URL exploit. In some cases this enables the remote execution of code, e.g. running a script by an external agent. Automated securing of these bugs is difficult because of the variety of controls to consider, and because of the likelihood of stopping a task that the programmer intended. One subcategory distinguished separately is privilege escalation to leak private information like passwords to the adversary. Format string exploit on buggy sprintf functions differs from privilege escalation in that it corrupts memory, to allow remote code execution. Fortunately sprintf is only one alert of sixty-eight total in 2004-2006; the lack of exploits in 2005 and 2006 may potentially be due to bug fixes. Denial-Of-Service was the third most common attack (7.0%), but arguably less severe than remote code execution. Memory layout errors cause memory corruption, that potentially may execute remote code. The two examples are caused by incorrect layout of arguments to RPC function calls, or reading of raw binary file data. These occur at such a low level of the operating system, it makes it difficult to include in the scope of this thesis's investigation.

Figure II.1: Cert Alerts 2004-2006

### II.A.1 Bounds Security Exploits

Buffer overflow may intentionally alter instruction control allowing the remote execution of code on a computer. We first describe the most basic form of buffer overflow on stack arrays called "Stack Smashing", as popularized by AlephOne [1]. Consider a fixed size buffer allocated on a stack. A buffer overflow can occur when the application copies external data into the buffer but does not check for the size of the input data, especially while copying strings (e.g. using strcpy). In the string case, the end of a string is determined by checking for the null character which maybe intentionally missing. An adversary can exploit buffer overflows by copying executable code or malicious data into the memory buffer. When writing to the stack array, the adversary can overwrite the return address with his own value targeting malicious code as illustrated in Figure II.2, and the control will jump to execute the malicious code upon return from the function. Stack smashing has been used in CodeRed, Nimda, and Slammer just to name a few Internet worms.

Buffer overflow remains by far the most prevalent and consequently dangerous of CERT Alert bug. One reason is that it maybe exploited in so many

Figure II.2: Stack Smashing example

different ways. Once a defense technique is raised against an exploit, another variant appears circumventing the defense. A phalanx of defenses such as sentinels [20], reordering of stack variables [24], better code reviews, and varying the base of the stack, has blunted "stack smashing" exploits. However in the continuing arms-race this lead to heap exploits involving manipulating malloc/free data structures in Lea's Unix heap memory allocator [45] and similar data structures in Windows XP heap allocator [4]. As heap attacks do not touch the stack, stack protection schemes do nothing for this exploit. A heap attack manipulates free list pointers to allow the adversary to overwrite arbitrary memory locations, and has been used on Sudo, Secure Locate, Traceroute, and Netscape browser. This capability allows heap attacks to change function pointers, to point to malicious code, that will then get executed when the function pointer is invoked. Because heap exploits are flexible there are many variations. One example is the Global Offset Table (GOT) used for locating the run-time relocation data, including function pointers in dynamic link libraries. GOT is just an array of pointers, initialized by the dynamic linker. An adversary can corrupt a libc function pointer in GOT, then when the corresponding function is called, it can result in execution of malicious code written by the adversary. Another example are C++

virtual methods that are invoked through function pointers.

The above description of buffer overflow exploits might imply that they only perform malicious code execution, however data manipulation by buffer overflow is another dangerous capability. The adversary can modify the input strings to system calls such as "system" or "popen", by overflowing the buffer location adjacent to the input strings. These input strings determine the Unix command to be executed and hence the adversary gets to execute a command of his choice. Buffer-overflow attacks can also be used for denial-of-service by simply corrupting data in a program that causes the program to crash such as overwriting pointers with null values.

### II.A.2 C and C++ Code Base

Much of the recent buffer overflow exploits occur in programs written in C and C++ due to those languages unsafe features. Though there exist safe languages protected by built-in run-time bounds checking and by full type-safety such as Java and C#, the C and C++ languages have a large and important installation base. For example, the Redhat 7.1 Linux distribution is composed of the following source languages: C is 71% and C++ is 15% [90]. Virtually all important operating system kernels such as Linux, BSD, other flavors of Unix, and Windows are written in C or C++, as are many potentially vulnerable device drivers. Even components of the Java and .Net virtual machine are written in unsafe languages (C and C++). C and C++ have the largest installed base of code as measured by open source projects. A snapshot of the FreshMeat Open Source database on 12 January 2005 in Table II.1 lists the prevalence of the top 5 languages having a total of 85.6% of projects. Combined C and C++ have 51.4% while Java has 18.1%.

Table II.1: Distribution of open source projects by languages

| language | % of projects |

|----------|---------------|

| С        | 34.3%         |

| Java     | 18.1%         |

| C++      | 17.1%         |

| Perl     | 16.1%         |

| Python   | 8.6%          |

| Rest     | 14.4%         |

| C,C++    | 51.4%         |

### II.B Implementation of Bounds Check

Bounds checking is performed when a pointer is dereferenced to access an object or buffer to ensure that the access is to the intended object. Array access is treated similarly as it can be decomposed to pointer dereference and check on the effective address generated by the addition of the index and array base. Bounds check is done by keeping track of low and high bounds information of the objects and comparing them against the effective address used while dereferencing a pointer as seen in Figure II.3(a). It is called two-branch because an inlined implementation will have two branches assembly instructions. The base of the allocated memory region for the object defines the low bounds. The maximum extent of the region, that is the base plus size of the object, defines the high bounds. Bounds checking defeats buffer overflow attacks at the point it attempts to exceed the object's bounds, by raising an exception or jumping to a handler, thus preventing any out-of-bounds data from being read or written. For the code sequences used to do bounds checking shown in Figure II.3(a), we assume that low, and high meta-data are given by some mechanism discussed later in section II.E.

A second form of bounds check uses the low bound and size of the

object, that combines the low and high bound comparisons as illustrated by Figure II.3(b). For the high bounds check, the comparison is straightforward where the offset of the pointer from the low bounds is compared against the size of the object. Exceeding size results in raising error handling. For the low bound check, it uses wrap-around property of unsigned subtract on negative numbers (low out-of-bounds) to become a large positive number - typically larger than size. It is possible for an extremely distant pointer and large object that wrap around to appear in-bound, though this is exceedingly unlikely. We provide this more efficient *single-branch* bounds check for comparison. Figure II.3(b) assumes the availability of *low*, and *size* meta-data.

A third software bounds check is to call a dedicated bounds instruction that exists in the x86 instruction set. bounds instruction is functionally identical to case II.3(a) but clearly has fewer instruction. We compare different bounds checks implementations in greater detail in section II.D. The bound instruction has only two operands as shown in Figure II.3(c). The first input (ptr) specifies a general purpose register containing the effective address that needs to be bounds checked, and the second input (b\_ptr) is a memory operand that references a memory location containing the low and high bounds. On execution, the bound instruction verifies if the first-operand's address is between the low and high bounds. If the bounds are exceeded, it issues a bounds-checking exception. The in-memory bounds information constrains the check code-generation because it is not possible to encode constant bounds in the compare instructions as with Figure II.3(a) and (b) sequences. The code generator uses meta-data given with the pointer and creates additional in-memory meta-data for arrays. The organization of this meta-data is discussed further in section II.E.

We consider the check code sequence to help us understand some of the performance overheads seen with bounds checking. Initially we are interested

Figure II.3: Psuedo-Code of Bound Check and minimum number of assembly instructions. (a) Two Branch - 4 inst (b) Single Branch - 3 inst (c) Bounds - 1 inst

in how many instructions are present in a check as excess dynamic instructions reduce performance, and the number of branches due to the cost of branch mispredictions. Just for this approximate comparison we assume meta-data is directly loaded from memory allowing the CISC architecture to fold meta-data loads into another instruction, or converts them into a move instruction. Also a single if statement is converted to at least two instructions - compare and conditional jump, with potentially one or more move instruction(s) needed to marshal values to registers. Using these simple rules we find that the minimal number of executed x86 assembly instructions are four for two-branch (a), three for single-branch (b) and one for bound op (c) discussed next. As their descriptions imply, the branch counts are two (a), one (b), and zero (c).

### II.B.1 Representing Bounds Information

A bounds checker needs bounds information to perform its verification. We will now describe how the bounds meta-data information is organized and recovered when a pointer is dereferenced.

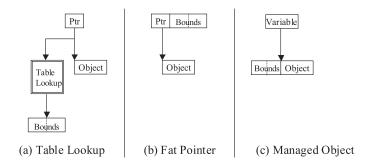

We categorize the bounds checking techniques on how it manages the bounds information. There are three approaches to associating the bounds meta-

Figure II.4: Bounds Check Meta-Data representation

data to the object as shown in Figure II.4 - (a) meta-data table, (b) fat-pointer, and (c) adjacent to the object (referenced by pointer).

#### • Table Lookup

The first approach maintains bounds meta-data separate from the pointer in a table. This makes it unnecessary to change the memory layout of the pointer, reducing the effort to port non-bounds checked applications. To lookup the bounds meta-data for a bounds verfication, it does a lookup on the bounds meta-data table with the pointer address as the index. The C language complicates table lookup by allowing interior pointers that change the addresses passed, though the same meta-data should be returned. Consequently the table is not organized as a fast hash lookup that requires exact match, but instead uses tree search with additional runtime cost that allow ranges of addresses to return the same meta-data. Table lookup is illustrated in Figure II.4(a).

Jones and Kelly [44], and the derivative CRED by Ruwase and Lam [76] uses Table Lookup. CRED fixes the problem of out-of-bounds pointers found in the earlier Jones and Kelly. By definition out-of-bound pointers violate bounds and are forbidden by language specification, but in practice are often found in code and ignored so long as they are not referenced. Both table-

lookup implementations report much higher run-time overhead than fatpointer based bounds checkers (10X or greater).

## • Fat Pointer

Fat pointer modify the representation of a pointer to include the low and high bounds [25, 60] meta-data. Figure II.4(b) shows that the bounds are stored with the pointer in memory adjacent to the pointer value. Because of the direct association, this *fat pointer* format can directly handle interior pointers without any special consideration, and because no table lookups are necessary, it is fast. As a consequence this thesis uses *direct-assocation*. Austin et.al. [5] proposed a variation of the fat pointer *directly assocating* the base and size representation to the pointer, to be used with single branch bounds check as described by Figure II.3(b).

## • Managed Object

Managed languages such as C# and Java name their objects without exposing the pointer to the programmer, making arbitrary pointers addressing impossible. Because the pointer always references the base of the object, bounds information can be fixed at a given distance to the object, that is known at compile time. Consequently lookup is fast. *Managed object* metadata supports other features like managed memory e.g. garbage collection, dynamic typing, etc. This model is illustrated in Figure II.4(c).

For the rest of the thesis we consider only directly associated meta-data. This is due to the performance overhead of table lookup, and the frequency of interior pointers with C/C++ that prevent the use of managed objects.

## II.C Software Memory Check Related Work

This section reports related work for software memory checks: We describe alternatives to fat-pointer bounds checking or other software checks to prevent memory corruption. We describe several software optimization techniques to minimize the number of checks. Because implementations exist for software checks, we can compare their run-time performance to our software optimization techniques to contrast the differences of these approaches. Third we report related hardware enhancements to reduce the performance overhead for memory checks.

## II.C.1 Bounds Checking and Their Alternatives

## **Bounds Checking**

As mentioned in subsection II.B there are two main styles for C/C++ bounds checking based on how they associate meta-data, which is through table lookup and directly associated meta-data in fat-pointers. Bounds checking techniques are represented by CRED [76] for table lookup, and McGary [25] for direct-association of the meta-data. CRED is an improvement of the earlier Jones and Kelly table lookup bounds checker [44]. CRED also reduces the numbers of bounds checks through an optimization limitting checks string object references. Both table lookup mechanisms have large run-time overheads. Using our set of benchmarks we measured an overhead of 1370% for base CRED (Jones and Kelly is similar). We then measured CRED, where their string optimization reduces the overhead to 120%. Recently CRED was improved by using BDD pointer analysis to filter out non-string types in their string-only optimization [7], reducing runtime overhead to around 100%. CRED was also used to tolerate bound check failures by safing the violation continuing, rather than raise an exception [74].

In this model, out-of-bound read returns back a nonsense value to prevent information leakage, while out-of-bound writes do not update memory to prevent memory corruption.

McGary [25] and Cyclone [43] perform bounds checking with fat-pointers meta-data. While McGary's inlines checks and bounds updates, all other bounds checkers we have examined invoke procedure calls to perform these tasks which explains in part McGary's much reduced overhead relative to them. Our measurements of McGary's reports an overhead of 72%, and in this thesis we present optimizations to reduce this overhead even further. Austin et al. [5] does bounds checking and dangling pointer checks using some additional meta-data state for a complete pointer verification.

## **Protecting Code Pointers**

An alternative to bounds checking are pointer protection techniques represented by ProPolice [24] and PointGuard [19], that provide some of the lowest overhead of software techniques. We measured 1% performance overhead with ProPolice on our benchmarks, by using a "canary" - a small piece of data placed on the stack between buffers and the return address to check for buffer overflow. Upon exiting a function, the canary is checked, and if overwritten by some overflow attack, the thread is terminated and the incident is reported. ProPolice also provides variable reordering to further protect stack data. ProPolice is a refinement of the earlier StackGuard [20], and both protect stacked memory but not other memory such as heap. An improvement is PointGuard [19] that encrypts all pointers with an XOR function providing better coverage than ProPolice. In PointGuard, an overflow attack overwrites the encrypted pointers, which decrypt to most likely meaningless values. While much stronger, PointGuard does not prevent attacks that overwrite data not containing pointers, and PointGuard is