### UC Davis UC Davis Electronic Theses and Dissertations

#### Title

Applied Machine Learning for Analyzing and Defending against Side Channel Threats

**Permalink** https://escholarship.org/uc/item/43v6p8c5

**Author** Wang, Han

Publication Date 2022

Peer reviewed|Thesis/dissertation

# Applied Machine Learning for Analyzing and Defending against Side Channel Threats

By

#### HAN WANG DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

$\mathrm{in}$

Electrical and Computer Engineering

in the

#### OFFICE OF GRADUATE STUDIES

of the

#### UNIVERSITY OF CALIFORNIA

DAVIS

Approved:

Houman Homayoun, Chair

Seterah Rafatirad

Chen-Nee Chuah

$\begin{array}{c} \text{Committee in charge} \\ 2022 \end{array}$

© Copyright by Han Wang 2022 All Rights Reserved

#### Abstract

The sharing of hardware components in modern processors helps to achieve high performance and meet the increasing computation demand. Though isolation has been done among users and applications at operating system level, recent research shows that attacks can leverage sophisticated approaches to observe the behaviors of the shared hardware components and infer secrets including password, secret key, etc. Such observations and corresponding attacks are called as side channels and side-channel attacks (SCAs). A number of SCAs have been discovered including Flush+Reload, Flush+Flush, Prime+Probe, Spectre, Meltdown, Fallout, RIDL, ZombieLoad. SCAs have threatened the security of billions of hardware devices, including chips manufactured by Intel, Apple, ARM, etc. Therefore, it is urgent to address the security threats caused by SCAs.

This dissertation pursues the use of machine learning to design effective defense mechanisms and obtain a comprehensive understanding of the side channel threats for emerging applications. In particular, we propose to tackle from three aspects: detection, mitigation and vulnerability analysis.

For detection part, we leverage the microarchitecture level information, i.e. hardware performance counters, to build machine learning-based SCAs detectors. Eventually, we propose two customized machine learning classification models to capture SCAs at real-time and detect zero-day SCAs respectively. As the increase edge devices deployed in the network, we also investigate the machine learning-based detectors against malware and SCAs on autonomous vehicles, mobiles and laptops respectively. We find that hardware performance counters can effectively capture the SCAs with machine learning techniques.

A second aspect of the dissertation is exploring the existing system level and hardware level settings for designing light-weight SCAs mitigation approaches. We find that randomizing the frequency and prefetchers can obfuscate side channel traces and protect against secret leakage. Based on the effectiveness of machine learning-based SCAs detection and randomization-based mitigation, we further developed a detection-mitigation defense approach to further minimize performance overhead incurred by adjusting hardware and system level parameters.

In the last part of this dissertation, we evaluated the side channel leakage in more general applications which are mostly neglected in the prior side channel research community. We find that hardware performance counters can also be used by attackers to fingerprint websites users visited. Besides, we also discover that the inputs' labels of deep learning models are susceptible to be leaked via side-channel attack, i.e. Flush+Reload. To the best of our knowledge, we are the first group to identify the correlation between label information and side channel observations, highlighting the importance of reexamining the side channel vulnerability in general applications.

#### Acknowledgments

After completing my bachelor's degree, I went for a job directly and gradually realized I wanted to explore topics in-depth. Luckily, I got accepted into the graduate school and worked with my Ph.D. advisor, Dr. Houman Homayoun. When I look back on the decision, I think this might be one of the most intelligent decisions I have ever made. In the past three years at Davis, I had the opportunities to work on research topics I am passionate about and received numerous support from mentors, collaborators, and excellent peers. Without them, I will definitely not be able to complete the research work and gain the fruitful research training I had. I want to thank them individually for supporting and helping me.

First of all, I would like to thank my Ph.D. advisor, Dr. Houman Homayoun. Since I had no prior research experience when I started my Ph.D., he offered me enormous guidance to help me adapt to the change from industry to academia. Besides, his passion and vision for research always motivated me to focus on research problems and made the journal enjoyable. I am also grateful that Dr.Houman Homayoun supports my professional choice and provides me with extensive help. I would achieve none of my work without his support and mentorship.

I am thankful to other faculty members I collaborated during my Ph.D., including but not limited to Dr. Chen-Nee Chuah, Dr. Zubair Shafiq, Dr. Avesata Sasan, Dr. Khaled Khasawneh, and Dr. Sai Manoj P D. They provided valuable feedback, feedback, and inspiration over the years that I studied at University of California Davis and George Mason University. I am also thankful to the dissertation committee members: Dr. Setereh Rafatirad and Dr. Chen-Nee Chuah, for providing helpful comments and invaluable feedback about this dissertation.

I also want my peers from ASEEC Lab, including Hossein Sayadi, Hosein Mohammadi Makrani, Chongzhou Fang, Gaurav Kolhe, Ning Miao, Tyler Sheaves, Ryan Tsang, Asmita Asmita, Katayoun Neshatpour, and Maria Malik. They definitely enriched my Ph.D. journey, and I am fortunate to work with them.

Lastly, I would like to express my gratitude for the support and encouragement from my parents and older sister. I could imagine how hard it is for them not to be able to see me in person for years. Their tremendous understanding is always one of my strongest motivations.

# Contents

| $\mathbf{A}$  | Abstract ii               |                                                                                                                                                                                                                                                                                                             |                                                                        |  |  |  |

|---------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|

| A             | ckno                      | wledgments                                                                                                                                                                                                                                                                                                  | $\mathbf{iv}$                                                          |  |  |  |

| $\mathbf{Li}$ | st of                     | Figures                                                                                                                                                                                                                                                                                                     | vii                                                                    |  |  |  |

| $\mathbf{Li}$ | st of                     | Tables                                                                                                                                                                                                                                                                                                      | $\mathbf{i}\mathbf{x}$                                                 |  |  |  |

| 1             | <b>Intr</b><br>1.1<br>1.2 | coduction         Motivation         Overview of the Dissertation                                                                                                                                                                                                                                           | <b>1</b><br>2<br>5                                                     |  |  |  |

|               | 1.3                       | Organization                                                                                                                                                                                                                                                                                                | 10                                                                     |  |  |  |

| 2             | Bac<br>2.1<br>2.2<br>2.3  | <b>Ekground</b> Hardware-assisted Side-Channel Attacks Detection         Side Channel Mitigation         Side-Channel Vulnerability Assessment         2.3.1         Website Fingerprinting         2.3.2         Deep Learning Leakage                                                                     | <b>12</b><br>12<br>14<br>16<br>16<br>17                                |  |  |  |

| 3             |                           | Machine Learning-based Side-Channel Attacks Detection via Hardware Perfor-                                                                                                                                                                                                                                  |                                                                        |  |  |  |

|               | man<br>3.1                | nce Counters         Detecting side-channel attacks at real-time using low-level hardware features         3.1.1       Background and Motivation         3.1.2       Proposed Methodology         3.1.3       Results Evaluation                                                                            | <ol> <li>18</li> <li>19</li> <li>21</li> <li>27</li> <li>32</li> </ol> |  |  |  |

|               | 3.2<br>3.3                | Hybrid Dynamic Time Warping and Gaussian Distribution Model for Detecting         Emerging Zero-Day Microarchitectural Side-Channel Attacks         3.2.1 Hardware Performance Counters (HPCs) Data         3.2.2 Proposed Methodology         3.2.3 Experimental Results and Evaluation         Conclusion | 34<br>35<br>36<br>42<br>47                                             |  |  |  |

|               |                           |                                                                                                                                                                                                                                                                                                             |                                                                        |  |  |  |

| 4             | <b>Ha</b> r<br>4.1        | cdware-assisted On-device Detection on Emerging Edge devices         Evaluation of Machine Learning-based Detection against Side-Channel Attacks on         Autonomous Vehicle         4.1.1       Machine Learning based Detector         4.1.2       Building ML-based Detector                           | <b>49</b><br>49<br>51<br>52                                            |  |  |  |

|               |                                                      | 4.1.3 Results Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54                                                                                           |  |  |  |

|---------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|

|               | 4.2                                                  | Proposed Micro AI-based Countermeasure against Malware and Side-Channel Attacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56                                                                                           |  |  |  |

|               |                                                      | 4.2.1 Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 61                                                                                           |  |  |  |

|               |                                                      | 4.2.2 Proposed Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64                                                                                           |  |  |  |

|               |                                                      | 4.2.3 Experimental Results and Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 69                                                                                           |  |  |  |

|               | 4.3                                                  | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 76                                                                                           |  |  |  |

| <b>5</b>      | Side                                                 | e-Channels Mitigation via Randomization and Obfuscation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 78                                                                                           |  |  |  |

|               | 5.1                                                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 79                                                                                           |  |  |  |

|               |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 79                                                                                           |  |  |  |

|               |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 79                                                                                           |  |  |  |

|               |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 81                                                                                           |  |  |  |

|               |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 82                                                                                           |  |  |  |

|               | 5.2                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |  |  |  |

|               |                                                      | U U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 84                                                                                           |  |  |  |

|               |                                                      | 1 02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 86                                                                                           |  |  |  |

|               | -                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 90                                                                                           |  |  |  |

|               | 5.3                                                  | Accurate and Efficient Cross-Layer Countermeasure for Run-Time Detection and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.0                                                                                          |  |  |  |

|               |                                                      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 96                                                                                           |  |  |  |

|               |                                                      | 1 07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 97                                                                                           |  |  |  |

|               |                                                      | 5.3.2 Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .00                                                                                          |  |  |  |

|               | 5 4                                                  | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |  |  |  |

|               | 5.4                                                  | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |  |  |  |

| 6             | Ma                                                   | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .04                                                                                          |  |  |  |

| 6             | Mae<br>App                                           | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |  |  |  |

| 6             | Ma                                                   | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .04<br>06                                                                                    |  |  |  |

| 6             | Mae<br>App                                           | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .04<br>06                                                                                    |  |  |  |

| 6             | Mae<br>App                                           | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .04<br>06<br>.07                                                                             |  |  |  |

| 6             | Mae<br>App                                           | Conclusion       1         chine Learning-based Side Channel Vulnerability Analysis for Emerging plications       1         Accurate and Efficient Machine Learning-Based Website Fingerprinting Attack through Hardware Performance Counters       1         6.1.1       Background       1         6.1.2       Leaked-Web Attack Implementation       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .04<br>.06<br>.07<br>.11<br>.15                                                              |  |  |  |

| 6             | <b>Mae</b><br><b>Ap</b><br>6.1                       | Conclusion       1         chine Learning-based Side Channel Vulnerability Analysis for Emerging plications       1         Accurate and Efficient Machine Learning-Based Website Fingerprinting Attack through Hardware Performance Counters       1         6.1.1       Background       1         6.1.2       Leaked-Web Attack Implementation       1         6.1.3       Experimental Results and Analysis       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .04<br>.07<br>.11<br>.15<br>.19                                                              |  |  |  |

| 6             | Mae<br>App                                           | Conclusion       1         chine Learning-based Side Channel Vulnerability Analysis for Emerging plications       1         Accurate and Efficient Machine Learning-Based Website Fingerprinting Attack through Hardware Performance Counters       1         6.1.1       Background       1         6.1.2       Leaked-Web Attack Implementation       1         6.1.3       Experimental Results and Analysis       1         Stealthy Inference Attack on DNN via Cache-based Side-Channel Attacks       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .04<br>06<br>.07<br>.11<br>.15<br>.19<br>.23                                                 |  |  |  |

| 6             | <b>Mae</b><br><b>Ap</b><br>6.1                       | Conclusion       1         chine Learning-based Side Channel Vulnerability Analysis for Emerging plications       1         Accurate and Efficient Machine Learning-Based Website Fingerprinting Attack through Hardware Performance Counters       1         6.1.1       Background       1         6.1.2       Leaked-Web Attack Implementation       1         6.1.3       Experimental Results and Analysis       1         Stealthy Inference Attack on DNN via Cache-based Side-Channel Attacks       1         6.2.1       Introduction       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .04<br>06<br>.07<br>.11<br>.15<br>.19<br>.23<br>.24                                          |  |  |  |

| 6             | <b>Mae</b><br><b>Ap</b><br>6.1                       | Conclusion       1         chine Learning-based Side Channel Vulnerability Analysis for Emerging plications       1         Accurate and Efficient Machine Learning-Based Website Fingerprinting Attack       1         through Hardware Performance Counters       1         6.1.1       Background       1         6.1.2       Leaked-Web Attack Implementation       1         6.1.3       Experimental Results and Analysis       1         Stealthy Inference Attack on DNN via Cache-based Side-Channel Attacks       1         6.2.1       Introduction       1         6.2.2       Background and Motivation       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .04<br>06<br>.07<br>.11<br>.15<br>.19<br>.23<br>.24<br>.26                                   |  |  |  |

| 6             | <b>Mae</b><br><b>Ap</b><br>6.1                       | Conclusion       1         chine Learning-based Side Channel Vulnerability Analysis for Emerging plications       1         Accurate and Efficient Machine Learning-Based Website Fingerprinting Attack through Hardware Performance Counters       1         6.1.1       Background       1         6.1.2       Leaked-Web Attack Implementation       1         6.1.3       Experimental Results and Analysis       1         Stealthy Inference Attack on DNN via Cache-based Side-Channel Attacks       1         6.2.2       Background and Motivation       1         6.2.3       Overview of Attack       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .04<br>06<br>.07<br>.11<br>.15<br>.19<br>.23<br>.24<br>.26<br>.29                            |  |  |  |

| 6             | <b>Mae</b><br><b>Ap</b><br>6.1                       | Conclusion       1         chine Learning-based Side Channel Vulnerability Analysis for Emerging plications       1         Accurate and Efficient Machine Learning-Based Website Fingerprinting Attack       1         through Hardware Performance Counters       1         6.1.1       Background       1         6.1.2       Leaked-Web Attack Implementation       1         6.1.3       Experimental Results and Analysis       1         Stealthy Inference Attack on DNN via Cache-based Side-Channel Attacks       1         6.2.1       Introduction       1         6.2.2       Background and Motivation       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .04<br>06<br>.07<br>.11<br>.15<br>.19<br>.23<br>.24<br>.26<br>.29<br>.32                     |  |  |  |

|               | Mac<br>App<br>6.1<br>6.2<br>6.3                      | Conclusion       1         chine Learning-based Side Channel Vulnerability Analysis for Emerging plications       1         Accurate and Efficient Machine Learning-Based Website Fingerprinting Attack through Hardware Performance Counters       1         6.1.1       Background       1         6.1.2       Leaked-Web Attack Implementation       1         6.1.3       Experimental Results and Analysis       1         Stealthy Inference Attack on DNN via Cache-based Side-Channel Attacks       1         6.2.1       Introduction       1         6.2.3       Overview of Attack       1         6.2.4       Evaluation       1         6.2.4       Evaluation       1         6.2.4       Evaluation       1         6.2.4       Evaluation       1                                                                                                                                                                                                                                                                                                                                                                                                                           | .04<br>06<br>.07<br>.11<br>.15<br>.19<br>.23<br>.24<br>.26<br>.29<br>.32<br>.36              |  |  |  |

| <b>6</b><br>7 | Mac<br>App<br>6.1<br>6.2<br>6.3<br>Fut               | Conclusion       1         chine Learning-based Side Channel Vulnerability Analysis for Emerging plications       1         Accurate and Efficient Machine Learning-Based Website Fingerprinting Attack through Hardware Performance Counters       1         6.1.1       Background       1         6.1.2       Leaked-Web Attack Implementation       1         6.1.3       Experimental Results and Analysis       1         Stealthy Inference Attack on DNN via Cache-based Side-Channel Attacks       1         6.2.1       Introduction       1         6.2.2       Background and Motivation       1         6.2.3       Overview of Attack       1         6.2.4       Evaluation       1         1       1       1         1       1       1         1       1       1         1       1       1         1       1       1         1       1       1         1       1       1         1       1       1         1       1       1         1       1       1         1       1       1         1       1       1         1       1       1                                                                                                                                        | .04<br>06<br>.07<br>.11<br>.15<br>.23<br>.24<br>.26<br>.29<br>.32<br>.36<br><b>38</b>        |  |  |  |

|               | Mac<br>App<br>6.1<br>6.2<br>6.3<br>Fut<br>7.1        | Conclusion       1         chine Learning-based Side Channel Vulnerability Analysis for Emerging plications       1         Accurate and Efficient Machine Learning-Based Website Fingerprinting Attack       1         through Hardware Performance Counters       1         6.1.1 Background       1         6.1.2 Leaked-Web Attack Implementation       1         6.1.3 Experimental Results and Analysis       1         Stealthy Inference Attack on DNN via Cache-based Side-Channel Attacks       1         6.2.1 Introduction       1         6.2.2 Background and Motivation       1         6.2.3 Overview of Attack       1         6.2.4 Evaluation       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1                                                                                                                                                                                | .04<br>06<br>.07<br>.11<br>.15<br>.23<br>.24<br>.26<br>.29<br>.32<br>.36<br><b>38</b><br>.39 |  |  |  |

| 7             | Mac<br>App<br>6.1<br>6.2<br>6.3<br>Fut<br>7.1<br>7.2 | Conclusion       1         chine Learning-based Side Channel Vulnerability Analysis for Emerging plications       1         Accurate and Efficient Machine Learning-Based Website Fingerprinting Attack through Hardware Performance Counters       1         6.1.1       Background       1         6.1.2       Leaked-Web Attack Implementation       1         6.1.3       Experimental Results and Analysis       1         Stealthy Inference Attack on DNN via Cache-based Side-Channel Attacks       1         6.2.1       Introduction       1         6.2.2       Background and Motivation       1         6.2.3       Overview of Attack       1         6.2.4       Evaluation       1         1       Conclusion       1         1       1       1       1         1       1       1       1         1       1       1       1         1       1       1       1         1       1       1       1         1       1       1       1         1       1       1       1         1       1       1       1         1       1       1       1         1       1 <td>.04<br/>06<br/>.07<br/>.11<br/>.15<br/>.23<br/>.24<br/>.26<br/>.29<br/>.32<br/>.36<br/><b>38</b><br/>.39</td> | .04<br>06<br>.07<br>.11<br>.15<br>.23<br>.24<br>.26<br>.29<br>.32<br>.36<br><b>38</b><br>.39 |  |  |  |

# List of Figures

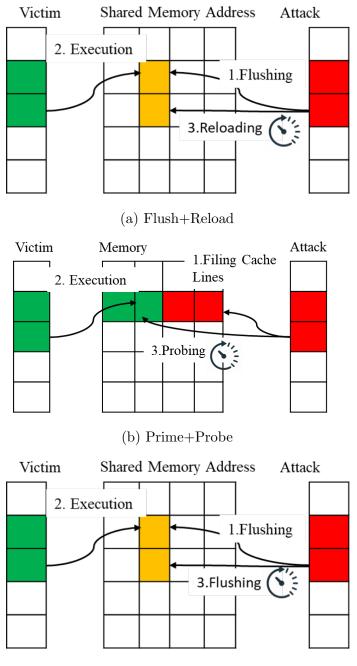

| 3.1  | Working principle of three emerging cache-based side-channel attacks                   | 22 |

|------|----------------------------------------------------------------------------------------|----|

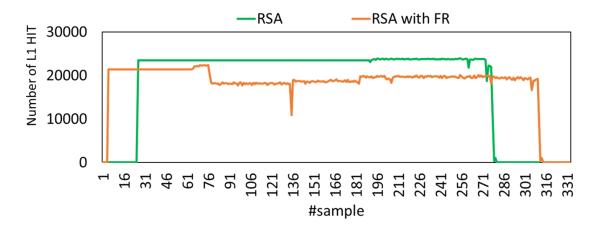

| 3.2  | L1 HIT of RSA and RSA under Flush Reload attack                                        | 24 |

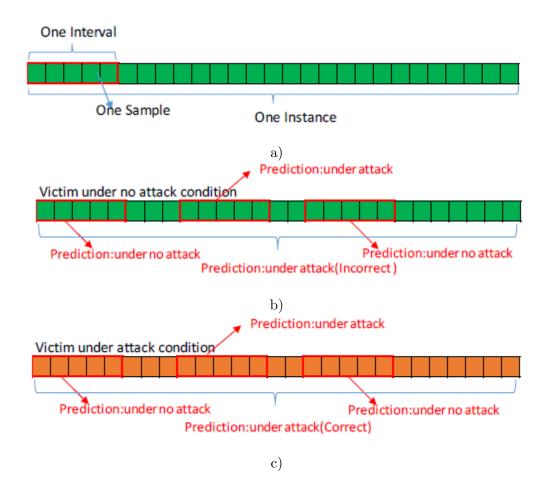

| 3.3  | False Alarm Problem: a) Concept; b) VNA condition; c) VA condition                     | 25 |

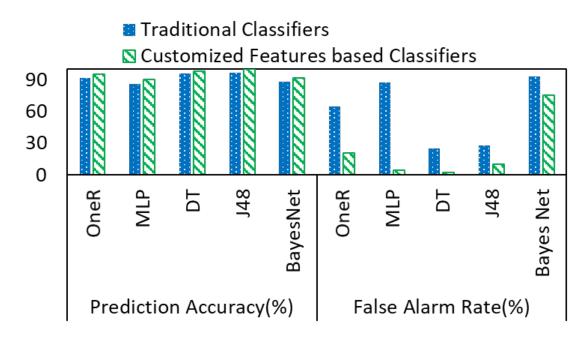

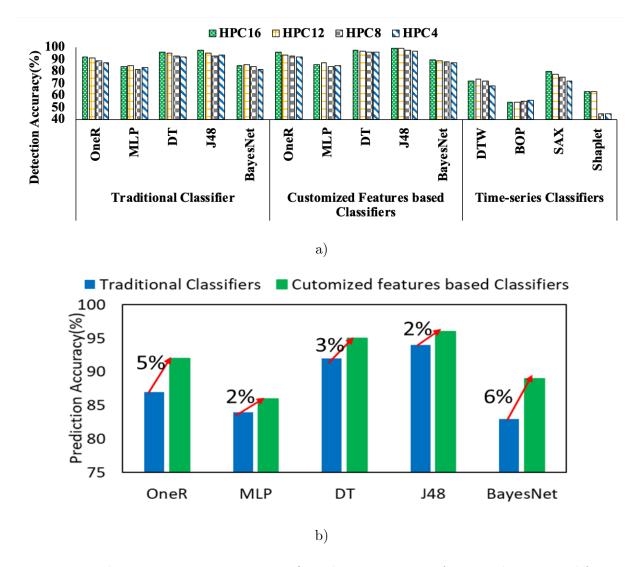

| 3.4  | Traditional and customized features based classifiers comparison (datasets collected   |    |

|      | based on Section 3.1.2)                                                                | 26 |

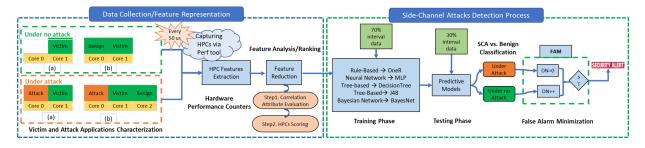

| 3.5  | Overview of SCARF, the proposed real-time SCAs detection methodology based on          |    |

|      | victim application HPCs                                                                | 26 |

| 3.6  | Prediction accuracy comparison: a) prediction accuracy of proposed customized          |    |

|      | features based classifiers and the rest two type classifiers; b) zooming in prediction |    |

|      | accuracy of traditional and customized features based classifiers                      | 31 |

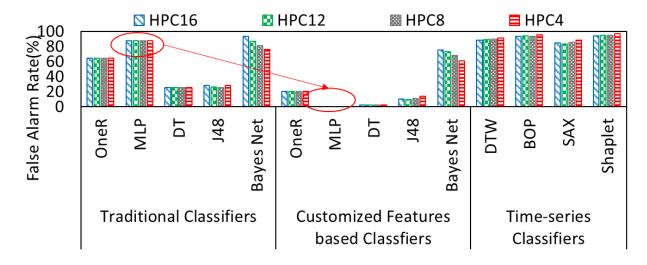

| 3.7  | False alarm rate comparison                                                            | 32 |

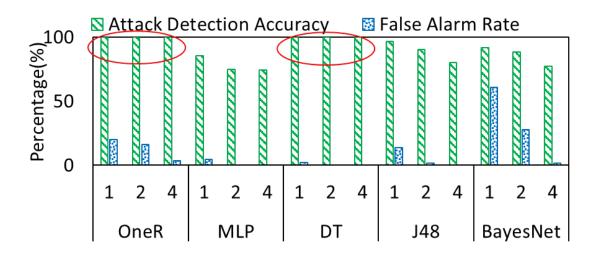

| 3.8  | Attack detection accuracy vs false alarm rate with various DN values                   | 34 |

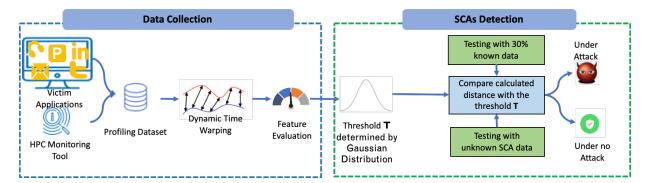

| 3.9  | Overview of <i>HybriDG</i> , the proposed hybrid Model for detecting emerging zero-day |    |

|      | SCAs                                                                                   | 36 |

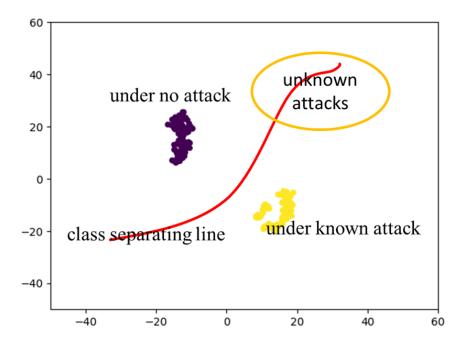

| 3.10 | TSNE plot for victim under no attack and victim under known attacks samples            | 37 |

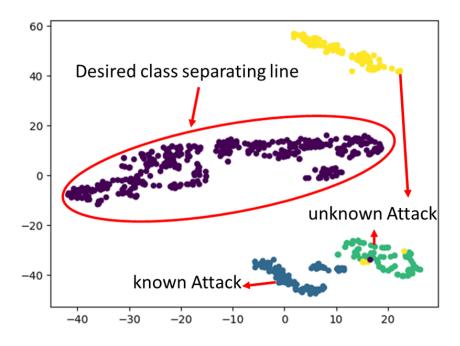

| 3.11 | TSNE plot with desired classifying line for victim under no attack, known attack,      |    |

|      | and unknown attack samples                                                             | 38 |

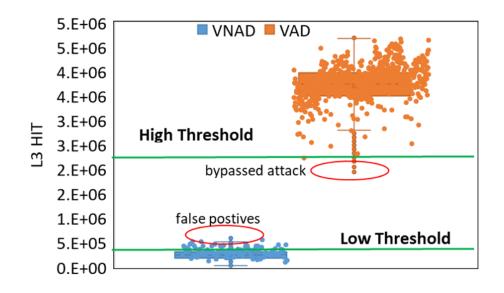

| 3.12 | Different threshold influences(VNAD: victim under no attack distances; VAD: victim     |    |

|      | under attack distances.)                                                               | 40 |

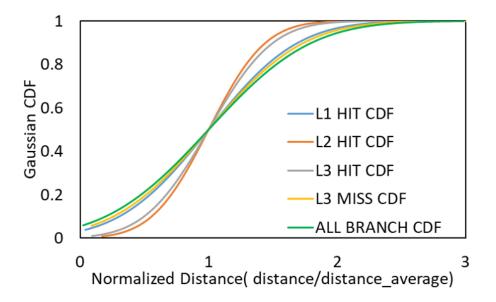

| 3.13 | Gaussian distribution of various HPCs temporal traces                                  | 40 |

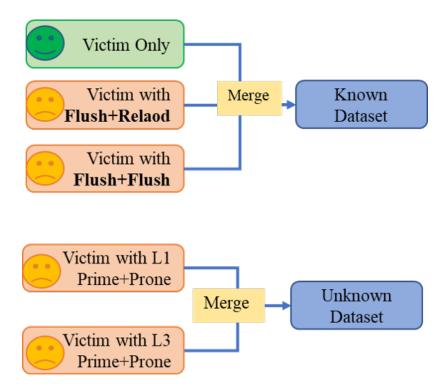

| 3.14 | Testing datasets                                                                       | 43 |

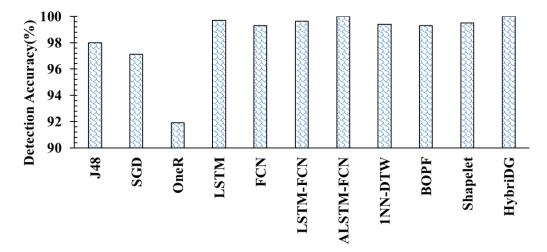

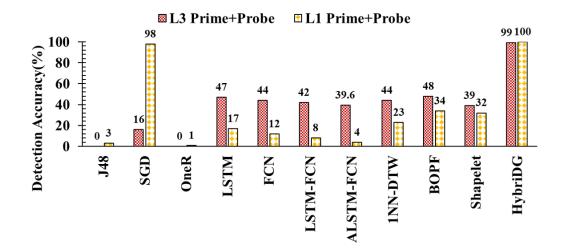

| 3.15 | Known attacks detection accuracy of various classifiers                                | 44 |

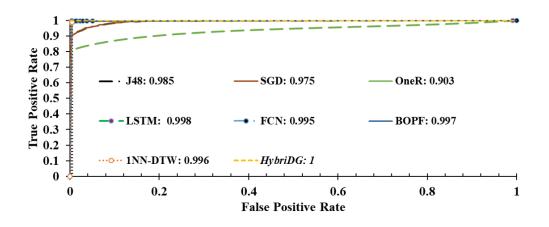

| 3.16 | ROC Curve and AUC value of various classifiers                                         | 45 |

| 3.17 | Unknown attacks detection accuracy                                                     | 45 |

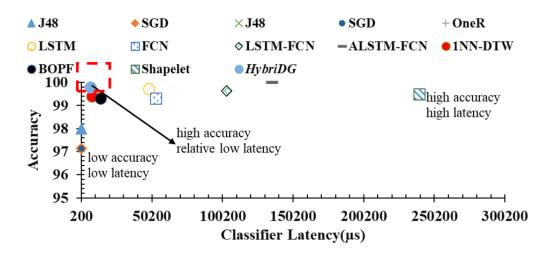

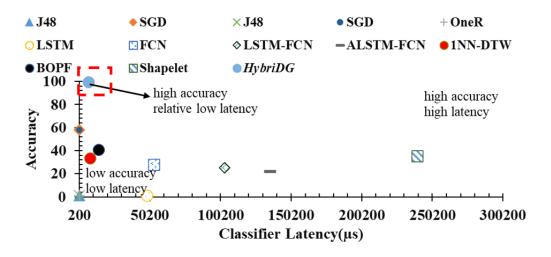

| 3.18 | Efficiency comparison among various classifiers for known dataset                      | 46 |

| 3.19 | Efficiency comparison among various classifiers for unknown dataset                    | 47 |

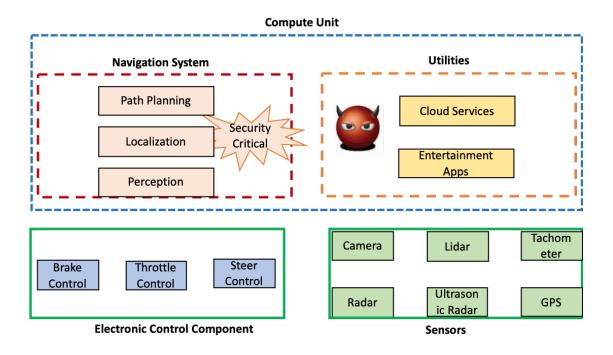

| 4.1  | General hardware and software architecture of an autonomous vehicle                    | 50 |

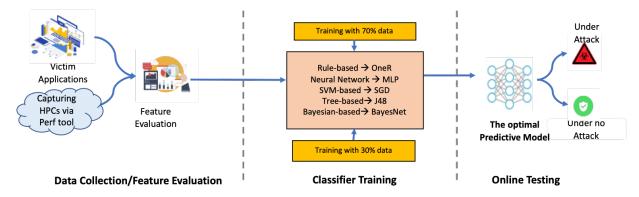

| 4.2  | Overview of the ML-based Detector                                                      |    |

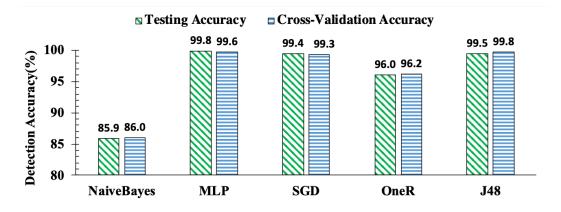

| 4.3  | Testing accuracy and cross-validation accuracy                                         |    |

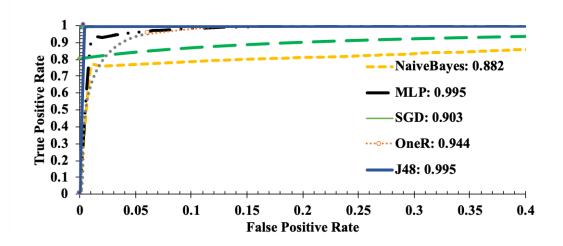

| 4.4  | ROC Curve and AUC value of various classifiers                                         |    |

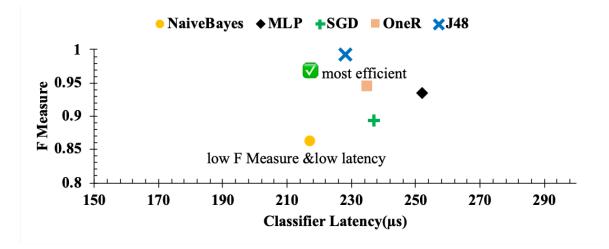

| 4.5  | Efficiency comparison among various classifiers                                        | 56 |

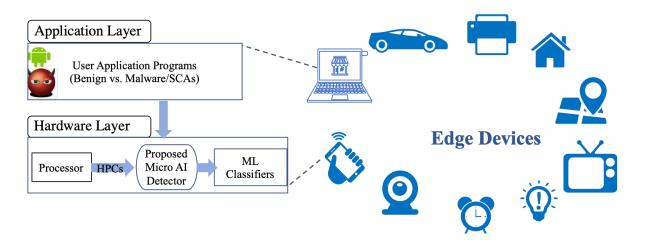

| 4.6  | Application of the proposed micro AI enabled countermeasure for securing edge          |    |

|      | devices at the hardware level                                                          |    |

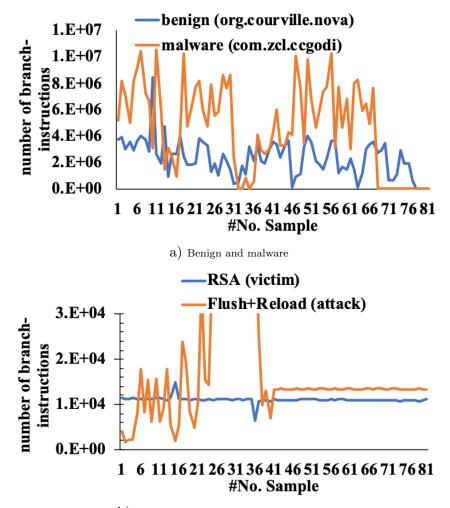

| 4.7  | Branch-instruction HPC traces between benign(victim) and attacks                       |    |

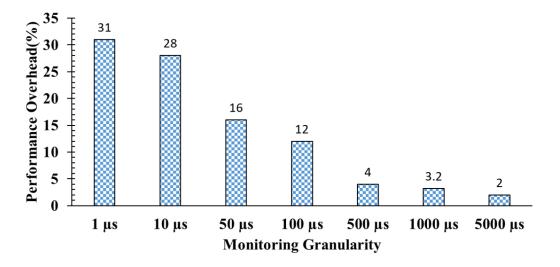

| 4.8  | Performance overhead with various monitoring granularity                               |    |

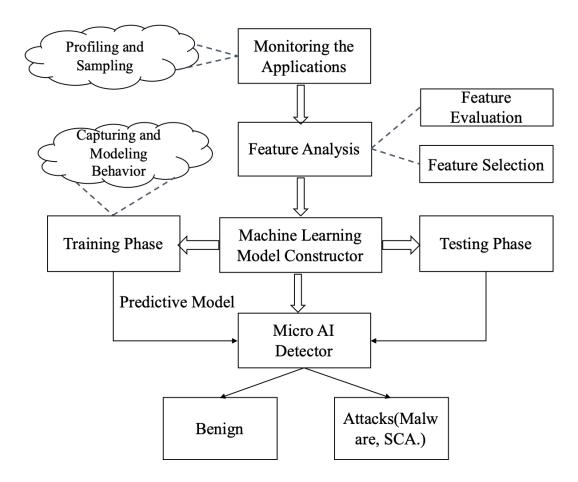

| 4.9  | Overview of the proposed machine learning-based countermeasure for edge devices .      | 65 |

|      |                                                                                        |    |

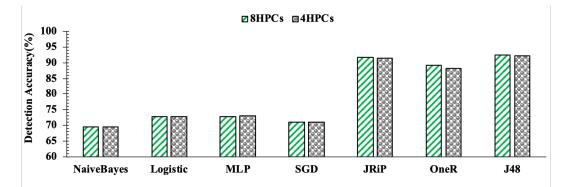

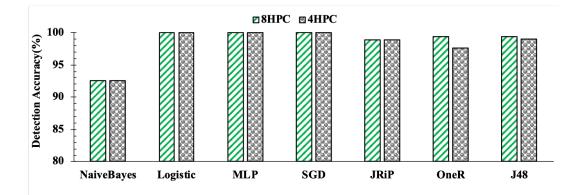

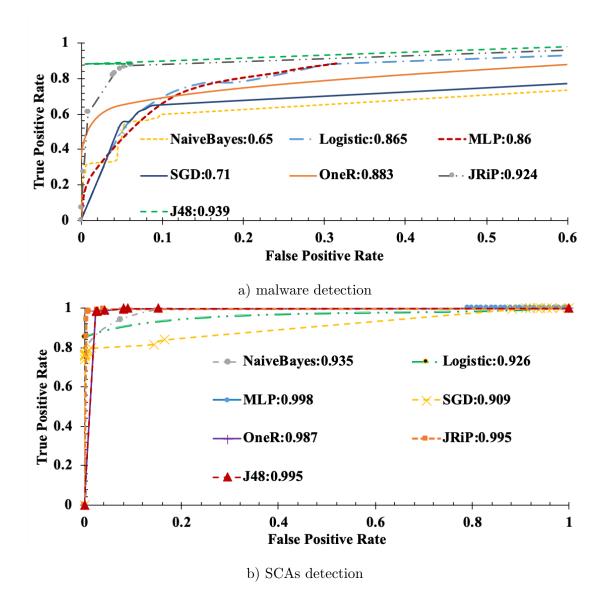

| $\begin{array}{c} 4.11 \\ 4.12 \end{array}$ | Malware detection accuracy of different classifiers with various HPCs       6         SCAs detection accuracy of different classifiers with various HPCs       7         ROC Curve and AUC values comparison across various classifiers       7         Efficiency comparison across various classifiers with 4 HPCs       7 | $\frac{10}{2}$   |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

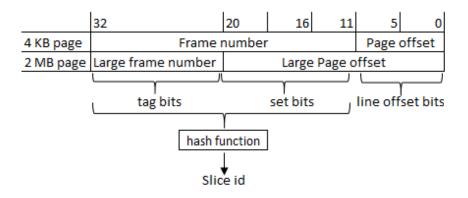

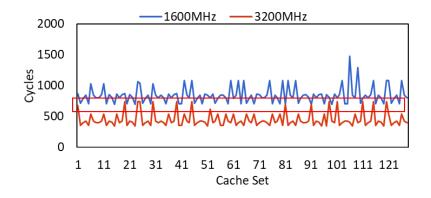

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5             | Cache architecture                                                                                                                                                                                                                                                                                                           | 0<br>2<br>3<br>8 |

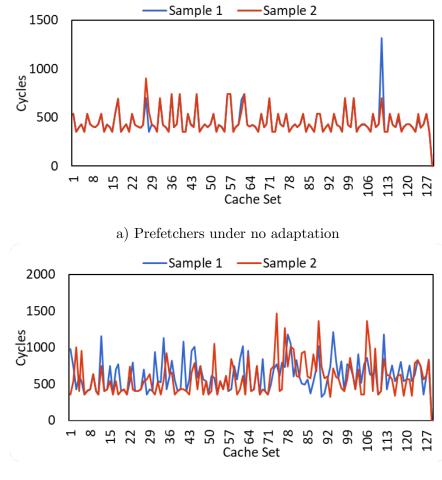

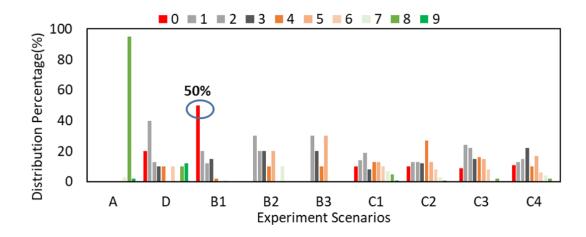

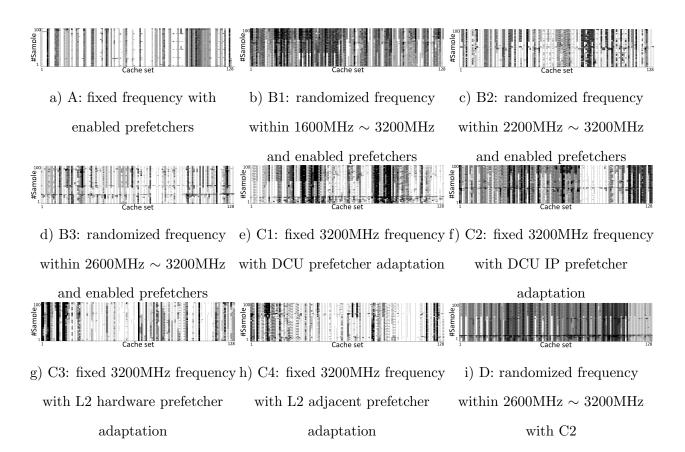

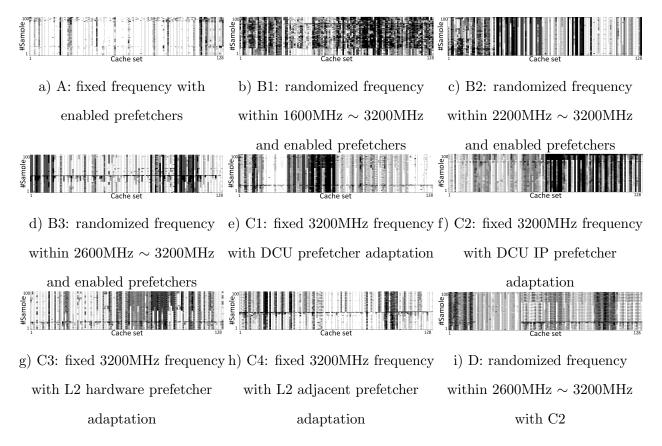

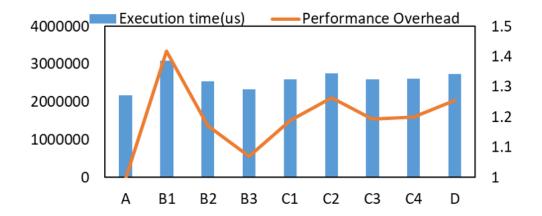

| 5.6<br>5.7<br>5.8                           | AES cache access heatmap under different randomization cases (A, B, C and D) $\dots$ 8<br>RSA cache access heatmap under different randomization cases (A, B, C and D) $\dots$ 9<br>A $\sim$ D execution time and performance overhead where A $\sim$ D is normalized by A $\dots$ 9                                         | 0                |

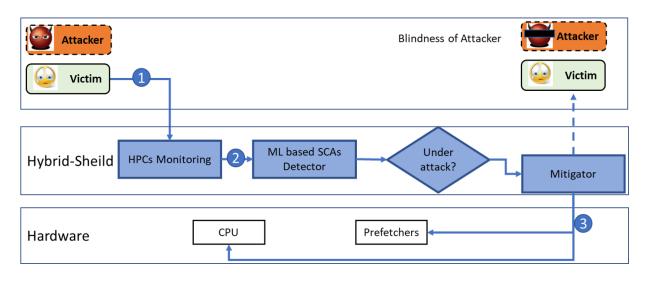

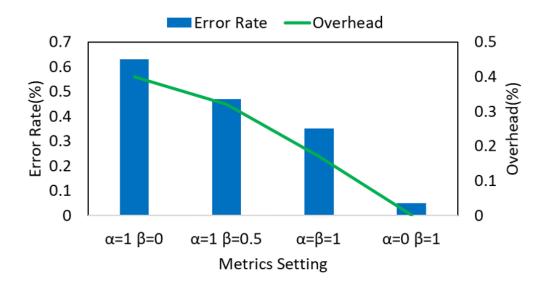

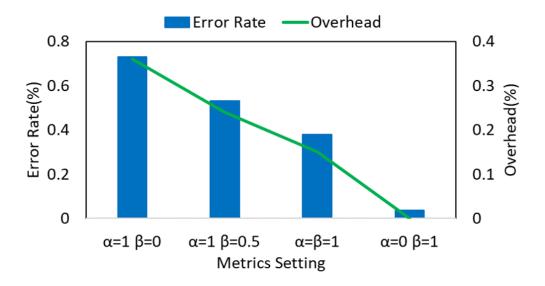

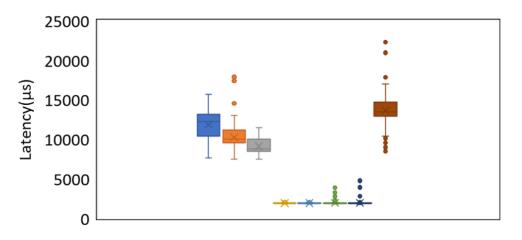

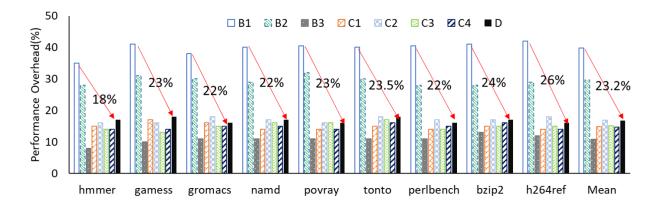

| $5.9 \\ 5.10 \\ 5.11 \\ 5.12$               | Overview of Hybrid-Shield9Flush+Reload Error Rate and RSA Overhead10Prime+Probe Error Rate and RSA Overhead10Latency of randomizing across $A \sim D$ 10Performance overhead analysis of $B \sim D$ Scenarios across different SPEC CPU2006                                                                                  | $7\\0\\1$        |

|                                             | benchmarks                                                                                                                                                                                                                                                                                                                   | 3                |

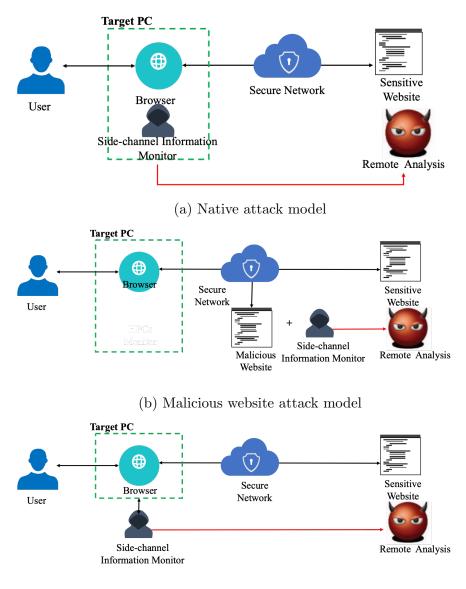

| 6.1                                         | Website fingerprinting attacks threat model                                                                                                                                                                                                                                                                                  |                  |

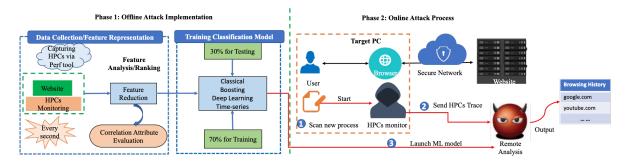

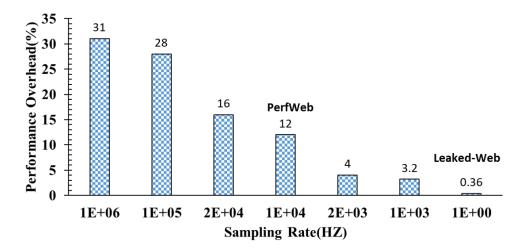

| $\begin{array}{c} 6.2 \\ 6.3 \end{array}$   | Overview of the proposed <i>Leaked-Web</i> attack model                                                                                                                                                                                                                                                                      | 6                |

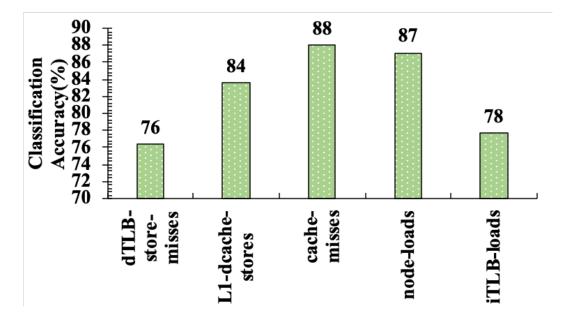

| $6.4 \\ 6.5$                                | The average classification accuracy under Firefox for each HPC                                                                                                                                                                                                                                                               |                  |

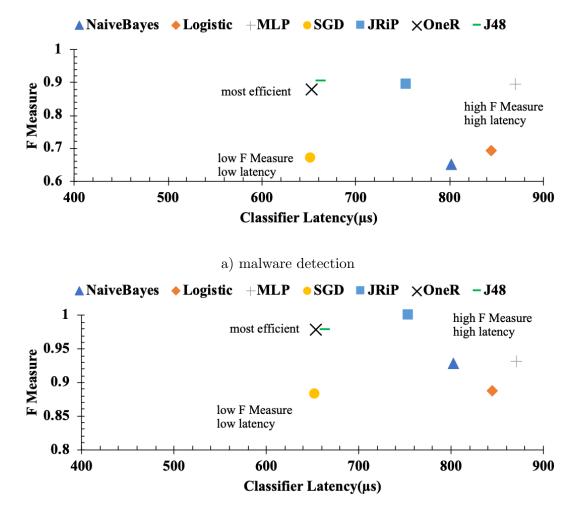

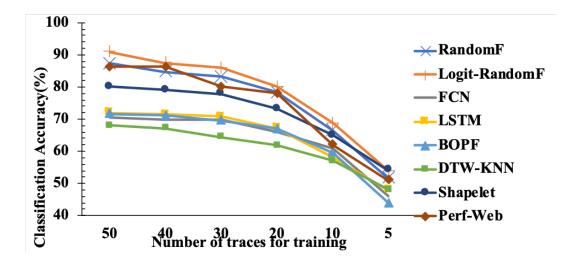

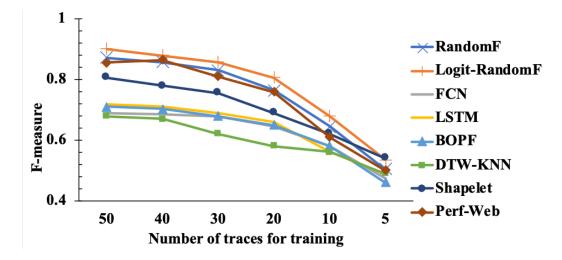

| $6.6 \\ 6.7$                                | F-measure with various classification algorithms 4 HPCs                                                                                                                                                                                                                                                                      |                  |

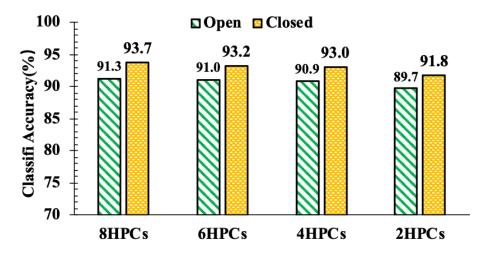

| 6.8                                         | for closed and open world dataset                                                                                                                                                                                                                                                                                            | 1                |

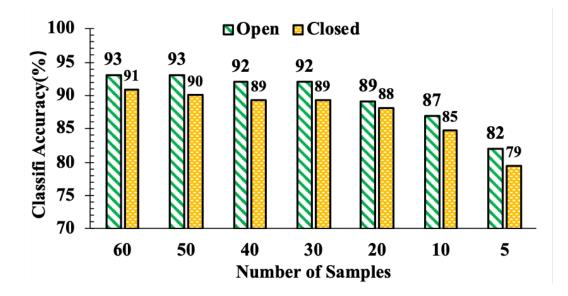

| 6.9                                         | world dataset                                                                                                                                                                                                                                                                                                                |                  |

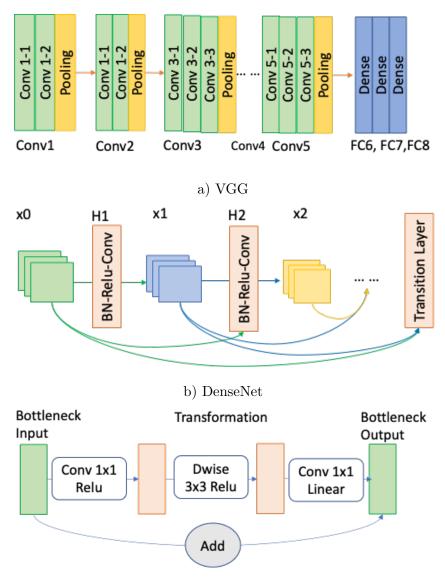

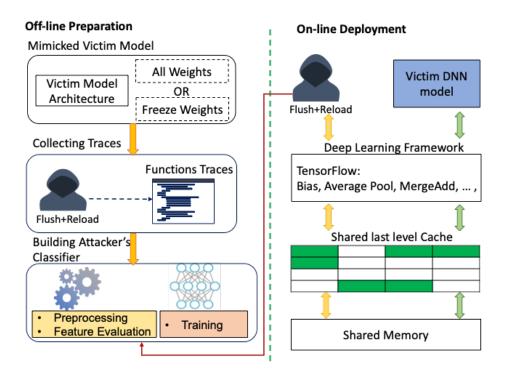

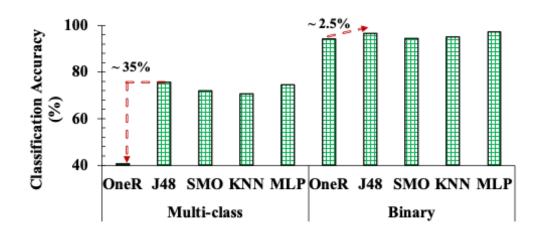

|                                             | Design of the presented attack                                                                                                                                                                                                                                                                                               | 7                |

|                                             | attack on MobileNet v1                                                                                                                                                                                                                                                                                                       | 3                |

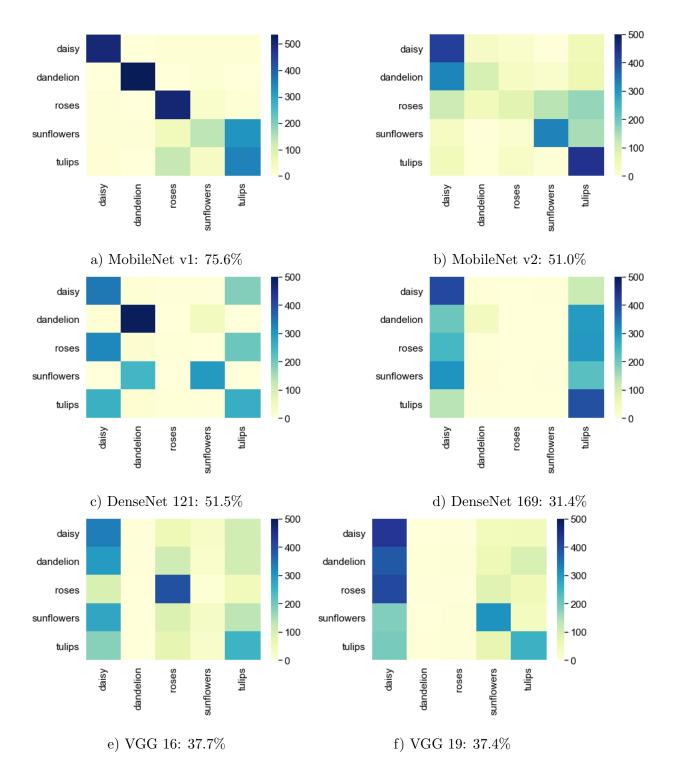

| 6.12                                        | Heatmap of multi-class attacking success rate under setting A of six models: MobileNet v1, MobileNet v2, DenseNet 121, DenseNet 169, VGG 19, and VGG 16                                                                                                                                                                      | 5                |

# List of Tables

| 3.1          | False Positive and False Negative evaluation (True: VNA; False: VA)                        | 24  |

|--------------|--------------------------------------------------------------------------------------------|-----|

| 3.2          | Architectural configurations                                                               | 27  |

| 3.3          | The experimented victim and attack applications                                            | 27  |

| 3.4          | The collected HPC features and their ranking                                               | 28  |

| 3.5          | Selected Monitoring HPCs List                                                              | 36  |

| 3.6          | VNA dection accuracy and false positive rate with the 1.5 $\times$ distance_average across |     |

|              | various HPCs                                                                               | 41  |

| 3.7          | Theoretical false positive rate and corresponding L2 threshold value                       | 41  |

| 3.8          | Selected classifiers                                                                       | 42  |

| 4.1          | Common Compute Unit for Autonomous Vehicles                                                | 51  |

| 4.2          | List of HPC events collected for SCAs detection                                            | 53  |

| 4.3          | F-measure of various classifiers                                                           | 55  |

| 4.4          | Comparison of recent hardware-assisted malware and side-channel attack detection           |     |

|              | techniques and their implementation methods                                                | 57  |

| 4.5          | Experiment setup                                                                           | 65  |

| 4.6          | The collected HPC features                                                                 | 66  |

| 4.7          | The collected HPC features and their ranking                                               | 68  |

| 4.8          | Evaluated ML classifiers for attacks detection                                             | 69  |

| 4.9          | False Positive Rate of various classifiers with 4 HPCs                                     | 71  |

|              | F-measure of various classifiers with 4 HPCs                                               | 71  |

|              | ML classifier execution overhead                                                           | 75  |

| 4.12         | Hardware implementation results of ML-based micro AI countermeasures                       | 77  |

| 5.1          | 4 Prefetchers in Intel Computer Architecture                                               | 80  |

| 5.2          | Hardware Platform                                                                          | 87  |

| 5.3          | Experiment Scenarios                                                                       | 87  |

| 5.4          | Error Rate of Flush+Reload recovered key                                                   | 93  |

| 5.5          | Comparison of the recent works on SCAs protection (Red color indicates drawbacks           |     |

|              | of the work)                                                                               | 95  |

| 6.1          | Recent Website Fingerprint attacks comparison and contributions of the Leaked-Web          |     |

| 6.2          | The collected HPC features and their ranking                                               |     |

| 6.3          | Monitored function list                                                                    |     |

| $6.4 \\ 6.5$ | Prominent functions for the introduced attacker                                            | 131 |

| 0.0          | sunflowers, and tulips)                                                                    | 122 |

|              | sumowers, and tunps)                                                                       | 199 |

### Chapter 1

# Introduction