#### UNIVERSITY OF CALIFORNIA RIVERSIDE

### Using Multithreaded Techniques to Mask Memory Latency on FPGA Accelerators

#### A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Computer Science

by

Robert Joseph Halstead

March 2015

Dissertation Committee:

Dr. Walid A. Najjar, Chairperson Dr. Vassilis Tsotras Dr. Nael Abu-Ghazaleh Dr. Zizhong Chen

Copyright by Robert Joseph Halstead 2015 The Dissertation of Robert Joseph Halstead is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgments

I thank my committee, without whose help, I would not have been here.

To my parents and family.

#### ABSTRACT OF THE DISSERTATION

#### Using Multithreaded Techniques to Mask Memory Latency on FPGA Accelerators

by

Robert Joseph Halstead

Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, March 2015 Dr. Walid A. Najjar, Chairperson

The performance gap between CPUs, and memory memory has diverged significantly since the 1980's making efficiency memory utilization a key concern for any application developer. Modern CPUs will process orders of magnitude more data than their memory architectures can sustain. Multiple levels of caches are used by the major CPU architects to cope with this issue. Frequently used data is stored as close as possible to the core, which allows it to be retrieved in a few cycles. Compared to the thousands of cycles it would take to be retrieved from main memory. However, data locality is important for caches to be effective, and as applications become more and more irregular the CPU's performance drops. This causes many important applications (e.g. sparse matrices, graphs, hash tables) to suffer from poor performance. This thesis explores how custom hardware accelerators using memory masking multithreaded techniques can be used to improve performance. In hardware multithreaded designs thread states are managed directly in hardware, and with enough application parallelism they can fully mask memory latency without storing data in caches. Designs scale well to match the memory architectures bandwidth. The emergence of heterogeneous FPGA platforms has made it easier to build and test the design on real world hardware.

This thesis starts with the issue of programmability. Hardware development is notoriously difficult and time consuming. The CHAT tool, a C-to-VHDL compiler, is presented that assists developers by generating custom multithreaded kernels from high level software descriptions. The thesis proceeds by using CHAT to generate a custom Sparse Matrix Vector (SpMV) kernel. Results show how multithreading can provide data independent performance. Compared to the software and GPU performance which drops significantly as the benchmark's irregularity increases. Cache miss rates increase on the CPU, and memory cannot be coalesced as efficiently on the GPUs. Finally we use multithreading to accelerate two common database operations: Hash join, and aggregation. They are the first in-memory implementations on FPGA hardware. The hash join design shows an improvement of 2x over the best multicore software designs available, and does so with 33% less memory bandwidth. Aggregation shows comparable performance when generating hash tables. However, it generates multiple tables that need to be merged, and this step reduces performance on high cardinality datasets.

### Contents

| Li       | st of           | Figure | es                                     | x                   |

|----------|-----------------|--------|----------------------------------------|---------------------|

| Li       | st of           | Tables | 5                                      | xiii                |

| 1        | $\mathbf{Intr}$ | oducti | on                                     | 1                   |

| <b>2</b> | Bac             | kgrour | nd                                     | 6                   |

|          | 2.1             | Latenc | cy Masking Multithreaded Architectures | 7                   |

|          |                 | 2.1.1  | Full Latency Masking Architectures     | 8                   |

|          |                 | 2.1.2  | Sun UltraSPARC T Processors            | 9                   |

|          | 2.2             | Sparse | e Matrix Vector Multiplication         | 10                  |

|          |                 | 2.2.1  | Sparse Matrix Formats                  | 10                  |

|          |                 |        | 2.2.1.1 Coordinate Format              | 11                  |

|          |                 |        | 2.2.1.2 Compressed Sparse Row          | 11                  |

|          |                 |        | 2.2.1.3 ELLPACK                        | 13                  |

|          |                 |        | 2.2.1.4 Hybrid format                  | 14                  |

|          |                 | 2.2.2  | FPGA Approaches                        | 14                  |

|          |                 | 2.2.3  | GPU Approaches                         | 15                  |

|          | 2.3             | Accele | erating Database Operations with FPGAs | 16                  |

|          |                 | 2.3.1  | Query Processing & DBMSes              | 17                  |

|          |                 | 2.3.2  | Join Operations                        | 18                  |

| 3        | СН              | АТ - С | Compiled Hardware Accelerated Threads  | 20                  |

| Ŭ        | 3.1             |        | omy of Irregular Applications          | <b>2</b> 2          |

|          | 3.2             |        | HAT Compiler                           | ${25}$              |

|          | 0.2             | 3.2.1  | Hi-CIRRF in SUIF 2.0                   | $\frac{-\circ}{25}$ |

|          |                 | 3.2.2  | Lo-CIRRF in LLVM                       | $\overline{27}$     |

|          | 3.3             | -      | e Irregular Applications               | $\frac{-1}{28}$     |

|          |                 | 3.3.1  | One Dimensional Indexing               | 29                  |

|          |                 | 3.3.2  | Two Dimensional Indexing               | 30                  |

|          | 3.4             | Experi | imental Evaluation                     | 31                  |

|          |                 | 3.4.1  | Convey HC-2ex Implementation           | 31                  |

|          |                 | 3.4.2  | Runtime Performance                    | 33                  |

|          | 3.5             | Conclu |                                        | 35                  |

| <b>4</b> | AN   | Aultithreaded Sparse Matrix Mulitplication Kernel                  | 36 |

|----------|------|--------------------------------------------------------------------|----|

|          | 4.1  | A Multithreaded Sparse Matrix Kernel                               | 37 |

|          |      | 4.1.1 SpMV Kernel Code                                             | 37 |

|          |      | 4.1.2 Processing Element                                           | 38 |

|          |      | 4.1.3 Thread Management                                            | 40 |

|          |      | 4.1.4 HC-2ex FPGA Implementation                                   | 41 |

|          | 4.2  | Experimental Evaluation                                            | 42 |

|          |      | 4.2.1 Experimental Setup                                           | 42 |

|          |      | 4.2.2 Memory Footprint of Sparse Matrix Storage Formats            | 45 |

|          |      | 4.2.3 Dense Matrix Experiments                                     | 45 |

|          |      | 4.2.4 Throughput Comparison with CSR                               | 47 |

|          |      | 4.2.5 FPGA vs. GPU Throughput with different Sparse Matrix Formats | 50 |

|          |      | 4.2.6 Normalized Throughput                                        | 51 |

|          |      | 4.2.7 Throughput on Truly Irregular Data                           | 52 |

|          | 4.3  | Conclusion                                                         | 53 |

|          |      |                                                                    |    |

| <b>5</b> |      | GA based Multithreading for In-Memory Hash Joins                   | 55 |

|          | 5.1  | Related Work                                                       | 55 |

|          | 5.2  | Proposed Approach                                                  | 57 |

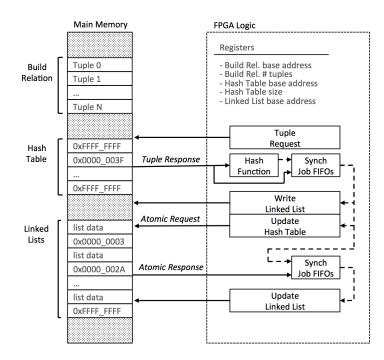

|          |      | 5.2.1 Build Phase Engine                                           | 57 |

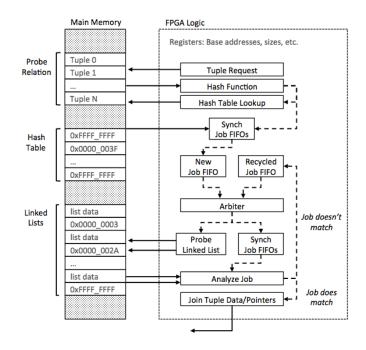

|          |      | 5.2.2 Probe Phase Engine                                           | 59 |

|          |      | 5.2.3 Possible Optimizations                                       | 61 |

|          | 5.3  | Experimental Results                                               | 62 |

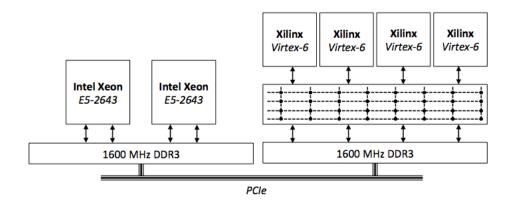

|          |      | 5.3.1 Convey-MX Platform                                           | 64 |

|          |      | 5.3.2 FPGA & Software Implementations                              | 64 |

|          |      | 5.3.3 Dataset Description                                          | 66 |

|          |      | 5.3.4 Throughput evaluation                                        | 67 |

|          |      | 5.3.5 Scalability                                                  | 71 |

|          |      | 5.3.6 Throughput Efficiency                                        | 75 |

|          |      | 5.3.7 FPGA Area Utilization                                        | 77 |

|          | 5.4  | Conclusion                                                         | 78 |

| 6        | FP   | GA based Multithreading for In-Memory Aggregation                  | 79 |

| Ū        |      | A FPGA Aggregation Kernel                                          | 80 |

|          | 6.2  | Implementation Considerations & Limitations                        | 83 |

|          | 6.3  | Experimental Evaluation                                            | 84 |

|          | 0.0  | 6.3.1 FPGA & Software Implementations                              | 84 |

|          |      | 6.3.2 Dataset Description                                          | 86 |

|          |      | 6.3.3 Throughput Evaluation                                        | 88 |

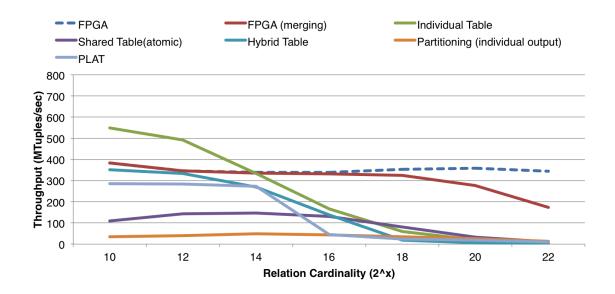

|          |      | 6.3.4 Effects of the Merge Operation                               | 92 |

|          | 6.4  | Conclusion                                                         | 93 |

|          | 0.1  |                                                                    | 50 |

| 7        | Cor  | nclusion                                                           | 94 |

| Bi       | blio | graphy                                                             | 97 |

|          | c    |                                                                    |    |

## List of Figures

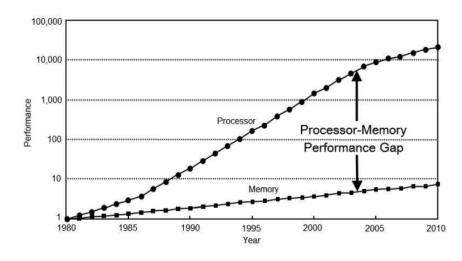

| 1.1 | Graph comparing the performance of single core processors to memory from the 1980's to the 2010's.                                                                                              | 2  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

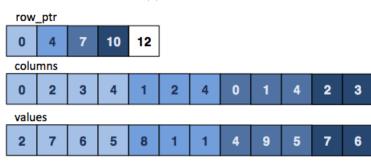

| 2.1 | An example matrix that is used to show how different sparse matrix formats store data.                                                                                                          | 11 |

| 2.2 | COO, CSR and ELL sparse matrix storage formats for the example matrix in Figure 2.1.                                                                                                            | 12 |

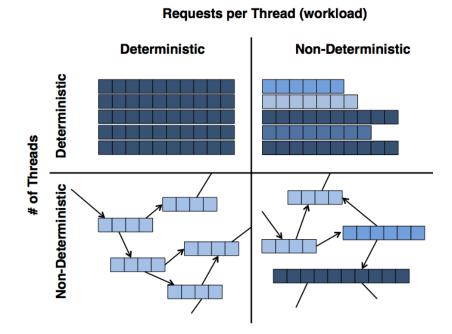

| 3.1 | A taxonomy of irregular applications where the number of threads and<br>the workload sizes are, or are not deterministic                                                                        | 23 |

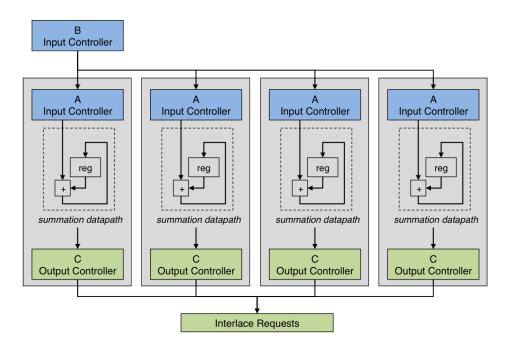

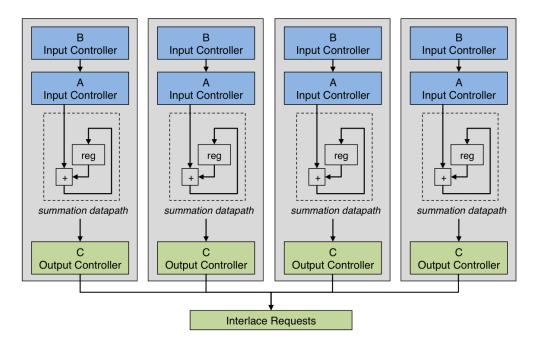

| 3.2 | FPGA components for the 1-dimensional kernel as generated by CHAT.<br>Notice that the B input controller is optimized to shared its data between<br>all A input controllers.                    | 31 |

| 3.3 | FPGA components for the 2-dimensional kernel as generated by CHAT.<br>Notice that the B input controller cannot share its data between separate<br>A input controllers                          | 32 |

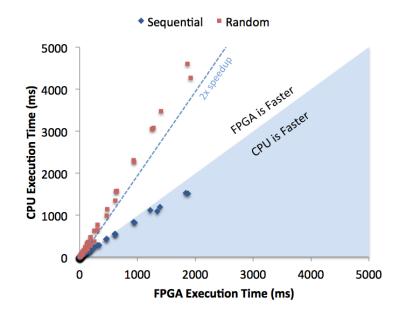

| 3.4 | FPGA vs CPU runtime performance comparing sequential and random data on a 1-dimensionally index array. Dataset sizes range from 1 million 8-byte integers to 10-billion 8-byte integers.        | 33 |

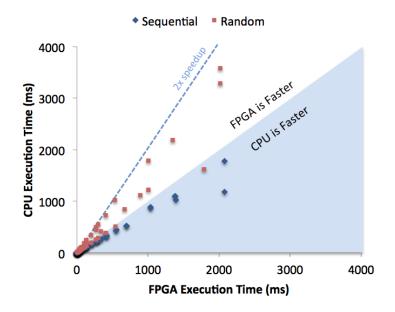

| 3.5 | FPGA vs CPU runtime performance comparing sequential and random data on a 2-dimensionally index array. Dataset sizes range from 1 million 8-byte integers to 10-billion 8-byte integers.        | 34 |

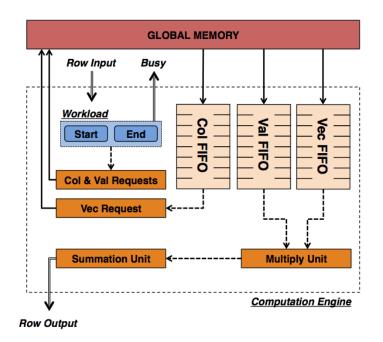

| 4.1 | Each PE is assigned a thread. It requests the necessary data (Column, Vector, and Value) from global memory. Returned data values are pushed through the multiply pipeline, and summation unit. | 39 |

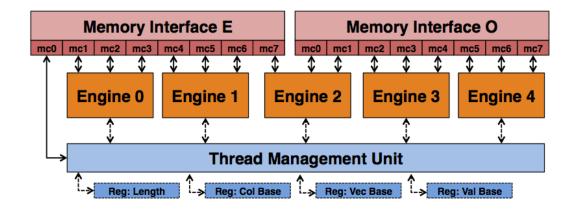

| 4.2 | The MT-FPGA architecture on one AE. Control signals specify the number of jobs (length), and the base addresses of the sparse matrix arrays.<br>All memory channels of the AE are utilized      | 40 |

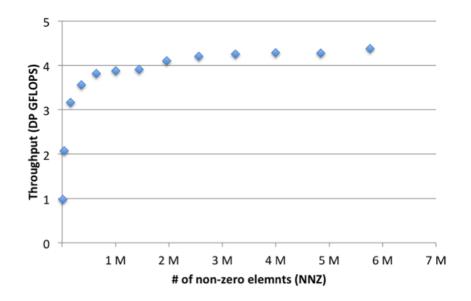

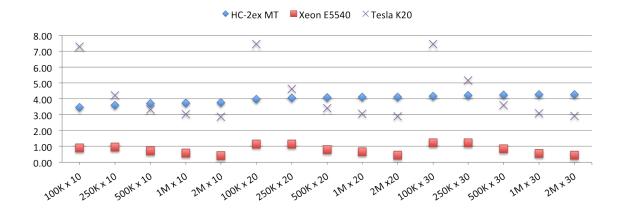

| 4.3  | The sustained SpMV throughput as the matrix sizes increase. The ma-<br>tricies are dense, but stored in CSR format. The Convey HC-2ex is fully<br>utilized with 20 PEs | 46 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

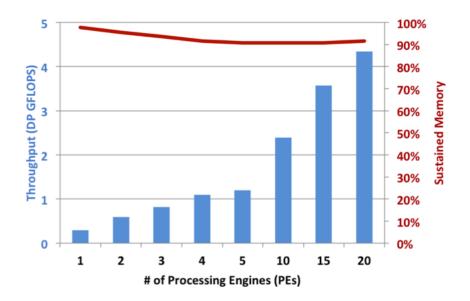

| 4.4  | The sustained memory bandwidth, and throughput as the number of PEs increases. All test use a dense 4 million non-zero element dense matrix stored in CSR format.      | 47 |

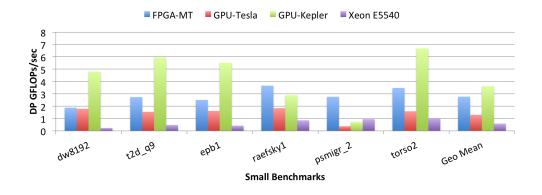

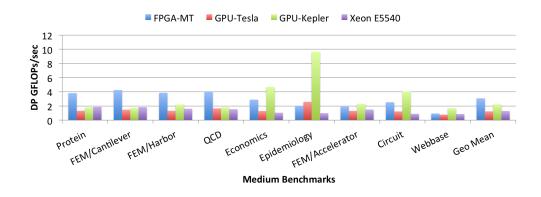

| 4.5  | FPGA, CPU, and GPU throughput performance on suite 1                                                                                                                   | 48 |

| 4.6  | FPGA, CPU, and GPU throughput performance on suite 2                                                                                                                   | 48 |

| 4.7  | FPGA, CPU, and GPU throughput performance on suite 3                                                                                                                   | 48 |

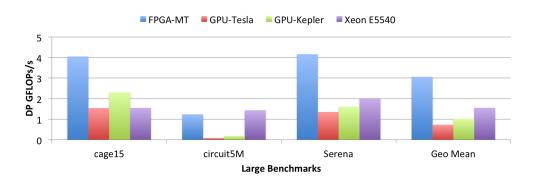

| 4.8  | FPGA vs Kepler GPU throughput performance. The GPU uses different matrix formats to improve performance.                                                               | 50 |

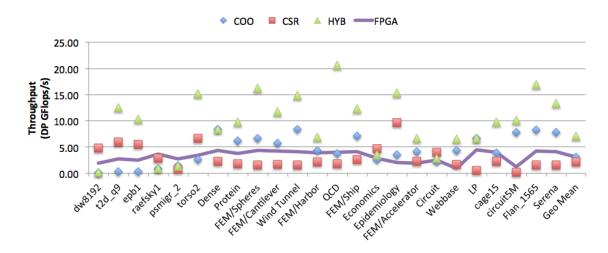

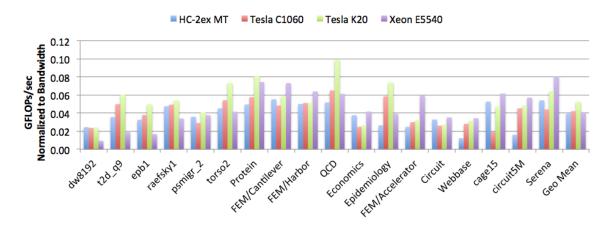

| 4.9  | Throughput performance for each architecture normalized to the available bandwidth.                                                                                    | 51 |

| 4.10 | Visual printout of the sparse matrices used to benchmark Section 4.2.4 results                                                                                         | 52 |

| 4.11 | FPGA, CPU, and GPU throughput performance on truly irregular data.                                                                                                     | 52 |

| 5.1  | The FPGA Build Phase Engine.                                                                                                                                           | 58 |

| 5.2  | The FPGA Probe Phase Engine.                                                                                                                                           | 60 |

| 5.3  | The Convey MX software and hardware regions.                                                                                                                           | 63 |

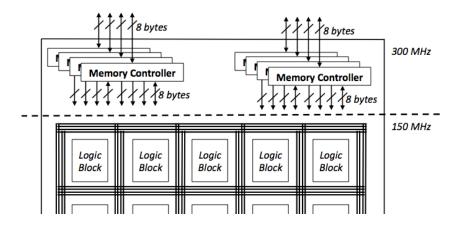

| 5.4  | Each Convey MX FPGA AE has 8 memory controllers, which are split into 16 channels for the FPGA's logic cells.                                                          | 63 |

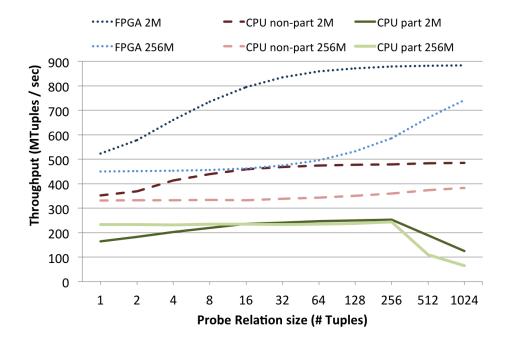

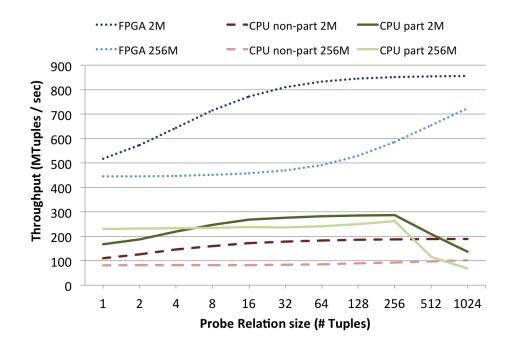

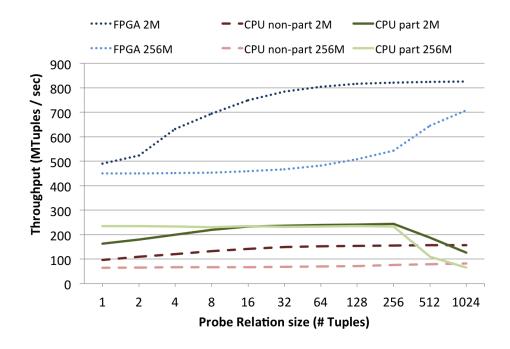

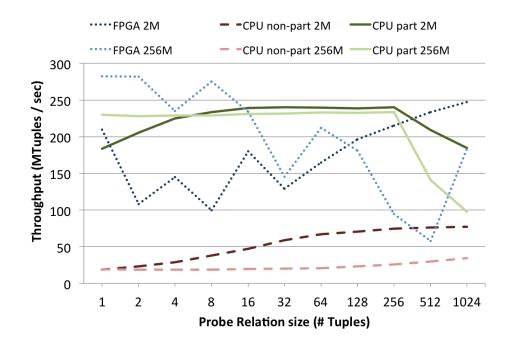

| 5.5  | Unique dataset throughput as the build relation size is increased                                                                                                      | 68 |

| 5.6  | Random dataset throughput as the build relation size is increased                                                                                                      | 68 |

| 5.7  | $Zipf_{-}0.5$ dataset throughput as the build relation size is increased                                                                                               | 69 |

| 5.8  | $Zipf_{-}1.0$ dataset throughput as the build relation size is increased                                                                                               | 69 |

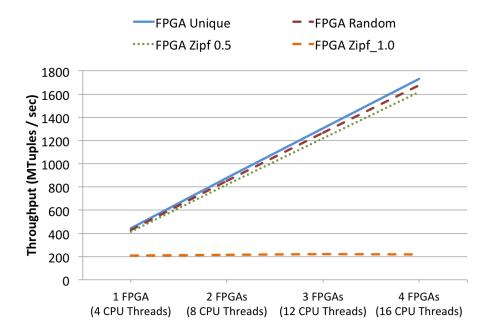

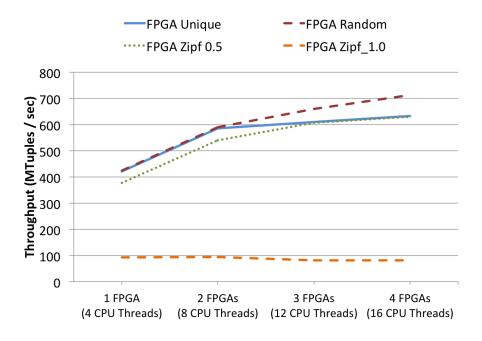

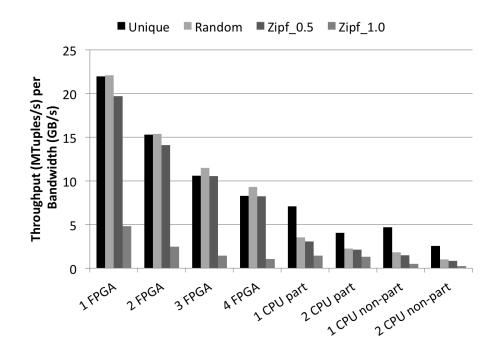

| 5.9  | FPGA throughput scaling. The Build Relation has $2^{21}$ , Probe has $2^{28}$ tuples                                                                                   | 72 |

| 5.10 | FPGA throughput scaling. The Build and Probe Relations both have $2^{28}$ tuples                                                                                       | 72 |

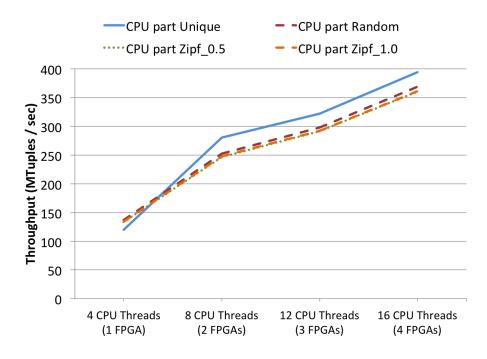

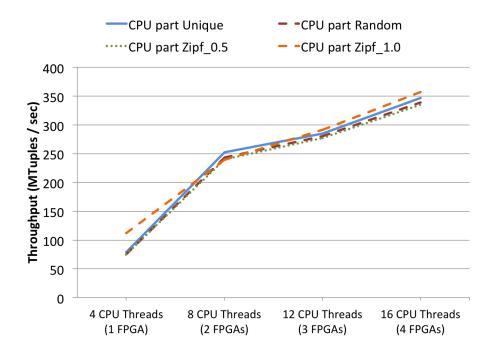

| 5.11 | Partitioned CPU throughput scaling. The Build Relation has $2^{21}$ , Probe has $2^{28}$ tuples                                                                        | 73 |

| 5.12 | Partitioned CPU throughput scaling. The Build and Probe Relations both have $2^{28}$ tuples                                                                            | 73 |

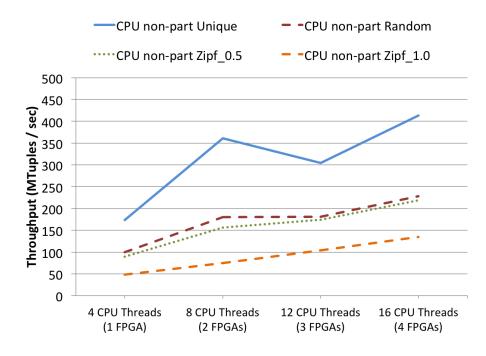

| 5.13 | Non-Partitioned CPU throughput scaling. The Build Relation has $2^{21}$ ,<br>Probe has $2^{28}$ tuples                                                                                       | 74 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.14 | Non-Partitioned CPU throughput scaling. Build and Probe Relations both have $2^{28}$ tuples $\ldots$                                                                                         | 74 |

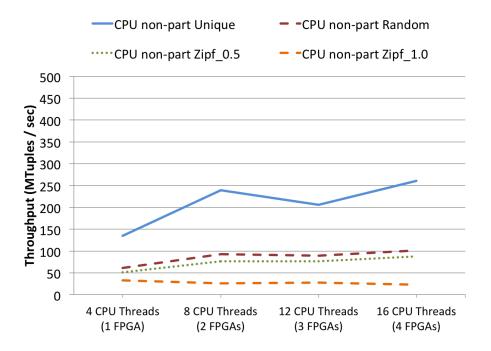

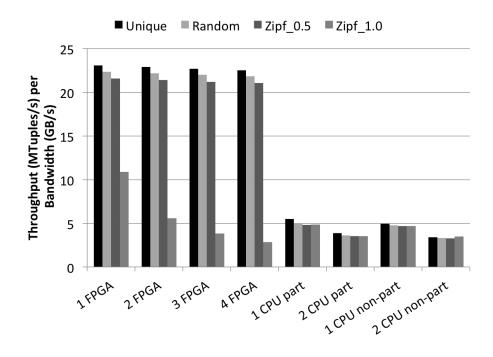

| 5.15 | Throughput efficiency when Build Relation has $2^{21}$ , Probe has $2^{28}$ tuples                                                                                                           | 76 |

| 5.16 | Throughput efficiency when Build and Probe Relations both have $2^{28}$ tuples                                                                                                               | 76 |

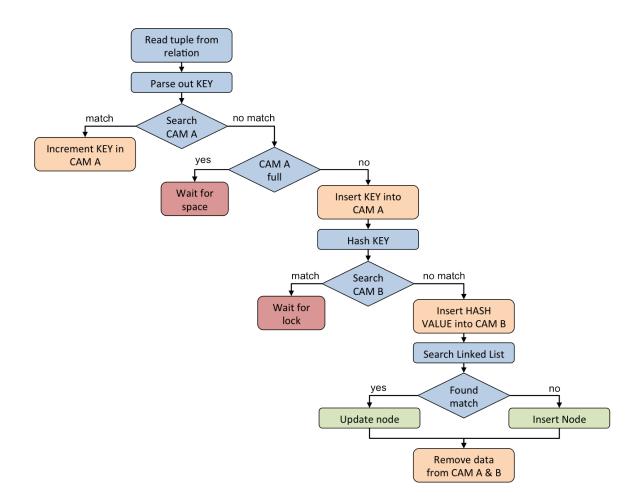

| 6.1  | A flow chart for an aggregation job through the kernel                                                                                                                                       | 80 |

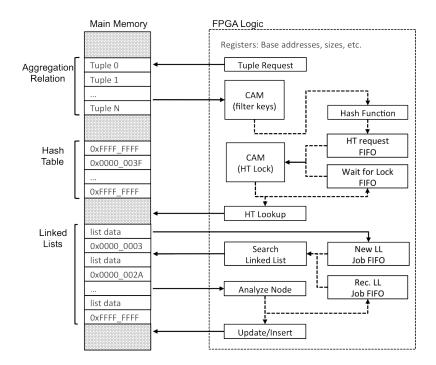

| 6.2  | The FPGA aggregation engine.                                                                                                                                                                 | 81 |

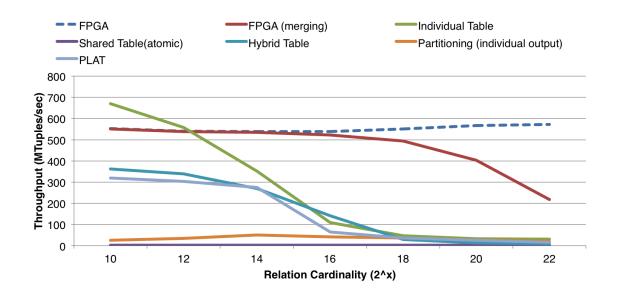

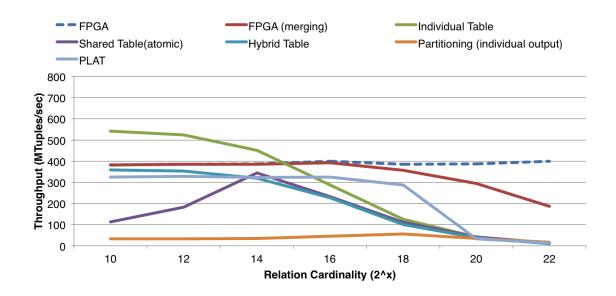

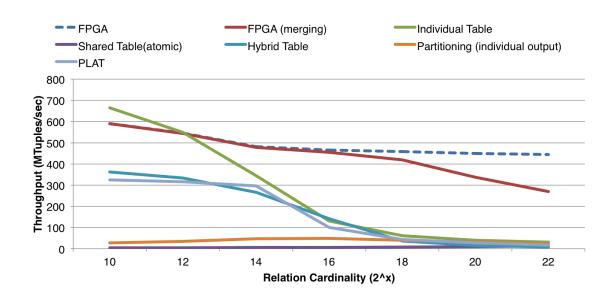

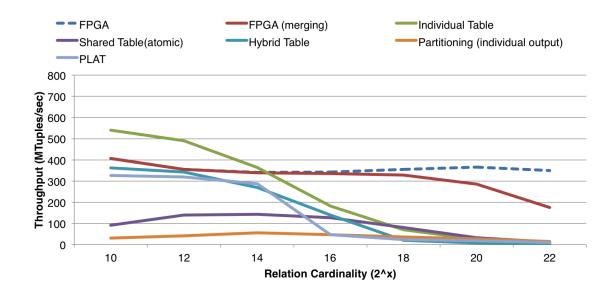

| 6.3  | Aggregation throughput for hardware and software approaches on the uniform dataset.                                                                                                          | 87 |

| 6.4  | Aggregation throughput for hardware and software approaches on the heavy hitter dataset                                                                                                      | 88 |

| 6.5  | Aggregation throughput for hardware and software approaches on the moving cluster dataset                                                                                                    | 89 |

| 6.6  | Aggregation throughput for hardware and software approaches on the self similar dataset.                                                                                                     | 89 |

| 6.7  | Aggregation throughput for hardware and software approaches on the Zipf 0.5 dataset.                                                                                                         | 90 |

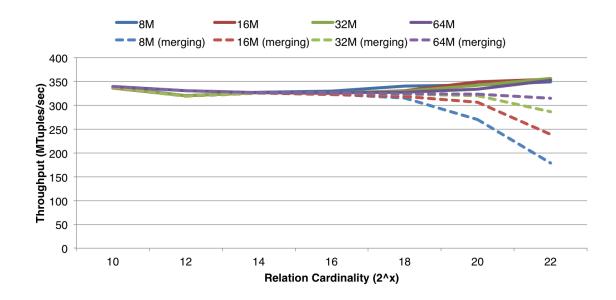

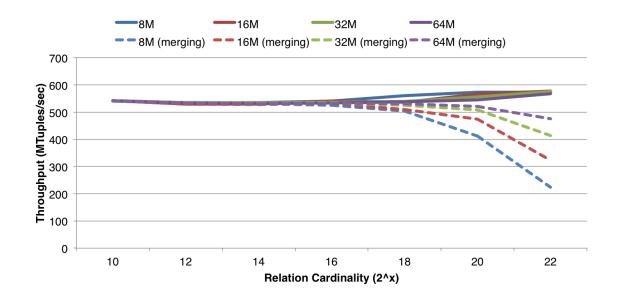

| 6.8  | Aggregation throughput for the FPGA on multiple relation sizes with<br>uniform key distribution. Results are shown without (solid line), and<br>with (dashed line) the merge operation       | 91 |

| 6.9  | Aggregation throughput for the FPGA on multiple relation sizes with<br>heavy hitter key distribution. Results are shown without (solid line), and<br>with (dashed line) the merge operation. | 92 |

### List of Tables

| 1.1 | Cache sizes for Intel Xeon Processors.                                                                                                                                                                                 | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Specifications for the UltraSPARC T series procesors                                                                                                                                                                   | 9  |

| 4.1 | FPGA utilization when varying the number of PEs                                                                                                                                                                        | 41 |

| 4.2 | An architecture specification for the various hardware used in SpMV com-<br>parisons                                                                                                                                   | 42 |

| 4.3 | Sparse matrix dimensions, and their throughput (DP GFLOPS) on our hardware accelerators. All benchmarks are taken from the UF Sparse Matrix Collection [67].                                                           | 43 |

| 4.4 | The memory storage requirement (MB) for each benchmark in the three sparse matrix formats. ELL pads all smaller rows to the length of the longest. When this is unreasonably long (> 10 GB) we mark its size as $N/A.$ | 44 |

| 5.1 | FPGA Resource utilization.                                                                                                                                                                                             | 77 |

### Chapter 1

### Introduction

Processor performance has significantly outpaced memory performance creating a latency gap. The major chip manufactures rely on multilevel cache designs to help their CPU processors maintain high performance. Caches leverage the spacial and temporal locality within an application to reduce the number of requests back to main memory. Frequently used values are stored closer to the processing core where the latency is much lower. The paradigm woks well for many applications, but there exists many important applications that do not work well on caches. We call them irregular applications, and by definition they have poor locality. Applications like sparse matrices, graphs, hash tables, etc. Developers working on these problem often try to remove irregularity or find ways to improve locality. They are contorting their problems to work with commodity processors. Table 1.1 shows a few processors Intel has released in its Xeon line. A trend emerges showing a continual growth in the shared L3 caches size. A similar pattern can be seen with other chip manufactures, and suggests that the caching model will be around for the foreseeable future.

Table 1.1: Cache sizes for Intel Xeon Processors.

| Processor | # of Cores | L2 cache size | L3 cache size |

|-----------|------------|---------------|---------------|

| E3-1290   | 4          | 256  KB       | 8 MB          |

| E5-4620   | 8          | 256  KB       | 20  MB        |

| E7-8880   | 15         | 256  KB       | 37.5  MB      |

Figure 1.1: Graph comparing the performance of single core processors to memory from the 1980's to the 2010's.

Figure 1.1 shows how the gap between CPU and memory performance haw widened since the early 1980s up until the 2010s. Modern processors can now generate 3 orders of magnitude more requests than the memory architectures can fulfill. This high request rate coupled with long access latencies means that processors spend the majority of their time idle. Caches hold data for common memory addresses closer to the processing units, which shortens the access time by limiting requests to global memory. CPU cores request data from the on-chip cache, and if the request hits the value is returned within a few cycles. Much faster than the thousands of cycles needed to fetch data from main memory. When a request misses, or needs to be written back, the architecture will issue a global request, but it is only done when necessary.

Applications with predictable memory access patterns are called regular applications. They often have high locality, and are well suited for caching platforms. Application with unpredictable memory access patterns are called irregular applications. They often have poor locality, but developers still try to make them work on commodity hardware (i.e. caching CPUs). Their workloads pull data from many different memory locations jumping around memory in seemingly random ways. Two examples of irregular applications that this thesis addresses are hash tables, and sparse matrices. Hash tables rely on good hashing functions that randomly distribute keys across a range of values. Two jobs that accesses the table one after the other can be reading or writing to vastly different physical locations in memory. This thesis uses hash tables in the context of database applications, but they are also used for filtering, virus detection, and ironically caching. Sparse matrices are used for graphs, economic models, and simulations. They are often large with few non-zero elements. Storage formats are very important for fast processing, but because the non-zero values can be spread erratically around the matrix these formats introduce irregularity. Sparse Matrix Vector multiplication (SpMV) is a common operation that is considered in this thesis.

Latency masking multithreaded architectures are an alternative to the caching model common in todays CPUs. Commercial machines like the Tera MTA [4], or Cray XMT [45] have been used in research labs since the early 1990s. They came from research architectures like the Denelcore HEP [60], and Horizon [36]. They provide direct hardware support to manage a large number of threads on a single core. When one thread issues a memory request it relinquishes execution, and it is context switched out for another. The thread is unstalled once the request has been fulfilled, and ut can continue executing. These platforms support enough threads to fully mask the memory latency. If all threads were to issue a request one after the other by the time the last request is issued the data for the first thread will be available. Identifying enough parallelism in an application is the hurdle preventing these platforms from becoming general purpose machines. The Sun UltraSPARC T series processors offer a middle ground between multithreaded, and cache architectures. They rely on caches, but also offer direct hardware support for 8 to 16 concurrent threads.

Field Programmable Gate Arrays (FPGAs) have shown massive speedup potential for a wide range of applications. Their ability to support highly parallel designs, coupled with their re-programmability have made them very attractive platforms for regular applications. Custom pipelined datapaths allow the FPGA to execute in parallel what could take thousands of operations in software. They can outperform software designs by 100x to 1000x all while reducing energy consumption. Image processing [17, 69], computer vision [33], data mining [57], bioinformatics [21, 22], financial analysis [56], and streaming databases [44, 47] are just a few of areas where FPGAs can been used.

Programmability, and ease of use deter many software developers from expanding into hardware development. FPGAs are notorious for complex designs, long debug cycles, and difficult verification among other things. Some if these difficulties are inherent to the platform. Hardware design is fundamentally different from software design, and require a shift in thinking. However, some of these issues can be alleviated by advances in hardware design tools. Major FPGA manufactures are actively developing High Level Synthesis (HLS) tools to help software software developers utilize their boards. The goal for HLS is to compile a high-level language (C, C++, Java, etc.) directly to RTL. These tools could gain more interest as industry continues to develop new heterogeneous architectures that incorporate FPGAs. Companies like Convey Computers [16], Maxeler Technologies [42], and Pico Computing [53] are already already offer them. Software APIs allow developers to easily interface software execution with their hardware. Depending on the architecture data can be offloaded to the FPGA similar to GPU platforms, or the FPGA can have direct access to global memory. FPGAs now have easy access to significantly larger memory spaces, which allows researchers to consider much larger real-world problems. However, the larger memories come at a cost of higher latencies. It is an open question, the best way to deal with longer memory access times. Caches are tried, and true for CPUs, but FPGAs offer a level of parallelism that can be leveraged by other methods.

This thesis considers how multithreaded architecture approaches to latency masking can be applied to the emerging FPGA memory latency issue. It starts by addressing the FPGA programmability issue. The Compiled Hardware Accelerated Threads (CHAT) tool is a C-to-VHDL compiler that can be used to create custom multithreaded circuits. It is intended to improve development time for application developers who are not familiar with hardware by generating synthesizeable VHDL. A standard FIFO interface is used to request, and collect data making the circuit platform independent. Developers only need to interface it with their memory architecture. CHAT is then used to develop a Sparse Matrix Vector (SpMV) kernel. Finally, this thesis considers how latency masking multihreading can be applied to common relation database operations. It presents the first end-to-end in-memory hash join implementation entirely on an FPGA. Custom multithreaded circuits are presented for the join's build and probe phases. A custom multithreaded circuit is also presented for aggregation.

### Chapter 2

### Background

FPGAs are traditionally used for streaming, and regular applications. They provide developers a highly parallel platform that can allocate tens to thousands of individual components, and run them all concurrently. Custom pipelined datapaths can be created for regular applications because by definition they have predictable memory access patterns. In this domain FPGAs have been used to achieve significant speedups over software designs [44, 72, 47, 33].

The FPGA community has began pushing to include reconfigurable fabrics in heterogeneous architecture. Often this required labs to build one-off custom machines to test their designs. However, since the mid 2000's commercial platforms have began to enter the market. This thesis looks to expand the application domain of FPGAs by considering applications that are not streamable. That do not have regular memory access patterns. We incorporate known techniques like latency masking and multithreadding. The FPGA now decides the memory locations it needs, instead of being simply pushed new values. We apply our designs to sparse matrix and database applications.

#### 2.1 Latency Masking Multithreaded Architectures

Multithreaded architectures provide direct hardware support to manage multiple threads on a single core. This differs from modern multiprocessor architectures that can execute multiple threads in parallel, but do so on independent cores. A single multithreaded core can handle 10s to 100s of concurrent threads while a single multiprocessor core handles only one, or two with "simultaneous multithreading" technology.

In parallel applications a multithreaded architecture can offer better core utilization than a multiprocessor architecture. Multiprocessor architectures use multitasking to interleave thread execution, which allocates time slots for threads to be scheduled into. In the simple case each thread is scheduled in round-robin fashion and given equal time to execute. However, if a thread is waiting for a resource (i.e. a cache miss) it will still be scheduled into a slot, and during this time the multiprocessor core will be idle. In contrast the multithreaded architecture has dedicated hardware resources for thread management. When a thread needs an unavailable resource it issues the request and goes into a stalled state. The multithreaded core is then free to execute non-stalled threads, and it only goes idle if all threads are stalled.

The extra hardware to manage thread states typically results in slower clock frequencies for multithreaded arheitectures compared to multicore ones. Longer pipelines are also common to manage the context switching, which could hurt performance on single threaded applications. However, this is more of a concern for sequential, than for parallel, applications.

#### 2.1.1 Full Latency Masking Architectures

Memory masking multithreaded architectures are not a novel idea. They have existed in some form since the Denelcore HEP [60, 30], and Horizon Architecture [36, 68] was proposed in the late 1980's, if not earlier. The idea was simple. Architects first measured how many clock cycles it took to fulfill a memory request. In the Horizon's case most requests averaged between 50 to 80 cycles, but almost all requests could be handled within 128 cycles. The architects then built custom processors to supported that many outstanding requests; 128 threads in the case of the Horizon. The processors had very fast context switching (one clock cycle) so that once a request was issued by a thread it could immediately switch to another thread. In this way the processor was fully utilized. In the worst case all 128 threads would issue a memory request. However, by the time the 128th request was issued the 1st request would be fulfilled, and the processor could continue running without interruption. This technique is called memory masking, and is integral to a multihreaded architecture's performance.

The Tera Computer Company released its Tera MTA [3, 4, 61] machine. Each of its processors could run at 300 MHz, and they could support 128 hardware threads. The only physical machine, that we are aware of, was installed at the San Diego Supercomputer Center [10] and it contained 4 processors. Therefore, It could support 512 threads. To lower the network traffic the MTA's instructions were fetched through a shared cache. However, it had no data cache and relied purely on multithreading to mask the memory latency.

The Tera Computer Company eventually merged with the research division of Cray. They continued to develop their multithreaded platforms; Cray MTA-2 (2002), and Cray MTA-3/XMT (2009). The MTA-2 was not widely adopted with one unit being sold to the United States Naval Research Laboratory. The XMT was much more successful in the research community [45, 71, 25, 15]. It supported up to 8,192 processors each running at 500 MHz, and they could share 128 TBs of RAM [20]. However, the largest machines sold only contained 64 processors, but the Cray research labs built and tested machines with up to 512 processors.

The main challenge for multithreaded architectures has been to extract enough parallelism to fully utilize their processors. Identify parallelism at compile time or runtime is a non-trivial task. This issue is a major factor preventing these architectures from being general purpose machine, and being more widely adopted. However, they have found use in the High Performance Computing industry because they perform well on irregular applications. Modern CPUs rely on efficient caching to sustain a high performance, and they struggle with the poor spatial and temporal locality inherent to irregular applications. However, memory masking is unaffected by the irregular access patterns.

Year Cores Threads/Core Cache Clock Freq (GHz) UltraSPARC T1 2005 4 3 MB L2 8 1.4UltraSPARC T2 2007 8 8 4 MB L2 1.6UltraSPARC T3 2010168 6 MB L2 1.67UltraSPARC T4 4 MB L320118 3.08 UltraSPARC T5 16 8 8 MB L3 2013 3.6

Table 2.1: Specifications for the UltraSPARC T series processors.

#### 2.1.2 Sun UltraSPARC T Processors

Starting in 2005 Sun produced a line of multithreaded multicore processors based on its UltraSPARC architecture; Table 2.1. The first processor (UltraSPARC T1) had 8 cores that could support 4 threads concurrently. Each core would context switch between active threads each cycle. This increased the overall latency of a single thread, but allowed the cores to be better utilized. Threads did not need to be from the same application, but cache performance improved if the threads were accessing the same data locations. Sun stedaly improved the architecture by adding more floatingpoint units, memory bandwidth, and increased the number of cores. However, when the UltraSPARC T4 was released they decreased the number of cores, but dramatically increased the clock frequency. This was a move to broaden their target audience by improving the single thread performance.

#### 2.2 Sparse Matrix Vector Multiplication

Sparse matrix Vector (SpMV) multiplication is a very important kernel to Scientific, and High-Performance computing. It has been widely studied for many years. Most research has focused on how to best store the data in memory; 1. minimize the area (memory footprint), and 2. improve a platform's memory accesses. Many formats have been proposed from the simple Coordinate (COO) or Compressed Sparse Row (CSR) formats to the specialized ELLPACK and Diagonal (DIA) formats. No one ideal format exists for all matrices on all platforms. In this section we present the common sparse matrix storage formats, and report the significant results and approaches for SpMV using hardware accelerators.

#### 2.2.1 Sparse Matrix Formats

The first concern of any sparse matrix application is how to best store the matrix in memory for the given architecture. Many different approaches have been proposed throughout the years, and we highlight the most general ones here. The

Figure 2.1: An example matrix that is used to show how different sparse matrix formats store data.

memory masking model is unconcerned with the access patterns, and therefore we are interested in finding the matrix format with the smallest memory footprint. We use the matrix in Figure 2.1 to help show how each format stores its data.

#### 2.2.1.1 Coordinate Format

The coordinate format (COO) is the most intuitive approach to storing a sparse matrix: for each non-zero element it stores its row position, column position, and value. As shown in Figure 2.2(a) each data point is stored in a separate array. Each non-zero element is assigned a unique index, and this index is used to access each array. In our example we assign the indices in sequential order, but this is not a requirement of COO. Non-zero elements can be spread randomly throughout the array so long as the row, column, and value share the same index within their respective arrays.

#### 2.2.1.2 Compressed Sparse Row

The compressed sparse row (CSR) is a natural extension to the COO format and is the most commonly used format. It stores all the column position, and value points in two separate arrays; just like COO. However, it saves memory by compressing the row position. As shown in Figure 2.2(b) some row positions are repeated multiple

| row  | s       |   |   |   |   |   | - |   | _ |   |   |

|------|---------|---|---|---|---|---|---|---|---|---|---|

| 0    | 0       | 0 | 0 | 1 | 1 | 1 | 2 | 2 | 2 | 3 | 3 |

| colu | columns |   |   |   |   |   |   |   |   |   |   |

| 0    | 2       | 3 | 4 | 1 | 2 | 4 | 0 | 1 | 4 | 2 | 3 |

| valu | values  |   |   |   |   |   |   |   |   |   |   |

| 2    | 7       | 6 | 5 | 8 | 1 | 1 | 4 | 9 | 5 | 7 | 6 |

(a) COO format

(b) CSR format

| value | s |   |   | <br>columns |   |   |   |  |

|-------|---|---|---|-------------|---|---|---|--|

| 2     | 7 | 6 | 5 | 0           | 2 | 3 | 4 |  |

| 8     | 1 | 1 | 0 | 1           | 2 | 4 | * |  |

| 4     | 9 | 5 | 0 | 0           | 1 | 4 | * |  |

| 7     | 6 | 0 | 0 | 2           | 3 | * | * |  |

<sup>(</sup>c) ELL format

Figure 2.2: COO, CSR and ELL sparse matrix storage formats for the example matrix in Figure 2.1.

times. Instead of storing repetitive values the CSR format uses a  $row_p tr$  array, which only points to the first element of each row. To be functionally correct the column, and value array must be sorted by row such that all elements in row i are placed before any element in row i + 1.

The compressed sparse column format (CSC) is almost identical to CSR, but instead of compressing the row array it compresses the column array. The CSC format is less widely used because its workloads are harder to distribute evenly. SpMV has one output per row (not per column), and with CSR each output can be computed within a single processing element (PE). CSC would require synchronization across multiple PEs to prevent race conditions.

#### 2.2.1.3 ELLPACK

The ELLPACK (ELL) format rose in popularity with vector processors. Peak performance required each processor to run the same workload. To achieve this ELL would zero pad the smaller rows until they were the same length as the largest. Figure 2.2(c) shows how our example matrix would be stored in ELL format. Because all rows are the same length the ELL only requires 2 arrays; one for the columns, and one for the values. The column position for zero padded data can have any value, but it should be less than the number of columns in the matrix to avoid out-of-bound memory accesses.

ELL is not as general a sparse matrix format as COO or CSR. It is only useful when all rows within a matrix have a small variance on the number of non-zero elements per row. If one, or a few rows are much larger than the rest it can cause too much zero padding. The extra work from processing zero values would eliminate any of performance gains.

#### 2.2.1.4 Hybrid format

A hybrid (HYB) format was proposed by [8] for GPU accelerators. It splits the matrix storage between the ELL, and the COO formats. Data that can be reasonably (low zero padding) stored in ELL will be, and the remaining values are stored in COO format. This method both reduces the zero padding caused by longer rows, and it still allows the GPU to benefit from ELL's structured memory; at least for part of the computation.

#### 2.2.2 FPGA Approaches

The FPGA architecture is well suited to streaming application paradigms, and as such much FPGA research has focused on streaming applications. Sparse Matrix Vector multiplication (SpMV) is no exception. Most published research has focused on removing all irregularity for SpMV, and then using an FPGA to improve performance. The most common approach is to store the vector (i.e. the point of irregularity) in on-chip BRAMs. Allowing each vector accesses to be handled in one cycle regardless of the access pattern. Modern high-end FPGA do have large quantities of BRAMs on-chip [76], but they are at most a few megabytes. Not reasonable for the high performance computing environment where SpMV matters.

Substantial SpMV work has focused on how to best implement the floatingpoint Multiply Accumulate (MAc) circuit. Floating-point multiplication takes around 12 cycles, and addition can take up to 27 cycles. Managing states during the accumulation is non-trivial because row lengths can vary drastically even within the same benchmark. Adder tree structures [64, 80] with feedback loops can be used to handle multiple row elements in one cycle. However, the number of non-zero elements per row must be larger than the number of channels. Otherwise the design is underutilized, and loses performance. Other approaches have considered statically assigning the partial dot products to multiple processing engines [19, 58]. Here a control unit manages the communication, and ensures proper execution within the design. However, the number of concurrent rows in the MAc circuit is limited to at most two at any given time. However, multiple MAc circuit can be placed on the FPGA to support more rows in parallel [78]. [24] developed an accumulation reduction circuit that supports an arbitrary number of rows, and can read a new value every cycle. However, all data from one row must enter the circuit before any data from another row enters. A control unit arbitrates the data flow between the floating-point addition unit and temporary buffers.

The emergence of heterogeneous FPGA platforms by Convey Computers, Maxeler, and Pico has allowed researches to easily implement their designs on real world hardware. A custom SpMV personality was develop for the Convey HC-1 [49]. The design caches memory requests locally in case data needs to be reused, but because of the irregular nature of SpMV it could only sustain 40% of the peak performance.

#### 2.2.3 GPU Approaches

GPUs are large vector machines that rely on SIMD parallelism to achieve peak performance. The have a fixed architecture that was developed to quickly process graphics applications. However, with the introduction of the CUDA programing API in the late 2000's GPUs have begun branching further into high performance computing applications. Because the hardware is not customizable much of the research has focused on how to best reshape the data to best utilize the platform. Performance depends on either having a lot of data executing on the same instructions (SIMD), and/or coalescing the memory requests to fully utilized the memory bandwidth. GPUs often have a major memory bandwidth advantage over CPU, and FPGA platforms. The Nvidia Tesla K20 has 208 GB/s of bandwidth, and the newer Nividia Tesla K40 has 288 GB/s of bandwidth.

The ELLPACK sparse matrix format was developed to run sparse matrix applications on early vector processors, and is a common starting point for many SpMV GPU ports. Slice ELLPACK [46] partitioned adjacent rows together in strips, and each strip was stored as its own ELLPACK matrix. The strips could be reordered by size to improve the GPU's SIMD performance. R-ELLPACK [70] reordered the matrix such that rows accessing the same vector locations would be closer to each other, and therefore improving the locality. The Hybrid (HYB) [8] format stores most of the matrix in ELLPACK, but some elements (in rows where the number of non-zero elements is larger than the average) are stored in COO format.

There is no "one best" format for SpMV on GPU. If the data is random a generic format like CSR or COO may be best. If the data has dense areas spread throughout the matrix a blocked format may be best. If the data is structured a custom format may be best. The research community have empirically shown this to be true [7, 40]. The HYB format gives bester results, on average, when the matrix is unoptimized [8], but CSR has been shown better when the rows are first reordered into clusters [52]. The clSpMV tool [62] is an OpenCL SpMV solver that analyzes the matrix and chooses a format from one of three distinct categories (Diagonal, Flat, or Blocked).

#### 2.3 Accelerating Database Operations with FPGAs

Data analytics is a driving force behind many businesses. Begin able to quickly identify a custom base, and their needs is paramount in the fast paced and competitive environment. Commercial platforms like IBM's Netezza [31] and Teradata's Kickfire [65] offer FPGA solutions for Database Management Systems. They cover a full range of database operations from selection and projection, to joins and aggregation. They work in conjunction with software to analyze workloads and run queries on the best available resources (software or hardware). Academia is also working to improve these systems with new and innovative hardware designs.

#### 2.3.1 Query Processing & DBMSes

Academia has developed tools that compile quires down to hardware circuits using custom library components. The Glacier library [48] is a set of specialized building blocks that can be combined to make an engine for streaming queries. However, it is only practical for common queries that have a high re-use rate. The synthesis time to build an engine is high, and needs to be amortized over many runs to be practical. The technique has been shown useful for event processing systems like high frequency trading [56]. The Q100 [75] architecture is a fixed platform with many ASIC database processing units. A query stream is scheduled through the necessary units. Resources may go unused for a given query, but the platform avoids long build times.

Netezza [31] is a complete DBMS that uses FPGAs as a filter between the hard disk and main memory. Customizable queries are sent to the FPGAs which utilize their close proximity to the hard disk to quickly filter relations before sending them to memory. The platform tries to reduce the costly data transfers from disk to main memory [23]. The trade off for this approach is that all requests must start on disk. In-memory databases cannot leverage the addition hardware FPGAs.

Another full DBMS, Kickfire [65], uses FPGA hardware accelerators connected through either PCIe or hypertransport. It defines various database operations as HARP logic [35] that consists of a hardware circuit and a large memory systems. All queries are analyzed by Teradata's C2 software, which decides if it should handle the job itself, send it back the the DBMS, or offload it to HARP logic. The customized hardware supports many common relational database operations [12, 29, 43]

#### 2.3.2 Join Operations

The stream join operation is a common in on-line algorithms where a complete result is not needed. The algorithm is only concerned with joining tuples within a window of data, and because of this the entire window can be streamed to a processing element and handled. This differs from the traditional relational join which has to find all matches between two relations. The streaming nature made it an ideal target for FPGA acceleration. The Handshake Join algorithm [66] treats the two relations as athletes congratulating each other after a match. Data streams through the FPGA in opposite directions. Two windows of data (one for each relation) are held entirely on the FPGA, and custom hardware comparators look for matches. When a match is found the tuples are joined and output. The design can be easily extended to larger window sizes as the FPGA chips continue to grow in resources, or multiple FPGAs can be chained together.

Joining tuples can be an issue for the design. When multiple tuples match their outputs need to be serialized through a limited number of channels. However, the Handshake Join implementation has been extended to include an admission control unit [50, 51]. The unit stalls the stream until the FPGA has enough resources available to continue. This throttling of inputs is important on applications that join a lot of tuples.

The relational join operations is very important to OLAP workloads, and the push for real time analysis has lead researchers to explore FPGA designs. Sort-merge join, and hash join are the most common implementations. In software hash join has been shown to outperform sort-merge [1], but a switch has been predicted as CPUs increase their SIMD register sizes [5]. Counter intuitively the FPGA community has focused their efforts on sort-merge implementations [55, 75, 14]. The reason for this is simple. FPGAs excel at streamable regular applications like merging sorted lists. Therefore the trick is to develop a streamable sorting algorithm in hardware, which can be done with sorting networks [37, 32].

### Chapter 3

# CHAT - Compiled Hardware Accelerated Threads

Designing a hardware accelerator is a difficult task. Not only are the platforms significantly different from the traditional Von-Newman model, but so too are the development cycle and tools. The learning curve is often steep even for classically trained software developers. The divide is so drastic that developers who write hardware accelerators often do not refer to themselves as software developers. In this section we present the CHAT tool to help bridge the gap between hardware and software development.

The CHAT (Compiled Hardware Accelerated Threads) tool is designed to assist developers with implementing irregular applications on FPGAs. Ease of programmability has historically been a roadblock preventing many developers from exploring FPGA design options. A steep learning curve coupled with a long debug cycle has made the startup costs too high. However, there are many performance and energy benefits to be gained from using reconfigurable custom hardware. CHAT attempts to lower the startup costs by allowing developers to describe their circuits in a high level language, and simply compile the design into a Hardware Description Language (HDL). We are not alone in this research. Many academic and industry initiatives are attempting to address this issue with High Level Synthesis (HLS) tools. Among the most mature are Vivado HSL[77] (formerly AutoESL[79]), Altera OpenCL (AOCL)[2], ROCCC[72, 54] and LegUp[13, 39].

HSL tools make differing assumptions about their target applications, their target architectures, and their design goals. These limitations are necessary because the nature of hardware development is so different from that of software development. FPGA accelerators are typically used for regular/streaming applications where the data has a high spatial and temporal locality. The FPGA's highly parallel nature allows it to execute many operations concurrently for a massive performance increase. The typical HLS tool targets these regular applications, but it is often at the expense of irregular application support.

Vivado HLS, and AOCL are developed by Xilinx and Altera, respectively, and therefor designs are tightly coupled to their company's FPGA platforms. Furthermore, both these tools only generate designs where all relevant data is stored local to the FPGA chip. Doing so allows the tools to handle both regular and irregular applications because all data accesses can be handled in one cycle. However, major restrictions are placed on the size of problem sets. The largest FPGAs currently available only offer a few MBs of local storage, and many interesting problems often require many megabytes, or more of data.

ROCCC and LegUp both assume an off-chip memory source, which makes them more generalized in the size of problems they can solve. However, ROCCC and LegUp make different assumptions about their target architectures. ROCCC is very general and generates VHDL that is synthesizes on any platform. Designs can be unrolled, and the number of I/O memory channels are customizable. In contrast LegUp generates Verilog specifically for Altera boards, and designs are limited to two memory channels. Therefore, LegUp kernels cannot sustain good performance on high bandwidth machines. These tools also make different assumptions about their target algorithms. LegUp is very general and can interface with a TigerMIPS soft-core processor to handle operations that are unreasonable as digital circuits. ROCCC always assumes streamable regular applications which allows it to generate highly optimized kernels. These difference arise because both tools were designed with different goals in mind. ROCCC builds faster, and scalable designs for specific applications, and LegUp supports a wider range of applications.

CHAT is a complement to the ROCCC Compiler. Like ROCCC it is platform and memory independent allowing for easy porting to emerging FPGA architectures; Convey Computers[16], Pico Machines[53], Maxeler Technologies[42], etc. However, where ROCCC generates highly optimized kernels for streaming applications CHAT generates less optimized, but still highly efficient, kernels for irregular applications.

#### 3.1 Taxonomy of Irregular Applications

FPGA accelerators are not a general purpose solution for any software application with poor performance. They are specialized platforms with a set of features that are well suited to particular applications. Historically, this meant streaming and compute bound applications. However, FPGAs also offer potential benefits for highly parallel irregular applications. Modern CPUs rely on good caching algorithms to maintain performance, but by definition irregular applications have poor spatial and temporal locality. Multithreaded architectures were proposed [36, 68, 4, 3, 20] as a possible solu-

Figure 3.1: A taxonomy of irregular applications where the number of threads and the workload sizes are, or are not deterministic.

tion, but their design was not reasonable for general purpose computing. FPGAs offer a middle ground where CPUs can offload certain jobs to custom multithreaded FPGA accelerators.

The multithreaded paradigm requires sufficient parallelism within an application to fully mask long memory latencies. Therefore, not all irregular applications are reasonable on such architectures. Here we classify the different types of irregular applications could have. We also describe how these applications may look within C code, and explain the various FPGA constructs needed to implement these applications as digital circuits.

The CHAT tool defines a thread as any output result to memory, and every application will have at least one. Distinct threads can access the same memory location, or even overwrite previous results. CHAT applications can fall into one of 4 classes as shown in Figure 3.1. At runtime the application's total number of threads can be deterministic, or not. In addition each thread can have a deterministic, or nondeterministic number of reads and writes.

Applications where the number of threads are deterministic can be optimized to reduce, or eliminate redundancy. For example consider an application where Nthreads read from the same memory location. The compiler can merge them into a single request, and propagate the value to the N datapaths eliminating N-1 requests. Applications with a non-deterministic number of threads cannot merge datapaths so they need constructs to prevent, or limit redundancy. For example consider traversing a graph with breadth-first search. Each node in the graph is treated as a thread. New threads are continually generated during the traversal. However, Two nodes, A and B, could both point to the same third node C. Without synchronization two threads would be generated for node C, and performance would begin to decrease exponentially as more redundant threads are created and processed.

A single hardware Processing Engine (PE) is assigned a thread, or multiple threads. To improve a design's parallelism and performance multiple PEs can be used in the hardware kernel. However, doing so requires scheduling of threads to the available PEs, and this can be done statically or dynamically depending on the type of application. If an application's workload (requests per thread) is deterministic the scheduling can be optimized at compile time. For example, in the simple case all threads have the same workload. Therefore, the datapath can assign threads to PEs in round-robin fashion. If an application's workload is non-deterministic then the hardware needs a runtime Thread Management Unit (TMU). Each PE uses flags to signal when it can handle a new job. The TMU queues up jobs, and assigns them dynamically as PEs become available. This dynamic scheduling allows long jobs to occupy a single PE while the other PEs handle many smaller jobs.

## 3.2 The CHAT Compiler

CHAT is a C to VHDL compiler for irregular applications. It is based around research done for the ROCCC [72, 54] tool, but extends the infrastructure to support irregular applications. CHAT analyzes kernels at two levels. First high-level analysis builds a Data Flow Graph (DFG) using the SUIF 2.0 toolset [74] and generates an intermediate representation. Next low-level analysis creates a Control Flow Graph (CFG) using the LLVM compiler [38] and generates the VHDL design.

Algorithm 1 C code for a simple irregular application.

```

void passthrough (int *A, int *B, int *C, int length) {

int i;

for (i = 0; i < length; ++i)

C[i] = B[ A[i] ];

}</pre>

```

#### 3.2.1 Hi-CIRRF in SUIF 2.0

High-level analysis reads the hardware kernel described in the C language. However, because C was developed as a software language, not all its constructs make sense in a hardware context; e.g. Dynamic Allocation, Recursion, pointer arithmetic, etc. Therefore, CHAT only supports a subset of the language. For example arrays are treated as streams of data. They occupy contiguous blocks of memory, but they can be randomly accessed. CHAT does not currently support pointer chasing. Rows for multi-dimensional arrays are assumed to be stored one after the other. Constant values are stored in hardware registers. Variable values are temporarily stored in registers,

# Algorithm 2 Sample of the CIRRF generated by CHAT.

• • •

```

CHAT_{init_inputscalar(length)};

```

```

CHATInputStreams(A,B);

```

. . .

```

for (i = 0 ; (i < length) ; i = i + 1) {

CHATInputFifo1_0(A, i, suifTmp2, 0) ;

CHATDataFifo1_2(B, suifTmp2, suifTmp3, 0);

suifTmp4 = CHATIntToInt(suifTmp3, 32) ;

...

CHATOutputFifo1_2(C, i, suifTmp4, 0) ;

CHAT_output_C_scalar() ;

CHATOutputStreams(C) ;

}</pre>

```

and the values are moved around the hardware datapath. Branches in execution will generate multiple datapaths that are filtered through a multiplexer.

The goal of high-level analysis is to identify the hardware components, and create a dataflow graph (DFG). New passes are added to the SUIF 2.0 [74] compiler to achieve this goal. We use Algorithm 1 to highlight the major steps in CHAT, but each step may require multiple passes in SUIF. First CHAT's high-level analysis will identify 3 data streams (A, B, and C), and one registered value (*length*). Two streams will be identified as input streams (A, and B) because they read values, and one stream will be identified as an output stream (C) because it is written too. CHAT does not support streams that both read, and write. Temporary registers are created, called 'suifTmps', to direct the datapath. Finally, the CIRRF [27] is output. A sample of the CIRRF file is shown in Algorithm 2.

User inputs are used to further customize the Hi-CIRRF pass. Parallelism can be increased by unrolling the for loops which will duplicate the datapaths in the DFG. Doing so could cause redundant hardware. CHAT will analyze the unrolled design, and merge components working on the same exact data.

#### 3.2.2 Lo-CIRRF in LLVM

CHAT's low-level analysis reads the DFG from the Hi-CIRRF pass. It creates a control flow graph (CFG), and then generates the synthesizable VHDL. Thread management is a key consideration during this phase. Each thread must maintain its state locally on the FPGA, but because of the FPGA's parallelism multiple threads can be changing states in the same clock cycle. All thread data is stored on-chip in BRAMs, which are configured as FIFOs. This can be done because CHAT assumes all memory requests are returned in-order. However, the compiler could be extended to support out-of-order memory requests. In this case a design would implement CAMs instead of FIFOs.

The Lo-CIRRF compilation is implemented by a number of different passes in in the LLVM [38] compiler. Here we give a high level overview of what happens, but just as in the previous section each step may require many different passes. First the compiler assigns each CIRRF statement into their own basic block, which allows parallel scheduling for non-sequential operations. A element must block until its dependencies have valid data, but other elements are free to execute. Buffers are placed throughout the datapath to limit stalling, and alleviate back-pressure. Paths requiring memory requests will also be padded with large buffers to allow multiple outstanding requests.

Portability is another goal for the CHAT tool. Designs assume nothing about the FPGA board it will be implemented on. However, the compiler does create hooks for developers to leverage for performance. They are important for complex operations (i.e. division, or floating point operations) where custom DSP blocks are often available, but are usually board dependent. The compiler will generate simple FIFOs for small buffers, but for larger buffers the compiler provides hooks to the developer. Custom IP cores can therefore be used to improve timing, and area utilization.

## 3.3 Simple Irregular Applications

In this section we use the CHAT tool to build two simple irregular applications. We also show throughput performance results on a Convey HC-2ex machine. Both are summation circuits. The first design uses a 1-dimensional stream as the index, and the other design uses a 2-dimensional stream.

```

void summation(int **A, int *B, int *C, int m, int p) {

int i, j;

for(j = 0; j < m; ++j)

for(i = 0; i < p; ++i)

C[j] += A[j][B[i]];

}</pre>

```

#### 3.3.1 One Dimensional Indexing

We implement the basic irregular application expressed in Equation 3.1. The actual CHAT code for this equation is shown in Algorithm 3. In this design array B has a regular access pattern, which iterates from 0 to m. However, array A has an irregular access pattern because it uses values from B in its index. The values in B can be anything.

$$C[m] = \sum_{i=1}^{p} A[m, B[i]]$$

(3.1)

The CHAT tool will generate two input controllers (A, and B), and a single output controller (C). It will also generate two counter components for variables i and j. Finally the compiler will create a summation datapath. Data from the i counter will be used for the B input controller to issue memory requests. As the results return they will be routed to the A input controller where they are combined with the j counter for a new memory request. The memory requests for A are routed into the summation datapath, and once p elements have been accumulated the result is sent to the C output controller. The output controller writes the final result to memory. The design requires only three memory channels, and should be replicated to utilized the Convey's 16 memory channels. Replicating the design is done through the compiler by unrolling a for loop. Unrolling the inner for loop increases thread level parallelism. Each cycle a single thread issues multiple request, which go into a summation tree. Unrolling the outer for loop increases application level parallelism. Each cycle multiple threads are executing in parallel. However, this also means the same B values can be used by all A controllers. The compiler identifies this, and generate a single B input controller, and routes the value to all A input controllers.

#### Algorithm 4 Summation kernel with a 2-dimensional index stream.

void summation(int \*\*A, int \*\*B, int \*C, int m, int p) {

int i, j;

for(j = 0; j < m; ++j)

for(i = 0; i < p; ++i)

C[j] += A[j][B[j][i]];</pre>

#### 3.3.2 Two Dimensional Indexing

}

We also implement an irregular application that is indexed by a 2-dimensional stream as shown in Algorithm 4. CHAT will optimize this kernel very differently than the 1-dimensional kernel. The B input controller will provide different values for each row in A, and therefore it cannot be merged into a single shared memory channel. Multiple B input controllers must be created for each A input controller.

Figure 3.2: FPGA components for the 1-dimensional kernel as generated by CHAT. Notice that the B input controller is optimized to shared its data between all A input controllers.

# 3.4 Experimental Evaluation

In this section we show how the CHAT tool can be used to generate kernels for real world architectures. We implement both kernels on a Convey HC-2ex, and explain the our design considerations.

#### 3.4.1 Convey HC-2ex Implementation

The CHAT tool has no limit to how many times a design can be unrolled, but in practice architecture limitations must be considered. The Convey HC-2ex used here uses Xilinx Virtex-6 760 boards with 16 memory channels per FPGA. The summation circuit is very space efficient so our design is memory channel limited, but larger designs may be area limited. The developer must consider these limitations when using CHAT. To best utilize the memory channels we must consider how CHAT will optimize the

Figure 3.3: FPGA components for the 2-dimensional kernel as generated by CHAT. Notice that the B input controller cannot share its data between separate A input controllers.

1-dimensional kernel. The layout of components is shown in Figre 3.2. Each input memory controller (A and B) will continually request data, and therefore need their own dedicated channel. The design will have only a single B controller which is shared. Each output memory controller only has a single valid request per row, and therefore it is not continually writing results. Therefore, the C controllers can be interlaced into a single channel. Considering the HC-2ex's restrictions we can unroll the design 14 times. One memory channel is used by the B controller, another channel is used for all 14 Ccontrollers, and 14 channels are used for 14 A controllers.

CHAT cannot optimize the 2-dimensional kernel to share a single B input controller. The layout of components is shown in Figure 3.3. All controllers for Aand B still continually request data, but now there are multiple B controllers. The C controllers can still be interlaced into one memory channel. Therefore, the design can only be unrolled 7 times for the Convey HC-2ex. 7 channels are used for the

Figure 3.4: FPGA vs CPU runtime performance comparing sequential and random data on a 1-dimensionally index array. Dataset sizes range from 1 million 8-byte integers to 10-billion 8-byte integers.

B controllers, 7 channels are used for the A controllers, and 2 channels are used to interlace the C controllers.

Our experiments compare the performance of 2 FPGAs to one Xeon E5-2643 CPU. We use two FPGAs because the summation kernels presented here are memory bounded, and each FPGA only has 19.2 GB/s of bandwidth, which is much lower than the CPU's 51.2 GB/s. Using 2 FPGAs doubles the bandwidth to 38.4 GB/s, which is still lower than the CPU.

#### 3.4.2 Runtime Performance

To test feasibility we gather runtime results on two different datasets. First we use purely sequential data to get a base-line measurement. This will yield the best performance for the cache dependent CPU tests. It also ensures the FPGA memory accesses will have few bank conflicts, which should minimize any stalling. The second

Figure 3.5: FPGA vs CPU runtime performance comparing sequential and random data on a 2-dimensionally index array. Dataset sizes range from 1 million 8-byte integers to 10-billion 8-byte integers.

datasets uses randomly generated values because we are interested in performance on irregular applications. Results are reported for both the 1-dimensional kernel (Figure 3.4) and the 2-dimensional kernel (Figure 3.5).

Looking at results for the 1-dimensional kernel, Figure 3.4, we can see that performance is comparable for sequential data. This is occurs for two main reasons. First sequential data has excellent spacial locality. Second this is a memory bounded application, and the bandwidth for the FPGA(38.4 GB/s) is comparable to the CPU(51.2 GB/s). The CPU does enjoy slightly faster performance, but it comes from the 33% higher bandwidth, and its order of magnitude faster clock frequency. However, on random data we begin to see the advantage of multithreading. The random data loses all spacial locality, and the CPU performance drops accordingly. Multithreading performance relies on an application's parallelism, and therefore the FPGAs performance is unaffected by different data. The results show that the FPGA can sustain about 2.4x speedup over software in spite of it's slower clock and smaller bandwidth. Results are similar for the 2-dimensional kernel, Figure 3.5. The sequential data is comparable for both the FPGA, and the CPU results. The FPGA's runtime on random data is only about 2x faster than the CPU. Performance drops on both architectures because the FPGA can no longer share hardware for the *B* array, and the CPU loses the temporal locality of the *B* array.

# 3.5 Conclusion

In this section we presented the CHAT HLS compiler for irregular applications. Unlike the current HLS tools being developed by industry and research labs it focuses on large applications with poor temporal and spatial locality. The tool can generate custom hardware kernels which use a memory masking multithreaded model to efficiently utilize the FPGAs bandwidth regardless of the memory access pattern. Results showed around a 2x speedup over software on two irregular kernels. 2x is not usually a significant performance increase for FPGA applications which have shown speedups of 100x to 1,000x. However, our results are on memory bounded not compute bounded applications. We achieved our 2x speedup while yielding a 33% bandwidth advantage to software.

# Chapter 4

# A Multithreaded Sparse Matrix Mulitplication Kernel

Sparse Matrix Vector Multiplication (SpMV) is a memory bounded problem that often has a poor Flop/Byte performance. The operations are simple (multiplication, and addition) so throughput depends on how fast the Processing Engines can receive data. Even though the algorithm is simple computationally, it is a very important application to many fields in computer science (i.e. Scientific Computing, HPC, etc). In this chapter we explore how multihreading can be used to implement and improve this common operation. The first concern addressed is how the sparse matrix can be best store in memory to minimize the number of memory accesses. Then based on the matrix format a custom multihreaded memory masking kernel is generated by the CHAT tool. Finally, the hardware kernel's limits and scalability are explored in the results section. The performance is also compared with state of the art approaches in software, and GPU platforms.

## 4.1 A Multithreaded Sparse Matrix Kernel

We use the CHAT compiler to generate a multithreaded SpMV kernel. Our design is based around the Compressed Sparse Row (CSR) format from Section 2.2.1.2. Two design choices were important in selecting CSR. First it requires a minimal amount of memory while being able to support any matrix. ELLPACK uses less memory on some matrices, but is not a general purpose solution. Second CSR can be easily broken into independent threads.

#### Algorithm 5 CHAT SpMV kenrel source code.

#### 4.1.1 SpMV Kernel Code

Sample code for a SpMV kernel is shown in Algorithm 5. This is, line for line, the code used by the compiler. All arrays are treated as streams of data into the FPGA. Most (*row*, *val*, *col*) are accessed in a streaming (regular) fashion. However, the *vec*  array is accessed by the *col* array therefore is treated as an irregular accesses. Thread workloads are determined by the two adjacent elements in the *row* stream. Threads are issued in order, but they are not required to have the same workload size. Thus the *out* array can write to memory out-of-order. The kernel writes whenever a thread finishes. The designer can unroll the outer for-loop to generate multiple PEs yielding higher parallelism.

#### 4.1.2 Processing Element

The bulk of the SpMV's work is done by the processing element (PEs). These engines operate independently and the number of PEs is limited by the resources available on the FPGA (i.e. number of memory channels). Each thread assigned to a PE will generate one output, which is the sum-of-products for a row. Thread states must maintain the running sum, and the start/end positions for the memory requests. As requests are fulfilled the data is sent to a summation unit which produces the final sumof-products. Each PE manages the requesting, multiplying, and summing for multiple threads (rows) concurrently.

The PE's component layout is shown in Figure 4.1. Each PE manages memory requests to the column, value, and vector arrays. Our implementation is for the Convey HC-2ex machine, which supports in-order memory requests. The physical accesses to memory are fulfilled out-of-order, but the HC-2ex uses a custom crossbar to reorder the data before returning it to the PE. Thread states can therefore be stored in FIFO buffers.

A PE will uses a busy flag to stall new threads from entering the datapath. Once a thread job is assigned to a PE the flag is asserted until all initial requests for

Figure 4.1: Each PE is assigned a thread. It requests the necessary data (Column, Vector, and Value) from global memory. Returned data values are pushed through the multiply pipeline, and summation unit.

data have been made. Because threads can be small they may not require enough data to fully mask memory. After all the initial requests have been made a new thread job will enter the PE, and multiple requests for different threads can be outstanding at any given time. Workloads are balanced across PEs because new jobs are not assigned until the PE is ready. A long job will prevent only one PE from getting new jobs while other PEs are handling many smaller jobs.

FIFO buffers within each PE are large enough to support all the outstanding requests. As memory returns the data for the column array it is used to generate the memory requests for the vector array. The data returned for the value array is held in buffer until the corresponding vector request is fulfilled. As data is returned from memory it is buffered in the Value and Vector FIFOs with its thread ID (row index). The summation unit uses the thread IDs to manage concurrent threads. Our compiler