# UC Irvine UC Irvine Electronic Theses and Dissertations

**Title** Efficient Low Power Headphone Driver

Permalink https://escholarship.org/uc/item/49f174wt

Author Abdelfattah, Khaled

Publication Date 2019

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, IRVINE

#### Efficient Low Power Headphone Driver

#### DISSERTATION

# submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

#### in Electrical Engineering

by

#### Khaled Abdelfattah

Dissertation Committee: Professor Michael Green, Chair Professor Ahmed Eltawil Professor Nader Bagherzadeh

© 2019 Khaled Abdelfattah

### **DEDICATION**

То

my beloved wife Rania Sultan whose support was the most important major element to my success in getting this work accomplished.

То

# my parents who always gave me the moral support and the urge to continue every time I stumble.

То

my kids who were always there to keep me going on.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                                  | iv  |

|--------------------------------------------------|-----|

| LIST OF TABLES                                   | ix  |

| ACKNOWLEDGMENTS                                  | х   |

| CURRICULUM VITAE                                 | xi  |

| ABSTRACT OF THE DISSERTATION                     | xiv |

| CHAPTER 1: INTRODUCTION                          | 1   |

| CHAPTER 2: State-of-the-art designs              | 29  |

| CHAPTER 3: Proposed System Architecture          | 41  |

| CHAPTER 4: Proposed System Detailed block design | 68  |

| CHAPTER 5: Experimental Results                  | 107 |

| CHAPTER 6: Summary and Conclusions               | 119 |

| REFERENCES                                       | 120 |

# **LIST OF FIGURES**

|             |                                                                                                              | Page |

|-------------|--------------------------------------------------------------------------------------------------------------|------|

| Figure 1.1  | Crest factor for an audio signal                                                                             | 2    |

| Figure 1.2  | Audio band                                                                                                   | 3    |

| Figure 1.3  | Simplified diagram for a typical audio codec chip                                                            | 3    |

| Figure 1.4  | Effect of finite battery internal resistance on audio drivers                                                | 9    |

| Figure 1.5  | A typical PSRR measurement result                                                                            | 10   |

| Figure 1.6  | Stereo Headphone Module                                                                                      | 10   |

| Figure 1.7  | Evolution of headphone PA supply arrangement                                                                 | 13   |

| Figure 1.8  | Class-A topology                                                                                             | 15   |

| Figure 1.9  | Class-B topology                                                                                             | 16   |

| Figure 1.10 | Class-AB topology                                                                                            | 17   |

| Figure 1.11 | Class-G topology, supply modulation                                                                          | 18   |

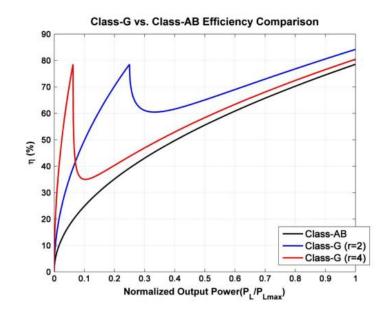

| Figure 1.12 | Relative comparison between Class-AB, and Class-G ( $r=2, r=4$ )                                             | 20   |

| Figure 1.13 | Class-H topology, supply modulation                                                                          | 21   |

| Figure 1.14 | Class-H amplifier supplies by a buck converter (positive supply),<br>and flyback converter (negative supply) | 22   |

| Figure 1.15 | Class-D loop driving differential loudspeaker load                                                           | 23   |

| Figure 1.16 | Block diagram for PWM switch control                                                                         | 25   |

| Figure 1.17 | Block diagram for $\Sigma\Delta$ switch control                                                              | 25   |

| Figure 1.18 | Block diagram for a sliding mode switch control                                                              | 26   |

| Figure 1.19 | Illustration of the nonlinearity foldback issue in Class-D                                                   | 27   |

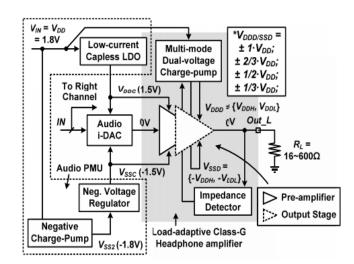

| Figure 2.1  | Load-adaptive Class-G stereo headphone amplifier architecture                                                | 29   |

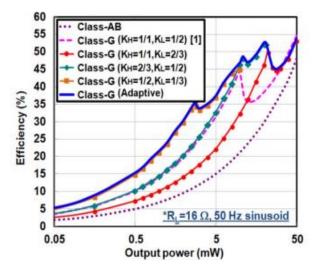

| Figure 2.2    | Total-path efficiency versus output power level                                                  | 31 |

|---------------|--------------------------------------------------------------------------------------------------|----|

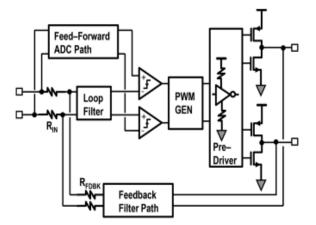

| Figure 2.3    | Class-D structure of the JSSC Nov 2014 paper                                                     | 32 |

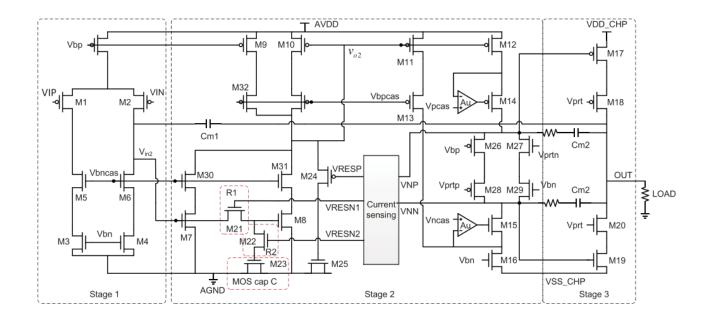

| Figure 2.4    | Class-AB driver schematic                                                                        | 34 |

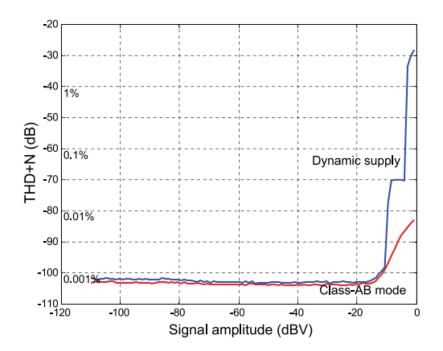

| Figure 2.5    | Measured A-weighted THD+N versus input signal amplitude<br>for 1 kHz signal frequency, 0 dB gain | 35 |

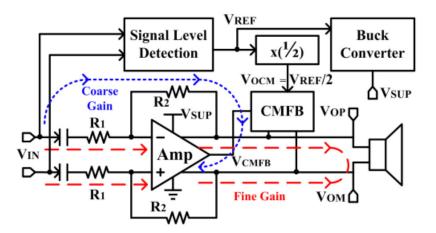

| Figure 2.6    | System-level illustration of the proposed Class-H amplifier                                      | 36 |

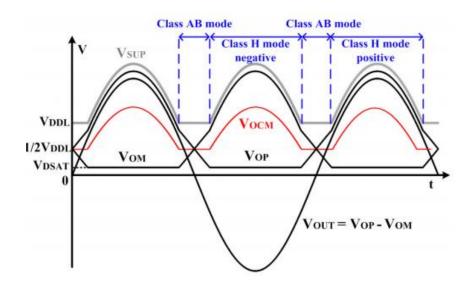

| Figure 2.7    | Amplifier output waveforms with sinusoidal input signals                                         | 37 |

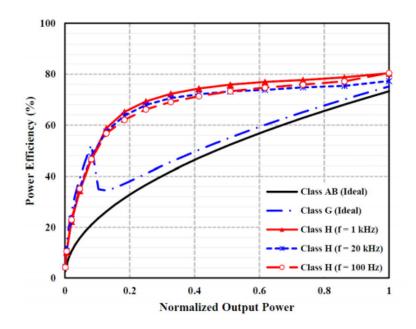

| Figure 2.8    | Class-H measured efficiency plot                                                                 | 38 |

| Figure 2.9    | Sliding-mode system architecture                                                                 | 39 |

| Figure 2.10   | Measured THD+N vs output power plot                                                              | 40 |

| Figure 3.1    | Simplified proposed architecture                                                                 | 41 |

| Figure 3.2(a) | PWM spectrum before filter and filter response                                                   | 42 |

| Figure 3.2(b) | PWM spectrum after filtering.                                                                    | 42 |

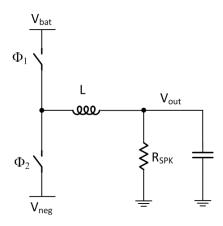

| Figure 3.3    | Simplified power stage                                                                           | 43 |

| Figure 3.4    | A simplified block diagram for the switching regulator                                           | 44 |

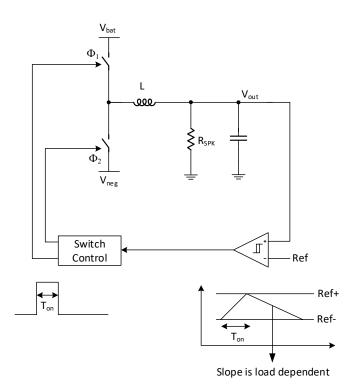

| Figure 3.5    | Fixed on-time PFM/DCM scheme                                                                     | 46 |

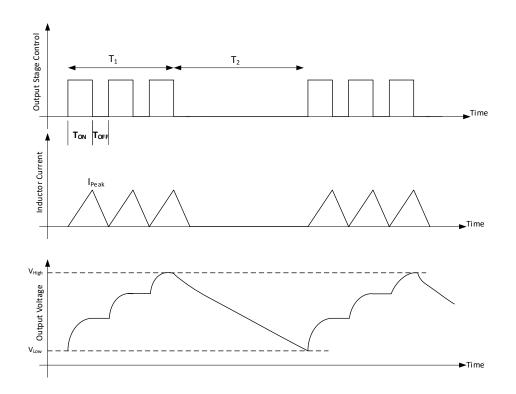

| Figure 3.6    | Output stage control, inductor current, and output voltage                                       |    |

|               | for PFM/DCM scheme                                                                               | 47 |

| Figure 3.7    | PWM/CCM control scheme                                                                           | 48 |

| Figure 3.8    | Output stage diagram with the ac model parameters labeled                                        | 49 |

| Figure 3.9    | Output stage during $\phi_1$                                                                     | 50 |

| Figure 3.10   | Output stage during $\phi_2$                                                                     | 51 |

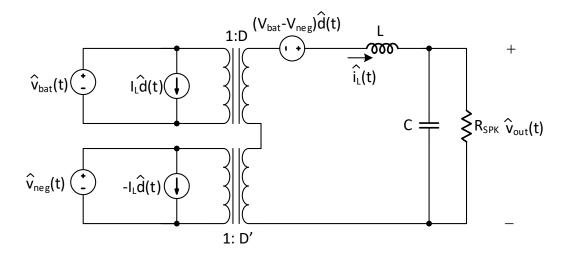

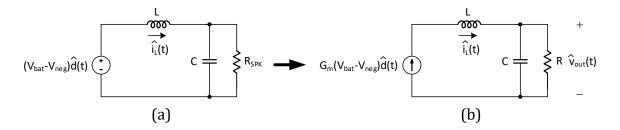

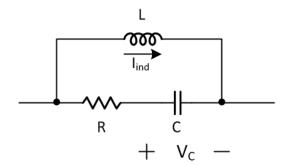

| Figure 3.11   | AC model for the output stage                                                                    | 53 |

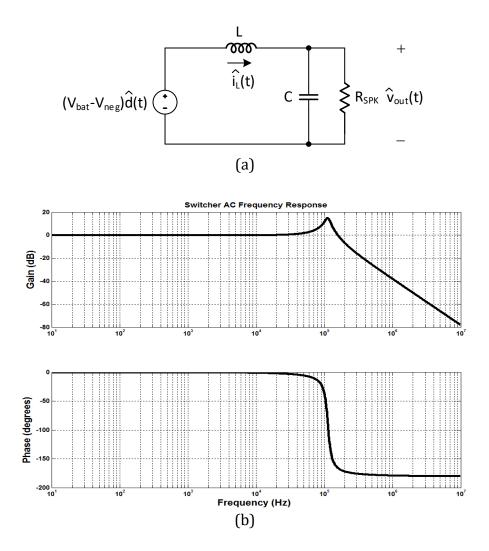

| Figure 3.12a  | Simplified switcher AC model                                                                     | 54 |

|               | v                                                                                                |    |

| Figure 3.12b | Its frequency response                                                      | 54 |

|--------------|-----------------------------------------------------------------------------|----|

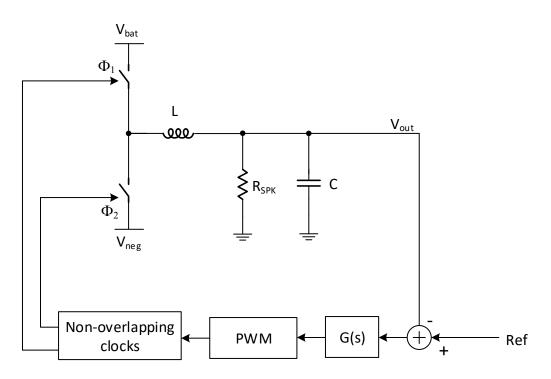

| Figure 3.13  | Block Diagram for the PWM loop                                              | 55 |

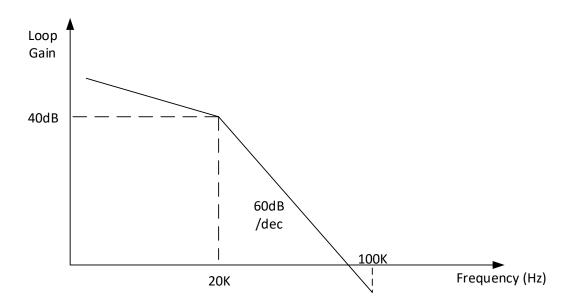

| Figure 3.14  | Hypothetical open loop gain to push LC poles outside audio band             | 56 |

| Figure 3.15a | Voltage mode excitation                                                     | 57 |

| Figure 3.15b | Current mode excitation                                                     | 57 |

| Figure 3.16  | Peak-current control for current mode CCM loop                              | 57 |

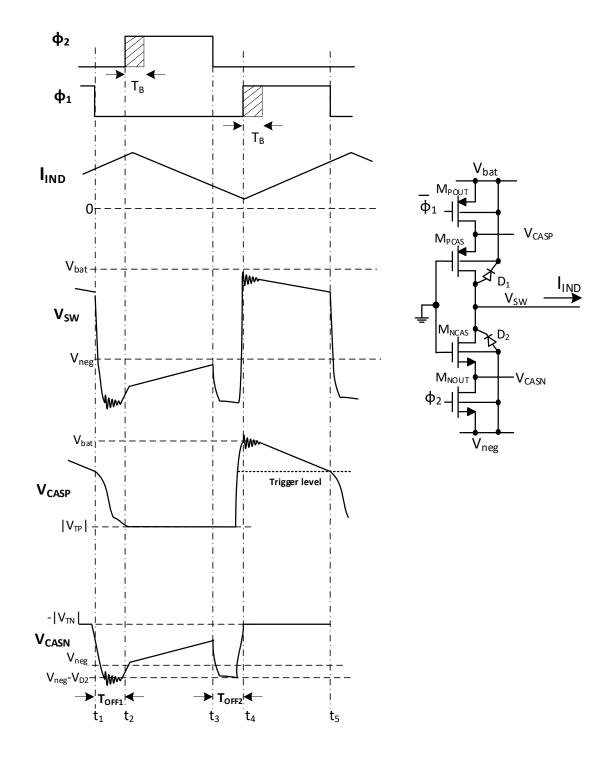

| Figure 3.17  | Peak-Valley current mode control scheme                                     | 59 |

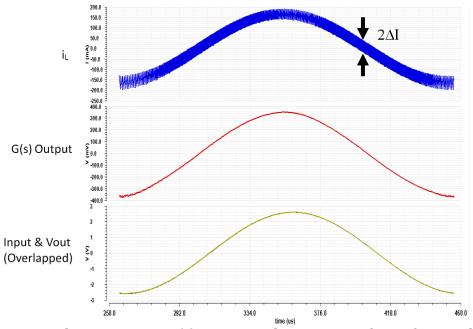

| Figure 3.18  | Inductor current, G(s) output, and output waveforms for CCM loop            | 60 |

| Figure 3.19  | AC model for the loop                                                       | 61 |

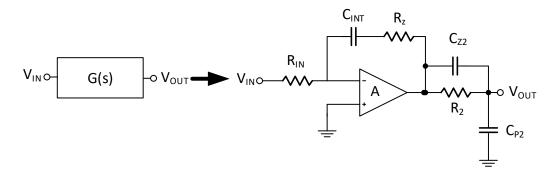

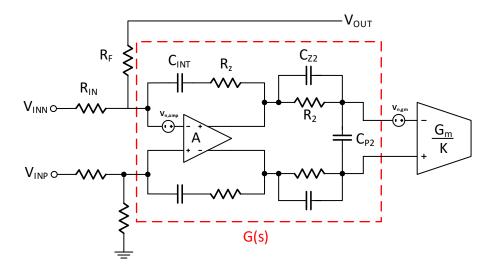

| Figure 3.20  | Realization of the loop filter G(s)                                         | 62 |

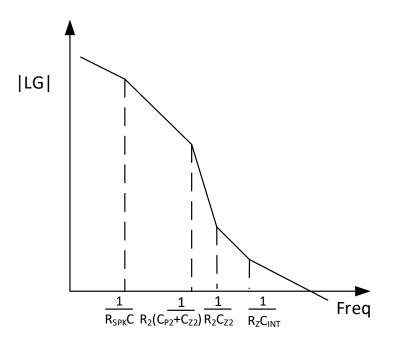

| Figure 3.21  | Open loop gain vs frequency showing locations of all poles/zeros            | 63 |

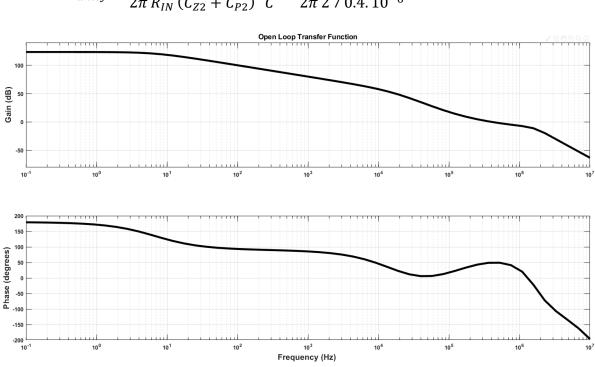

| Figure 3.22  | Open loop Bode plots                                                        | 64 |

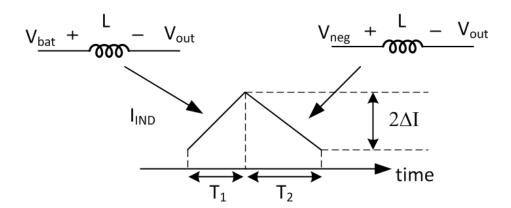

| Figure 3.23  | Voltage across the inductor during the 2 phases                             | 65 |

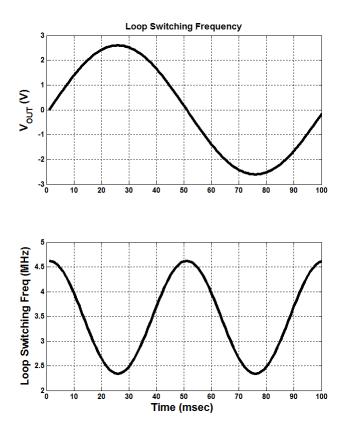

| Figure 3.24  | Loop switching frequency and output voltage vs. time                        | 66 |

| Figure 4.1   | Simplified proposed architecture                                            | 68 |

| Figure 4.2   | Watkins-Johnson output stage                                                | 70 |

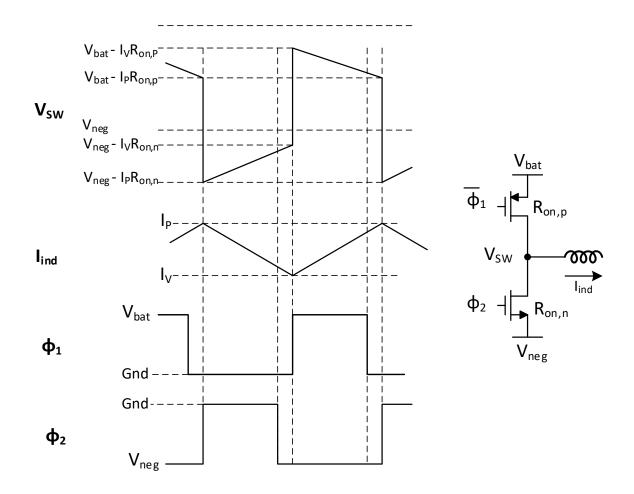

| Figure 4.3   | Inductor waveform during the two phases                                     | 71 |

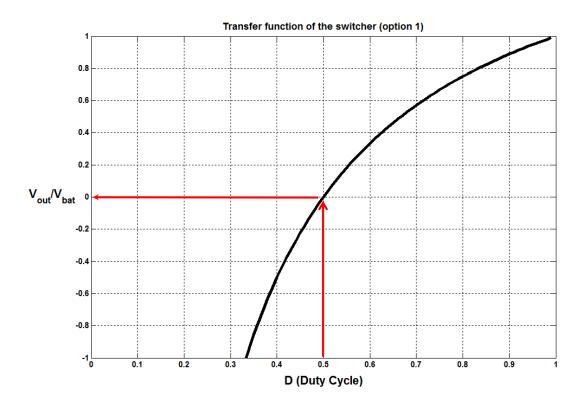

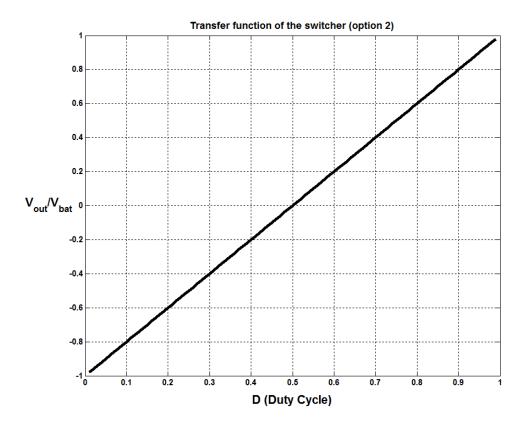

| Figure 4.4   | Transfer function vs. duty cycle for Watkins-Johnson                        | 72 |

| Figure 4.5   | Half bridge Class-D switching stage                                         | 73 |

| Figure 4.6   | Inductor waveform during the two phases                                     | 74 |

| Figure 4.7   | Transfer function vs. duty cycle for half bridge Class-D with dual supplies | 75 |

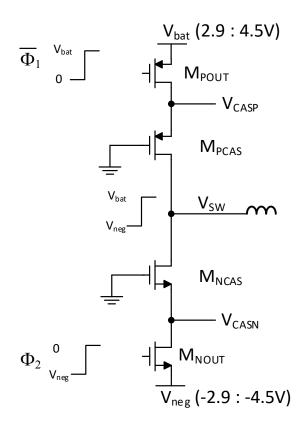

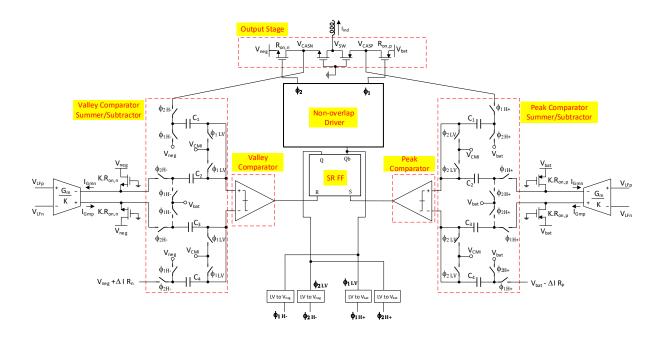

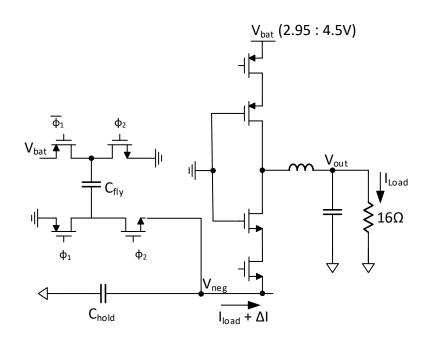

| Figure 4.8   | Actual implementation for the output stage                                  | 76 |

| Figure 4.9  | Sensing I <sub>ind</sub> using RC sense network                                | 78  |

|-------------|--------------------------------------------------------------------------------|-----|

| Figure 4.10 | Timing waveforms to illustrate the current sensing technique                   | 80  |

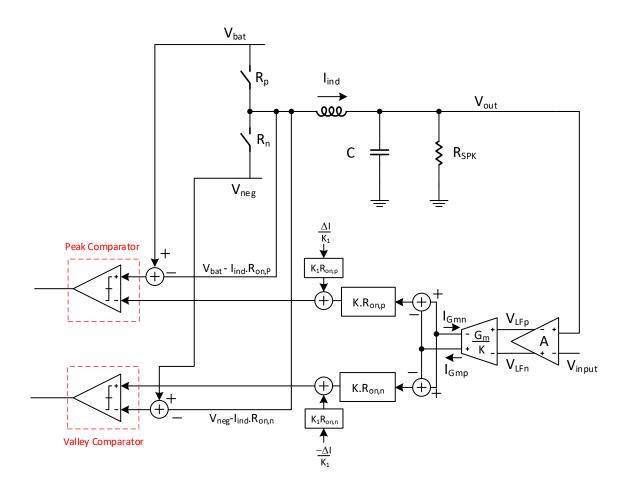

| Figure 4.11 | Scaling of loop filter output to cancel effect of switcher $R_{\text{on}}$     | 81  |

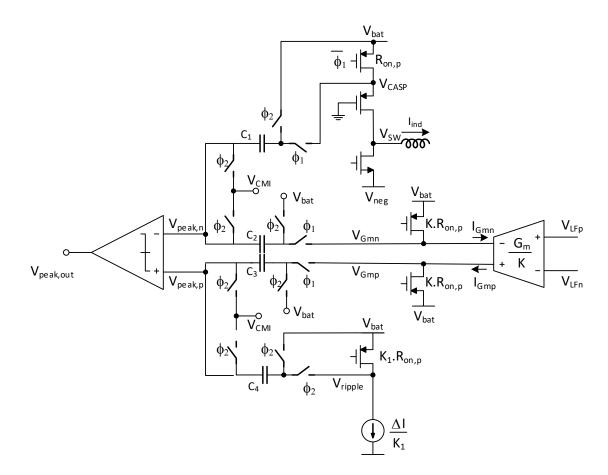

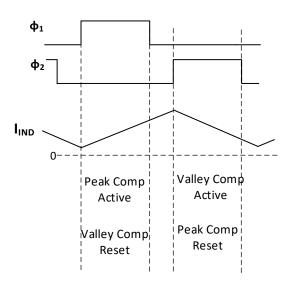

| Figure 4.12 | Capacitive summation/subtraction for peak comparator                           | 84  |

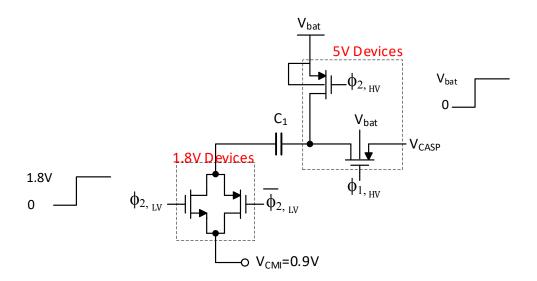

| Figure 4.13 | Switch implementation for $C_1$ path of Figure 4.12                            | 85  |

| Figure 4.14 | 1.8V to V <sub>bat</sub> level shifter                                         | 86  |

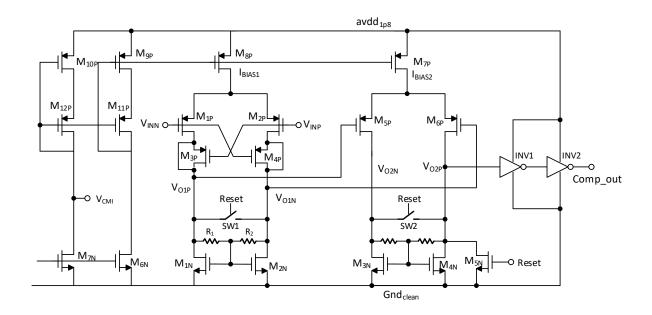

| Figure 4.15 | Peak/Valley comparator implementation                                          | 87  |

| Figure 4.16 | Comparator modes                                                               | 90  |

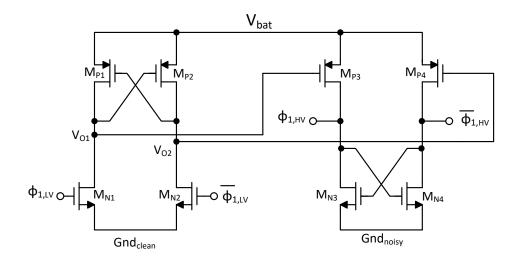

| Figure 4.17 | Switching clock generation                                                     | 91  |

| Figure 4.18 | Transient waveforms for the output stage for a positive large inductor current | 92  |

| Figure 4.19 | G(s) with input/output interface                                               | 95  |

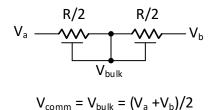

| Figure 4.20 | Resistor terminal definition                                                   | 97  |

| Figure 4.21 | Circuit technique to eliminate the conductivity modulation                     | 98  |

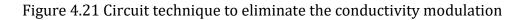

| Figure 4.22 | Amplifier implementation                                                       | 98  |

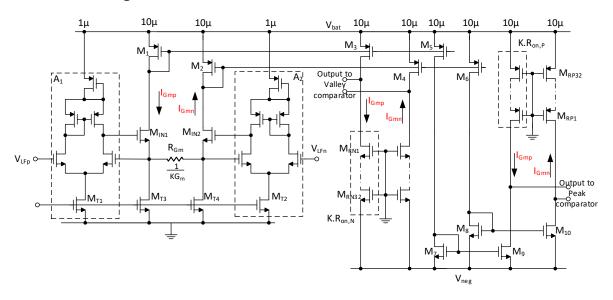

| Figure 4.23 | Transconductance implementation                                                | 100 |

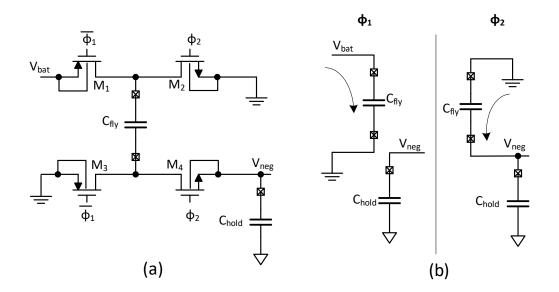

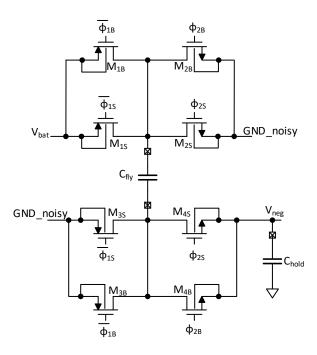

| Figure 4.24 | Negative charge-pump topology                                                  | 101 |

| Figure 4.25 | Charge-pump loaded by the output stage                                         | 102 |

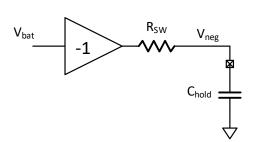

| Figure 4.26 | CP Model                                                                       | 103 |

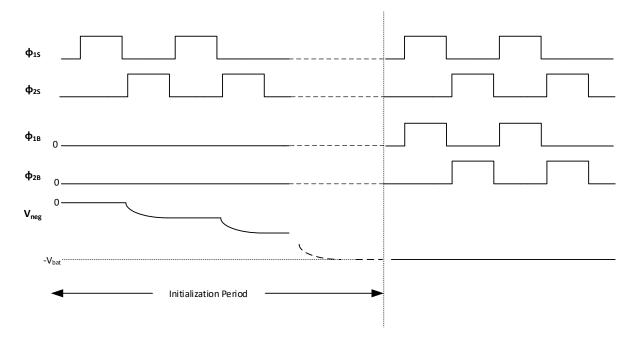

| Figure 4.27 | Charge-Pump Design                                                             | 105 |

| Figure 4.28 | Relative timing of the different clock phases of the CP                        | 106 |

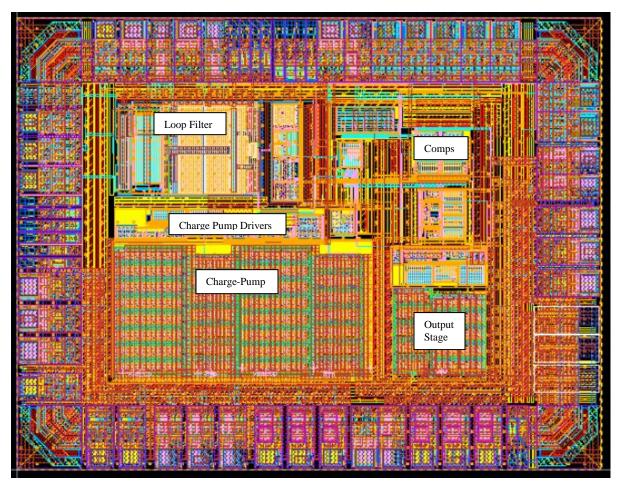

| Figure 5.1  | Chip Layout                                                                    | 107 |

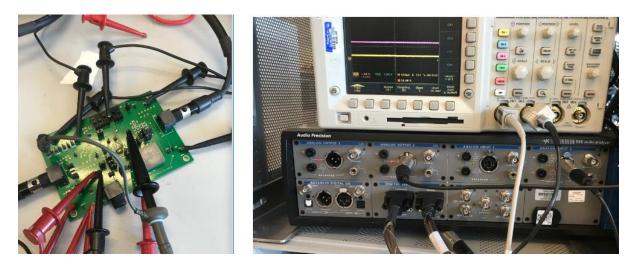

| Figure 5.2  | Test Setup                                                                     | 108 |

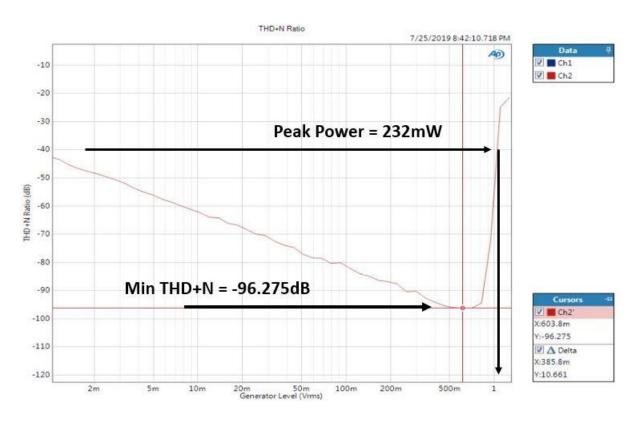

| Figure 5.3  | Measured THD+N vs. the rms of the input signal for a 16 $\Omega$ load          | 109 |

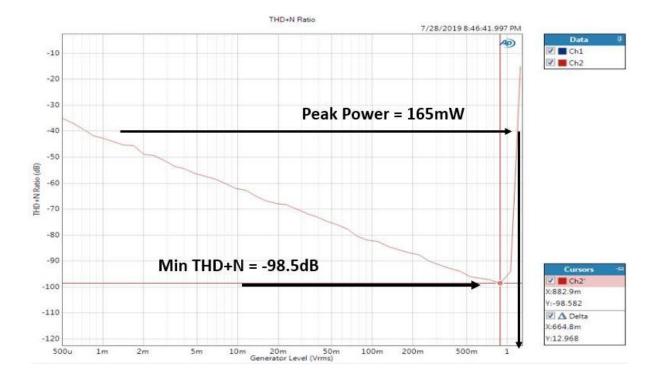

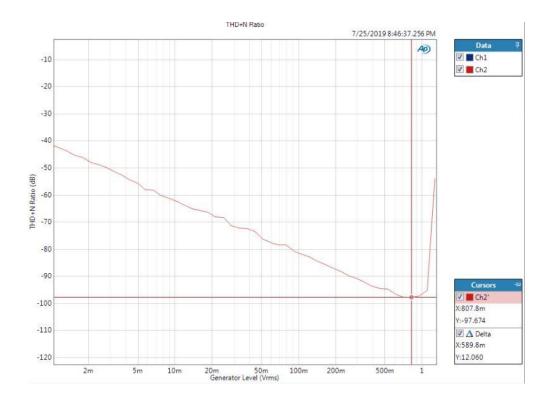

| Figure 5.4  | Measured THD+N vs. the rms of the input signal for a 32 $\Omega$ load  | 110 |

|-------------|------------------------------------------------------------------------|-----|

| Figure 5.5  | Measured THD+N vs. the rms of the input signal for a 600 $\Omega$ load | 111 |

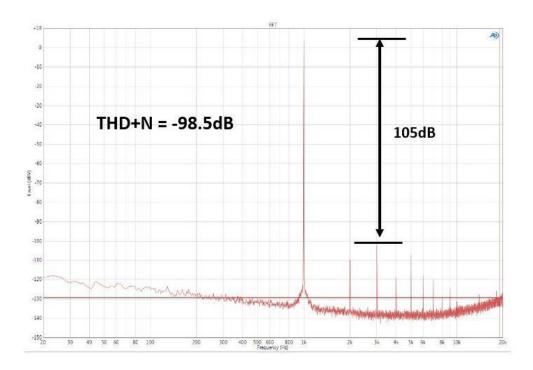

| Figure 5.6  | Figure 5.6 Output spectrum for 1.5Vrms 1kHz output with a              |     |

|             | $32 \Omega$ load                                                       | 112 |

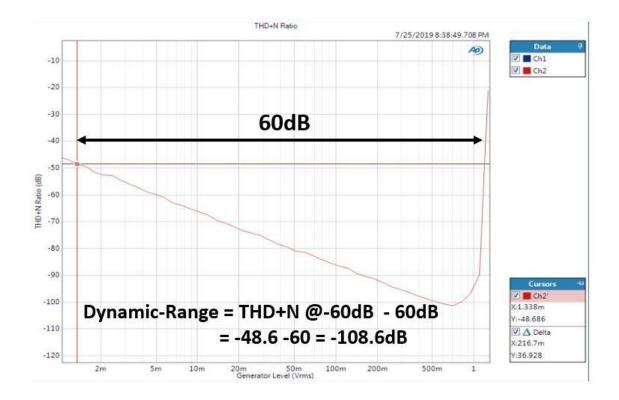

| Figure 5.7  | Measured A-weighted Dynamic Range for a 32 $\Omega$ load               | 112 |

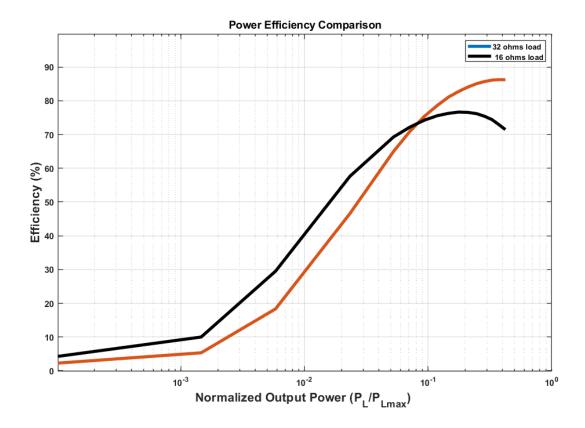

| Figure 5.8  | Measured power efficiency for 16 and 32 $\Omega$ loads                 | 113 |

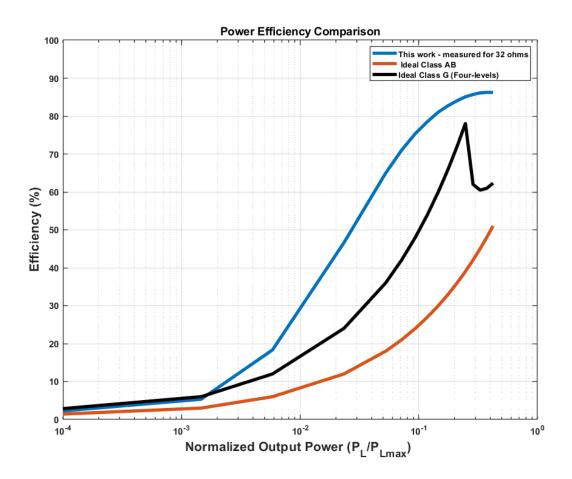

| Figure 5.9  | Power efficiency comparison                                            | 114 |

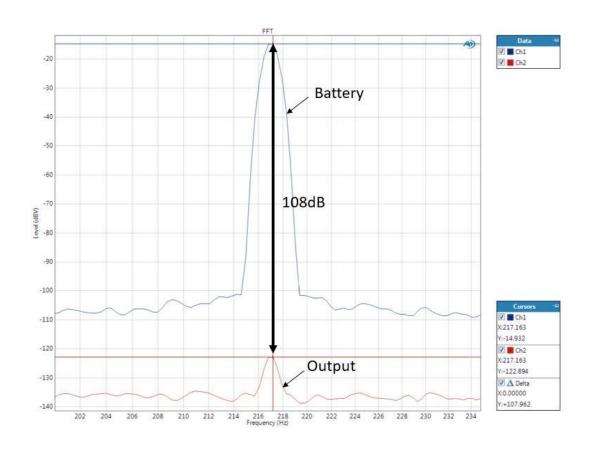

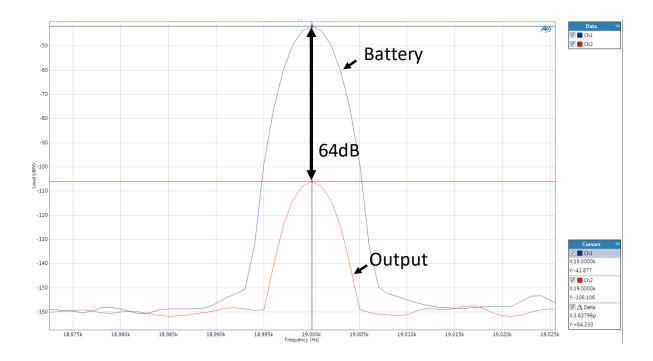

| Figure 5.10 | PSRR at 217Hz                                                          | 116 |

| Figure 5.11 | PSRR at 1kHz                                                           | 116 |

| Figure 5.12 | PSRR at 19kHz                                                          | 116 |

### LIST OF TABLES

|                                            | Page |

|--------------------------------------------|------|

| System key parameters and component values | 63   |

| Output stage device sizes                  | 77   |

| Noise contributions                        | 96   |

| Table 4.3 | Negative charge-pump switch sizes                                         | 104 |

|-----------|---------------------------------------------------------------------------|-----|

| Table 5.1 | Performance summary and comparison with the state-of-the-art publications | 117 |

Table 3.1

Table 4.1

Table 4.2

#### ACKNOWLEDGMENTS

I would like to thank my sincere wife Rania Sultan for her amazing patience, support and solidarity she showed for years. This work would never have gotten completed without her and her persistent support, and endless encouragement.

I would also like to express the deepest appreciation to my dissertation Committee Chair, Professor Michael Green, who has been very patient and supportive throughout this journey. Without his guidance and persistent help, this dissertation would not have been possible.

Special thanks to my committee members: Professor Ahmed Eltawil who allowed me to access his research group server for an extended period of my research which helped my progress significantly, and Professor Nader Bagherzadeh. I greatly appreciate their critical feedback during the defense.

In addition, I would like to thank both Dr. Sherif Galal and Dr. Ahmet Tekin for their inspiration and discussions in the early phase of this work.

Furthermore, I thank my colleagues: Wael Elsharkasy, Siavash Yazdi, and Hang Zhao for their help throughout my work, along with my friend Mahmoud Elhebeary for his help and support in finalizing the board design.

Last but not least, I would like to express my gratitude to my father-in-law Samir Sultan for his help checking and proofreading the dissertation.

х

### **CURRICULUM VITAE**

#### Khaled Abdelfattah

| 1999               | B.Sc. in Electrical Engineering, Cairo University, Egypt                                      |

|--------------------|-----------------------------------------------------------------------------------------------|

| 1999-2001          | M.Sc. in Electrical Engineering, Cairo University, Egypt                                      |

| 2001-2007<br>Unive | PhD Candidate, Research Assistant, in Electrical Engineering rsity of California, Los Angeles |

| 2007-2014          | Principal Design Engineer, Broadcom Corp., Irvine                                             |

| 2011-2019<br>Unive | PhD Candidate, in Electrical Engineering<br>rsity of California, Irvine                       |

| 2014-present       | Senior Staff Design Engineer, Qualcomm Inc., Irvine                                           |

#### FIELD OF STUDY

Mixed signal analog design with emphasis on high precision analog design.

#### PUBLICATIONS

- K. Abdelfattah, M. Green, "2Vrms 16Ω Switching Headphone Driver with 82% Peak Efficiency,100dB+ SNDR and 1mA/Channel", International Midwest Symposium on Circuits and Systems, MWSCAS, Aug. 2017

- K. Abdelfattah, Galal, I. Mehr, A. Check. Yu, M. Tjie, A. Tekin, X. Jiang, T.Brooks, "A 40nm Fully Integrated 82mW Stereo Headphone Module for Mobile Applications", Journal of Solid-State Circuits, Vol. 49, Issue 8, 2014, pp. 1702-1714

- K. Abdelfattah, Galal, I. Mehr, A. Chen, X. Jiang, A. Tekin, T. Brooks, "A Direct-Battery Hookup, Fully Integrated Stereo Headphone Module with 82mW Output Power and

110 dB PSRR", Custom Integrated Circuits Conference proceedings, Sep,2013 (Best Poster Award)

- Sherif Galal, H. Zheng, K. Abdelfattah, V. Chandrasekhar, I. Mehr, A. Chen, J. Platenak, N. Matalon, T. Brooks, "A 60mW Class-G Stereo Headphone Driver for portable Battery-Powered Devices", IEEE Journal of Solid-State Circuits, Vol. 47, Issue 8, 2012, pp. 1921-1934

- Xicheng Jiang; Jungwoo Song; Minsheng Wang; Jianlong Chen; Hui Zheng; Galal,

S.; Abdelfattah, K.; Brooks, T.L.," A 100 dB ground-referenced single-ended Class D amplifier in 65nm CMOS', 2011 Symposium on VLSI circuits ,2011, pp. 58-59

- Xicheng Jiang, Min Gyu Kim, Felix Cheung, Fang Lin, Hui Zheng, Jianlong Chen, Alex Chen, Darwin Cheung, Khaled Abdelfattah, Seong-Ho Lee, Hanson Huang, Kishore Kasichainula, Yonghua Cong, Jiangfeng Wu, Chang-Hyeon Lee, George Chih, Yun Tu, Todd L. Brooks, Edison Jiang, Hongwei Kong, Chaoyang Zhao, Mustafa Keskin, "A 40 nm CMOS Analog Front End with Enhanced Audio for HSPA/EDGE Multimedia Applications," in IEEE European Solid-State Circuits Conference (ESSCIRC), Sep. 2012.

- Sherif Galal, H. Zheng, K. Abdelfattah, V. Chandrasekhar, I. Mehr, A. Chen, J. Platenak, N. Matalon, T. Brooks, "A 60mW 1.15mA/channel Class-G Stereo Headphone Driver with 111 dB DR and 120 dB PSRR", Custom Integrated Circuits Conference proceedings, Sep,2011

- Sherif Galal; Jurgen van Engelen; Jared Welz; Henrik Jensen; Khaled Abdelfattah; Felix Cheung; Sasi Arunachalam; Xicheng Jiang and Todd Brooks, "A 32-channel

xii

front-end for wireless HID using inverse- STF pre-filtering technique", Custom Integrated Circuits Conference proceedings, Sep,2010

- Khaled Abdelfattah and Behzad Razavi, "Modeling Op Amp nonlinearity in Switched-Capacitor Sigma-Delta Modulator", Custom Integrated Circuits Conference proceedings, Sep10-13, 2006.

- K.M. Abdelfattah, A.M. Soliman, "A Novel exponential voltage to current converter", Journal of Analog Integrated Circuits, Systems, and Signal Processing, Vol. 21, No. 5, 2002, pp. 473-483

- K.M. Abdelfattah, A.M. Soliman, "Variable gain amplifiers based on a new approximation method to realize the exponential function", IEEE Trans. on Circuits and Systems I, Vol. 49, Issue: 9, Sep 2002, pp. 1348-1354

- K.M. Abdelfattah, A.M. Soliman, "Wide band squaring circuit with application to exponential V-I converter", Journal of Telecommunications, Frequenz, Volume 57, May 2003, pp. 112-116

- K.M. Abdelfattah, A.M. Soliman, "A New approach to realize variable gain amplifiers" Journal of Analog Integrated Circuits and signal Processing, 30(3): 257-263; Mar 2002.

#### **ABSTRACT OF THE DISSERTATION**

Efficient Low Power Headphone Driver By

Khaled Abdelfattah

Doctor of Philosophy in Electrical Engineering University of California, Irvine, 2019 Professor Michael Green, Chair

In recent years, the consumer electronics market for battery-powered devices such as smartphones and tablets has been rapidly expanding. The requirements for audio CODEC in these portable devices have extended from merely supporting voice calls to high-fidelity music playback. As a result, audio driver performance has become one of the most important differentiating factors among products from different suppliers. There are three basic performance metrics that are typically used to benchmark audio modules: the maximum delivered output power, the audio fidelity measured in terms of dynamic range, THD+N, and finally the battery life. Maximizing all three of these performance metrics has proven to be an exceptionally hard task as portrayed by the research publications.

This work presents an attempt to push all three of these metrics together and provide an acceptable balance which is achieved by selecting the right topology. Conventionally, headphone drivers are designed using a linear amplifier topology for many reasons- most prominently- to achieve a superior THD+N and PSRR requirement which in the past was essentially the only key performance metric needed. This came at the expense of realizing mediocre power efficiency targets, thereby wasting battery life. This picture changed

xiv

dramatically over the last decade with smartphones and other portable devices becoming the first choice of the young generation. These devices are extremely power hungry due to the unlimited functions and features they provide and therefore battery life has come to the spotlight as a key resource that need to be preserved. As a result, in this work a headphone driver is based on a switching topology that is able to deliver more than 230mW of power (or equivalently 2Vrms) to a 16 $\Omega$  load while achieving better than -98dB of THD+N, more than 108dB of SNR, and about 108dB PSRR while still maintaining a peak power efficiency of more than 84%.

# CHAPTER 1 INTRODUCTION

### **1.1 Motivation**

With the advances of portable electronics over the last decade, customer demands on audio systems have evolved dramatically. In particular, demands for higher output power while maintaining excellent sound fidelity for portable devices are continuously growing. At the same time, in order to maximize the battery charging cycle; power dissipation from the battery should be minimized. This translates into an increased demand for highly efficient designs that can maintain high fidelity [1-3].

Traditionally, linear topologies are used because of their superior sound quality and low distortion; however, it remains challenging for such topologies to meet the continuous demands placed on portable electronics to achieve a longer battery charging cycle. As a result, many improvements to decrease the power dissipation, and increase power efficiency have been introduced in the literature. Some of these approaches combine different topologies and switch between them depending on the signal amplitude, or by modulating their supply in either discrete or continuous fashion [4-13].

On the contrary, switching topologies, which are characterized by their highpower efficiency, yet poor distortion, have been continuously used for audio subsystems that do not demand the same fidelity, such as loudspeaker drivers [14-17]

1

In this work, a switching topology is used to achieve both very high fidelity and very high efficiency for a headphone subsystem.

# **1.2 Audio Signals**

Audio signals have some distinct features [20], which are listed here:

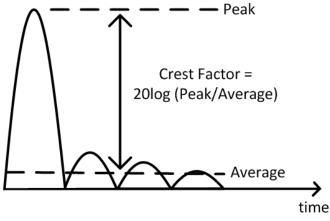

1. Their amplitude probability density function has a Gaussian distribution. As shown in Figure 1.1, audio signals possess a large peak to average ratio (also known as crest factor) of about 15dB on average, which means that audio signals spend most of their time near the average.

Figure 1.1 Crest factor for an audio signal

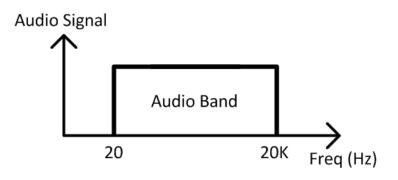

2. Their frequency range, which is set by the limited frequency response of the ear, is between 20 Hz and 20kHz as shown in Figure 1.2. However, given that most people cannot hear 20kHz tones, the power is mainly concentrated at medium frequencies and peaks near 1-2kHz.

Figure 1.2 Audio band

3. In addition, the ear has a large dynamic range of several decades of sound pressures (SPL). For example, low-level background noise can be as low as 50dB, whereas rock band music is around 110dB, and usually the required signal-to-noise ratio of an audio system is usually more than 80dB.

# **1.3 Audio Codecs**

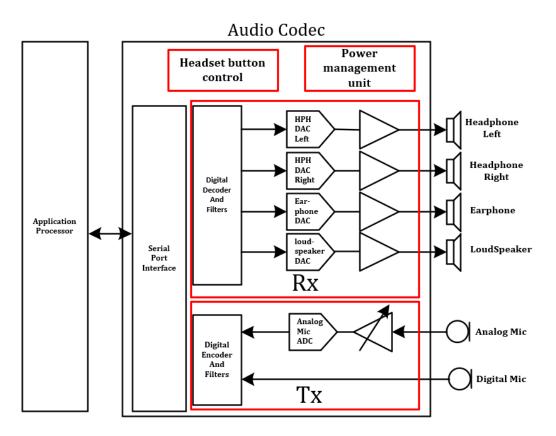

Figure 1.3 Simplified diagram for a typical audio codec chip

Audio codecs are continuously evolving and continue to include many complex functions and support advanced features [21]. Figure 1.3 shows the most basic functions that exist in an audio codec chip, which are:

1. Several receiver channels (Rx), which send the audio signals to different audio peripherals such as earpiece, headphone, lineout, and speakerphone. These channels receive their input signals in PCM digital format from the device application processor (AP) and then pass through digital filters followed by a sigma-delta modulator to reduce their number of bits -which can be as high as 24 bits depending on the quality of the source- down to few bits. As the number of bits goes down, the bit rate increases from 48Kb/s to few Mb/s.

The high-rate, low-resolution signal is used to drive a high-fidelity digital-toanalog converter (DAC), followed by an efficient audio driver to drive the load. Depending on the receiver channel, the load can be electrically represented by different simplified models:

- b. Headphone load: 16 or  $32\Omega$  single-ended ground-referenced resistor.

- c. Earpiece load:  $32\Omega$  differential resistor.

- d. Loudspeaker load: Differential load consisting of 4 or  $8\Omega$  resistor in series with a  $\sim 64\mu$ H inductor.

- e. Lineout: Can be either differential or single-ended, and load is usually a resistor on the order of a few  $k\Omega$ .

- 2. Several transmitter channels (TX) are used to receive audio signals from the microphones and then send them to the device application processor for storage or for playback. External microphones can be either analog or digital; digital

microphones digitize the audio signals, which are directly routed to the application processor. If an analog microphone is used, then a codec chip receives the analog data that passes through a programmable gain stage (PGA) to maintain a predefined signal-to-noise ratio and then to an anti-aliasing filter followed by analog-to-digital converter (ADC). The output digital stream is then filtered and sent to the application processor.

Analog microphones come in different types, such as dynamic, electret, or MEMSbased. The most common high-fidelity type is the electret microphone, which requires a low-noise bias voltage to operate. This voltage, commonly referred to as mic bias, is usually designed in the Tx path using a low noise reference and an LDO to drive the external electret mic.

- 3. Power management unit usually receives a single supply (in most cases the battery voltage itself) and is used to generate:

- a. Band-gap based voltage and currents used to set the ADC and DAC references, as well as the DC bias current for various analog blocks.

- b. Class-H or Class-G power supplies, that supply the final audio driver to increase the efficiency.

- c. Negative supply for headphone drivers.

- d. Regulated supplies for the sensitive parts of the system, such as front-end stages to enhance PSRR.

- 4. Headset button control unit keeps track of the Tx and headphone ports to detect an insertion, and then sends an interrupt signal to the application processor before identifying the plug-in accessory type. The unit also measures the

headphone impedance and detects whether any of the multi-function buttons on the headset is pressed and estimates the duration for which the button is pressed in order to for the AP to correctly decode the function that the user intends.

### **1.4 Key performance parameters for audio drivers**

This section focuses on the receive path and discusses the different key parameters that are used to evaluate the performance of a specific receiver path.

#### 1. Audibility and battery life

a. Maximum power delivered to the Rx load

End-users usually are interested in more loudness coming out of their portable device; typical speakerphone output power is usually in the range of a few watts, while headphone and earpiece output power is usually lower than 100mW.

b. Quiescent current

This is an important parameter primarily because of the audio signal high crest factor. As discussed before, audio signals spend most of the time in low amplitude, in which case the power consumed by the device is dominated by the quiescent power more than the output power. Reducing the quiescent current is important to maximize the battery life for all Rx channels, and especially critical for the headphone path since it is the most used for music playback. c. Since it is desirable to increase output power while decreasing the quiescent current, a figure-of-merit (FOM) is introduced to combine these two parameters to benchmark audio drivers, defined by:

$$FOM \equiv \frac{I_{load,peak}}{I_{Quiscent}} \tag{1.1}$$

d. Power Efficiency

It is defined as:

$$Power \ Efficiency \equiv \frac{Output \ Power}{Power \ consumed \ from \ the \ battery}$$

(1.2)

This parameter is usually measured as a function of the output power. It is always desirable to increase the power efficiency at all power levels to maximize battery life; therefore, special types of audio drivers are used to maximize the power efficiency. For example, loudspeakers use Class-D output stage, which can deliver up to 90% power efficiency at maximum output power. On the other hand, headphone drivers typically use a Class-AB output stage to maximize the power efficiency while maintaining excellent audio quality.

#### 2. Fidelity

Since the human ear has high sensitivity to noise and distortion, several parameters are used to quantify the effects of the noise and distortion introduced by the audio drivers to evaluate their fidelity. a. Signal-to-noise-ratio (SNR)

Defined as the ratio of the full-scale rms signal to the integrated noise within a 20kHz frequency band. The noise is usually measured with no signal and weighted with a special filter known as A-weighting, which imitates the ear response.

b. Dynamic Range (DR)

Dynamic range is a measure to rate the ratio of both random noise and the  $\Sigma\Delta$  quantization noise to the output full scale. A small signal (-60dB) is applied to the input to avoid the effect of any nonlinearities, and the output is integrated within the audio band. 60dB is added back in order to refer back to full-scale input, as shown in the following equation:

$$DR \equiv \frac{Signal @ - 60dB}{Integrated noise floor(20 - 20KHz)} + 60dB$$

(1.3)

c. Total Harmonic Distortion+ Noise (THD+N) ratio

This measure quantifies the effect of both system noise and nonlinearities in presence of a signal. It is usually measured as a function of the input signal and span a few decades of signal range.

d. Power Supply Rejection Ratio (PSRR)

Power supply rejection ratio is an especially important parameter for portable devices working in a GSM network. On such a network, the mobile device may transmit in either the 800 or 1900MHz bands with RF power up to 3W. In GSM transmission, the mobile device pulses its RF transmitter on and off at a rate of 217Hz with a duty cycle of about 10%. While in the "on" state, the RF

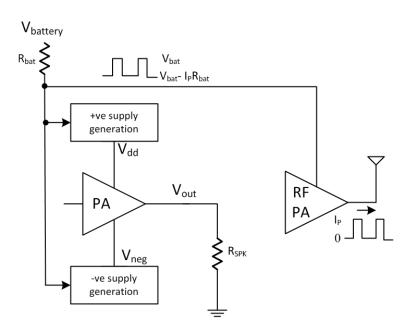

transmitter draws a large amount of current. Since the battery is the only source of power in a mobile device, and it has a finite source resistance ( $R_{BAT}$ ) as shown in Figure 1.4, the supply voltage of the codec effectively becomes modulated with about 500mV peak-to-peak square wave at 217Hz. This disturbance becomes audible if it propagates to the audio port, and thus it is necessary for the audio driver to reject the supply disturbance.

Figure 1.4 Effect of finite battery internal resistance on audio drivers

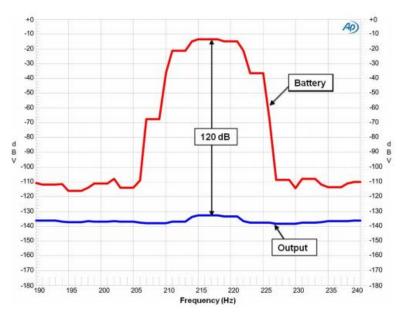

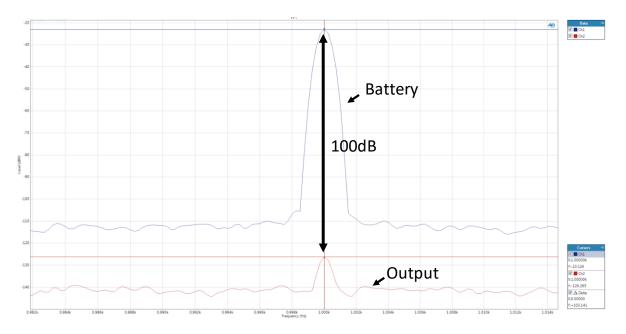

Figure 1.5 shows a typical PSRR measurement result where a 217Hz  $500mV_{PP}$  disturbance is applied on the battery. Battery disturbance and the audio output spectrum are plot and compared.

Figure 1.5 A typical PSRR measurement result

# **1.6 Headphone path**

As explained in Section 1.4, there are several Rx receiver modules within a codec chip, each having its own unique requirements in terms of the acceptable fidelity as well as output power. Of these modules, the headphone module presents the most challenging design because of its stringent fidelity demands that exceeds those of other Rx channels as well as ever increasing demands for higher output power without degrading the efficiency [2,3].

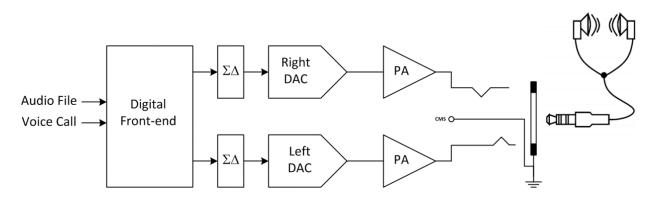

Figure 1.6 Stereo Headphone Module

Figure 1.6 depicts the overall stereo headphone module consisting of identical left and right channels. The headphone module receives two streams of data, one for each channel, from the digital front-end module. This module controls several functions such as gain companding, signal pre-distortion, and several other signal conditioning functions. In a typical Hi-Fi audio CODEC, words for prerecorded CD quality data are 24 bits wide sampled at 48, 192, or 384kHz. In order for this data to drive the speaker, a high-accuracy DAC is needed to convert the signal from digital to analog while preserving the CD audio quality. A typical  $\Sigma \Delta$  DAC consists of a digital  $\Sigma\Delta$  modulator followed by a DAC, the basic idea being to oversample the incoming data stream and then truncate it. The truncation error, which has a white spectrum is shaped by the  $\Sigma\Delta$  modulator such that the in-band portion is significantly reduced down to the system requirement, while the out-of-band error is increased. The oversampled and truncated  $\Sigma \Delta$  output data has fewer levels; thus, a fast, lowresolution DAC is needed. Due to fewer DAC levels, fewer unit elements are needed, which results in die area savings. Another advantage of using a  $\Sigma \Delta$  DAC is the ability to easily implement dynamic element matching [18-19] for the DAC elements, which is often required to reduce the impact of the unit mismatch on the overall THD+N performance. The DAC analog output is then passed through the PA (power amplifier) feedback loop conventionally configured as a linear power topology, such as Class-AB, to drive the 16 $\Omega$  speaker load. The PA driver loop uses the common-mode-sense input (CMS) to couple any noise on the headphone ground back to the module output. This arrangement provides ground noise immunity, particularly important in an SoC environment.

In this work, the focus is on the design of the PA driver loop, where highly efficient switching topology is used to increase the output power, which increases the overall efficiency while maintaining high fidelity.

## **1.7 Headphone PA supply**

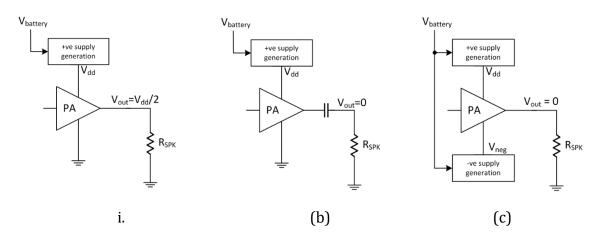

The headphone load can be modeled simply as a load resistor (normally 16 or  $32 \Omega$ ) referenced to ground. Early PA designs used a single supply and set the common mode at the output to half the supply voltage as shown in Figure 1.7(a). This approach means that the PA is realized as a Class-A amplifier and therefore suffers from very poor efficiency when no signal is present. In addition, applying a DC voltage to the speaker for an extended period of time may eventually damage it. Figure 1.7(b) shows a second approach to use a blocking capacitor to block the DC while allowing only the ac variation to propagate to the speaker load. While this approach is safer for the speaker and would result in better efficiency, the blocking capacitor along with the speaker load form a high-pass filter whose cutoff frequency must be less than 20Hz. If the speaker load resistance is set to  $16\Omega$ , this translates into a capacitor value of approximately  $500\mu$ F, which would be very costly and bulky [9].

#### (c) dual supplies.

A better approach, shown in Figure 1.7(c), which has recently become the usual for headphone PA design now is to use dual supplies: positive and negative, so that the output common mode can be comfortably set to ground without the need for a blocking capacitor [9]. This solution simplifies the design of the PA at the expense of adding the complexity of designing some circuitry that can generate a negative on-chip supply with high enough efficiency.

Designing the PA supplies has been an integral part of achieving a high power efficiency for the entire headphone module. PA supplies could be either constant as in Class-A, AB, and B topologies, or it can depend on the signal, which can be either discrete as in Class-G, or continuous as in Class-H. In the next section, an overview of the different types of PA topologies will be discussed.

### **1.8** Overview of power amplifier topologies

There are two categories for PA topologies, linear and switching. Linear topologies such as Class-A, AB and G/H are designed to have a smooth transition between different devices in delivering the output power throughout the signal swing. This way, when the audio signal transitions from positive to negative swing, the amplifier smoothly reduces the transconductance of the pmos side --which delivers positive swing to the output-- and increases the transconductance of the nmos side in a similar way. This smooth transition usually results in very low distortion for the output signal, and therefore linear topologies have been extensively used for headphone PA design. However, since the nmos and pmos drivers require sufficient headroom across them in order to effectively handle the signal swing with no distortion issues, this headroom results in power dissipated inside the PA, effectively lowering the power efficiency of the design.

On the other hand, switching topologies rely on operating the driving transistors with minimum headroom as they are used merely as switches while delivering audio-encoded PWM/PDM signal to the output, and therefore the power dissipation is significantly lower increasing the overall efficiency. However, this results in sudden transitions between the nmos and pmos driving sides, which degrades the PA signal-to-distortion ratio.

Switching topologies have been used extensively for high-power audio drivers such as speaker phone drivers, at the expense of high distortion.

14

### a. Linear topologies

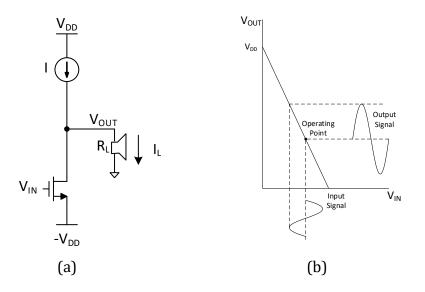

#### 1. Class-A

Figure 1.8 Class-A topology. (a) Circuit Diagram, (b) Signal transfer function. Figure 1.8(a) shows a simple Class-A PA output stage consisting of one output device (nmos or pmos) and a current source. The signal transfer function shown in Figure 1.8(b) shows a very linear relationship between V<sub>OUT</sub> and V<sub>IN</sub> due to the output device remaining in the saturation region throughout the signal swing. The power efficiency (η) is defined as:

$$\eta \equiv \frac{Power \ delivered \ to \ the \ load}{Power \ consumped \ from \ the \ supplies} \tag{1.4}$$

Since power delivered to the load is  $\frac{V_{out,peak}^2}{2R_L}$ , and the average power drawn from each supply is  $V_{DD}I$ , then the efficiency is calculated as:

$$\eta = \frac{1}{4} \frac{V_{out,peak}}{V_{DD}} \frac{V_{out,peak}}{IR_L}$$

(1.5)

Since  $V_{out,peak}$  is always smaller than  $V_{DD}$  and  $IR_L$ , the maximum efficiency is limited to only 25%.

This poor efficiency is a direct result of the fact that this amplifier is always on and never cut off, regardless of the magnitude or polarity of the input, as the Class-A amplifier has a  $360^{\circ}$  conduction angle, meaning it is on and conducts throughout a full cycle of the input sine wave.

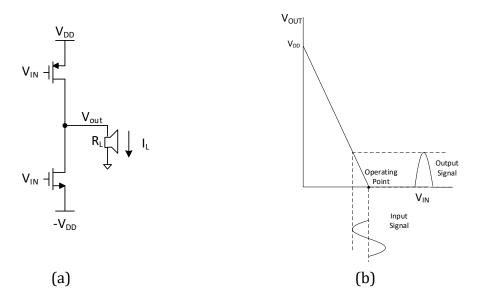

#### 2. Class-B

The Class-B amplifier uses a "push-pull" arrangement with a pair of complementary amplifier devices Nmos/Pmos, each biased at cutoff with the conduction angle of each amplifier at 180<sup>°</sup> (half cycle) as shown in Figure 1.9. When the bipolar, zero-centered input signal goes positive, one device comes out of cutoff and goes into its saturation region, conducts, and amplifies; when the signal goes negative, the other device does the same while the first one is cutoff and thus dissipating near-zero power.

Figure 1.9 Class-B topology. (a) Circuit Diagram, (b) Signal transfer function.

Class-B amplifiers suffer from crossover distortion, which generates harmonics, arising because of the slight lag or discontinuity as one active element turns on while the other turns off. Distortion is typically 10-20%. This may be acceptable for some situations but not for higher-quality audio designs. On the other hand, the realized efficiency is much better than Class A and is given by:

$$\eta = \frac{\pi}{4} \frac{V_{out,peak}}{V_{DD}} \tag{1.6}$$

The maximum efficiency is limited to only 78% when Vout, peak equals VDD

#### 3. Class-AB

The Class-AB amplifier is a blend of Class-A and Class-B and strives to offer a compromise in efficiency and performance [4-6].

Figure 1.10 Class-B topology. (a) Circuit Diagram, (b) Signal transfer function.

In this topology, shown in Figure 1.10, each active element is biased slightly in the saturation region, so there is some overlap between the two at the turn-on/turn-

off center point. This reduces distortion to a low level – typically 1% and even down to 0.1% – at a slight increase in power dissipation. There is a tradeoff between the conduction angle, which is somewhat greater than  $180^{\circ}$ , and resulting distortion, with increased conduction angle and associated dissipation yielding lower distortion. Class-AB efficiency is slightly less than that of Class-B, due to the quiescent current that flows from  $V_{DD}$  to  $-V_{DD}$  when no signal is present.

Due to the compromise between efficiency and distortion that Class-AB offers, it is probably the most commonly used headphone audio amplifier approach.

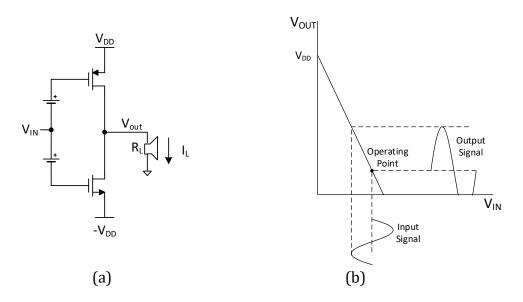

4. Class-G

The Class-G topology makes use of the fact that music and voice signals have a high crest factor with most of the signal content at lower amplitudes [7-11]. The Class-G topology uses multiple power supplies, operating from the power rail that provides the optimum combination of headroom and power dissipation. A Class-G powered module uses a minimum of two different supply rails. The module operates from the lower supply rail until the signal swing required exceeds what the lower supply rail can accommodate, at which point the module switches the output stage to the higher supply rail. Once the output signal drops below a predetermined level, the module switches back to the lower rail. Power dissipation is greatly reduced for typical musical or voice sources.

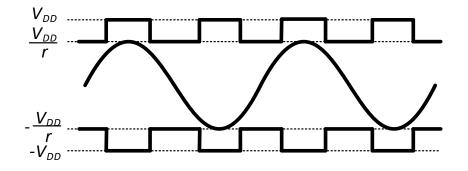

Figure 1.11 shows an example where a sine wave is playing through the Class-G amplifier, while the Class-G supply is changing between  $V_{DD}$  and  $\frac{V_{DD}}{r}$ , where r > 1, according to the instantaneous value of the sine wave.

Figure 1.11 Class-G topology, supply modulation

For a sinewave output, with two level supplies, Class-G efficiency is given by:

$$\eta = \frac{\pi r}{4} \frac{\frac{V_{out,peak}}{V_{DD}}}{1 + (r-1)\cos\theta}$$

(1.7)

where  $\theta$  is given by:

$$\theta = \sin^{-1} \left( \frac{V_{DD}}{r V_{out, peak}} \right)$$

(1.8)

Figure 1.12 shows a comparison of the power efficiency between Class-AB, two-level Class-G with *r*=2, and two-level Class-G with *r*=4, all plotted versus normalized output power  $\frac{P_L}{P_{Lmax}}$ , where  $\frac{P_L}{P_{Lmax}}$  is given by [9]:

$$\frac{P_L}{P_{Lmax}} = \left(\frac{V_{out,peak}}{V_{DD}}\right)^2 \tag{1.9}$$

Figure 1.12 Relative comparison between Class-AB, and Class-G (r=2, r=4)

If the supply generation module is assumed to be lossless, then the power consumed from the source must equal to the power delivered to the load, i.e. if the module draws  $I_{V_{DD}}$  from the input supply ( $V_{DD}$ ), then by generating a smaller output voltage  $\left(\frac{V_{DD}}{r}\right)$ , the output current available to the load increases by the same factor r; i.e,

$$I_{Load} = r I_{V_{DD}} \tag{1.10}$$

As an example, if r=2, then the current drawn by the output is halved when referred to the input, which is a huge power saving. Practically speaking, Class-G supply generation circuit is lossy and often times consumes both static and dynamic power, which lowers the overall achieved efficiency improvement.

Although the Class-G idea looks very attractive, it suffers from the following disadvantages:

- 1. Due to the limited slew rate of the supply generation circuit, it is hard to use it over the entire audio band. Thus, the power savings is only limited to low-frequency audio, and the supply is fixed at *V*<sub>DD</sub> for the high-frequency content.

- 2. To prevent excessive distortion to the output signal, it is critical that the supply generation circuit switches back from  $\frac{V_{DD}}{r}$  to  $V_{DD}$  at the correct time. If any delay is incurred, it would result in increased distortion. Usually, enough margin is implemented in the transition point to make sure that under worst propagation delay, the output signal is still perfect. This margin is another limitation on how much power saving can be achieved.

#### 5. Class-H

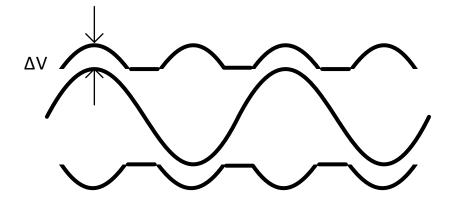

Class-H amplifiers take the idea of Class-G one step further creating an infinitely variable supply rail [12-13]. An example of a class-H amplifier is shown in Figure 1.13.

Figure 1.13 Class-H topology, supply modulation

A Class-H supply is usually designed to leave a fixed headroom ( $\Delta V$ ) on each side to keep the distortion low while maximizing the efficiency, given by:

$$\eta = \frac{V_{out,peak}}{V_{out,peak} + \frac{4\Delta V}{\pi}}$$

(1.11)

Although Class-H presents more efficiency improvement, it comes with the same disadvantages as in Class-G: (1) lacking the ability to track the signal over the entire audio band, and thus limiting the efficiency improvement to low frequency and (2) the inherent tradeoff in the choice of  $\Delta V$  to avoid any instantaneous misalignment between the signal and the supply.

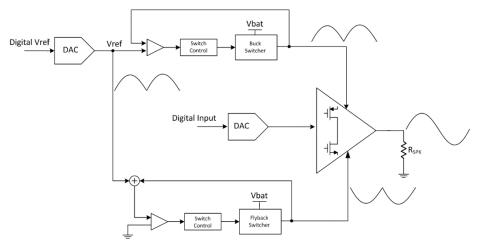

The Class-H positive supply is usually generated by a buck converter that receives its reference from the same digital engine that sends the audio signal to be played back. A digital word representing the instantaneous supply value is received, then converted to analog and used as a reference for the buck converter loop as shown in Figure 1.14.

The negative supply can be generated by an inductor-based flyback loop as in Figure 1.14, or by simply taking the buck output and inverting it using a negative charge pump (NCP).

Figure 1.14 Class-H amplifier supplies by a buck converter (positive supply), and

flyback converter (negative supply)

It is worth noting that both the buck and flyback (or NCP) dissipated additional quiescent currents, which adds to the overall power consumption. In addition, this solution uses two external inductors on the PCB in order to generate the required supplies.

#### **b.** Switching topologies

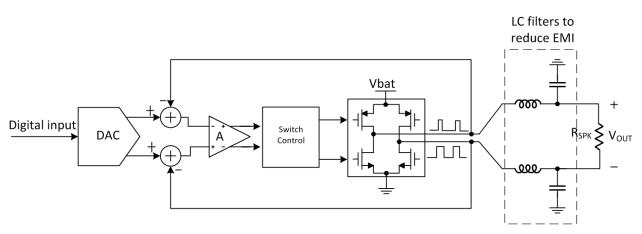

The Class-D is the most common switching topology in which the output stage devices operate as switches, and not as linear gain devices as in the linear topologies. These switches commutate between the supply rails to generate a train of pulses, which represent the required output signal modulated by a high-frequency carrier. The modulation scheme can be either pulse width, or pulse density modulation. The output audio content can be retrieved back by low-pass filtering before being applied to the speaker [15,17]. Since the output devices are never both "on" at the same time, only one device is used to connect either supply to the output, and since each switch is ideally either an open circuit or a short circuit, they dissipate very low power, resulting in very high efficiency, often close to ~90%.

Figure 1.15 Class-D loop driving differential loudspeaker load

A Class-D amplifier can be used in a single-ended (SE) structure to drive singleended loads such as headphone, or in a differential structure known as bridge-tiedload (BTL) for differential loads such as speakerphones as shown in Figure 1.15. The Class-D amplifier is characterized by the need for a series external LC filter to reduce the high-frequency content and smoothen the output sharp edges in order to comply with electromagnetic interference (EMI) requirements. Placing the LC filter close to the chip ensures that radiated emission from either the PCB traces or the connected wires, which could act as antennas, is limited.

Due to the required high output power for speakerphone applications, the Class-D amplifier has been commonly used in the literature. For an output power as high as 5-10W, the power dissipated on the chip is nearly 10% (0.5-1W) if the Class-D is used. In comparison to other power amplifier classes, limiting the on-chip power dissipation by choosing the Class-D topology saves on the required chip area needed to dissipate the heat to maintain a reasonable device junction temperature.

Next, the pros and cons for the different modulation schemes to encode the data for Class-D are discussed followed by a discussion of the main drawbacks of using the Class-D for high-fidelity applications

#### **Class-D modulation schemes:**

1. Pulse-Width Modulation (PWM)

This is the most widely used scheme due to the simple circuitry and low power dissipation. In this type, the PWM is generated by comparing the output of the error amplifier shown in Figure 1.15 to a sawtooth periodic signal at the

24

carrier frequency to produce PWM train of pulses as shown in Figure 1.16 [15,17].

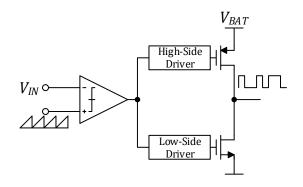

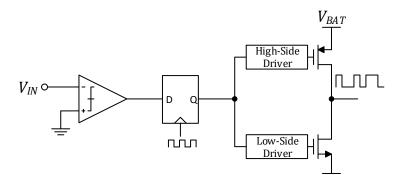

Figure 1.16 Block diagram for PWM switch control

2. Sigma-Delta Modulation ( $\Sigma \Delta$ )

In this modulation scheme, the error amplifier output is quantized into a single bit using a synchronous comparator as shown in Figure 1.17.

Figure-17 Block diagram for  $\Sigma\Delta$  switch control

By choosing higher carrier frequency, the non-linearities and in-band quantization noise, can be reduced. However, this comes at the cost of higher dynamic power, and added complexity to maintain the fidelity of the highfrequency clock source. Another option is to use a higher-order modulator, which increases the hardware complexity and the power dissipation. 3. Sliding-mode Control

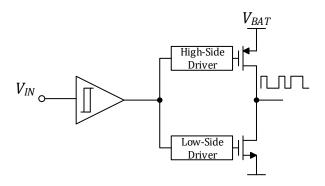

In this type, the synchronous comparator is replaced by a hysteretic comparator as shown in Figure 1.17 resulting in a variable carrier frequency as a function of the signal [14,16], thereby, eliminating issues related to the fidelity of the clock source as well as all quiescent current needed to generate it.

Figure 1.17 Block diagram for a sliding mode switch control

#### Drawbacks for using Class-D for high fidelity applications:

All types of Class-D loops suffer from higher THD due to the following reasons:

a. A typical Class-D output spectrum shown in Figure 1.18 has the signal and distortion components present around the carrier frequency (and its harmonics), and since the loop internally mixes the fed-back output spectrum with the carrier frequency, it inadvertently folds back the distortion components into the audio band and thereby reducing the THD+N.

Figure 1.18 Illustration of the nonlinearity foldback issue in Class-D

- b. Except for the sliding mode control, all other modulation schemes have a fixed carrier frequency, which is usually chosen to guarantee high loop bandwidth at the signal zero crossings. When the signal is at its positive or negative peak, the loop doesn't need to have the same carrier frequency and therefore dissipates more dynamic power than necessary.

- c. As described before, an LC output filter is needed to comply with the stringent EMI specifications. If either the inductance and/or the capacitance exhibits variation as a function of the signal amplitude, the audio band gain may vary as a function of the signal amplitude resulting in added distortion components.

#### 1.9 Focus of this dissertation and flow of next chapters

This dissertation focuses on increasing the overall PA efficiency by using a switching topology while maintaining high fidelity performance similar to the linear topologies. Sliding-mode control is employed to implement a Class-D loop while an additional current sensing loop is implemented in order to improve the THD+N without increasing the loop order or the carrier frequency.

In chapter 2, a summary of most recent or widely used state-of-the-art headphone amplifier designs is presented and discussed. In chapter 3, the proposed system architecture is introduced along with an analysis of the loop dynamics and an explanation of the system advantages. Chapter 4 explains the design of the key analog building blocks in details. Experimental results are discussed in Chapter 5, and a summary of the work and conclusions are discussed in chapter 6.

## CHAPTER 2 State-of-the-art designs

In this chapter, several recent publications covering the topologies that were discussed in Chapter 1 are presented. The focus is on the innovations in these papers as well as their measurement results.

#### 2.1 JSSC Oct 2016 Class-G [8]

In this paper, a load-adaptive Class-G headphone amplifier with supplyrejection bandwidth enhancement technique was introduced. Depending on the load impedance, the amplifier selects proper voltage rails and controls the Class-G switching activities to minimize the power loss of the amplifier and the Class-G power generator.

Figure 2.1 Load-adaptive Class-G stereo headphone amplifier architecture

Figure 2.1 depicts the architecture of the load-adaptive Class-G stereo headphone amplifier, which is powered from a 1.8 V output buck converter with 85% efficiency. The amplifier consists of two identical audio channels with an audio power

management unit (PMU). The PMU includes a negative charge pump (NCP) that provides a fixed -1.8 V negative supply, a low-current capless LDO, and a negativevoltage regulator, which provide regulated supplies to the critical analog circuits. A multi-mode dual-voltage charge-pump (MMDV-CP) and an impedance detector are embedded in the amplifier for the load-adaptive Class-G operation. The MMDV-CP generates either a high (±VDDH) or a low (±VDDL) supply level according to the input digital signal level, where the values of VDDH and VDDL are decided by the headphone impedance and the gain setting of amplifiers. For different impedance levels, the charge-pump can provide four voltage rails ( $\pm V_{DD}$ ,  $2/3V_{DD}$ ,  $1/2V_{DD}$  and  $1/3V_{DD}$  to best fit the signal profile and reduce the power loss of the amplifier. The Class-G switching scheme is mainly determined by the power efficiency of the MMDV-CP. Frequent switching of the supply rails is prohibited if the increase of the current efficiency by the Class-G operation is less than the current dissipated by the Class-G charge-pump. Different from heavy loads (under  $50\Omega$ ), the load current reduction by the Class-G operation for light loads is not obvious. For the same output power requirement, the load current delivered to a  $600\Omega$  is much smaller than the current into a  $16\Omega$  load.

To improve the power efficiency of the Class-G charge pump during the supply rails switching, a hold-time mechanism is used in the charge-pump controller design to prevent frequent switching of the supply rails. By increasing this hold time, the switching power loss of the Class-G charge-pump is reduced. For higher headphone impedance with less current benefit by the Class-G operation, a longer hold time is recommended to reduce the power loss of charge pump. The switching period for

30

their realization is set to 1msec, and the hold time for a  $600\Omega$  load is approximately 40msec. In addition, the authors highlighted the underlying PSRR issue in the Class-G output stages, where the supply switching due to the Class-G operation may degrade audio signal quality. The authors introduced an additional correction loop within the PA to help reduce this effect.

Figure 2.2 Total-path efficiency versus output power level

The authors solution achieves a maximum output power of 62mW, 108 dB DR, -95dB minimum THD+N, and 1.35mA/channel quiescent current from the 1.8V supply.

Figure 2.2 shows the total path power efficiency comparison between this solution, several other Class-G solutions (with different supply configurations), and the classical Class-AB implementation. Due to the adaptive nature of this design, the power efficiency tracks the envelope of the several other Class-G solutions, which of course comes at the expense of added complexity and circuitry that enables the supply to track the gain and load changes.

#### 2.2 JSSC Nov 2014 Class-D [17]

In this paper, the authors implemented several techniques to enhance THD+N and PSRR for the classical Class-D audio driver.

Figure 2.3 Class-D structure of the JSSC Nov 2014 paper

The architecture shown in Figure 2.3 includes a feed-forward ADC path, feedback filter, and edge-rate control in the driver stage. The feed-forward path is designed to process the signal so that the loop filter can process only the difference between the input and the feedback signals. Thus, the loop filter responds primarily to errors injected into the loop. This architecture extends the operating range of the loop filter to support a larger signal level and, therefore, a larger output power capability. To avoid PSRR performance degradation due to the feed-forward architecture, the loop filter, feedback, and feed-forward paths are powered by an internally-compensated LDO, which consumes 50  $\mu$ A of quiescent current and requires less than 1% of the Class-D amplifier area. Instead of using simple resistor feedback, the proposed architecture includes filters in the feedback path to reduce the high-frequency intermodulation distortion associated with

direct feedback and eliminate the loop filter input common-mode disturbance from the Class-D output. The design is implemented using a 180 nm CMOS and achieves 1.75 W into an 8 $\Omega$  speaker, 105 dB SNR, 95% efficiency, -88dB peak THD+N, and 96dB PSRR at 217Hz. The quiescent current is not reported but can be estimated to be close to 5mA from the efficiency plot.

# 2.3 IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS Sep 2016 Class-AB [4]

In this paper, the authors are focused on optimizing the quiescent current consumption of the headphone driver. This is done by an attempt to solve a classical problem in which the transconductance of the output stage of a linear amplifier design has a wide variation as a function of the load current, and therefore stability optimization becomes complicated. A brute-force solution is to conduct enough quiescent current in the output stage, so the stability is guaranteed in the worst case (i.e. for a zero-amplitude output). In this paper, the authors propose a new solution where the output load current is sensed and used to adjust the second-stage pole for a Class-AB three-stage driver to guarantee the stability for all load current conditions. Figure 2.4 shows the Class-AB amplifier used, which consists of three stages and a current sensing block, which senses the load current through the gate voltage of the output devices and controls the small signal resistances of M21 and M22 inside the second stage to change the second pole location as a function of the load current.

Figure 2.4 Class-AB driver schematic

The prototype chip is implemented in a 55 nm CMOS process. The measured static current consumption of the core circuit is 0.35 mA with a 1.8 V supply voltage. Measurement verified -85 dB THD+N, 106 dB signal dynamic range, and 55 mW output power under a wide range of load capacitances from 5 pF to 20 nF. Figure 2.5 shows the measured THD+N vs signal for the driver when powered by a fixed supply and a Class-G supply. The THD+N degradation starts approximately at a signal amplitude of -18dBV for both cases but gets much worse for Class-G supply.

Figure 2.5 Measured A-weighted THD+N versus input signal amplitude for 1 kHz signal frequency, 0 dB gain

# 2.4 IEEE TRANSACTIONS ON VLSI SYSTEMS JUNE 2017 Class-H [13]

This paper presents a Class-H power amplifier aiming for audio applications on battery-powered electronic devices. The power supply of the amplifier is adaptively adjusted to track the instantaneous input signal amplitude for higher power efficiency. By embedding audio input signal amplitude information into the Class-AB amplifier's output common-mode voltage level, the amplifier can operate with only single-rail power supply. This solution is not applicable as a headphone driver because it assumes a differential load and thus it uses a differential amplifier. However, it is still useful to discuss this paper here to develop some understanding of the achievable THD performance when Class-H is used.

Figure 2.6 System-level illustration of the proposed Class-H amplifier

Figure 2.6 illustrates the proposed amplifier, which consists of three building blocks: A fully differential Class-AB amplifier, an input amplitude detection (IAD) block, and a buck converter. The audio input signal VIN is fed simultaneously into the main Class-AB amplifier as well as the IAD block, through which, the instantaneous signal amplitude is measured and processed. Output voltage VREF is used as the reference voltage of the buck converter. To ensure maximal output swing at all times, 1/2 VREF is taken as the reference voltage to the common-mode feedback (CMFB) circuit of the Class-AB amplifier VOCM.

As illustrated in Figure 2.7, the proposed design has two operation modes, which are dependent on the input signal amplitude. For small input signal levels, the amplifier works like a normal Class-AB amplifier with its output CM level VOCM biased at half of VDDL. When the input signal exceeds this threshold, the system enters Class-H mode where VOCM tracks the extracted reference voltage. This process makes one of the output nodes swing up with a doubled gain and the other stay at a predefined dc level VDSAT.

Figure 2.7 Amplifier output waveforms with sinusoidal input signals

The prototype was fabricated in a 0.18-µm CMOS process, and consumes 3.52 mW quiescent power, not including the supply generation circuit. The circuit is able to deliver up to 263 mW peak output power to a  $16\Omega$  load and achieves a peak THD+N ratio of -80 dB. The peak power efficiency of the system is 80.4%. Figure 2.8 shows the measured efficiency plot. Quite interestingly the authors argued that using Class-H instead of Class-D reduces the external component cost because of saving the external LC components; however, in order to generate the Class-H supply, the authors had to use a buck converter, which inevitably uses an external LC filter.

Figure 2.8 Class-H measured efficiency plot

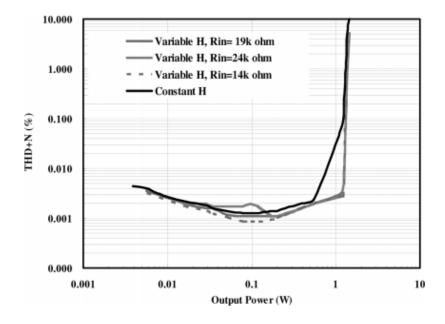

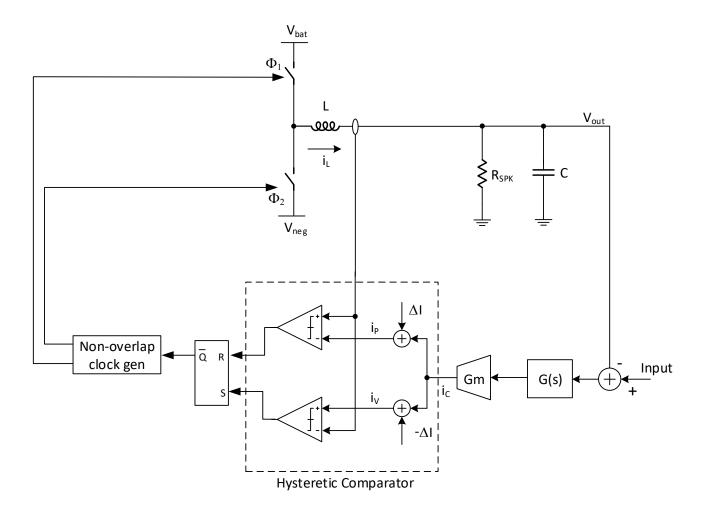

#### 2.5 JSSC Oct 2011 Sliding-mode class-D [14]

A hysteretic modulator consisting of a third-order self-oscillating Class-D audio amplifier that utilizes a hysteretic comparator is presented. The hysteretic modulator potentially allows for a low-cost implementation by eliminating the requirement for an external high-quality carrier. The authors argued that one of the concerns in the design of hysteretic modulators is the decrease of the switching frequency with input amplitude, which can deteriorate the loop gain and linearity performance as the output power level increases, or even cause stability problems in a high-order design. As a solution, the authors presented a frequency stabilization technique based on continuous variation of the hysteresis window in response to the input amplitude to minimize the variation of the switching frequency.

Figure 2.9 Sliding-mode system architecture

Figure 2.9 shows the system architecture used in this paper, which consists of a third-order loop with a hysteretic comparator. For such a high-order loop filter, the swing of the first integrator is limited by the hysteretic comparator itself; however, the last two integrators, are prone to clipping due to power supply limitation when the integrators try to generate a large error correction term in response to a large input. When the switching frequency decreases below a certain value, the output of the third integrator clips, and the loop gain, and error correction degrade rapidly. Consequently, the performance becomes worse than that of a first-order modulator.

To alleviate this degradation, the hysteresis factor is varied in response to the input level, so that the switching frequency can be adjusted properly to reduce the swing of the last integrator. By using this technique, high linearity is achieved with consistent distortion performance up to relatively high-power levels; i.e., nearly 90% of the maximum output power.

The chip prototype is implemented in a  $0.7\mu m$  CMOS process and realizes a fully differential topology driving an  $8\Omega$  load while achieving DR of 116.5 dB, a THD+N of 0.0012%, and output power of 125 mW. Using a 5V power supply the amplifier can deliver 1.45 W into the load with a 5% THD. The efficiency is greater than 84% for output power larger than 1 W. The authors did not report the power consumption, but it can be estimated that the quiescent current is about 20mA from their efficiency plot.

Figure 2.10 shows the measured THD+N vs the output power.

Figure 2.10 Measured THD+N vs output power plot

## CHAPTER 3 Proposed System Architecture

#### 3.1 Architecture

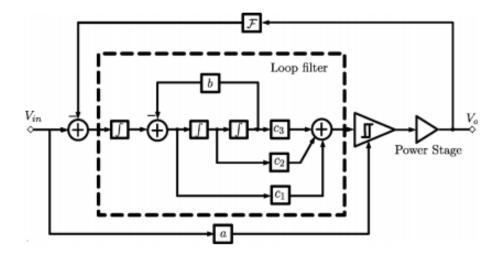

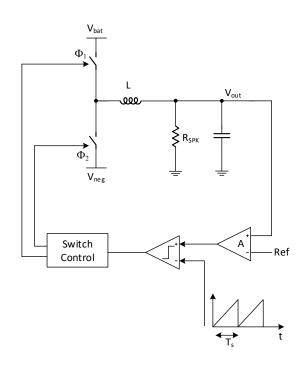

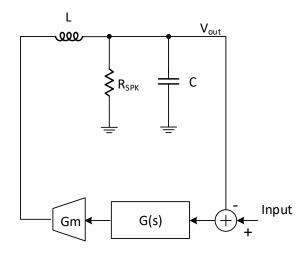

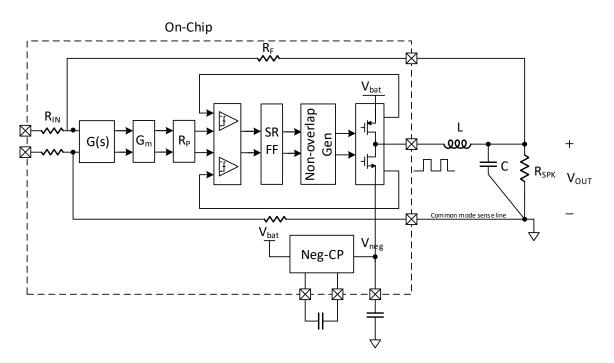

The proposed architecture is a switching topology that consists of a singleended switching output stage followed by an LC filter whose output is fed back to the error amplifier. A simplified version of the system architecture is shown in Figure 3.1.

Figure 3.1 Simplified proposed architecture

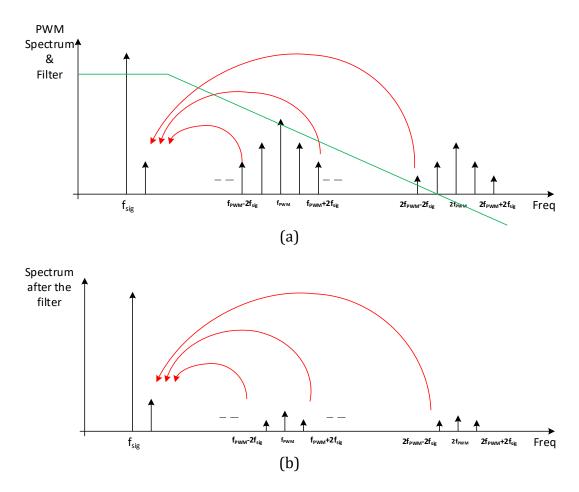

Unlike classical switching topologies, the LC loop filter is included in the feedback loop, which offers several advantages:

1. Attenuating the output switching ripples:

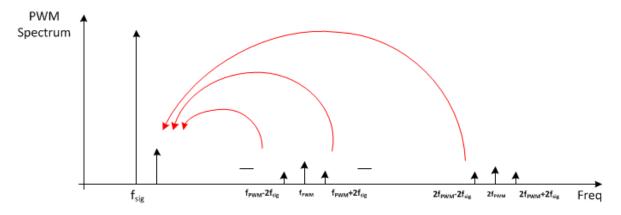

The PWM spectrum has a low-frequency signal content in addition to the upconverted signal and harmonics around the carrier frequency, as shown in Figure 3.2. Since, the output signal is fed back to the error amplifier, whose output gets sampled within the loop, the harmonic content around the carrier frequency gets mixed with the carrier frequency and all the harmonics are folded back into the audio band, degrading the linearity of the system as shown in Figure 3.2a. The proposed architecture addresses this point by including the LC filter within the loop

before the feedback point, thereby filtering the output of the switching stage before being fed back. Depending on the LC corner frequency, the high-frequency harmonics are attenuated, and the audio foldback can be tolerated, which results in overall better linearity performance as shown in Figure 3.2b.

Figure 3.2 (a) PWM spectrum before filter and filter response, (b) PWM

spectrum after filtering.

2. LC filter non-linearity is also attenuated:

The switching topologies usually employ an LC filter to attenuate the Electromagnetic Interference (EMI), which is an FCC requirement [22]. The LC filter is typically placed off-chip between the Class-D driver and the load. However, the

variations of the inductance and capacitance [23, 24] can lead to a variation of the audio band gain as a function of the signal swing, which translates into distortion.

In the proposed architecture, since the LC is pushed inside the loop, any change to the corner frequency is corrected by the negative feedback action, and therefore the distortion components are attenuated by the in-band loop gain.

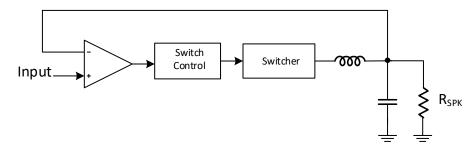

#### **3.2 Power Stage and Control Scheme.**

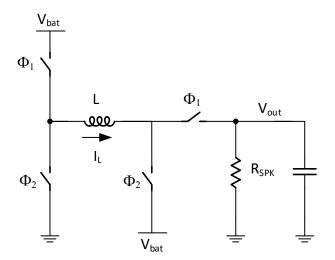

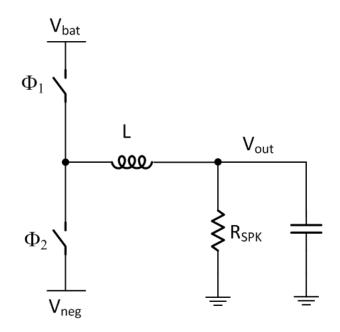

Before discussing the details of the system design, it is important to first discuss the power stage architecture to lay foundations for later discussions on how the system control works. More detailed discussion on the power stage details and comparison against other possible options will be elaborated on in Chapter 4. Figure 3.3 shows a simplified version of the power stage, which is a half-bridge Class-D topology with dual supplies (also known as a buck converter).

Figure 3.3 Simplified power stage

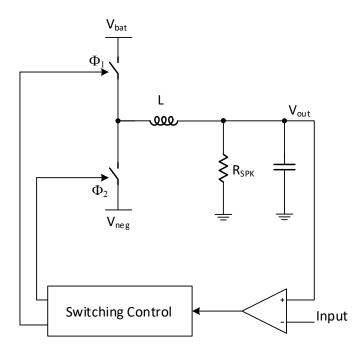

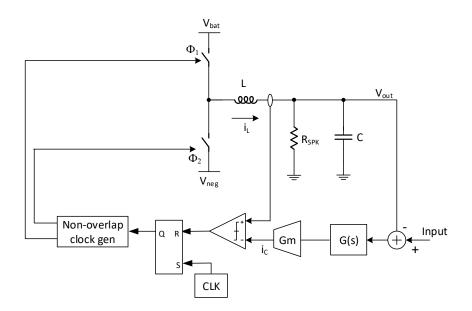

The high- and low-side switches, usually PMOS and NMOS respectively, are controlled by a non-overlapping clock generator that is embedded inside the switching control block as shown in Figure 3.4.

Figure 3.4 A simplified block diagram for the switching regulator

The switching control block receives an error signal that results from comparing the output to the input signal. This error signal then drives the output stage to ensure the output tracking. The switching regulator loop, as the name implies, converts an input voltage to a desired output voltage by turning the input voltage on and off; i.e., this method involves chopping the input voltage and smoothing it out to match the required output voltage. There are two principal methods by which the input voltage is chopped: (1) Pulse Frequency Modulation (or Discontinuous Conduction Mode), abbreviated as PFM/DCM [25].

(2) Pulse Width Modulation (or Continuous Conduction Mode), abbreviated as PWM/CCM [25].

Details on how the two schemes work are described below.

## 3.2.1 PFM/DCM Approach

The PFM method is of two types: fixed-on time or fixed-off time. An example of the fixed-on type is shown in Figure 3.5, for which on-time is fixed, and off-time is variable; this means that the length of time it takes for V<sub>bat</sub> to connect to the output next time varies. When the load current increases, the number of on-times in a given length of time is increased to keep pace with the load. Thus, under a heavy load, the frequency increases, and under a light load it diminishes.

Figure 3.5 Fixed on-time PFM/DCM scheme

Figure 3.6 shows how the output stage control, inductor current, and output voltage vary under a light load condition. The output voltage is bounded between two levels set by V<sub>High</sub> and V<sub>Low</sub>, and the output is continuously being compared against these 2 thresholds, and once it falls below the lower threshold, V<sub>Low</sub>, the control block enables the high-side switch for a fixed period T<sub>ON</sub>, during which the current in the inductor ramps up from 0 to I<sub>Peak</sub>. As a result, V<sub>OUT</sub> increases, then follows a period T<sub>OFF</sub> during which the inductor current ramps down to zero. The operation repeats until V<sub>OUT</sub> reaches the high threshold V<sub>High</sub>, after which V<sub>OUT</sub> is left unregulated while the output capacitor discharges because of the current loading. Once V<sub>OUT</sub> drops below V<sub>Low</sub>, the overall procedure repeats.

This scheme is attractive to use for light loading condition, because of the reduced switching frequency, which translates to less dynamic power losses and thus, higher efficiency. On the negative side, for a light load the loop is kept unregulated during T<sub>OFF</sub>, which means that for an audio input, no rejection of any nonlinearity or disturbance is applied during this time, and therefore distortion or supply disturbances may impact the fidelity of V<sub>OUT</sub>.

Figure 3.6 Output stage control, inductor current, and output voltage for PFM/DCM scheme

#### 3.2.2 PWM/CCM Approach

The PWM method represents the most commonly employed voltage control method. In this method, the duty cycle of the switching pulses changes to produce the required average output value. The switching action is continuous even for a light load, which forces the output to follow the audio input at the expense of more switching losses and less efficiency compared to PFM.

The continuous switching action for CCM enables the continuous application of a negative feedback mechanism. This ensures that the average output can follow the input signal closely while rejecting the disturbance on either the negative or positive switching stage supply by modulating the pulse width.

Figure 3.7 PWM/CCM control scheme

Figure 3.7 shows an example for a PWM system, where an error amplifier with large gain (A) compares the input reference with the output, from which the error signal is compared to a periodic sawtooth waveform with a frequency (1/Ts). Thanks to the sawtooth waveform, the comparator output can produce a pulse-width-modulated signal as a function of the error amplifier output. Slope compensation is often required for PWM systems if the output duty cycle is larger than 50% to prevent loop instability [25].

In this work PWM is used to ensure that the audio output can track the input reliably for all input levels and load conditions.

#### 3.3 Study of Loop Stability

#### 3.3.1 Switcher AC model

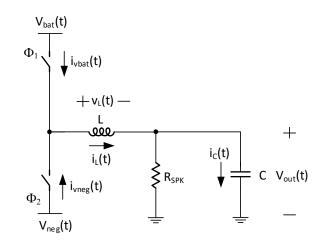

To study the PWM loop stability, an ac model for the switcher needs to be devised and all the required parameters for the ac model are labeled on Figure 3.8.

Figure 3.8 Output stage diagram with the ac model parameters labeled

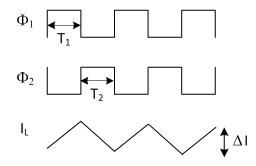

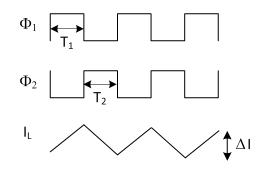

Clock phases  $\phi_1$  and  $\phi_2$  are assumed to be non-overlapping with duty cycle d(t) and d'(t) respectively, and a period T<sub>S</sub>. Each of the parameters shown in Figure 3.8 has a low- frequency, and high-frequency component due to the switching action. For example, V<sub>bat</sub> carries a DC value and a high-frequency switching ripple while V<sub>out</sub>(t)

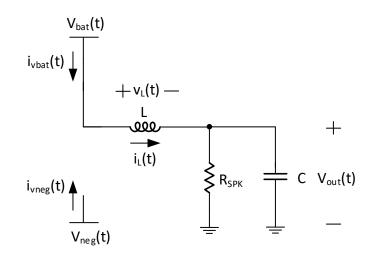

Figure 3.9 Output stage during  $\phi_1$

carries the output audio signal and a high-frequency switching ripple. For the purpose of the stability analysis, the high-frequency ripples are eliminated, and the moving average technique is used to extract the low-frequency content for  $v_{bat}(t)$ ,  $v_{neg}(t)$ ,  $v_{out}(t)$ ,  $i_L(t)$  in order to calculate the average value for  $v_L(t)$ ,  $i_C(t)$ ,  $i_{vbat}(t)$ , and  $i_{vneg}(t)$  in both phases.

During  $\phi_1$ , the output stage can be simplified as shown in Figure 3.9, and the following equations hold:

$$v_L(t) = \langle v_{bat}(t) \rangle_{T_S} - \langle v_{out}(t) \rangle_{T_S}$$

(3.1)

$$i_{C}(t) = \langle i_{L}(t) \rangle_{T_{S}} - \frac{\langle v_{out}(t) \rangle_{T_{S}}}{R_{SPK}}$$

(3.2)

$$i_{vbat}(t) = \langle i_L(t) \rangle_{T_S} \tag{3.3}$$

$$i_{vneg}(t) = 0 \tag{3.4}$$

Where  $\langle x(t) \rangle_{T_S}$  represents the moving average for x(t) over one period and is given by:

$$\langle x(t,T_S) \rangle_{T_S} = \frac{1}{T_S} \int_t^{t+T_S} x(\tau) d\tau$$

(3.5)

Since x(t) represent a stationary process, then  $\langle x(t,T_S) \rangle_{T_S} = \langle x(t) \rangle_{T_S}$

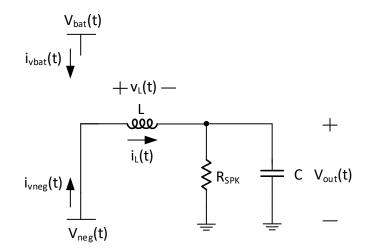

Figure 3.10 Output stage during  $\phi_2$

During  $\phi_2$ , the output stage can be simplified as shown in Figure 3.10:

$$v_L(t) = \langle v_{neg}(t) \rangle_{T_S} - \langle v_{out}(t) \rangle_{T_S}$$

(3.6)

$$i_{C}(t) = \langle i_{L}(t) \rangle_{T_{S}} - \frac{\langle v_{out}(t) \rangle_{T_{S}}}{R_{SPK}}$$

(3.7)

$$i_{vneg}(t) = \langle i_L(t) \rangle_{T_S}$$

(3.8)

$$i_{vbat}(t) = 0 \tag{3.9}$$

Now that  $v_L(t)$ ,  $i_C(t)$ ,  $i_{vbat}(t)$  average values are calculated in  $\phi_1$  and  $\phi_2$  where the duty cycle is d and d' respectively, a weighted average over the entire cycle is given by:

$$\langle v_L(t) \rangle_{T_S} = d(t) \cdot \left[ \langle v_L(t) \rangle_{T_S} \right]_{\emptyset 1} + d'(t) \cdot \left[ \langle v_L(t) \rangle_{T_S} \right]_{\emptyset 2}$$

=  $d(t) \cdot \langle v_{bat}(t) \rangle_{T_S} + d'(t) \cdot \langle v_{neg}(t) \rangle_{T_S} - \langle v_{out}(t) \rangle_{T_S}$ (3.10)

$$\langle i_{C}(t) \rangle_{T_{S}} = \langle i_{L}(t) \rangle_{T_{S}} - \frac{\langle v_{out}(t) \rangle_{T_{S}}}{R_{SPK}}$$

(3.11)

$$\langle i_{vbat}(t) \rangle_{T_S} = d(t). \langle i_L(t) \rangle_{T_S}$$

(3.12)

$$\langle i_{vneg}(t) \rangle_{T_S} = d'(t) \cdot \langle i_L(t) \rangle_{T_S}$$

(3.13)

For the purpose of the stability analysis, an ac perturbation is applied to d and d' such that  $d(t) = D + \hat{d}(t)$  and  $d'(t) = D' - \hat{d}(t)$ . Due to this perturbation, each of the current and voltage variables (e.g. x(t)) can now be assumed to have two lowfrequency components: Intended low-frequency content (X) and an ac component ( $\hat{x}(t)$ ).

Substituting into (3.10) -(3.13) results in:

$$V_{L} + \hat{v}_{L}(t) = \left(D + \hat{d}(t)\right) \cdot \left(V_{bat} + \hat{v}_{bat}(t)\right) + \left(D' - \hat{d}(t)\right) \cdot \left(V_{neg} + \hat{v}_{neg}(t)\right) - \left(V_{out} + \hat{v}_{out}(t)\right) (3.14)$$

$$I_{L} + \hat{v}_{out}(t) = I_{L} + \hat{v}_{out}(t) \qquad (2.15)$$

$$I_{C} + \hat{\imath}_{C}(t) = I_{L} + \hat{\imath}_{L}(t) - \frac{v_{out} + v_{out}(t)}{R_{SPK}}$$

(3.15)

$$I_{vbat} + \hat{i}_{vbat}(t) = (D + \hat{d}(t)) \cdot (I_L + \hat{i}_L(t))$$

(3.16)

$$I_{vneg} + \hat{\iota}_{vneg}(t) = \left(D - \hat{d}(t)\right) \cdot \left(I_L + \hat{\iota}_L(t)\right)$$

(3.17)

To simplify (3.14)-(3.17), it is important to note that at steady state

$$i_L(t+T_S) = i_L(t)$$

(3.18)

$$V_C(t+T_S) = V_C(t)$$

(3.19)

This means that the average of  $v_L(t)$  taken over entire cycle  $(i.e.: \langle v_L(t) \rangle_{T_S})$  must have a zero average, i.e.:

$$V_L = 0 = D.V_{bat} + D'.V_{neg} - V_{out}$$

(3.20)

Similar argument applies yields that:

$$I_{C} = 0 = I_{L} - \frac{V_{out}}{R_{SPK}}$$

(3.21)

Substituting (3.20) and (3.21) into (3.14) -(3.17) and neglecting the second-order terms yields:

$$\hat{v}_L(t) = D.\,\hat{v}_{bat}(t) + D'.\,\hat{v}_{neg}(t) + \hat{d}(t).\,\left(V_{bat} - V_{neg}\right) - \hat{v}_{out}(t)$$

(3.22)