# UC San Diego UC San Diego Electronic Theses and Dissertations

## Title

Semiconductor Nanowires for Optoelectronic, Renewable Energy and Retinal Prosthetic Applications /

**Permalink** https://escholarship.org/uc/item/4dt0h9gb

## Author

Jing, Yi

**Publication Date** 2013

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA, SAN DIEGO

## Semiconductor Nanowires for Optoelectronic, Renewable Energy and Retinal Prosthetic Applications

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Applied Physics)

by

Yi Jing

Committee in charge:

Professor Deli Wang, Chair Professor Prabhakar R. Bandaru Professor Andrew C. Kummel Professor Jie Xiang Professor Paul K.L. Yu

2013

Copyright

Yi Jing, 2013

All rights reserved

The Dissertation of Yi Jing is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2013

# Dedication

To my family

# **Table of Contents**

| Signatu   | re Pageiii                                                                             |

|-----------|----------------------------------------------------------------------------------------|

| Dedicat   | ioniv                                                                                  |

| Table of  | f Contentsv                                                                            |

| List of H | iguresvii                                                                              |

| List of 7 | ۲ablesxi                                                                               |

| Acknow    | vledgementsxii                                                                         |

| Vita      |                                                                                        |

| Abstrac   | t of The Dissertationxviii                                                             |

| Chapter   | 1 : Introduction1                                                                      |

| 1.1       | Semiconductor Nanowires1                                                               |

| 1.2       | Surface States and Surface Recombination                                               |

| 1.3       | Light Absorption in Nanowires                                                          |

| 1.4       | Top-down Nanofabrication of Si Nanowires9                                              |

| 1.4.      | 1 E-beam lithography and nanoimprint lithography9                                      |

| 1.4.      | 2 Dry Etching of Si Nanowires                                                          |

| 1.4.      | 3 Metal Assisted Wet Chemical Etching of Si Nanowires                                  |

| 1.5       | Bottom-up growth of nanowires14                                                        |

| 1.6       | Scope of This Dissertation15                                                           |

| -         | 2 : Si Nanowire Photodetector Arrays for Image Sensing and Retinal<br>sis Applications |

| 2.1       | Introduction—Nanowire Photodetectors                                                   |

| 2.2       | Single Nanowire Photoconductors                                                        |

| 2.2.      | 1 Fabrication of Individual Addressable Si Nanowire Photodetector Array20              |

| 2.2.      | 2 Single Si Nanowire Photodetector Characterization                                    |

| 2.2.      | 3 Integration to CMOS for Image Sensor Applications                                    |

| 2.3       | Axial P-N Junction Si Nanowire Photodetectors                                          |

| 2.3.      | 1 Device Fabrication                                                                   |

| 2.3.      | 2 Device Characterization                                                              |

| 2.4                                                         | 4 Radial Junction Si Nanowire Photodetectors                                                                                                                                                                                                                                                                               | 34             |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.:                                                         | 5 Integration with Nanowire Solar Cell and Self-powered System                                                                                                                                                                                                                                                             |                |

| 2.                                                          | 6 Si Nanowire Photodetectors for Retinal Prosthesis                                                                                                                                                                                                                                                                        | 41             |

| 2.                                                          | 7 Conclusion                                                                                                                                                                                                                                                                                                               | 45             |

| Chapter 3 : Si Nanowires for Photovoltaic Applications      |                                                                                                                                                                                                                                                                                                                            | 47             |

| 3.                                                          | 1 Introduction                                                                                                                                                                                                                                                                                                             | 47             |

| 3.                                                          | 2 Planar Si Solar Cells with Si Nanowire Light Absorber                                                                                                                                                                                                                                                                    |                |

|                                                             | 3.2.1 Introduction                                                                                                                                                                                                                                                                                                         | 48             |

|                                                             | 3.2.2 Solution Etching of Si Nanowires                                                                                                                                                                                                                                                                                     | 49             |

|                                                             | 3.2.3 Device Fabrication and Characterization                                                                                                                                                                                                                                                                              | 51             |

|                                                             | 3.2.4 Conclusion                                                                                                                                                                                                                                                                                                           | 54             |

| 3.                                                          | 3 Si Nanowire Radial Junction Solar Cells                                                                                                                                                                                                                                                                                  | 54             |

|                                                             | 3.3.1 Introduction                                                                                                                                                                                                                                                                                                         |                |

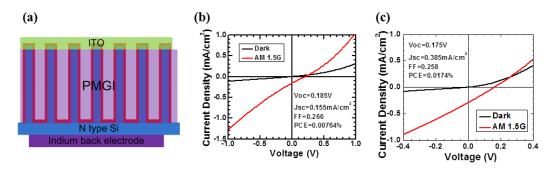

|                                                             | 3.3.2 Nanoscale Doping                                                                                                                                                                                                                                                                                                     |                |

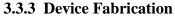

|                                                             | 3.3.3 Device Fabrication                                                                                                                                                                                                                                                                                                   |                |

|                                                             | 3.3.4 Effects of Doping Concentration of Nanowire Core                                                                                                                                                                                                                                                                     | 63             |

|                                                             | 3.3.5 Auger Recombination                                                                                                                                                                                                                                                                                                  | 68             |

|                                                             | 3.3.6 Effects of Surface Passivation                                                                                                                                                                                                                                                                                       | 72             |

|                                                             |                                                                                                                                                                                                                                                                                                                            |                |

|                                                             | 3.3.7 Conclusion                                                                                                                                                                                                                                                                                                           |                |

|                                                             | 3.3.7 Conclusion<br>pter 4 : III-V Nanowire Solar Cells                                                                                                                                                                                                                                                                    |                |

|                                                             | pter 4 : III-V Nanowire Solar Cells                                                                                                                                                                                                                                                                                        |                |

| Cha                                                         | <pre>upter 4 : III-V Nanowire Solar Cells 1 Introduction</pre>                                                                                                                                                                                                                                                             | 84<br>84       |

| Char<br>4.                                                  | <ul> <li>apter 4 : III-V Nanowire Solar Cells</li> <li>Introduction</li> <li>Catalyst-free Growth of InAs Nanowires</li> </ul>                                                                                                                                                                                             | 84<br>84<br>86 |

| Char<br>4.<br>4.                                            | <ul> <li>apter 4 : III-V Nanowire Solar Cells</li> <li>Introduction</li> <li>Catalyst-free Growth of InAs Nanowires</li> <li>Catalyst-free Growth of InAs based Core/multi-shell Nanowires</li> </ul>                                                                                                                      |                |

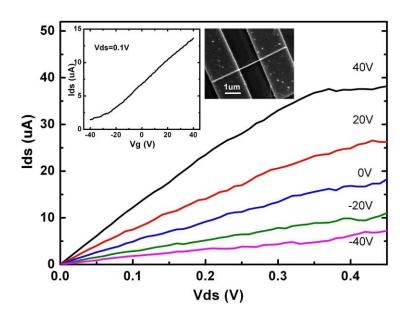

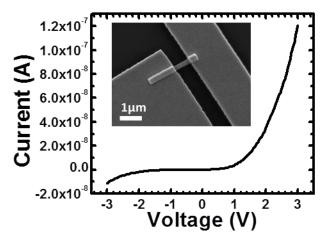

| Chay<br>4.<br>4.<br>4.                                      | <ul> <li>apter 4 : III-V Nanowire Solar Cells</li> <li>Introduction</li> <li>Catalyst-free Growth of InAs Nanowires</li> <li>Catalyst-free Growth of InAs based Core/multi-shell Nanowires</li> <li>Transport Properties of Single InAs Nanowire</li> </ul>                                                                |                |

| Chay<br>4.<br>4.<br>4.<br>4.                                | <ul> <li>apter 4 : III-V Nanowire Solar Cells</li> <li>Introduction</li> <li>Catalyst-free Growth of InAs Nanowires</li> <li>Catalyst-free Growth of InAs based Core/multi-shell Nanowires</li> <li>Transport Properties of Single InAs Nanowire</li> <li>III-V Core/multi-shell Nanowire Solar Cells</li> </ul>           |                |

| Chay<br>4.<br>4.2<br>4.2<br>4.2<br>4.2<br>4.2               | <ul> <li>apter 4 : III-V Nanowire Solar Cells</li> <li>Introduction</li> <li>Catalyst-free Growth of InAs Nanowires</li> <li>Catalyst-free Growth of InAs based Core/multi-shell Nanowires</li> <li>Transport Properties of Single InAs Nanowire</li> <li>III-V Core/multi-shell Nanowire Solar Cells</li> </ul>           |                |

| Chay<br>4.<br>4.2<br>4.2<br>4.2<br>4.2<br>4.2               | <ul> <li>III-V Nanowire Solar Cells</li> <li>Introduction</li> <li>Catalyst-free Growth of InAs Nanowires</li> <li>Catalyst-free Growth of InAs based Core/multi-shell Nanowires</li> <li>Transport Properties of Single InAs Nanowire</li> <li>III-V Core/multi-shell Nanowire Solar Cells</li> <li>Conclusion</li> </ul> |                |

| Chay<br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>4.<br>6<br>Chay | <ul> <li>III-V Nanowire Solar Cells</li></ul>                                                                                                                                                                                                                                                                              |                |

# **List of Figures**

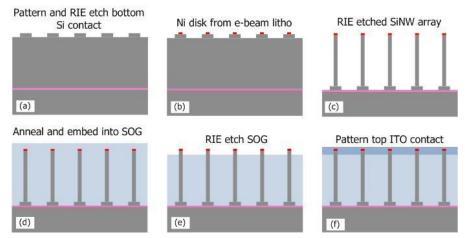

| Figure 2.1: Process flow for fabrication of individually addressable vertical Si nanowire photoconductor array                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

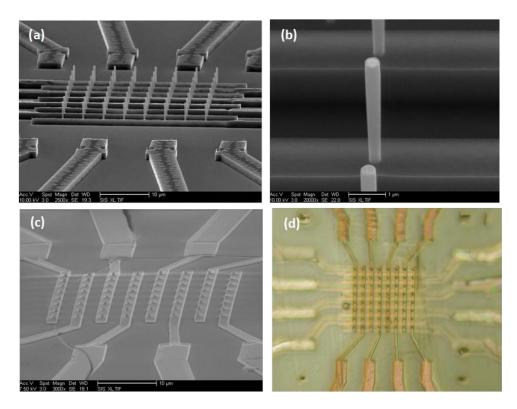

| <ul> <li>Figure 2.2: (a) A SEM image (75° tilted view) of Si nanowires array. (b) A magnification of SEM image (45° tilted view) of Si nanowires. (c) A SEM image of Si nanowire photoconductor array. (d) Optical microscope image (top view) of Si nanowire photoconductor array</li></ul>           |

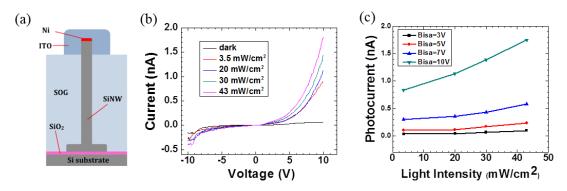

| <ul><li>Figure 2.3: (a) Schematics of a single Si nanowire photodetector. (b) I-V curves of a representative Si nanowire device under dark and illumination with varying light intensities. (c) Curves of photocurrent as a function of incident light intensity at different applied biases</li></ul> |

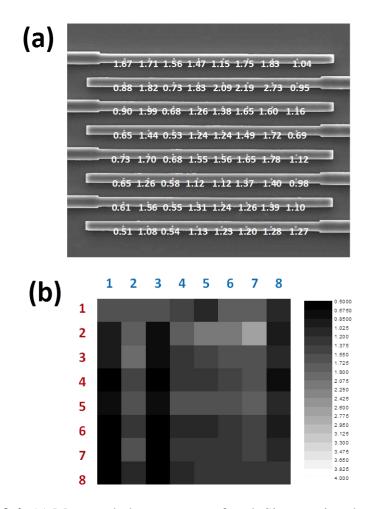

| <ul><li>Figure 2.4: (a) Measured photocurrents of each Si nanowire photodetector in the array.</li><li>(b) A simple demonstration of the response of the photodetector array as an image sensor to uniform white light illumination with each device representing one pixel.</li></ul>                 |

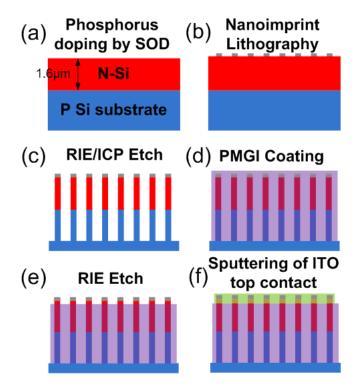

| Figure 2.5: Schematics of fabrication process of Si axial p-n junction photodetectors                                                                                                                                                                                                                  |

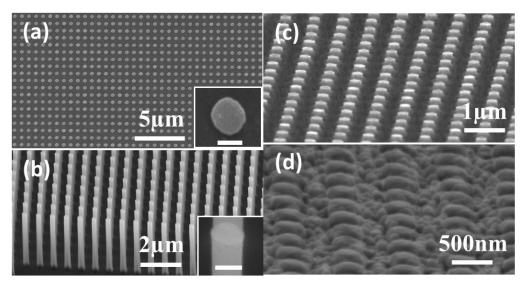

| <ul> <li>Figure 2.6: (a) SEM images of Ni dot array. (b) SEM images of vertical Si nanowire array. (c) A SEM image of Si nanowires embedded in PMGI with expose nanowire tips. (d) A SEM image of Si nanowire device with sputtered ITO top contact at 45<sup>o</sup> tilted view.</li> </ul>          |

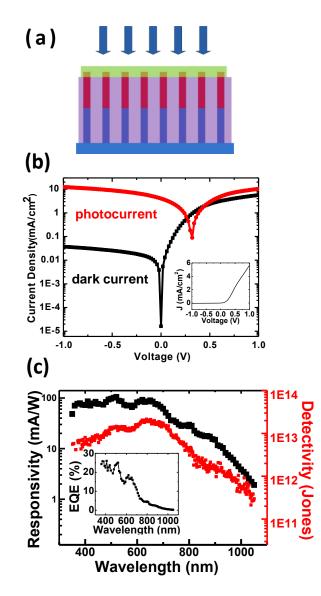

| Figure 2.7: (a) Schematic of a Si axial junction nanowire photodiode. (b) Semi-log I-V curves of a typical photodiode under dark and with white light illumination (100 mW/cm <sup>2</sup> ). (c) Spectra photoresponsivity and specific detectivity of the photodiode under zero bias                 |

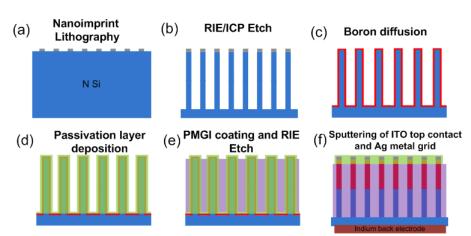

| Figure 2.8: Fabrication Process of Si radial junction nanowire photodiodes34                                                                                                                                                                                                                           |

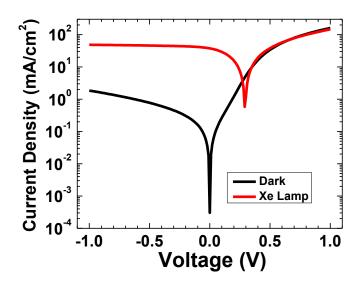

| Figure 2.9: Representative I-V curves of the Si radial junction nanowire photodiode measured under dark and illumination with a white light source (Xe arc lamp, 100 mW/cm <sup>2</sup> )                                                                                                              |

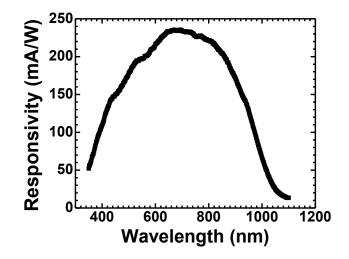

| Figure 2.10: Spectra responsivity of Si radial junction nanowire with Al <sub>2</sub> O <sub>3</sub> passivation                                                                                                                                                                                       |

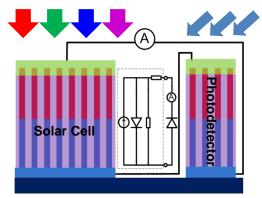

Figure 2.11: Illustration of the Si axial junction nanowire photodetector driven by a Si

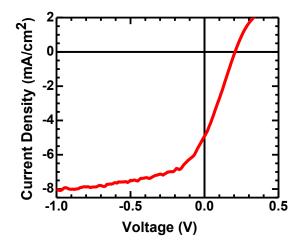

| Figure 2.12: I-V curve of a representative Si nanowire axial p-n junction solar cell measured with AM 1.5G illumination (100 mW/cm <sup>2</sup> )39                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

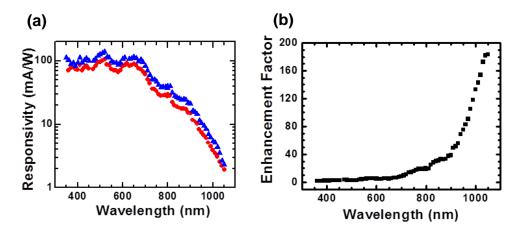

| <ul> <li>Figure 2.13: (a) Spectra responsivity of the nanowire photodetector driven by a nanowire solar cell (▲). The (●) curve is the responsivity at zero voltage bias for comparison. (b) Enhancement factor of the responsivity40</li> </ul>                                                  |

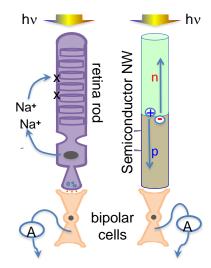

| Figure 2.14: Illustration of a Si axial p-n junction nanowire photodetector served as photoreceptor to generate charges for retinal neuron stimulation                                                                                                                                            |

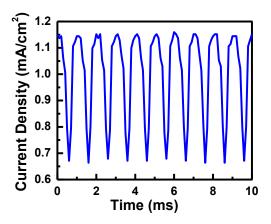

| Figure 2.15: Time-resolved photocurrent measured by switching white light illumination at a frequency of 1000 Hz                                                                                                                                                                                  |

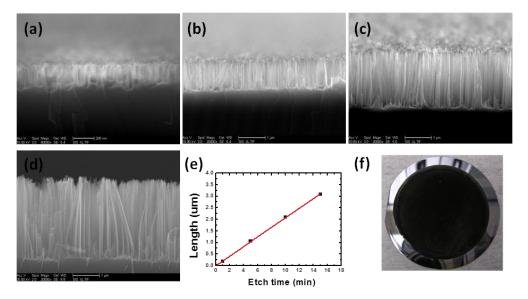

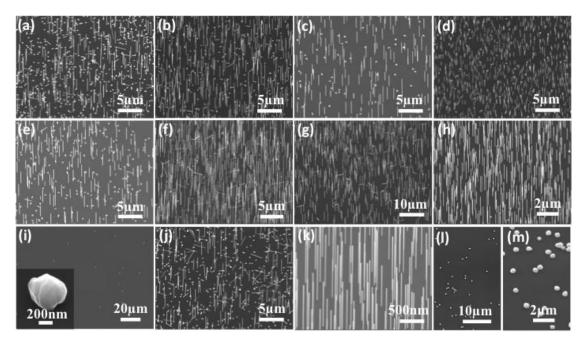

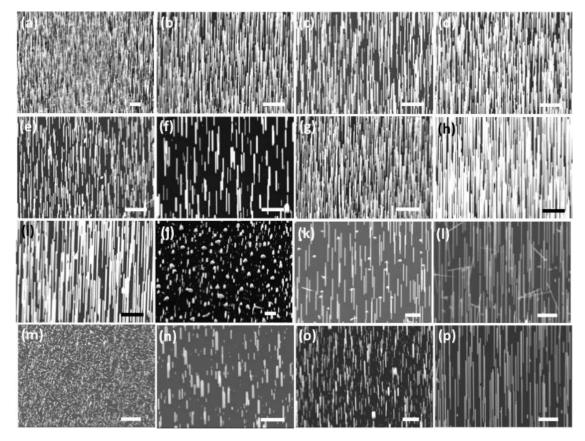

| <ul><li>Figure 3.1: SEM images of Si wafers etched for different amounts of times (a) 1 min;</li><li>(b) 5 min; (d) 10 min; (d) 15 min. (e) Plot of nanowire length vs. etch time. (f) Optical image of a large-area Si nanowire array created on a 2-inch Si wafer with 20 min etching</li></ul> |

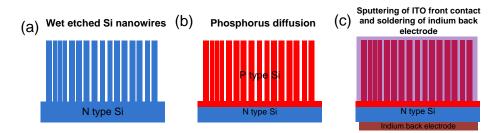

| Figure 3.2: Illustration of fabrication process of planar Si solar cell with nanowire absorber                                                                                                                                                                                                    |

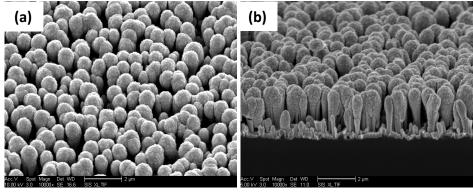

| Figure 3.3: SEM images of Si nanowire based solar cell with ITO front contact at (a) 45 °tilted view, and (b) 75 °tilted view                                                                                                                                                                     |

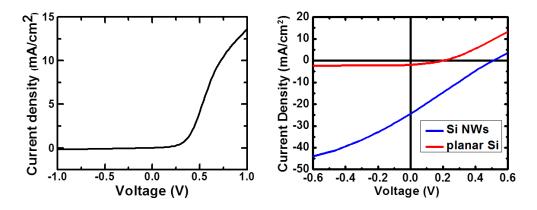

| Figure 3.4: (a) I-V characteristics of a typical Si nanowire based solar cell measured under dark condition. (b) I-V characteristics of a typical Si nanowire based solar cell (blue) and a planar device (red) with AM 1.5G illumination (100 mW/cm <sup>2</sup> )                               |

| Figure 3.5: Illustration of the radial junction nanowire solar cell                                                                                                                                                                                                                               |

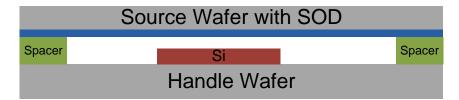

| Figure 3.6: Schematic of boron diffusion using SOD in RTA57                                                                                                                                                                                                                                       |

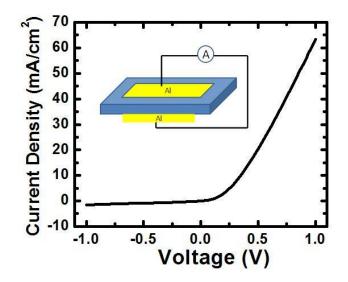

| Figure 3.7: I-V curve of doped Si p-n junction. One-step diffusion was carried out at 800 °C for 20 s. The inset is the schematic of the p-n diode                                                                                                                                                |

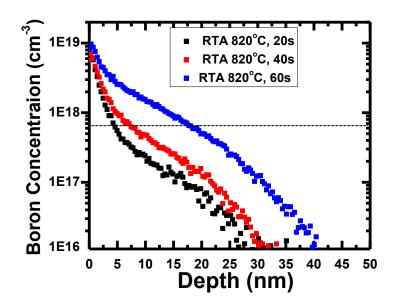

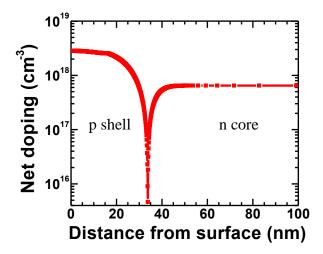

| Figure 3.8: SIMS analysis of boron distribution profile in planar Si. The Si was doped<br>using one-step diffusion at 820 °C for 20 s, 40 s and 60 s, respectively.<br>The doping concentration of n-type Si wafer is $6.5 \times 10^{17}$ cm <sup>-3</sup> 59                                    |

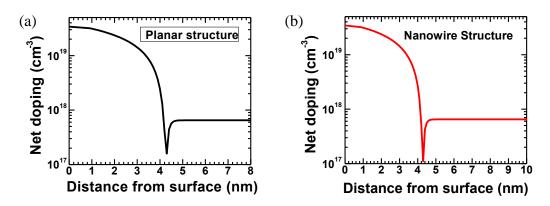

| Figure 3.9: Silvaco Athena simulations of boron profiles in Si diffused at 820 °C for 20 s in (a) planar geometry and (b) cylindrical geometry. N-type Si with an arsenic concentration of $6.5 \times 10^{17}$ cm <sup>-3</sup> is considered                                                    |

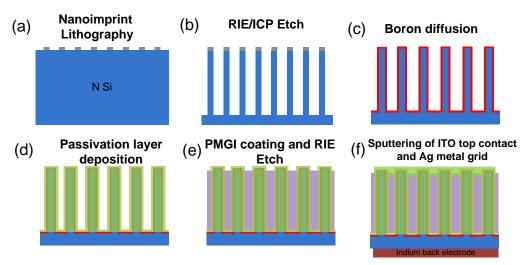

| Figure 3.10: The fabrication process of Si nanowire radial junction solar cells                                                                                                                                                                                                                   |

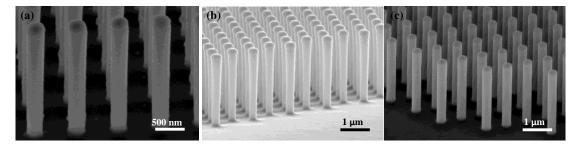

| Figure 3.11: SEM images of (a) as-etched Si nanowires, (b) Si | nanowires embedded in |

|---------------------------------------------------------------|-----------------------|

| PMGI, and (c) Si nanowires with 300 nm ITO top                | contact               |

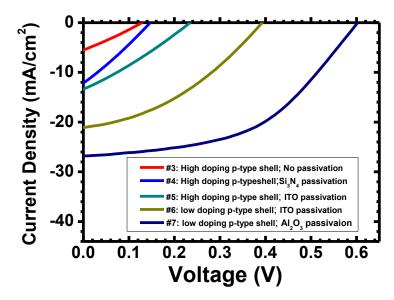

- Figure 3.15: I-V curves of Si nanowire radial junction solar cells measured under AM 1.5G illumination (100 mW/cm<sup>2</sup>)......71

- Figure 3.16: SEM images of Si radial junction nanowires with a layer of passivation material as shell: (a) PECVD Si<sub>3</sub>N<sub>4</sub>, (b) ITO, and (c) ALD Al<sub>2</sub>O<sub>3</sub>.......76

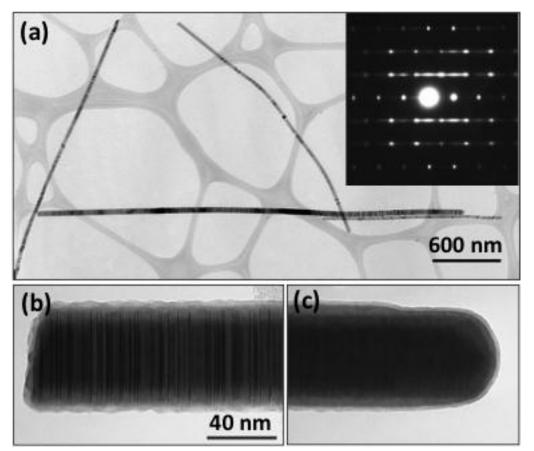

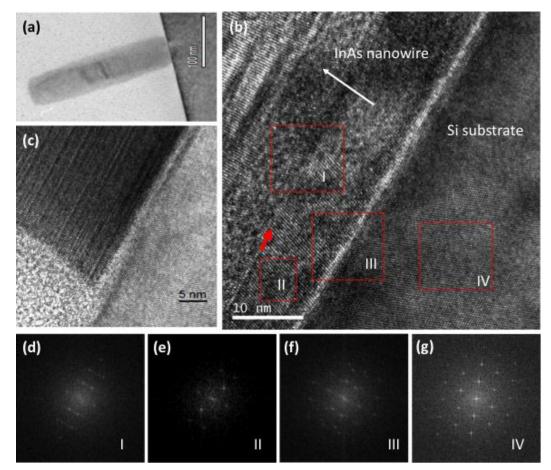

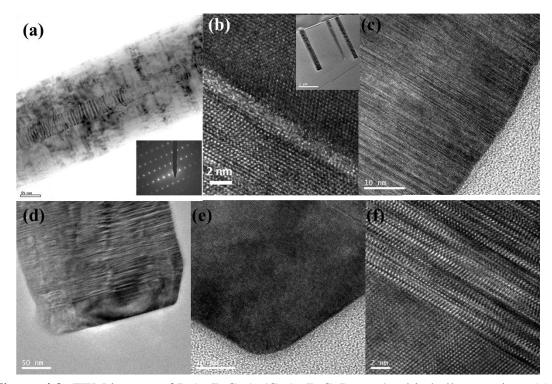

- Figure 4.5: Cross sectional TEM images of InAs nanowires grown for 5 min on Si (111). (a) Low resolution TEM showing InAs nanowires embedded in PMGI. (b) and (c) HRTEM of InAs/Si interface. Fast Fourier transforms of (d) region I, (e) region II, (f) region III, and (g) region IV......101

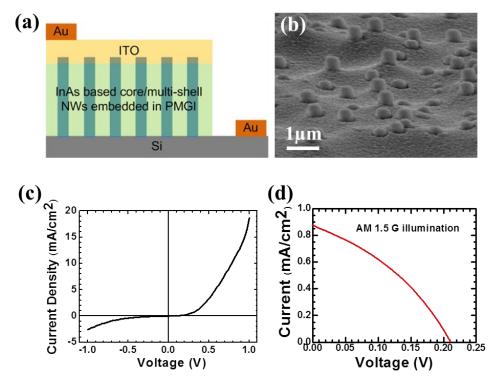

- Figure 4.12: (a) Schematic of InAs/InGaAs/GaAs/InGaP core/multi-shell nanowire solar cell. (b) A SEM image of front surface of device with ITO front contact. I-V measurement of InAs(n)/InGaAs/GaAs/InGaP(p) nanowire solar cell (c) under dark, and (d) with AM 1.5G illumination......114

# List of Tables

| Table 3.1: | Comparison of Si solar cells with and without nanowire as light absorber                                                                                                     |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.2: | Summery of performance of solar cells with different n-type core doping concentrations                                                                                       |

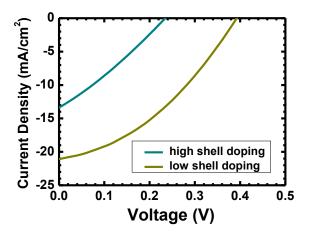

| Table 3.3: | Comparison of Si nanowire radial junction solar cells with different shell doping concentrations. The surface states of nanowires were passivated using a layer of ITO shell |

| Table 3.4: | A list of samples with different diffusion conditions and passivation materials                                                                                              |

| Table 3.5: | Summary of performance of solar cells with different p shell doping and passivation materials                                                                                |

## Acknowledgements

First of all, I would like to express my sincere gratitude to my advisor, Prof. Deli Wang, for his instruction during my time at UCSD. Over the years, he has always been supportive to my Ph.D study and research. He provided his knowledge and experience in semiconductor nanowire research. His guidance and advice helped me all the time of research and writing of this dissertation.

I would also like to thank all my committee members, Prof. Paul Yu, Prof. Jie Xiang, Prof. Andrew Kummel and Prof. Probhakar Bandaru for their valuable advice and insightful comments. I would also like to thank Prof. S. S. Lau for his guidance when I joined UCSD.

I appreciate the research help and friendships from my fellow labmates from Wang group. I thank Dr. Cesare Soci, Dr. Shadi Dayeh, Dr. Xinyu Bao, Wei Wei, David Aplin, Ke Sun, Muchuan Yang, Siarhei Vishniakou, Brian Lewis, Alieza Kargar, Atsushi Ohoka, Matt Chandrangsu for collaboration and useful discussions in my research. I would also like to thank Namseok Park, Conor Riley, Sun Young Noh, Zhelin Sun and the rest of lab for their friendships and support during my time a UCSD.

In addition, I would like to express my gratitude to our collaborators. Dr. Chulmin Choi in Prof. Sungho Jin's group at MAE department of UCSD, Huisu Jeong in Prof. Gun Young Jung's group at Gwangju Institute of Science and Technology, Korea helped us with the nanoimprint process. Soonshin Kwon in Prof. Jie Xiang's group at UCSD helped us with the low-temperature characterization of nanowire devices. Dr. Dajria Susac in Prof. Karen Kavanagh at Simon Fraser University and Dr. Chun Li in Dr. Yoshio Bando's group at National Institute of Material Science, Japan helped us with the transmission electron microscopy characterization of III-V nanowire structures. Dr. Massoud Khraiche in Prof. Gabriel Silva's provided valuable discussion on nanowire retinal prosthesis.

Last but not least, I am grateful to my parents and wife. I truly could not have done this without your love and support.

Chapter 2, in part, has been submitted for publication of the material as it may appear in Nano Letters 2013. Yi Jing, Huisu Jeong, Ke Sun, Muchuan Yang, Gun Young Jung, and Deli Wang, "High-detectivity vertical Si nanowire artificial photoreceptors for retinal prosthesis applications". The dissertation author was the primary investigator and author of this paper.

Chapter 3, in part, has been submitted for publication of the material as it may appear in ACS Nano 2013. Yi Jing, Siarhei Vishniakou, Chulmin Choi, Ke Sun, Huisu Jeong, Muchuan Yang, Alireza Kargar, Sungho Jin, Gun Young Jung, and Deli Wang, "Effects of Doping and Passivation on Radial junction Si nanowire arrays for photovoltaic applications". The dissertation author was the primary investigator and author of this paper.

Chapter 4, in part, has been accepted for publication in The Journal of Physical Chemistry C, 2013. Yi Jing, Xinyu Bao, Wei Wei, Chun Li, Ke Sun, David Aplin, Yong Ding, Zhong-Lin Wang, Yoshio Bando, and Deli Wang, "Catalyst-free heteroepitaxial MOCVD growth of InAs nanowires on Si substrates". The dissertation author was the primary investigator and author of this paper.

## Vita

| 2005 | Bachelor of Science, Physics<br>Peking University, Beijing, China                                     |

|------|-------------------------------------------------------------------------------------------------------|

| 2007 | Master of Science, Electrical Engineering (Applied Physics)<br>University of California, San Diego    |

| 2013 | Doctor of Philosophy, Electrical Engineering (Applied Physics)<br>University of California, San Diego |

#### **Publications**

- 1. **Yi Jing**, Xinyu Bao, Wei Wei, Chun Li, Ke Sun, David Aplin, Yong Ding, Zhong-Lin Wang, Yoshio Bando, and Deli Wang, "Catalyst-free heteroepitaxial MOCVD growth of InAs nanowires on Si substrates", The Journal of Physical Chemistry C, Accepted, 2013.

- Yi Jing, Huisu Jeong, Ke Sun, Muchuan Yang, Gun Young Jung, and Deli Wang, "High-detectivity vertical Si nanowire artificial photoreceptors for retinal prosthesis applications", submitted to Nano Letters, 2013.

- 3. **Yi Jing**, Siarhei Vishniakou, Chulmin Choi, Ke Sun, Huisu Jeong, Muchuan Yang, Alireza Kargar, Sungho Jin, Gun Young Jung, and Deli Wang, "Effects of doping and passivation on Si radial junction nanowire solar cells", submitted to ACS Nano, 2013.

- Alireza Kargar, Yi Jing, Sung Joo Kim, Conor T. Riley, Xiaoqing Pan, and Deli wang, "ZnO/CuO heterojunction branched nanowires for photoelectrochemical hydrogen generation", ACS Nano, 2013, Article ASAP.

- Alireza Kargar, Ke Sun, Yi Jing, Chulmin Choi, Huisu Jeong, Gun Young Jung, Sungho Jin, and Deli Wang, "3D branched nanowire photoelectrochemical electrodes for efficient solar water splitting", ACS Nano, 2013, 7, 9407.

- Namseok Park, Ke Sun, Zhelin Sun, Yi Jing, and Deli Wang, "High efficiency NiO/ZnO heterojunction UV photodiode by sol-gel processing", Journal of Materials Chemistry C, 2013, 1, 7333.

- Siarhei, Vishniakou, Brian Lewis, Xiaofan Niu, Alireza Kargar, Ke Sun, Michael Kalajian, Namseok Par, Muchuan Yang, Yi Jing, Paul Brochu, Zhelin Sun, Chun Li, Truong Nguyen, Qibing Pei, and Deli Wang, "Tactile feedback display with spatial and temporal resolutions", Scientific Reports, 2013, 3, 1.

- 8. Alireza Kargar, Ke Sun, Sung Joo Kim, Dylan Lu, **Yi Jing**, Zhaowei Liu, Xiaoqing Pan, and Deli Wang, "Three-dimensional ZnO/Si broom-like nanowire heterostructures as photoelectrochemical anodes for solar energy conversion", Phys, Status Solidi A, 2013, 1-8.

- Alireza Kargar, Ke Sun, Yi Jing, Chulmin Choi, Huisu Jeong, Yuchun Zhou, Kristian Madsen, Perry Naughton, Sungho Jin, Gun Young Jung, and Deli Wang, "Tailoring n-ZnO/p-Si Branched Nanowire Heterostructures for Selective Photoelectrochemical Water Oxidation or Reduction", Nano Letters, 2013, 13, 3017.

- 10. Ke Sun, Yi Jing, Chun Li, Xiaofeng Zhang, Ryan Aguinaldo, Alireza Kargar, Kristian Madsen, Khaleda Banu, Yuchun Zhou, Yoshio Bando, Zhaowei Liu, Deli Wang, "3D Branched Nanowire Heterojunction Photoelectrodes for High-Efficiency Solar Water Splitting and H<sub>2</sub> Generation", Nanoscale, 2012, 4, 1515.

- 11. Ke Sun, Namseok Park, Sun Young Noh, **Yi Jing**, Sungho Jin, Paul Yu, and Deli Wang, "Nickel oxide functionalized silicon for efficient photo-oxidation of water", Energy Environ. Sci., 2012,5, 7872-7877.

- Ke Sun, Wei Wei, Yong Ding, Yi Jing, Zhong Lin Wang and Deli Wang, "Crystalline ZnO thin film by hydrothermal growth", Chem. Commun., 2011, 47, 7776–7778.

- K. Sun, A. Kargar, N. Park, P. Naughton, K. Madson, T. Bright, Y. Jing, and D. Wang, "Compound Semiconductor Nanowire Solar Cells", IEEE Journal of Selected Topics in Quantum Electronics, pp. 1033-1049, 2011.

- Ke Sun, Yi Jing, Namseok Park, Deli Wang, "Solution process of large scale high sensitivity ZnO/Si hierarchical nano-heterostructure photodetectors", 2010, 132 (44), pp15465–15467.

- 15. Shadi A. Dayeh, Peng Chen, **Yi Jing**, Edward T. Yu, Deli Wang, and S. S. Lau, "Vertically integrated InAs nanowires on insulator-on-Si for electrical isolation." Appl.Phys. Lett. 93, 203109, 2008.

- Peng Chen, Yi Jing, S. S. Lau, Dapeng Xu, Luke Mawst, T. L. Alford, Charles Paulson, T. F. Kuech, "High crystalline-quality III-V layer transfer onto Si substrate", Appl.Phys. Lett. 92, 092107, 2008.

- 17. Wayne Chen, Peng Chen, Yi Jing, S.S. Lau, T. F. Kuech, Jiariu Liu, Xeimei Wang, and Wei-Kan Chu, "Double-flip transfer of indium phosphide layers via adhesive wafer bonding and ion-cutting Process", App. Phys. Lett. 90, 052114, 2007.

## **ABSTRACT OF THE DISSERTATION**

## Semiconductor Nanowires for Optoelectronic, Renewable Energy and Retina Prosthetic Applications

by

Yi Jing

Doctor of Philosophy in Electrical Engineering (Applied Physics)

University of California, San Diego, 2013

Professor Deli Wang, Chair

This dissertation presents works on two significant application areas of semiconductor nanowire. The first is nanowire photodetectors and their applications for image sensing and retinal prosthesis. The second is nanowire solar cells for renewable energy application and both Si and III-V nanowire devices are extensively discussed.

Three structures of Si nanowire photodetectors are presented, including nanowire photoconductor, axial and radial junction nanowire photodiodes. Using the design of a crossbar structure, an individually addressable vertical Si nanowire photoconductor array was presented, followed by discussion on integration to CMOS for image sensing applications. In addition, the Si axial junction nanowire photodiodes were also demonstrated, which showed excellent detectivities in visible spectrum at zero bias, with a peak value of  $2.14 \times 10^{13}$  Jones at wavelength of 636 nm. Furthermore, the radial junction nanowire photodiodes were discussed as well, which exhibited enhanced photo responsivity due to shorter carrier separation and collection paths. These nanowire photodiode arrays promises potential application for retinal prosthesis by replacing the dysfunctional photo receptors in human retina.

In addition to photodetectors, I also demonstrated Si nanowire solar cells including both planar Si solar cells with nanowire absorber and Si radial junction nanowire solar cells. A low-cost chemical etching method was introduced to fabricate large-scale Si nanowire array as light absorber to improve the light absorption of planar Si solar cells. The efficiency of this device is over one order of magnitude higher than the one without nanowires. In addition, the Si radial junction nanowire solar cells were studied. A systematic study on design parameters, including nanowire core and shell doping concentrations, band structures and surface passivation methods, were discussed to achieve optimal device performance. With optimal design, a power conversion efficiency of 8% was demonstrated.

InAs based nanowire core/multi-shell heterojunction solar cells were investigated as well. A systematic study of catalyst-free MOCVD growth of InAs

xix

nanowires on Si substrates was performed. Various growth parameters and surface treatment methods were studies to achieve optimal nanowire growth and reveal the growth mechanism. Based on the InAs nanowire growth, the III-V core/multi-shell nanowires were successfully fabricated and solar cells have been demonstrated.

## **Chapter 1: Introduction**

#### **1.1 Semiconductor Nanowires**

A nanowire is a one dimensional (1D) nanostructure, with a diameter constrained to the nanometer scale, typically around from a few nm to a few hundred nm, and an unconstrained length on the order of several µm to tens of µm. The first semiconductor nanowire, or so called whisker, was experimentally demonstrated by Wagner and Ellis in 1964.<sup>1</sup> Nowadays, study of semiconductor nanowires has been one of the most active fields of research. Owing to their unique properties resulting from one dimensionality and large surface-to-volume ratio, nanowire structures are not only utilized for exploring phenomena at the nanoscale but also expected to play a critical role for future applications in electronics,<sup>2</sup> photonics,<sup>3</sup> thermoelectrics,<sup>4, 5</sup> chemical/bio-sensing,<sup>6</sup> optoelectronics<sup>7, 8</sup> and renewable energy.<sup>9, 10</sup> From a perspective of fundamental physics, the 1D nanowire structure is an ideal platform to study the properties which may be inaccessible or difficult to achieve in conventional bulk materials. In addition, the properties of nanowire devices can be enhanced as a result of combination of shape, density and strong confinement of photon, phonon and electrons. For example, vertical nanowire arrays can exhibit absorption of light close to the Lambertian limit with properly designed geometry.<sup>11</sup> On the other hand, insignificant parameters of materials in conventional devices may greatly influence the device performance as the size enters into nanoscale. For instance, because of the high surface-to-volume ratio, trapping of carriers at the surface states drastically affects the transport and optical properties of nanowires. The presence of surface states could significantly enhance the photoconductive gain by trapping one type of photo-generated carrier while leaving behind the other unpaired carriers,<sup>8</sup> or increase surface combinations thus reduce the solar cells efficiency. Therefore, it is essential to understand the electrical and optical properties of nanowire structures in order to provide design guidance for high-performance nanoscale devices for future applications.

A large variety of preparation methods have been developed to fabricate nanowire structures and from a broad range of materials. The fabrication methods mainly can be categorized into two groups: top-down and bottom-up. Fabrication of nanowires with well controlled size, shape, position and doping has been achieved using both top-down and bottom-up approaches. Each approach has its pros and cons. The top-down approach utilized lithographic or self-assembled patterning of nanoscale mask structures on the substrate; then selectively etches the materials away from the substrate to form nanowire structures. Both planar and vertical nanowire structures have been demonstrated using top-down approach. On the contrary, bottom-up approach uses gases comprising of the constituent materials to epitaxially grow nanowires, either with the assistant of metal catalysts or catalyst-free methods. With the rapid progress of fabrication technologies, various novel nanowire structures have been demonstrated, including radial (core-shell) homo- and heterojunctions, axial structures and 3D branched nanowire configurations.<sup>10, 12-17</sup> The enriched versatile nanowire structures greatly enhance the device functionality for practical applications.

#### **1.2 Surface States and Surface Recombination**

Due to the high surface-to-volume ratio, surface states, such as dangling bonds, defects, and adsorbates, play a much more dominant role in electrical, carrier transport and photoconduction properties of nanostructures than that in thin films and bulk crystals. As a result, the performance and function of nanowire devices are expected to be strongly influenced by surfaces states. Such high surface sensitivity, although beneficial for some device applications, presents challenge to device fabrication as it leads to difficulty in the reproducibility and controllability of device performance. Thus, it raises the importance of understanding mechanism and careful engineering of the surface states so that we can fully use the benefits of surface states while keep the deleterious impacts to the minimum.

The electrical properties of nanowires, such as conductivity and doping type, strongly depend on the effects of surface states and may be surface-dominated with increasing of the surface-to-volume ratio. For example, the transport properties of Si nanowires are strongly influenced by the surrounding ambient and surface conditions.<sup>18,</sup> <sup>19</sup> In air, gas molecules (mainly water molecules) get absorbed on Si nanowires due to the large number of dangling bonds and defects present on the surfaces. The absorbed water molecules would trap electrons from Si nanowires, forming OH<sup>-</sup> ions. The negative charges on the surfaces of Si nanowires would cause surface band bending, and lead to accumulation of excess holes in the valence band. In the case of p-type Si nanowire, the excess holes contribute to the electrical transport and enhance conductance. For n-type Si nanowire, however, the excess holes from surface adsorption may fully compensate the electrons in nanowire and convert the nanowire to p-type.<sup>20</sup> This phenomenon is more pronounced for nanowires with smaller diameter, owing to the larger surface-to-volume ratio.

The effects of surface states also influence the photoconductive properties of nanowires. It has been recently observed and discussed that modification of surface states leads to high gain in photoconductive.<sup>8, 18, 19, 21-26</sup> For example, in ZnO nanowire UV photodetectors,<sup>8</sup> oxygen molecules are absorbed on the oxide surface and capture the free electrons present in the n-type semiconductor. Due to the Fermi-level pinning at the surface of nanowires, a low conductivity depletion layer is formed near the surface. Depending on the diameter and doping profile of nanowire, it is possible to obtain completely depleted nanowire or nanowire with thin conducting channels, which leads to low dark current.<sup>21</sup> When photons with energy above bandgap  $E_g$  impinge on the

nanowire surface, electron-hole pairs are generated. Holes migrate to the surface along the potential slope produced by band bending and discharge negatively charged adsorbed oxygen ions, while unpaired electrons prefer the inner part of the nanowire, increasing the conductivity and passing through the nanowire multiple times before recombination, which leads to photoconductive gain as high as  $10^{8.8}$

Besides the benefits resulting from the high surface-to-volume ratio, the nanowire device may also suffer from deleterious effects caused by large surface area if not well designed. One of the most important factor need to be considered is the surface recombination for solar cells. In the surface recombination process, an electron from the conduction band recombines with a hole in the valence band via defect level within the band gap. The increased recombination of photo-generated carriers at the dramatically increased surface area of the nanowire solar cells decreases the efficiency by reducing device short-circuit current and open-circuit voltage. For solar cells, implementation of passivation techniques is essential in order to achieve minimum surface recombination.<sup>27</sup>

From the above examples, we conclude that surface states can dominate the transport, photoconductive and recombination properties of nanowire devices. These surface-related phenomena should be generic to any nanowire systems with different materials and diverse architectures, of which surface constitutes a significant portion.

#### **1.3 Light Absorption in Nanowires**

The light absorption is one of the most important processes that determine the performance of nanowire photodetectors and solar cells. Due to the unique one-dimensionality and small size, there are many fundamental advantages of nanowire structures for light absorption, such as suppressed reflection, reduced transmission and weak angular dependence. Optimal design of nanowire structures with enhanced absorption is of great importance to achieve high performance nanowire devices. In the following, we will start our discussion with photon management of individual nanowires, which are basic building blocks of devices.

For conventional thin film or bulk devices, light absorption mainly relies on the intrinsic optical properties of the materials. However, with the emerging of nanowire devices, engineering of light absorption through control over the size, dimension and orientation of the nanowires becomes important. Cao et al proposed and demonstrated a novel method, called leak-mode resonances, for optimal design of light absorption.<sup>28</sup> When illumination wavelength matches one of its leaky-modes, strong resonances occur inside a single nanowire, resulting in trapped light in circulating orbits by multiple total internal reflections from the periphery, leading to enhanced absorption.<sup>29</sup> Owing to the coupling to different transverse electric (TE) and transverse magnetic (TM) leak-mode resonances of the nanowire, distinct peaks occur at matched wavelengths. At the resonance wavelengths, the external quantum efficiency of nanowire is substantially

larger than that of the thin film. Of particular importance is that subbanggap photoresponse can also be dramatically improved (>25-fold) using leak-mode resonance. Theoretical simulation using full-field finite difference frequency domain (FDTD) further confirms that absorption enhancement results from the leak-mode resonances. Optimal wavelength selectivity of single nanowire photodetectors can be achieved through careful design of diameters. Due to the dependence of resonances on size parameter, the absorption peaks increase monotonically with increasing nanowire diameters.<sup>30</sup>

In addition to single nanowire, vertical nanowire arrays also show enhanced light absorption.<sup>31</sup> By embedding the vertical nanowires into low refractive index materials, nanowires with diameter comparable to or smaller than the wavelength of incident light can absorb not only the portion of the wave directly on it, but also the surrounding wave. Numerical simulation shows that the coupling of light results in significantly larger percentage of photon energy within the nanowire volume than the physical fill factor, especially at larger pitch size.<sup>31</sup>

Total absorption is determined by both reflection and transmission. For many thin film devices, surface reflection is one of the main mechanisms responsible for the loss of quantum efficiency and usually an antireflection coating is required.<sup>32-34</sup> On the contrary, numerical analysis have shown that the reflectance of nanowires is significantly lower than that of the thin film in the entire spectral range due to the reduced density of the nanowire structure.<sup>35</sup> Experimental measurements on optical properties of Ge nanowires further indicate a monotonic reduction of reflectance with decreasing diameter of nanowire.<sup>36</sup> This phenomenon can be attributed to the enhanced light scattering when the diameter of nanowires becomes comparable to or smaller than the wavelength of incident light.<sup>37</sup>

Furthermore, both numerical simulations and optical measurements of Si and Ge nanowire arrays show negligible transmission at small wavelengths.<sup>35, 36, 38</sup> However, at long wavelengths, nanowire structures exhibit higher transmittance than thin film. As the nanowire diameter is reduced, a blue shift in wavelength corresponding to the onset of measurable transmittance is observed.<sup>36</sup> The higher transmittance cannot be compensated by the low reflectance, resulting in reduced absorption of long wavelength light in the nanowires. The absorption of low energy photons can be improved by careful design of physical fill factor. Although the nanowire arrays with smaller fill factor have shown better absorption of small wavelength light, calculations show that nanowires with larger physical fill factor has higher absorption in the long wavelength regime. By changing physical fill factor, the overall absorption of nanowire structure can be increased close to its thin film counterpart at long wavelengths. Further enhancement of light absorption at long wavelengths can be achieved using dual-diameter nanowire arrays.<sup>36</sup> In this design, the light reflection can be suppressed by small diameter nanowire tips; while the light transmitted to the larger diameter base can be efficiently absorbed due to larger physical fill factor.

#### **1.4 Top-down Nanofabrication of Si Nanowires**

In general, there are two approaches to fabricate Si nanowires using top-down process: ICP/RIE dry etching (a combination of inductively coupled plasma and reactive ion etching) and chemical wet etching. The dry etching of Si nanowires usually requires patterning of Si wafers to form nanoscale dots array as etch mask; then the nanowires are created by selectively etching away of Si using ICP/RIE process. On the other hand, Si nanowires can also be formed by chemical etching either using a mask or by a maskless approach. In the following sections, we will discuss the two approaches in details.

#### 1.4.1 E-beam lithography and nanoimprint lithography

For fabrication of position-controlled nanowire array, the top-down process usually starts with pattern definition of the substrate. Traditionally, the nanoscale patterns are created using E-beam lithography and more recently nanoimprint lithography was also developed to fabricate large area arrays of nanoscale pattern.

By using a beam of electrons to expose the resist, E-beam lithography can beat the diffraction limit of light and make nanoscale structures with precisely controlled position, shape and size. However, the main disadvantage of the E-beam lithography is the long processing time, which dramatically increases the manufacturing cost. Also, the long exposure time leaves the users vulnerable to beam drift or instability which may occur during the exposure. Thus, the application of this technique is limited to pattern small area structures.

On the contrary, nanoimprint lithography provides an alternative way to define nanoscale patterns with low cost and high throughput. In a nanoimprint lithography process, a thin layer of imprint resist is spin-coated onto the substrate; then a mold, which has predefined patterns, is brought into contact with the sample and they are pressed together under certain pressure. The resist is then either thermally or UV cured and becomes solid. After mold separation, the pattern is transferred from mold to the resist. A similar pattern transfer process can be used to further transfer the pattern from the resist to the underneath substrate using dry etch.<sup>39</sup> Due to the quick processing and high throughput, nanoimprint lithography technology has been used to fabricate devices in electrical, optical, photonic and biological applications.<sup>40-44</sup>

#### 1.4.2 Dry Etching of Si Nanowires

Reactive ion etcher (RIE) has been widely used in industry for fabrication of integrated circuits and microeletromechanical (MEMS) systems. It uses chemically reactive ions to remove materials deposited on wafers. By independently controlling the ion density and the momentum imparted to the ions, various highly fined Si structures can be achieved, such as high aspect ratio Si nanowires.

Generally speaking, there are two types of configurations of RIE systems: the parallel plate RIE system and inductively coupled plasma (ICP) RIE system. A typical parallel plate system consists of a cylindrical vacuum chamber with two parallel plates (which form a capacitor) sitting at the top and bottom of the chamber respectively, and a wafer platter situated in the bottom portion of the chamber. The wafer platter is electrically isolated with the rest of chamber. Gases enter through the small inlets in the top portion of the chamber and exit to the vacuum system through the bottom. When a radio frequency (RF) voltage, typically set at a frequency of 13.56 megahertz, is applied to the plates, plasma is generated in the chamber owing to the strong RF electric field. In each cycle of the field, electrons are accelerated up and down in the chamber. However, the much more massive ions cannot track the rapidly oscillating electric field changes and moves relatively little in response to the RF electric field. Accumulation of negative charges on the platter builds up a negative voltage, which forms electric field between the parallel plates. The resulting electric filed caused by this voltage drives the negative ions in plasma towards the wafer platter, where they collide with the sample to be etched.

In an ICP process, the excitation of plasma is similar to the parallel plate system, except that instead of RF electric field, the plasma is generated by an RF magnetic field, which is delivered inductively, via a coil wrapped around RIE plasma discharge region. The changing magnetic field induces an electric field that tends to circulate the plasma in the plane parallel to the plates. With ICP process, very high plasma densities can be achieved, although the etch profile tends to be more isotropic.

Usually, the ICP/RIE process, which combines the parallel plate and ICP RIE, is employed to etch Si. In this process, the ICP is utilized as a high density source of ions which increases the etch rate, whereas a separate RF bias is applied to the Si substrate to create directional electric fields near the substrate to achieve more anisotropic etch profiles. In other words, the ICP controls the number of ions reaching the substrate to chemically etch while the parallel plate RIE controls the momentum of the ions reaching the substrate to mechanically etch.

In this work, the ICP/RIE process (gases:  $CF_4$  and  $SF_6$ ) is employed to etch Si nanowires using Oxford Plasmalab 100 system. The Si etching mainly relies on  $SF_6$  gas. When Si is etched by  $SF_6$  gas, the following two spontaneous etching reactions may occur:<sup>45</sup>

It can be seen that the all byproducts are volatile. The silicon-containing product is  $SiF_4$  gas while the sulfur-containing product depends on temperature. The equilibrium product is either  $SF_4$  gas for temperatures above  $100^{\circ}C$ , or  $Si_2F_2$  for temperatures below  $-30^{\circ}C$ . Both products can exist when temperature is between  $-30^{\circ}C$  to  $100^{\circ}C$ .

To achieve high aspect ratio Si structures, passivating the sidewalls by

dissociating gas reactants in a plasma environment is a common strategy. The passivation layer protects sidewall from lateral etching and improves anisotropy. There are several gases can function as passivating agents, such as  $O_2$  and  $C_4F_8$ .  $C_4F_8$  is the most common one and used in this work. During sidewall passivation,  $C_4F_8$  breaks down in the plasma to produce  $CF_2$  and longer chain radicals. Then  $CF_2$  is adsorbed to from a teflon-like polymer, i.e. the passivation layer, on the sidewall and base surfaces.<sup>46</sup>

In summary, with a combination of  $SF_6$  and  $C_4F_8$  gases, the etch gas  $SF_6$  is injected and ionized in the chamber to provide fluorine ions and radicals to etch Si, while simultaneously passivation gas  $C_4F_8$  is injected and ionized to create a passivation layer to protects sidewall and base surfaces of Si from chemical etching. However, the passivation layer on the base surface is etched away faster by the milling of fluorine ions than re-deposition. Thus, sidewall of Si is protected by the passivation layer while base surface is free to etch, leading to formation of high aspect ratio Si nanowires.

#### 1.4.3 Metal Assisted Wet Chemical Etching of Si Nanowires

Metal assisted wet chemical etching is a rapid and low-cost technique to fabricate large-scale Si nanowire arrays.<sup>47-51</sup> This simple technique involves only wet chemical processing under the near ambient conditions and is easy to scale up to wafer size, leading to a low-cost operation. The etching of Si is usually catalyzed by metal

particles formed on Si surface via either electroless deposition or physical vapor deposition, such as sputtering. The Si surface that comes in contact with the metal is selectively etched in hydrofluoric acid (HF) based aqueous solution, leaving behind arrays of Si nanowires.<sup>48</sup> For instance, by immersing the Si wafers in HF aqueous solution containing silver nitrate (AgNO<sub>3</sub>), the Si etching and silver deposition start to occur simultaneously at the surface. The deposited silver nanoclusters act as local cathodes while the surrounding areas serve as anodes. Thus the Si underneath the silver nanocluster is oxidized into SiO<sub>2</sub>. Subsequently, SiO<sub>2</sub> is dissolved by HF, leaving a pit underneath the Ag nanocluster. As a result, successive deposition of silver produces a dendrite layer covering Si substrate and vertically aligned Si nanowires are created.<sup>47</sup>

#### **1.5 Bottom-up growth of nanowires**

The bottom-up growth has been widely used to synthesis various semiconductor nanowires, including Si,<sup>1</sup> Ge,<sup>52</sup> III-V compounds<sup>53-55</sup> and so on. The mostly used method for nanowire growth is the vapor-liquid-solid (VLS) process, which was firstly proposed by Wagner and Ellis to grow Si nanowires in 1964.<sup>1</sup> By introducing a catalytic metal nanoparticle, which can absorb reactants in vapor phase to form supersaturated liquid alloy inside the nanoparticle, the single crystal nanowires can grow from the nucleated seeds at the liquid-solid interface.<sup>53</sup> Through control of

the growth conditions, one could control the length, location, morphology and doping of the nanowires. Au is the most commonly used catalyst for single crystalline nanowire growth. However, it forms unwanted deep level traps in semiconductor nanowires during growth, which is notoriously deleterious to the performance of nanowire devices.<sup>56-58</sup> To circumvent this issue, research efforts have been devoted to develop growth method without assist of Au particles, such as self-catalyzed growth<sup>59-65</sup> and catalyst-free growth. The self-catalyzed growth is also categorized as VLS growth since one or more nanowire elements, usually In<sup>61</sup> or Ga<sup>62</sup> droplets, are used as the seed nanoparticles. On the other hand, no catalyst is used during the nucleation and growth for the catalyst-free method. For example, selective-area growth uses partially masked substrate, usually by an oxide or nitride layer, with lithographically defined opening pattern. Subsequently, semiconductor materials nucleate and initiate nanowire growth in the openings after increasing the temperature and introducing the reactant gases.

#### **1.6 Scope of This Dissertation**

The scope of this dissertation is as follows:

Chapter 2 presents Si nanowire photodetectors and their applications for image sensing and retinal prosthesis. We discuss three structures of nanowire photodetectors: nanowire photoconductor, nanowire axial junction photodiode and nanowire radial junction photodiode. Firstly, fabrication and understanding of a single Si nanowire photoconductor is provided. Using the design of a crossbar structure, an individually addressable vertical Si nanowire photoconductor array is presented, followed by discussion on integration to CMOS for image sensing applications. Secondly, Si nanowire axial and radial junction photodiodes are discussed. Both photodiodes exhibit good photo responsivity at zero bias. These nanowire photodiode arrays could be used to replace dysfunctional photo receptors in human retina, promising potential application for retinal prosthesis.

Chapter 3 discusses the Si nanowire based photovoltaic devices, including planar Si solar cells with nanowire absorber and Si nanowire radial junction solar cells. First a planar Si solar cell with nanowire absorber is introduced. A low-cost chemical etching method is used to fabricate large-scale vertically aligned Si nanowire array. The Si nanowire array is utilized as light absorber to improve the light absorption of the planar solar cell. Then Si nanowire radial junction solar cells are presented. The fabrication process and key factors that contribute to achieving optimal device performance are discussed.

In chapter 4, we discuss III-V nanowire core/multi-shell heterostructure based photovoltaic devices. First a simple catalyst-free MOCVD method is studied to growth vertical InAs nanowires on low-cost Si substrates. Several aspects of the growth method are investigated to achieve optimal nanowire growth and elucidate the growth mechanism. Then this method is extended to growth InAs based nanowire core/multi-shell heterostructures. The morphology and structure properties of nanowire heterostructures are characterized by scanning electron microscope (SEM) and transmission electron microscopy (TEM). Photovoltaic devices are fabricated and characterized, demonstrating a III-V nanowire tandem cell on low-cost Si substrate.

In chapter 5, a summary of the dissertation and possible areas for future work are discussed.

# **Chapter 2: Si Nanowire Photodetector Arrays for Image**

# **Sensing and Retinal Prosthesis Applications**

# 2.1 Introduction—Nanowire Photodetectors

Semiconductor nanowires have been extensively investigated as building blocks for nanoscale electronics<sup>2</sup> and optoelectronics<sup>7, 66-68</sup> due to their unique properties. In particular, nanowire photodetectors have attracted significant interest because of promising applications for single photon detection, image sensing, medical imaging and diagnosis. Due to the unique one-dimensionality and large surface-to-volume ratio, semiconductor nanowires exhibit high internal gain and high sensitivity.<sup>8, 31</sup> With rapid progress of the fabrication technology, numerous nanowire structures have been realized without constraint of lattice mismatch using either top-down or bottom-up processes with precisely controlled doping, size, shape and position, including structures which are traditionally inaccessible. The enriched versatile nanowire structures further enhance nanowire photodetection applications. Therefore, a deep understanding of the physical mechanism and versatile design of the nanowire structures is crucial to obtain optimized nanowire photodetectors and consequently achieve higher performance devices for practical applications.

Photodetectors are semiconductor devices that convert incident light to

electrical signal. There are different types of photodetectors, such as photoconductors and photodiodes, but the general physical mechanism of photodetectors is the same. Basically, the performance of a photodetector depends on three processes: (1) carrier generation by incident light; (2) carrier transport; and (3) extraction of carriers as terminal current to provide the output signal.<sup>69</sup>

Photoconductors conduct a single carrier type, whereas photodiodes extract carriers of each type.<sup>69</sup> In a photoconductor, one type of carrier is trapped while the other circulates under the influence of an electric field. The ratio of  $\tau_n/\tau_t$  (here  $\tau_n$  is the carrier lifetime;  $\tau_t$  is the transit time) gives the photoconductive gain, which is determined by how fast the electrons transit across the electrodes and contribute to the photocurrent in the circuit before they recombine with holes. Photoconductors are capable of high gain because of traps, which delay band-to-band recombination and impede the extraction of trapped carriers. In nanowire structures, the effect of traps is much more influential on the performance of photodetectors.

Photodiodes consist of two materials, with at least one being a semiconductor, where a large difference in the materials' work functions produces a built-in potential. An internal electrical field in the semiconductor depletion region near the junction propels electrons and holes in opposite directions. Response times of photodiodes are typically microseconds or less for direct-gap semiconductors, and can be shorter than electron-hole recombination times. Nanowires offer a variety of opportunities to design photodiode architectures, including homo- or hetero-junction devices formed either axially along the nanowire<sup>70</sup> or radially by core-shell junctions.<sup>15, 71</sup>

# **2.2 Single Nanowire Photoconductors**

In this section, we present fabrication of a vertical Si nanowire photoconductor array with individual addressability using E-beam lithography and an ICP/RIE process. The electrical properties of devices are determined by I-V measurements. Using a design of crossbar structure, the photoconductor array can be individually addressed and function as an image sensor. This reliable and repeatable fabrication process results in high yield (100%) functional devices in the array. The uniformity of the device performance was also discussed. A preliminary result of the small pixel image sensor array was demonstrated under uniform white light illumination, leading to the potential application of fabricating miniaturized high-detectivity image sensors.

#### 2.2.1 Fabrication of Individual Addressable Si Nanowire Photodetector Array

The fabrication started from a p-type (100) silicon-on-insulator (SOI) wafer with a device layer thickness of 5  $\mu$ m and a doping concentration of ~10<sup>15</sup> cm<sup>-3</sup>. Firstly, E-beam lithography was used to pattern stripes and connecting electrodes onto poly(methyl methacrylate) (PMMA) resist. Then Ni was deposited using E-beam evaporation and lift-off. The ICP/RIE process (Gases: C4F8 and SF6) was carried out to anisotropically etch Si, resulting a pattern of Si stripes in the central region and Si

**Figure 2.1:** Process flow for fabrication of individually addressable vertical Si nanowire photoconductor array.

lines connecting to electrode pads in the outer region (Figure 2.1 (a)). After etching off Ni mask by Ni etchant, another E-beam lithography process with alignment was used to pattern nanoscale Ni disks onto the Si stripes (Figure 2.1 (b)). Similar to the first etching, Si was dry etched down the SiO<sub>2</sub> layer to create a Si nanowire array sitting on the stripes. Then the SOI substrate with Si nanowires was annealed at 650  $\mathbb{C}$  for 60 s in forming gas (5% H<sub>2</sub>, 95% N<sub>2</sub>) to form nickel monosilicide (NiSi) between the Ni disks and nanowire tips to ensure an ohmic top contact. Al was patterned and evaporated onto the Si stripes and contact pads by E-beam lithography, and annealed at 400  $\mathbb{C}$  for 60 s in N<sub>2</sub> to form an ohmic bottom contact. Transparent spin-on glass (SOG, Futurrex, Inc) was spin-coated to fill the spacing between nanowires as an insulating layer (Figure 2.1 (d)). Excess spin-on glass was removed using O<sub>2</sub> RIE etching to expose the nanowire tips (Figure 2.1(e)). A patterned layer of transparent indium tin oxide (ITO) was sputtered and lift-off to form top contact.

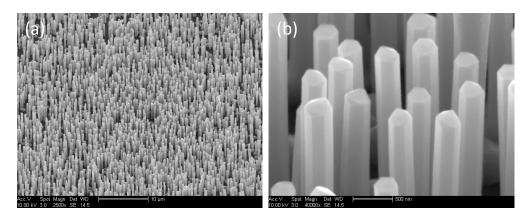

**Figure 2.2:** (a) A SEM image  $(75^{\circ} \text{ tilted view})$  of Si nanowires array. (b) A magnification of SEM image (45° tilted view) of Si nanowires. (c) A SEM image of Si nanowire photoconductor array. (d) Optical microscope image (top view) of Si nanowire photoconductor array.

The morphology of Si nanowire array was characterized by SEM and optical microscope. Figure 2.2 (a) shows a SEM image of fabricated  $8 \times 8$  Si nanowire array. The diameters, length and pitch size of nanowire array are ~~200-240 nm, 3.7 µm and 4 µm, respectively. The Si nanowires sit on 1.5 µm wide and 1.3 µm thick electrically insulating Si stripes. Figure 2.2 (c) illustrates the patterned ITO electrodes on top of the Si nanowires embedded in SOG. The crossbar contact structure enables the individual addressability of Si nanowire photodetector array, as shown in Figure 2.2 (d).

#### 2.2.2 Single Si Nanowire Photodetector Characterization

**Figure 2.3:** (a) Schematics of a single Si nanowire photodetector. (b) I-V curves of a representative Si nanowire device under dark and illumination with varying light intensities. (c) Curves of photocurrent as a function of incident light intensity at different applied biases.

The electrical properties of a single Si nanowire photodetector were characterized by current-voltage (I-V) measurements using a semiconductor parameter analyzer (Agilent B1500). The light source used in this experiment was a while light lamp. Figure 2.3 (a) shows typical I-V curves of a single Si nanowire device from the array under dark and varying light illumination levels at room temperature. Under dark, rectifying I-V curve was observed owing to the Schottky contact between Si and nickel silicide. Upon illuminated, the device shows very small photo response under reverse bias. When the device is forward biased, the measured current increases significantly. It shows that the current is increased by 2 orders of magnitude with a light intensity of 43 mW/cm<sup>2</sup> at 10 V bias. With increasing illumination light intensity, the photocurrent increases proximately linearly (Figure 2.3 (b)). The photoconduction of the Si nanowire devices mainly arise from two factors: (1) the enhancement of the

carrier lifetime caused by the trapping of carriers in the surface states; (2) decrease of the carrier transit time due to small dimension of nanowire devices.<sup>8</sup> Because of the high surface-to-volume ratio, surface states have been reported to play an important role in photoconductive and carrier transport behaviors for various nanostructures, such as ZnO nanowires, boron nanobelts,<sup>72</sup> Ge nanowires,<sup>73</sup> CdS nanoribbons.<sup>22</sup> In the case of p type Si nanowires, due to the presence of large number of dangling bonds and defects, water molecules adsorb on the nanowire surface when exposed to humid ambient.<sup>20</sup> The adsorption effect is especially important in etched nanowires due to the rough surface. The adsorbed molecules can trap electrons to form OH<sup>-</sup> ions. The existence of the negative charges on the surface causes band bending. Upon illumination with photon energy higher than the band gap, electron-hole pairs are generated. The photo-generated electrons migrate to the surface and are captured by the surface traps, resulting in accumulation of excess holes in valence band inside the nanowire. The excess holes contribute to the electrical transport and induce photoconduction.

#### 2.2.3 Integration to CMOS for Image Sensor Applications

An image sensor is a device that converts an optical image to an electrical signal. Image sensors have been widely used in cameras, camcorders, scanners, fax machine, and other camera modules. The two main Si based image sensor technologies are charge-coupled devices (CCDs) and CMOS image sensors. A CCD

image sensor is an analog device, which converts the incident light into small electrical charge in each photo sensor. The charges are subsequently converted to voltage one pixel at a time as they are read from the chip. CCD is a more mature technology. Ever since it was first reported by Bell lab in 1970, significant research advances have been achieved on CCD image sensors, leading to a very high level of performance with low readout noise, high dynamic range and excellent responsivity. However, CCD based camera system requires not only one image sensor chip but also a set of ancillary chips, such as signal processors and analog-to-digital converters, which greatly increases the fabrication cost, power consumption and hampers miniaturization of cameras. On the other hand, the CMOS imaging chip is a type of active pixel sensor made using the CMOS semiconductor process, which offers lower fabrication cost, lower power consumption, high miniaturization and increased functionality.

However, miniaturization of CMOS technology does not always lead to enhanced image sensor performance. The main obstacles of the conventional CMOS image sensor systems are the poor scalability and low responsivity of the photodetector.<sup>74</sup> To overcome the limitations of conventional devices and meet the need for scaling down, high-sensitive nanoscale photodetectors are highly desirable. Semiconductor nanowire photodetector, which promises high responsivity and small size, is an attractive candidate for applications in integration with CMOS image sensors. Recently, extensive research efforts have been devoted to develop large-area nanowire based image sensing devices.<sup>75-77</sup>

**Figure 2.4:** (a) Measured photocurrents of each Si nanowire photodetector in the array. The SEM image is a top view of Si stripes with Ni dots on top. The array is illuminated by a uniform white light lamp  $(3.5 \text{mW/cm}^2)$ . (b) A simple demonstration of the response of the photodetector array as an image sensor to uniform white light illumination with each device representing one pixel. The contrast map corresponds to the photocurrent map.

To demonstrate the concept that the vertical Si nanowire photodetector array can function as an image sensor, the photocurrent (the current with illumination subtracts dark current) of the individual nanowire photodetector in the 8×8 Si nanowire array was measured under uniform white light illumination with a power density of  $3.5 \text{ mW/cm}^2$ . Figure 2.4 (a) shows the mapping of measured photocurrents. The results show 100% yield functional nanowire devices and a nonuniform distribution of photocurrents (I<sub>ph0</sub>), ranging from 0.53 nA to 2.73 nA (see Figure 2.4 (a)). A 2D contrast map of the photocurrent was plotted considering each nanowire device as a pixel (see Figure 2.4 (b)). The map shows relative small spatial variation of the light intensity, which is consistent with the uniform illumination. To further enhance the device uniformity, the relative intensity, which is defined as measured current of imaging an object divided by photocurrent with uniform illumination, can be used to plot contrast map. Thus, potential application as functional, small pixel and high resolution image sensor of the Si nanowire photodetector array has been demonstrated.

# 2.3 Axial P-N Junction Si Nanowire Photodetectors

#### **2.3.1 Device Fabrication**

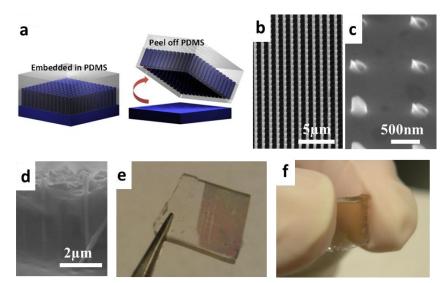

The fabrication process of Si axial p-n junction nanowire photodiode array is illustrated in Figure 2.5. The substrates used in this study were p-type Si (100) wafers with a boron doping concentration of  $1 \times 15$  cm<sup>-3</sup>. Firstly, the Si surface was inverted to form an n-type top layer via phosphorus diffusion using spin-on-dopant (SOD) (Figure

2.5 (a)). The junction depth was found to be ~1.6  $\mu$ m using ICP/RIE etch and four point probe method. Secondly, nanoimprint lithography and ICP/RIE etching were used to pattern the Si substrates and fabricate large-area Si nanowire arrays. Ni dots array with an area of 2×2 cm<sup>2</sup> was patterned on Si wafers as the etch mask by nanoimprint lithography (Figure 2.5 (b)), followed by evaporation of 40 nm thick Ni and lift-off processes. Thirdly, the vertically aligned Si nanowires with an axial p-n

**Figure 2.5**: Schematics of fabrication process of Si axial p-n junction photodetectors. (a) Phosphorus diffusion of Si wafers using spin-on dopant to form a planar p-n junction. (b) Nanoimprint lithography and E-beam evaporation to pattern Ni dots array on Si wafers. (c) ICP/RIE dry etch of Si nanowire array. (d) Spin-coating of PMGI polymer as an insulating filling material. (e) Removal of excess PGMI by O<sub>2</sub> RIE to expose nanowire tips. (f) Sputtering of ITO as transparent top contact.

junction were created by ICP/RIE process with  $C_4F_8$  and  $SF_6$  gases (Figure 2.5 (c)). Upon a rapid thermal annealing process at 650 °C for 60 s in N<sub>2</sub>, a NiSi layer was formed on top of Si nanowires to ensure a good electrical contact. Subsequently, the Si nanowire array was embedded in a poly(methylglutarimide) (PMGI, Microchem) insulating layer by spin-coating (Figure 2.5 (d)). The tips of Si nanowires were then exposed by removing excess PMGI with O<sub>2</sub> RIE etching. Finally, 300 nm transparent indium tin oxide (ITO) was sputtered as a top electrode to the nanowires (Figure 2.5 (f)); and a layer of indium was formed on the backside of the substrates as back electrode using soldering iron.

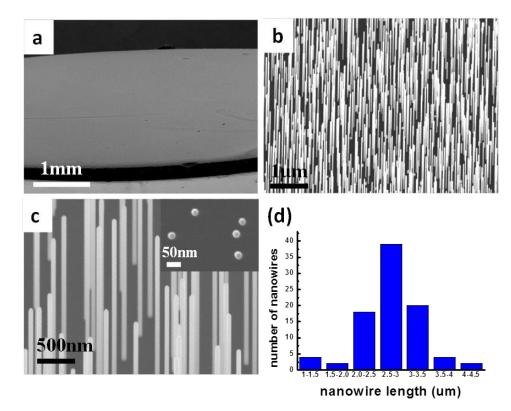

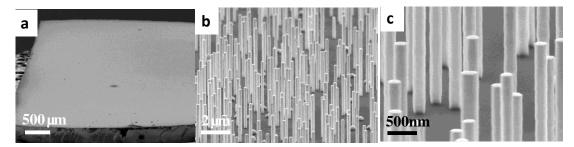

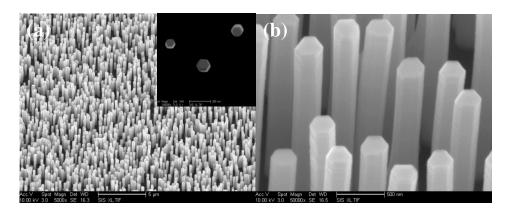

**Figure 2.6:** (a) SEM images of Ni dot array patterned by nanoimprint lithography. Inset shows magnified image of a Ni dot. Scale bar is 200 nm in the inset. (b) SEM images of vertical Si nanowire array at  $45^{\circ}$  tilted view. Nanowire length ~ 4 µm and scale bar in the inset is 200 nm. (c) A SEM image of Si nanowires embedded in PMGI with expose nanowire tips at  $45^{\circ}$  tilted view. (d) A SEM image of Si nanowire device with sputtered ITO top contact at  $45^{\circ}$  tilted view.