### UNIVERSITY OF CALIFORNIA Santa Barbara

### Sigma Delta Stream Computation: A New Paradigm for Low Power and High Resolution Feedback Control

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

by

Joseph Sam Poverelli

Committee in Charge:

Professor Forrest Brewer, Chair Professor Joao Hespanha Professor Katie Byl Professor Li-C. Wang

March 2020

The Dissertation of Joseph Sam Poverelli is approved.

Professor Joao Hespanha

Professor Katie Byl

Professor Li-C. Wang

Professor Forrest Brewer, Committee Chairperson

December 2019

Sigma Delta Stream Computation: A New Paradigm for Low Power and High Resolution Feedback Control

> Copyright © 2020 by Joseph Sam Poverelli

This dissertation is dedicated to my children. May they surpass me in all ways.

### Acknowledgments

Without the help of many people, this work would never have been completed. I first would like to express my deepest gratitude to my adviser and mentor Forrest Brewer. Forrest always believed in me even when I doubted myself and I will always have great respect for him. I would like to thank Li-C Wang, Katie Byl, and Joao Hespanha for serving on my committee, imparting knowledge, and having patience with me. To my wife Stephanie for taking good care of our children and offering constant encouragement. To my father and late mother who always have been supportive in everything I do. I would also like to thank my fellow lab mates Merritt, Kunal, Carrie, Prashansa, David, and Aditya for all of their help, encouragement, and banter. I also have many thanks to give to Val de Veyra for all her help on the administrative side of things. My friends Kyle, Wade, Ben, and others are also of special note as they provided me with comradery and emotional support. Finally, I owe thanks to Fifth Gait Technologies and Wyatt Technologies for keeping me employed and fed during this time. Thank you all so much.

### Curriculum Vitæ

### Joseph Sam Poverelli

#### Education

| 2019 | Ph.D. in Electrical and Computer Engineering (Expected), University      |

|------|--------------------------------------------------------------------------|

|      | of California, Santa Barbara.                                            |

| 2012 | M.S. in Electrical and Computer Engineering, University of California,   |

|      | Santa Barbara.                                                           |

| 2009 | B.S. in Electrical Engineering, University of California, Santa Barbara. |

### Publications

- Arya, K.; Poverelli, J.; Brewer, F., "Ongoing challenges in automated cyberphysical crossdomain design," International Conference on Computing, Networking and Communications (ICNC), 2013., pp. 341-347, Jan 2013 doi: 10.1109/ICCNC.2013.6504106

- Poverelli, J.; Brewer, F., "Direct ΣΔ Bitstream Processing for High Performance Feedback Control," *IEEE Conference on Control Technology and Applications (CCTA), 2019.*, pp. 444-449, Aug 2019 doi: 10.1109/CCTA.2019.8920720

### Abstract

### Sigma Delta Stream Computation: A New Paradigm for Low Power and High Resolution Feedback Control

by

Joseph Sam Poverelli

This dissertation describes a design and analysis methodology for  $\Sigma\Delta$  bitstream filters and controllers in digital hardware. These circuits emulate continuous linear time invariant (LTI) models and directly process  $\Sigma\Delta$  encoded bitstreams produced by  $\Sigma\Delta$ -based data converters. Since these converters are oversampled, there is a natural opportunity for clocking at the oversampling rate allowing for multiplierless, low latency designs. Direct processing of bitstreams also eliminates lowpass filtering and decimation necessary for conventional bit-parallel DSP. Combined, these changes reduce the hardware resources by more than an order of magnitude in FPGA implementations, with similar improvements in power overhead. MASH techniques (used extensively in data converters) are developed to allow for substantive improvement in resolution or reduction of the oversampling rate. These results have very substantive implications in the design of low-complexity, high performance controllers. In particular, these techniques can obviate conventional DSP augmented designs allowing for robust control in applications unreachable with current technology.

# Contents

| Ackı            | nowledgments                                                                                                                                                                                                                                                                                  | $\mathbf{v}$                                                                                                           |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Curi            | riculum Vitae                                                                                                                                                                                                                                                                                 | vi                                                                                                                     |

| $\mathbf{List}$ | of Figures                                                                                                                                                                                                                                                                                    | xi                                                                                                                     |

| $\mathbf{List}$ | of Tables                                                                                                                                                                                                                                                                                     | xiii                                                                                                                   |

| 1.<br>1.        | ntroduction         .1       Motivations         .1.1.1       Limitations in Conventional Discrete Control Algorithms         .1.2       High Resolution Data Conversion         .2       Direct ΣΔ Processing for High Performance Control         .3       Contributions and Thesis Outline | <b>1</b><br>5<br>7<br>9<br>11                                                                                          |

| Bibl            | iography                                                                                                                                                                                                                                                                                      | 12                                                                                                                     |

| 2.<br>2.<br>2.  | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                          | <ol> <li>14</li> <li>14</li> <li>19</li> <li>21</li> <li>26</li> <li>28</li> <li>28</li> <li>32</li> <li>33</li> </ol> |

| Bibl            | iography                                                                                                                                                                                                                                                                                      | 33                                                                                                                     |

| 3 P<br>3.       | 3.1.1       Shift-based Bitstream Design         3.1.2       Direct State-Space Filter         3.1.3       Assumptions on Filter/Controller Architecture                                                                                                                                      | <b>35</b><br>36<br>41<br>42<br>43<br>44                                                                                |

|          | 5.3<br>5.4 | $ \begin{array}{l} \text{MASH } \Sigma\Delta \text{ Filter Implementation } $                                                                               | 97<br>97<br>02<br>05<br>10              |

|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|          | 5.3        | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                        | 97<br>97<br>02<br>.05                   |

|          |            | 5.2.1.1 Lowpass Filter Designs                                                                                                                              | 97<br>97                                |

|          |            |                                                                                                                                                             | 97                                      |

|          |            | 5.2.1 Single Stage Designs                                                                                                                                  |                                         |

|          | <u> </u>   |                                                                                                                                                             |                                         |

|          | 5.2        |                                                                                                                                                             | 97                                      |

|          |            | 5.1.5 Design of Conventional Comparison Filter                                                                                                              | 96                                      |

|          |            | 5.1.4 Matlab/Simulink, Xilinx System Generator, and Vivado                                                                                                  | 94<br>95                                |

|          |            | 5.1.2Calculating SNR                                                                                                                                        | 93<br>94                                |

|          |            |                                                                                                                                                             | 92<br>93                                |

|          | 5.1        |                                                                                                                                                             | 92<br>02                                |

| <b>5</b> | -          |                                                                                                                                                             | <b>91</b>                               |

| Bi       | ibliog     | raphy                                                                                                                                                       | 89                                      |

|          | 4.5        | Conclusion                                                                                                                                                  | 89                                      |

|          | 4.4        | Design Example                                                                                                                                              | 87                                      |

|          |            | 4.3.1 Choosing Filter Bitwidths                                                                                                                             | 86                                      |

|          | 4.2        | MASH $\Sigma\Delta$ Controller Design and Performance Metrics                                                                                               | 85                                      |

|          | 4.2        | 4.1.1 MASH $\Sigma\Delta$ for Direct Signal Processing                                                                                                      | 79<br>81                                |

| -1       | 4.1        | Multistage Noise Shaping (MASH) $\Sigma\Delta$ Modulation                                                                                                   | 74<br>79                                |

| 4        |            |                                                                                                                                                             | 73                                      |

| B        | hlior      | raphy                                                                                                                                                       | 70                                      |

|          | 3.7        | Conclusions                                                                                                                                                 | 69                                      |

|          | 3.6        | Previous Work                                                                                                                                               | 69                                      |

|          | 3.5        | Design Example                                                                                                                                              | 60<br>67                                |

|          | 3.4        | Filter Bitwidth Optimization                                                                                                                                | $\begin{array}{c} 63 \\ 65 \end{array}$ |

|          | o (        | 0 1                                                                                                                                                         | 60                                      |

|          |            | 3.3.4.3 Output Noise Propagation due to Scaling Coefficient Rounding .                                                                                      | 57                                      |

|          |            | 3.3.4.2 Output $\Sigma\Delta$ Representation Noise Propagation                                                                                              | 55                                      |

|          |            | 3.3.4 Noise Analysis $\ldots \ldots \ldots$ | $54 \\ 54$                              |

|          |            | 3.3.3 Coefficient Sensitivity                                                                                                                               | 51                                      |

|          |            | 3.3.2 Dynamic Range Scaling of State Variable Integrators                                                                                                   | 48                                      |

|          |            | 3.3.1 Design by Emulation                                                                                                                                   | 46                                      |

|          | 3.3        | $\Sigma\Delta$ Filter Design and Performance Metrics                                                                                                        | 46                                      |

| 6               | $\Sigma\Delta$                                            | Based    | Digital Control                                                             | 113 |

|-----------------|-----------------------------------------------------------|----------|-----------------------------------------------------------------------------|-----|

|                 | 6.1 Control Specific Advantages of $\Sigma\Delta$ Filters |          |                                                                             |     |

|                 |                                                           | 6.1.1    | Controller Latency                                                          | 114 |

|                 | 6.2                                                       |          | ng Output Feedback Control Designs for $\Sigma\Delta$ Based Implementations |     |

|                 |                                                           | -        | Scaling of Controllers                                                      |     |

|                 |                                                           |          | Set-point Tracking                                                          |     |

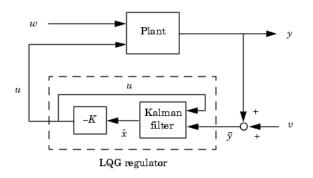

|                 |                                                           |          | LQG Regulation                                                              |     |

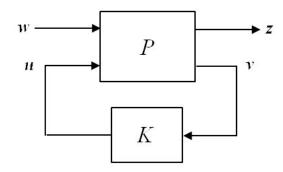

|                 |                                                           |          | $H_{\infty}$ Control Design                                                 |     |

|                 | 6.3                                                       |          | Configurations                                                              |     |

|                 | 6.4                                                       |          | tion Examples                                                               |     |

|                 |                                                           |          | Inverted Pendulum                                                           |     |

|                 |                                                           |          | AFM Cantilever Q-Control                                                    |     |

|                 | 6.5                                                       |          | sions                                                                       |     |

| Bibliography 13 |                                                           |          | 133                                                                         |     |

| 7               | Cor                                                       | nclusion | IS                                                                          | 136 |

|                 | 7.1                                                       | Future   | Work                                                                        | 137 |

|                 |                                                           | 7.1.1    | Design Partition and Cascade Realizations                                   | 137 |

|                 |                                                           | 7.1.2    | Modulated (non-baseband) Controllers and Filters                            | 138 |

|                 |                                                           |          | Nonlinear Control                                                           |     |

| Bi              | Bibliography 141                                          |          |                                                                             |     |

# List of Figures

| $1.1 \\ 1.2$      | Conventional Embedded $\Sigma\Delta$ Control Loop                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2<br>1.3        | Typical $\Sigma\Delta$ ADC Architecture                                                                                                                       |

| $1.5 \\ 1.4$      | Embedded $\Sigma\Delta$ Control Loop                                                                                                                          |

| 2.1               | Pusle Density Modulated Sinusoid Signal                                                                                                                       |

| 2.1<br>2.2        | Anatomy of PDM Signal PSD                                                                                                                                     |

| 2.2<br>2.3        | a) Continuous Time and b) Discrete Time $\Sigma\Delta$ Modulators                                                                                             |

| $\frac{2.5}{2.4}$ | $\Sigma\Delta$ Quantizer Linearization                                                                                                                        |

| $2.4 \\ 2.5$      | Linearization of 2nd Order $\Sigma\Delta$                                                                                                                     |

| $\frac{2.5}{2.6}$ | 1st and 2nd Order Discrete $\Sigma\Delta$ Modulators                                                                                                          |

| 2.0<br>2.7        | 1st and 2nd Order $\Sigma\Delta$ STF and NTF Bode Plot                                                                                                        |

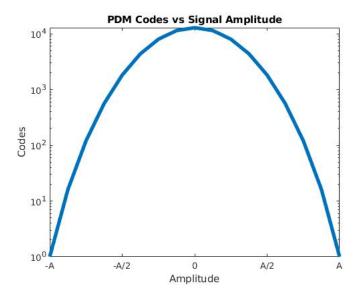

| 2.1<br>2.8        | PDM Codes vs Signal Amplitude for $OSR = 16$                                                                                                                  |

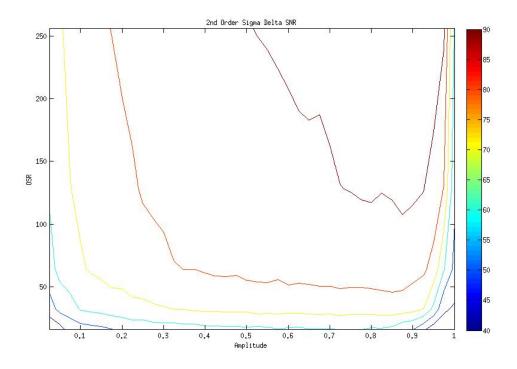

| 2.0<br>2.9        | SNR vs OSR and Amplitude                                                                                                                                      |

| 2.3               |                                                                                                                                                               |

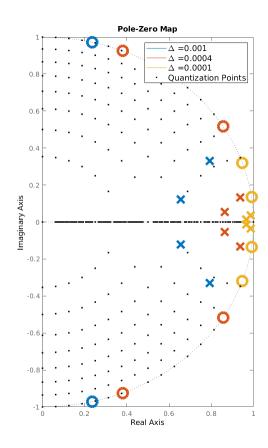

| 3.1               | 5-bit Fixed Point Pole Locations for Direct Form IIR Filter                                                                                                   |

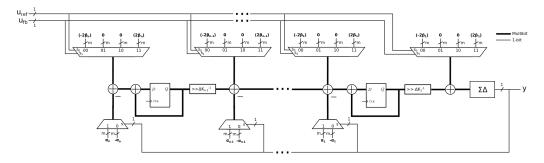

| 3.2               | Shift Based $\Sigma\Delta$ Filter Architecture                                                                                                                |

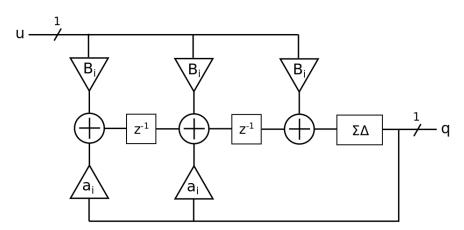

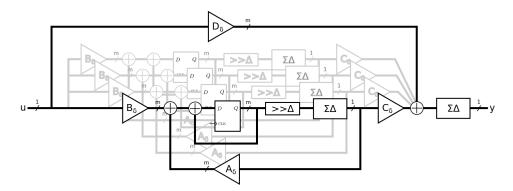

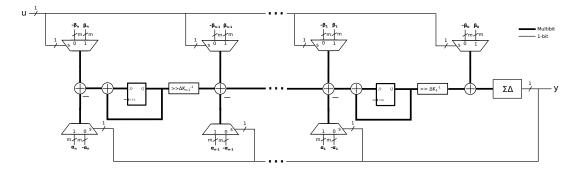

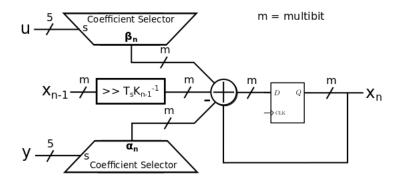

| 3.3               | $\Sigma\Delta$ State Space Filter Architecture                                                                                                                |

| 3.4               | Sigma Delta IIR Filter                                                                                                                                        |

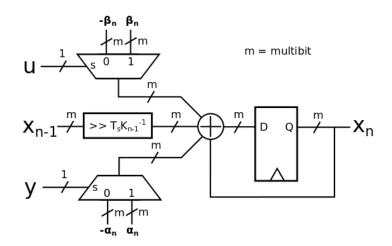

| 3.5               | Sigma Delta Filter Node                                                                                                                                       |

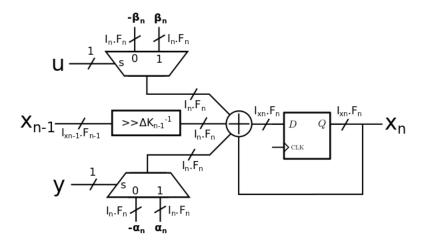

| 3.6               | Sigma Delta Filter Node Bitwidths                                                                                                                             |

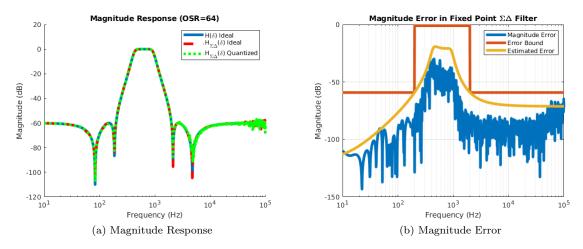

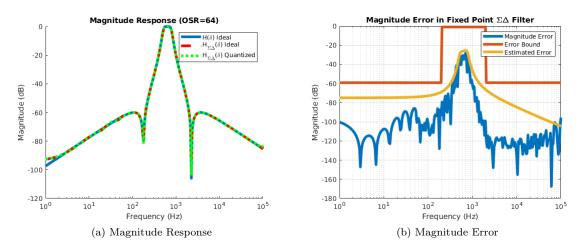

| 3.7               | Filter Magnitude Response $(OSR = 64, ENOB = 12)$                                                                                                             |

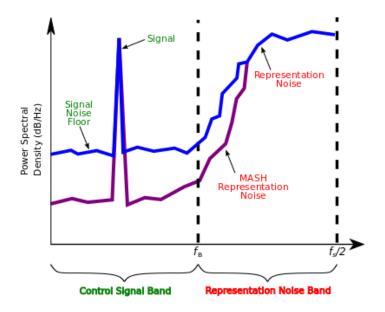

| 4.1               | MASH Power Spectral Density                                                                                                                                   |

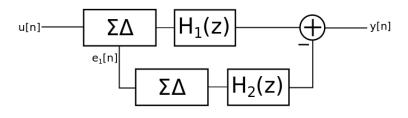

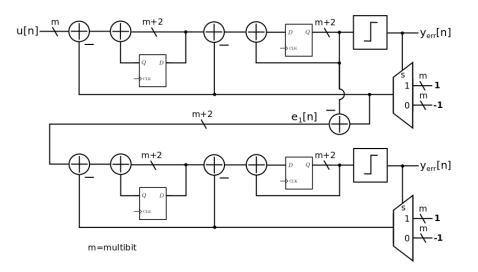

| 4.2               | Conventional 2 Stage MASH                                                                                                                                     |

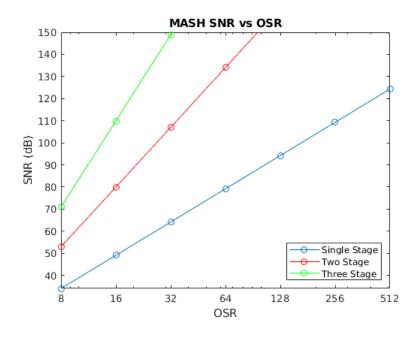

| 4.3               | Ideal MASH 2-2 SNR vs OSR                                                                                                                                     |

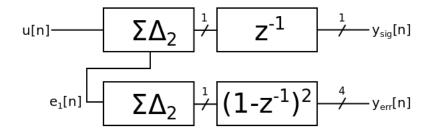

| 4.4               | Proposed 2 Stage MASH                                                                                                                                         |

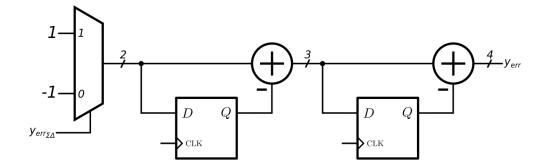

| 4.5               | Double Differentiator Circuit                                                                                                                                 |

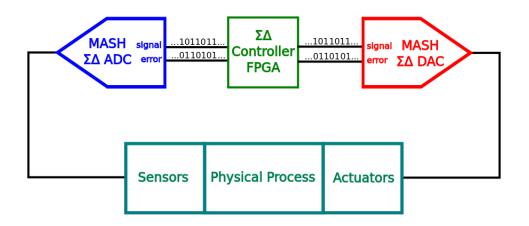

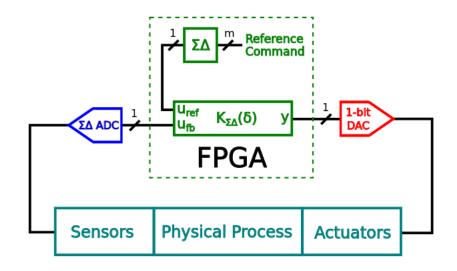

| 4.6               | $MASH \Sigma\Delta Embedded Control System \dots \dots$ |

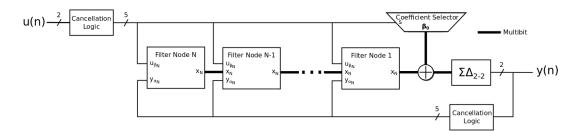

| 4.7               | MASH IIR Filter                                                                                                                                               |

| 4.8               | Discrete MASH $\Sigma\Delta$ Circuit                                                                                                                          |

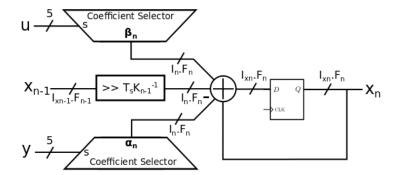

| 4.9               | MASH IIR Filter Node                                                                                                                                          |

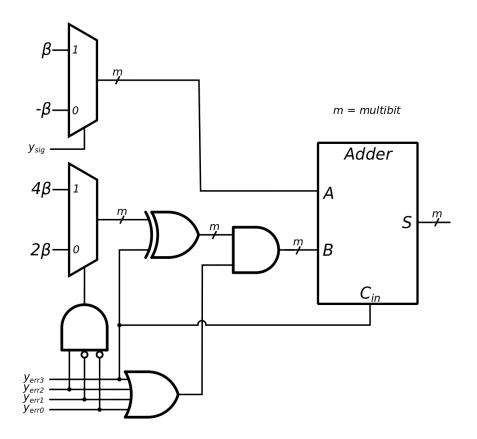

|                   | MASH 2-2 Coefficient Selector Circuit                                                                                                                         |

|                   | MASH $\Sigma\Delta$ Filter Node Bitwidths                                                                                                                     |

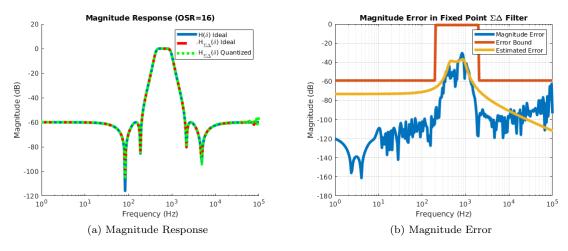

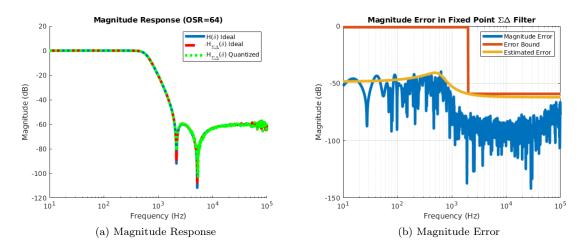

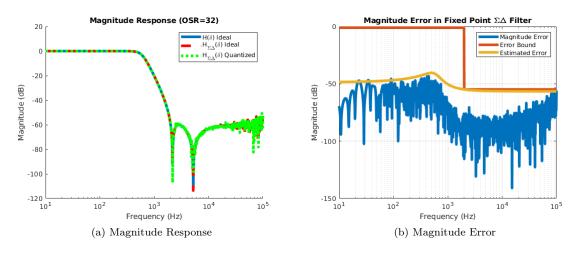

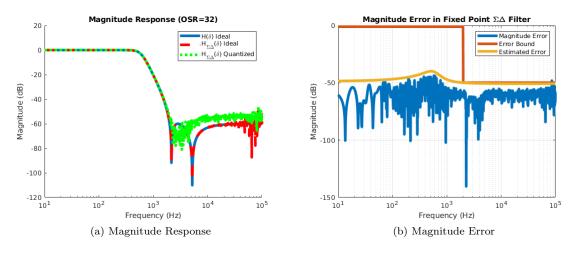

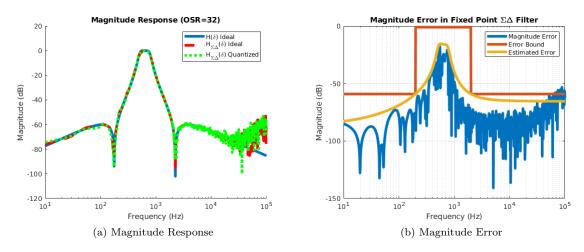

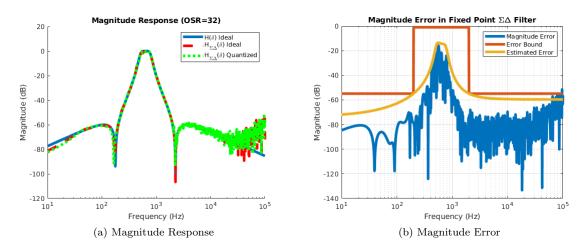

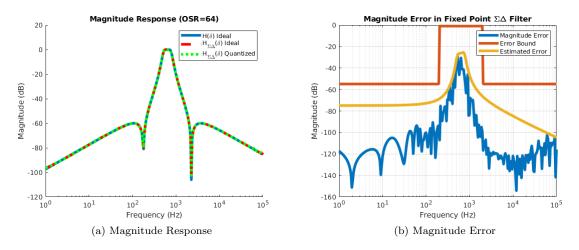

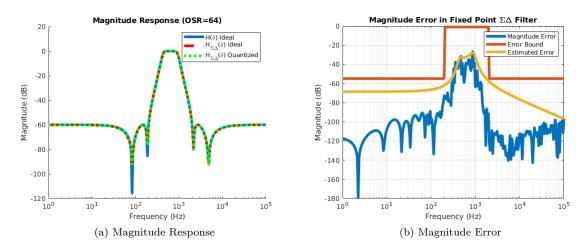

|                   | Filter Magnitude Response and Error                                                                                                                           |

|                   | ~ *                                                                                                                                                           |

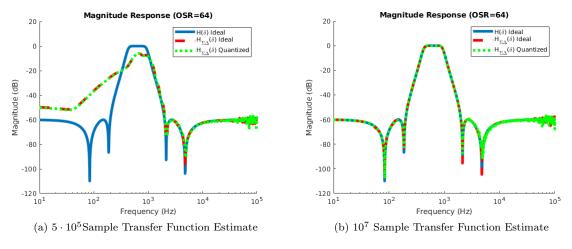

| 5.1  | Insufficient Sample PSD Effects                                                                                                                                                              |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

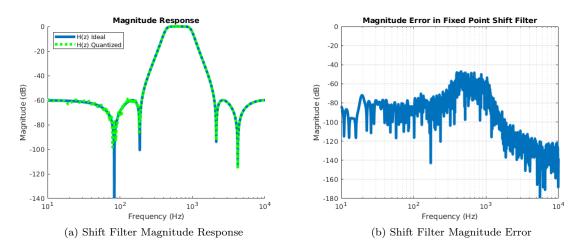

| 5.2  | Magnitude Response and Error for Shift Based Bandpass Filter Design 96                                                                                                                       |

| 5.3  | Lowpass Filter (4th order, OSR=64, $\rho_{LP1}$ )                                                                                                                                            |

| 5.4  | Lowpass Filter (4th order, OSR=32, $\rho_{LP2}$ )                                                                                                                                            |

| 5.5  | Lowpass Filter (4th order, OSR=32, $\rho_{LP3}$ )                                                                                                                                            |

| 5.6  | Bandpass Filter (6th order OSR=32, $\rho_{BL1}$ )                                                                                                                                            |

| 5.7  | Bandpass Filter (6th order OSR=32, $\rho_{BP2}$ )                                                                                                                                            |

| 5.8  | MASH Bandpass Filter (6th order OSR=64, $\rho_{BL1}$ )                                                                                                                                       |

| 5.9  | MASH Bandpass Filter (6th order OSR=64, $\rho_{BL2}$ )                                                                                                                                       |

| 5.10 | MASH Bandpass Filter (8th order OSR=64, $\rho_{BL2}$ )                                                                                                                                       |

|      |                                                                                                                                                                                              |

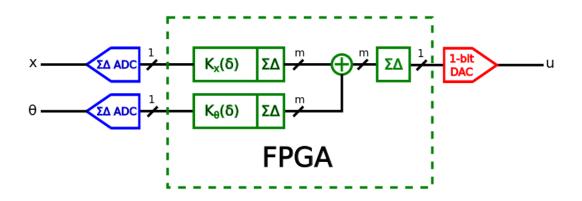

| 6.1  | Reference Tracking Embedded $\Sigma\Delta$ Controller                                                                                                                                        |

| 6.2  | RTL Diagram of Reference Tracking $\Sigma\Delta$ Controller                                                                                                                                  |

| 6.3  | LQG Regulator System Diagram                                                                                                                                                                 |

| 6.4  | $H_\infty$ Controller Diagram                                                                                                                                                                |

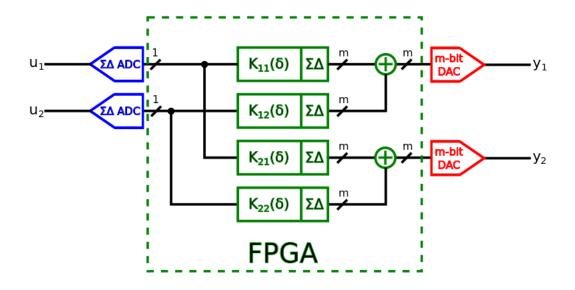

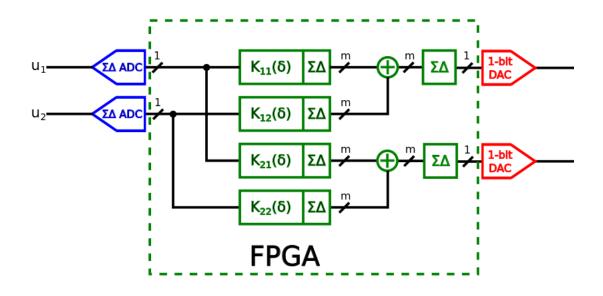

| 6.5  | MIMO Configuration with Parallel Output                                                                                                                                                      |

| 6.6  | MIMO Configuration with $\Sigma\Delta$ Encoded Output $\ldots \ldots \ldots$ |

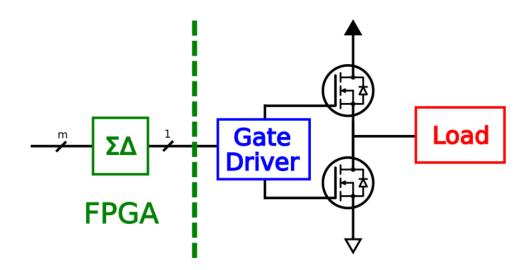

| 6.7  | $\Sigma\Delta$ Output Half-Bridge Drive                                                                                                                                                      |

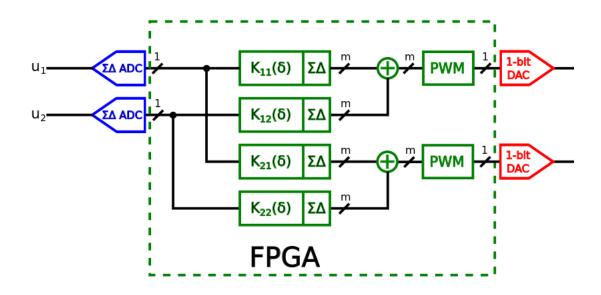

| 6.8  | MIMO Configuration with Pulse Width Modulated Output 124                                                                                                                                     |

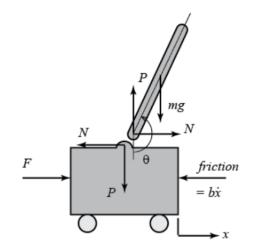

| 6.9  | Inverted Pendulum on a Cart                                                                                                                                                                  |

|      | Pendulum Controller FPGA Implementation                                                                                                                                                      |

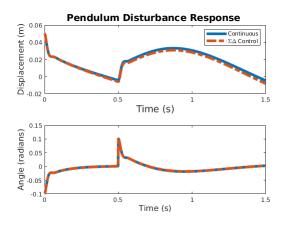

| 6.11 | Pendulum Controller Time Simulation                                                                                                                                                          |

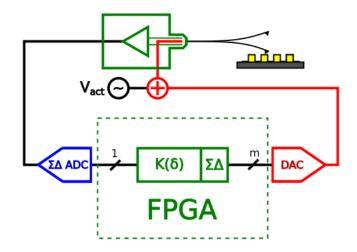

| 6.12 | AFM Cantilever Q Control Loop Implementation                                                                                                                                                 |

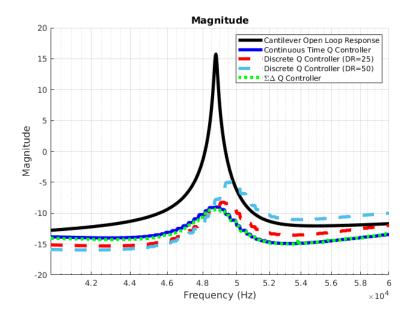

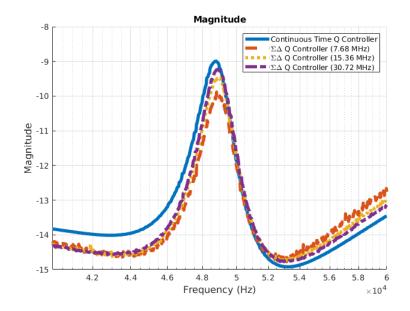

| 6.13 | AFM Continuous, Discrete, and $\Sigma\Delta$ Q-Controller Magnitude Response 130                                                                                                             |

| 6.14 | AFM $\Sigma\Delta$ Q-Controller Magnitude Response                                                                                                                                           |

|      |                                                                                                                                                                                              |

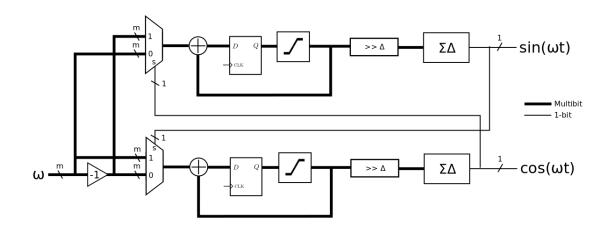

| 7.1  | Two Phase Oscillator Circuit                                                                                                                                                                 |

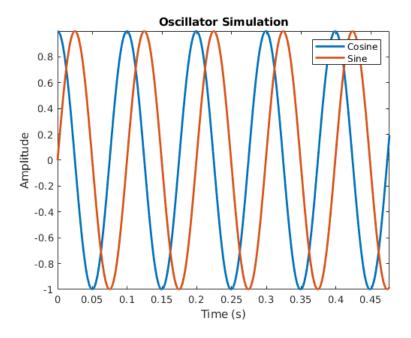

| 7.2  | Two Phase Oscillator Simulation 140                                                                                                                                                          |

# List of Tables

| 2.1          | DC $\Sigma\Delta$ Input and Corresponding Bitstream Output                                                                                                           | 32       |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| $3.1 \\ 3.2$ | Design Parameters of $\Sigma\Delta$ Filter                                                                                                                           | 67<br>68 |

| $4.1 \\ 4.2$ | Design Parameters of MASH $\Sigma\Delta$ Filter                                                                                                                      | 88<br>89 |

| $5.1 \\ 5.2$ | Band-pass Shift Filter FPGA Resource Utilization $\dots \dots \dots$ | 96       |

| db)<br>5.3   | Lowpass Filter Implementation (Cheby II f_band= $2kHz$ , f_b= $10kHz$ , Rs = 60                                                                                      | 101      |

|              | Lowpass Filter Implementation (Cheby II f band= $2kHz$ , f b= $100kHz$ , Rs = $60$                                                                                   | 101      |

|              | Bandpass Filter Implementation (Cheby II f $band=2kHz$ , f $b=10kHz$ , Rs = 60                                                                                       | 102      |

| db)          | Bandpass Filter Implementation (Cheby II f band= $2kHz$ , f b= $10kHz$ , Rs = 60                                                                                     | 104      |

| db)          | Bandpass Filter Implementation (Cheby II f band= $2kHz$ , f b= $100kHz$ , Rs =                                                                                       | 105      |

| 60 d         | b)                                                                                                                                                                   | 105      |

| Rs =         | $= 60 \text{ db}) \dots \dots$                                 | 108      |

| Rs =         | MASH Bandpass Filter Implementation (Cheby II f_band=2kHz, f_b=10kHz,<br>= 60 db)                                                                                    | 109      |

|              | MASH Bandpass Filter Implementation (Cheby II f_band=2kHz, f_b=10kHz, = 60 db)                                                                                       | 110      |

| 6.2          | $\Sigma\Delta$ Q Controller Fixed Point Parameters                                                                                                                   |          |

| 6.1          | $\Sigma\Delta$ Q Controller Parameters                                                                                                                               | 131      |

### Chapter 1

## Introduction

### 1.1 Motivations

Digital embedded controllers have become indispensable in modern life. Practically every modern convenience makes use of embedded digital control in order to improve performance, cost, and reliability. Lithium Ion batteries, for instance, contain an embedded charge controller running on a micro-processor to manage complex charging profiles that improve capacity and longevity as well as preventing cell detonation. The advent of digital technology has made embedded processors extremely inexpensive with the consequence that the vast majority of embedded controllers are implemented in software. Despite the effectiveness of micro-controllers in implementing complex control inexpensively, there are performance limitations that impair the ability to be a viable implementation solution for many applications requiring low latency and/or high bandwidth.

Software based control on a micro-controller requires several thousands of processor instructions to service interrupts and perform loop iterations. At practical clock rates, the latency at which a micro-controller can sample data, process a control algorithm, and update the control output is on the scale of tens of microseconds at best. For applications that require bandwidths above tens of kilohertz, digital signal processors (DSPs) are required. Having hardware architectures that are designed for high throughput and high bandwidth computation, DSPs are able to reduce the latency of digital control implementations to hundreds of nanoseconds. The price for the reduced latency, however, is a substantial increase is component cost, as well as drastic increase in power consumption to the point where mobile (battery based) implementations are often impossible.

For control applications requiring bandwidths of a megahertz or more, the current options are logic-based hardware control using field programmable gate arrays (FPGAs) or continuous control implemented with analog components. Applications such as micro-electromechanical-systems (MEMS) and atomic force microscopy require very high bandwidth controllers, due to the small device scale. [59] FPGA programmable logic can accommodate complex controller designs that can run at hundreds of megahertz with the downside of being high cost and requiring high power consumption. Analog components on the other hand, can achieve control bandwidths of greater than hundreds of megahertz but have a litany of issues. These issues include controller hardware inflexibility, high cost, low reliability, high noise, and high sensitivity to parameter variations and drift which contribute to the complexity of such designs [7]. All of these issues contribute to the high cost of constructing controllers for low-latency systems. This is particularly onerous for MEMS devices where the base cost could be quite low due to economies of manufacturing scale.

This thesis presents an alternative strategy for implementing low complexity, low power, low latency, continuous time performance controllers in digital logic. The control implementation strategy does this by directly processing high resolution, high bandwidth  $\Sigma\Delta$  encoded bitstreams. Both inputs and outputs can be encoded as sigma-delta bitstreams leading to inexpensive composability and a substantial reduction of communication costs. Additionally, the potential for stable operation in adverse environments is enhanced as this representation is not place sensitive (bit-weighted) and is inherently incremental. Thus, such controllers are candidates for satellite and high reliability applications as well as extreme low power (IOT) scenarios.  $\Sigma\Delta$  converters are the premier data converter for high resolution, medium bandwidth applications. They are inexpensive, exceptional linear, and produce a compact oversampled bitstream representation as their natural outputs. This work allows direct connection between  $\Sigma\Delta$  converters and the controller hardware without need to perform parallel data conversion and thus eliminates the associated overhead and latency.

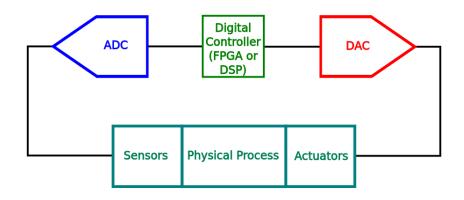

These ideas can be made more concrete by by means of controller block signal flow diagram. The signal chain samples an underlying continuous phenomena and converts it to a discrete signal representation, processes the sampled data via the discrete control law, and then converts the output sampled data back into an analog actuation signal. Such a signal chain is depicted in Figure 1.1.

Figure 1.1: Conventional Embedded  $\Sigma\Delta$  Control Loop

As shown above, the signal chain is comprised of the following components:

- Physical Process: This is the physical process that is intended to be controlled.

- Sensors/Transducers: Sensors and transducers are the components that convert a physical phenomenon (e.g. sound waves, pressure, displacement, etc.) to an electrical signal such as Voltage. These devices can range from microphones to accelerometers.

- Analog to Digital Converter (ADC): The ADC converts as electrical signal, typically a Voltage, into a series of time sampled discrete binary values.

- FPGA, DSP,  $\mu$ Controller: The control law in implemented discretely in a processing element such as a digital signal processor or  $\mu$ controller or in discrete hardware inside of an

FPGA. For the DSP and  $\mu$ controller, the control law is written in a low level programming language such as C in order more closely manage the binary mathematics that underlie the control law.

- Digital to Analog Converter (DAC): The DAC converts a discrete binary value into an electrical signal such as a Voltage.

- Actuator: The actuator is the component that physically interacts with the outside world. These could be motors, voice coils, electromagnets, etc. and are driven by the output of the DAC.

For a general embedded control system, each component is indispensable in the implementation of the control algorithm. However, proper care must be taken by the design engineer in choosing components that will meet or exceed the required closed loop performance constraints. For example, two of the most important considerations when selecting components are that of sampling frequency and resolution. ADCs, for instance, come in several varieties that have trade-offs in sampling frequency/bandwidth and resolution. For loops that require both high resolution and high bandwidth, finding an appropriate ADC may be expensive or outright impossible given the system constraints. In these cases analog controllers are used despite their issues regarding additional noise, environmental degradation, and hardware non-flexibility.

Currently, embedded digital control systems suffer pervasive limitations due to the digital algorithm implementation structured around processing 2's compliment signal representations at rates not far from Nyquist bounds. The reason for doing so is the intuitive simplicity of the time-shift/Z-transform model and is reinforced by the control design software (both system level and implementation) making this assumption. The ubiquity of these models and tools builds expectations of latency, complexity, and power consumption into the design methodology. Indeed, the view of many control engineers is that increasing the sampling bandwidth substantially beyond Nyquist adds complexity and expense as well as decreasing the stability of the implementation. This view is supported by classical analysis of coefficient resolution versus sampling rate, again given the time-shift implementation paradigm. In this thesis, simple controllers are implemented that exploit the inherent oversampling of the input ADC. Based on

digital integrators instead of time-shift operators, the new designs offer latencies on the scale of the oversampling clock period while demonstrating enhanced stability and relaxation of coefficient resolution. (As an example, a high-order bandbass filter can be directly implemented as a single filter element in contrast to composed bi-quad elements made to accommodate coefficient sensitivity at high sample rates). A side benefit of this methodology allows the removal of all hardware multipliers from the design allowing for substantive hardware power and complexity savings, without any latency cost.

#### 1.1.1 Limitations in Conventional Discrete Control Algorithms

While DSPs and FPGAs have made digital control extremely viable in regards to the synthesis of complex control algorithms, there are a number of challenges that limit practical performance. Perhaps the most detrimental aspect of conventional controller designs is the of discrete shift operator constructions. This model is one where a the next controller state x depends on a function f of current values of x and input u at time index k which can be written as

$$x\left(k+1\right) = f\left(x\left(k\right), u\left(k\right)\right)$$

For the linear system variety, the Z-transform is the primary tool for analysis and frequency domain design. The shift operator and Z-transform constitute the predominant paradigm in discrete time controller design, analysis, and implementation. Although it may seem shocking, shift operator based controllers are actually poorly suited to implement controllers that require high performance in terms of simultaneous latency and resolution.

Consider the continuous time state space controller model

$$\dot{x} = Ax + Bu$$

$$y = Cx + Du$$

where  $x \in \mathbb{R}^n$ ,  $y \in \mathbb{R}^m$ ,  $u \in \mathbb{R}^k$ ,  $A \in \mathbb{R}^{n \times n}$ ,  $B \in \mathbb{R}^{n \times k}$ ,  $C \in \mathbb{R}^{m \times n}$ ,  $D \in \mathbb{R}^{m \times k}$ , and  $n, m, k \in \mathbb{Z}^+$ . Applying a zero-order hold discretization method with a defined sampling period  $\Delta$ , the discrete shift operator based equivalent model becomes

$$x^+ = A_z x + B_z u$$

$$y = C_z x + D_z u$$

where

$$A_{z} = e^{A\Delta}$$

$$B_{z} = \int_{0}^{\Delta} e^{A(t-\tau)} B d\tau$$

$$C_{z} = C$$

$$D_{z} = D$$

Now suppose that one were to reduce  $\Delta$  to a small value analogous to significantly increasing the sampling frequency. As the sampling period approaches zero the state transition matrix  $A_z$ becomes

$$\lim_{\Delta \to 0} A_z = \lim_{\Delta \to 0} e^{A\Delta} = I$$

The implication here is that for fast sampling controllers, the state transition matrix  $A_z$  approaches the identity matrix and imposes the issue of the system poles (i.e. the eigenvalues of  $A_z$ ) gravitating to z = 1 on the real axis in the complex plane. System poles approaching a limit point on the stability boundary makes the overall control algorithm extremely sensitive to small perturbations in the controller coefficients. Stated another way, the controller requires extremely accurate coefficients to differentiate between the separate pole values. Unfortunately, embedded control systems, whether they are implemented on a DSP, FPGA, or other device, operate on quantized signal and coefficient values. The allowable number of bits to represent a number in real discrete controller implementations is limited, which in turn, limits the achievable sampling rate.

The sensitivity problem associated with shift-based control algorithms leads to controllers that are relatively complex requiring larger, more powerful, and more expensive components to implement. Perhaps the most tragic pitfall of the shift-based controller design is that it disincentives control designers from creating digital controllers that operate at higher bandwidths. Abstractly, controlling any system with lower latency should result in higher performance control. This valid intuition is not supported by the inherent singularity of the Z-transform as bandwidths increase. These issues are in the mathematical model, not in the physical reality. In the case of MEMs devices, where system time scales are significantly smaller due to the down scaling of physical size, high bandwidth is a must. This points to constructing a mathematical model efficiently supporting high bandwidth operation.

### 1.1.2 High Resolution Data Conversion

The sampling frequency of the digital controller will largely be determined by the physical time constants of the physical process itself. Typically, the sample frequency is chosen to be an order of magnitude higher than the highest frequency component of the physical process. After a sampling frequency has been chosen, it is also necessary to choose the resolution of the overall control system. Many factors can determine the required resolution such as system steady-state error bounds or the resolution the front end sensors/transducers. Once the the resolution has been found the first component of the embedded signal chain can be chosen, the analog to digital converter.

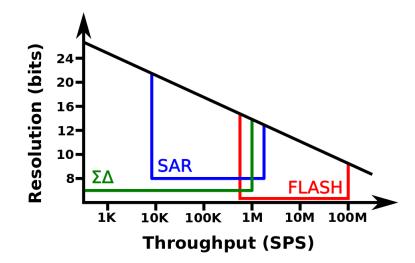

Analog to digital converters come in a variety of architectures each of which has its own trade offs. The most popular ADCs are the Dual-Slope ADC, the Successive Approximation/Pipeline ADC, the  $\Sigma\Delta$  ADC, and the Flash ADC. When it comes the performance metrics of throughput (i.e. sample per second) and resolution, each ADC type occupies a different area in that two dimensional performance space. As can be seen in Figure 1.2, the various ADC types have different trade off in resolution and speed.

Figure 1.2: ADC Architecture Resolution vs. Throughput

In this work, we focus on  $\Sigma\Delta$  ADC which is an oversampled converter whose output is a high speed stream of 1s and 0s. For high resolution and medium throughput requirements,  $\Sigma\Delta$ data conversion is the premier encoding strategy for high performance applications [1]. As such, it find ubiquitous employment in many devices who directly supply the bitstream encoding (so-called PDM or pulse-density-modulation in this use). Everything from ADCs to MEMs microphones to class D amplifier stages currently exist on the market which directly produce or make use of  $\Sigma\Delta$  encoded bitstream signals [10, 11, 6]. However, most designers treat bitstreams as a liability or burden which is demonstrated through how bitstreams are typically converted immediately to a sampled parallel representation.

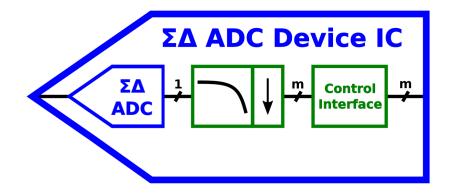

Typical  $\Sigma\Delta$  ADCs have an architecture shown in 1.3. On the front end is the  $\Sigma\Delta$  converter itself which converters the analog signal input to that of an oversampled bitstream of ones and zeros. The bitstream is then lowpass filtered (usually 3rd-order integration) and then decimated to close to the Nyquist Bandwidth in order to convert the bitstream into a bit-parallel number representation. The bit-parallel number is then read out through an interface port, such as a serial peripheral interface (SPI) port, to a processing unit, such as a  $\mu$ controller, DSP, or FPGA.

Figure 1.3: Typical  $\Sigma\Delta$  ADC Architecture

The reason for the conversion is so that the data fits the conventional design paradigm; 2's compliment numbers running at Nyquist rates are easy to understand and design around while alternatives are not widely known. Bitstreams, on the other hand, are difficult to understand; they run at an oversampled rate and the amplitude/information of the signal is not apparent by merely inspecting the waveform. Indeed, in practice, the bit-representation noise is 50x times the signal amplitude. Despite the initial unintuitive nature of the bitstream, it will be shown that controllers with resolutions beyond 24-bits can be easily created directly from bit-stream data.

### 1.2 Direct $\Sigma\Delta$ Processing for High Performance Control

Through understanding the fundamental limitations imposed by the conventional signal chain and controller algorithm design, we now come to the question of whether or not we can supplant the conversion and interface logic and process  $\Sigma\Delta$  encoded bitstreams directly. The answer to this quandary is a resounding yes and the primary exploration of this thesis.

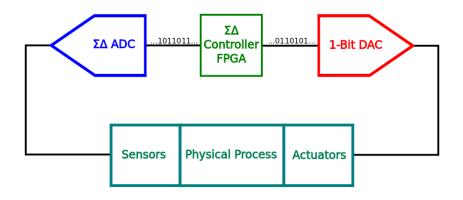

Consider the embedded  $\Sigma\Delta$  controller loop shown in figure 1.4. The diagram illustrates a signal chain where the bitstream from the front end ADC is routed directly to a purpose built controller and whose output is another  $\Sigma\Delta$  encoded bitstream. The output bitstream can at this point be a simple one bit DAC (e.g. a half bridge driver stage). The advantages of such a configuration are obvious. For starters, gone is the lowpass filtering and decimation of the bitstream leaving a simple one bit interface. The output of the controller is a one bit interface as well with both streams running at the oversampled clock rate. Not only is input and output interface complexity greatly reduced, but so is the controller latency. What is not seen in the diagram is that the controller will run at the oversampled clock rate in the FPGA fabric as well, creating a signal chain that has significantly reduced latency. As a consequence, controller bandwidth and stability margins increase substantially.

Figure 1.4: Embedded  $\Sigma\Delta$  Control Loop

Another advantage obfuscated in the diagram is the complexity of the controller itself. As will be shown later chapters, the resource complexity of the controller in the FPGA fabric is substantially reduced compared to its conventional counterparts due to the simplification of arithmetic operations on one bit wide signals as opposed to multibit wide 2's compliment representations. The reduction in hardware complexity means that smaller, lower power, and less expensive FPGAs (or ASICs) can be used for implementations. This is due to the elimination of multipliers (the single largest digital component) from these designs.

### 1.3 Contributions and Thesis Outline

This dissertation presents a methodology for the optimized hardware design of  $\Sigma\Delta$  controllers for use in embedded FPGA and ASIC systems.  $\Sigma\Delta$  controllers are discrete circuits which emulate continuous time transfer functions and whose input and output are  $\Sigma\Delta$  encoded binary bitstreams. The following contributions will be made in the remainder of the document:

- 1.  $\Sigma\Delta$  Controller Design and Noise Analysis: For this contribution, the discrete  $\Sigma\Delta$  Controller architecture will be described in great detail at the register transfer level (RTL) with attention given to choosing bitwidths in the internal signal paths of the circuit. Representation noise associated with  $\Sigma\Delta$  encoded signals and the noise injection from these components are accurately modeled with an appropriate linear noise transfer function (NTF) model.

- 2. MASH  $\Sigma\Delta$  Controllers: As a means to increase the overall resolution of a  $\Sigma\Delta$  controller beyond what is possible with a single stage modulator, multistage noise shaping (MASH)  $\Sigma\Delta$  converters will be introduced into the discrete controller architecture. By making modest modifications to the original controller circuitry, MASH based controllers have the capacity to achieve very high resolution at lower clock rates in comparison to the single stage designs. MASH based controllers can also be clocked at significantly lower rates to achieve the same resolution as the original single stage design. Details on how to design the MASH controller circuitry will be presented as well as an appropriate noise analysis.

- 3. Controller Optimization: Taking quantization noise and coefficient quantization/transfer function deviation into account, a convex optimization strategy is proposed for reducing the number of bits required for the internal signals of the controller architecture. The optimizer in turn reduces the number of flip flops required for the controller state. Given a controller design, coefficients and internal signal bitwidths are adjusted in order to meet noise and transfer function deviation metrics set by the designer.

- 4. Implementation and Resource and Power Analysis: Given a  $\Sigma\Delta$  controller design, it will be shown how to implement the circuit in an FPGA. Various designs will be presented that

range in filter order, clock frequency, and resolution in order to assess the compactness and efficiency of the  $\Sigma\Delta$  controller architecture. It will also be demonstrated that the designs can indeed fit within small low power FPGAs that lack any internal digital signal processing resources.

The remainder of this thesis is arranged as follows: Chapter 2 focuses on modeling and characterization of  $\Sigma\Delta$  bitstreams. A linear frequency model of the modulator dynamics will be presented as well as how to use a power spectral density estimate of the bitstream to quantify the resolution of the encoding. Nonlinear phenomena that degrade the quality of the bitstream will also be explored as well as how to mitigate their effects. In chapter 3, the hardware description of the  $\Sigma\Delta$  controller architecture is described. A design and performance analysis is presented as well in addition to an optimization strategy that reduces the number of bits required in the internal signals of the circuit. Chapter 4 expands on the architecture of the previous chapter by adapting it to process multistage noise shaping  $\Sigma\Delta$  encoded input and output signals for high resolution controller applications. Chapter 5 delves into the hardware implementation of the controller architectures presented in the previous two chapters particularly in regards to FPGA design. In chapter 6, various controller/filter examples will be implements based on various design criteria and compared for resolution, power, and FPGA resource usage. The final chapter will illustrate several motivating control examples that take advantage of the high performance and low complexity of the  $\Sigma\Delta$  controllers and show that these controllers offer a superior implementation compared to conventional embedded controller designs.

### Bibliography

- N. N. Cikan and M. Aksoy. Analog to Digital Converters Performance Evaluation Using Figure of Merits in Industrial Applications. In 2016 European Modelling Symposium (EMS), pages 205–209, Nov 2016.

- [2] M. B. Coskun, H. Alemansour, A. G. Fowler, M. Maroufi, and S. O. R. Moheimani. Q Control of an Active AFM Cantilever With Differential Sensing Configuration. *IEEE Transactions on Control Systems Technology*, pages 1–8, 2018.

- [3] G. C. Goodwin, R. H. Middleton, and H. V. Poor. High-speed digital signal processing and control. *Proceedings of the IEEE*, 80(2):240–259, Feb 1992.

- [4] D.A. Johns and D.M. Lewis. Sigma-delta based IIR filters. In Circuits and Systems, 1991., Proceedings of the 34th Midwest Symposium on, pages 210–213 vol.1, May 1991.

- [5] Y. Matsuya, K. Uchimura, A. Iwata, et al. A 16-bit oversampling A-to-D conversion technology using triple-integration noise shaping. *IEEE Journal of Solid-State Circuits*, 22(6):921–929, Dec 1987.

- [6] Maxim Integrated. MAX98356: PDM Input Class D Audio Power Amplifier, July 2013. Rev. 1.

- [7] P Murphy, M Xie, Y Li, et al. Study of digital vs analog control. In Power Electronics Seminar Proceedings (CPES Center for Power Electronics Systems), pages 203–206, 2002.

- [8] Chiu-Wa Ng, Ngai Wong, H. Kwok-Hay So, and Tung-Sang Ng. Direct sigma-delta modulated signal processing in FPGA. In *Field Programmable Logic and Applications, 2008. FPL 2008. International Conference on*, pages 475–478, Sept 2008.

- [9] R. Schreier and G.C. Temes. Understanding Delta-Sigma Data Converters. Wiley, 2004.

- [10] STMicroelectronics. MP34DT05-A: MEMS audio sensor omnidirectional digital microphone, April 2019. Rev. 4.

- [11] Texas Instruments. ADS1204: Four 1-Bit, 10MHz, 2nd-Order Delta-Sigma Modulators, February 2009.

- [12] X. Wu and R. M. Goodall. One-bit processing for digital control. *IEE Proceedings Control Theory and Applications*, 152(4):403–410, July 2005.

### Chapter 2

# $\Sigma\Delta$ Encoded Pulse Density Modulated Signals

This thesis is predicated on the notion of performing signal processing upon pulse density modulated (PDM) signal representations. This implies that provisions for both efficient input and output of PDM encoded stream data must be supported. PDM is a one bit wide oversampled bitstream signal typically produced from a  $\Sigma\Delta$  modulator circuit and used extensively in analog to digital converter architecture designs. These bitstreams have a variety of unique properties such as frequency dependent representation noise that must be understood and characterized for effective use in arithmetic circuits. This chapter will describe PDM signals, how they are characterized and modeled, their drawbacks and limitations, and under what conditions  $\Sigma\Delta$  modulators may be directly used as PDM encoders for embedded control loop implementations.

### 2.1 Pulse Density Modulation

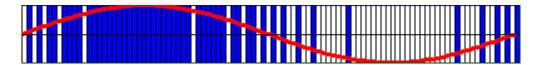

Pulse density modulation is a signal representation in the form of a stream of bits; ones and zeros. Whereas the information in an analog signal or a discrete parallel bit word sample (i.e. 2's complement) is contained within the amplitude, the information of a PDM signal is contained within the density of bits over a finite window of time. Take for instance the discrete sinusoidal signal and its PDM counterpart in figure 2.1.

Figure 2.1: Pusle Density Modulated Sinusoid Signal

As can be seen in the figure, the density of ones increases when the sinusoidal amplitude is closer to max amplitude while the density of zeros increases when the sinusoidal amplitude is closer to minimum amplitude. While PDM bitstreams are a sequence of ones and zeros, the binary bit values of the stream can be interpreted in one of two ways:

- Bipolar: Suppose a discrete signal x [n] is bounded in amplitude on the interval [-A, A] where A is the maximum magnitude of x [n]. Then a 1 in the corresponding PDM encoded signal of x [n] represents a value of A and a 0 represents a value of -A.

- Unipolar: Suppose a discrete signal x[n] is bounded in amplitude on the interval [0, A] where A is the maximum magnitude of x[n]. Then a 1 in the corresponding PDM encoded signal of x[n] represents a value of A and a 0 represents a value of 0.

In this work, PDM signals will be interpreted as bipolar in order to take advantage of the symmetry of the representation and ability to simply represent negative values.

Given a PDM signal, it may become useful to demodulate the bitstream in order to recover the original pulse code modulated (PCM) signal. To first order, the original signal can be obtained via discrete integration of the bitstream. Suppose a bitstream signal  $q[n] \in [-A, A]$ . Its PCM counterpart can be obtained by

$$x\left[n\right] = \frac{1}{\Delta} \sum_{k=-\infty}^{n} q\left[k\right]$$

where  $\Delta$  is the sampling period of the oversample rate. While simply integrating may not provide the best demodulation technique as opposed to high order lowpass filtering, it does hint at the fact that the signal information in q[n] is contained within the baseband component. To better understand how to make use of bitstream signals and preserve their information, one must first understand how they are characterized. When encoding signals with PDM bitstreams, it is appropriate to ask questions about whether or not the bits are making an accurate representation. In particular, it is important to understand the nature of both the signal representation and the implicit noise inherent in representing a signal as a PDM bitstream. In the time domain, there is great difficulty in determining what the average value of the bitstream is at any given moment; one must first filter the bitstream to reveal its analog counterpart. However, in the frequency domain, the question becomes much clearer.

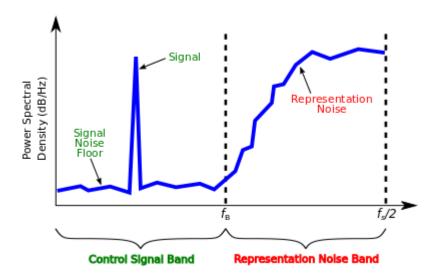

The power spectral density (PSD) of a PDM signal is the principle representation in which to analyze and characterize a bitstream as its signal and noise power versus frequency. The PSD reveals characteristics about a bitstream such as the signal it is encoding, the quality of the signal, and the distribution of the noise inherent in the representation. The anatomy of a power spectral density of a pulse density modulated signal can be seen in figure 2.2.

Figure 2.2: Anatomy of PDM Signal PSD

The PSD pictured is that of a PDM encoded discrete sinusoidal signal with a fundemental frequency of  $f_{sig}$ . The signal component can be seen as a spike at  $f_{sig}$ . Perhaps the most striking aspect of the PSD is the shape of the noise floor. The noise floor of the signal is flat in the lower frequencies up to  $f_B$  which corresponds to the input resolution of the encoded discrete signal or noise-floor associated with the input analog signal. (Abstractly, there is no lower bound on the PSD noise at low frequencies if sufficiently large resolution is used). In the higher frequencies, from  $f_B$  to  $f_s/2$ , the noise floor increases dramatically and saturates the power spectrum. The concentration of noise power in the higher frequencies is a hallmark of PDM signals and is in fact a by-product of the feedback correction nature of the encoder. That is, the high frequency noise is inherent in the representation but is pushed out of the signal band (i.e. frequencies below  $f_B$ ) and into the representation noise band (i.e. frequencies above  $f_B$ ). The quality of pushing or shaping the representation noise into high frequencies allows PDM bitstreams to achieve a very high quality encoding at the cost of the higher oversampled rate  $f_s$ versus the desired signal bandwidth  $f_B$ . Since the over-sampled signal is a binary bit-stream, it admits a variety of simple computation mechanisms all operated at the oversampled clock (sample) rate. The large ratio  $f_s/(2f_B)$  allows for very low noise representation of the desired signal band, while the binary nature of the output admits single threshold (hence very linear) ADC. It is for this reason that analog sigma-delta converters are the ubiquitous solution for high-resolution analog signal conversion, at any rate allowing a reasonable over sampling ratio.

In this thesis, the characterization of a PDM bitstream will be derived from its power spectral density. Thus is it necessary to formally introduce a variety of definitions and concepts that will aid in their proper use in later chapters:

• Signal Band: The signal band is the frequency range<sup>1</sup> from DC to  $f_B$  which signal components can exist without the contamination of high levels of background noise.

$<sup>^{1}</sup>$ It is not strictly necessary for the signal band to be base-band and modulated converters exist, however, the design of computation schemes for such designs is relegated to future work. In this work, we shall assume based-band conversion.

- Representation Noise Band: The representation noise band is the frequency range from  $f_B$  to  $f_s/2$  where the representation noise is pushed and dominates the signal spectral density.

- OSR: The oversample ratio (OSR) is the defined as the ratio between the oversampling frequency  $f_s$  and the Nyquist frequency  $2f_B$

$$OSR = \frac{f_s}{2f_B}$$

where  $f_B$  is the signal bandwidth.

• SNR: The signal to noise ratio (SNR) is defined as the ratio between the signal power  $\mu_x^2$  and the noise variance  $\sigma_n^2$  in the signal band from DC to  $f_B$ . The ratio is commonly expressed in units of decibels by

$$SNR(dB) = 10log_{10}\left(\frac{\mu_x^2}{\sigma_n^2}\right)$$

Both  $\mu_x^2$  and  $\sigma_n^2$  can be computed directly from the power spectral density of the PDM signal by integrating over the corresponding spectral density of the signal band  $f_B$ . The noise variance for example can be computed by

$$\sigma_n^2 = \int_{-f_B}^{f_B} S_n\left(f\right) df$$

where  $S_n(f)$  is the noise power spectral density. The SNR provides a metric for the quality of the encoded bitstream signal.

SINAD: The signal to noise and distortion ratio is defined as the ratio between the signal power μ<sup>2</sup><sub>x</sub> and the noise variance σ<sup>2</sup><sub>n</sub> plus the distortion variance σ<sup>2</sup><sub>d</sub> in the signal band from DC to f<sub>B</sub>. This ratio is commonly expressed in units of decibels by

$$SNR\left(dB

ight) = 10log_{10}\left(rac{\mu_{x}^{2}}{\sigma_{n}^{2} + \sigma_{d}^{2}}

ight)$$

Distortion can manifest as undesired frequency components in the power spectral density which lower the overall quality of the signal.

• ENOB: The effective number of bits (ENOB) is a measure of how many bits of signal information are contained in the bitstream signal based on given SNR or SINAD. The ENOB can be calculated by

$$ENOB = \frac{SINAD - 1.76}{6.02}$$

which is derived from and a direct comparison to Nyquist rate pulse code modulated encodings. [50]

The above definitions and concepts provide a basis for the complete characterization of PDM signals that will be used throughout this thesis. It will become evident in later chapters that utilizing PDM signals in signal processing and control-centric hardware implementations requires the ability to maintain the shape and form of their PSD's for high quality computations. In fact, there will be many times when a signal must first be encoded into a PDM in the first place in order to change representations when it is convenient to do so. The circuit to do the conversion from analog/PCM to PDM encoding, the workhorse of this thesis, is the  $\Sigma\Delta$  modulator.

### **2.2** $\Sigma\Delta$ Modulators

The  $\Sigma\Delta$  modulator is the converter/encoder circuit that transforms an analog or pulse code modulated signal into a high resolution bitstream of 1's and 0's. While most widely utilized in analog to digital converter architectures, they also find use in digital to analog converters as well as discrete applications such as phase lock loops [20]. By making use of oversampling and noise shaping,  $\Sigma\Delta$  modulators are able to create high SNR/ENOB PDM bitstream signals. This section will introduce and explain the  $\Sigma\Delta$  theory of operation.

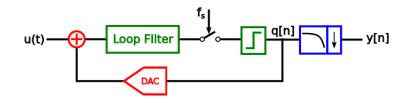

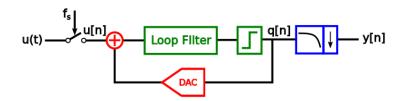

When designed for the purpose of analog to digital conversion,  $\Sigma\Delta$  modulators come in two varieties: analog and discrete. Figure 2.3 illustrates block diagrams of discrete and analog  $\Sigma\Delta$  ADC modulators with common blocks such as the loop filter, quantizer, and DAC. The primary difference between the two is where the discrete sampling takes place; in front of the modulator for discrete and before the quantizer for analog. At the circuit level, the loop filter of the discrete modulated is implemented with a switched capacitor architecture. The analog loop filter can be implemented with gm-C, active RC, LC, or other circuit architectures [50].

(a) Continuous Time  $\Sigma \Delta$

(b) Discrete Time  $\Sigma\Delta$

Figure 2.3: a) Continuous Time and b) Discrete Time  $\Sigma\Delta$  Modulators

Discrete  $\Sigma\Delta$  modulators can be modeled as a discrete piece-wise affine (PWA) system with bimodal dynamics. Consider the following  $\Sigma\Delta$  modulator PWA model

$$x^{+} = \begin{cases} A_{\Sigma\Delta}x + B_{\Sigma\Delta}u + f_{1} & \forall x_{1} \ge 0\\ A_{\Sigma\Delta}x + B_{\Sigma\Delta}u + f_{2} & \forall x_{1} < 0 \end{cases}$$

$$q = \begin{cases} 1 & \forall x_{1} \ge 0\\ -1 & \forall x_{1} < 0 \end{cases}$$

where  $A_{\Sigma\Delta} \in \mathbb{R}^{n \times n}$ ,  $x, B_{\Sigma\Delta}, f_1, f_2 \in \mathbb{R}^n, n \in \mathbb{Z}^+$  and  $q \in [-1, 1]$ . The nonlinear discontinuous nature of the dynamics imposed by the affine term  $f_i$  makes the modulator difficult to directly analyze and establish performance metrics. As will be seen shortly, the shape of the representation noise in Figure 2.2 is highly dependent upon the input signal to the modulator and requires that it hold to various limitations in order to produce a high quality signal encoding. To better ascertain the mysteries of the bitstream, it becomes necessary to fabricate a more tractable method for modeling its behavior.

### 2.2.1 $\Sigma\Delta$ Linearized Model

While the dynamics of  $\Sigma\Delta$  modulators are highly nonlinear, there are key assumptions about the nature of the quantization noise which make the analysis more tractable. In order to characterize  $\Sigma\Delta$  encoded bitstreams and estimate their performance, one must have a simple way of modeling the modulator dynamics. Fortunately, a simple model of the  $\Sigma\Delta$  modulator can be derived by making key assumptions about the nature of its one bit quantizer.

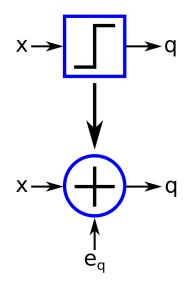

Treating the one bit quantizer as an additive noise source, the dynamics of the  $\Sigma\Delta$  modulator can be analyzed as a linear dynamic system with a stochastic noise input. The invocation of a linear dynamic  $\Sigma\Delta$  model is a well known and widely used technique and has been presented by authors such as Temes and Schreier in [50]. The linearization of the quantizer can be seen in Figure 2.4 while the linearization transformation of a discrete  $\Sigma\Delta$  modulator can be seen in figure 2.5.

Figure 2.4:  $\Sigma\Delta$  Quantizer Linearization

Figure 2.5: Linearization of 2nd Order  $\Sigma\Delta$

The linearized model allows one to modify the nonlinear state space dynamics of a modulator into the linear two input one output model:

$$x^{+} = A_{\Sigma\Delta}x + B_{\Sigma\Delta}u + B_{e}e$$

$$q = C_{\Sigma\Delta}x + e$$

where e is the additive quantization noise input,  $A_{\Sigma\Delta} \in \mathbb{R}^{n \times n}$ ,  $x, B_{\Sigma\Delta}, B_e \in \mathbb{R}^{n \times 1}$ ,  $C_{\Sigma\Delta} \in \mathbb{R}^{1 \times n}$ ,  $e, q \in \mathbb{R}$ , and  $n \in \mathbb{Z}^+$ . Taking the z transform of the linear time domain state space model above, the two following transfer functions from u to q and from  $e_q$  to q can be found as

$$STF(z) = \frac{Q(z)}{U(z)} = C_{\Sigma\Delta} \left( zI - A_{\Sigma\Delta} \right)^{-1} B_{\Sigma\Delta}$$

$$NTF(z) = \frac{Q(z)}{E(z)} = C_{\Sigma\Delta} (zI - A_{\Sigma\Delta})^{-1} B_e + 1$$

The signal transfer function, or STF, is the transfer function from the input to the output of the sigma delta without the addition of quantization noise. The noise transfer function, or NTF, is the quantization noise input to the output of the sigma delta without the signal component. The overall output response of  $\Sigma\Delta$  modulator can be found by

$$Q(z) = STF(z)U(z) + NTF(z)E_q(z)$$

which allows the information to be split between a signal component and representation noise component. The concept of separable signal and noise components is paramount to formulating the power spectral density in order to ascertain the performance of the modulator. To estimate the PSD of the signal output the following assumption about the quantization noise are made:

- 1. The quantization error  $e_q[n]$  is a wide sense stationary, white Gaussian random process.

- 2. The quantization error  $e_q[n]$  is uncorrelated with itself and and the input sequence of the  $\Sigma\Delta$  modulator.

3. The probability-density function of the quantization error  $\rho(e_q)$  is uniform over the entire quantization range  $\left[-\frac{q}{2}, \frac{q}{2}\right]$ .

$$\rho\left(e_{q}\right) = \begin{cases} \frac{1}{q} & |e_{q}| \leq \frac{q}{2} \\ 0 & |e_{q}| > \frac{q}{2} \end{cases}$$

where q is the quantization step.

While these assumptions are not always true, they do give a reasonable description of the actual quantization noise properties inherent in the nonlinear model for small and large amplitude signals with ample frequency content. From here, under these assumptions and the linear model, the PSD of the modulator output can be estimated.

Based on assumption that  $\rho(e_q)$  is uniform over the quantization range  $\left[-\frac{q}{2}, \frac{q}{2}\right]$ , we can find the mean of  $e_q$  as

$$\bar{e}_{q} = E\{e_{q}\} = \int_{-\infty}^{\infty} e_{q}\rho(e_{q}) de_{q} = \frac{1}{q} \int_{-q/2}^{q/2} e_{q} de_{q} = 0$$

and the variance of  $e_q$  as

$$\sigma_e^2 = E\left\{ \left(e_q - \bar{e}_q\right)^2 \right\} = \int_{-\infty}^{\infty} e_q^2 \rho\left(e_q\right) de_q = \frac{1}{q} \int_{-q/2}^{q/2} e_q^2 de_q = \frac{q^2}{12}$$

Due to the assumption that the noise is white, the nominal quantization noise power  $\sigma_e^2$  is spread out uniformly over the entire frequency space. The power spectral density of the additive quantization noise input is thus

$$S_e\left(f\right) = \frac{\sigma_e^2}{f_s}$$

and

$$S_e(f) = \frac{\sigma_e^2}{f_s} = \frac{q^2}{12f_s} = \frac{1}{3f_s}$$

for a unipolar single bit quantizer (i.e. q = 2).

At this point, the filtering of  $S_e(f)$  through the noise transfer function NTF(f) must be taken into account. The noise transfer function NTF(f) shapes the power spectral density of the additive quantization noise which leads to a noise power over the signal band to be found by the equation

$$\sigma_{\Sigma\Delta}^{2} = \int_{-f_{b}}^{f_{b}} S_{e}\left(f\right) \left|NTF\left(f\right)\right|^{2} df$$

Typically,  $NTF(f) \ll 1$  in the signal band and  $NTF(f) \approx 1$  in the representation noise band. The noise transfer dynamics thus attenuate signal band noise energy and push the vast majority of the noise energy into high frequencies. This is called noise shaping. The signal transfer function STF(f) on the other hand is typically unity gain in the frequency band allowing the signal to pass through while suppressing the representation noise. This leads to a very high SNR in the signal band of the PSD.

In order to characterize the performance of the modulator, sinusoidal inputs are generally chosen to calculate signal to noise ratios for individual frequency components. Supposing a sinusoid signal with period T and amplitude A, its average power over the signal band can be found by

$$\mu_x^2 = \frac{1}{T} \int_0^T \left( A\cos\left(\frac{2\pi t}{T}\right) \right)^2 dt = \frac{A^2}{2}$$

Having the average noise power of a sinusoidal input at any frequency depend only upon the amplitude of the signal allows a convenient way of calculating SNR as given by

$$SNR_{dB} = 10 \cdot log_{10} \left(\frac{\mu_x^2}{\sigma_{\Sigma\Delta}^2}\right)$$

In principle, the SNR should remain constant in the signal band for a sinusoid at any frequency for a given modulator.

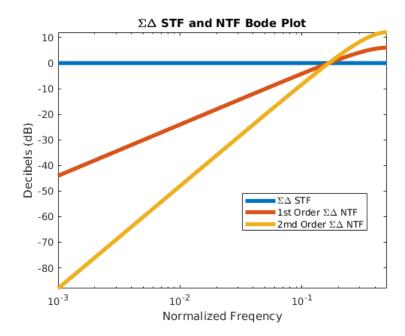

#### 2.2.2 1st and 2nd Order Noise Shaping Representations

The noise transfer function of the  $\Sigma\Delta$  modulator defines the noise shaping that manifests in the passband of the bitstream signal. To have a sharper noise transfer function is to have a potentially higher signal to noise ratio. The shape of the noise transfer function corresponds to the order of the modulator or rather the number of delay elements that exist in the loop.

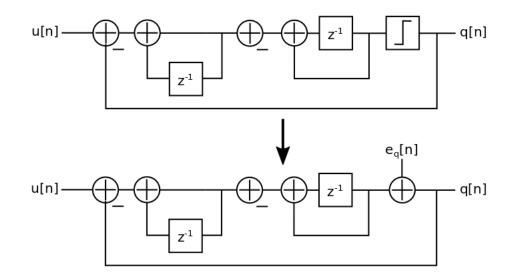

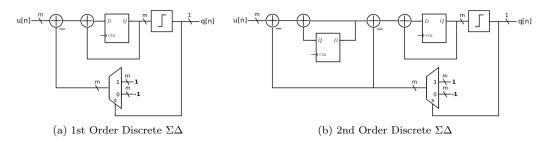

The first and second order discrete  $\Sigma\Delta$  modulators shown in figure 2.6, consists of one and two accumulators respectively as well as a 1 bit quantizer in the feedforward path.

Figure 2.6: 1st and 2nd Order Discrete  $\Sigma\Delta$  Modulators

By imposing the linear additive noise model on the 1st and 2nd order modulators it becomes straightforward to derive their signal and noise transfer functions. For the 1st order modulator the STF and NTF are