# Using modern C++ to improve CUDA programs

By

#### MYTHREYA KURICHETI THESIS

Submitted in partial satisfaction of the requirements for the degree of

#### MASTER OF SCIENCE

in

**Computer Science**

in the

#### OFFICE OF GRADUATE STUDIES

of the

UNIVERSITY OF CALIFORNIA

DAVIS

Approved:

John D. Owens, Chair

Jason Lowe-Power

Julian Panetta

Committee in Charge

2024

Copyright © 2024 by Mythreya Kuricheti All rights reserved. To my parents and my brother

# CONTENTS

|   | List       | f Figures                                                                                                                               | 'n |

|---|------------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

|   | List       | f Tables                                                                                                                                | i  |

|   | Abst       | act                                                                                                                                     | i  |

|   | Ackı       | owledgments                                                                                                                             | X  |

|   | <b>-</b> . |                                                                                                                                         |    |

| 1 | Intro      |                                                                                                                                         | 1  |

|   | 1.1        | The Problem                                                                                                                             | 1  |

|   | 1.2        | Prior work                                                                                                                              | 2  |

|   |            | 1.2.1 Compilers                                                                                                                         | 3  |

|   |            | 1.2.2 Libraries                                                                                                                         | 4  |

|   | 1.3        | Approach                                                                                                                                | 4  |

|   | 1.4        | Goals                                                                                                                                   | 5  |

|   | 1.5        | Contributions                                                                                                                           | 6  |

|   | 1.6        | Benefits                                                                                                                                | 7  |

|   | 1.7        | Outline                                                                                                                                 | 7  |

|   |            |                                                                                                                                         |    |

| 2 | Bacl       |                                                                                                                                         | 9  |

|   | 2.1        | The GPU                                                                                                                                 | 9  |

|   | 2.2        | Programming model                                                                                                                       | 0  |

|   |            | 2.2.1 Shaders                                                                                                                           | 0  |

|   |            | 2.2.2 CUDA                                                                                                                              | 1  |

|   | 2.3        | Problem                                                                                                                                 | 2  |

|   | 2.4        | Prior work                                                                                                                              | 5  |

|   |            |                                                                                                                                         |    |

| 3 | Imp        | ementation 10                                                                                                                           | 6  |

|   | 3.1        | constexpr and consteval 10                                                                                                              | 6  |

|   |            | 3.1.1 Introduction $\ldots \ldots 1'$ | 7  |

|   |            | 3.1.2 The problem                                                                                                                       | 7  |

|   |            | 3.1.3 Compile-time evaluation                                                                                                           | 8  |

|     | 3.1.4    | NVCC compilation path            | 19 |

|-----|----------|----------------------------------|----|

|     | 3.1.5    | Using constexpr                  | 20 |

|     | 3.1.6    | Problems with this approach      | 22 |

|     | 3.1.7    | Summary                          | 23 |

| 3.2 | conce    | epts usage                       | 23 |

|     | 3.2.1    | Introduction                     | 24 |

|     | 3.2.2    | The problem                      | 25 |

|     | 3.2.3    | Constraints for kernels          | 25 |

|     | 3.2.4    | Problems with this approach      | 29 |

|     | 3.2.5    | Summary                          | 29 |

| 3.3 | Allocat  | tor                              | 30 |

|     | 3.3.1    | Introduction                     | 30 |

|     | 3.3.2    | Allocators and containers        | 32 |

|     | 3.3.3    | The problem                      | 32 |

|     | 3.3.4    | Allocator using CUDA APIs        | 35 |

|     | 3.3.5    | Potential disadvantages          | 38 |

|     | 3.3.6    | Summary                          | 39 |

| 3.4 | Vector   |                                  | 39 |

|     | 3.4.1    | The problem                      | 40 |

|     | 3.4.2    | Implementation considerations    | 41 |

|     | 3.4.3    | Potential disadvantages          | 44 |

|     | 3.4.4    | Summary                          | 46 |

| 3.5 | Iterator | rs                               | 46 |

|     | 3.5.1    | Introduction                     | 47 |

|     | 3.5.2    | Grid-Stride loop                 | 49 |

|     | 3.5.3    | The problem                      | 49 |

|     | 3.5.4    | Prior work                       | 50 |

|     | 3.5.5    | Grid-stride loop using iterators | 51 |

|     | 3.5.6    | Potential disadvantages          | 53 |

|   |      | 3.5.7    | Summary                 | . 54 |

|---|------|----------|-------------------------|------|

|   | 3.6  | Corout   | tines                   | . 55 |

|   |      | 3.6.1    | Introduction            | . 55 |

|   |      | 3.6.2    | Why coroutines          | . 56 |

|   |      | 3.6.3    | Coroutines in C++       | . 56 |

|   |      | 3.6.4    | Coroutines and CUDA     | . 58 |

|   |      | 3.6.5    | Potential disadvantages | . 60 |

|   |      | 3.6.6    | Summary                 | . 61 |

| 4 | Case | e study  |                         | 62   |

|   | 4.1  | ·        | uction                  | . 62 |

|   | 4.2  |          | round                   |      |

|   | 4.3  | e        | n decisions             |      |

|   |      | 4.3.1    | Existing libraries      |      |

|   |      | 4.3.2    | Native bindings         |      |

|   |      | 4.3.3    | Native solver libraries |      |

|   | 4.4  |          | als                     |      |

|   | 4.5  |          | nentation details       |      |

|   | 4.6  | -        | nentation results       |      |

|   | 4.7  | 1        | ary of implementation   |      |

|   | 4./  | Summa    |                         | . /1 |

| 5 | Futu | ire worl | k                       | 73   |

|   | 5.1  | Future   | work in abstractions    | . 73 |

|   | 5.2  | Future   | work in HEC-RAS         | . 75 |

| 6 | Con  | clusion  |                         | 77   |

| U | COI  | CIUSIVII |                         | 11   |

# LIST OF FIGURES

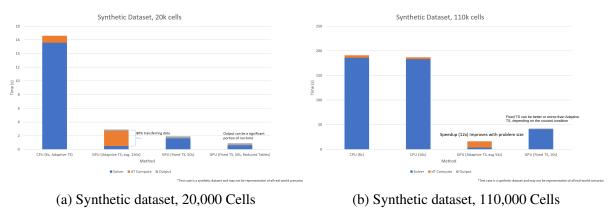

| 4.1 | CPU vs. GPU performance | • |  | • |  | • | • | • | • | • | • | • | • |  |  |  | • | • | • |  |  |  |  | • | • |  | • | 70 | 0 |

|-----|-------------------------|---|--|---|--|---|---|---|---|---|---|---|---|--|--|--|---|---|---|--|--|--|--|---|---|--|---|----|---|

|-----|-------------------------|---|--|---|--|---|---|---|---|---|---|---|---|--|--|--|---|---|---|--|--|--|--|---|---|--|---|----|---|

LIST OF TABLES

#### ABSTRACT

#### Using modern C++ to improve CUDA programs

The classic style of writing and porting HPC applications to the GPU uses pointers to buffers or data-structures as kernel parameters. This style discards type information, leading to "flattening" of CPU-side data-structures before using them as kernel parameters, followed by a need to reconstruct them in GPU code to retain flexibility. In this thesis, we identify several major problems during the porting process, including lack of vectors or views into a GPU buffer, bounds checking, iterator support, macro-dependent function specialization on the GPU, and GPU allocators for arbitrary types. These are all features that are already supported by CUDA in kernel code, but programmers are generally unable to use them due to data-structures decaying to pointers in kernel invocations. We demonstrate these problems and present techniques to overcome them in an implementation in C++ and CUDA. We use modern C++ features to make CPU-side features (such as iterators, ranged-for loops, and bounds checking) first-class citizens in GPU kernel code while maintaining interoperability with existing libraries. The result is a new ability to use CPU-style coding patterns in GPU kernel code. We demonstrate that our abstractions generate equally good assembly as the classical implementations. As a case study, we use the library to simplify the porting process of accelerating a shallow-water simulation framework "HEC-RAS" to the GPU.

#### ACKNOWLEDGMENTS

I am extremely grateful to have been guided by Professor John Owens through my Master's programme and through the work that went into this thesis. Thanks to Professor John Owens for his kindness, patience, feedback, and support. His expertise and knowledge were incredibly valuable, and I am truly grateful for his guidance and mentorship.

I would like to thank Dr. Serban D. Porumbescu for his guidance and mentorship that helped me navigate academic, professional, and personal matters. I am really grateful for the extremely insightful discussions we had on these topics. I learnt a lot from the technical discussions we had with Dr. Matthew Drescher which helped me broaden my skills. I am also extremely thankful for the kindness and support offered by all the members of my research group, and for sharing their knowledge and expertise. I am also extremely thankful to all the members of the research group for their kindness, support offered, and for sharing their knowledge and expertise.

I would like to thank Professor Jason Lowe-Power and Professor Julian Panetta for their guidance, support, and excellent feedback on my thesis.

I would also like to thank the Computer Science administrative staff, especially Jessica Stoller, Alyssa Bates, and Lorena Galvan for helping me navigate academic requirements and responsibilities.

I would like to thank my friends for their incredible support, advice, and encouragement through the years.

# Chapter 1 Introduction

Over the past few years, accelerators such as GPUs and ASICs have been developed to accelerate highly parallel workloads or specific applications such as matrix multiplication. These workloads have historically been implemented in C, C++, and Fortran and run on the CPU. Some parts of the data processing in these programs are parallel, and utilizing processors such as GPUs for those computations can provide a considerable gain in performance.

# **1.1 The Problem**

GPUs are highly parallel co-processors designed for parallel data processing. They are driven by the CPU (the host) and are programmed using tools provided by the hardware vendor. GPUs (the device) have thousands of cores, significantly more than a CPU, and have fast device-local memory separate from the CPU. The GPU scheduler parallelizes GPU programs (kernels) by executing the same program across all threads, whereas CPU programs must explicitly spawn threads. Due to these architectural differences, we cannot use host-specific data-structures and functions in kernels without modifications.

Hardware vendors provide tools, APIs, and constructs within the confines of the language (or an extension of it) to let the user move data and specify the execution spaces in which a function may be used. The compiler uses this information to generate appropriate code for the host and device. Applications running on the CPU can initiate work on the GPU by using these APIs. Since host-local data is inaccessible from the GPU (under most circumstances [41]), we must use these APIs to copy data. This can lead to code duplication when replicating data-structures across host and device, managing raw pointers, and manual copies to move data between execution spaces—all of which add to the maintenance cost of the application. Therefore, writing applications that target the GPU is not as straightforward as writing CPU programs under most circumstances due to the heterogeneity.

As a concrete example (which we further expand upon in chapter 3), when using CUDA with C++, users are often required to flatten their data-structures and have them decay to pointers or POD ("Plain Old Data") types that can be trivially copied to the GPU. As a consequence, standard C++ features such as iterators and range-based for-loops—which are, in fact, supported in host *and* device code by the compiler—cannot be used in device code. The fundamental problem is that we often have to reconstruct these higher-order types from the simplified or flattened-out types on the device to take advantage of these features.

All of these problems arise due to the existence of two different execution domains and their respective data spaces that are bridged minimally by the tools offered. This clear separation is in many ways an architectural decision by the manufacturer of the hardware that helps them establish a precise and well-defined programming and memory-model, which would otherwise be difficult and complicated to grasp if not for the "minimal bridge." This limits how expressive GPU programs can be. Our work focuses on improving the user experience when traversing this bridge between fundamentally different pieces of hardware. As a consequence of being driven by the CPU, we go through this "bridge" to interact with the GPU. This acts like a filter, limiting and guiding application architecture.

# **1.2 Prior work**

Hardware vendors such as AMD and NVIDIA expose their APIs through C or C++. Apple exposes its hardware through the Metal API but uses Objective-C. We refer to these officially released tools by hardware vendors as "native." HPC applications are written in C, C++, and Fortran ("native languages"), so it stands to reason that the major vendors expose their hardware through APIs in these languages. These APIs are usually verbose, which allows the vendor to simplify their implementation and ensure minimal overhead. While this offers maximum control of the hardware, it is not user-friendly. Various tools have been developed to abstract

common use cases and simplify writing kernels. We will now take a look at common approaches for building such tools. We then present our reasoning as to why these tools do not entirely address the problem we describe.

#### **1.2.1** Compilers

Programming APIs such as Vulkan, OpenGL, and DirectX allow the user to target the GPU, but programs (known as "shaders" in the computer graphics world) are written in a different language<sup>1</sup> (a domain-specific language—DSL) than the one used on the host. These shaders require separate compilation tools than the ones used for host code, and generally cannot be implemented in the same file as host code (the exception being the program is stored as string literal and is compiled at runtime). Compiler support is required to let the user implement shaders in the same language as the host implementation. For example, "Unified Shader Specialization" [46] taps into existing C++ features and adds custom attributes to the language by modifying the Clang compiler to express shader specialization, which is used to generate host and device code. CUDA takes a similar approach and extends the C++ language to support heterogeneous compilation from the same source file.

Similarly, for languages not supported by the hardware vendor, an approach is to implement a transpiler to the supported language (Hybridizer [1]) or a compiler (such as ILGPU [24] for C#, Rust-CUDA<sup>2</sup> for Rust) to generate GPU-native binaries. While in theory this allows them to accept any data-structure as an argument to a kernel, they generally accept only a limited subset offered by the language or the library itself (ArrayView in the case of ILGPU) to simplify the transformation. These supported structures are generally flat buffers, aggregates, or trivially-copyable value types. The compiler implementation limits the flexibility of this approach. A compiler cannot cover all possible use-cases. With adequate compiler support, we can implement libraries to overcome these limitations, which we discuss below.

<sup>&</sup>lt;sup>1</sup>GLSL and HLSL are the most common ones, used by OpenGL and DirectX respectively.

<sup>&</sup>lt;sup>2</sup>Rust-CUDA: https://github.com/Rust-GPU/Rust-CUDA

### 1.2.2 Libraries

Libraries such as oneAPI [21], SYCL,<sup>3</sup> and Thrust [4] allow the user to program the GPU in C++. They expose a set of highly optimized GPU routines that can be composed by the user to achieve the functionality they desire. If custom functionality is required, the user can pass a functor or a lambda function encapsulating the desired behavior to the library, which is parallelized and executed on the GPU. Essentially, these libraries approach the problem by hiding the complexity behind their own APIs. The user writes code that expresses their *intent* at a high level, and the library uses the most optimal implementation based on this information. While this offers customization and safety—goals we also claim to achieve, it does not necessarily offer *complete control* over both the GPU and CPU implementations. Thrust and stdgpu [47] address some of the issues we present (iterators and vectors in kernels). stdgpu also provides GPU counterparts for common CPU data-structures such as a stack, queue, vector, and maps; one can use them in both host and device code.

These libraries are indispensable when writing GPU-accelerated code. They address some of the issues we present, offer a large set of performant algorithms and data-structures that work on the host and device, and should be used where appropriate. We present additional techniques and tools that can be used alongside these libraries to provide similar flexibility to user-defined types and make them easily accessible in kernels. We focus on constructs that allow the user to control *both* the host and device implementations, and the structures that bridge them while staying within the confines of tools offered by hardware vendors. We do not aim to replace these libraries; quite the opposite—we aim to complement them by improving the experience of traversing the "bridge" we previously mentioned.

# 1.3 Approach

We use language features such as compile-time processing, type introspection, macros, allocators, inheritance, and iterators to build functions that can be used in both host and device code. This also allows us to build data-structures that work on both host and device code, overcoming code duplication problems. These data-structures allow us to avoid the fragile and repetitive

<sup>&</sup>lt;sup>3</sup>SYCL: https://www.khronos.org/sycl/. Strictly speaking, SYCL is both a library and a compiler solution.

"glue code" that typically exists solely to chauffeur data between host and device code.

# **1.4 Goals**

A primary goal of the techniques presented is to let users write GPU kernels with the same expressiveness and feature set as CPU implementations without sacrificing performance. We present abstractions and tools that can be utilized generally. We focus on users who intend to write kernels, and aim to simplify their kernel programming experience. As such, we focus on abstractions that allow users to utilize the same data-structures on the CPU and the GPU, with the expectation that the user is aware of any potential disadvantages of not using GPU-specific data-structures where appropriate.

We operate under the assumption that HPC applications spend a significant portion of their execution time and compute resources in tight loops that implement their algorithms. Therefore, we strive to ensure that the parts of our abstractions that implement tight loops generate optimal code.

The traditional approach to measuring the performance of a new tool or an algorithm is to run benchmarks with different datasets and compare the results against contemporary state-ofthe-art implementations. This approach does not offer insights into the overhead of the abstraction for all use-cases.

Our methodology will be to compare the machine code that is generated for device code with and without using our implementation. If the generated machine code for the section that implements the compute loop on device code is identical, we claim to have achieved our goal—minimal overhead. We do not compare host code generation as the techniques we present are already used by tools such as Thrust. Since we are interoperable with Thrust, it can be used for host code if desired.

To that extent, we bring safety-oriented constructs such as spans and vectors to the GPU. Additionally, we move runtime errors to compile-time ones where possible. We try to address the gaps in features left (intentionally or otherwise) by existing libraries. We intend to *complement* existing libraries, not replace them.

We are not interested in building a new compiler or modifying existing ones to achieve our

goals. We instead focus on taking advantage of features offered by the officially supported tools ("native tools and languages") to simplify kernel development.

# **1.5** Contributions

We identify problems one may face when porting CPU code to the GPU. In particular, we address issues such as:

- 1. Function specialization for GPU and CPU leading to difficulties with code reuse.

- 2. Macro guards polluting the code—they textually eliminate code segments and are not checked for syntactic validity.

- 3. Having to simplify and flatten CPU data-structures into pointers and their associated metadata (such as buffer size) before passing them to kernels.

- 4. Lack of convenience features such as iterators and range-based for loops on the GPU as a consequence of the previous issue.

- 5. Incorrect implementations of the "Grid-stride loop" [19] (see section 3.5) leading to incorrect computations or runtime errors.

- 6. Mixing up of host and device pointers, and their sizes when using them as kernel parameters.

- 7. Trying to dereference GPU-only memory from the CPU.

To address these problems, we present a set of abstractions and techniques that allow users to use features taken for granted in host code (such as iterators) in device code too. We present a library that implements these techniques to exemplify the ideas discussed using CUDA and C++. We then demonstrate how these techniques assisted us in porting a C#-based shallow-water simulation framework to the GPU while giving examples with and without using these abstractions.

# **1.6 Benefits**

These techniques allow one to write code that reads like CPU code, reducing cognitive load on the programmer. We demonstrate that our techniques enable a user to:

- 1. Use spans, iterators, ranged for-loops in device code.

- 2. Pass a structure by reference or as a pointer into kernels.

- Leverage the RAII (Resource Acquisition is Initialization) paradigm to enable automatic allocation and cleanup of GPU memory.

- 4. Benefit from bounds-checking in debug mode on both host and device.

- 5. Share code between GPU and CPU implementations without macros, enabling compile checks for all code paths.

- 6. Maintain interoperability with existing libraries such as Thrust.

These features improve the expressiveness, maintainability, and readability of code without sacrificing performance or functionality. Some of the benefits mentioned above are brought forth by libraries such as Thrust but leave some features to be desired (e.g., Thrust vectors cannot be used in kernels, and stdgpu is focused on offering common CPU data-structures on the GPU).

# 1.7 Outline

We begin with some background on GPUs and their programming-model in chapter 2. In chapter 3, we describe the techniques being proposed. To begin with, we explain how compile-time processing simplifies writing device code in section 3.1. This also ties in with concepts in C++ (described in section 3.2), which enable us to enforce proper API usage at compile-time. We then present a simplified allocator and custom new and delete operators in section 3.3, which can be reused to simplify the implementation of user abstractions. Using this abstraction, we present an example of a vector in section 3.4 over a collection of elements. The feature that sets this apart from existing implementations is that it can be used in both host and device code. We also demonstrate how iterators (section 3.5) can be added to improve user experience. Where appropriate, we show that our abstractions generate optimal code. In chapter 4, we demonstrate how our utilities helped us port a C# CPU codebase to the GPU and share a few examples on how it improves user experience.

# Chapter 2

# Background

In this chapter, we describe the GPU, how it differs from the CPU, and look at existing programming methods. We will then discuss CUDA, and give a high-level description of the problem.

# 2.1 The GPU

The GPU is designed with different goals in mind from that of a CPU—GPUs trade latency for throughput. High throughput is achieved through multiple cores, many more than typically found in CPUs. These cores are simpler compared to their CPU counterparts, which enable more of them to be packed together. These cores are connected to device local memory (separate from the CPU RAM) with wide buses to keep the bandwidth and throughput high. On a CPU, parallelism is explicit—a user is expected to create and launch threads explicitly to utilize the parallelism offered on the CPU, if any. CPU threads are independent units of execution, relatively expensive to create, and can implement logic completely separate from the main execution path of the program.

GPUs are SIMT machines (single instruction, multiple threads) [45]. Programs executed on the GPU are implicitly parallel, and the user writes a piece of code, typically known as a shader or a kernel, that is executed on all the cores at once. GPU threads are cheap to create and typically operate on a single element of the data. Each thread independently executes the kernel. The GPU assigns a unique identifier to each thread, which can be used to index into the elements buffer and process them in parallel. Consequently, thousands of threads execute at once on a GPU, processing items in parallel. Fundamentally, the GPU is a co-processor at heart and any programming-model designed for the GPU must interact with, be controlled from, and be coordinated by the CPU. Therefore, it must, as a part of its design, support a heterogeneous execution model.

In the following section, we describe the major programming models at a high-level in their order of appearance, and their limitations at a high-level.

# 2.2 Programming model

GPUs and other application-specific hardware are driven by a CPU. The fundamental goal of a programming-model that exposes co-processors to the CPU (and the user) is to support constructs that submit commands to it and move data between the CPU and the co-processor. The programming-model is supported through the tools, libraries and APIs provided by the hardware vendor. Three common ways to program such hardware are:

- 1. Domain specific languages (DSLs), such as GLSL and HLSL, with their own compilers that generate hardware-specific machine code,

- 2. Extension of an existing language (such as brcc which extends C, and CUDA which extends C++), or

- 3. Through compiler transformations (or a new compiler "backend") that generates hardwarespecific code from existing languages (such as OpenMP<sup>1</sup>).

#### 2.2.1 Shaders

Well known examples of DSLs are shaders, which are extensively used in computer graphics. In such scenarios, data-structures on the CPU cannot be used directly in shaders, as not only are the execution spaces different, their languages are too. As such, a user must replicate their data representations in shaders to match those on the CPU and call the appropriate API functions to inform the driver to "bind" them together. The advantage of this approach is that the compilers designed for such languages can be specifically designed and optimized for the hardware. They are also small enough to embed in the programs themselves, affording the user the ability to change and recompile shaders on the fly.

<sup>&</sup>lt;sup>1</sup>OpenMP: The OpenMP API specification for parallel programming—https://www.openmp.org/specifications

But this approach has a major disadvantage—there is no type checking for types that are used across the host and device domains. The user is responsible for ensuring that the data types in the shader program and the CPU program have identical binary representations; this is not validated by the compiler. Incorrect binding of resources on either the shader or host code leads to runtime errors or data corruption. Users are required to implement a lot of "boilerplate" code on the host before running a kernel—initialize the rendering API, check for support for shader features and enable them, set up "bindings" to expose resources to shaders, handle the render loop, and compile shaders either ahead of time or on-time (depending on available features). All of this boilerplate code makes it cumbersome to quickly iterate and test new approaches and techniques, not to mention the effort required to debug these programs and shaders. To simplify programming, earliest GPGPU approaches used a custom compiler that transformed the user's code into shaders and a host program that launched the shader and retrieved the results.

For example, Ian Buck et al. in "Brook for GPUs: Stream Computing on Graphics Hardware" [5] use a source-to-source compiler brcc that generates C++ code, which invokes the shaders (either in DirectX or OpenGL). These are just some of the disadvantages [44] of using shaders and a graphics API to essentially trick the programming-model into performing computations that—one can argue—are completely divorced from the goals of a graphics API (rendering images to a framebuffer). Techniques such as using depth testing to discard work or for efficient branches were employed to improve the performance of early GPGPU applications. A user should not have to deal with the intricacies of a graphics API and shading language to implement applications that just want to utilize the parallelism in the hardware.

These efforts eventually led to the development of CUDA—it addresses many of the problems that plagued GPGPU programming using shaders and a graphics API. We discuss the advantages and disadvantages at a high-level in the next section (subsection 2.2.2), with some examples in section 2.3.

#### 2.2.2 CUDA

CUDA was released by NVIDIA in 2007 [28] to expose the parallelism of the GPU much more readily to the programmer through a simpler programming-model [38]. It addresses many of the challenges of GPGPU programming, offering a single-source model that allows the user to

implement both host and device code in the same file, simple API calls to launch a kernel and wait for its completion, and next to no boilerplate code (as opposed to using a graphics API and shaders) to write an end-to-end saxpy application. CUDA is an API and programming-model that is an extension of the C++ language [32], allowing one to write CPU and GPU code in C and C++, within the same file—a *massive* simplification compared to the shader programming-model. While it is simpler by orders of magnitude to implement GPGPU applications in CUDA (when compared to using graphics APIs and shaders), it is still challenging to write a non-trivial application, which we address in section 2.3.

CUDA is primarily exposed as a C API and provides parallelization and synchronization primitives that expose the underlying hardware parallelism more readily to the programmer—fine-grained and coarse-grained parallelism constructs establish a clear hierarchy that makes it easy to reason about computations running in parallel. CUDA, being an extension of the C++ language, makes it easy to extend; new hardware and API features can just be exposed as part of the software stack.<sup>2</sup> This affords rapid evolution of the language and the programming-model, making it easy to extend and respond to the needs to the broader community. Since it is not based on a graphics API, it takes a simple API call to launch a kernel that is parallelized on the GPU. Host and device code can use the same data types without modifications under most circumstances—users no longer have to worry about ensuring that host and device data layouts are identical, without assistance from the compiler.

# 2.3 Problem

CUDA has addressed many of the challenges of using shaders for GPGPU programs, but programming in CUDA still presents a number of challenges, some of which we cover in this section to motivate the problem (with details in chapter 3). This thesis focuses on using the tools available in CUDA and C++ to simplify some of the common usage patterns and overcome their pitfalls—we are not interested in building a new tool (such as a new compiler), but wish to use existing language and API features to address these concerns.

CUDA is primarily exposed as a C API-all resources allocated must be explicitly managed

<sup>&</sup>lt;sup>2</sup>While this is possible with shaders, they require an extension mechanism which requires the user to check for and enable the feature in both host code and shader code.

and freed appropriately. This pattern of allocating, using, and freeing resources is repetitive and error prone and could lead to memory leaks and hard-to-diagnose out-of-bounds accesses, some of which may lead to security issues [8]. Even when using Thrust (Listing 2.1) or similar libraries, the abstractions do not carry over into kernel code.

For example, data-structures such as std::vector in C++ cannot be used in kernel code due to various restrictions (enforced by the compiler—functions not explicitly annotated as callable from device cannot be used in device code), in no small part due to the hardware differences and device-local memory heaps. The code, driver, and the runtime environment that exposes the hardware to the user cannot account for all possible use-cases to enable transparent usage of CPU-native data-structures in device code.

This style of writing kernels leads to raw pointers and their sizes being passed around within device code, which discards type-information. Therefore, abstractions that exist on the CPU and are taken for granted—collections (std::vector, std::span), allocators (std::allocator), and iterators—cannot be directly used on the GPU.

Consequently, CUDA kernel parameters take raw pointers and their associated sizes. For example, if a kernel operates on two memory regions of different sizes, it takes four parameters—two pointers, and size of the memory region for each of the respective pointers. This means that convenience features such as iterators and ranged for-loops are not available in kernel code.

In this thesis, we present ways to implement similar abstractions that can be used across CPU and GPU code. While we use C++ as the language of choice since it's officially supported by NVIDIA, similar constructs can be utilized in other programming languages that support equivalent constructs, such as Rust.

```

global void kernel(

Vertex* verts, int num verts,

2

Edge* edges, int num_edges) {

3

4

while (/* process vertices and edges */) {

5

process(verts[i]); // no bounds checking

6

7

}

8

// no iterator support

9

for(auto& vert : verts) {

10

}

11 }

12

```

```

13 thrust::device_vector<Vertex> verts {};

14 thrust::device_vector<Edge> edges {};

15

16 kernel<<<b, t>>>(

thrust::raw_pointer_cast(verts.data()),

17

verts.size(),

18

thrust::raw_pointer_cast(edges.data()),

19

edges.size());

20

21

22 void load_data(/**/) {

// Load data into a CPU buffer

23

std::vector<data> cpu_data {...};

24

thrust::device_vector<data> gpu_data {};

25

// Then meticulously copy it to the GPU buffer

26

27

. . .

28 }

29

_host____device___auto_func() {

30

#ifdef ___CUDA_ARCH_

31

#if __CUDA_ARCH__ >= 700

32

// ARCH-specific code

33

#endif

34

/* generic device logic */

35

#else

36

/* host logic */

37

38

#endif

39 }

```

Listing 2.1: Motivating examples: Macro pollution, lack of iterators in device code, and the inability to manipulate data in a thrust device\_vector from the host in a performant way.

Since CUDA is an extension of the C++ language, it supports most modern C++ features, even in kernel code. Despite this, a user cannot just pass in host data-structures into kernel code due to the aforementioned issues, leading to fewer opportunities where they can utilize all the features that C++ offers.

As a motivating example of the kinds of problems we seek to address, in Listing 2.1, the compiler does not warn us about swapped and incorrectly passed in parameters, if we swap the sizes. An equivalent C++ function would have accepted std::vector<T> as parameters for the respective types.

We bring forth and discuss more examples in chapter 3, where we present various sections that explain the problem and come up with ways to address the problem. In particular, we

• explain some modern C++ features that enable us to create a few building blocks that can be used in a generic fashion to improve CUDA programming.

- demonstrate how compile-time programming can be used to replace macros and simplify writing host and device-specific code (see Listing 2.1, line 30).

- present a way to allocate objects on device-local and managed-memory with the new keyword.

- show how a custom allocator backed by managed memory dramatically simplifies writing and loading data into GPU-native data-structures.

- demonstrate the need for owning and non-owning container types that can be used both on the host and in device code, and how it enables us to use iterators.

- explore coroutines and how they can be utilized to abstract concurrent kernel launches.

# 2.4 Prior work

There exist first-party (Thrust [4], libcu++ [29]) and third-party (cuda-api-wrappers [16]) libraries that simplify some of the resource management and also provide a set of highly optimized routines for common operations such as *reduce* and *scan*. But none of these libraries extend functionality into kernel code, i.e., when the user finally starts to write a CUDA kernel, all of the parameters decay into raw pointers and their associated sizes, and the kernel body drops down to C-like abstractions. For example, it is not possible to use a thrust::device\_vector in kernel parameters. Programming forums such as StackOverflow<sup>3</sup> cite examples that outline a simple implementation of a vector that can be used in device code.

Libraries such as Thrust and RAJA [3, 23] typically follow a functional programming style, where operations such as loops are written as either lambda functions or functors. When using lambda functions, local variables have to be either copied or passed as references.

Our work takes a different approach, as described in section 1.3 and section 1.4. In the following chapter, for each section, we address a specific problem, present a solution, and conclude with considerations that users must be aware of.

<sup>&</sup>lt;sup>3</sup>Stackoverflow: Using std::vector in device code: https://stackoverflow.com/a/45671310

# Chapter 3 Implementation

In this chapter, we will take a look at the specific techniques proposed, examples of their implementation, and their potential drawbacks. We first describe the technique and language feature being used to assist with finding the appropriate equivalent in other languages. We then describe the problem being addressed and proceed to give an example implementation in C++ to demonstrate its utility. Finally, we conclude with potential problems that one might face when using these approaches, and potential alternatives where possible. In all of the examples that follow, cup is used as the top-level namespace for the set of utilities we propose.

# 3.1 constexpr and consteval

Some programming languages (such as C++) provide the ability to evaluate the result of a function call or an expression at compile-time. This allows one to avoid the runtime overhead, provided such an expression can be computed at compile-time. We can tap into this machinery to specialize parts of a function's implementation based on the compilation context—introspect the types of function arguments and the compilation target (host or device), and specify specialized implementations. In this section, we will take a look at how C++ constexpr and consteval can be used to our advantage to simplify code specialization and improve code maintainability and readability, Listing 3.1 (a) vs. (b).

```

__host__ _

device

1 __host__

device

2 auto func(/**/) {

2 auto func() {

if constexpr ( cup::device_code() ) {

3 #if defined(__CUDA_ARCH__)

3

4

// GPU code

// GPU code

4

5

if constexpr ( cup::

5

# if __CUDA_ARCH_ > 860

// arch is compute_86 or newer, can use

compiling_architectures(500) ) {

6

// specialized code for compute_50

those features

6

7

7

#endif

8

}

8

// fallback to common features

9 # else

9

else {

// Host code

// CPU code

10

10

}

11

11 #endif

12 }

12 }

```

(a) if constexpr usage

(b) Using \_\_\_CUDA\_ARCH\_\_\_macros

Listing 3.1: Using if constexpr allows one to express the compile-time decisions using constructs that are similar to classical control-flow statements, improving readability.

# 3.1.1 Introduction

There are instances when we would like to use the same function (when writing libraries consumed by others, for example) across both host and device, but specialize the implementation a different codepath for host vs. device code—so that we take advantage of the hardware effectively. In other words, we want an abstracted function that does the right thing and takes advantage of the hardware transparently on behalf of the user. For example, both the GPU and CPU offer hardware-accelerated or highly-optimized math intrinsics for fused-multiply-add, trigonometric, and logarithmic functions. Utilizing these could dramatically speed up programs that are math-heavy in tight loops. A library author could then expose a single matrix-multiply routine that uses the GPU if possible, or falls back to a CPU implementation, making the API easy to use for the end user.

# 3.1.2 The problem

CUDA allows one to implement host and device code in the same source file. Since code generation for device is opt-in, it offers a way to inform the compiler of sections (of source code) where device code needs to be generated. In C++, the canonical way to achieve this is to check for the \_\_CUDA\_ARCH\_\_ macro [31] (Listing 3.1), or by using function decorators (\_\_host\_\_ and \_\_device\_\_). In GPU code, the \_\_CUDA\_ARCH\_\_ macro is set to the current virtual architecture being compiled for and can be used to take advantage of modern

CUDA hardware features. While this works, we claim that we can do better due to the various issues that macros present. Macros textually eliminate sections of source code in the preprocessor stage, meaning that the eliminated section is not checked for syntactical correctness by the compiler.

Essentially, we are making a decision at *compile-time*—whether a section of code is processed by the compiler machinery responsible for host or device code generation—to implement host and device-specific code-paths. C and C++ macros do not introduce variable scoping. If the user does not explicitly introduce a new scope, all the variables in func are within the same scope. Failure to implement the code common for all architectures, as shown in the example below (Listing 3.1, line 7), can lead to hard-to-diagnose errors during runtime.

```

1 auto func() {

#if defined(__CUDA_ARCH__)

2

// GPU code

3

# if __CUDA_ARCH_ > 860

4

// arch is compute_86 or newer, can use those features

5

6

#endif

7

// fallback to common features

# else

8

// CPU code

9

#endif

10

11 }

```

Listing 3.1: Macros do not introduce a variable scope and the compiler is unable to check the code for syntactic validity in the textually-eliminated branches.

We want to use C++ language constructs—if statements in place of macros—to detect device and host code. This approach leads to code that reads like the rest of the code and clearly expresses the intent of the programmer. Before we explain the usage of such constructs, we will explain the language features that make this possible in subsection 3.1.3, an overview of how the CUDA compiler processes source files in subsection 3.1.4, and finally, in subsection 3.1.5, we use this understanding to implement constructs demonstrated in Listing 3.1.

#### **3.1.3** Compile-time evaluation

constexpr and consteval are C++17 and C++20 features respectively that allow one to hint and require computations be performed at compile-time, respectively, rather than at runtime. To enable this feature on nvcc, use the command-line flag --expt-relaxed-

constexpr [34].

Since these computations can be performed at compile-time rather than at runtime, the compiler can evaluate the result of this expression during the compilation process and just store the computed value at each call-site.

```

1 template <typename T>

2 constexpr T square(T a) {

return a * a;

3

4 }

6 __global__ void kernel(float* f) {

\star f = square(2.8);

7

8 }

9

10 int main() {

auto res = square (3.14);

11

printf("Res: %.3f", res);

12

13 }

```

Listing 3.2: Calls to square are usually eliminated in release mode, as the results of the call are computed at compile-time.

In Listing 3.2, an optimizing compiler completely eliminates the call to square in both host and device code.

# **3.1.4** NVCC compilation path

Both host and device code may be present in the same file, yet the compiler has to generate different instructions for each of them. To achieve this, the CUDA compiler (nvcc) splits host and device code into temporary files (since the functions are decorated with <u>host</u>, <u>device</u>, <u>global</u> attributes), and inserts code to facilitate the copy of function-call parameters from host to device code—from CPU to GPU. During this code-splitting process [33], the compiler defines <u>CUDA\_ARCH</u> macro in device files but not in host files. This can be used to distinguish host and device compilation paths, as in Listing 3.1.

```

1 consteval bool device_code() {

2 #ifdef __CUDA_ARCH___

3 return true;

4 #else

5 return false;

6 #endif

7 }

```

Listing 3.3: consteval functions are *required* to be evaluated at compile-time. We can abstract the macros behind a helper function and use it instead.

### 3.1.5 Using constexpr

By wrapping this macro \_\_\_CUDA\_ARCH\_\_\_ into a utility function, we can clean up and replace most macro guards. This (Listing 3.3) allows one to use typical function-call syntax to write host and device-specific code. The advantage of this approach is that both branches are verified to be syntactically correct, since they are not eliminated by the preprocessor, leading to more robust code. This also introduces appropriate variable scoping, as opposed to variables being in the same scope when using macros.

An alternative approach is to explicitly define two different functions with the same name for host and device, but this feature is supported only on the clang compiler [6] (at the time of writing).

This idea can be extended further, using if constexpr to conditionally compile device code based on the architecture (Listing 3.4).

```

consteval bool compiling architectures(int arch) {

2

constexpr std::array archs { __CUDA_ARCH_LIST__ };

return std::find(archs.begin(), archs.end(), arch)

3

!= archs.end();

4

5 }

6

7 ___device_

8 auto func() {

// ...

9

if constexpr (compiling_architectures(500)) {

10

// code for compute_50 virtual architecture

11

12

}

13 }

```

Listing 3.4: We can check at compile-time if we are compiling for a specific architecture using standard C++ code that isn't polluted by macros.

An alternate approach is to template the functions on the architecture so that the right function is picked.

```

1 #ifdef CUDA ARCH

2 constexpr int DEVICE_ARCH { __CUDA_ARCH__ };

3 #else

4 constexpr int DEVICE_ARCH { 0 }; // host

5 #endif

7 template <int arch = DEVICE_ARCH>

& __device__

9 void func(); // define this to use as fallback

10

ii template <>

12 __device__

13 void func<860>() {

14

printf("Arch 860 specific code!\n");

15 }

16

17 __global__ void kernel(float* f) {

// default template parameter picks specialization for

18

// current architecture

19

20

func();

21 }

```

Listing 3.5: Template specialization can be used to implement architecture-specific code, and a generic fallback can be implemented in the first definition.

We claim that these approaches are robust because given a list of device architectures to compile for, if the user forgets to implement any architecture-specific specialization, the compilation will fail. In Listing 3.5, a specialization for compute\_60 has not been defined. When attempting to compile for that architecture, we get a linker error due to an unresolved external to a mangled name (for example, \_Z4funcILi600EEvv). To get a more user-friendly diagnostic, a static\_assert (example in Listing 3.6) dependent on the template parameter can be used as the body of func (Listing 3.5, line 9). To use a fallback (features supported on all devices), it is sufficient to define func in Listing 3.5, line 9.

```

i template <int arch = DEVICE_ARCH>

```

```

2 __device__

```

```

3 void func() {

4 static_assert(0 == arch, "Function not defined for this

architecture");

5 }

```

Listing 3.6: Unused template functions are not instantiated. Their body can contain a static\_assert to ensure architecture-specific code is always implemented.

Functions decorated with constexpr can be utilized in device code unmodified in most cases. For example, the ratio and chrono headers can be used unmodified in device code.

### **3.1.6** Problems with this approach

A potential disadvantage of this approach is that some device-only functions (such as math intrinsics) cannot be called in the device codepath, as they are syntactically invalid in the host codepath (Listing 3.7, line 4). A macro would textually eliminate these calls in the host codepath, but with the if constexpr approach, the compiler terminates compilation due to missing definitions. C++ allows the false branch of if constexpr to be discarded under certain conditions [13]. The usual workaround is to wrap these intrinsics behind functions (which internally use macros, limiting their scope), and use them instead in these code blocks.

```

n __host___device__

2 float fma_round_down1(float x, float y, float z) {

if constexpr (cup::device_code()) {

3

return ::__fmaf_rd(x, y, z);

4

5

}

else {

6

return x * y + z;

7

8

}

9 }

10

11

<u>_host__</u>device__

12 float fma_round_down2(float x, float y, float z) {

#ifdef __CUDA_ARCH___

13

return ::___fmaf_rd(x, y, z);

14

15

#else

16

return x * y + z;

17

#endif

18 }

19

20 // Error message from the compiler

21 main.cu: In function 'float fmamul_round_down1(float, float, float)':

22 main.cu:11:10: error: '::__fmaf_rd' has not been declared; did you

mean '___fmaf64x'?

11 |

return ::___fmaf_rd(x, y, z);

23

24

```

Listing 3.7: if constexpr does not work with intrinsics since they are syntactically invalid in host code.

Replacing instances of \_\_CUDA\_ARCH\_\_ macro with compile-time checks is not always viable, as some device functions textually exist in the files generated in codepath for host, and vice-versa. In instances where replacement with this approach doesn't work, one can try to diagnose the issue by asking the compiler not to delete the intermediate generated files with the --keep parameter and inspecting them.

#### 3.1.7 Summary

In this section, we

- described the disadvantages of using macros, and problems they cause;

- explored compiler features constexpr and consteval that let us make decisions at compile-time;

- described how this compiler machinery can be taken advantage of to replace most macrobased (e.g., \_\_\_CUDA\_ARCH\_\_\_) host and device code specialization;

- contrasted the advantages of our approach with classic macro-based implementations (code is easier to read and maintain); and

- laid out the shortcomings of our approach (we may not be able to completely replace macros), and potential workarounds.

# 3.2 concepts usage

The ability to inspect types and make decisions based on those types is a powerful feature, but a library author cannot know all the types a user may define, making it restrictive. Specifically, the library author can implement logic based on a closed set of types, and once distributed, the set cannot be expanded by the user. An alternative approach is to specify the *behaviors* of the types, rather than the types themselves. Specifying the behavior of a type or the properties allows one to operate on the behaviors offered by the types. For example, an integer is a type whose members can be ordered, whereas a type that represents complex numbers cannot.

By decoupling these behaviors from the types themselves, it is possible to implement decisionmaking on an open set of types. As such, a library author can specify that their implementation requires certain behaviors (say, *the members of the type can be ordered*) of the types passed in. The end user has to specify what behaviors their custom types affords. This allows any set of libraries and their types to interoperate. C++ 20 and above provide this through a language feature knows as concepts—a named set of requirements. Similar functionality is provided by Rust with the trait system.

#### 3.2.1 Introduction

C++20 introduces a new language feature called concepts. A concept is a way to specify restrictions and requirements that are checked at compile-time. For example, Listing 3.9 is an example of a concept that enforces that a type T must support hashing. Without concepts, the compiler prints the full traceback that is often multiple pages long, earning C++ quite a notoriety around templates and error messages. For example, Listing 3.8 generates a wall of error messages during compilation that must be parsed through; sifting through them requires some familiarity with C++ diagnostics to identify the root cause of the issue.

```

1 struct S {

2     int p;

3     bool operator==(const S&) const = default;

4 };

5

6 int main() {

7     std::unordered_map<S, int> maps {};

8 }

```

Listing 3.8: An example that generates a wall of error messages.

Listing 3.9: Concept to check if a type supports hash.

When an object that does not satisfy the hashable concept is passed as a parameter to func in Listing 3.9, the error message is much more descriptive and easily actionable. Apart from being more user-friendly, concepts also serve as an early-exit mechanism if a constraint is not satisfied [11].

#### 3.2.2 The problem

Issues such as,

- compile-time error messages that are often hard to read and take action against; and

- common and easy-to-repeat errors (e.g., passing host pointers to device function, double free, leaking memory) that cause either undefined behavior or runtime crashes

reduce the developer's productivity. Time spent diagnosing these issues is better spent optimizing and implementing the application.

Succinct but descriptive error messages by the compiler, and the ability to catch more errors at compile-time improves the efficiency of the user. This can dramatically improve user experience as it allows them to stay in the tight test-implement iteration loop. Runtime errors must be explicitly tested for with manual or automated tests. For example, one of the most common issues that users face when porting or writing new kernels is passing in host pointers into kernel code. This leads to crashes at runtime. Ideally, we want to be able to detect this at compile-time where possible. We also want to improve compiler diagnostics to overcome the issue described in Listing 3.8.

Concepts make it easier to identify and fix errors during compilation, and decouple behaviors from the types themselves, making it easier to use across libraries. This mechanism allows us to convert some runtime errors (or the corresponding checks) to compile-time ones, which we also explore in this section.

#### **3.2.3** Constraints for kernels

We can implement concepts that require kernel parameters and buffers to point to valid GPU memory, which prevents a user from launching a kernel with a buffer that points to CPU heap during compilation.<sup>1</sup> This implementation(e.g., Listing 3.11) requires that the allocators return typed pointers—for example, dptr<float> instead of float\*. This involves three steps:

- Create a discriminator (typically an enum) to identify the memory type (host, device, pinned, etc.)—Listing 3.10.

- Create a user-defined type templated on the type of the pointer (e.g., float, int) and the discriminator.

- Wrap the native allocator in a function that returns the native pointer wrapped in the type created in the previous step.

We demonstrate how this technique can be implemented in C++ to illustrate its utility.

```

1 enum class pointer_loc : uint8_t {

2    HOST,

3    DEVICE,

4    MANAGED,

5    // PINNED,

6    // other types

7 };

```

#### Listing 3.10: Discriminator using an enum

We can now tie these discriminators with the pointer types to create a new type that, in its type information, includes the kind of allocation. This is useful for compile-time decision-making. For example, we can use device\_ptr<float> in place of float \*—the latter does not have information on the *kind* of memory (host vs. device) it points to (Listings 3.11, 3.12). We can use this type information to implement rich decision-making at compile-time, and by implementing concepts that utilize this information, provide descriptive diagnostic messages (Listing 3.13).

```

1 template <typename T, pointer_loc T1 = pointer_loc::HOST>

2 struct pointer_t {

3    static constexpr pointer_loc type { T1 };

4    T* value { nullptr };

5

6    [[nodiscard]]

7    constexpr T* operator*() noexcept {

```

<sup>1</sup>The initial design by Dr. Ian Buck et al. in "Brook for GPUs: Stream Computing on Graphics Hardware" [5] exposes a way to use custom data types created from a superset of language-native primitives (such as float2 alongside float, but is still limited by what C and the shading language allowed). This approach is flexible and allows a user to construct arbitrary types. We extend this approach by retaining additional metadata—source of a memory allocation—by using the C++ type-system to afford additional type-safety at compile-time.

```

return value;

8

}

9

10

[[nodiscard]]

11

constexpr T& operator[](size_t pos) noexcept {

12

return value[pos];

13

}

14

15 };

16

17 static_assert(sizeof(pointer_t<float>) == sizeof(float*));

18 static_assert(sizeof(pointer_t<int>) == sizeof(int*));

```

Listing 3.11: A new template type pointer\_t that wraps the underlying pointer with a discriminator allows us to track the allocation type, which can be inspected later to implement custom routines.

Since this type info exists *only* at compile-time, this pointer-like type has zero runtime overhead—it is the same size as the underlying pointer it encapsulates. We can create handy aliases for commonly used types, such as host\_ptr<T> (Listing 3.12, line 5). We now implement a concept that inspects the types for the constraints we want. For example, for a pointer to be addressable from the device, it must be one of device-local or managed (amongst others, such as zero-copy, and mapped host-pinned), see Listing 3.12, line 11.

```

1 template <typename T>

2 using device_ptr = pointer_t<T, pointer_loc::DEVICE>;

4 template <typename T>

s using host_ptr = pointer_t<T, pointer_loc::HOST>;

7 template <typename T>

& using managed_ptr = pointer_t<T, pointer_loc::MANAGED>;

10 template <typename T>

n concept device_addressable_ptr = requires {

T::type;

12

T::type == pointer_loc::DEVICE || T::type == pointer_loc::MANAGED;

13

14 };

15

16 // using the concept

17 __global_

18 void kernel(device_addressable_ptr auto ptr) {

//

19

20 }

21

22 // alternate way to check for concept

23 template <typename T>

24 auto foo() {

```

Listing 3.12: Aliases and Concepts that use the discriminator to enforce the requirement that only device-accessible types are passed as kernel parameters.

If the constraint is not satisfied, the compiler gives us a descriptive error message (Listing 3.13). Not all compilers currently support all the features of concepts as a consequence of it being a fairly new feature, but one can expect support in their compiler of choice in future releases. We present our examples with the clang, compiler which supports concepts.

Listing 3.13: A user-friendly error message that points the user to the constraint that failed.

This approach moves a runtime error to a compile-time one, and clearly points the user to where and what the error is, making it more actionable. Concepts can also be used to ensure that kernels that call lambda functions pass in the correct parameters. This is especially useful for libraries such as Thrust that make use of functors and lambda functions to customize the functionality of their algorithms (Listing 3.14). Concepts can be used in conjunction with if constexpr to implement conditional checks in a more declarative way (Listing 3.12, line 25).

```

1 template<typename LambdaFunc, typename... Args>

2 requires std::invocable<LambdaFunc, Args...>

3 __global___ void launch(LambdaFunc func, Args... args) {

4     func(std::forward<Args>(args)...);

5 }

```

Listing 3.14: concepts paired with lambda functions can be used to ensure that the argument types are compatible.

#### **3.2.4** Problems with this approach

Concepts take template parameters as arguments. Therefore, all the disadvantages of using templates carry over. They must be defined and implemented in headers. There are workarounds, such as forwarding the parameters to the implementation, to get the best of both worlds modern compilers are exceptionally good at stripping away layers of abstractions. There may be an impact on compile times, but the "early-exit" mechanism, where the compiler terminates compilation as soon as the constraint is not satisfied, could help too—this depends on the application.

An alternate approach is to wrap kernel launches (just like the workaround above) and at runtime, check if the pointers point to valid GPU memory with cudaPointerGetAttributes when using the CUDA Unified Memory API. On some system configurations, it is legal to dereference memory allocated on the host (with malloc, for example) in device-code [41].

On such systems, this approach might nevertheless be useful as there is a performance impact when not using device-local memory—the memory is either "streamed" to the GPU incurring large latency, or may stall the kernel on startup as the memory pages are migrated to the GPU.

This approach requires that memory-allocation APIs and allocators return strongly-typed pointers that include additional type information (such as the heap location). Therefore, CUDA APIs cannot be used directly. One could argue that this approach isn't as flexible as initially claimed, as this implementation depends on a custom type (pointer with additional type information) we introduced—the claimed advantage of concepts. This is completely accurate. But first-party libraries (such as Thrust) are indispensable and used widely enough when writing most CUDA programs that such concepts can be built over its types without sacrificing cross-library portability. As we will demonstrate in section 3.3, a custom allocator that wraps CUDA APIs can be written that ties into this system, which can be integrated into tools that Thrust provides.

#### 3.2.5 Summary

In this section, we

- briefly explored what C++20 concepts are, and how they simplify existing C++ code;

- presented a problem—how do we ensure that the user passes pointers that are valid in device code at compile-time instead of trying to validate them at runtime;

- described why this is useful—it saves time and allows the user to quickly iterate and ensure correctness without having to run the app and deal with runtime crashes;

- combined concepts with constexpr, consteval, and templates to ensure correctness at compile-time, with legible and easy-to-read error messages; and

- laid out the shortcomings and challenges that one may face when implementing or using this approach—cross-library portability, compiler support, and having to reimplement some of the internals to support this feature.

# 3.3 Allocator

Applications typically have varying memory requirements at runtime, and acquire memory with system calls. Operating systems expose these APIs through system headers. While these APIs allow one to allocate memory, they do not necessarily help with managing it. Some languages allow one to specify allocation behavior. We can tap into this functionality to allocate objects on various heaps—on both host and device. Advanced allocation strategies (such as arena allocation and memory pools) can also be implemented within these allocators to tune application performance.

Strictly speaking, allocators are not *necessarily* a language feature, but a technique or an abstraction that utilizes language features (destructors and constructors in C++, for example) to simplify and assist with memory management. Their feature-set may differ across languages, but the underlying idea is the same—a tool to assist the user with memory management without the pitfalls that often accompany handling raw pointers and manual memory management.

#### **3.3.1** Introduction

C++ programmers typically follow a paradigm known as RAII (resource acquisition is initialization) [14] to manage memory allocations. RAII is a technique in which the initialization of a variable is not distinct from acquiring the resources it manages (as opposed to creating a variable and then populating it with resources to manage). Initialization and acquisition of resources happens at once, allowing for the destructor to clean those resources up when the variable falls out of scope.

In this section, we describe how similar functionality can be implemented over CUDA memory management APIs. We can combine this with the "typed pointers" described in the previous section to allow for succinct code (Listing 3.15, and Listing 3.16 vs. Listing 3.17) that is not littered with mallocs and their corresponding frees—which must be in the reverse order of the allocations when dealing with nested data-structures to prevent leaks. For example, std::unique\_ptr and std::vector are automatically cleaned up at the end of their scope. We want to use similar features and techniques to manage GPU memory, and improve interoperation with host code (e.g., a std::vector of integers backed by GPU-addressable memory). This could be ideal for porting legacy CPU-only applications to the GPU in steps.

In this section, we start by describing what allocators are, present a basic implementation of an allocator to understand the features it offers, and then we augment it with the features described in the previous section. We conclude with how they are useful to the user.

```

void load_data(const auto& file) {

// use device local memory (cudaMallocManaged)

2

std::vector<int, cup::managed_allocator<int>> gpu_ints {};

3

qpu_ints.reserve(...);

4

5

while(file.has_more_data()) {

6

// read data from file

7

8

// construct GPU-native data-structures directly in

// GPU memory instead of copying it over from the CPU

9

qpu ints.emplace back(data);

10

}

11

12

// process data

13

14

kernel<<<...>>>(gpu_ints.data(), gpu_ints.size(), ...);

15

// qpu ints deallocated at end of scope

16

17 }

```

Listing 3.15: What we want to achieve. The memory for the vector's elements is backed by GPU memory and is cleaned up automatically. This abstraction is much simpler to follow than using raw CUDA API calls.

#### **3.3.2** Allocators and containers

An allocator encapsulates strategies for access or addressing, allocation and deallocation, and construction and destruction of objects [9]. One of the template parameters of a C++ container is an allocator, which is used for allocating its members (for example, the items in a std::vector).

By following a set of guidelines, we can implement our own allocator and container to suit our needs [10]. In particular, an allocator must expose methods such as allocate and deallocate. We want to use similar features to manage GPU memory.

A container library is a generic collection of class templates and algorithms. Prominent examples of containers include std::vector and std::array [12]. Containers are not unique to C++. Other languages offer similar equivalents. A typical container exposes methods such as begin, end, and the indexing operator to access elements. They automatically handle resizing and reallocation, using an allocator to allocate and deallocate memory.

Libraries such as Thrust provide a set of primitives that the user can use to construct the functionality we demonstrate in this section. We add to it in that we use concepts (described in the previous section) to enhance and augment these constructs and features. Before we do so, we give an overview of how such abstractions work, to better understand the integration of user-implemented and language-provided machinery.

#### **3.3.3** The problem

CUDA applications primarily allocate memory on the GPU through a rich set of API functions, of which cudaMalloc, cudaMallocManaged, and cudaFree are the most common. Allocating memory for an object in CUDA follows a repetitive pattern that can be abstracted away into a function. Consider the example in Listing 3.16—a mesh data-structure must be copied onto the GPU. It is easy for the user to forget the factor sizeof (T).

Common errors that users run into include: forgetting to free memory and leaking it; calling free twice on the same pointer; dereferencing a null pointer or a pointer that is invalid on the GPU; and out-of-bounds access. We can wrap this allocation and deallocation into a type that automates this for the user, preventing a whole class of errors. Existing libraries such as Thrust offer such allocators. By combining them with the ideas demonstrated in the previous section,

we can improve their utility. Let us take a look at an example to motivate and describe the features we would like to have—automatic allocation and cleanup of GPU memory, restrict kernel parameters to pointers that are valid on the GPU, automatic utilization of optimal routines to copy memory between various heaps, and allocators that are compatible with the C++ container paradigm.

```

struct point {

double x;

2

double y;

3

4 };

5

6 struct mesh {

std::vector<point> edge_points;

7

std::vector<point> face_points;

9 };

10

n struct mesh_gpu {

point* edge_points;

12

point* face_points;

13

14 };

15

16 std::vector<mesh> meshes { ... };

17 mesh_gpu* d_mesh; // to store the device address

18

19 static_assert(sizeof(mesh) == sizeof(mesh_gpu));

20

21 CUDA_CHECK (cudaMallocManaged (

22

&d mesh,

sizeof(point) * mesh.size()));

23

24

25 // allocate pointers in d_mesh

26 CUDA_CHECK(cudaMallocManaged(

& (d_mesh->edge_points),

27

sizeof(point) * mesh.edge_points.size()));

28

29

30 CUDA_CHECK (cudaMallocManaged (

31

& (d_mesh->face_points),

sizeof(point) * mesh.edge_points.size()));

32

33

34 // copy data to the GPU

35 for (int mesh = 0; mesh < meshes.size(); ++mesh) {</pre>

for (int j = 0; j = meshes.face_points.size(); ++j) {

36

37

d_mesh[i]->face_points[j] = meshes[i].face_points[j];

38

}

// same for edge points

39

40 }

41

42 kernel<<<>>>(d_mesh->face_points, meshes.size());

```

Listing 3.16: Copying data from CPU to GPU—it is hard to figure out what is happening and check for correctness

The code in Listing 3.16 looks correct at first glance, but there are a few errors.

- Listing 3.16, line 23 should be sizeof (mesh\_gpu)

- Listing 3.16, line 32 should be mesh.face\_points.size()

- Listing 3.16, line 37 is correct, but cudaMemcpy is faster

- Listing 3.16, line 42 should be meshes.face\_points.size()

If a structure has many vectors, as in Listing 3.16, it is necessary to first allocate the root object, and then recursively allocate and copy the containing elements. Had the root object d\_mesh been allocated using cudaMalloc, this program would crash, as the pointer should not be dereferenced in host code. Consequently, all the assignments should be replaced with cudaMemcpy. Each time any new member is added to this structure, one should not forget to copy the appropriate elements to the GPU. This process is error-prone, distracts the user from implementing the core of the algorithm, and is sometimes hard to debug, especially when the memory is inaccessible from the host. One must remember to appropriately free these regions too, starting with the innermost object. Freeing just the root object leaks memory of all the contained objects. These problems can be avoided by abstracting all the allocation and deallocation behavior into an allocator, and ensuring that the types follow the RAII paradigm.

```

struct mesh {

std::vector<point> edge_points;

2

std::vector<point> face_points;

3

4 };

5

6 struct mesh_gpu {

cup::vector<point> edge_points;

7

cup::vector<point> face_points;

8

9

mesh_gpu& operator=(const mesh& cpu_mesh) {

10

11

// uses cudaMemcpy

edge_points = cpu_mesh.edge_points;

12

face_points = cpu_mesh.face_points;

13

// or some other implementation that optimizes

14

```

```

15  // memory layout for the GPU

16  }

17