### UC Riverside UC Riverside Electronic Theses and Dissertations

#### Title

Simulation for Reliability, Hardware Security, and Ising Computing in VLSI Chip Design

**Permalink** https://escholarship.org/uc/item/4pz0538r

**Author** Cook, Chase William

Publication Date 2019

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA RIVERSIDE

# Simulation for Reliability, Hardware Security, and Ising Computing in VLSI Chip $$\mathrm{Design}$$

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

by

Chase W. Cook

December 2019

Dissertation Committee:

Dr. Sheldon X.-D. Tan, Chairperson Dr. Daniel Wong Dr. Nael Abu-Ghazaleh

Copyright by Chase W. Cook 2019 The Dissertation of Chase W. Cook is approved:

Committee Chairperson

University of California, Riverside

#### Acknowledgments

This dissertation represents the culmination of work that would not have been possible if not for the support, mentorship, and collaboration from numerous individuals.

Firstly, I'd like to thank my PhD adviser, Dr. Sheldon Tan for making me the engineer and scholar that I am today and for giving me the opportunity to pursue this rigorous degree program in the first place. His years of experience and his immense wealth of technical and theoretical knowledge have been invaluable to my work and career.

I'd also like to thank my committee members, Dr. Daniel Wong and Dr. Nael Abu-Ghazaleh, both of whom inspired me during my early coursework and helped shaped my work that would follow.

I would like to also thank the members of the VLSI Systems and Computation Lab. Specifically, I'd like to thank Taeyoung Kim, Zeyu Sun, Hengyang Zhao, Shaoyi Peng, Han Zhou, Sheriff Sadiqbatcha, and Wentian Jin all for their collaboration and advice which has led to this work. Their fellowship has been invaluable and is greatly appreciated.

Additionally, I would have never pursued this degree if it were not for the following professors who pushed me to be more than I thought I could be: Dr. Hani Mehrpouyan, Dr. Alice Parker, and Dr. Shahnam Mirzaei.

Lastly, I want to thank my family, especially my wife Christina, my daughter Olivia, my parents Greg and Joleen, and my brother Clayton for their constant love and support. To my parents Greg and Joleen, for their unwavering love and support.

#### ABSTRACT OF THE DISSERTATION

Simulation for Reliability, Hardware Security, and Ising Computing in VLSI Chip Design

by

Chase W. Cook

Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, December 2019 Dr. Sheldon X.-D. Tan, Chairperson

The continued scaling of VLSI circuits has provided a wealth of opportunities and challenges to the VLSI circuit design area. Both these challenges and opportunities, however, require new simulation tools that can enable their solution or exploitation as classical methods typically dealt with problem domains with smaller scales or less complexity. In this dissertation, simulation methods are presented to address the emerging VLSI design topics of Electromigration induced aging and Ising computing and are then applied to the application areas of hardware security and graph partitioning respectively.

The Electromigration aging effect in VLSI circuits is a long-term reliability issue affecting current carrying metal wires leading to IR drop degradation. Typically, simple analytical equations can determine a wire's effective age or if it will be affected by the EM aging effect at all. However, these classical methods are overly conservative and can lead to over design or unnecessary design iterations. Furthermore, it is expected that the EM aging effect will become more severe in future Integrated Circuits (ICs) due to increasing current densities and the prevalence of polycrystaline copper atom structures seen at small wire dimensions. For this reason, more comprehensive simulation techniques that can efficiently simulate the EM effect with less conservative results can help mitigate over design and increase design margins while reducing design iterations.

The area of Hardware Security is becoming increasingly important as the chip supply chain becomes more globalized and the integrity of chips becomes more difficult to verify. Utilizing the accurate simulation techniques for EM, we can utilize this reliability effect to demonstrate how a reliability based attack could be perpetrated. Furthermore, we can utilize this aging effect as a defense mechanism to help us validate the integrity of an IC and detect counterfeit chips in the component supply chain market.

Ising computing is an emerging method of solving combinatorial optimization problems by simulating the interactions of so-called spin glasses and their interactions. Borrowing concepts from quantum computing, this methods mimics the quantum interaction between spin glasses in such a way that finding a ground state of these spin glass models leads to the solution of a particular problem. In this dissertation, effective methods of simulating the spin glass interactions using General Purpose Graphics Processing Units (GPGPUs) and finding their ground state are developed.

In addition to the GPU based Ising model simulations, important combinatorial problems can be mapped to the Ising model. In this dissertation the Ising solver is applied to graph partitioning which can be utilized in VLSI design and many other domains as well. Specifically, solvers for the max-cut problem and the balanced min-cut partitioning problem are developed.

# Contents

| $\mathbf{Li}$                                                     | List of Figures xi    |                                                                                   |                |

|-------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------|----------------|

| $\mathbf{Li}$                                                     | st of                 | Tables                                                                            | xiii           |

| 1                                                                 | $\operatorname{Intr}$ | oduction                                                                          | 1              |

|                                                                   | 1.1                   | Electromigration                                                                  | 1              |

|                                                                   | 1.2                   | Hardware Security                                                                 | 4              |

|                                                                   |                       | 1.2.1 Hardware Trojans                                                            | 5              |

|                                                                   |                       | 1.2.2 Counterfeit IC Detection                                                    | $\overline{7}$ |

|                                                                   | 1.3                   | Ising Computing and Graph Partitioning                                            | 8              |

|                                                                   | 1.4                   | Contributions                                                                     | 11             |

| <b>2</b>                                                          | Rev                   | iew of EM physics and stress modeling                                             | 13             |

| 3 Finite Difference Method for Simulating Electromigration in Mul |                       | te Difference Method for Simulating Electromigration in Multi-Branch              | L              |

|                                                                   | inte                  | rconnects                                                                         | 17             |

|                                                                   | 3.1                   | Void Volume Calculation                                                           | 18             |

|                                                                   | 3.2                   | Finite Difference Method for EM Analysis                                          | 18             |

|                                                                   | 3.3                   | Numerical result and discussions                                                  | 21             |

|                                                                   |                       | 3.3.1 Validation for single 2-terminal wire                                       | 22             |

|                                                                   |                       | 3.3.2 Validation for three wire T-shape intersection                              | 23             |

|                                                                   | 3.4                   | Summary                                                                           | 25             |

| <b>4</b>                                                          | Kry                   | lov Subspace Method for Fast Electromigration Simulation                          | 31             |

|                                                                   | 4.1                   | The linear time invariant ordinary differential equations for EM stress evolution | 32             |

|                                                                   |                       | 4.1.1 Steady-state analysis for nucleation phase                                  | 36             |

|                                                                   | 4.2                   | The proposed Krylov fast EM stress analysis                                       | 38             |

|                                                                   |                       | 4.2.1 Singularity mitigation for EM ODE matrices                                  | 38             |

|                                                                   |                       | 4.2.2 Fast Krylov subspace-based stress analysis                                  | 40             |

|                                                                   |                       | 4.2.3 EM simulation under time-varying temperature                                | 45             |

|                                                                   |                       | 4.2.4 Scaling schemes for numerical stability                                     | 47             |

|                                                                   | 4.3                   | Numerical results and discussions                                                 | 48             |

|          |               | $4.3.1 \\ 4.3.2$ |                                                                                                                                                 | $49 \\ 51$ |

|----------|---------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5        | Flo           | ctromia          | ration Based Hardware Trojans Design                                                                                                            | 58         |

| J        | 5.1           | -                |                                                                                                                                                 | <b>5</b> 9 |

|          | $5.1 \\ 5.2$  |                  |                                                                                                                                                 | 59<br>62   |

|          | 0.2           |                  | 8                                                                                                                                               |            |

|          |               | 5.2.1            | 0                                                                                                                                               | 64         |

|          |               |                  |                                                                                                                                                 | 65         |

|          | 5.3           |                  |                                                                                                                                                 | 69         |

|          |               |                  | 0 1 0                                                                                                                                           | 69         |

|          |               |                  |                                                                                                                                                 | 74         |

|          | 5.4           | Mitigat          | 1 0                                                                                                                                             | 76         |

|          |               | 5.4.1            | 1                                                                                                                                               | 76         |

|          |               | 5.4.2            | Burn-in testing                                                                                                                                 | 78         |

|          | 5.5           | Conclu           | sion $\ldots$                                                  | 80         |

| 6        | On-           | -Chip C          | counterfeit IC Detection Using Electromigration Aging Sensor                                                                                    | 81         |

|          | 6.1           | -                |                                                                                                                                                 | 82         |

|          | 6.2           |                  |                                                                                                                                                 | 84         |

|          |               | 6.2.1            |                                                                                                                                                 | 87         |

|          |               | 6.2.2            | 1 00                                                                                                                                            | 88         |

|          |               | 6.2.3            |                                                                                                                                                 | 89         |

|          |               | 6.2.4            |                                                                                                                                                 | 91         |

|          | 6.3           | -                | 1 0 0 0                                                                                                                                         | 95         |

|          | 0.0           | 1 valifor        |                                                                                                                                                 | 00         |

| <b>7</b> | $\mathbf{GP}$ |                  |                                                                                                                                                 | 99         |

|          | 7.1           | Review           | 0                                                                                                                                               | 00         |

|          | 7.2           | 0                |                                                                                                                                                 | 02         |

|          |               | 7.2.1            | Ising model overview                                                                                                                            | 02         |

|          |               | 7.2.2            | Annealing method for Ising model solution 1                                                                                                     | 06         |

|          | 7.3           | Ising m          | nodel for the max-cut problem                                                                                                                   | 09         |

|          | 7.4           | GPU I            | mplementation $\ldots \ldots 1$ | 11         |

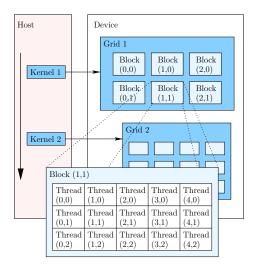

|          |               | 7.4.1            | GPU Architecture                                                                                                                                | 11         |

|          |               |                  |                                                                                                                                                 | 13         |

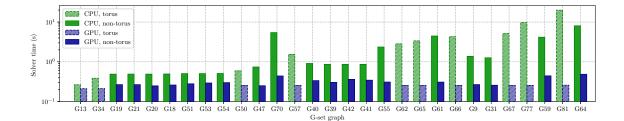

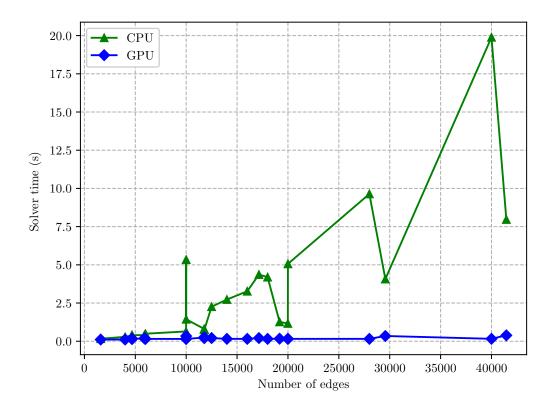

|          | 7.5           |                  |                                                                                                                                                 | 16         |

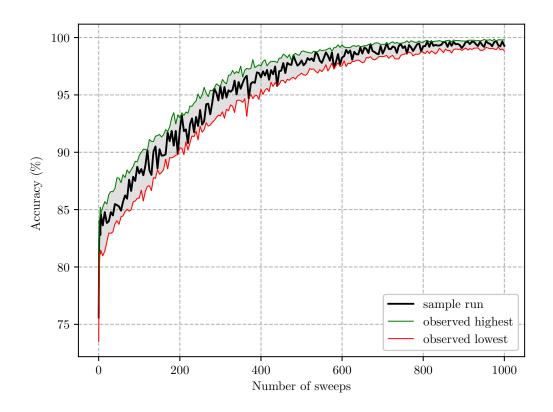

|          |               | 7.5.1            |                                                                                                                                                 | 17         |

|          |               |                  |                                                                                                                                                 | 20         |

|          | 7.6           |                  |                                                                                                                                                 | 20<br>29   |

|          | 1.0           | Summe            | ary                                                                                                                                             | 29         |

| 8        | $\mathbf{GP}$ | U-based          | d Ising Computing for Balanced Min-cut Bi-partitioning                                                                                          | 30         |

|          | 8.1           |                  |                                                                                                                                                 | 31         |

|          | 8.2           |                  | * 0                                                                                                                                             | 33         |

|          |               | 8.2.1            |                                                                                                                                                 | 33         |

|          |               | 8.2.2            | *                                                                                                                                               | 35         |

|          |               |                  |                                                                                                                                                 | 37 37      |

|          |               | 0.4.0            |                                                                                                                                                 | 01         |

|    | 8.3   | Experi | imental results and discussions | . 138 |

|----|-------|--------|---------------------------------|-------|

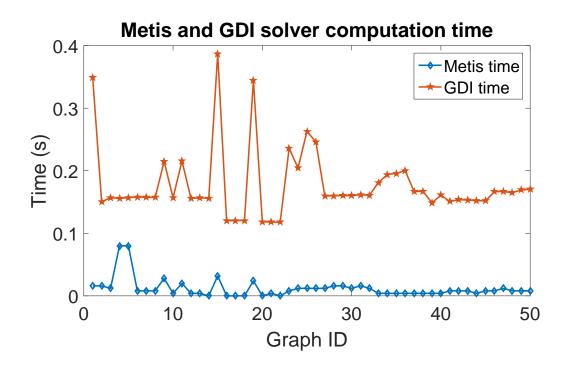

|    |       | 8.3.1  | Solution time study             | . 138 |

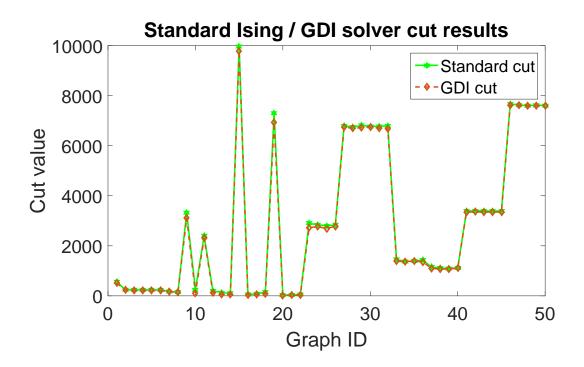

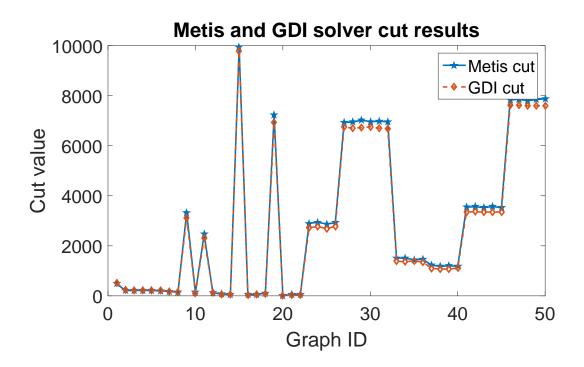

|    |       | 8.3.2  | Solution quality study          | . 142 |

|    | 8.4   | Summ   | ary                             | . 144 |

| 9  | Con   | clusio | n                               | 146   |

|    | 9.1   | Summ   | ary of Contributions            | . 146 |

|    |       | 9.1.1  | Reliability                     | . 146 |

|    |       | 9.1.2  | Hardware security               | . 147 |

|    |       | 9.1.3  | Ising computing                 | . 148 |

| Bi | bliog | raphy  |                                 | 149   |

# List of Figures

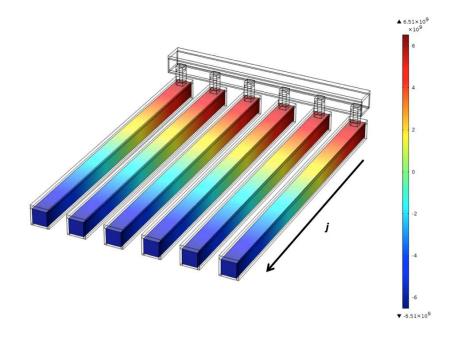

| 2.1  | Two-segment wire with steady-state EM induced stress                                                                                                          | 14       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2  | EM-stress evolution in the nucleation phase (a) and growth phase (b)                                                                                          | 16       |

| 3.1  | The testing interconnect structures: (a) 1-wire (b) 2 connected wires                                                                                         | 23       |

| 3.2  | EM-stress distribution change over time with $j = 5 \times 10^9 A/m^2$ in single                                                                              |          |

|      | 2-terminal wire for void growth                                                                                                                               | 24       |

| 3.3  | EM-stress distribution change over time with $j = 5 \times 10^9 A/m^2$ in single                                                                              |          |

|      | 2-terminal wire for void growth                                                                                                                               | 25       |

| 3.4  | T-shape nucleation phase for horizontal wire                                                                                                                  | 26       |

| 3.5  | T-shape nucleation phase for vertical wire                                                                                                                    | 27       |

| 3.6  | T-shape growth phase for horizontal wire                                                                                                                      | 28       |

| 3.7  | T-shape growth phase for vertical wire.                                                                                                                       | 29       |

| 3.8  | Growth of void volume over time $(t=1E7)$                                                                                                                     | 30       |

| 4.1  | Discretization of the two-segment wire with length L, and segment lengths $\frac{L}{2}$ .                                                                     | 32       |

| 4.2  | A two-terminal wire with the electron flow indicated by the arrow                                                                                             | 36       |

| 4.3  | Example piecewise constant current density $\mathbf{j}$ input as a function of time $t$ .                                                                     | 41       |

| 4.4  | Cathode stress over time for multiple wire temperatures                                                                                                       | 46       |

| 4.5  | Nucleation stage validation for two wire segments. <i>FastEM</i> solved using $q = 7$                                                                         | -        |

| 1.0  | with $0.0155\%$ average error.                                                                                                                                | 50       |

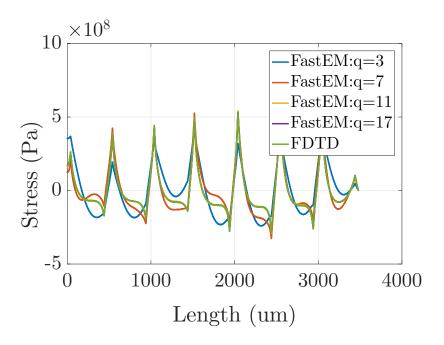

| 4.6  | Growth stage validation for two wire segments. FastEM solved using $q = 7$ with 0.0123% average error.                                                        | 51       |

| 4.7  | Cathode stress comparison under piecewise constant current density input.                                                                                     | 51       |

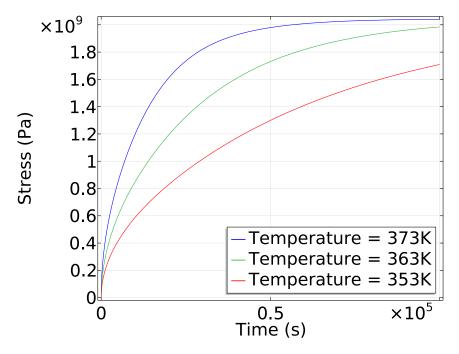

| 4.8  | Cathode stress comparison under precewise constant current density input.<br>Cathode stress under varying temperature $T = 360K$ , $370K$ , $365K$ , $390K$ . | 53       |

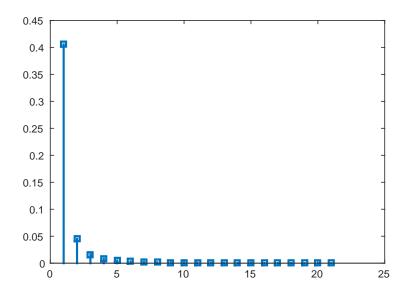

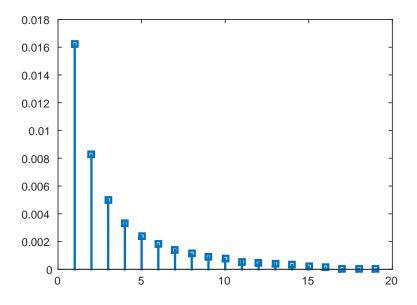

| 4.9  | Eigenvalue plot showing all eigenvalues                                                                                                                       | 55<br>54 |

| 4.10 | Eigenvalue plot showing an eigenvalues.                                                                                                                       | 55       |

| 4.11 |                                                                                                                                                               | 00       |

| 4.11 | computed poles                                                                                                                                                | 57       |

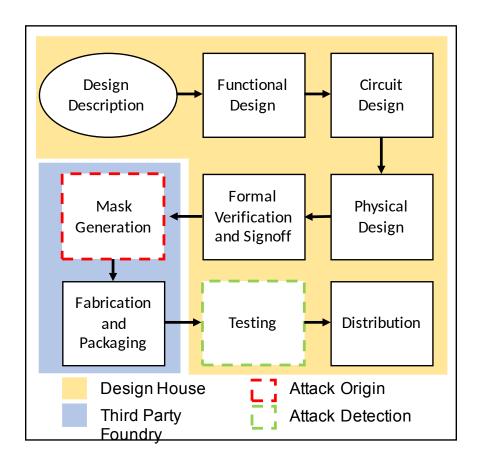

| 5.1  | IC design and manufacturing flow showing attack and detection opportunities                                                                                   | 63       |

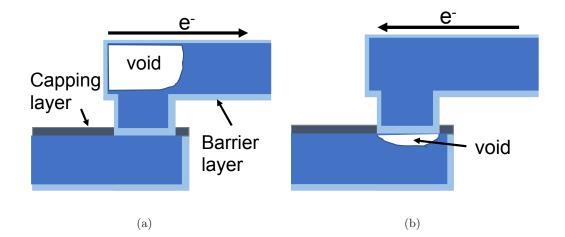

| 5.2  | Via-below (a) and Via-above (b) wire structures showing void formation lo-                                                                                    |          |

|      | cations                                                                                                                                                       | 66       |

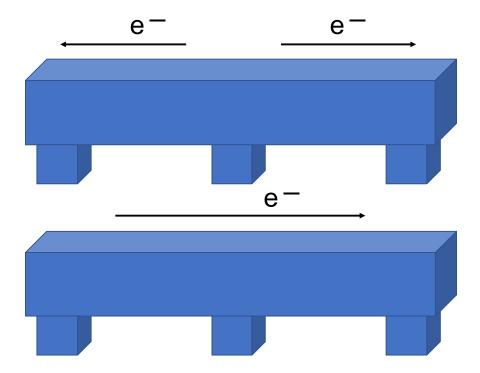

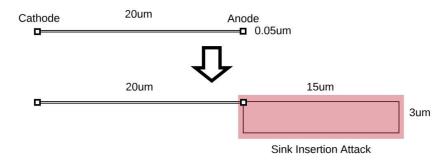

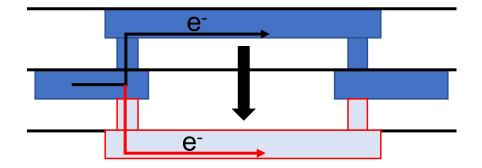

| 5.3          | A two segment wire structure with the same current density (below) and                                    | 07           |

|--------------|-----------------------------------------------------------------------------------------------------------|--------------|

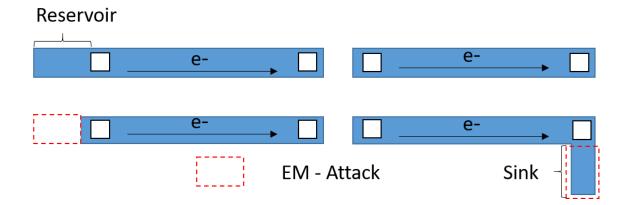

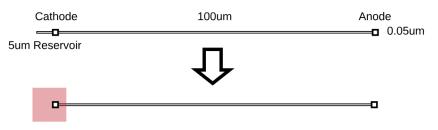

| E 4          | different current densities (above)                                                                       | 67<br>70     |

| $5.4 \\ 5.5$ | Illustrations of the reservoir reduction and sink insertion attacks An example reservoir reduction attack | 70<br>71     |

| 5.6          | An example reservon reduction attack                                                                      | $71 \\ 72$   |

| $5.0 \\ 5.7$ | The originally up-stream wire is moved to a lower level of metalization to                                | 12           |

|              | put it in the down-stream configuration in the layer demotion attack                                      | 73           |

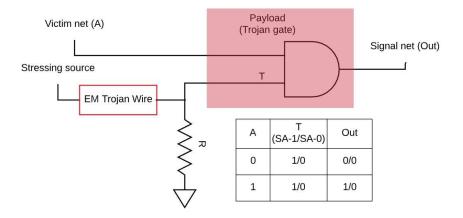

| 5.8          | Example circuit of an EM Trojan wire being used as a trigger for a Trojan                                 |              |

| -            | gate payload                                                                                              | 75           |

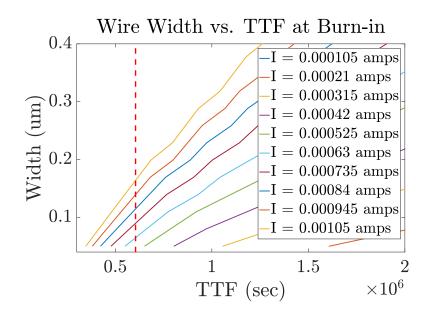

| 5.9          | Burn-in testing reduces the range of failure times available to an attacker by                            | -            |

|              | inducing failure in aggressive TTF targets                                                                | 79           |

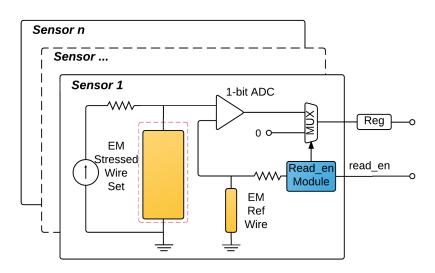

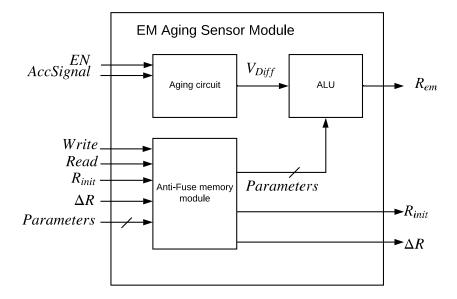

| 6.1          | The existing EM-based aging sensor design [37, 38]                                                        | 85           |

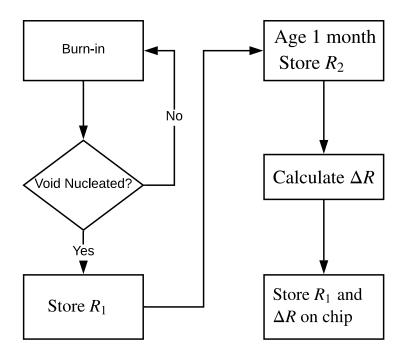

| 6.2          | The EM aging sensor self calibration methodology                                                          | 87           |

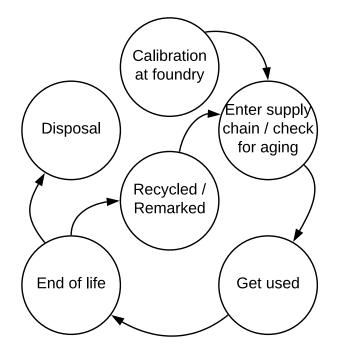

| 6.3          | The IC supply chain life cycle depicting the pre-distribution self calibration                            |              |

|              | stage, potential counterfeiting, and authentication during the IC distribution.                           | 88           |

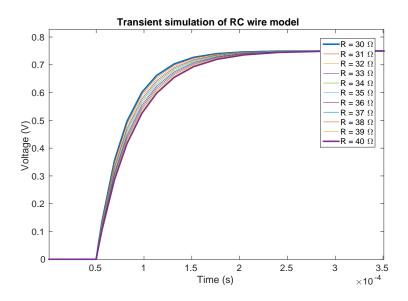

| 6.4          | Transient SPICE simulation of the RC model while sweeping the resistance                                  |              |

|              | value showing the gradual degradation of rise time, and thus signal delay $\ .$                           | 90           |

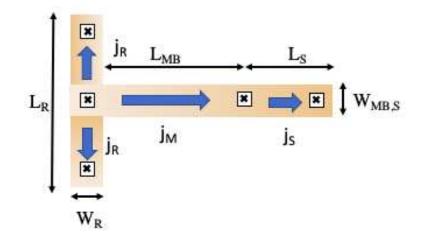

| 6.5          | The proposed hybrid multi-segment wire structure design                                                   | 91           |

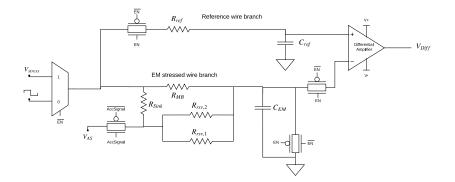

| 6.6          | The EM induced delay-based aging sensor architecture                                                      | 93           |

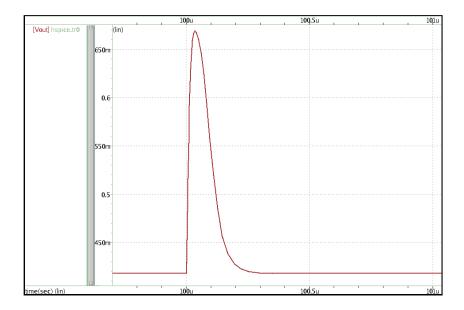

| 6.7          | SPICE simulation of the differential amplifier showing the detection of the                               |              |

|              | delay degradation caused by increased resistance in an EM failed wire $\ . \ .$                           | 93           |

| 6.8          | The proposed EM induced delay-based aging sensor architecture                                             | 94           |

| 7.1          | The 2D nearest neighbor Ising model.                                                                      | 103          |

| 7.2          | An example of a generally connected Ising model                                                           | 105          |

| 7.3          | Depiction of the local minima and global minimum in the energy minimiza-                                  | 100          |

|              | tion problem.                                                                                             | 107          |

| 7.4          | The Nvidia CUDA programming model showing the Host (CPU) and Device                                       |              |

|              | (GPU) and the relation between threads, blocks, and grid s                                                | 112          |

| 7.5          | Convergence region of the GPU-based annealing for the Ising model on the                                  |              |

|              | G-set G47 problem.                                                                                        | 120          |

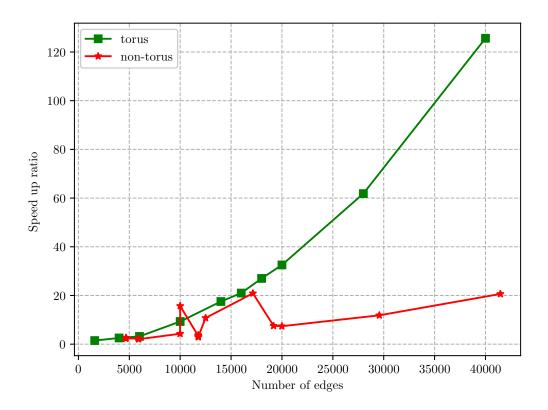

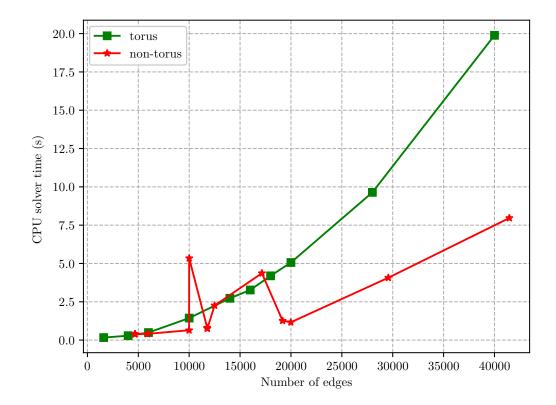

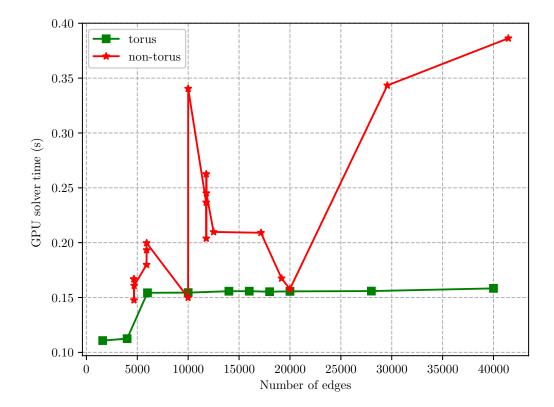

| 7.6          | Speedup results of the GPU against the CPU for the G-set benchmark problems                               | 121          |

| 7.7          | Graphic of the performance in seconds of the GPU and CPU for increasingly                                 |              |

|              | large graphs.                                                                                             | 124          |

| 7.8          | The performance results for the GPU against the CPU, separated by the                                     |              |

|              | graph type, torus and non-torus.                                                                          | 125          |

| 7.9          | CPU performance comparing torus and non-torus graphs                                                      | 127          |

| 7.10         | GPU performance comparing torus and non-torus graphs                                                      | 128          |

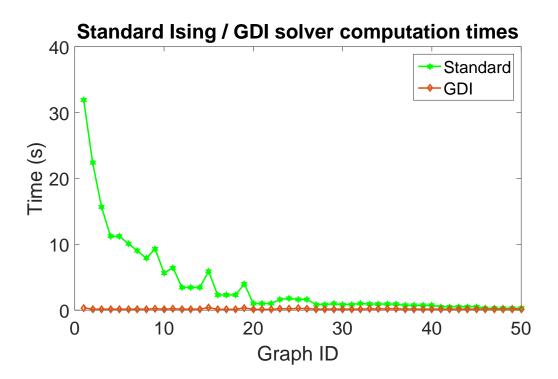

| 8.1          | Performance gains of the GDI solver min-cut algorithm.                                                    | 140          |

| 8.2          | Performance comparison of the GDI GPU Ising solver and METIS                                              | 140          |

| 8.3          | Solution quality of the proposed GPU-based Ising solvers                                                  | $141 \\ 142$ |

| 8.4          | Cut quality results for the G-set benchmark problems                                                      | 143          |

# List of Tables

| 3.1 | Notations and typical value in our transient simulation                                                                                   | 22  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | Single-threaded performance comparison between FDTD and <i>FastEM</i> on in-<br>terconnect trees from the IBM power grid benchmark ibmpg2 | 53  |

| 4.2 | Multi-threaded performance comparison between FDTD and FastEM on in-                                                                      |     |

| 19  | terconnect trees from the IBM power grid benchmark ibmpg2                                                                                 | 54  |

| 4.3 | Scalability performance results comparing FDTD and <i>FastEM</i> using increasingly large n-segment trees.                                | 56  |

| 6.1 | The designed hybrid wire sensor parameters                                                                                                | 96  |

| 6.2 | Acceleration operating conditions of designed wire                                                                                        | 97  |

| 6.3 | Comparison with the EM-sensor in [38]                                                                                                     | 98  |

| 7.1 | Accuracy comparison of the GPU max-cut value against the best known cut values for the G-set benchmark.                                   | 118 |

| 7.2 | Accuracy comparison of the GPU max-cut value against the cut values ob-                                                                   | 110 |

| 7.3 | tained by CPLEX                                                                                                                           | 118 |

|     | for the G-set benchmark (G prefix) problems and large custom problems (C prefix)                                                          | 122 |

| 8.1 | Summary of results for the standard (std.) and Globally decoupled (GDI)                                                                   |     |

|     | Ising solver compared with the METIS results. Graphs with less than 1000 nodes are omitted                                                | 139 |

## Chapter 1

## Introduction

This dissertation focuses on the effecient and practical simulation of physical phenomenon in ICs and applies these simulations to practical problem domains. Specifically, simulation of the Electromigration aging effect is firstly explored and then applied to the area of Hardware Security. The dissertation then explores the simulation of Ising Spin glasses as a method of solving combinatorial optimization problems. An introduction to each of these subjects is presented in the following.

#### 1.1 Electromigration

Electromigration (EM) is the primary long term aging effect in Integrated Circuits (IC) affecting the metal interconnects subjected to electrical current. It has been estimated that the EM induced lifetime of interconnects will be halved for each new generation of process technology node [44]. This is due to the increasing current density and also because the metal deposition process of copper dual damascene interconnects at small scales leads to polycrystalline grain structures which are more susceptible to EM failure. As a long term aging effect, electromigration affects the expected lifetime of an IC and must be considered during reliability sign-off.

The electromigration effect comes from the momentum transfer between electrons colliding with the metal atoms in a confined metal wire [14,51]. In a perfectly uniform atomic lattice the number of collisions is minimal, however; in the presence of discontinuities in this lattice, which is the scenario involving polycrystalline grain structures described previously, the collisions are more frequent leading to more momentum transfer resulting in stress generation in the wire. Typically, this stress will remain in an equilibrium state, with tensile stress in the cathode of a wire and compressive stress in the anode of the wire. However, if the stress reaches a critical level, the atoms in the cathode of the wire can defuse and end up deposited at the anode. This metal migration can then cause the resistance of the wire to increase as a void forms in the cathode of the wire which decreases the volume of the conducting metal volume and ultimately may even force electrons to conduct through the highly resistive liner of the metal wire.

Traditionally, semi-empirical analytical methods are used to predict a wire's susceptibility to EM. Primarily, Blacks equation [14] is used to estimate a wire's Mean Time To Failure (MTTF) as shown below in (1.1).

$$MTTF = Aj^{-n}exp\{E_a/k_BT\}$$

(1.1)

In this equation, j is the current density,  $k_B$  is the Boltzmann constant; T is the absolute temperature,  $E_a$  is the EM activation energy, A is a process dependent constant. A

is typically determined from a variety of parameters such as the metal grain structure, wire geometry, wire test conditions and others. The current density exponent n is also dependent on a number of parameters but primarily is material dependent. However, it has been found to be a variable parameter that heavily depends on the stressing conditions and is overly conservative which leads to over design and between 2X and 3X larger guard-bands than necessary [9]. This comes from the fact that parameters such as n are highly dependent on the stressing conditions and EM testing, which is used to determine these parameters, is done at high stressing conditions and then extrapolated to normal use conditions. In addition to resulting in over design, certain applications require accurate Time To Failure estimations, in which these traditional methods are not adequate.

To mitigate these issues, Physics-based models have been proposed which more accurately describe the EM effect and its subsequent failure mechanics. A good summary of these models can be found in [28]. The primary models in use are the stress-based Korhonen equation [51] and the metal atom vacancy concentration based model by Clement [25]. In this work the stress based Korhonen model is used. However, it should be noted that these models are actually the same and can both be used to derive each other but the stress based method is more intuitive for conceptualization of the EM mechanics.

The Korhonen model has been extended in [72] to describe a two phased failure process consisting of a nucleation phase and a growth phase. In the nucleation phase stress is generated in the wire until the wire reaches a critical tensile stress level which causes atoms to migrate. Once atoms begin to migrate, the second phase known as the growth phase starts and describes the growing void volume due to atom depletion [72]. Efficiently solving this physics model can generate less conservative EM assessments leading to less over-design and less design iterations. Furthermore, specific applications that require high accuracy EM simulation can benefit greatly. This manuscript presents a numerical solution technique for the EM-induced stress dynamics PDE for both the void nucleation and void growth phases in multi-branch interconnects. Additionally, a model reduction technique is employed to vastly accelerate simulation time while also considering time-varying temperature and current densities.

#### 1.2 Hardware Security

The integrated circuit (IC) supply chain has become increasingly globalized giving semiconductor companies unprecedented access to over-seas markets. A consequence of this proliferation is that it is becoming increasingly difficult to validate the integrity of the component supply chain [81] giving rise to illicit markets that deal in counterfeit ICs or even the malicious alteration or otherwise unsanctioned uses of electronics components.

The counterfeiting of ICs pose significant financial and security risks. The International Chamber of Commerce estimated losses due to counterfeiting and IP theft for G20 nations to be as high as \$1.7 trillion in 2015 [20]. Furthermore, the illicit market discourages innovation as companies become more weary of disclosing technologies with the public. The concern over counterfeit ICs in these critical application areas was validated when the U.S. military discovered counterfeit ICs in several defense systems [85] which highlights the need to develop countermeasures. Furthermore, the risk of malicious attacks from so-called hardware Trojans is an increasing concern. Often it is the case that IC design companies utilize 3rd party foundries to fabricate their ICs. Many of these dedicated foundries are over-seas and out of reach for domestic regulatory oversight and are difficult for their clients to directly monitor the manufacturing process. Because of this, the potential for bad actors at these 3rd party foundries to maliciously alter a device to create a hardware Trojan exists.

The security concern over both counterfeit ICs and hardware Trojans, primarily for critical applications (e.g. aerospace, defense, utility, and medical) has resulted in numerous calls for research from government agencies such as the IARPA TIC program [4], and the DARPA TRUST [3] and IRIS [2] programs. To combat these threats, developing novel methods of attack and defense are required to build an effective defensive toolbox for IC designers. The work in this dissertation builds upon the modeling and simulation methods developed for EM and applies these tools to create novel contribution in the space of hardware security.

#### 1.2.1 Hardware Trojans

Hardware Trojans are malicious alterations or additions to an IC. They may be implemented at a foundry without the original IC designer's knowledge. The scope of these malicious alterations can vary and may be as small as a single gate or may contain more complex logic modules. Hardware Trojans typically have two main components, a trigger and a payload [79,88]. The Trojan trigger activates the Trojan so it can carryout the task it was designed for. Trojan Triggers may be activated by a certain bit pattern in the IC's logic, they may use external sensors to utilize temperature or other environmental effects, or they may even be timer based. The Trojan payload is the part of the Trojan that actually performs the attack. The attack can be as simple as disabling a logic gate or may be as complicated as to leak sensitive information to the outside world.

One method of attack, reliability-based Trojans, utilizes the semiconductor aging effects to carry out an attack [69,71,83]. Attacks utilizing reliability effects may attempt to accelerate IC aging so as to cause premature failure of the victim chip. Primarily, reliabilitybased attacks utilize device reliability effects such as Bias Temperature Instability (BTI) and Hot Carrier Injection (HCI). However, on a couple attacks have been proposed that utilize long term interconnect aging [69,71]. These works propose both EM and Time-Dependent Dielectric-Breakdown (TDDB) type attacks but they only rely on current density based methods and semi-empirical aging models, such as Black's equation, which are meant for conservative reliability sign-off and are not suitable for Trojan designs.

Reliability-based Trojan attacks have a tremendous advantage over classical Trojans, that rely on sensors and logic, as they are more difficult to activate. The most commonly proposed methods of detecting hardware Trojans involves functional testing designed to trigger the Trojan during testing and allowing the observation of the attack and may also measure chip parameters such as temperature and power [79,88]. However, if a Trojan utilizes reliability effects, it can be difficult to produce the conditions required to cause the activation of such a Trojan. In this dissertation, the EM effect and the simulations methods presented are utilized to conceptualize and design EM-based hardware Trojans that can be utilized as a trigger, payload, or combination of both. Advanced EM failure dynamics are also considered which allow for finer control of the failure process.

#### 1.2.2 Counterfeit IC Detection

Counterfeit ICs represent the portion of the illicit IC market that sales ICs that do not conform to the original design specification, are old ICs that are sold as new, or are remarked to misrepresent the IC as something it is not. It often is the case that counterfeit ICs are combinations of these attributes, e.g., an old used IC remarked as a new IC with enhanced features that the actual IC does not have [7, 34]. Counterfeit ICs represent a significant financial and security threat.

The typical method of detecting a counterfeit IC involves visually inspecting a batch of electronics components [85]. More advanced visual inspection methods have been proposed such as the work in [33] that relies on thermal imaging in conjunction with statistics to increase the efficiency of visual inspection. However, these are time consuming processes requiring special expertise and are not always reliable [85]. For this reason, onchip aging sensors have been proposed to combat counterfeit ICs [80]. Early aging sensors used counters but these are vulnerable to attack. This led to the development of sensors based on the semiconductor aging effects. The first proposed aging sensor used transistor aging in a ring oscillator which, as it aged, would have frequency variations which could use be used to indicate a used IC. However, these methods can only detect short lifetimes, on the order of weeks, making false positives due to testing during manufacturing possible. To measure long term aging, EM-based aging sensors were proposed [37,38]. Unlike the BTI effect, EM is a long term aging aging effect which makes it ideal for measure age in units of years rather than weeks. The initially proposed EM-based aging sensors had the draw back of being highly area inefficient, requiring a large number of long redundant wires and multiple modules for detecting multiple ages.

The work presented in this manuscript shows a novel self-calibrating EM-based aging sensor that vastly improves upon the previously proposed aging sensors by removing the need for redundant wires and also for multiple sensors to measure larger ranges of ages.

#### **1.3** Ising Computing and Graph Partitioning

There are many hard combinatorial optimization problems such as max-flow, maxcut, graph partitioning, satisfiability, and tree based problems, which are important for many scientific and engineering applications. With respect to VLSI design automation, these problems translate to finding optimal solutions for cell placement, wire routing, logic minimization, via minimization, and many others. The vast complexity of modern integrated circuits (ICs), some having millions or even billions of integrated devices, means that these problems are almost always computationally intractable and require heuristic and analytical methods to find approximate solutions. It is well-known that traditional von Neumann based computing can not deterministically find polynomial time solutions to these hard problems [67].

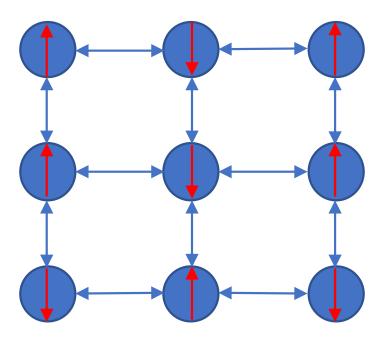

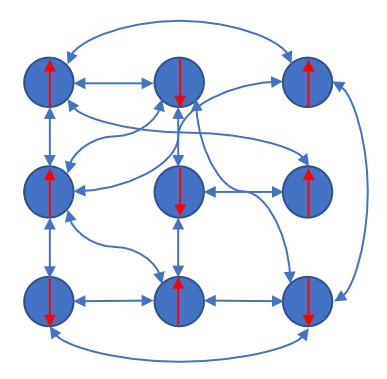

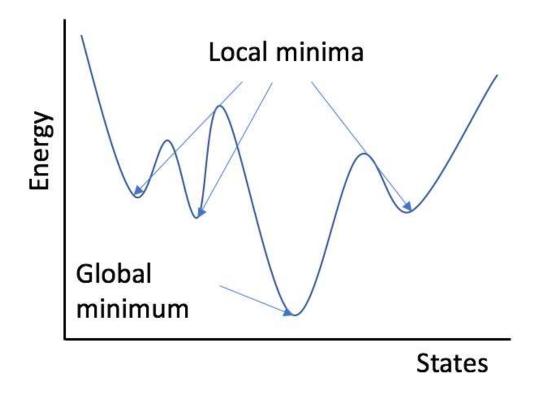

To mitigate this problem, a new computing paradigm utilizing the *Ising spin glass* model or *Ising model* has been proposed [61]. The Ising model is a mathematical model describing interactions between magnetic spins in a 2D lattice [59]. The model consists of *spins*, each taking one of two values  $\{+1,-1\}$  (to represent up and down states of a spin along a preferred axis) and are generally arranged in a 2D lattice. The spin's value is determined so that its energy is minimized based on interactions with its neighbor spins. Such local spin updates will lead to the ground state (globally lowest energy configuration) of the Ising model. It was shown that many computationally intractable problems (such as those in class NP complete or NP hard) can be converted into Ising models [56]. Some natural processes, such as quantum annealing process, were proposed as an effective way for finding such a ground state [17, 48]. D-Wave [6] is one such quantum annealing (also called adiabatic quantum computation) solver based on the Ising model and it shows  $10^8$  speedup over simulated annealing on the weak-string cluster pair problem [30]. However, existing quantum annealing requires close to absolute zero temperature operating on superconductive devices, which are very complicated and expensive. Furthermore, these machines currently are very limited on the size and complexity of the problems they can solve.

While quantum computing has yet to reach maturity, there exists a number of other hardware-based annealing solutions which have been proposed to exploit the highly parallel nature of the annealing process used to solve the Ising model. In [89], a novel CMOS based annealing solver was proposed in which an SRAM cell is used to represent each spin and thermal annealing process was emulated to find the ground state. In [35,90], the FPGA-based Ising computing solver has been proposed to implement the simulated annealing process. However, those hardware based Ising model annealing solvers suffer several problems as detailed in Section 7.1. In this dissertation, a GPU-based Ising model solver is proposed, using a modified simulated annealing heuristic, that can handle any combinatorial problem that is mapped to the Ising model as well as any general problem case associated with it. The maxcut solution is presented first as it is relevant to many VLSI design automation problems. Furthermore, max-cut is a relatively difficult problem to solve without highly efficient heuristic solvers. This manuscript will show that Ising computing by the simulated annealing process is very amenable to fine-grain GPU-based parallel computing. Further proposed is an update method that utilizes the GPU scheduler to achieve a random update pattern enabling independent parallel spin updates. This allows us to maximize thread utilization while also avoiding sequential and deterministic update patterns for a more natural annealing process.

In addition to the max-cut problem, which has a trivial mapping to the Ising model, a solution method is presented for the balanced min-cut bi-partitioning problem. In this problem, the balance constraint will lead to a complete graph in the resulting Ising model. The reason is that the *balance* constraint is a global constraint. As a result, each Ising spin glass is connected to all the Ising spins glasses in the graph, therefore; each local spin update becomes a global update. Current Ising model solvers and quantum annealing computers often do not have architectures amenable to the embedding of problems with complete graphs, e.g., the Chimera graph architecture used in D-wave computer [6]. However, recent study shows that balanced min-cut problems on the D-wave computer indeed yields better results than the state of the art partitioning solvers like METIS [82], but the problem sizes solved are still limited to thousands of nodes and requires co-processing on traditional hardware due to the limited number of available qubits in the QA machine. In this dissertation, an effecient method for mapping the balanced min-cut bipartitioning problem is presented that handles the balancing constraint more efficiently avoiding the complete graph structure and essentially decoupling the spins globally.

Furthermore, unlike other hardware accelerated solvers for the Ising model (e.g. FPGA and ASIC implementations), the proposed method for both max-cut and min-cut solvers do not require solving the NP-hard graph embedding problem which would drastically increase the computational complexity of the solver.

#### 1.4 Contributions

The work presented in this manuscript presents several contributions in the area of simulation and the application of those simulation techniques to the area of reliability based hardware security:

- The first proposed numerical solution to the Korhonen PDE for transient simulation of EM-induced Stress Dynamics for multi-branch interconnects considering both void nucleation and void growth phases.

- A Krylov subspace based model reduction technique to drastically speed-up the numerical solution of the Korhonen PDE. This novel approach is also the only known model reduction method for transient EM simulation that can consider time varying current and temperature.

- The first proposed comprehensive EM-based Hardware Trojan design utilizing physics based models and advanced EM failure dynamics for both Trojan triggers and payloads.

- A Novel self-calibrating EM-based aging sensor to combat counterfeit ICs. The presented approach drastically improves upon previously proposed EM-based aging sensors, and aging sensors in general, in terms of circuit area, accuracy, and range of lifetimes measurable.

- A GPU accelerated method for solving generally connected Ising spin-glass models with applications in graph partitioning. The solver presented avoids costly graph embedding required for other hardware-based solutions when considering complex graph structures. The work addresses both the max-cut and balanced min-cut bipartitioning problems.

### Chapter 2

# Review of EM physics and stress modeling

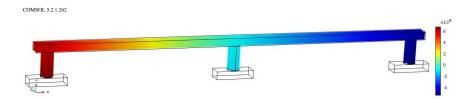

This chapter presents a review of the Electromigration (EM) aging effect. EM is a physical phenomenon of the migration of metal atoms along the direction of the applied electrical field. Atoms (either lattice atoms or defects / impurities) migrate along the trajectory of conducting electrons. During the migration process, hydrostatic stress is generated inside the embedded metal wire due to momentum exchange between lattice atoms and electrons resulting in tension at the cathode and compression at the anode ends of the line. Void and hillock formation are created by the depletion and subsequent deposition of atoms respectively. Fig. 2.1 shows the typical copper dual damascene interconnect structure, which has three terminal vias connecting to other interconnect wires, and the steady-state stress distributions before void nucleation. As time goes on, the lasting unidirectional electrical load will increase hydrostatic stress, as well as the stress gradient which

Figure 2.1: Two-segment wire with steady-state EM induced stress.

acts as a counter-force for atomic migration along the metal line. Generally, when a wire is long, this stress can reach a critical level, resulting in void nucleation at the cathode and/or hillock formation at the anode end of line.

The currently employed method for estimating time to failure is based on Black's equation [14],

$$MTTF = Aj^{-n}exp\{E_a/k_BT\}$$

(2.1)

where j is the current density,  $k_B$  is the Boltzmann's constant; T is the absolute temperature; and  $E_a$  is the EM activation energy. The symbol A is a constant, which depends on a number of factors, including grain size, line structure and geometry, test conditions, current density, thermal history, etc. The current exponent n was found to be 2 for aluminum interconnects in [14]. However, Black's equation is under growing criticism as the extracted parameters, for example, the current exponent n and activation energy  $E_a$ , are not constant and are stress condition-dependent. This is problematic because these parameters are typically found using high stressing accelerated test conditions which are extrapolated to the real use case. This essentially means the parameters used at testing and not realistic representations of the parameters that should be used in real use conditions. Furthermore, this equation is only applicable to a single wire segment. Physics based EM models have been proposed [25, 28, 51] which can be used to mitigate the issues with Black's equation. For a general interconnect wire in two dimensions, transient hydrostatic stress evolution due to EM effects is analyzed in the Korhonen model [51] and stress  $\sigma(x,t)$  is described by Korhonen's partial differential equation (PDE) with the following zero-flux boundary conditions (BC) and initial stress condition (IC):

$$PDE : \frac{\partial \sigma}{\partial t} = \frac{\partial}{\partial x} \left[ \kappa \left( \frac{\partial \sigma}{\partial x} + G_x \right) \right] + \frac{\partial}{\partial y} \left[ \kappa \left( \frac{\partial \sigma}{\partial y} + G_y \right) \right]$$

$$BC : \frac{\partial \sigma}{\partial x}(0,t) = G_x, \ \frac{\partial \sigma}{\partial y}(0,t) = G_y$$

$$BC : \frac{\partial \sigma}{\partial x}(L,t) = -G_x, \ \frac{\partial \sigma}{\partial y}(L,t) = -G_y$$

$$at \ 0 < t < t_{nuc}$$

$$IC : \sigma(0) = [\sigma_1(0), \sigma_2(0), ..., \sigma_n(0)] \ at \ t = 0$$

$$(2.2)$$

Here,  $\kappa = D_a B\Omega/k_B T$  and  $G = \frac{eZ\rho j}{\Omega}$ , which is a function of current density j and  $D_a = D_0 exp(-\frac{E_D - \Omega^* \sigma_T}{k_B T})$  is the effective atomic diffusivity where  $E_D$  is the activation energy of the atom diffusion, T is the absolute temperature and k is the Boltzmann constant. B is the effective bulk elasticity modulus. And  $G = \frac{eZ\rho j}{\Omega}$ , where e is the electron charge, eZ is the effective charge of the migrating atoms,  $\rho$  is the wire electrical resistivity, and j is the current density.

When tensile stress reaches a critical level, a void is formed at the cathode. When this void is formed, the stress at the void location will immediately go to zero, however; the stress around the void will be close to the same stress level as it was immediately prior to the void nucleation [51,72]. This creates a large stress gradient around the void at nucleation time as described by [51]:

$$\frac{\partial \sigma}{\partial x}(x_{nuc}, t) = \frac{\sigma(x_{nuc}, t)}{\delta}, \text{ at } t_{nuc} < t < \infty$$

(2.3)

In Equation (2.3),  $x_{nuc}$  is the location of the void nucleation at a boundary and  $\delta$  is the width of the void interface [73].

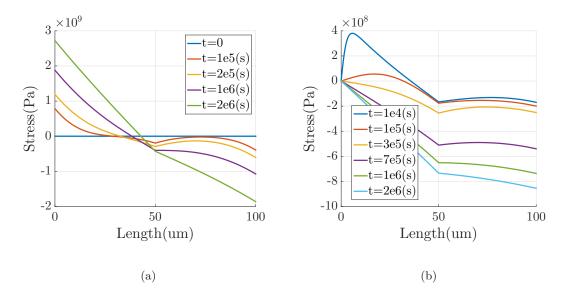

Figure 2.2: EM-stress evolution in the nucleation phase (a) and growth phase (b).

Fig. 2.2 shows stress development over time in a two-segment wire (shown in Fig. 2.1) for Korhonen's equation for both nucleation phase (Fig. 2.2(a)) and growth phase (Fig.2.2(b)). For nucleation phase, over time, tensile (positive) stress will be developed at the cathode (left) node and compressive (negative) stress will be developed at the anode (right) node. The built-up stress (its gradient) will serve as the back force for atomic flux. If the highest stress at the cathode node exceeds the critical stress, voids will be created. The time to reach the critical stress is called nucleation time( $t_{nuc}$ ).

## Chapter 3

# Finite Difference Method for Simulating Electromigration in Multi-Branch interconnects

This chapter presents the Finite Difference Time Domain method (FDTD) used for simulating dynamic stress evolution in the IC back-end-of-line. By solving the PDE for dynamic stress evolution from 2 that leads to EM failure, this method avoids the conservativeness introduced by the semi-empirical Black's equation and the Blech Limit [15](unlike Black's equation, the Blech limit does not estimate a time to failure but rather determines EM mortality). The new simulation method captures both the nucleation and growth stress dynamics and also enables the simulation of EM in multi-branch interconnects. This is an important consideration as it has been shown that wires in an interconnect tree are not independently effected by EM but instead their stress distribution and generation are coupled with neighboring segments in the tree [21, 58]. We further calculate the void volume growth allowing for the determination of resistance degradation in the interconnect tree.

#### 3.1 Void Volume Calculation

During the void growth phase, a void has actually nucleated in the wire and begins to grow. This void causes changes to the electrical properties of the wire, resistance for example, and leads to the eventual failure of the interconnect. For this reason, being able to measure the void volume growth is critical to the proper analysis of the interconnect. Using the dynamic stress evolution of the wire, which will be calculated by the proposed FDTD method, the volume of the void can be calculated as it grows. This is accomplished by calculating the atom drift volume in the wire [76]. Essentially, the stress  $\sigma$  over bulk elasticity modulus B is integrated over the length L of the wire and multiplied by the wire's cross-sectional area A.

$$V(t) = A \int_0^L \frac{\sigma(t)}{B} dx$$

(3.1)

From this equation we can then begin to make inferences about the effect the growth will have on the interconnect's electrical properties.

#### **3.2** Finite Difference Method for EM Analysis

The Finite Difference Time Domain (FDTD) method is a numerical method of solving a Partial Differential Equation (PDE) [66]. A Numerical method finds an approximate solution by iteratively obtaining values as apposed to analytically finding a solution to a PDE. FDTD gives us the ability to quickly and easily find a solution for complicated PDEs that would otherwise be difficult to solve using analytical methods. Furthermore, it has the ability to handle complex geometries.

FDTD works by discretizing both the time and spatial variables in a PDE. This discretization is accomplished by employing the local Taylor expansion to PDE, in conjunction with the wire geometry being discretized, which yields a system of linear equations which are solved for the discrete values within the geometry. While there are several discretization schemes, this work uses the central difference method to discretize the spatial variable x and the first order backward method to discretize time t.

$$\frac{\sigma_i^{n+1} - \sigma_i^n}{\Delta t} = \kappa \frac{\sigma_{i+1}^{n+1} - 2\sigma_i^{n+1} + \sigma_{i-1}^{n+1}}{\Delta x^2}$$

(3.2)

In (3.2), the superscript n indicates the time step and subscript i is the space index, x.

$$-S\sigma_{i+1}^{n+1} + (1-2S)\sigma_i^{n+1} - S\sigma_{i-1}^{n+1} = \sigma_i^n$$

(3.3)

where  $S = \kappa \frac{\Delta t}{\Delta x^2}$ . This discretization method gives us an implicit scheme for solving the PDE numerically. This Implicit scheme allows us more freedom on how large the time step  $\Delta t$  can be as we don't need to worry about stability, which is a problem in explicit methods [66].

For the boundary conditions, stress is dependent on the derivative of the stress function. Thus, Neumann boundaries are used and discretized [53].

$$\sigma_x(0,t) = G = \frac{\partial \sigma_i^n}{\partial x} \tag{3.4}$$

$$\sigma_x(0,t) = \frac{\partial \sigma_i^n}{\partial x} = \frac{\sigma_i^{n+1} - \sigma_{i-1}^{n+1}}{\Delta x} = G$$

(3.5)

We can now use this discretization scheme and plug it into (3.3) to obtain the following.

$$(S+1)\sigma_i^{n+1} - S\sigma_{i+1}^{n+1} = \sigma_i^n - SG\Delta x$$

(3.6)

Note that the derivation for the second boundary condition  $\sigma_x(L,t)$  is omitted. The resulting system of equations can be mapped to an equation in the form of  $A\sigma^{n+1} = \sigma^n$ . A is a tri-diagonal coefficient matrix with the diagonal elements equal to (1-2S) and the lower and upper diagonal elements equal to (-S). The vector  $\sigma^{n+1}$  is a vector of unknown stress along the wire and  $\sigma^n$  is a vector of previously solved for stress. The first element in  $\sigma^n$  is  $\sigma_{left}^n + \beta$  and the last element is  $\sigma_{right}^n - \beta$ . These correspond to the boundary conditions at each end of the wire where  $\beta$  is equal to  $SG\Delta x$ .

Each solution of the system of equations results in a vector containing the stress of the wire at a single time step. Subsequent solution of this system, using previous time step solution as the  $\sigma^n$  vector, can produce a vector containing the stress at the respective time steps. By iteratively solving the system of equations, we obtain the transient stress evolution for the entire wire length. This previous section shows the basic FDTD scheme for a one dimensional wire, however; this can be easily expanded to the two or three dimensional case. The discretization for the two dimensional case used in this work is presented below, albeit without derivation.

$$-S_y \sigma_{i+1,j}^{n+1} + (1+2S_y+2S_x) \sigma_{i,j}^{n+1} - S_y \sigma_{i-1,j}^{n+1} - S_x \sigma_{i,j+1}^{n+1} - S_x \sigma_{i,j-1}^{n+1} = \sigma_{i,j}^n$$

(3.7)

In this equation, i is the discrete variable in the x - axis and j is the discrete variable in the y-axis. The value S also is specified as  $S_x$  or  $S_y$  to differentiate discretization steps used in either direction.

The void growth phase follows the void nucleation phase. For void growth phase, the A matrices are similar (with different boundary and initial conditions). When solving, an arbitrary vector of initial conditions can be used or the output stress distribution from the previous void nucleation phase can be used. Once this has been determined by the user, the growth phase portion of the framework operates the same as the void nucleation phase. That is, the new growth phase discretized equation  $A\sigma^{n+1} = \sigma^n$  is formed and is then solved iteratively to generate transient data for the wire stress.

#### **3.3** Numerical result and discussions

The proposed FDM-based EM analyzer was prototyped in MATLAB. COMSOL multiphysics [1] is used to validate the numerical solver.

In order to validate our result, a FEA tool, COMSOL [1] is used. In the nucleation phase, the initial conditions are set to be zero and default zero flux boundary conditions are used. In the growth phase, initial conditions come from the time at which the cathode in the nucleation phase reaches critical stress. We summarize the major notations and typical parameter values in Table 3.1.

| Term            | Typical value      | Description                               |

|-----------------|--------------------|-------------------------------------------|

| ρ               | 3.00e-8Ω· m        | Electrical resistivity                    |

| e               | 1.60e-19C          | Electric charge                           |

| $Z^*$           | 10                 | Effective valence charge                  |

| Ω               | $1.18e-29 m^3$     | Atomic volume                             |

| k               | 1.38e-23J/K        | Boltzmann constant                        |

| В               | 1.10e11Pa          | Back flow stress modular                  |

| $D_0$           | $7.56e-5m^2/s$     | Self-diffusion coefficient                |

| $E_a$           | 1.76e-19J          | Activation energy                         |

| $\sigma_{crit}$ | $500 \mathrm{MPa}$ | Critical stress                           |

| T               | 373K               | Absolute temperature                      |

| δ               | 3e-7m              | Effective thickness of the void interface |

Table 3.1: Notations and typical value in our transient simulation

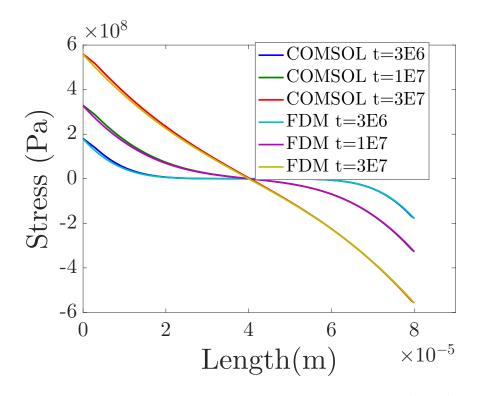

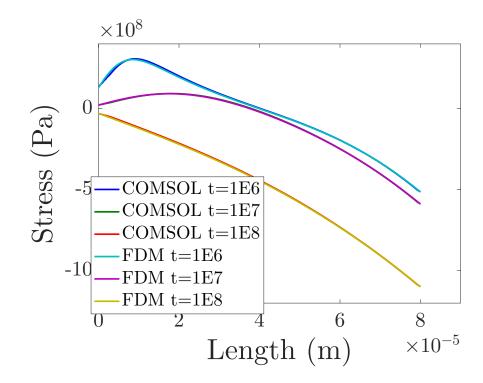

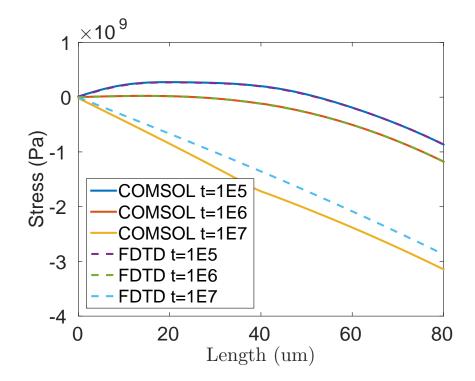

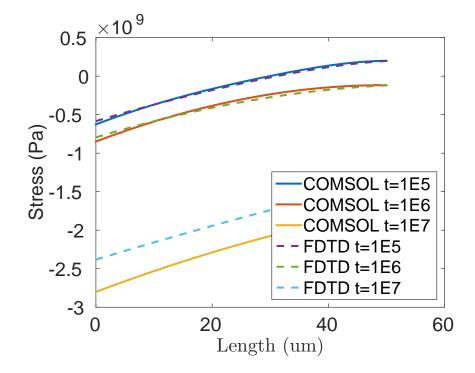

#### 3.3.1 Validation for single 2-terminal wire

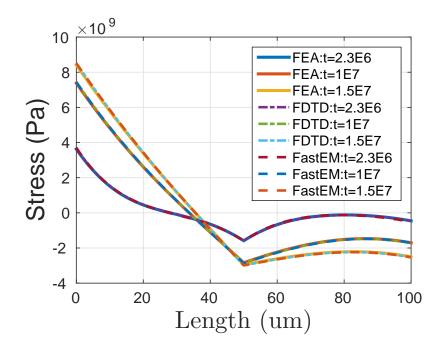

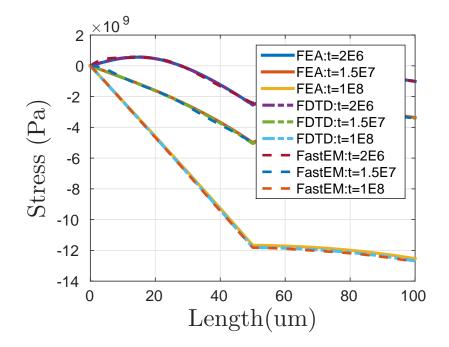

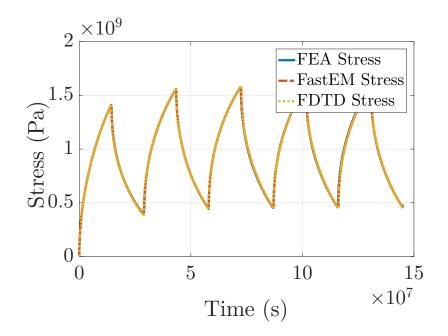

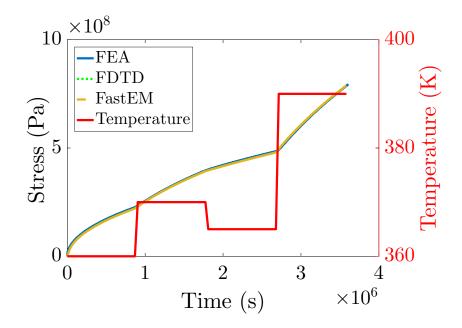

For the 2-terminal single wire as shown in Fig 3.1(a), tensile stress was generated in the cathode (left node) while the anode node experiences compressive stress. This agrees with our expectations which say that a void should be nucleated at the cathode end of the single wire. Root Mean Squared Error(RMSE) when compared to COMSOL for the void nucleation phase, seen in Fig 3.3.1, and void growth phase, seen in Fig 3.3.1, are 0.8033% and 0.4435% respectively.

Figure 3.1: The testing interconnect structures: (a) 1-wire (b) 2 connected wires

#### 3.3.2 Validation for three wire T-shape intersection

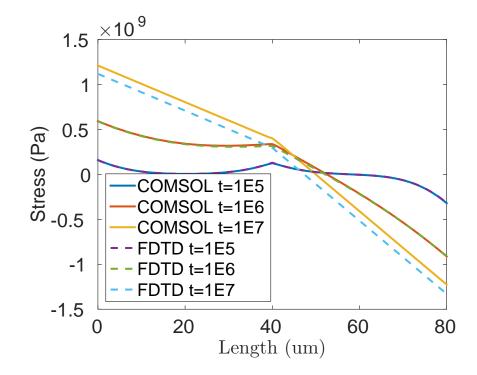

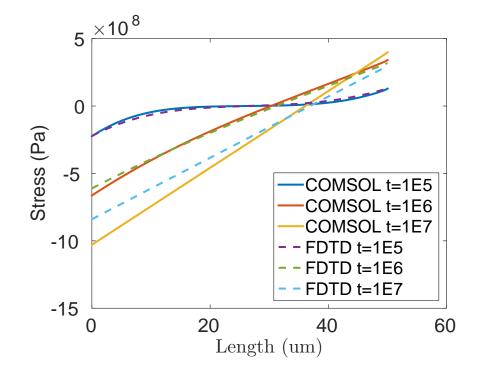

In the three wire T-shaped interconnect shown in Fig 3.1(b), currents were applied as:  $j_1 = 5 \times 10^9 A/m^2$ ,  $j_2 = -6 \times 10^9 A/^2$ ,  $j_3 = -7 \times 10^9$ . With current flowing in through wire one, we expect the void to nucleate here. Results show that our expectations are met and the numerical data agrees with the COMSOL results for both nucleation, seen in Fig 3.3.2 and Fig 3.3.2 and growth phases, Fig 3.3.2 and Fig 3.3.2. RMSE for the nucleation

Figure 3.2: EM-stress distribution change over time with  $j = 5 \times 10^9 A/m^2$  in single 2-terminal wire for void growth

phase is 2.011% and 2.23% for the growth phase. Results for other current configurations are omitted for space but produce similar results.

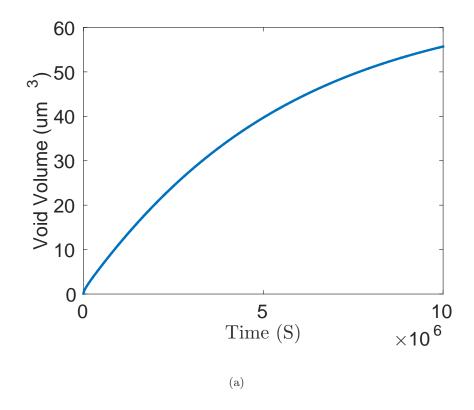

Once the dynamic stress evolution data has been collected from the FDTD analysis, we can apply the void volume calculation to see the transient void volume growth. These results are shown in Fig 3.8(a).

Figure 3.3: EM-stress distribution change over time with  $j = 5 \times 10^9 A/m^2$  in single 2-terminal wire for void growth

#### 3.4 Summary

In this chapter, an accurate EM simulation method using FDTD in multi-branch interconnects based on the first principle of EM physics was presented. The presented numerical method is the first consider both the nucleation and growth phase simulations for multi-branch interconnects. Void volume during the void growth phase was also calculated. The presented method also can easily accommodate existing non-uniform residual stress distribution which is another new contribution. lastly, Numerical results showed that the proposed method agrees with the COMSOL based Finite Element Analysis in terms of accuracy which provides validation of the proposed method.

Figure 3.4: T-shape nucleation phase for horizontal wire

Figure 3.5: T-shape nucleation phase for vertical wire

Figure 3.6: T-shape growth phase for horizontal wire

Figure 3.7: T-shape growth phase for vertical wire.

Figure 3.8: Growth of void volume over time (t=1E7)

### Chapter 4

# Krylov Subspace Method for Fast Electromigration Simulation

This chapter builds upon the previously presented FDTD method for simulating dynamics stress evolution for Electromigration analysis. While the FDTD based method provides a simulation framework for simulating nucleation and growth phases in multibranch interconnects, the numerical solution time can scale poorly for large interconnect trees. To combat this, this chapter proposes a Krylov subspace-based model reduction technique, called "FastEM", to accelerate simulation time while maintaining a high degree of simulation accuracy. Furthermore, this chapter also presents a method for transient current density and thermal simulation in the model reduced simulation framework. Numerical results show that the proposed method can lead to 1-2 orders of magnitude speed-up over the existing method.

## 4.1 The linear time invariant ordinary differential equations for EM stress evolution

In this section, we show how to perform the finite difference discretization for the given stress partial differential equation, also known as the Korhonen equation in (5.1), to create the LTI ODE system. While the derivation is similar to the FDTD presented in the previous chapter, we utilize an implicit method to formulate an LTI System of equations this time.

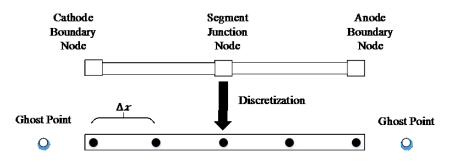

A two-segment wire example is used throughout the section for demonstration with total length L and separate G values for each segment as shown in Fig. 4.1. The wire is discretized into five nodes; two edge boundary nodes at each end of the wire, one junction node at the middle of the wire, and two non-boundary nodes, each between the junction and an edge node.

Figure 4.1: Discretization of the two-segment wire with length L, and segment lengths  $\frac{L}{2}$ .

The finite difference method (FDM) is a method of finding a numerical solution to partial differential equations (PDEs) [66]. The PDE can be discretized using many different methods; in our implementation, a central difference method (4.1) is used to discretize the spatial variable x (and y in the two-dimensional case as shown later). We use the central difference method due to the low truncation error compared to other discretization methods, such as the forward and backward differences, at the cost of only adding one term to each equation. Note that this is different from the Finite Difference Time Domain method (FDTD) in [26], where time is also discretized.

$$\frac{\partial \sigma}{\partial t}(x,t) = \kappa \frac{\sigma_{i+1} - 2\sigma_i + \sigma_{i-1}}{\Delta x^2}, \quad \kappa = \frac{D_a B\Omega}{kT}$$

(4.1)

Boundary conditions are discretized depending on location (internal junctions or edges) and EM phase (nucleation or growth). Edge boundaries are introduced during the handling of ghost points in the discretization scheme. These ghost points are terms in the central difference scheme that do not correspond to physical points on the wire structures. Boundary conditions are discretized using the backward difference scheme shown in (4.2).

$$Nucleation: \frac{\partial \sigma}{\partial x}(0,t) = \frac{\sigma_i - \sigma_{i-1}}{\Delta x} = G$$

$$\frac{\partial \sigma}{\partial x}(L,t) = \frac{\sigma_{i+1} - \sigma_i}{\Delta x} = -G$$

$$Growth: \frac{\partial \sigma}{\partial x}(0,t) = \frac{\sigma_i - \sigma_{i-1}}{\Delta x} = \frac{\sigma(0,t)}{\delta}$$

$$\frac{\partial \sigma}{\partial x}(L,t) = \frac{\sigma_{i+1} - \sigma_i}{\Delta x} = -G$$

(4.2)

By isolating the ghost point term to one side of the equation, we can replace it in the original central difference equation (4.1) allowing us to eliminate the non-existent point while also introducing the boundary condition. Equation (4.3) demonstrates the new central difference equation when the ghost point is eliminated at the cathode.

$$\frac{\partial \sigma}{\partial t}(0,t) = \frac{\kappa}{\Delta x^2} (G_1 \Delta x - \sigma_i + \sigma_{i+1})$$

(4.3)

Internal junctions require no ghost point replacement and instead use the fact that flux is continuous at wire junctions to introduce the boundary conditions as in (4.4).

$$\frac{\partial\sigma}{\partial t}(\frac{L}{2},t) = \frac{\kappa}{\Delta x^2}(\sigma_{i-1} - 2\sigma_i + \sigma_{i+1} + (G_2 - G_1))$$

(4.4)

In (4.4),  $G_1$  and  $G_2$  belong to the two respective wire segments that meet at the junction. Additionally,  $\frac{L}{2}$  indicates that the example is a single wire with two segments where the junction boundary occurs at half the length of the whole wire.

As previously mentioned, we preserve the continuity of the time domain term which allows us to rewrite these equations as an ODE and LTI dynamic system. Using the previously derived equations (4.1), (4.2), and (4.4) for boundary and internal nodes, we can rewrite these equations into matrix format:

$$\begin{bmatrix} \vec{\sigma}_{1} \\ \vec{\sigma}_{2} \\ \vec{\sigma}_{3} \\ \vec{\sigma}_{4} \\ \vec{\sigma}_{5} \end{bmatrix} = \frac{\kappa}{\Delta x^{2}} \begin{bmatrix} -1 & 1 & 0 & 0 & 0 \\ 1 & -2 & 1 & 0 & 0 \\ 0 & 1 & -2 & 1 & 0 \\ 0 & 0 & 1 & -2 & 1 \\ 0 & 0 & 0 & 1 & -1 \end{bmatrix}$$

$$\times \begin{bmatrix} \sigma_{1} \\ \sigma_{2} \\ \sigma_{3} \\ \sigma_{4} \\ \sigma_{5} \end{bmatrix} + \begin{bmatrix} \frac{\kappa \beta \rho}{\Delta x} & 0 \\ 0 & 0 \\ \frac{-2\kappa(\beta \rho)}{\Delta x} & \frac{2\kappa(\beta \rho)}{\Delta x} \\ 0 & 0 \\ 0 & -\frac{\kappa \beta \rho}{\Delta x} \end{bmatrix} \begin{bmatrix} j_{1} \\ j_{2} \end{bmatrix}$$

(4.5)

where  $\beta = \frac{eZ}{\Omega}$ .

For the growth phase, the void is nucleated at the cathode node. Then, the resulting LTI system for the two-segment wire case becomes:

$$\begin{bmatrix} \dot{\sigma}_{1} \\ \dot{\sigma}_{2} \\ \dot{\sigma}_{3} \\ \dot{\sigma}_{4} \\ \dot{\sigma}_{5} \end{bmatrix} = \frac{\kappa}{\Delta x^{2}} \begin{bmatrix} (-\frac{\Delta x}{\delta} - 1) & 1 & 0 & 0 & 0 \\ 1 & -2 & 1 & 0 & 0 \\ 0 & 1 & -2 & 1 & 0 \\ 0 & 0 & 1 & -2 & 1 \\ 0 & 0 & 0 & 1 & -1 \end{bmatrix}$$

$$\times \begin{bmatrix} \sigma_{1} \\ \sigma_{2} \\ \sigma_{3} \\ \sigma_{4} \\ \sigma_{5} \end{bmatrix} + \begin{bmatrix} 0 & 0 \\ 0 & 0 \\ -\frac{2\kappa(\beta\rho)}{\Delta x} & \frac{2\kappa(\beta\rho)}{\Delta x} \\ 0 & 0 \\ 0 & -\frac{\kappa\beta\rho}{\Delta x} \end{bmatrix} \begin{bmatrix} j_{1} \\ j_{2} \end{bmatrix}$$

$$(4.6)$$

As a result, in both the void nucleation and growth phases, we can write the LTI ODE for stress evolution in the following general form:

$$\mathbf{C}\dot{\sigma}(t) = \mathbf{A}\sigma(t) + \mathbf{Bj}(t), \qquad (4.7)$$

$$\sigma(0) = [\sigma_1(0), \sigma_2(0), ..., \sigma_n(0)]$$

In the case of (4.5), **A** is the 5 × 5 coefficient matrix, **C** is a 5 × 5 identity matrix, **B** is  $5 \times 2$  input matrix, and  $\mathbf{j}(\mathbf{t})$  is the 2 × 1 column vector containing the current density of each wire segment for the respective time t.

We note that the presented example only requires equations for the one-dimensional case. However, to handle more general cases, these equations can simply be extended to the two-dimensional domain as shown in (4.8).

$$\frac{\partial \sigma}{\partial t}(x, y, t) =$$

$$\kappa \frac{\sigma_{i+1,j} - 2\sigma_{i,j} + \sigma_{i-1,j}}{\Delta x^2} + \kappa \frac{\sigma_{i,j+1} - 2\sigma_{i,j} + \sigma_{i,j-1}}{\Delta y^2}$$

(4.8)

#### 4.1.1 Steady-state analysis for nucleation phase

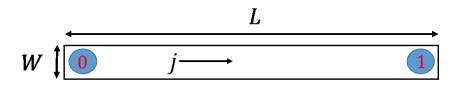

In this subsection, we show that the ODE for the nucleation phase which we derived from Korhonen's equation shown in (4.5) has the same steady-state stress result as the recently proposed voltage-based EM method in [74]. We demonstrate this using one simple example, a two-terminal wire as shown in Fig. 4.2. We let the total length be L. We

Figure 4.2: A two-terminal wire with the electron flow indicated by the arrow.

then use this wire segment length as the spatial step size and use the backward difference method shown in (4.2) for boundary derivation. The resulting system of equations for the two-terminal case is presented in equations (4.9).