#### **UC Santa Barbara**

#### **UC Santa Barbara Electronic Theses and Dissertations**

#### **Title**

Smart Resource Sharing for Concurrency and Security

#### **Permalink**

https://escholarship.org/uc/item/4rs6n9s6

#### **Author**

Gao, Ying

#### **Publication Date**

2017

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA Santa Barbara

# Smart Resource Sharing for Concurrency and Security

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

by

Ying Gao

Committee in Charge:

Professor Timothy P. Sherwood, Chair

Professor Frederic T. Chong

Professor Yuan Xie

Professor Tao Yang

January 2018

# The Dissertation of Ying Gao is approved:

Professor Frederic T. Chong

Professor Yuan Xie

Professor Tao Yang

Professor Timothy P. Sherwood, Committee Chairperson

December 2017

Smart Resource Sharing for Concurrency and Security

Copyright © 2018

by

Ying Gao

#### Acknowledgements

I am very grateful for the opportunity to obtain an academic school life that is primarily provided by my advisor, Timothy Sherwood. Because of his words-not-able-to-describe patience, open-mindedness and wisdom, I, once started as a very junior student from a different major other than computer science or engineering, have been well guided and nurtured through the wonderful computer world over the years. In both computer architecture and operating systems, that represents two of the most critical areas of hardware and software aspects of computing, I have since tasted the best of interesting knowledge to learn and the "worst" of intriguing and difficult problems to solve.

Every Ph.D.'s experience could be properly analogized to roller-coaster rides. The thrilling ups and downs are not for the faint of hearts. I thus deeply appreciate my parents' support and faith in me, and their strong insight in pursuing the most advanced degree. I cherish the spirit learned from my mom, who is extremely disciplined and seldom gives up. I also want to thank my dad, who consistently shares his life experience to pull me out of the numerous down times.

I also owe my sincere thank you to my senior, Hassan Wassel, who made my first publication happen. His diligence and integrity, willingness to help, insights into research and most importantly, a kind heart, set the best model as a researcher and a mentor. Every time I thought of that fall when we were discussing on the NoC project, it would still boost my enthusiasm and keep me forward.

I also appreciate the two summer internships and the people I have met and worked with from industry. The project at Intel left me tremendous interest in concurrency problems that pave the way for my future career.

Mysteriously, I want to thank a VP from Google that I do not remember the name of. Thank you for pointing out the weaknesses in my research and for changing the way I look at research problems. Your silver hair and flowing pony tail now remains an unforgettable view.

Of course not the least, a deep thank you to all my collaborators and my committee who have given inspiring opinions and strong support. Also a thank you to my teachers, fellow lab mates and class mates, for I have learned so much from all of you. At last, I thank my close friends for everything.

#### Curriculum Vitæ

#### Ying Gao

#### Education

| 2017 | Doctor of Philosophy, University of California, Santa Barbara |

|------|---------------------------------------------------------------|

| 2015 | Master of Science, University of California, Santa Barbara    |

| 2011 | Bachelor of Science, Tianjin University                       |

#### Awards

| Micro Top Pick | IEEE Micro Top Pick from Computer Architecture |

|----------------|------------------------------------------------|

|                | Conferences, January - February, 2014          |

#### **Professional Experience**

| Sept 2012 - 2017 | Graduate Research Assistant, University of California, |

|------------------|--------------------------------------------------------|

|                  | Santa Barbara                                          |

| Jun - Sept 2015  | Summer Intern, VMware Inc., Palo Alto                  |

| Jul - Sept 2013  | Research Intern, Intel Corporation, Santa Clara        |

#### **Publications**

- 2017 **Ying Gao** and Timothy Sherwood. Cashmere: Application-Driven Computation Concurrency in a Mobile Operating System, *to submit*.

- 2017 **Ying Gao**, Hassan Wassel, Jason Oberg, Frederic Chong, and Timothy Sherwood. Provably Non-Interfering Architecture for Secure Networks-On-Chip, to submit.

- 2016 Ying Gao and Timothy Sherwood. Hardware-Assisted Context Management for Accelerator Virtualization A Case Study with RSA, Proceedings of the 29th International Conference on Architecture of Computing Systems (ARCS) 2016.

- 2014 Hassan Wassel, **Ying Gao**, Jason Oberg, Ted Huffmire, Ryan Kastner, Frederic Chong, and Timothy Sherwood. "Networks on Chip with Provable Security Properties, IEEE Micro: Micro's Top Picks from Computer Architecture Conferences (IEEE **Micro** top pick), May-June 2014.

- 2013 Hassan Wassel, **Ying Gao**, Jason Oberg, Ted Huffmire, Ryan Kastner, Frederic Chong, and Timothy Sherwood. SurfNoc: A Low Latency and Provably Non-Interfering Approach to Secure Networks-On-Chip, *Proceedings of the 40-th International Symposium on Computer Architecture* (**ISCA**) 2013.

#### Abstract

#### Smart Resource Sharing for Concurrency and Security

#### Ying Gao

Different layers of the computer system, from the low-level hardware accelerators and networks-on-chip (NoC) in multi-core systems, to the upper-level operating systems and software applications, rely on the sharing of hardware computing resources. Unfortunately such sharing, when not carefully managed, can introduce a host of protection problems and sources of information leakage. We describe a set of methods by which it is possible to systematically scale performance via hardware sharing without exacerbating security properties by being aware of the design and characteristics of individual layers and components. The key to this is efficiently dealing with security vulnerabilities introduced by sharing in terms of time and space through the creation of new security-conscious sharing interfaces. In a systematic way is to first define coordination techniques into more detailed patterns, and by bridging the gap of less efficient universal measures with provably more performant and secure patterns.

Specifically we demonstrate the usefulness of a sharing pattern for hardware and software systems where separation is of concern (interference and timing channel mitigation, etc). The most important insight is that in order to fully utilize computing resources (to improve performance and availability), the entities that share these resources must coordinate in a pre-calculated way. More dynamic approaches to improve performance and concurrency are likely to introduce new interference in the system. While we show that certain static scheduling measures in lower level hardware such as networks-on-chip can provably eliminate timing channels, the dynamic nature of software systems makes covert channels harder to be confined. Besides, software systems also face other types of security problems beyond side channels. To improve concurrency and performance without exacerbating security requires a slightly different approach.

To study the obstacles that hinder software applications' scaling in a system because of security concerns, we delve into the Android operating system and its application ecosystem structure. A prime avenue for attack is introduced because of its distributed sharing eco-pattern. We propose a centralized approach with a single reliable service as a method to enable computation reuse among applications. The proposed centralization technique favors well-protected application-to-system communications over vulnerable application-to-application communications. Thus not only computation concurrency is boosted but also the possibility of an app being attacked through the attack-prone Inter-Component Calls (ICCs) due to possible distributed computation sharing is eliminated. This approach further enables improvements to security with the addition of a novel

application-centric grouping for isolation. We show through a prototype on Android how our approach supports and protects inter-app resource sharing, while improving concurrency at scale.

# Contents

| Li | ist of            | Figure        | es                                                      | xii        |

|----|-------------------|---------------|---------------------------------------------------------|------------|

| 1  | Intr              | oducti        | ion                                                     | 1          |

|    | 1.1               | Non-In        | nterference and Domain Isolation                        | 3          |

|    | 1.2               | Thesis        | s Statement and Dissertation Roadmap                    | 5          |

|    |                   | 1.2.1         | Networks-on-Chip with Provable Security Properties      | 5          |

|    |                   | 1.2.2         | Hardware-Assisted Accelerator Virtualization            | 6          |

|    |                   | 1.2.3         | Application-Centric Access Control and Computation Con- |            |

|    |                   | curren        | acy in Mobile Systems                                   | 8          |

| 0  | <b>TN</b> T - 4   | 1             | China ith Daniel La Consider Daniel in                  | 10         |

| 2  |                   |               | on Chip with Provable Security Properties               | 10         |

|    | 2.1               |               | ed Work                                                 | 14<br>18   |

|    | 2.2               |               | oC Architecture                                         | _          |

|    |                   | 2.2.1         | A Motivating Example                                    | 18         |

|    | 0.2               | 2.2.2         | SurfNoC Scheduling                                      | 21<br>24   |

|    | 2.3               |               | oC Router Micro-architecture                            |            |

|    |                   | 2.3.1 $2.3.2$ | Partitioning Virtual Channels                           | 25<br>25   |

|    |                   | 2.3.2 $2.3.3$ | Allocators                                              | 25<br>27   |

|    |                   | 2.3.3 $2.3.4$ |                                                         | 28         |

|    |                   | 2.3.4 $2.3.5$ | Pipelining and separation discussion                    | 30         |

|    | 2.4               |               | RTL Implementation                                      | 37         |

|    | 2.4               | 2.4.1         | Experimental setup                                      | 37<br>37   |

|    |                   | 2.4.1         | Impact on latency                                       | 38         |

|    |                   | 2.4.2         | Throughput                                              | 41         |

|    |                   | 2.4.4         | Area and power overhead                                 | 44         |

|    | 2.5               |               | eation of Non-interference                              | $44 \\ 45$ |

|    | $\frac{2.5}{2.6}$ |               | usions                                                  | 47         |

|    | 4.0               | Control       |                                                         | 41         |

| 3 | Hardware-Assisted Context Management for Accelerator Viralization                         |

|---|-------------------------------------------------------------------------------------------|

|   | 3.1 Related Work                                                                          |

|   | 3.2 Baseline RSA Accelerator Architecture                                                 |

|   | 3.2.1 Montgomery's Modular Multiplication and Exponentiatio                               |

|   | 3.2.2 Sharing an RSA Accelerator                                                          |

|   | 3.3 Tightly Integrated Virtual Accelerator Approaches                                     |

|   | 3.3.1 Baseline Virtual RSA Accelerator Design Overview                                    |

|   | 3.4 Optimized Solution                                                                    |

|   | 3.5 Experimental Evaluation                                                               |

|   | 3.5.1 Relative Performance                                                                |

|   | 3.5.2 Area Cost and Power Consumption                                                     |

|   | 3.6 Conclusions                                                                           |

|   |                                                                                           |

| 4 | Application-Centric Computation Concurrency                                               |

|   | 4.1 Background on Android Access Model, Security Challenges and Inter Application Charing |

|   | Inter-Application Sharing                                                                 |

|   | 4.2.1 Background on Android Audio Applications                                            |

|   | 4.2.1 Background on Android Audio Applications                                            |

|   | 4.3 Overview of Cashmere Architecture                                                     |

|   | 4.3.1 Library Paths Identification                                                        |

|   | 4.3.2 Computation Memorization and Management                                             |

|   | 4.3.3 Application-Guided Grouping                                                         |

|   | 4.3.4 Concurrent I/O                                                                      |

|   | 4.4 Implementation                                                                        |

|   | 4.4.1 Two-Phase Grouping                                                                  |

|   | 4.4.2 Inner-Group Isolation                                                               |

|   | 4.4.3 Inter-Group Isolation                                                               |

|   | 4.5 Evaluation                                                                            |

|   | 4.5.1 Library Call Indirection Overhead                                                   |

|   | 4.5.2 Dictionary Model Influence in Latency and Accuracy                                  |

|   | 4.5.3 Concurrent Apps Performance                                                         |

|   | 4.5.4 Grouping Overhead and Impact                                                        |

|   | 4.5.5 Security Analysis                                                                   |

|   | 4.6 Conclusions                                                                           |

| _ |                                                                                           |

| 5 | Conclusions 5.1. Contributions                                                            |

|   | 5.1 Contributions                                                                         |

|   | 5.2 Looking Forward                                                                       |

Bibliography 138

# List of Figures

| 2.1 Time-division multiplexing scheduling in a 16-node 2D mesh (only     |    |

|--------------------------------------------------------------------------|----|

| one direction of channels is shown for illustration purposes)            | 50 |

| 2.2 Surf scheduling in a 16-node 2D mesh (only one direction of chan-    |    |

| nels is shown for illustration purposes)                                 | 51 |

| 2.3 Surf scheduling in 16-node 2D mesh with three application domains    |    |

| (denoted by white, grey, and black) assuming a single-cycle routers for  |    |

| illustration purpose. The schedule runs as white, white, grey, and black |    |

| and repeats, giving the white domain half the bandwidth. A packet (the   |    |

| white box under the node S) belongs to the white domain is sent from     |    |

| the node marked by S to the node marked by R. The figure contains six    |    |

| consecutive cycles. At $T=1$ , the packet is forwarded on the S port in  |    |

| the y-dimension (which is scheduled to forward white packets). It keeps  |    |

| moving in the y-dimension until $T=3$ when it needs to move in the       |    |

| x-dimension on the W port. The packet waits 2 cycles (T=4 and T=         |    |

| 5) until it is the white domain's turn on the W port and finally it is   |    |

| forwarded to its destination on $T = 6$ . Another wait may happen again  |    |

| in the destination router (R) to forward the packet on the ejection port |    |

| waiting for the white domain's turn                                      | 52 |

| 2.4 Partitionable virtual channels                                       | 53 |

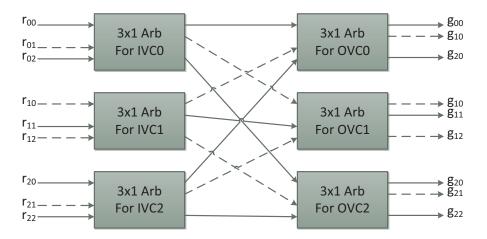

| 2.5 Virtual channel allocator: A 3x3 separable input-first VC allocator. |    |

| In this example, we assume that VC0 and VC2 are assigned to domain       |    |

| 0 and VC1 is assigned to domain 1. Dashed lines shows signals that can   |    |

| never be 1 due to route computation restrictions. This example shows     |    |

| that we can reconstruct the allocator into smaller ones                  | 53 |

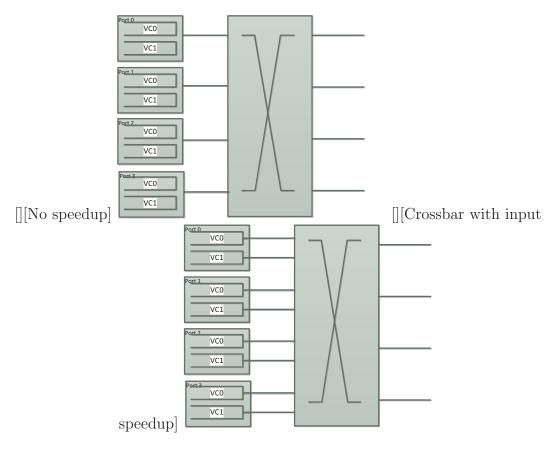

| 2.6 Crossbar with input speedup to eliminate contention on switch        |    |

| input port between VCs from different domains                            | 54 |

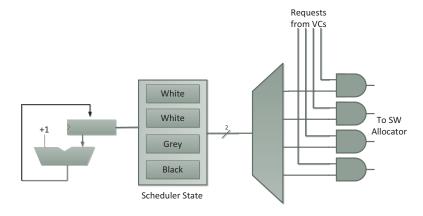

| 2.7 Scheduler: The scheduler output is used to mask requests to the      |    |

| switch output ports according to the surf schedule                       | 54 |

| 2.8 a) Buffer write operation from west input port: input flit arrives       |     |

|------------------------------------------------------------------------------|-----|

| from domain-0s VC-0 (D0-VC0), control logic selects D0-VC0 buffer            |     |

| queue based on the Source ID and the Destination ID of the flit. b)          |     |

| Result of Buffer write operation: Input flit is queued in the buffer and     |     |

| the tail pointer increments from 0 to 1)                                     | 55  |

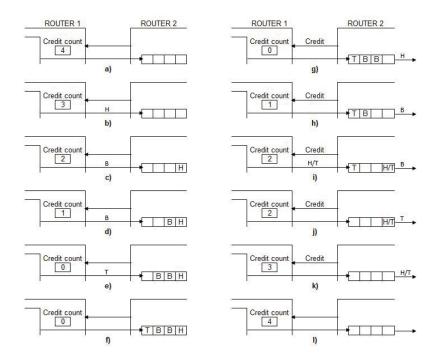

| 2.9 Description of credit-based flow. a) Initial state: credit count is 4.   |     |

| b)-f) router 1 sends out four flits H, B, B, and T to router 2; the credit   |     |

| count decrements to 0. g)-l) router 2 sends out credit signals to router     |     |

| 1; credit count of router 1 becomes 4 again                                  | 55  |

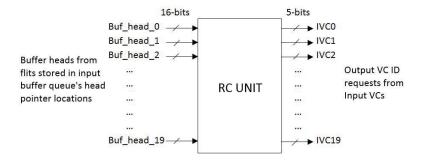

| 2.10 RC unit takes 16-bit heads from the flits pointed by buffer queues      |     |

| head pointers and generates request for output VCs for each input VC.        |     |

| For example, the IVC0 signal stores the output VC ID requested by            |     |

| input virtual channel-0 of domain-0 (D0-VC0)                                 | 56  |

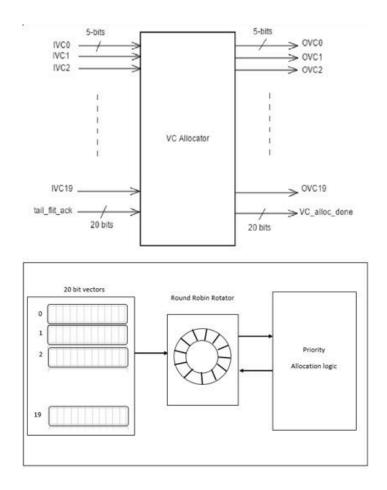

| 2.11 The I/O ports of the VC allocator unit (top) and the VC unit            |     |

| implementation (bottom). For OVC0, for instance, the 4th bit in the          |     |

| 20-bit vector is set if IVC4 requests for OVC0. The vectors are then         |     |

| rotated based on the previously granted request such that it receives        |     |

| the least priority. The priority allocation logic then grants each of the    |     |

| output VC to the first bit that is set in the respective vector              | 57  |

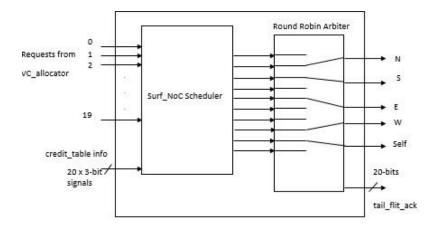

| 2.12 The SurfNoC schedule (SA) logic masks all the requests that do          |     |

| not belong to the scheduled domain for the current clock cycle or do not     |     |

| satisfy the credit requirements. Thus, at most, only 2 output VCs can        |     |

| contend for the same output port. The round robin arbiter shown above        |     |

| allocates each of the five output ports to one of the two potential requests |     |

| every clock cycle. The 'tail_flit_ack' signal is computed by making use      |     |

| of the buffer head information that is globally exposed to all the units     |     |

| by the buffer unit. For instance, the 4th bit is set if the 4th buffer/IVC4  |     |

| is going to forward a tail flit on the output port                           | 58  |

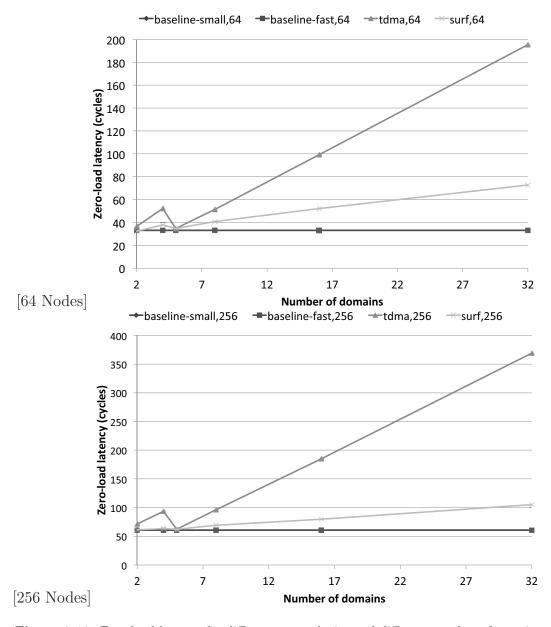

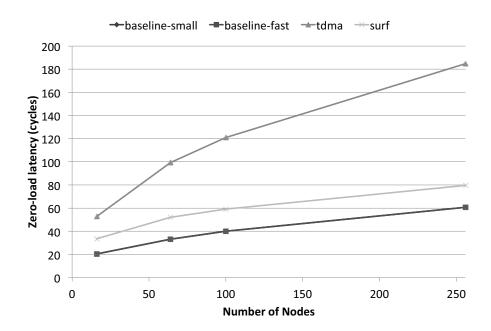

| 2.13 Zero-load latency for different network size and different number       |     |

| of security domains (the two baselines are overlapped because zero-load      |     |

| latency does not depend on buffers and crossbar input speedup)               | 59  |

| 2.14 Zero-load latency against different network size with 16 domains        |     |

| (the two baselines are overlapped because zero-load latency does not         |     |

| depend on buffers and crossbar input speedup)                                | 60  |

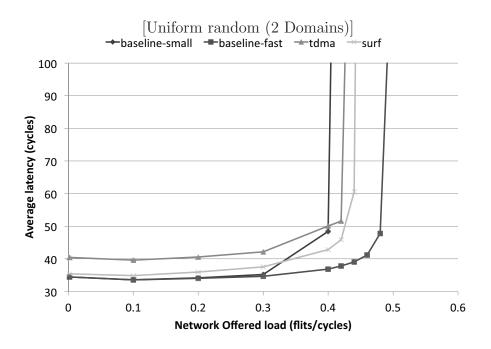

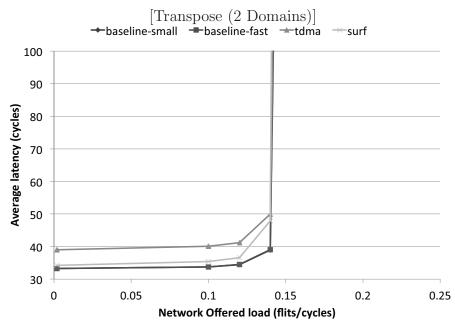

| 2.15 Average latency as a function of aggregate domains offered load for     |     |

| 2D mesh network of 64 Nodes: We can see that latency is stable below         |     |

| network saturation point.                                                    | 61  |

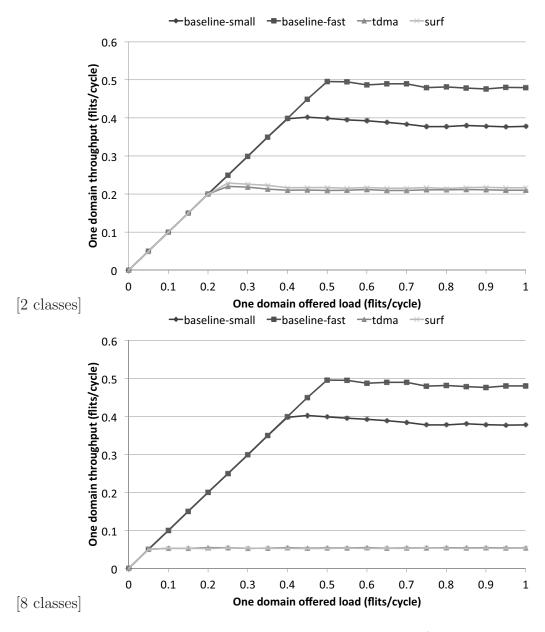

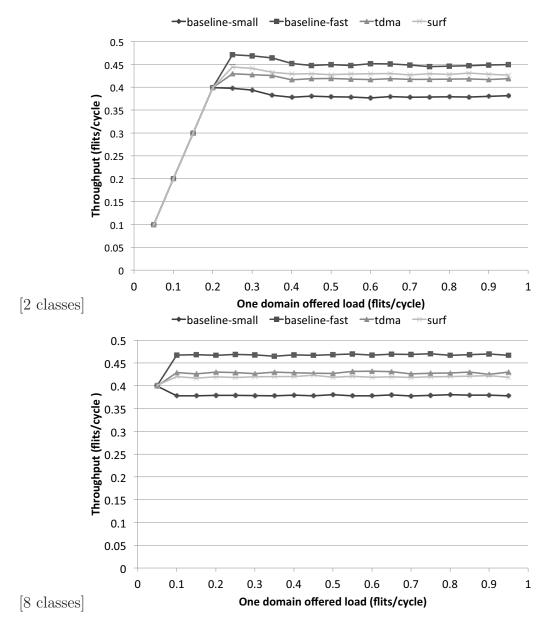

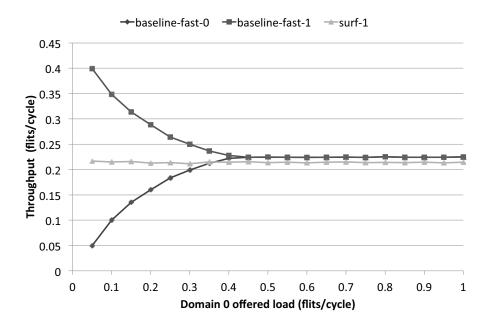

| 2.16 Throughput as a function of offered load of one domain (only one        |     |

| domain is injecting) for 2D 64-nodes mesh using different number of          | ~ - |

| domains                                                                      | 62  |

| 2.17 Aggregate network throughput as a function of offered load of one domain (all domains are injecting packets) for 2D 64-nodes mesh using different number of domains                                                                                                                                                                                                                                                                                                                             | 63<br>64 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

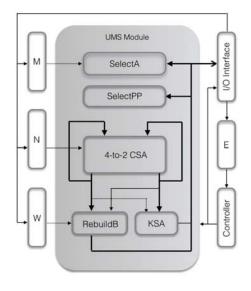

| 3.1 Traditional RSA accelerator block architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71       |

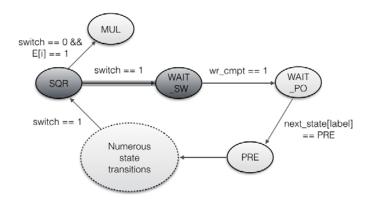

| stand for modular multiplication and square operation respectively 3.3 State diagram of an example transition case in the baseline architecture. When receiving active switch signal in SQR state, it will jump to WAIT_SW state to store intermediate results in local RAM. label denotes VM ID. If the current requesting VM was in PRE state during last switch out, next_state will be set to PRE. After numerous state transitions, the VM that was switched off during SQR state might request | 71       |

| again, and have a chance to restore its state                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 75       |

| exponentiation operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75       |

| diate results at previous SP                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 77       |

| ture state retrieval                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 77       |

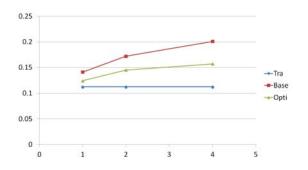

| ber of VMs allowed to concurrently occupy the device                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 85       |

| 3.8 Comparison of area costs for v-1, v-2 and v-4 designs                                                                                                                                                                                                                                                                                                                                                                                                                                            | 86       |

| 3.9 Comparison of peak power consumption for v-1, v-2 and v-4 designs                                                                                                                                                                                                                                                                                                                                                                                                                                | 86       |

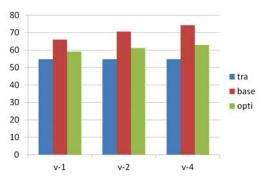

| 4.1 The Cashmere Platform Architecture. Upon an application calling       |     |

|---------------------------------------------------------------------------|-----|

| a lib function, the call will be directed to the modified audio library   |     |

| extended with binder IPC client interface to send lib call requests to    |     |

| Shared Lib Service. Shared Lib Service is a registered service served as  |     |

| a transition channel between client apps and the Cashmere server ap-      |     |

| plication. Library function table is the major component of the server    |     |

| application, it records previously computed lib calls and will reply to   |     |

| future identical calls directly, only un-computed fresh lib calls will be |     |

| passed on to the original library. Note that the original audio SR lib,   |     |

| in our case libpocketsphinx.so will be renamed so applications cannot     |     |

| directly call it upon and instead the modified lib is named libpocket-    |     |

| sphinx.so.                                                                | 101 |

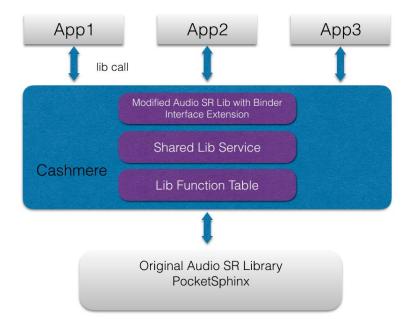

| 4.2 Cashmere as a registered service through Service Manager provided     |     |

| by Android platform. Cashmere is in Android user space                    | 102 |

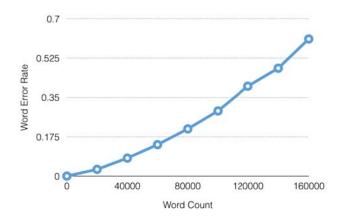

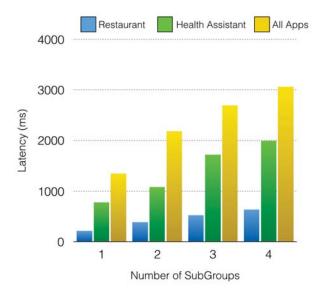

| 4.3 Average WER to varied vocabulary dictionary sizes on PocketSphinx.    | 116 |

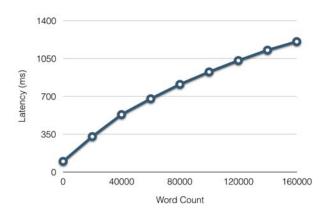

| 4.4 Average latency to varied vocabulary dictionary sizes                 | 117 |

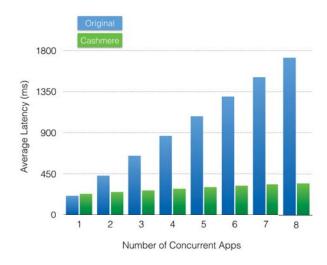

| 4.5 Average latency of concurrently running audio apps natively and       |     |

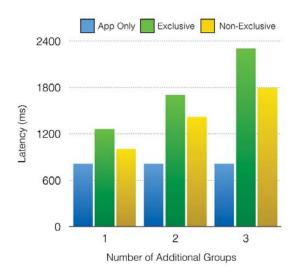

| in Cashmere.                                                              | 119 |

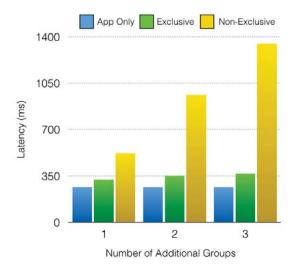

| 4.6 Average latency of running an app with small to medium vocabu-        |     |

| lary sizes without concurrent apps, running exclusively but concurrently  |     |

| with additional groups, and running non-exclusively but concurrently by   |     |

| joining one of the additional groups in Cashmere                          | 121 |

| 4.7 Average latency of running an app with large vocabulary sizes with-   |     |

| out concurrent apps, running exclusively but concurrently with addi-      |     |

| tional groups, and running non-exclusively but concurrently by joining    |     |

| one of the additional groups in Cashmere                                  | 122 |

| 4.8 Average latency of concurrently running different combinations of     |     |

| apps in Cashmere.                                                         | 125 |

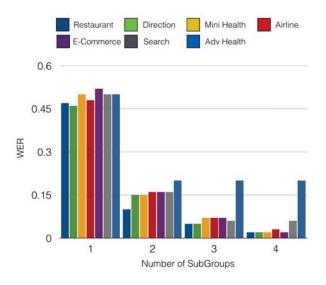

| 4.9 Average WER to varied vocabulary dictionary sizes                     | 127 |

|                                                                           |     |

## Chapter 1

### Introduction

The dissertation presents a step towards a more systematic design methodology by which one can construct scalable components sharing across hardware software boundaries. The need to bridging the gap between the diverse heterogeneous hardware landscape envisioned by many as the future, and the designed-for-single-core simple software operating systems is acute. From the hardware perspective, as we entered the multi-core and manycore era, communications and sharing efficiency among cores has become one of the biggest obstacles to efficiency. From the operating systems perspective, managing the emerging accelerator architectures and scheduling the complex software that multiplex their resources them becomes a significant new burden. The problem is especially acute in mobile platforms where

the computing resources are diverse, energy is limited, and the demand for new features is ever present.

While scheduling for performance alone is hard enough, when coupled with security concerns, the burden is even higher. All sharing comes with the risk of information leaking. If the shared state is not managed correctly it is possible for two different subsystems to learn about each others' actions. A malicious software could gain useful information about a victim when conflicts in the resources appear. Two more malicious subsystems might even purposefully communicate through such resource contention by forming a covert channel. The classic Denial-of-Service (DoS) attack is another example of how the system can be broken down by improper sharing schemes. Of course these specific scenarios are just a tip of the iceberg of the attacks enabled by systems engineered without a mind to secure sharing. Due to the creativity of attackers and the lack of established fail-proof designs, a large body of work exists focused on vulnerability and malware studies across all system layers.

Designs that attempt to balance security and performance in the context of the coordinating hardware/software subsystems is the topic of this thesis. It is difficult to solve performance and security problems at the same time, or at least to enhance one without hurting another. However, we show in this thesis a set of three patterns for managing the above attack scenarios while maintaining performance,

two in hardware-level (networks-on-chip and accelerators) and one in software system level (Android mobile OS). We show how careful interface design coupled with proposed coordination patterns can dramatically boost system performance and concurrency by efficient sharing without compromising the original system's security properties.

Before we dive into the details of either of the scenarios, we begin with some background on the growing demand for isolation inside hardware units and among applications in the operating systems.

#### 1.1 Non-Interference and Domain Isolation

In high-assurance systems it is a common practice to break the system into a set of domains, which are to be kept separate. These domains should have no effect on one another. For example, the Mars Curiosity rover software runs on a RAD750 processor, a single-core radiation-hardened version of the Power architecture with a special-purpose separation kernel[1]. The kernel partitions the tasks, such as guidance, navigation and the various science packages from one another to help prevent cascading failures. Future space missions are looking to use multicore systems[2][84], which adds another layer of communication, but there are serious concerns about the introduction of opportunities for interference between system components[68]. The problem is that typical networks-on-chip have many internal

resources that are shared between packets from different domains, which we would otherwise wish to keep separate. Such resource contention introduces interference between these different domains, which can create a performance impact on some flows, pose a security threat by creating an opportunity for timing channels, and generally complicates the final verification and certification process of the system because all of the ways in which that interaction might occur must be accounted for. Non-interference means that injection of packets from one domain cannot affect in any way (including the timing of delivery of) packets from other domains.

Similarly, in operating systems such resource contention also exist among applications. The problem is even more acute in mobile operating systems where a lot of resources are from I/O devices (usually only one for each type) and often request real-time processing. To prevent such contention and to keep strict isolation, many mobile systems are designed to allow only one application to access the device at a time. However, this is in direct conflict with the current need of running concurrent applications both foreground and background. For example, a user might use voice command to order food by speech recognition (SR) featured restaurant apps meanwhile discussing with friends on social apps using audio, she/he might also require the help of a SR supported search assistant app as well. In the newest release Android Nougat (2016), the split screen feature is the first time Android will allow the convenience of running multiple applications in the

foreground. To bring isolation into the OS that requires application concurrency is not an easy task, under limited hardware computing resources and energy, it becomes even more difficult when we talk about scalability.

#### 1.2 Thesis Statement and Dissertation Roadmap

I propose that under coordinated domain-aware sharing schemes, in almost all system layers, it is possible to increase concurrency and scalability while maintaining useful security properties (e.g. isolation). I demonstrate this observation through its application in low-level networks-on-chip, hardware accelerators, and higher-level operating systems and applications. The rest of this chapter provides an overview of our proposed steps towards a system that provides superior concurrency without exacerbating isolation properties.

# 1.2.1 Networks-on-Chip with Provable Security Properties

One simple way to ensure separation within a networks-on-chip is to simply time multiplex the network. Each "domain" gets it's turn across the entire network at a time. However, this approach introduces huge latencies and simple ways of relaxing TDMA introduce inter-domain interference. In replacing the non-scalable

TDMA approach, we propose a technique that assures multi-way non-interference in NoCs with low overhead on latency to allow for verification of high assurance systems such as those in aerospace and automotive systems. By carefully scheduling the network into waves that flow across the interconnect, data from different domains carried by these waves are strictly non-interfering while avoiding the significant overheads associated with cycle-by-cycle time multiplexing. The technique, named SurfNoC, significantly reduces the latency incurred by temporal partitioning. We describe the scheduling policy and router microarchitecture changes required, and evaluate the information-flow security of a synthesizable implementation through gate-level information flow analysis. When comparing our approach for varying numbers of domains and network sizes, we find that in many cases SurfNoC can dramatically reduce the latency overhead of implementing cycle-level non-interference.

#### 1.2.2 Hardware-Assisted Accelerator Virtualization

In recent years, hardware accelerators are becoming first class citizens on chips because of their usefulness in improving performance and saving power in computation intensive tasks. However, unlike CPUs that can context switch effortlessly (without losing intermediate data) through registers and deep pipe-lining, the options for time multiplex sharing on accelerators are often limited – one either

drops the current computing task or the requesting app should wait in queue for the occupying task to finish. The former usually introduces wasted cycles and the latter degrades responsiveness.

In order to fix the designed-not-for-share accelerator architectures, we examine a set of hardware design approaches whereby the interface is split providing two virtual units. We build a public-key crypto accelerator virtualization and study the trade-off between sharing granularity and management overhead in time and space. Based on observations made during the design of several such systems, we propose a hybrid local-remote scheduling approach that promotes more intelligent decisions during hardware context switches and enables quick and safe state packaging. We find that performance can vary significantly among the examined approaches, and that our new design, with explicit accelerator support for state management and a modicum of scheduling flexibility, can allow highly contended resources to be efficiently shared with only moderate gains in area and power consumption. The statically designed separation in interfaces, switching points and fixed trackable memory are all in support for isolation. The work is also the result of cooperation within hardware architecture design and software scheduling.

# 1.2.3 Application-Centric Access Control and Computation Concurrency in Mobile Systems

While the previous two sections introduce the smart sharing schemes in hardware designs, when looking into the higher operating system level we find that sharing schemes can also be modified to enable application concurrency. A typical example is the Android system where applications would benefit from further communication and sharing. However, due to Android's applification [5] (decentralized) nature (each app has a Linux userID along with server client communication mechanism among apps) and arguably flawed permission model (permissions are mostly requested by app on installation and the components within an app share the same permission), there has been huge number of attacks [15][23] targeting these vulnerabilities. While research on Android has seen a tremendous amount of effort towards improving the security and privacy issues[96][94][24][31][88][27], very few have explored the problem with an eye towards enhancing computation concurrency and performance.

To discover the obstacles hindering the progress of application concurrency and performance in Android, we systematically studied the system designs and components that are both vulnerability-prone and performance-unfriendly. We make the key observation that the lack of centralization in Android could be hurting both security and performance. Inspired by the PeerReview[36] concept in distributed

systems community, we propose a central platform to guide interested apps in forming groups for sharing on different I/O libraries and computations. By refraining the communication paths among collaboration-specified apps, server app side security concerns can be relieved, thus promoting confidence and an improved willingness to share. Besides, the attack-prone inter-app communications are replaced by app-to-central service communications, the client app should be less worried in being attacked during sharing. For computation heavy library sharing, the central platform employs computation memorization to record library function call chains from concurrent running apps and dispatch computations with superior scalability.

### Chapter 2

## Networks on Chip with Provable

# Security Properties

Programmers are increasingly asked to manage a complex collection of computing elements including a variety of cores, accelerators, and special purpose functions. While these many-core architectures can be a boon for common case performance and power-efficiency, when an application demands a high degree of reliability or security the advantages becomes a little less clear. On one hand, the ability to spatially separate computations means that critical operations can be physically isolated from malicious or untrustworthy components. There are many advantages to providing physical separation which have been well explored in the literature [72, 92]. On the other hand, real systems are likely to use dif-

ferent subsets of cores and accelerators based on the needs of the application and thus will require a shared communication network. When a general purpose interconnect is used, analyzing all the ways in which an attacker might influence the system becomes far more complicated. The problem is hard enough if we restrict ourselves to considering only average case performance or packet ordering, but the difficulty of the problem increases even further if we attempt to prevent even cycle-level variations.

In high assurance systems it is common practice to break the system into a set of domains which are to be kept separate. These domains should have no-effect on one another. For example, the Mars Curiosity rover software runs on a RAD750 processor, a single-core radiation-hardened version of the Power architecture with a special purpose separation kernel [1]. The kernel partitions the tasks such as guidance, navigation and the various science packages from one another to help prevent cascading failures. Future space missions are looking to use multicore systems [84, 2] which adds another layer of communication, but there are serious concerns about the introduction of opportunities for interference between system components.

The problem is that typical networks-on-chip have many internal resources that are shared between packets from different domains which we would otherwise wish to keep separate. These resources include the buffers holding the packets, the crossbar switches, and the individual ports and channels. Such resource contention introduces "interference" between these different domains which can create a performance impact on some flows, pose a security threat by creating an opportunity for timing channels [89], and generally complicates the final verification and certification process of the system because *all* of the ways in which that interaction might occur must be accounted for.

These concerns are similar to, but distinct from, the problem of providing quality-of-service guarantees. While QoS can minimize the performance impact of sharing between domains by providing a minimum guaranteed level of service for each domain (or class) [32, 33, 50, 34], as shown by Wang and Suh, quality of service techniques will still allow timing variations and thus do not truly support non-interference [89]. The only way to be certain that the domains are non-interfering is to statically schedule the domains on the network over time. However, a straightforward application of time multiplexing leads to significant increases in latencies as each link in the network is now time multiplexed between many different domains.

The core idea behind our approach is that, if a strictly time multiplexed link is seen as an oscillating behavior, we can stagger the *phases* of these oscillations across the network such that a set of "waves" are created. As these waves traverse the network they provide an opportunity for packets of the corresponding domain

to travel unimpeded along with these waves (thus avoiding excessive latency) while still requiring no dynamic scheduling between domains (thus preventing timing corruption or information leakage). Channels in the same dimension and direction appear to "propagate" different domains such that after passing through the pipeline of the router, the channel is ready to forward a packet coming from the same dimension and domain without any additional wait (unless there is contention from packets of the same domain). In this way packets "surf" the waves in each dimension. We identify the many potential hazards non-interference faces in a modern network-on-chip, we discuss the details and ramifications of our surf scheduling methodology, and we argue that our approach truly does not allow even cycle-level cross-domain interference. Specifically in this chapter:

- 1. We present a link scheduling scheme and network router design which simultaneously supports both low-latency packet-switched operation and non-interference between domains.

- 2. We show that as the network grows in size, as the number of domains increases, and as the asymmetry between domains becomes larger, the benefit for a surf-scheduled network over TDMA continues to increase.

- 3. We evaluate the latency, throughput, area, and power consumption of these approaches through a detailed network simulation.

4. Finally, we argue that the technique is truly sound through an analysis of the router micro-architecture and with the help of formal verification via gate-level information flow analysis.

The rest of the chapter is organized as follows. We begin with a discussion of related work and how our proposed solution fits in the design space in Section 2.1. Next, in Section 2.2, we describe the core idea behind the SurfNoC schedule followed by a detailed router micro-architecture discussion in Section 2.3. Section 2.4 presents the evaluation of the system and explores the relationship between domains, partition asymmetry, and scheduling. Then, we provide a gate-level information-flow analysis in Section 2.5 Finally, Section 2.6 concludes the paper with our final thoughts and a discussion of future directions.

#### 2.1 Related Work

Our proposed solution to non-interference in NoCs touches on many problems that has been proposed in the literature, such as timing channels in micro architecture, QoS in network-on-chips, fault-containment and composability in system-on-chips, and security in NoCs. In this section, we will try to review some of this related work and show how our work fits in the design space.

Timing Channels and Non-interference in Micro-architecture There has been an recent renewed interest in the analysis of timing channel attacks and mitigations through micro-architecture state such as cache interference [6, 90, 91] and branch predictors [7, 8]. One approach to these problems is a technique that can verify non-interference of hardware/software systems (including high performance features such as pipelining and caching) using gate-level information flow tracking [87, 85, 86]. More recently, a NoC timing channel protection scheme for a system with security lattices was been proposed [89]. This paper proposes a priority-based arbitration scheme to allow packets with LOW labels to always win arbitration (except when they reach a pre-specified quota during each system epoch to prevent denial-of-service attacks from the LOW domain). This ensures that information cannot flow from the domain with HIGH label to the domain with LOW label, but allows for information flow in the other direction. It can be extended to multiple security labels as long as they form a lattice. In this work, we propose a technique that assures multi-way non-interference in NoCs with low overhead on latency to allow for verification of high assurance systems such as those in aerospace and automotive systems.

QoS in Network-on-chips Techniques for achieving NoC quality-of-service guarantees have been proposed based on solutions to analogous problems in macro-

scale networks. These approaches for the most part attempt to limit the rates of each flow [32, 33, 50, 34]. However, quality-of-service guarantees are known to be not sufficient for timing channel protection [89]. Optimizations that allow flows to go over their designated rate when uncontended and the lack of fault containment is problematic for high assurance systems [72] because of the high cost of any unaccounted variation in such systems. The time division approach proposed here provides for both fault containment and timing channel elimination.

Security in NoCs Security in NoCs has been studied from several aspects that focus on specific attack mitigations such as defending against denial-of-service (DoS), battery-draining attack [26] and maintaining access control of specific memory region in shared memory systems [26, 69], and buffer overflow attacks [55, 56]. Gebotys and Zhang have focused on confidentiality by providing encryption techniques for data transmitted over the NoC in a SoC setting [28]. Availability is handled in the Tile64 iMesh networks by separating (and in fact physically separating) the network accessible by user applications from the network used by the OS and IO device traffic [92]. Our scheme can protect against DoS and bandwidth depletion attacks between domains because of the static time allocation to different domains.

Non-interference in NoCs Non-interference in network-on-chips has been studied in the system-on-chip domain to provide composibility and fault containment as well as time-predictability for real-time performance guarantees [38, 65]. Composibility means that the system can be analyzed as a set of independent components which allows for easier verification of the overall system without having to verify all possible interleavings of events in the system. This has been specially critical in high assurance systems that requires very high level of verification because of safety ramifications of the system. Æthearal proposed a timedivision multiplexed (TDM) virtual circuit switching network to provide guaranteed services (GS) for performance critical applications with real-time deadlines and a packet switched best-effort (BE) network for applications with less requirements [29]. A lighter version that only provides GS was proposed to further simplify routers [79, 37]. More recently, Stefan and Goossens proposed a modification on Æthearal that enables multi-path routing both static and dynamic (based on a true random number generator) in order to enhance the security by using nondeterministic path instead of source routing used in Æthearal [80]. In addition, the need for real-time worst case execution time (WCET) analysis inspired a set of work, such as, the T-CREST project which tries to build a time-predictable multicore for real time applications. They proposed a integer programming technique

to minimize the length of static schedule of all-to-all circuit switching connections in a TDM way [75].

Regarding packet switching networks, Avici TSR network [21] uses separate virtual channels for each destination in the network but packets destined to different locations share physical channels. Under saturation, physical channels are allocated fairly, but destinations can go over their fair share when the network is not saturated which can leak information by detecting the variation of bandwidth a certain node receives.

To the best of our knowledge, our scheme is the first to provide a packetswitched network that can guarantee two-way (or multi-way) non-interference and timing channel protection in a way that is both a) provable down to the gate-level implementation and b) provides low latency overhead.

#### 2.2 SurfNoC Architecture

#### 2.2.1 A Motivating Example

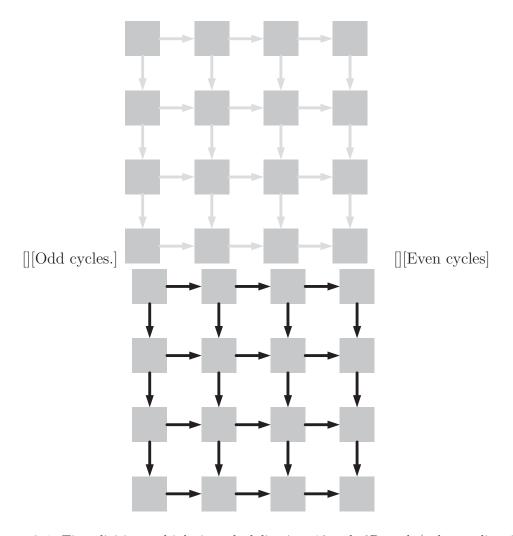

Consider the 16-node half mesh network (channels are drawn in one direction left-to-right and top-down for illustration purposes) in Figure 2.1, assuming that even nodes belong to domain 0 and odd nodes are part of domain 1. A straight forward way to support non-interference is by partitioning the virtual channels and

time-multiplexing the physical channels and crossbars between different domains such that channels are only allowed to propagate packets from domain 0 (black) on even cycles and packets from domain 1 (grey) on odd cycles (assuming a single cycle routers) as shown in Figures 2.1 and 2.1. This time-multiplexing scheme ensures that the latency and throughput of each domain is completely independent of the timing of the other domain's load. However, this baseline scheme means that packets will have to wait an extra cycles at each hop. Even worse, as we scale the number of partitions from 1 to D, assuming a single-cycle router each packet will have to wait D-1 cycles per hop. This is an expensive price to pay, and one that continues to get worse the further away you attempt to communicate. If we want to hold on to non-interference, we will still need these strict time-varying partitions, but by changing the phase of their oscillations we can dramatically reduce the latencies involved.

A better schedule for time-multiplexing will make sure that domains wash over the network as a wave, such that each dimension appears to be "propagating" one domain in a pipelined fashion. Figure 2.1 shows a simplified view of this point. Every link still rotates evenly through domain 0 and domain 1, but if we consider the top row in Figure 2.1, we can see alternating channels (grey, black, grey). In the next cycle (shown in Figure 2.1, the channels used to propagate packets from domain 0 (black) will carry packets from domain 1 (grey), and vice versa. Before entering the network, the packet waits in the injection port until its domain's turn. The schedule ensures that when the packet is ready to egress the router that there will be no delay waiting its domain's turn at the downstream router. The only exceptions to this rule are when a packet needs to change dimensions (such as when the packet turns from traveling along the X dimension to the Y dimension) and when there is contention from packets in the *same* domain.

As an optimization, we constrain our schedule such that two directions of the router propagate packets from the same domain at the same time. For example, the top-left router in Figure 2.1 propagates packets from domain 0 (black) both to the right and down. In this case, any packet which is sent in a downward and/or rightward direction will only have to wait to enter the network and will have no additional waits during turns between dimensions (again, unless there is intra-domain contention). Of course this example is very simple as it has only two domains, even divisions, and does not consider the latency of the network routers. In the next section, we will show how to devise detailed strategy for k-ary n-cube meshes and tori networks and discuss how non-interference can be shown at the level of an implementation.

### 2.2.2 SurfNoC Scheduling

The most basic routing algorithm in meshes and tori is dimension-ordered routing. That is, a packet walks through a dimension until it cannot move further without going farther from the destination and then transfers to an other dimension. Thus, routing is linear in each dimension which provides an opportunity to reduce wait time between hops. This way packets will only have to wait when they enter the network from the injection channel and when they change dimensions. We will describe this idea in details in the rest of this section.

The straightforward way to support time-division multiplexing is to operate the whole network in time slices that are divided between application domains. That is a packet waits at each hop until the network is forwarding packets from that its domain. This approach leads to a zero-load latency  $L_0$  that is proportional to the number of application domains D, pipeline depth P, and the number of hops H, as shown in Equation 2.1. This solution might work efficiently for a small number of domains such as 2 to 4 domains but in high assurance applications as many as tens of domains can be found [72].

$$L_0 = HP(D-1) (2.1)$$

Building on the technique we developed in the motivating example, we propose SurfNoC scheduling in which different routers (and in fact different ports of the same router) can forward packets from different domains at the same cycle. In this schedule, a packet waits until it can be forwarded in one dimension (i.e. its output channel is forwarding packets from its domain at this cycle) and then does not experience any wait at any downstream router in this dimension (assuming there is no contention from packets from the same domain) in a way similar to the schedule developed in the half-mesh example. After finishing the first dimension, the packet may experience another wait until it can be forwarded on the next dimension. We call this schedule Surf scheduling because a packet is like a surfer who waits to "ride" a wave until some location and then waits to "ride" another wave. In this analogy, waves are dimension pipelines. Equation 2.2 shows that maximum zero-load latency and clearly shows that the overhead is additive not multiplicative as in the straightforward way. The term (n-1+2) comes from n-1 transitions between dimensions and 2 waits during injection and ejection. It is worth noting that this is the maximum wait not the typical one as the schedule may require less wait.

$$L_0 = HP + ((n-1)+2)(D-1)$$

(2.2)

The way to implement these different "waves" is by scheduling different directions in a router independently; an idea inspired by dimension-slicing used in dimension-ordered routing in meshes and tori. We used what we call directionslicing of the pipelines, such that each direction has its own pipeline. This pipeline is a *virtual* one going through different routers (not in the same router). We will describe this idea in the case of a 2D mesh or torus.

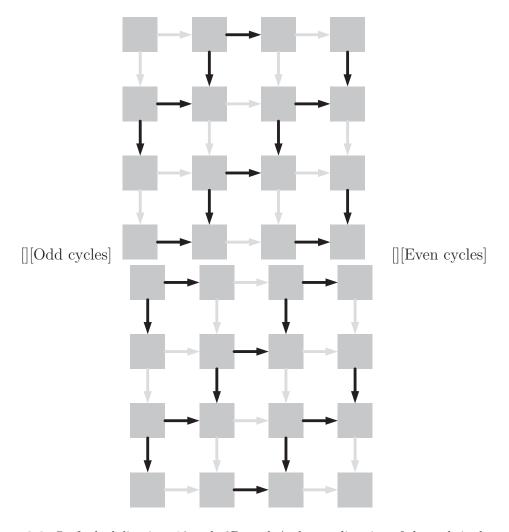

In a 2D mesh or torus, each dimension has two directions (E and W for the x-dimension; N and S for the y-dimension). The pipelines of directions of the same dimension (i.e. N, S and E, W) are running in opposite ways as shown in Figure 2.3. In this technique, each port of a router is scheduled independently of all other ports in a pipelined way such that the downstream router in the same direction will forward packets from the same domain after P cycles where P is the pipeline depth of the router. These schedules are imposed on output channels of each router to avoid timing channels based on contention in the allocator (as detailed in the next section).

Figure 2.3 illustrates an example of 16-node 2D mesh schedule of 3 domains (colored white, grey, black). There are two waves south-east (SE) (as the one shown in Figure 2.2 and north-west (NW) running in the mesh. Each channel propagates packets according to the following schedule (white, white, gray, and black) and repeats. It is worth noting that using such a schedule results in half of the bandwidth being allocated to the white domain, whereas the black and grey domains guarantee only a quarter of the bandwidth for each of them. This illus-

trates the benefit of our schedule in statically assigning non-uniform bandwidth allocation to domains.

packet ordering and deadlock freedom

# 2.3 SurfNoC Router Micro-architecture

The micro-architecture of the SurfNoC router has two main goals:

- Ensuring a timing channel free contention between packets, i.e. contention

can occur between packets from the same domain and not between packets

from different domains;

- 2. Scheduling the output channels of each routers in a way that maintains the surf schedule across the whole network;

In order to achieve these two goals, we used a dynamic number of virtual channels that are partitioned between domains independent of load (§2.3.1). We analyzed the VC allocator and switch allocators to make sure they are timing-channel free (§2.3.2). The scheduling of output channels is done through masking requests to the switch allocator from packets until its turn for the output channel arrives in the wave pipeline (§2.3.3).

### 2.3.1 Partitioning Virtual Channels

Spatial partitioning of the queues is not a new idea [89, 21]. Static partitioning of virtual channels is done through restricting the routing algorithm so that it generates output virtual channels in the range allowed for domain of the packet. This partitioning ensures non-interference between packets from different domains while they wait in the buffers before being forwarded, i.e. eliminating the head-of-line (HOL) problem between domains.

We added support for different queue length as well as different number of queues (or virtual channels) using the same amount of storage.

#### 2.3.2 Allocators

The SurfNoC router has two allocators, VC allocator and SW allocator. We used a separable-allocator as the baseline allocator. These allocators use round robin arbiters. This may lead to timing channels if requests are allowed from different domains to the same resource. We will detail how we prevent that from happening for both allocators.

Virtual Channel Allocators The requesters of the VC allocator are packets requesting the upstream router virtual channels. The resources are virtual channels of the upstream routers. By restricting the routing circuit to only issue

requests for virtual channels that belongs to the corresponding domain, contention is guaranteed to be between packets from the same domain. Actually, we can use this property to reconstruct the VC allocator to be D VC allocators of size  $v \times v$  where D is the number of domains and v is the number of virtual channels per domain (across ports not per port) instead of one large VC allocator of size  $V \times V$  where V = D.v. This design can help save power by power-gating some of these allocators if the number of required domains is less than D for a certain application. Figure 2.5 depicts an example of  $3 \times 3$  VC allocator and illustrates the rational behind the non-interference support in the VA stage as well as the optimization of separate D allocators. This also shows that we can use any arbiters or allocator design for VC allocation because it is intrinsically interference-free.

Switch Allocator The SW allocator assigns output ports to virtual channels. Since any virtual channel can request any port, we cannot apply the same technique we used for the VC allocator of dividing the allocator into separate smaller allocators. Another problem arises from the fact that switch ports are shared among virtual channels from different domains (as shown in Figure 2.3.2) which means that requests to the switch can be denied if two VCs (belonging to two different domains) on the same input port and requesting two legitimate (according to the surf schedule) output ports will contend on the crossbar input port

leading to one of them delayed, and thus a timing channel exists. We can solve this problem by using the input speedup parameter of the crossbar with value D, and hence no contention between domains on switch input ports. Figure 2.3.2 shows an example of such configuration.

mention the time/space trade-off in the discussion section in the end of the paper

By solving the input port request of the allocator, we can now design the switch allocator as a separable one of size  $Dp \times p$  where p is the number of ports of the router. It is worth noting that it does not matter if the allocator is input-first or output-first because of two reasons. First, an input arbiter is responsible for one input to the crossbar that is shared between VCs from the same domain. Second, by using dimensional order routing and the surf scheduling, a VC can request only one output port. Requests to an output port are masked using the scheduler state so that only requests from the domain which owns the current time slot reaches the allocator (i.e. no contention between different domains can happen in the output arbiter).

#### 2.3.3 Scheduler

The scheduler is a set of p tables each indexed by a counter, one for each router output port. The initial state of the counter is pre-determined at design time in

order to enforce the surf schedule. The number of slots in the tables is determined by the number of domains. The selected element from the array is used as input to a decoder. The decoder output is used to mask requests to the switch allocator as shown in Figure 2.7. If the number of domains D is greater than the pipeline depth (including channel traversal) P, the schedule table is initialized according to Equation 2.3 where  $S_{id}$  is the schedule of port i at index d, l is the location of the node in the dimension of port i, l' is the location of the node in the other dimension.

$$S_{id} = \begin{cases} ((D-P)(l+l') + d) \mod D & \text{if } i \in \{0,2\} \\ (-(D-P)(l+l') + d) \mod D & \text{if } i \in \{1,3\} \end{cases}$$

(2.3)

# 2.3.4 Pipelining and separation discussion

We have so far discussed separation regarding each pipeline stage separately but the question remains whether pipelining and pipeline stalls can cause interference or not. We will discuss each pipeline stage and the basic idea is to ensure that stalls do not induce interference between separate domains.

Buffer write and route computation (BW/RC) This stage is the first stage of the pipeline and because of credit-based flow control we are assuming, flits do not enter the router unless there is a guaranteed space in the buffer for it. Spatial

separation is ensured because VC allocation is done in the upstream router. Route computation can be done in parallel for all flits at the front of all virtual channels (waiting for RC). No interference can be caused in this stage.

Virtual channel allocation (VA) At this stage all flits send requests to the VC allocator. Using our design, interference can happen between virtual channels from the same domain but not between those from distinct domains. Stalled flits because of lack of free virtual channels (in the downstream router) prevent only flits from the same virtual channel from making progress. This can be insured by recording state in the pipeline for each virtual channel, i.e. stalls due to virtual channel allocation have to be per virtual channel (not per input port).

Switch allocation (SA) Switch allocation can fail, due to contending flits for switch ports (limited to virtual channels from the same domain), which causes stalls in the pipeline. We avoid stalling the whole port (which leads to interference between domains) by having a separate state in the pipeline stage for each virtual channel. Switch allocation can also be stalled because of lack of buffering in the downstream router, i.e. waiting for a credit. This stall effect is limited to a virtual channel and can be handled using the same way the failed SW allocation stall.

| Parameters                  | Specifications                            |  |  |  |

|-----------------------------|-------------------------------------------|--|--|--|

| Architecture                | 4*4 Torus                                 |  |  |  |

| Routing Algorithm           | Dimension order deterministic routing     |  |  |  |

| Domain count                | 2 (D0 and D1)                             |  |  |  |

| Virtual channels per domain | 2 (VC0 and VC1)                           |  |  |  |

| Number of ports             | 5 (West, East, North, South, and Self)    |  |  |  |

| Flit Size                   | 144 bits (payload-128 bits, head-16 bits) |  |  |  |

| Flow control type           | Credit-based flow                         |  |  |  |

| Input Buffer queue type     | FIFO queue of depth 4                     |  |  |  |

| Arbiter type                | Priority based round-robin                |  |  |  |

Table 2.1: Specifications of implemented design.

The key idea here is stalls can affect flits in the stalled stage and all previous stages only from the same virtual channel. Thus, we can guarantee separation because we statically assign virtual channels to domains.

## 2.3.5 RTL Implementation

Table 2.1 briefly describes the specifications of the implemented SurfNoc router design.

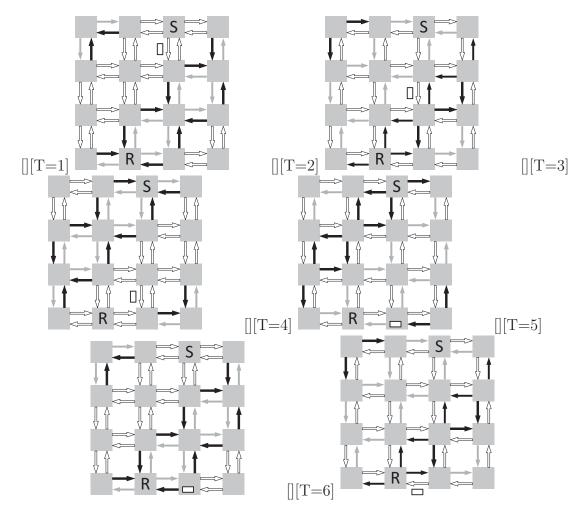

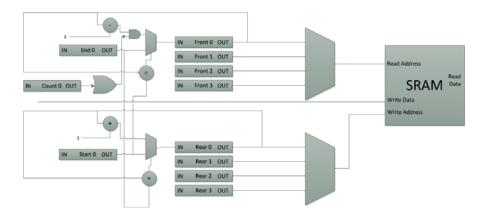

Buffer Write This stage is the first stage of the pipeline, and because we are assuming a credit-based flow control, flit do not enter the router unless there is a guaranteed space in the buffer for them. Buffers are implemented as circular FIFO queues where the incoming flit is queued when it arrives from one of the input ports. There is one buffer queue for each virtual channel. Buffer unit selects one of the virtual channel buffers to queue the flit. This decision is made entirely using

the source router ID, destination router ID, the current router ID, and the surf schedule. The flits wait in the buffers to be processed by the route computation (RC) unit. The flits are de-queued from the buffer when the crossbar sends out flits to the downstream routers.

In our implementation, we used five ports, two domains, and two virtual channels per domain. Hence, there were total of twenty virtual channels across all the ports. The domain of the flit was selected based on the surf schedule and the virtual channel was selected based on whether there was a need to take the wraparound link. Wraparound link is taken when the path to the destination router is shorter through the wraparound link as compared to the normal link. Virtual channel, VC0 was used when there was no need of wraparound links. However, if the router selected the wraparound link, VC1 was used for routing to avoid the deadlock condition and hence, the flit was queued into the VC1 of the selected port and domain.

Figure 2.8 gives an example of buffer write operation. The upstream router sends flit from domain 0s virtual channel-0 buffer. The current router receives the flit at its west port. There are four possible buffers corresponding to each domain and virtual channel. However, the control logic extracts information about the source ID and destination ID from the flit and puts the flit in the west ports

domain-0 VC-0 buffer (at location pointed by tail pointer). The tail pointer increments and points to next location in the queue.

Credit Table Since we are using a credit-based flow control, the buffer unit maintains a credit table that stores the number of buffer space available in the downstream routers for each virtual channel buffer. The router can de-queue the current routers buffer and send out the flit from one of the output ports only when there is at least one buffer space available in the downstream router. The router stalls if there are no credits available for the downstream routers virtual channel buffer. Credit table is not maintained for the port connected to the processor are the flits are sent to the processor if it is ready to accept the flit. A valid signal is kept that tells if the processor is ready to accept the flits. The router looks for this signal and sends out the flit only when the signal is set.

The credit count of the credit table is incremented and decremented based on the credit in and credit out signals. The current router sends out credit out signal to the upstream router when a flit is de-queued from the current routers virtual channel buffer to indicate that a space is emptied in the current router. The upstream router in turn increments the credit count upon receiving this signal. Similarly, when the downstream router sends out flit from one of its virtual channel buffer, the current router receives credit in signal from the downstream router and it increments the credit count for that virtual channel buffer. Figure 2.9 illustrates the above description of credits flow and the result of flit transfer on the credit table count.

Route Computation As we implemented deterministic dimension order routing, a flit first travels in east/west dimension until it reaches the destination column (router); then, it changes dimension and travels in north/south dimension until it reaches the destination row (router). If the routing distance from current router to the destination router is equal from two paths, the deterministic routing always selects the path which does not have wraparound link in order to avoid any dependency that might arise if the decision is made on fly. RC unit processes the current flit (pointed by head pointer) in the buffer queue and if the flit type is head or head-tail, it computes the output port and output virtual channel for routing. In other words, RC unit computes the route on per packet basis (not per flit). Also, similar to the buffer unit, RC unit computes the route that is based entirely on the source router ID, destination router ID, and the current router ID. After selecting the output virtual channel for the route, RC unit sends this request to the VC allocator unit to actually allocate the output virtual channel for a packet Figure 2.10.

When the RC unit takes a flit from the buffer, it already knows the domain of the flit because there are separate buffers for each domains virtual channels. Because the output port and domain are known, the RC has only two choices of output virtual channels for the selected domain and the output port. In our implementation, because there are two virtual channels for a domain, there are only two choices of output virtual channels, VC0 and VC1. RC unit selects either VC0 or VC1 based on the need of taking the wraparound link. Wraparound link is taken when the path to the destination router is shorter through the wraparound link as compared to the normal link.

Virtual Channel Allocation The VC unit performs the function of arbitrating between the 20 input virtual channels for allocating the 20 output virtual channels. The inputs to the VC unit are 20 requests from the input virtual channels, each request holding the 5 bit ID of the desired output virtual channel, as computed by the RC unit. For each output virtual channel, a 20-bit vector is extracted from these inputs. In this vector, each bit is set if the corresponding input VC requests that output VC. This concept is shown in Figure 2.11. These vectors are then rotated based on a round-robin scheme that ensures fairness in arbitration. Here the zeroth bit of the vector gets the highest priority and the nineteenth bit gets the lowest priority. In every round of arbitration, original vector is rotated a

number of times such that the request that was granted in the previous round is pushed to the nineteenth bit. Thus the request that is granted the output virtual channel in the current round of arbitration gets the least priority in the next round of arbitration. After the rotation, a priority allocator is implemented that allocates each output virtual channel to the highest priority requester which is the first valid request starting from the zeroth bit. Once an output VC is allocated, its state is changed to 'BUSY'. The output VC is freed (status changed to 'FREE') when the switch allocation unit sends an acknowledgement that the outgoing flit is the tail flit of the current packet. Thus, an output VC is allocated when the head flit of a packet is encountered and is held by the same packet/input VC till it forwards all its flits. The outputs of the VC unit are the 5-bit input VC IDs that have been granted the 20 output virtual channels and a 20-bit 'VC\_alloc\_done' vector in which each bit is set if the corresponding output VC is busy.

Switch Allocation The primary role of the switch allocator is to allocate the five output ports among the 20 output virtual channels. Additionally, it also sends out the tail flit acknowledgement signal for the other units, whenever the flit that is going to be forwarded on an output port is a tail flit. The main difference between the virtual channel arbitration and switch port arbitration is that the former is on per-packet basis, whereas the latter is on per-flit basis. Thus, the SA

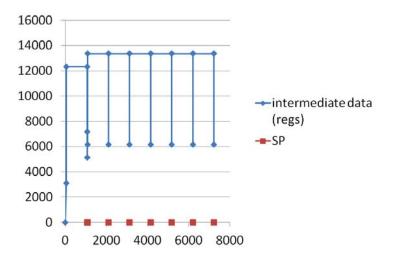

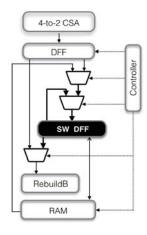

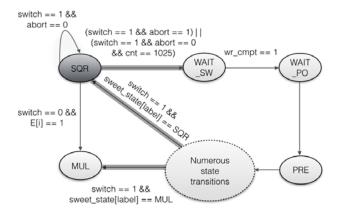

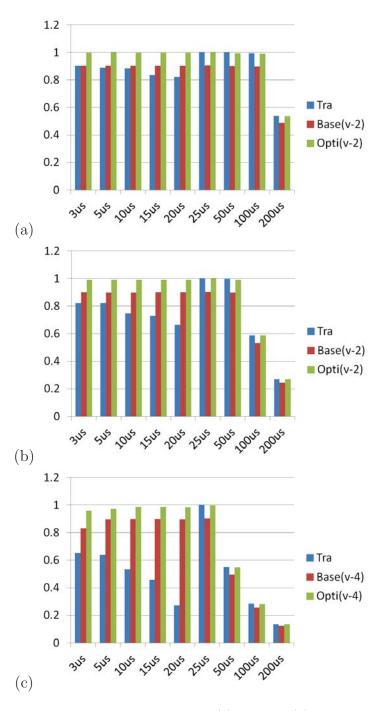

unit performs the arbitration for the output port on every clock cycle. In other words, it does it for each flit based on the SurfNoC schedule. At a given clock cycle, there can be contention between packets of same domain only, as per the SurfNoC schedule. So, for every output port, the SA unit checks the schedule and allows only valid requests to contend for the output ports. A request is realized as valid if there is a credit available in the corresponding downstream router and if the flit belongs to the right domain. Again, the output port is granted to one of the valid requests based on a round robin scheme. The inputs to this unit are the input VC IDs that have been granted the 20 output VCs and the credit table information from the buffer unit. The outputs are the 5-bit input VC IDs that have been granted each of the five output ports and the 20-bit tail flit acknowledgement signal (Figure 2.12).