### UNIVERSITY OF CALIFORNIA, IRVINE

A Fine-grain Parallel Execution Model for Homogeneous/Heterogeneous Many-core Systems

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Electrical and Computer Engineering

by

Tongsheng Geng

Dissertation Committee: Professor Jean-Luc Gaudiot, Chair Professor Nader Bagherzadeh Professor Rainer Doemer Professor Stéphane Zuckerman

© 2018 Tongsheng Geng

### DEDICATION

To my beloved parents, sister and friends For your endless love and support, without which I could never make it this far.

### TABLE OF CONTENTS

|                        |                   |                                            |                                                                    | Page                                               |

|------------------------|-------------------|--------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------|

| $\mathbf{L}\mathbf{I}$ | ST C              | OF FIG                                     | GURES                                                              | $\mathbf{v}$                                       |

| Ll                     | ST C              | OF TA                                      | BLES                                                               | vii                                                |

| $\mathbf{A}$           | CKN               | OWL                                        | EDGMENTS                                                           | viii                                               |

| $\mathbf{C}$           | URR               | ICUL                                       | UM VITAE                                                           | ix                                                 |

| $\mathbf{A}$           | BST               | RACT                                       | OF THE DISSERTATION                                                | xi                                                 |

| 1                      | Intr              | oduct                                      | ion                                                                | 1                                                  |

| <b>2</b>               | The               | Code                                       | let Abstract Machine and Runtime System                            | <b>5</b>                                           |

| 3                      | Exp<br>3.1<br>3.2 | Introd<br>Metho<br>3.2.1<br>3.2.2<br>3.2.3 | g Fine-Grain Event-Driven Multithreading<br>luction and Motivation | 8<br>8<br>10<br>10<br>15<br>16<br>20               |

|                        | 3.3<br>3.4        | 3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5  | A More Realistic Stencil-based Computation: LULESH                 | 20<br>23<br>24<br>24<br>26<br>32<br>33<br>37<br>37 |

|                        | 3.5               | 3.4.2                                      | Other Approaches to Optimize and Parallel Stencil Computations     | 39<br>41                                           |

| 4        | $\mathbf{Pro}$ | file-Based Dynamic Adaptive Work-Load Scheduler on Heterogeneous |           |

|----------|----------------|------------------------------------------------------------------|-----------|

|          |                | Architecture                                                     | <b>43</b> |

|          | 4.1            | Introduction and Motivation                                      | 43        |

|          | 4.2            | Background                                                       | 46        |

|          |                | 4.2.1 Heterogeneous Computing and Co-running Applications        | 46        |

|          |                | 4.2.2 Heterogeneous-DARTS Run-time System                        | 49        |

|          | 4.3            | Methodology: DAWL and IDAWL                                      | 51        |

|          |                | 4.3.1 Target: Dependence-heavy Iterative Applications            | 51        |

|          |                | 4.3.2 Dynamic Adaptive Work-Load Scheduler                       | 52        |

|          |                | 4.3.3 Profile-based Estimation Model                             | 57        |

|          | 4.4            | Experiment                                                       | 61        |

|          |                | 4.4.1 Experimental Testbed                                       | 61        |

|          |                | 4.4.2 Performance Analysis                                       | 64        |

|          |                | 4.4.3 Result of Profile-based Estimation Model                   | 71        |

|          | 4.5            | Related Work                                                     | 78        |

|          | 4.6            | Observations                                                     | 80        |

|          |                |                                                                  |           |

| <b>5</b> |                | eam-based Event-Driven Heterogeneous Multithreading Model        | 82        |

|          | 5.1            | Introduction and motivation                                      | 82        |

|          | 5.2            | Streaming Program Execution Model (SPXM)                         | 84        |

|          |                | 5.2.1 Two Levels Parallelism and Data Locality                   | 84        |

|          |                | 5.2.2 Streaming <i>Codelet</i> Model                             | 85        |

|          |                | 5.2.3 Streaming Codelet Abstract Machine Model                   | 87        |

|          | 5.3            | SPXM Design                                                      | 89        |

|          |                | 5.3.1 Streaming <i>Codelet</i>                                   | 89        |

|          |                | 5.3.2 Streaming Module ( <i>Threaded Procedure</i> )             | 91        |

|          |                | 5.3.3 Runtime Stream Scheduler                                   | 92        |

|          |                | 5.3.4 Detailed Example                                           | 95        |

|          | 5.4            | Related Work                                                     | 101       |

| 6        | Cor            | clusions and Future Work                                         | 104       |

| Bi       | bliog          | graphy                                                           | 106       |

|          |                |                                                                  |           |

### LIST OF FIGURES

### Page

| 3.1  | A Coarse-Grain Version of a Naïve Stencil Computation. Each codelet resets           |    |

|------|--------------------------------------------------------------------------------------|----|

|      | itself if there are remaining iteration steps.                                       | 15 |

| 3.2  | A Fine-Grain Version of 2D Stencil Computation with <i>OpenMP</i>                    | 16 |

| 3.3  | A Medium-Grain Version of a Naive 5-Point 2D Stencil Computation. The                |    |

|      | computation is decomposed into several sub- <i>Codelet</i> graphs, allowing a ma-    |    |

|      | chine to hold multiple synchronization units for a better workload balance.          | 17 |

| 3.4  | A Fine-Grain Version of a Naive 5-point 2D Stencil Computation. A single             |    |

|      | TP is generated, which holds the full Codelet graph. Codelets only signal the        |    |

|      | neighbors which read and write shared rows.                                          | 19 |

| 3.5  | A Fine-Grain In-Place Version of a Naïve 2D Stencil Computation. Multiple            |    |

|      | TPs can be generated, which hold a portion of the overall Codelet graph.             |    |

|      | <i>Codelets</i> only signal the neighbors which read and write shared rows. A single |    |

|      | matrix is required.                                                                  | 19 |

| 3.6  | LULESH Compute-Sync Graph. – OpenMP version – Coarse Grain                           | 22 |

| 3.7  | LULESH Compute-Sync Graph. – DARTS version, – Balanced Compute-                      |    |

|      | Sync Tree                                                                            | 22 |

| 3.8  | LULESH Compute-Sync Graph. – DARTS version, – Unbalanced Compute-                    |    |

|      | Sync Tree                                                                            | 23 |

| 3.9  | platform A: Strong Scaling– Matrix size: $1000 \times 1000$                          | 26 |

| 3.10 | platform A: Strong Scaling– Matrix size: 3000 × 3000                                 | 27 |

| 3.11 | platform A: Strong Scaling– Matrix size: 5000 × 5000                                 | 27 |

|      | PlatformB: Strong Scaling– Matrix size: 1000 × 1000                                  | 28 |

|      | PlatformB: Strong Scaling– Matrix size: 3000 × 3000                                  | 28 |

|      | PlatformB: Strong Scaling– Matrix size: 5000 × 5000                                  | 29 |

|      | Platform A: Weak Scaling– Thread Number: 32                                          | 31 |

|      | Platform B: Weak Scaling–Thread Number: 48                                           | 31 |

| 3.17 | Platform A: LULESH on $DARTS$ , vs $OpenMP$ , children $n$ is the arity of each      |    |

|      | node in the tree, <i>i.e.</i> , the number of children a node can have in the tree   | 34 |

| 3.18 | Platform B:LULESH on $DARTS$ , vs $OpenMP$ , children $n$ is the arity of each       |    |

|      | node in the tree, <i>i.e.</i> , the number of children a node can have in the tree   | 35 |

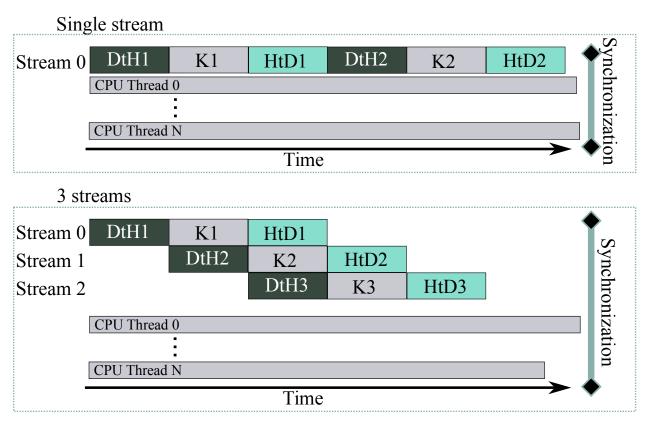

| 4.1  | Concurrent Streams overlap data transfer                                             | 49 |

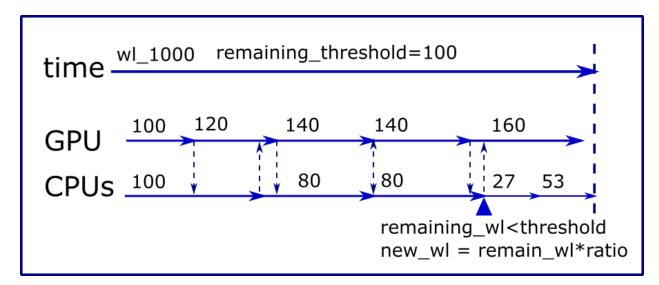

| 4.2  | Example: CPU-GPU Workload Balancing with DAWL                                        | 56 |

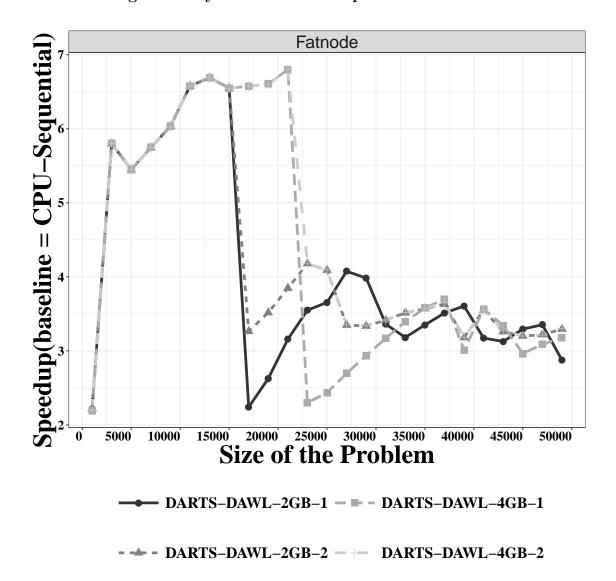

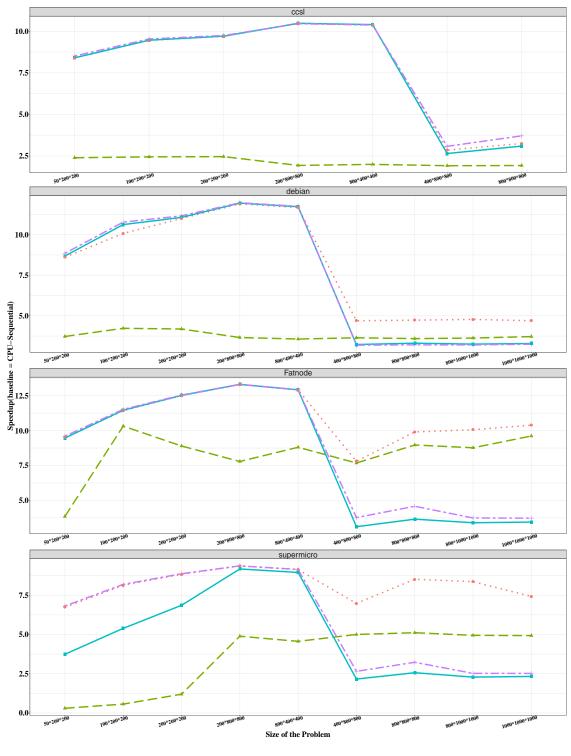

| 4.3  | 2D stencil: speed up when GPU memory is 2 and 4GB with different initial                                  |

|------|-----------------------------------------------------------------------------------------------------------|

|      | workload (GPU=CPU): $0.5 \times av_GPU$ (1) vs $2000 \times *$ (2)                                        |

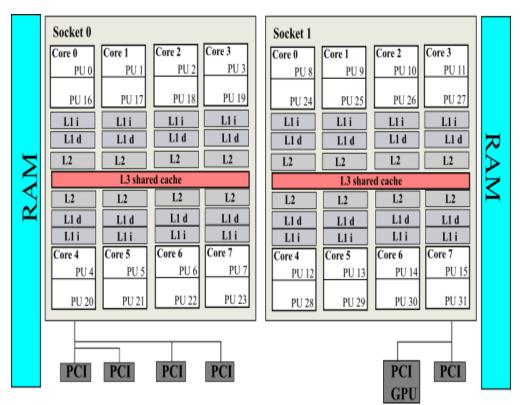

| 4.4  | fatnode topology                                                                                          |

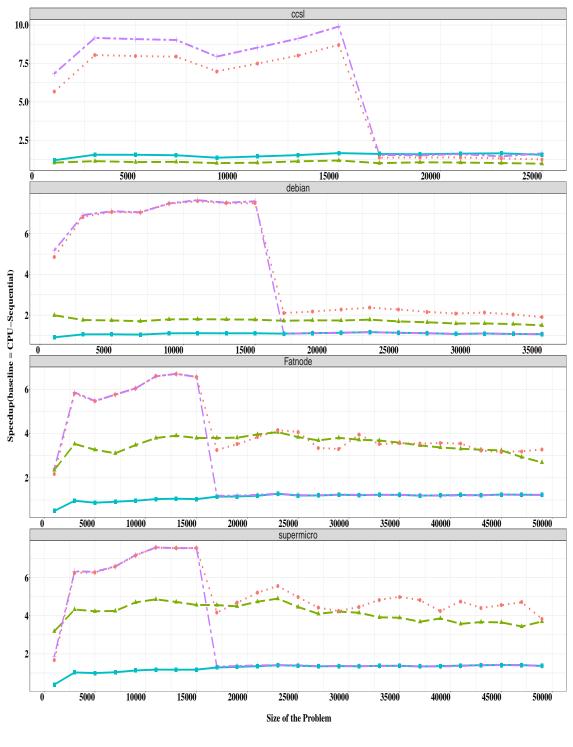

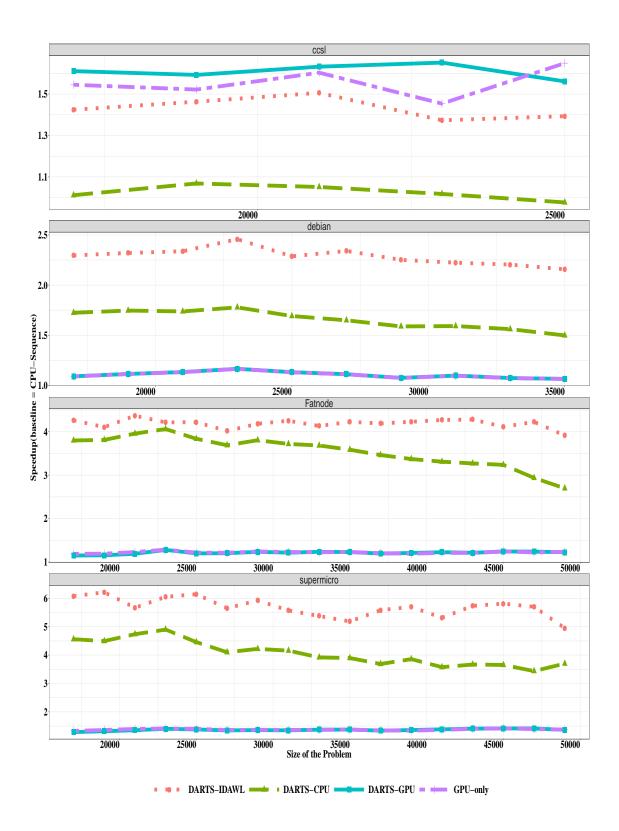

| 4.5  | 2D stencil: Speedup of the different versions                                                             |

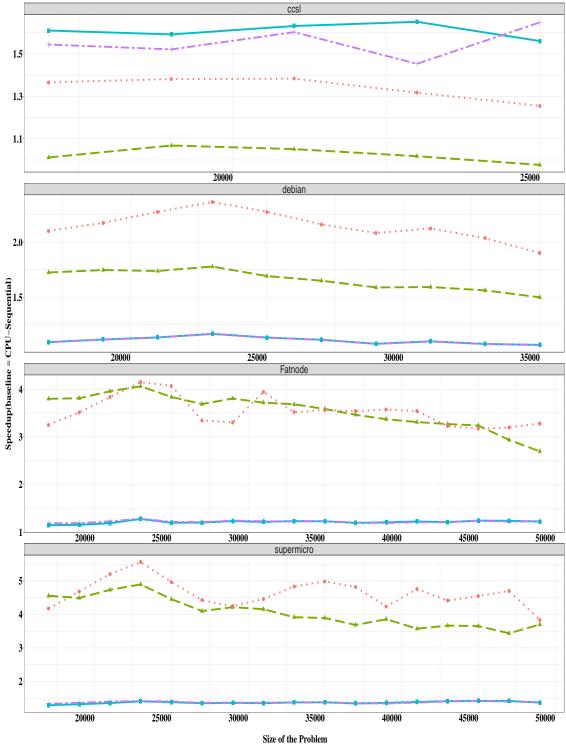

| 4.6  | 2D stencil: Speedup when matrices are larger than 17K                                                     |

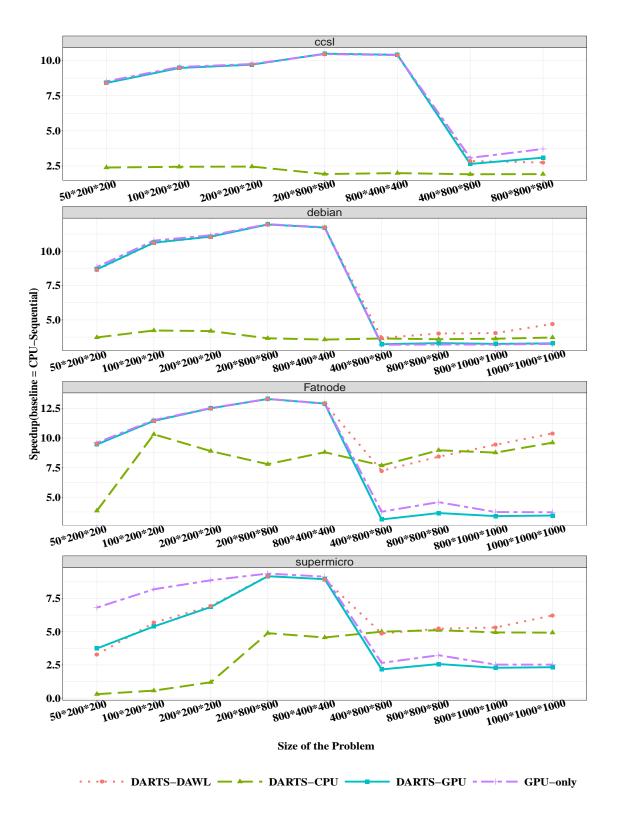

| 4.7  | 3D stencil: Speedup with different versions                                                               |

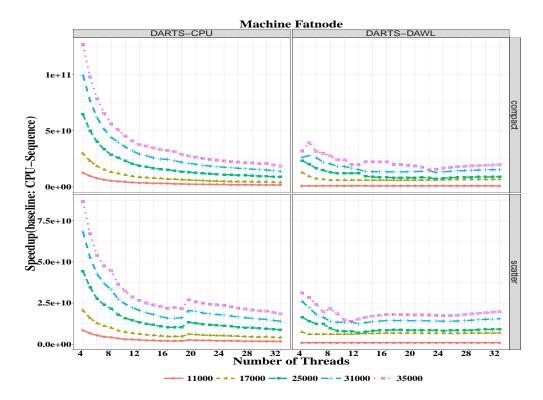

| 4.8  | 2D stencil: Performance with a varying number of HW threads on fatnode.                                   |

|      | Time in nanoseconds                                                                                       |

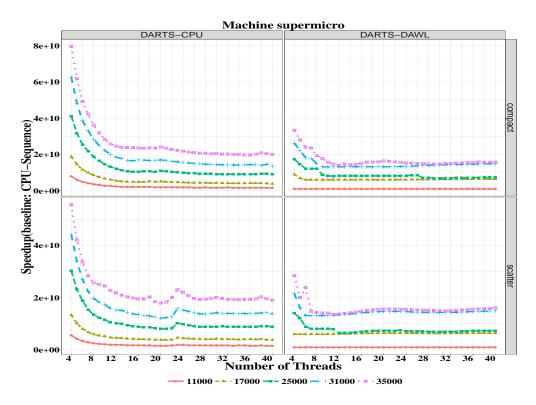

| 4.9  | 2D stencil: Performance with a varying number of HW threads on supermicro.                                |

|      | Time in nanoseconds. $\ldots$ $72$                                                                        |

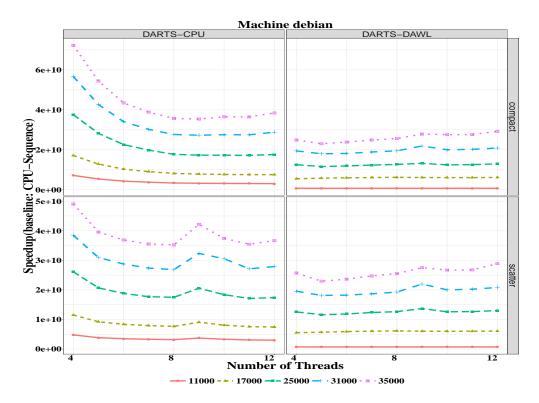

| 4.10 | 2D stencil: Performance with a varying number of HW threads on debian.                                    |

|      | Time in nanoseconds. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ |

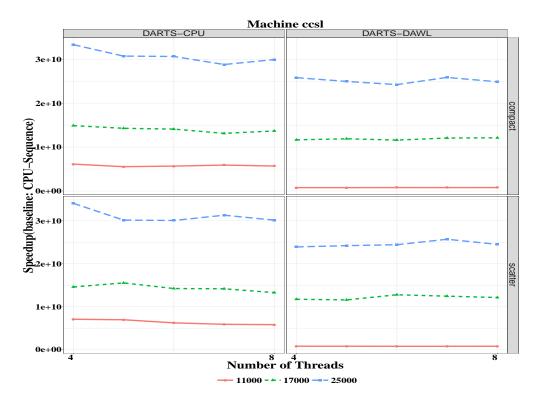

| 4.11 | 2D stencil: Performance with a varying number of HW threads on ccsl. Time                                 |

|      | in nanoseconds. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $.$ 73                                       |

| 4.12 | 2D stencil: Speedup when matrices are larger than 17K (IDAWL) 75                                          |

| 4.13 | stencil3D: speedup (IDAWL)                                                                                |

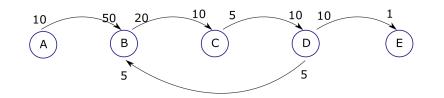

| 5.1  | sheduler: unbalanced SDFG to balanced SDFG                                                                |

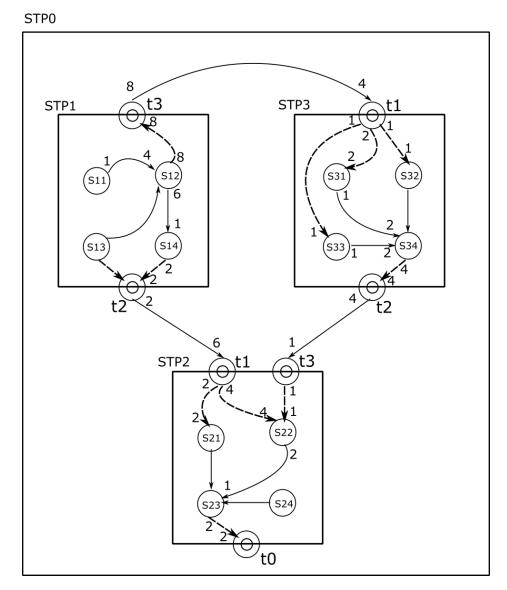

| 5.2  | Example: streaming Codelet graph $(SCG)$                                                                  |

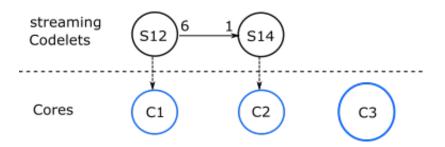

| 5.3  | mapping streaming <i>Codelets</i> to cores example                                                        |

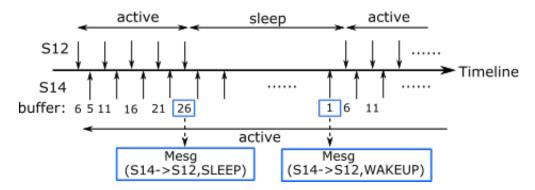

| 5.4  | message example1                                                                                          |

| 5.5  | message example2                                                                                          |

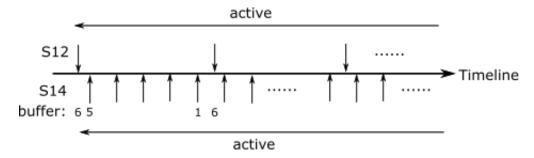

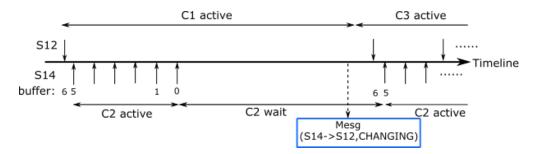

| 5.6  | message example3                                                                                          |

### LIST OF TABLES

### Page

| $3.1 \\ 3.2$ | Codelet Model macros and their meaning                                                                                                                  | 12         |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|              | Platform A features 64 GB of DRAM; Platform B features 128 GB                                                                                           | 24         |

| 3.3          | System Software Stack used for the experiments                                                                                                          | 24         |

| 4.1          | Hardware Platforms                                                                                                                                      | 60         |

| 4.2          | Software Environment.                                                                                                                                   | 61         |

| 4.3          | Stencil kernel implementation                                                                                                                           | 65         |

| 4.4          | Mean Absolute Percentage Error                                                                                                                          | 74         |

| 4.5          | 2D Stencil: Important Features for ML Estimation Model                                                                                                  | 77         |

| $5.1 \\ 5.2$ | streaming <i>Threaded Procedure</i> STPO attributes based on the Figure 5.2 streaming <i>Threaded Procedure</i> STP3 attributes based on the Figure 5.2 | $95 \\ 99$ |

| 5.3          | streaming <i>Codelet</i> S12 attributes based on the Figure 5.2                                                                                         | 99         |

### ACKNOWLEDGMENTS

First and foremost, I would like to thank my advisor Professor Jean-Luc Gaudiot, who guided me in my research and encouraged me with all his passion, patience and immense knowledge. It has been an honor to work and study under his guidance. I could not have imagined having a better advisor and mentor for my Ph.D study.

Besides my advisor, I would like to thank the rest of my thesis committee: Professor Nader Bagherzadeh, Professor Rainer Doemer, and Professor Stéphane Zuckerman for their insightful comments and encouragement, but also for the hard questions which incentivized me to expand the horizons of my research. Thanks also to Professor Tony Givargis and Professor Mohammad Al Faruque for serving on my Ph.D. qualifying examination committee.

I would like to share a special word of gratitude with professor Stéphane Zuckerman, from the Université Paris-Seine, Université de Cergy-Pontoise, for the generous sharing of his time and expertise in the course of my Ph.D study and related research. He initiated the DARTS project on which most this works is based and he spent much time passing his knowledge on to me.

I am extremely grateful to professor Alfredo Goldman, from the University of São Paulo, and Professor Sami Habib, from Kuwait University, who gave me extensive personal and professional guidance and taught me a great deal about both scientific research and life in general.

My sincere thanks also goes to professor Guang R. Gao, from the University of Delaware, who provided me with an opportunity to participate in the activities of his extraordinary multidisciplinary research group. Many thanks to the University of Delaware CAPSL research group members who granted me access to the laboratory and research facilities and provided technical support. Without they precious support it would not have been possible to conduct this research.

I thank all my fellow labmates in the PArallel Systems & Computer Architecture Lab (PAS-CAL) for the stimulating discussions, for their support during the sleepless nights we spent working together before deadlines, and for all the fun we had through the years.

Professor Gaudiot's wife, Teresa, took me under her wing and taught me so much about American culture and language. She has given me more than I could ever give her credit for here. I am immensely thankful to my "American mother."

A work of grateful acknowledgement to the National Science Foundation who supported my research under Grants No. XPS-1439165, XPS-1439097 and CCF-1763793. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the authors and do not necessarily reflect the views of the National Science Foundation.

### CURRICULUM VITAE

### Tongsheng Geng

#### **EDUCATION**

| <b>Doctor of Philosophy in Electrical and Computer Engineering</b><br>University of California, Irvine | 2018 |

|--------------------------------------------------------------------------------------------------------|------|

| Master of Science in Institute of Microelectronics<br>Tsinghua University                              | 2011 |

| Bachelor of Science in Mechanical Engineering<br>Zhengzhou University                                  | 2006 |

#### **RESEARCH EXPERIENCE**

| Graduate Research Assistant      | 2012 – 2018        |

|----------------------------------|--------------------|

| University of California, Irvine | Irvine, California |

#### TEACHING EXPERIENCE

**Teaching Assistant** University of California, Irvine **2015–2018** Irvine, California

#### REFEREED CONFERENCE PUBLICATIONS

# The Importance of Efficient Fine-Grain SynchronizationSeptember 2016for Many-Core SystemsIn Languages and Compilers for Parallel Computing-29 th International Work-<br/>shop,LCPC2016,Rochester, NY.USA, September 28-30,2016,pp203-217

#### SOFTWARE

**Fine-grain Execution Model Run-time system** https://github.com/gengtsh/darts Runtime system that implements fine-grain parallel execution execution model

### ABSTRACT OF THE DISSERTATION

A Fine-grain Parallel Execution Model for Homogeneous/Heterogeneous Many-core Systems

By

Tongsheng Geng

Doctor of Philosophy in Electrical and Computer Engineering University of California, Irvine, 2018 Professor Jean-Luc Gaudiot, Chair

Computing systems have undergone a fundamental transformation from single core devices to devices with homogeneous/heterogeneous many-cores connected within a single or multiple chips. However, while the core count per chip continues to increase dramatically, the available on-chip memory per core is only getting marginally bigger. How to successfully explore parallelism and deliver scalability is a major research issue and we have successfully attacked three main problems:

First, it is well known that, in homogeneous shared-memory many-core systems, traditional coarse-grain multithreading models are reaching their limits. We have thus proposed and designed a fine-grain event-driven multithreading execution model that will deliver the parallelism required to efficiently operate with dependence-heavy applications in shared-memory systems. By performing finer-grained and hierarchical synchronization, even "almost embarrassingly parallel" workloads can obtain large performance improvement.

Second, it has been recognized that, in heterogeneous High Performance Computing systems, the performance depends on how well the scheduler can allocate workloads to the appropriate computing devices and make communication and computation to overlap efficiently. With different types of resources integrated into one system, the complexity of the scheduler correspondingly increases. Moreover, when the applications have varying problem sizes on different heterogeneous resources, the complexity of the scheduler grows accordingly. Our proposed profile-based Iterative Dynamic Adaptive Work-Load balance scheduling approach (IDAWL) combines offline machine learning with online scheduling offers a general approach to efficiently utilize, in a dynamic fashion, available heterogeneous resources.

Finally, for those applications where the computation can be naturally expressed as streams, our Stream-based fine-grain program execution model, was developed to explore parallelism of hierarchical heterogeneous resources. It can exploit two levels (coarse- and fine-grain) of parallelism, efficiently utilizing locally available heterogeneous resources to construct streaming pipeline stages and minimize data movement to enhancing data locality.

### Chapter 1

### Introduction

Computing systems have undergone a fundamental transformation from single core devices to devices with homogeneous/heterogeneous many-cores connected within a single or multiple chips. In the past decade, The number of Processing Elements (PEs) found in generalpurpose high-performance processors has increased hundred-fold, as demonstrated by, e.q., the latest processors from Intel<sup>®</sup> and IBM<sup>®</sup>. Further, heterogeneous resources(GPUs, FPGAs, storage, etc.) are widely used in High-Performance Computing (HPC) platforms. For instance, the number of platforms of the Top500 equipped with accelerators has significantly increased during the last years [1]. In the future it is expected that the nodes' heterogeneity and count will increase even more: hybrid computing nodes mixing general purpose units with accelerators, I/O nodes, nodes specialized in data analytics, etc. The interconnect of a huge number of such nodes will also lead to more heterogeneity. Many issues must be envisioned in new software/hardware systems, including programmability, scalability, performance evaluation, and power efficiency [2]. Better performance and power consumption obtained from the use of more appropriate resources according to the computations to perform will be obtained at the cost of code development and more complex resource management. How to successfully exploit parallelism and deliver scalability is a major research issue in both Homogeneous and heterogeneous many-core systems.

In contrast to the rapid development of the hardware, the programming models and program execution models (PXMs), in the area of software parallel computing in homogeneous shared-memory many-core systems used by scientific applications, have remained mostly the same: MPI is used for inter-node communication and *OpenMP* is still favored for sharedmemory computations. However, while the *OpenMP* standard has evolved to provide ways to define fine-grain task-dependence graphs in OpenMP4 [3] and OpenMP4.5 [4], a large majority of application programmers use *OpenMP* features that are mostly related to parallel for loops, a coarse-grain style to express parallelism, *i.e.*, a programming style which requires the insertion of global barriers rather than finer-grain point-to-point synchronizations between individual threads. As long as the core count remained low in terms of sharedmemory compute nodes, global barriers were reasonable. However, this approach is not scalable: as the core count increases, the stress sustained by the memory subsystem leads to unacceptable contention on the various memory banks (both at the cache and DRAM levels). Moreover, the coarse-grain approach is still sustainable for CPU-bound workloads, but, with memory-bound applications, global barriers may kill performance due to the hardware synchronization mechanism, while high-performance based synchronization constructs rely on some sophisticated variation of busy-waiting (potentially mitigated with a sleep policy) which can hog the memory subsystem, particularly in the case of "almost embarrassingly parallel" algorithms and programs.

In heterogeneous High Performance Computing systems, the performance depends on how well the scheduler can allocate workloads to the appropriate computing devices and make communication and computation efficiently overlap. With different types of resources integrated into one system, the complexity of the scheduler correspondingly increases. Manual scheduling workloads is time-consuming, error-prone and becomes nearly infeasible for developers since any changes of hardware may render the original scheduling approach useless. A good heterogeneity-aware scheduler must leverage load-balancing techniques in order to obtain the best workload partition between CPUs and general-purpose accelerators—e.g., a GPU. Naïve heuristics may result in worsened performance and power consumption. This is particularly the case for iterative algorithms, such as stencil-based computations which require regular host-accelerator synchronizations. An unbalanced workload may cause a huge drag in performance. At the same time, stencil-based computations are at the core of many essential scientific applications: stencils are used in image processing algorithms, e.g., convolutions; partial differential equation solvers, Laplacian transforms, or computational fluid dynamics; linear algebra, the Jacobi method; etc.

Finally, streaming applications (where the computation can be naturally expressed as streams) include scientific computations, embedded applications, as well as the emerging field of social media processing. Program execution models centered on streams have been studied by many researchers and have been an active field of research for the past 30 years [5–9]. The most relevant early work on streams is the data flow execution model pioneered by Dennis [10, 11], the Synchronous Data Flow (SDF) model [12, 13] and Program Dependence Graph(PDG) model [14]. Other work include data-flow software pipelines [15, 16, 16–18]. However, these models do not address the parallelism and resources utilization problems existing in highly heterogeneous and hierarchical system. Moreover, it should be noted that core count per chip continues to increase dramatically while the available on-chip memory per core is only getting marginally bigger. This means that data locality, already a must-have in high-performance computing, will become an even critical point in streaming processing since smooth data movement will be a must in streaming processing.

The goal of this work is to propose a fine-grain event-driven parallel execution model to solve parallel computing, resource utilization and scalability issues coming with the new era of High-Performance computing. Specifically, it deals with the coarse-grain synchronization issues in homogeneous shared-memory many-core system, workload balance and streaming parallelism issues in hierarchical heterogeneous many-core system. The structure of this document is as follows. Section 2 reviews a fine-grain event-driven program execution model, abstract machine and correspondingly runtime system as background information; Section 3 proposes to demonstrate the need for fine-grain synchronization in homogeneous shared-memory many-core systems; Section 4 proposes an approach, combining offline machine learning with online scheduling, to offers a general approach to efficiently utilize, in a dynamic fashion, available heterogeneous resources; Section 5 proposes a stream-based fine-grain program execution model for streaming applications to explore parallelism of hierarchical heterogeneous resources; Section 6 concludes this work and presents the planned future work.

### Chapter 2

# The *Codelet* Abstract Machine and Runtime System

The *Codelet* Model [19] is a fine-grain event-driven program execution model which targets current and future multi- and many-core architectures<sup>1</sup>. In essence, it is inspired by data flow model of computation [20] and dynamic [21] models.

The quantum of execution is the *Codelet*, a fine-grain task that executes a sequence of machine instructions until completion and runs on a *von Neumann* type of processing element. A *Codelet* fires when all its dependencies (data and resource requirements) are met. A *Codelet* cannot be preempted while it is firing, *i.e.*, while it is executing its instructions.

Each time a *Codelet* produces data items or releases a shared resource, it signals the other *Codelets* which depend on such data item(s) and/or resource(s). Such a group of *Codelets* can be modeled as a directed graph called a *Codelet Directed Graph* (CDG) where *Codelets* are the nodes and their dependencies are the edges. In general, a given CDG statically specifies the dependencies between the *Codelets* it contains.

<sup>&</sup>lt;sup>1</sup>A short introduction is available at http://www.capsl.udel.edu/codelets.shtml.

A Threaded Procedure (TP) is a container that comprises a CDG and data to be accessed by the Codelets it contains. A TP is essentially an asynchronous function: once it is invoked, its caller resumes its execution. The TP itself can be scheduled to run anywhere in one of the clusters of the Codelet Abstract Machine, and the Codelets can run on any of the cluster's Computation Units. However, once scheduled, a TP and its content (data and code) must remain allocated in its cluster. However, individual Codelets may be scheduled for execution in any of the computation units comprised in the cluster.

The *Codelet* model relies on a *Codelet Abstract Machine* (CAM), which models a general purpose many-core architecture with two types of cores: scheduling units (SUs), which perform resource management and scheduling, and computation units (CUs), which carry out the computation. Compared to CUs, SUs have two more functions: control and synchronize all the CUs. A CAM is an extensible, scalable and hierarchy model. One cluster contains at least one SU, one or more CUs, and some local memory. Clusters can be grouped together to form a chip, which itself has access to some memory modules; Multiple chips consist of a node, and multiple nodes form a full CAM. The communication of between and within components of each level of hierarchy is done by the interconnection network.

A CAM is meant to be mapped on real hardware: the number of clusters, and computation units per cluster will be directly influenced by the actual hardware architecture on which a codelet program should be running. Further, different configurations may be used on the same target hardware, depending on the nature of the application.

The Delaware Adaptive Run-Time System (DARTS) [22–24] is a faithful implementation of the CAM. It is written in portable C++, and runs on any UNIX-based distribution. It targets shared-memory nodes. *DARTS* executes on regular multi-core chips and assigns a role to each core or thread: each processing element is either a SU or a CU. It also implements the configurable CAM, which can be configured at run-time by the user (or in code by the programmer). By default, *DARTS*'s CAM considers each socket to be a cluster, and assigns a single SU per cluster. Furthermore, there are two queues or pools, ready queue and waiting queue, to store these *Codelets*. When all the requirements of one *Codelet* are met, this *Codelet* will be moved from waiting queue to ready queue and SUs will push it to CUs ready queue to execute or execute by himself if all the CUs are busy or their ready queues are full. In specific case, to reduce data movement and utilize the data locality character, *DARTS* can pin the *Codelets* into CUs when the same *Codelets* are invoked repeatedly or periodically. *DARTS* is also extendable. Section 4.2.2 introduces *Heterogeneous-DARTS* which extend *DARTS* to support both CPU and GPU resources parallelism computing. Section 5 introduces *Streaming-DARTS* to support stream processing.

### Chapter 3

# Exploiting Fine-Grain Event-Driven Multithreading

### **3.1** Introduction and Motivation

In the past decade, the number of Processing Elements (PEs) found in general-purpose highperformance processors has increased between forty and a hundred times, as demonstrated by, *e.g.*, the latest processors from Intel® and IBM®. Further, the recent appearance of "accelerators" have reached even higher PE counts in recent years.

In the meantime, the programming models and Program execution Models (PXMs) used by scientific applications have remained mostly the same: *MPI* is used for inter-node communication and *OpenMP* is still favored for shared-memory computations. However, while the *OpenMP* standard has evolved to include finer-grain tasks with *OpenMP3* [25], and even to provide ways to define task-dependence graphs in *OpenMP4* [3] and *OpenMP4.5* [4], a large majority of application programmers use *OpenMP* features that are mostly related to parallel **for** loops, sometimes exploiting the nature of their scheduling and the size of their

iteration blocks. In turn, this approach tends to favor a rather coarse-grain style to express parallelism, *i.e.*, a programming style which requires the insertion of global barriers rather than finer-grain point-to-point synchronizations between individual threads.

As long as the core count remains low in terms of shared-memory compute nodes, global barriers is reasonable. However, it is not scalable: as the core count increases, the stress sustained by the memory subsystem leads to unacceptable contention on the various memory banks (both at the cache and DRAM levels). Moreover, the coarse-grain approach is still sustainable for CPU-bound workloads, but, with memory-bound applications, global barriers may kill performance due to the underlying hardware: on x86 machines, synchronization usually leverages the use of atomic operations, which can seriously hamper performance in a multi-core, multi-socket environment [26]. In particular, memory-bound workloads tend to tax the interconnection network which links sockets together. In general, high-performance based synchronization constructs rely on some sophisticated variation of busy-waiting (potentially mitigated with a sleep policy) which can hog the memory subsystem, as the system software designer expects contention to be low and the workload to be well-balanced—particularly in the case of "almost embarrassingly parallel" algorithms and programs. However, recent compute nodes feature a high core and hardware thread count: cores and hardware threads nowadays share more and more resources, such as functional units, caches, and DRAM banks. As a result, it could be tedious and error-prone to parallelism even "almost embarrassingly parallel" workloads with a high compute-to-memory operations ratio, such as matrix multiplication. On more memory-intensive kernels, the same problem arises, but on a larger scale. One such example is the use of partial differential equation iterative solvers for linear equation systems, in particular the application of Jacobi or Gauss-Seidel methods to a linear system by resorting to a stencil-based iterative solver: every element of an *n*-dimensional grid depends on its immediate neighbors, and potentially more remote ones. Such algorithms are used in a multitude of applications, e.g., to solve Laplace equations used in heat conduction and computational fluid dynamics solvers.

Section 3 demonstrates the need for fine-grain synchronization even in the presence of rather coarse-grained workload partitioning using a stencil-based iterative solver, 5-point 2D stencil kernel, as an example. Different variants of 2D stencil(section 3.2), including coarse-grain variants and fine-grain variants, are running on two different types of machines featuring x86 processors, with a different number of processing elements per chip, but also a different number of sockets per node. Furthermore, a realistic stencil-based computation mini-app, LULESH(Livermore Unstructured Lagrangian Explicit Shock Hydrodynamics) [27–29], is introduced in section 3.2.4 to support the idea that in a dependence-heavy context, yet with a uniform amount of work per thread, *fine-grain synchronization matters*, even in "regular" general-purpose systems.

### 3.2 Methodology: Apply Fine-Grain Parallelism

This section starts from a coarse-grain "parallel for" loop implementation of a simple, naïve 5-point 2D stencil computation expressed in *OpenMP4* and ported it to leverage the *Codelet* Model in *DARTS*. After that, Fine-grain task mechanism introduced in *OpenMP4.5* [4] and fine-grain model of *Codelet* will be described including data dependence and synchronization constructs. A realistic application, *LULESH* [27–29], will be used as an example to evaluate the differences of fine-grain and coarse-grain synchronization.

### 3.2.1 Basic Implementation of a Parallel Coarse-Grain 5-Point 2D Stencil Computation

The code presented in Listing 3.1 is a naïve *OpenMP* version of a coarse-grain multithreaded 5-point 2D stencil computation. To simplify the problem, a given number of time step instead of convergence test is considered. This version of the stencil code privatizes everything,

```

1

void

stencil_5pt(double* restrict dst,

double* restrict src,

\mathbf{2}

n_rows, const size_t

const size_t

n_cols,

\mathbf{3}

size_t

n_steps)

4

5

typedef double (*Array2D)[n_cols];

\mathbf{6}

#

pragma omp parallel default (none) shared (src, dst) \

\overline{7}

firstprivate(n_rows, n_cols, n_tsteps)

8

{

9

Array2D D = (Array2D) dst, S = (Array2D) src;

10

size_t n_ts = n_tsteps;

11

while (n_ts-- > 0) {

12

#

pragma omp for nowait

for (size_t i=1; i<n_rows-1; ++i)</pre>

13

for (size_t j=1; j<n_cols-1; ++j)</pre>

14

15

D[i][j] = 0.25 * (S[i-1][j]+S[i+1][j] + S[i][j-1]+S[i][j]

+1]);

16

SWAP_PTR(&D,&S);

17

pragma omp barrier

#

18

}

19

}

20

}

```

Listing 3.1: Naïve 5-Point 2D Stencil kernel—*OpenMP* version. Everything has been privatized, but threads can only proceed to the next time step if they all have swapped their array pointers.

so that each thread can perform all computations including pointer swapping and moving forward to the next time step. The computation itself is located in a parallel **for** loop (see line 13). There is no the implicit barrier at the end of the loop because of using **for nowait** clause, so that threads that finish processing their own iteration chunk may proceed to swap their source and destination pointers for the next time step. The only required synchronization is the global barrier (line 17) before looping to the next iteration in the **while** loop, to ensure that all threads have properly swapped their array pointers before resuming the computation.

A direct translation of Listing 3.1's code into a *DARTS* framework can be found in Listing 3.2 and 3.3. Obviously, comparing with *Openmp* version, the *DARTS* version of code is more verbose using *DARTS* runtime system API. The various keywords emphasized in bold red are macros defined to simplify the writing of *DARTS* programs. A short description of the various keywords is provided in Table 3.1. Listing 3.2 defines a Threaded Procedure(*TP*)

| Keyword                      | Description                                |

|------------------------------|--------------------------------------------|

| DEF_TP                       | Defines a new threaded procedure           |

| DEF_CODELET                  | Defines a new codelet                      |

| DEF_CODELET_ITER             | Defines a new codelet with a specific ID   |

| SYNC                         | Signals a codelet within the same TP frame |

| SIGNAL                       | Signals a codelet in another TP frame      |

| SIGNAL_CODELET               | Signals a codelet from a TP setup phase    |

| LOAD_FRAME                   | Loads the threaded procedure frame         |

| <pre>FIRE(CodeletName)</pre> | Code to run when CodeletName is fired      |

| INVOKE(TPName,)              | Invokes a new TP from a codelet            |

Table 3.1: Codelet Model macros and their meaning.

```

DEF_CODELET_ITER ( Compute, 0, NO_META_DATA );

1

DEF_CODELET

2

( Barrier, 2, NO_META_DATA );

3

DEF_TP(Stencil) {

4

// Data

double *dst, *src;

5

6

size_t

n_rows, n_cols, n_tsteps;

7

Code

11

8

Compute* compute;

9

Barrier barrier;

10

Stencil(double* restrict p_dst,

double* restrict p_src,

11

12

p_nRows, size_t

size_t

p_nCols,

13

size_t

p_nTSteps)

14

: dst(p_dst), src(p_src)

15

n_rows(p_nRows), n_cols(p_nCols), n_tsteps(p_nTSteps)

16

compute(new Compute[g_nCU])

17

barrier(g_nCU,g_nCU,this,NO_META_DATA)

18

{

19

for (size_t cid = 0; i < g_nCU; ++cid) {</pre>

20

compute[cid] = Compute{1,1, this, NO_META_DATA, cid};

21

SIGNAL_CODELET(compute[cid]);

22

}

23

}

24

};

```

Listing 3.2: Coarse-Grain 5-Point 2D Stencil kernel—DARTS version. Stencil TP definition and its associated codelets.

named Stencil and two *Codelets*, named Compute and Barrier. Compute *Codelet* is defined with default 0 dependence counts and Barrier *Codelet* is defined with default 2 dependence counts. The dependence count can be overridden when the *Codelet* is instantiated in *TP*.

The Stencil TP is essentially a C++ struct which allocates the right amount of Codelets

```

FIRE(Compute) {

1

2

LOAD_FRAME(Stencil);

3

typedef double (*Array2D)[n_cols];

= (Array2D) FRAME(dst),

4

Array2D

D

5

S

= (Array2D) FRAME(src);

6

const size_t n_rows = FRAME(n_rows),

7

n_{cols} = FRAME(n_{cols}),

n_steps = FRAME(n_steps);

8

9

10

// current codelet's ID

11

size_t cid = getID(),

12

lo = lower_bound(n_cols,cid),

13

hi = upper_bound(n_cols,cid);

14

for (size_t i = lo; i < hi-1; ++i)</pre>

15

for (size_t j = 1; j < n_cols-1; ++j)</pre>

16

D[i][j] = 0.25 * (S[i-1][j]+S[i+1][j]+ S[i][j-1]+S[i][j+1]);

17

SYNC(barrier);

\mathbf{EXIT}_{\mathbf{TP}}();

18

19

}

20

21

FIRE(Barrier) {

22

LOAD_FRAME(Stencil);

23

if ( FRAME(n_tstep) == 0 ) {

24

SIGNAL(done);

25

EXIT_TP();

26

}

27

double *src = FRAME(dst), *dst = FRAME(src);

28

29

size_t n_rows = FRAME(n_rows), n_cols = FRAME(n_cols),

30

n_tsteps = FRAME(n_tsteps);

31

Codelet *done = FRAME(done);

32

33

INVOKE(Stencil, src, dst, n_rows, n_cols, n_steps-1,

34

done);

\mathbf{EXIT}_{\mathbf{TP}}();

35

36

}

```

Listing 3.3: Coarse-Grain 5-Point 2D Stencil kernel—DARTS version. Compute *Codelet* and barrier *Codelet* definition. a new TP is invoked at each new iteration step.

for a given cluster of cores, and holds the data which the *Codelets* can access. The Compute *Codelet* proceeds to execute the stencil operation for one time step over a chunk of the data. When it is done firing, it signals the Barrier *Codelet*, which collects all the signals of all firing Computes. Barrier then proceeds to invoke a new Stencil *TP* where the source and destination arrays are swapped in the parameters list, and the time step is decreased. This variant performs poorly compared to *OpenMP* since creating a new *TP* in every time

step yields a rather high overhead which involves dynamically allocating and deallocating intermediate data structures to hold the TP frame, as well as creating a set of *Codelets* to process portions of iteration space.

```

1

FIRE(Compute) {

2

LOAD_FRAME(Stencil);

typedef double (*Array2D)[n_cols];

3

4

Array2D D = (Array2D) FRAME(dst), S = (Array2D) FRAME(src);

5

const size_t n_rows = FRAME(n_rows), n_cols = FRAME(n_cols),

6

n_steps = FRAME(n_steps);

7

8

size_t cid = getID(), // current codelet's ID

9

lo = lower_bound(n_cols,cid),

10

hi = upper_bound(n_cols,cid);

11

12

RESET(compute[cid]);

13

for (size_t i = lo; i < hi-1; ++i)

for (size_t j = 1; j < n_cols - 1; ++j)

14

15

D[i][j] = 0.25 * (S[i-1][j]+S[i+1][j] + S[i][j-1]+S[i][j+1]);

16

SYNC(barrier);

EXIT_TP();

17

18

}

19

20

FIRE(Barrier) {

LOAD_FRAME(Stencil);

21

22

if (FRAME(n_tstep) == 0 ) SIGNAL(done), EXIT_TP();

23

RESET(barrier);

24

25

for (size_t i = 0; i < g_nCU; ++i) SYNC(compute[i]);</pre>

26

\mathbf{EXIT}_{\mathbf{TP}}();

27

}

```

Listing 3.4: Coarse-Grain 5-Point 2D Stencil kernel—DARTS version. Compute *Codelet* and barrier *Codelet* definition. *Codelets* reset themselves until the last iteration step is reached.

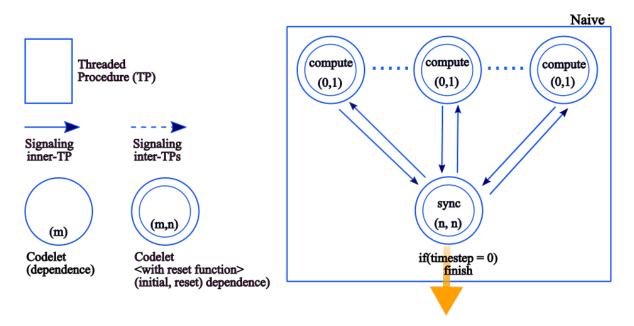

To reduce the overhead, a better version of the same coarse-grain behavior is provided in Listing 3.4. Adding RESET function to *Codelet* help reuse the same *TP* frame. The SYNC call allows a *Codelet* to signal a sibling contained within the same *TP* frame. In new version, Compute *Codelets* reset their dependence count when they are fired. Barrier signals the end of the computation if there are no more time steps, or it resets itself, and then signals Compute *Codelets*. This version is the "base" code we will be using to compare to *OpenMP* and refine in the section 3.3. Figure 3.1 illustrates this approach.

Figure 3.1: A Coarse-Grain Version of a Naïve Stencil Computation. Each codelet resets itself if there are remaining iteration steps.

### 3.2.2 Basic Implementation of a Parallel fine-Grain 5-Point 2D Stencil with *OpenMP*

The naïve *OpenMP* code leverages the regular coarse-grain fork-join execution model to parallelism code. As the loop is scheduled statically, the same *OpenMP* thread is tasked to process the same iteration chunk for each time step. Tiling method can be used to optimize the naïve code. As a result, even though as much asynchrony as possible was added to the code, there is still a need to issue a global barrier to wait between two time steps, to ensure each thread can start processing the new time step with the most up-to-date rows during the kernel's execution.

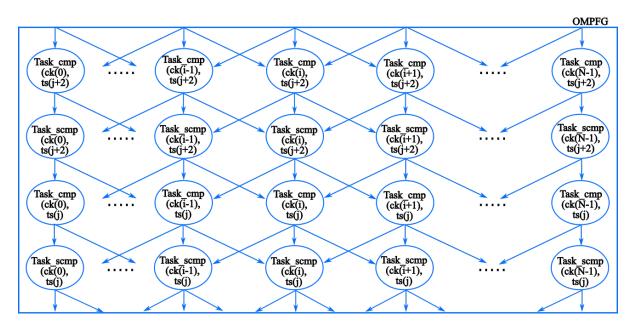

Figure 3.2 illustrates the fine-grain OpenMP4.5's tasks Data Flow Graph(DFG). OpenMP4.5 tasks directives, *i.e.*,task depends: in, task depends:out can help configure the connections between tasks. There are two types of tasks, task-comp and task-scomp. task-comp is a "regular" computing task, while task-scomp combines both a regular computation and a pointer swapping steps. ck(i) stands for  $chunk_i$  (the  $i^{th}$  iteration chunk in the loop/block

of matrix rows to process), and ts(j) stands for "time step j," the  $j^{th}$  time step in the iterative computation. The 2D stencil computation is partitioned into different chunks. Each chunk features the same number of columns and a similar amount of rows (the last chunk may feature a few more or a few less lines than the others, which mimics the way *OpenMP*'s parallel loops work). For each time step, there are different sets of dependencies to resolve, depending on which neighboring iteration chunks are being processed. Hence, task-comp for *chunk<sub>i</sub>* of time step j cannot begin computing until task-scomps of both *chunk<sub>i-1</sub>* (the "upper chunk") and *chunk<sub>i+2</sub>* (the "lower chunk") finish computing at time step j - 2.

Figure 3.2: A Fine-Grain Version of 2D Stencil Computation with *OpenMP*.

#### 3.2.3 Parallel Stencil Computations Using the *Codelet* Model

This section presents the various steps which were followed to produce a parallel fine-grained version of the 5-point 2D stencil code in the *Codelet* Model. *DARTS* explicitly specify *how* parallelism is created, orchestrated, and ended. It is necessary for fine-grain synchronization control including creating *Codelets* data dependencies and scheduling *Codelets* on specific threads.

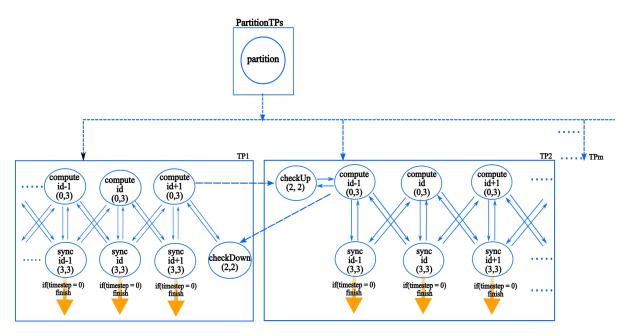

#### TP1 TPm compute compute compute compute compute compute PartitionTP (0,1) (0,1) (0,1) (0,1) (0,1) (0,1) partition syncTPs (m,m) sync sync (n, n) (n, n) if(time<mark>s</mark>tep fi<mark>n</mark>ish

### 3.2.3.1 Distributing The Computation Over Multiple Clusters In The Codelet Abstract Machine

Figure 3.3: A Medium-Grain Version of a Naive 5-Point 2D Stencil Computation. The computation is decomposed into several sub-*Codelet* graphs, allowing a machine to hold multiple synchronization units for a better workload balance.

As described in section 2, DARTS, by default, maps each single socket to a CAM's cluster of cores comprising one SU as control element and a serial of CUs as processing elements. As a consequence, parallelism is inherently hierarchical in this setting. Programming *Codelet* applications thus leads to building "natural" hierarchical barriers. The new naïve version with **RESET** function, shown in Listing 3.4 and Figure 3.1, is faithfully implementing one SU *CAM*. However, this configuration centralizes all *Codelet* graph creations onto a single processing element. This has several drawbacks. First among them, it effectively forces all cores to issue an atomic operation on the same memory location, thus forcing the serialization signals when a time step has been achieved. Second, it prevents the system from performing load-balancing when needed. To ensure a better load-balancing on a multi-socket sharedmemory node, it is preferable to map multiple clusters from the *CAM*, each with its own SU.

The way shown in Listing 3.3 partitions the *Codelet* graph into sub-graphs, each contained within its own TP, and each confined to a given cluster of cores, hence maintaining local-

ity. To avoid paying the overhead cost of dynamically allocating and deallocating *Codelets* array when create new *TP* in each time step, mentioned in section 3.2.1, the same array of *Codelets* is passed from invocation to invocation: the *Codelets* are created only once the first iteration step has been started and destroyed only once the last iteration step has been reached. Figure 3.3 provides a high-level view of the resulting *codelet* graph. This results in a somewhat *medium-grained* version of the stencil computation, shown in section 3.3.

#### 3.2.3.2 Toward a Finer-Grain Approach

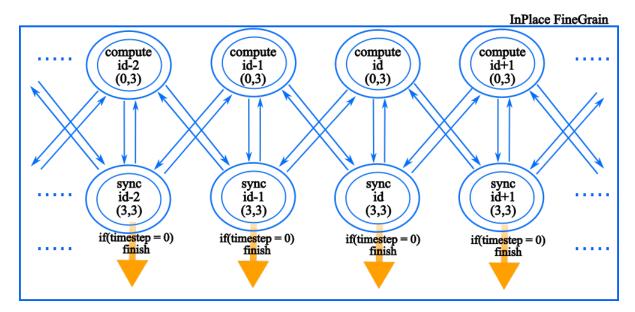

The goal is to allow portions of work to proceed with the next iteration step, as long as the shared rows they require to update their portion of the matrix are available. To make it simple, new version of code is still still decomposing the work along the rows of the matrices. However, each *Codelet* simply signals its neighbors when it is done updating the rows they depend on to move to the next iteration step. Hence, some *Codelets* may proceed to update the system at step  $S_{t+1}$  while others are still finishing step  $S_t$ . Figure 3.4 provides a diagram of the resulting *Codelet* graph where only one *TP* is created to hold the whole *Codelet* graph, where all dependencies are statically determined. The stress on the memory subsystem is not expected to be excessive, however, since signals are now only sent between "neighboring" cores.

#### 3.2.3.3 Reducing the Stencil Computation's Footprint

To reduce the memory footprint of the computation, instead of systematically using two matrices to iterative compute new values at each time step (subsequently requiring to exchange array pointers), it is possible to allocate a small buffer per *Codelet* in each invoked TP. Each buffer must be large enough to hold a set of at least three full rows in the matrix. As a result, The original naive loop thus becomes more complex, as each *Codelet* must

Figure 3.4: A Fine-Grain Version of a Naive 5-point 2D Stencil Computation. A single *TP* is generated, which holds the full *Codelet* graph. *Codelets* only signal the neighbors which read and write shared rows.

Figure 3.5: A Fine-Grain In-Place Version of a Naïve 2D Stencil Computation. Multiple *TP*s can be generated, which hold a portion of the overall *Codelet* graph. *Codelets* only signal the neighbors which read and write shared rows. A single matrix is required.

now first write the new values of the system to its local buffer first, then must write the newly updated row(s) back to the original matrix. However, this scheme lends itself well to fine-grain synchronization. Indeed, as Figure 3.4 only features TPs, Codelets, and their

dependencies, but not the actual code or data that are held in the TP frames, then it is also an adequate representation of an "in-place" version of a fine-grain version of an *n*-point stencil computation. However, this version suffers from the same limitation as the previous fine-grain variant: it requires to invoke a single TP, thus forcing the CAM to be mapped with a single SU for the whole machine, and, in turn, to accept that all TP creations will involve a potentially heavy serial step. Note also that since this implementation requires to allocate enough space for three full rows of the original matrix, there is no guarantee these buffers will fit in individual core's L1 data caches, or even L2 caches.

Hence, a final refinement is to allow for the distribution of the fine-grain "in-place" variant over multiple *TP*s. While the previous variants, including the initial fine-grain one, were relatively easy to implement, this specific implementation requires some careful coding when setting up the overall *Codelet* graph, as *Codelets* will reset themselves and signal each other not only within the same *TP* frame, but also across frames. However, the basic structure remains the same, and it clearly can be automated by a compiler. The resulting *Codelet* graph is shown in Figure 3.5. In this last variant, each *Codelet* graph features three types of *Codelets*: Compute performs the actual computation, as before. The CheckDown and CheckUp *Codelets* are signaled when rows shared by "upper" and/or "lower" neighbors are ready to be updated. In turn, they also signal other compute *Codelets* to let them know that the rows they are sharing with their neighbors are cleared for reading. Note we elected to partition the matrices row-wise to keep the case study simple, but further partitioning (along both rows and columns) would follow the same principles.

#### 3.2.4 A More Realistic Stencil-based Computation: LULESH

Livermore Unstructured Lagrangian Explicit Shock Hydrodynamics, or LULESH, is a "proxy app," *i.e.*, an application that is representative of a more complete and more complex type

of application currently in use in national laboratories all over the world and in particular in the US. Specifically, such applications are used to model deformation events, and in the particular case of LULESH, the Sedov blast wave problem for one material in three dimensions. It is a hexahedral mesh-based physics code with two centerings, Nodal centering and element centering, and time simulation constraints [27, 29]. As with all other "proxy" (or "mini") applications published by US national laboratories, the implementation prioritizes clarity over optimization. As a result, while the application is representative of more complex (and more complete) shock hydrodynamics currently deployed in production in various laboratories, *e.g.*, in terms of computation steps, data movements, *etc.*, it lacks many of the optimization that can be found in production-level implementations.

Well known code transformations, such as tiling, loop fusion, or loop distribution, is not the purpose of this section. The impact of transitioning from a coarse-grain implementation of the code toward a fine-grain one, and, in the context of this mini-app, how much performance can be hoped to be gained when "drowned" within a more complex application environment is the interesting part.

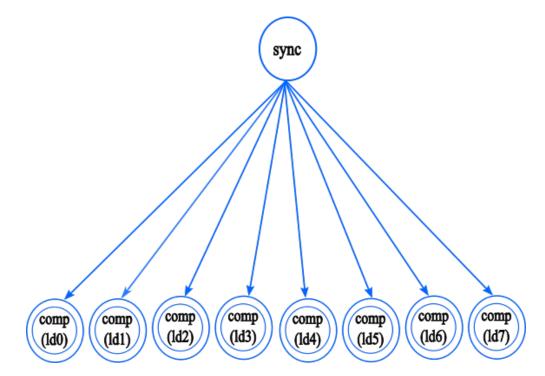

The "official" LULESH application [29] uses *OpenMP*'s coarse-grain synchronization constructs, as shown in Figure 3.6. For example, the Nodal centering function, one of most time consuming functions of LULESH, copes with all nodes' kinematics value such as force, acceleration, positions, velocities *etc*. The synchronization barrier will be used for every kinematics value calculation. The synchronization cost is proportional to the number of nodes.

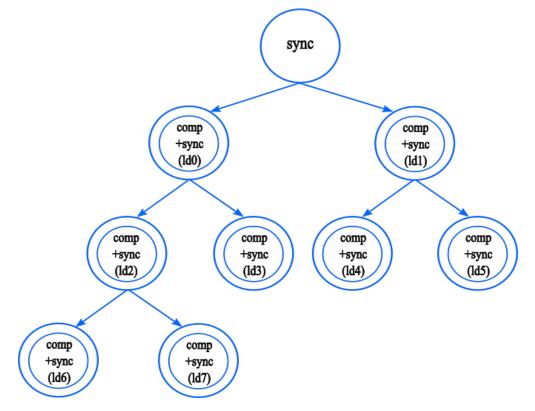

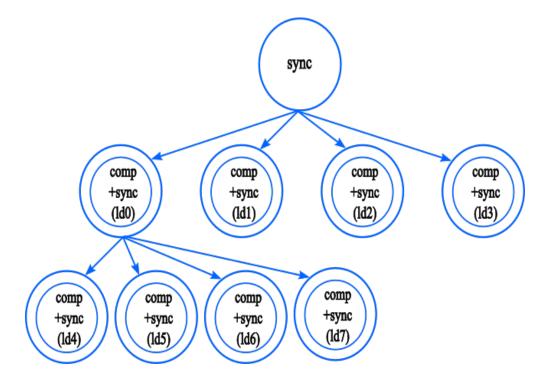

To avoid global barrier, a tree barrier approach can be used to control synchronization granularity. The tree can be balanced or unbalanced for a given arity k. The tree structure barrier impact the overall performance by reducing atomic operations in the overall computation. For instance, there are 8 processing elements in the hardware platform, if the arity of each node is set to 2 which ensures a balanced tree, as shown in Figure 3.7, then every

Figure 3.6: LULESH Compute-Sync Graph. - OpenMP version - Coarse Grain

Figure 3.7: LULESH Compute-Sync Graph. – DARTS version, – Balanced Compute-Sync Tree

Figure 3.8: LULESH Compute-Sync Graph. – DARTS version, – Unbalanced Compute-Sync Tree

inner code will have 2 children; if the arity of each name is set to 4, as shown in Figure 3.7, then this tree is unbalanced. There is no standard criteria to determine which type of tree is more efficient. The hardware, especially the number of available cores in one cluster, the structure of clusters and the memory hierarchy, affect the finally performance. In this tree structure, every *Codelet* fulfills two functions: computation and synchronization, excepted the root *Codelet*, which only performs synchronizations.

#### **3.3** Experiments

This section describes the results of each specific computation—naïve coarse-grain 2D stencil, fine-grain 2D stencil, and LULESH—implemented using *OpenMP* and *DARTS*. We compare the results obtained in each case.

#### 3.3.1 Experimental Testbed

|          | Processor    | #       | #       | Total | L1D   | L2    | L3    |                |

|----------|--------------|---------|---------|-------|-------|-------|-------|----------------|

| Platform | type         | Sockets | PEs per | PEs   | (KiB) | (KiB) | (MiB) | Comments       |

|          |              |         | Socket  |       |       |       |       |                |

| А        | Intel        | 2       | 16      | 32    | 32    | 256   | 20    | Private L2;    |

|          | Sandy Bridge |         |         |       |       |       |       | Hyperthreading |

| В        | Intel        | 4       | 12      | 48    | 32    | 256   | 15    | Private L2;    |

|          | Sandy Bridge |         |         |       |       |       |       | Hyperthreading |

Table 3.2: Compute Nodes Characteristics. "PE" = "Processing element." L2 and L3 caches are all unified. Hyperthreaded cores feature two threads per core. Platform A features 64 GB of DRAM; Platform B features 128 GB.

| Platform | Linux distribution | Kernel version | GCC version |

|----------|--------------------|----------------|-------------|

| А        | CentOS 7.1         | 3.10.0         | 8.1         |

| В        | Ubuntu 16.04 LTS   | 3.13.0         | 8.1         |

Table 3.3: System Software Stack used for the experiments.

The hardware platforms characteristics are described in Table 3.2. Table 3.3 provides the information related to the system software running on each compute node.Each platform offers a relatively varied system software layer, with compilers and OS kernels being slightly (or even widely) different from node to node. All experiments are run by pinning threads to a given processing element, and by setting the OMP\_PROC\_BIND environment variable to true (for *OpenMP*). *DARTS* automatically pins its work queues to the underlying processing elements. <sup>1</sup>

## 3.3.2 Experimental Protocol

Eight different variants of stencil code: Seq is the baseline and is a benchmark that runs sequentially on one CPU core; OpenMP runs the same code as Seq with added *OpenMP* directives running on all the available CPU cores; Naïve is a single TP implementation of the stencil computation, both OpenMP and Naïve are described in Section 3.2.1); OpenMPFG is

<sup>&</sup>lt;sup>1</sup>All the code is available on the Git repository: https://github.com/gengtsh/darts-heterogeneous.

the fine-grain variant which makes use of the tasking mechanisms available in OpenMP4.5, described in section 3.2.2; NaïveTPsPtr implements the same logic as Naïve, but distributes the work across several TPs, illustrated in Figure 3.3; FineGrain implements the fine-grain synchronization scheme and illustrated in Figure 3.4; InPlace's *Codelet* graph is identical to FineGrain's. However, FineGrain allocates two (dst and src) matrices, while InPlace only allocates one matrix and a small 3-row buffer within a compute *Codelet*. Hence, the synchronization logic of InPlace is more complex than FineGrain's. InPlaceTPs implements the same in-place variant, but distributes the computation across multiple TPs, described in Section 3.2.3.3 and illustrated in Figure 3.5. To summarize, OpenMP and Naïve implement coarse-grain synchronization scheme, NaïveTPsPtr and InPlaceTPs implement medium-grain synchronization scheme, and FineGrain and InPlace implement Fine-Grain synchronization scheme.

The experiments utilize the following protocol:

- 1. All 2D stencil computations run for 30 time steps

- 2. Each variant instance is run 20 times to increase the stability of the run, then the accumulated times are averaged after removing the 2 most extreme values (min and max).

- 3. Each binary containing a variant is run 10 times from the command line, and average the accumulated times once again.

The reason why computing the the average of different invocations of the binaries for each variant is because the overall system environment introduces enough noise to generate timings that can significantly differ, for sequential, CAM, as well as OpenMP model variants—especially for smaller input sizes.

LULESH experiments were done in a similar way as 2D Stencil: All the computations were

repeated 20 times and the whole executable were run 10 times each.

#### 3.3.3 Experiment Results — 5-Point 2D Stencil Kernel

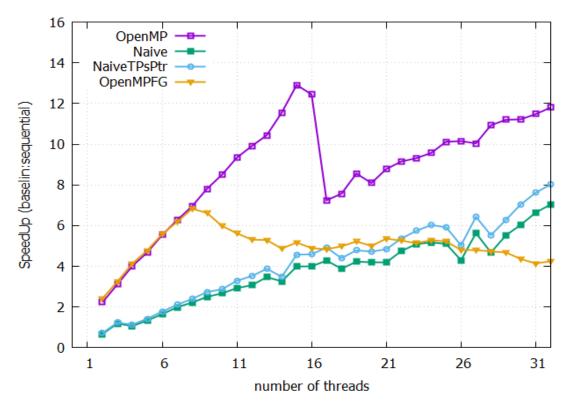

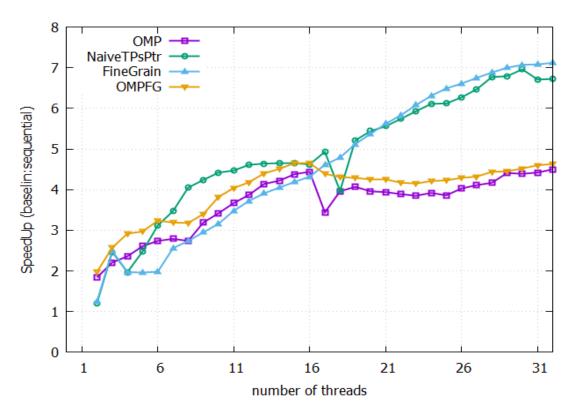

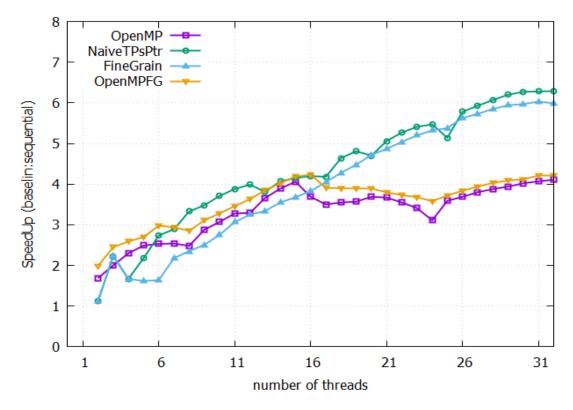

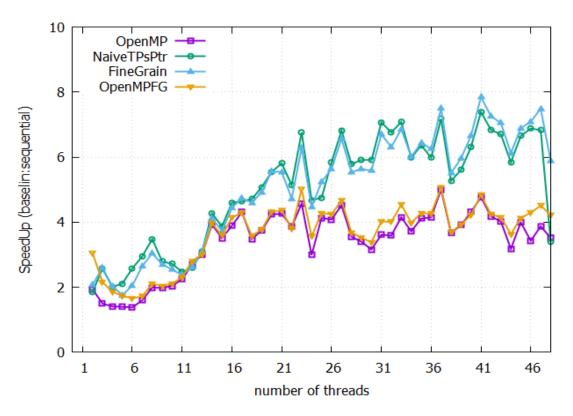

The results for strong scaling are shown in Figures: 3.9, 3.10, 3.11, 3.12, 3.13, and 3.14. Since there are eight different variants, as described in section 3.3.2, to maintain the readability of the Figures, only Seq, OpenMP, OpenMPFG and two best *DARTS* variants will be shown in these Figures.

Figure 3.9: platform A: Strong Scaling– Matrix size:  $1000 \times 1000$ .

The default CAM is used in the case of DARTS: each socket of the target platform is mapped to a cluster of cores. Each cluster thus features n-1 Compute Units (CUs) and one Scheduling Unit (SU). Hence all CUs are physically close to each other, ensuring that a *TP* allocated to a cluster displays some level of locality (at least at the L3 cache level). In other words, **compact** mapping polices, allocating software threads as closely as possible on the available

Figure 3.10: platform A: Strong Scaling– Matrix size:  $3000 \times 3000$ .

Figure 3.11: platform A: Strong Scaling– Matrix size:  $5000 \times 5000$ .

Figure 3.12: Platform B: Strong Scaling<br/>– Matrix size:  $1000\times 1000.$

Figure 3.13: PlatformB: Strong Scaling– Matrix size:  $3000 \times 3000$ .

Figure 3.14: PlatformB: Strong Scaling– Matrix size:  $5000 \times 5000$ .

Processing Elements (PEs) according to the underlying physical topology, is used in strong scaling test. As a result, in low-CU count case, not all the available aggregated cache will be used, especially, on a on a 2-socket compute node, if less than half of processing element(*i.e.*, one cluster/socket), then only one L3 module will be utilized. As described in section 3.3.2, the average execution time will be used as the final result since the execution times followed a normal distribution. For workloads that were mostly memory-bound, on Platform A, the standard deviation using *DARTS* is at most 5%, and less than 1% on average. On Platform B, the highest standard deviation reaches 18%, with an average of 10%.For cache-bound workloads, the standard deviation is much higher. For example, for 1000 × 1000 matrices, the standard deviation reaches 11% on Platform A (with an average of 5%), and 27% (with an average of 24%) on platform B. This is in part due to the dynamic scheduling algorithm which are used in the *DARTS*, which cannot guarantee that the same chunk of data will be processed by the same processing element.

In the *OpenMP* case, for both **OpenMP** and **OpenMPFG**, **OMP\_PROC\_BIND** are set to true to ensure that threads are pinned to a given PE. However, the *OpenMP* run-time system and the underlying OS are in charge of assigning a given (*OpenMP*) thread to the physical PEs, which results in threads being able to use all available L3 caches (when distributed over several sockets). Still, when resources start to be saturated, *i.e.*, when more than half of the processing elements (which in the case of both platforms are hardware threads) are used, and when they start to compete for FPUs, caches, *etc.*, the *DARTS* variants outperform the OpenMP version. As the PE count increases, so does the performance gap, as shown in Figure 3.10, 3.11, 3.13 and 3.14.In Platform A, figure 3.9 shows that the *OpenMP* coarsegrain variant has a clear advantage over *DARTS* and **OpenMPFG** fine-grain when the workload fits in the caches (*i.e.*, when the matrix size is 1000, or possibly 2000, as it still partially fits in the caches). Once the data grow beyond the capacity of L3 caches, as shown in Figure 3.10 and 3.11, *DARTS* Medium and Fine-Grain variants get the upper hand, and the **OpenMPFG** yields slightly better performance than **OpenMP**. The same trend can be found in Platform-B (Figure 3.12, 3.13 3.14).

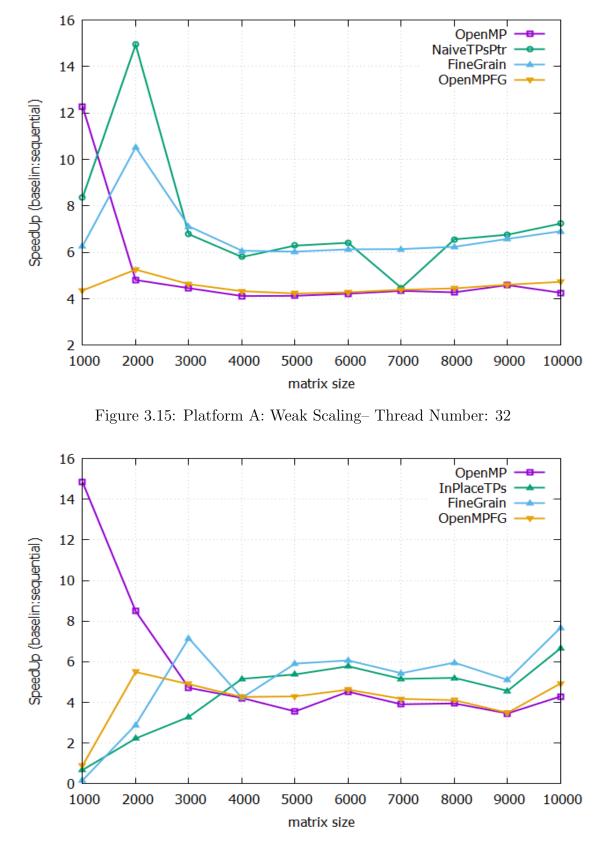

In weak scaling, shown in Figure 3.15 and Figure 3.16, FineGrain and NaiveTPsPtr achieve the best performance, with speedups reaching up to  $3 \times$  compared to two *OpenMP* variants. The OpenMP has a clear advantage over *DARTS* when the workload fits in the caches (*i.e.*, when the matrix size is  $1000 \times 1000$  on Platform A, or  $1000 \times 1000$  and  $2000 \times 2000$  on Platform B, as it still partially fits in the L3 caches). In the *OpenMP* coarse-grain case, loops are statically scheduled, thus ensuring that the same PE processes the same chunk of data, and hence minimizing cache misses. In the *OpenMP* fine-grain case(OpenMPFG), all the tasks, as described in Figure 3.2, are in the tasks pool, and will be invoked when their dependencies are satisfied. Tasks are dynamically assigned to available PEs and cluster. In contrast, *DARTS*'s scheduling policy is fully dynamic, and thus *Codelets* can be run by any PE belonging to the same cluster of cores. Hence a given data chunk may be processed by different PEs over two successive iteration steps, resulting in additional cache trashing.

Figure 3.16: Platform B: Weak Scaling–Thread Number: 48

Once the data grows beyond the capacity of L3 caches, DARTS gets the upper hand: the finer-grain variants either issue "local" atomic operations between neighbors (as with the **FineGrain** variant), or at least provide a hierarchical way to maintain some locality within their cluster of cores, thus reducing the overall memory traffic. In particular, the inclusive nature of the caches in Intel processors allows the hardware to recognize when a given memory location is owned by the "local" L3, and thus avoids a costly request for ownership across sockets. Fine-grain DARTS variants are always better than coarse grain ones. When problem sizes fit in the L3 cache(s), the OpenMP variant yield much better performance than all the DARTS variants, no matter the granularity. When problem sizes are larger than the L3 cache, the DARTS's FineGrain and NaiveTPsPtr variants yield better performance.

#### 3.3.4 5-Point 2D Stencil Kernel Results — Discussion

Coarse-grain synchronizations (e.g., barriers) tend to be implemented with a single memory location, even in state-of-the-art run-time systems (for example: GCC's OpenMP; Intel's implementation offers both linear and tree-based barriers). This has several negative consequences: (1) all processing elements issue an atomic operation to the same location, forcing the other PEs to flush their write buffers, sometimes more than once; (2) there is a "natural" contention due to the target single location. By contrast, finer-grain synchronization makes use of more locations with better locality effects. Write buffer flushes still occur, but tend to be limited to writing back in L3 (at least in the Intel case). In addition, Codelets can better exploit the "slack" that exists when a core is done running a thread, due to their event-driven nature.

Finer-grain synchronization clearly *does* provide better results on general-purpose many-core systems, as shown in Figures from 3.9 to 3.16. However, which variant works best varies significantly depending on which platform running tests. On Intel-based compute nodes, the

most refined variants did not perform very well in the end: the InPlace and InPlaceTPs variants under performed compared to their most simple counterparts, and even compared to the coarse-grain *OpenMP* variant. The main reason is the implementation is too naïve: while the InPlace variant does require less memory than the original code, its implementation is too simplistic. When computation *Codelets* are being fired, OS will allocate *Codelets* to different Hard threads. However, when a huge amount of *Codelets* are fired within a very small time range, some serialization operations, such as accessing OS's "memory allocator", will drop the overall performance. As Intel-based nodes feature inclusive caches, the data can only be as big as the L3s of the system. The situation maybe different, if the experiment run on the AMD-based Processor since AMD system cache are exclusive: the aggregated size of the L2 caches equals the aggregated size of the L3s, effectively doubling the overall size of the data that can be held in the caches. The AMD system also relies on write-through L1D caches (compared to Intel's write-back L1Ds), which allows for a better utilization of the L1D (there is roughly four times more reads than writes in the stencil computation)

Moreover, the purpose of this section is to show the benefits of "pure" fine-grain synchronization, without resorting to classical loop transformations such as tiling or loop skewing, even the allocation of just three complete rows is enough to quickly fill L1D caches. For example, the smallest input size for a matrix,  $1000 \times 1000$ , requires three rows of a thousand elements to implement the current in-place variants. However, this represents already  $\approx 2/3$  of the L1D cache of the compute nodes. Hence, to obtain an efficient in-place variant, additional blocking and tiling techniques need to be applied.

#### 3.3.5 Experiment Results — LULESH

Similarly to the 5-points 2D stencil kernel, the average execution time is used as final result since the execution times followed a normal distribution. The largest standard deviation was

2% for Platform A, and 1% for Platform B.

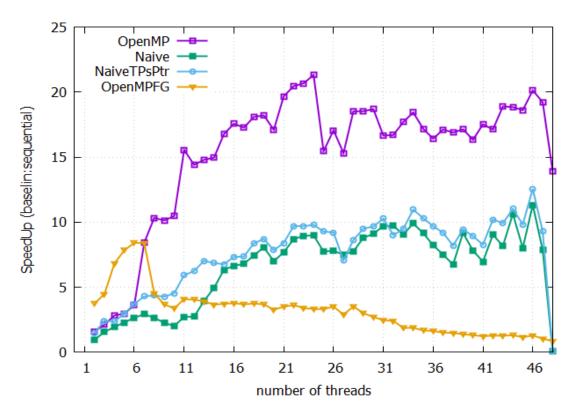

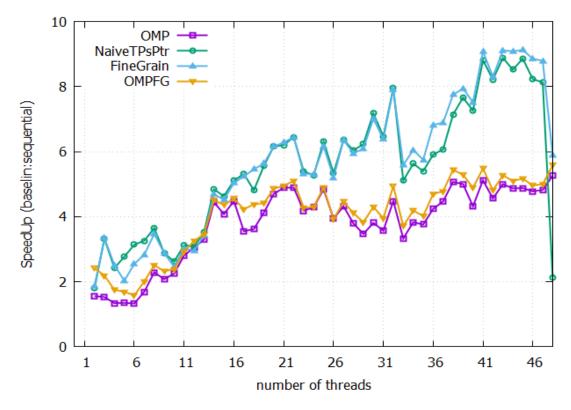

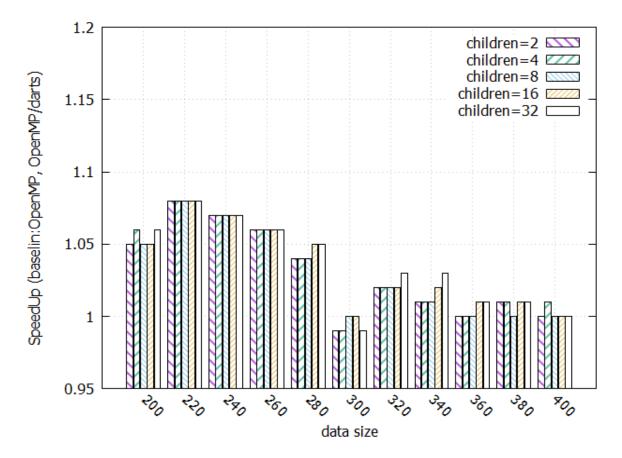

Figure 3.17: Platform A: LULESH on DARTS, vs OpenMP, children n is the arity of each node in the tree, *i.e.*, the number of children a node can have in the tree.

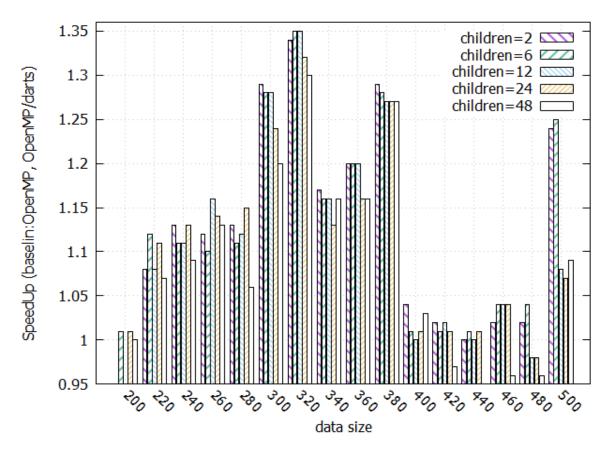

The overall performance of LULESH on *DARTS*, relies on three parts: the underlying computer architecture (in particular the memory aspects), the synchronization granularity, and input data size. As shown in Figure 3.18 (Platform B – see Table 3.2), compared to the reference *OpenMP* implementation, which uses coarse grain synchronization, the *DARTS*, Medium-Grain synchronization variant gets relatively good performance for small data sizes. For instance, when the input size is less than  $320^3$ , *i.e.*, the resolution of 3D LULESH is either over  $320^3$  elements or  $321^3$  nodes per time step. Medium grain variants (where the arity of each node is denoted by *children* = 6 and *children* = 12) fare relatively better than the coarse grain version (*i.e.*, *children* = 24 and *children* = 48) and the *OpenMP* reference code, but not by much. The main reason is that data fits in the various L3 caches, which

Figure 3.18: Platform B:LULESH on DARTS, vs OpenMP, children n is the arity of each node in the tree, *i.e.*, the number of children a node can have in the tree.

then allows for all synchronizations to occur relatively seamlessly.

For larger matrix sizes, Fine-Grain variants (with *children* = 2, which builds a binary computational tree, and *children* = 6) fare much better. For example, performance jumps by a wide margin when the data size reaches  $500^3$ . This is in part due to the fact that when the data set size increases, each individual *Codelet* has more work to perform, so ratio of computation-communication cost increase while communication belongs to serialization part and computation belongs to paralleling part. Furthermore, the *Codelet* graph builds a fine grain synchronization tree, as shown in Figures 3.7 and 3.8. In it, the non-root, non-terminal *Codelets* have two functions: computation and synchronization. The synchronization tree structure can help split this large data set into a series of small and relatively independent ones. The amount of computation is the same among all *Codelets*, but the communication

cost will be reduced compared to a coarse-grain variant leveraging a barrier. Because children *Codelets* only need to communicate/synchronize with their parent, data access conflicts are reduced within one cluster and between sockets/clusters, especially in the case that the computation spreads across all the PEs and all the clusters, fully utilizes the L3 cache, and needs to access data in main memory. Hence, the tree structure helps control the data flow, data transfers, and further reduces data access conflicts. For medium-sized computations, the situation is more complex. When the data set size reaches the L2 cache boundary, *e.g.*, data sizes from  $400^3$  to  $480^3$  as shown in Figure 3.18 (Platform B), the overall performance will rely on multiple factors, such as how *Codelets* were bound to cores or clusters, whether the leaves and their parent are allocated in the same socket or not, how deep of tree structure was, *etc.* For this data set, the best granularity cannot be easily predicted, and some fine-tuning is in order.

DARTS assign Codelets to different PEs and clusters by using the hwloc library and bind units to specific cores using their ID. In this experiments, the binding method is based on the granularity of synchronization and number of cores in one cluster. The basic rule is to try to put parent and children Codelets in one cluster/socket to reduce the data transformation time.

In the Figure 3.17 and 3.18, there are some special points, called *changing points*, which correspond to the medium sizes always somewhere "just above" the L3 cache sizes. The boundary between coarse-grain and fine-grain is vague since the cost of tree hierarchy communication and coarse-grain communication are similar during these changing cost. Different architectures have different changing points. For example, in Platform A (see table 3.2 and Figure 3.17), the changing point occurs at data size 300<sup>3</sup>, but in Platform B, the changing points are range from 400<sup>3</sup> to 480<sup>3</sup>. This is of course directly related to the sizes of the platforms' L3 size (individual and aggregated), as well as the way the workload is partitioned among the PEs.

## 3.4 Related Work

This section presents work pertaining to fine-grain and event-driven multithreading, as well as relevant approaches to run parallel executions of stencil computations.

# 3.4.1 Fine-Grain Multithreading Execution and Programming Models

In recent years, several attempts at providing more dynamic ways to create parallel work have been proposed. Many such attempts are inspired by data flow models of computation. Among them, we can mention Concurrent Collection [30–33], which implements a dynamic data flow inspired execution and programming model to orchestrate parallel programs execution. Cnc was used to run workloads that expose extremely fine-grain parallel algorithms, such as stencil computations in the LULESH application [34], using classical optimizations such as loop fusion and tiling to coarsen granularity and enhance the application's scalability. However, the authors lacked a cache-specific tuner and had to suffer a large overhead due to the data collection phase.

XKaapi [35, 36] is a macro-data flow run-time which targets multi and many core (possibly heterogeneous) systems. Much like most modern run-time systems (including *DARTS*), it relies on the use of work stealing for dynamic load-balancing, as well as work over-subscription to ensure the system is always usefully busy.