# UC Irvine UC Irvine Electronic Theses and Dissertations

### Title

Efficient Offline and Online Training of Memristive Neuromorphic Hardware

Permalink https://escholarship.org/uc/item/4t9278vc

**Author** Fouda, Mohammed

Publication Date 2020

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA, IRVINE

Efficient Offline and Online Training of Memristive Neuromorphic Hardware

#### DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Electrical and Computer Engineering

by

Mohammed E. Fouda

Dissertation Committee: Professor Ahmed Eltawil, Chair Professor Fadi Kuradhi Professor Emre Neftci Professor Nikil Dutt

$\bigodot$  2020 Mohammed E. Fouda

# DEDICATION

To my parents who I owe everything.

To my dear wife, Radwa, for her continuous support.

To Adam, my son, wishing him a successful life.

# TABLE OF CONTENTS

|                                               | Pa                                                                                                                                                    | ge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ST (                                          | OF FIGURES                                                                                                                                            | vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ST (                                          | OF TABLES                                                                                                                                             | cii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ST C                                          | OF ALGORITHMS x                                                                                                                                       | iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CKN                                           | OWLEDGMENTS                                                                                                                                           | xv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| [TA                                           | x                                                                                                                                                     | vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BST                                           | RACT OF THE DISSERTATION xv                                                                                                                           | iii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Intr<br>1.1<br>1.2<br>1.3<br>1.4              | oduction         Existing Digital Neuromorphic Hardware         Emerging Neuromophic Hardware         Contributions         Dissertation Organization | 1<br>2<br>3<br>6<br>8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Mer<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Weight Mapping                                                                                                                                        | <ol> <li>10</li> <li>12</li> <li>14</li> <li>16</li> <li>19</li> <li>20</li> <li>24</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Cro<br>3.1<br>3.2<br>3.3                      | Nano-scale Interconnect Parasitics Extraction                                                                                                         | <ul> <li>26</li> <li>27</li> <li>28</li> <li>29</li> <li>30</li> <li>31</li> <li>32</li> <li>34</li> <li>34</li> <li>36</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                               | ST C<br>ST C<br>CKN<br>ITA<br>BSTI<br>1.1<br>1.2<br>1.3<br>1.4<br>Men<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>Cro<br>3.1                         | ST OF FIGURES       ST         ST OF TABLES       ST         ST OF ALGORITHMS       x         CKNOWLEDGMENTS       ST         UTA       x         BSTRACT OF THE DISSERTATION       xv         Introduction       x         1.1       Existing Digital Neuromorphic Hardware       xv         1.2       Emerging Neuromophic Hardware       xv         1.3       Contributions       xv         1.4       Dissertation Organization       xv         Memristive Neuromorphic Hardware Challenges       xv         2.1       Weight Mapping       xv         2.2       Endurance and Retention       xv         2.3       Sneak Path Effect       xv         2.4       Delay       xv         2.5       Asymmetric Non-linearity Conductance Update Model       xv         2.6       Stuck-At Fault Effect       xv         2.7       Interconnect Parasitics Extraction       xv         3.1.1       Interconnect Wire Resistance       xv         3.1.2       Interconnect Conductance       xv         3.1.3       Interconnect Conductance       xv         3.1.4       Interconnect Conductance       xv <t< td=""></t<> |

|          |     | 3.3.1 Mathematical Model of Basic Switching Cell               | 38 |

|----------|-----|----------------------------------------------------------------|----|

|          |     |                                                                | 38 |

|          |     |                                                                | 40 |

|          | 3.4 | · ·                                                            | 44 |

|          |     | 3.4.1 Loading Effect On Crossbar Model                         | 46 |

|          |     |                                                                | 47 |

|          |     | 3.4.3 Simulation Results and Validation                        | 48 |

|          | 3.5 |                                                                | 49 |

|          |     |                                                                | 49 |

|          |     |                                                                | 51 |

|          | 3.6 |                                                                | 52 |

|          | 3.7 | •                                                              | 58 |

| 4        | Rea | ding and Writing Techniques for Crossbar Resistive Memories    | 60 |

|          | 4.1 |                                                                | 60 |

|          |     |                                                                | 63 |

|          | 4.2 |                                                                | 64 |

|          |     | 4.2.1 Proposed current sensing circuitry                       | 68 |

|          |     |                                                                | 73 |

|          |     | 4.2.3 Power Consumption Estimation                             | 73 |

|          |     | 4.2.4 Bias Mismatch Effect                                     | 77 |

|          | 4.3 | Modeling the write disturb problem                             | 79 |

|          |     | 4.3.1 Optimality problem formulation and solution              | 80 |

|          |     | 4.3.2 Results and Discussion                                   | 81 |

|          | 4.4 | One Step Row Write Technique                                   | 82 |

|          | 4.5 | Combined Reading and Writing Circuitry                         | 85 |

|          | 4.6 | Non-Stationary Polar Codes for Resistive Memories              | 85 |

|          |     | 4.6.1 Non-stationary polar code construction                   | 88 |

|          |     |                                                                | 89 |

|          |     | 11 0                                                           | 93 |

|          |     | 4.6.4 Binary Asymmetric Channel Modeling                       | 94 |

|          |     | 4.6.5 Punctured Polar Codes                                    | 95 |

|          | 4.7 | Conclusion and Future Perspective                              | 96 |

| <b>5</b> | Wir | re Resistance-aware Training for efficient Offline Learning 10 | 00 |

|          | 5.1 | Background and Related Work                                    | 01 |

|          | 5.2 | Multi-bit RRAM Device Under Study                              | 02 |

|          |     | 0                                                              | 04 |

|          |     | 0 11 0                                                         | 06 |

|          |     | 0                                                              | 07 |

|          | 5.3 |                                                                | 11 |

|          |     | 5.3.1 Nano-scale Crossbar Parasitics                           | 11 |

|          |     | 5.3.2 Source and Neuronal Resistance                           | 12 |

|          |     |                                                                | 14 |

|          | 5.4 | BNNs Realization on Binary Crossbar Arrays 1                   | 16 |

|   |       | 5.4.1   | BNNs on RRAM crossbars                                                                                                     |

|---|-------|---------|----------------------------------------------------------------------------------------------------------------------------|

|   |       | 5.4.2   | Necessity of Large Weight Array Partitioning                                                                               |

|   |       | 5.4.3   | Evaluation Results                                                                                                         |

|   |       | 5.4.4   | DNN Framework                                                                                                              |

|   | 5.5   | Mask    | Technique: Making Training Possible                                                                                        |

|   |       | 5.5.1   | Mask Method                                                                                                                |

|   |       | 5.5.2   | Mask Generation                                                                                                            |

|   |       | 5.5.3   | Architecture Solutions                                                                                                     |

|   | 5.6   | BNN I   | Results and Discussion                                                                                                     |

|   |       | 5.6.1   | Impact of Retraining on Binarized MLP Network                                                                              |

|   |       | 5.6.2   | Impact of Retraining on Binarized CNNs                                                                                     |

|   |       | 5.6.3   | Power Consumption in Resistive Crossbar Arrays 137                                                                         |

|   |       | 5.6.4   | Discussion and Comparison                                                                                                  |

|   | 5.7   | Exten   | ding Mask technique for Quantized Neural Networks                                                                          |

|   |       | 5.7.1   | Effect of Wire Resistance Problem on QNNs                                                                                  |

|   |       | 5.7.2   | Proposed IR-QNN Training and Inference                                                                                     |

|   |       | 5.7.3   | Batch Normalization during Inference                                                                                       |

|   |       | 5.7.4   | QNN Experimental Setup 152                                                                                                 |

|   | 5.8   | QNN     | Results and Discussion                                                                                                     |

|   |       | 5.8.1   | Stuck-At Fault Effect                                                                                                      |

|   |       | 5.8.2   | Effect of Device Variability                                                                                               |

|   |       | 5.8.3   | Effect of Limited Retention                                                                                                |

|   |       | 5.8.4   | Power and Area Results                                                                                                     |

|   |       | 5.8.5   | Time Overhead Comparison                                                                                                   |

|   | 5.9   |         | and Neuronal Circuits Requirements                                                                                         |

|   | 5.10  | Conclu  | $1 sion \dots \dots$ |

| 6 | Effic | cient ( | Online Learning 165                                                                                                        |

|   | 6.1   |         | endent Component Analysis using RRAMs                                                                                      |

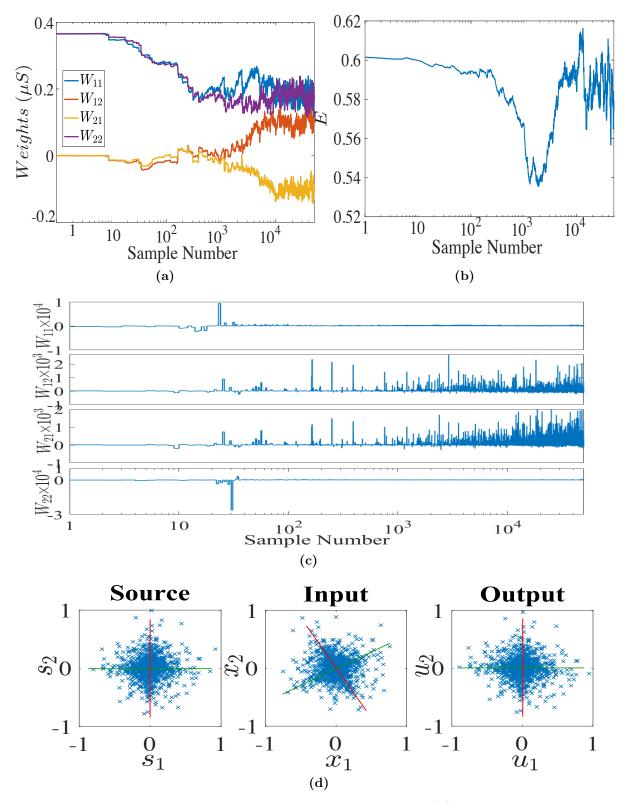

|   |       | 6.1.1   | Proposed RRAM's learning method                                                                                            |

|   |       | 6.1.2   | De-mixing Example and Results                                                                                              |

|   |       | 6.1.3   | Power, area and speed comparison with CMOS realization 174                                                                 |

|   | 6.2   | Deep 2  | Neural Network with Local Learning                                                                                         |

|   |       | 6.2.1   | Neural Network Model                                                                                                       |

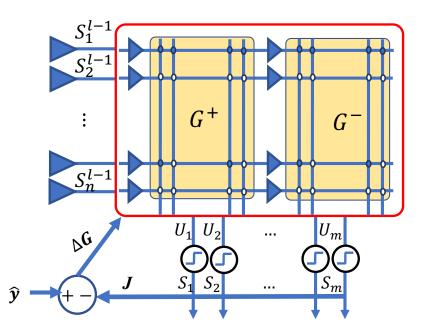

|   |       | 6.2.2   | Local Learning with Crossbar Arrays                                                                                        |

|   |       | 6.2.3   | Experimental Setup                                                                                                         |

|   |       | 6.2.4   | Online Training Under Asymmetric Nonlinear Updates                                                                         |

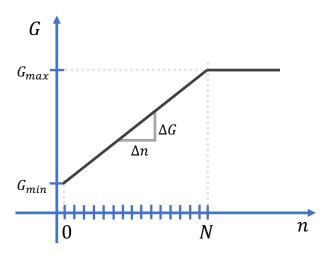

|   |       | 6.2.5   | Stochastic Ternary Update Method                                                                                           |

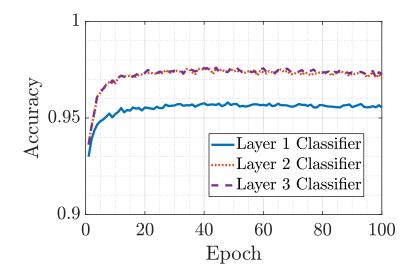

|   |       | 6.2.6   | Results and Comparison                                                                                                     |

|   |       | 6.2.7   | RRAM's Energy Update Model                                                                                                 |

|   |       | 6.2.8   | Limited Endurance                                                                                                          |

|   |       | 6.2.9   | Conductance Degradation Model                                                                                              |

|   | 6.3   | Error-  | triggered Learning                                                                                                         |

|   |       | 6.3.1   | Local Losses and Local Errors                                                                                              |

|   |       | 6.3.2   | Large-scale Simulation Experiments                                                                                         |

|    | 6.4   | Conclu | sion                                                  | 191 |

|----|-------|--------|-------------------------------------------------------|-----|

| 7  | Pros  | spects | on Memristive Neuromorphic Hardware                   | 193 |

|    | 7.1   | Synapt | tic Plasticity and Learning in SNN                    | 193 |

|    |       | 7.1.1  | Gradient-based Learning in SNN and Three-Factor Rules | 195 |

|    | 7.2   | Stocha | stic Spiking Neural Networks                          | 202 |

|    |       | 7.2.1  | Learning in Stochastic Spiking Neural Networks        | 203 |

|    |       | 7.2.2  | Three Factor Learning in Memristor Arrays             | 205 |

| Bi | bliog | raphy  |                                                       | 208 |

| A  | KCI   | L Form | nulation of the crossbar                              | 226 |

|    |       | A.0.1  | Linear Switching Modeling Equations Derivation        | 229 |

|    |       | A.0.2  | Nonlinear Switching Modeling Equations Derivation     | 232 |

|    |       |        |                                                       |     |

# LIST OF FIGURES

## Page

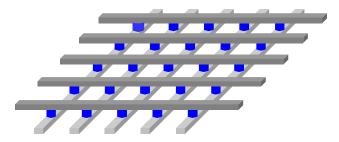

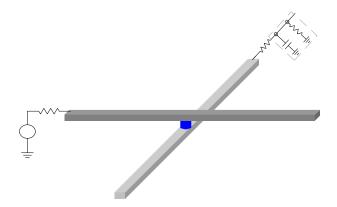

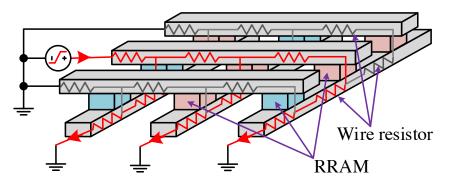

| 1.1                      | Crossbar containing switching devices (Blue).                                                                                                                                                               | 5              |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

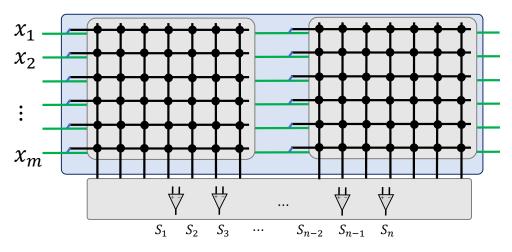

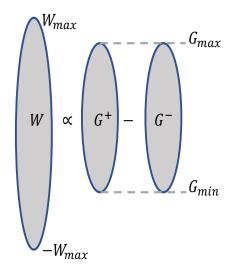

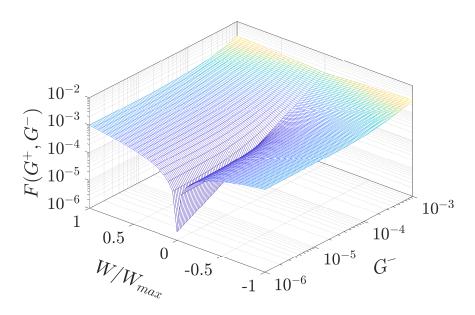

| 2.1<br>2.2<br>2.3<br>2.4 | Crossbar array realization of one layer neural network                                                                                                                                                      | 11<br>12<br>14 |

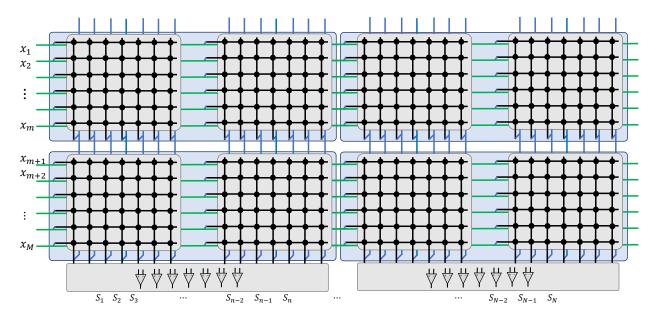

| 2.5                      | Realization of the partitioned matrices.                                                                                                                                                                    | 19             |

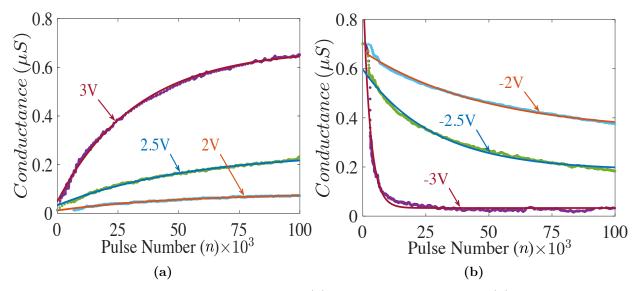

| 2.6                      | RRAM's conductance update (a) long term potentiation (b) long term de-                                                                                                                                      | 10             |

|                          | pression.                                                                                                                                                                                                   | 24             |

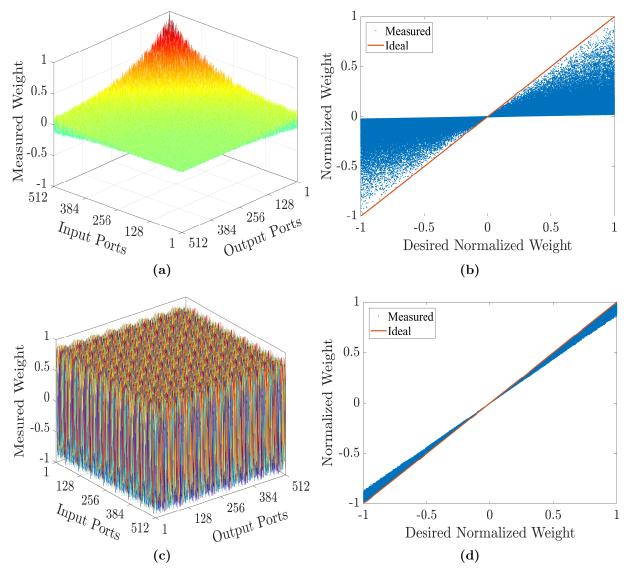

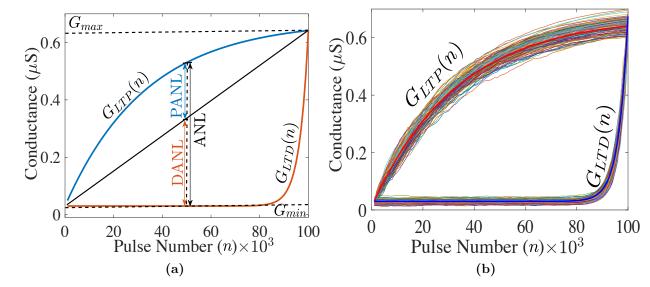

| 2.7                      | Non-idealities of the RRAM:(a) asymmetric nonlinear weight update (b) de-<br>vice Variations                                                                                                                | 25             |

| 3.1                      | ANSYS Q3D simulation of three parallel interconnect wires                                                                                                                                                   | 28             |

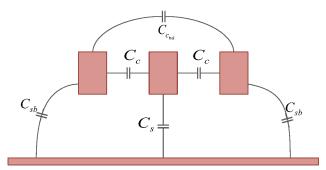

| 3.2                      | Capacitive model of interconnect.                                                                                                                                                                           | 30             |

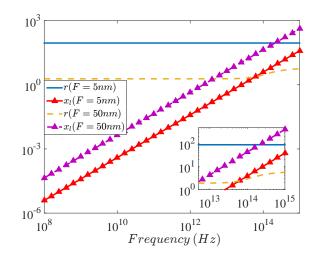

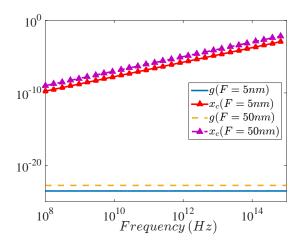

| 3.3                      | Resistance and inductance reactance per unit cell of interconnect wire                                                                                                                                      | 33             |

| 3.4                      | Conductance and capacitive susceptance per unit cell of interconnect wire.                                                                                                                                  | 33             |

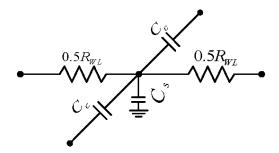

| 3.5                      | Summarized transmission line model                                                                                                                                                                          | 33             |

| 3.6                      | Basic cell model.                                                                                                                                                                                           | 35             |

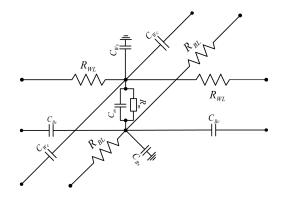

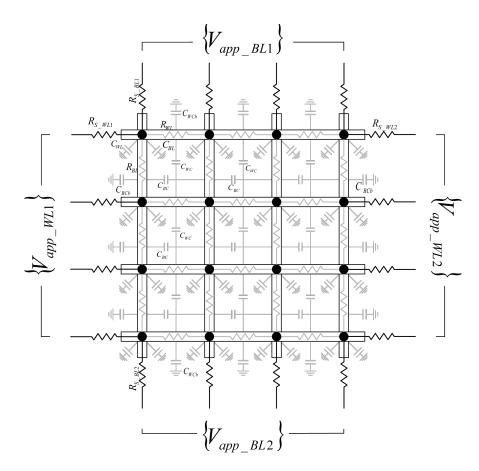

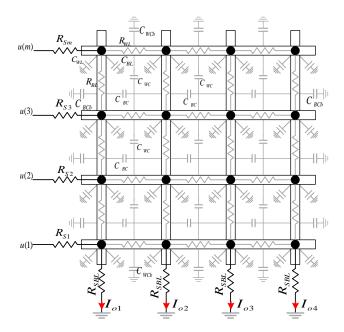

| 3.7                      | Circuit model of the crossbar array                                                                                                                                                                         | 36             |

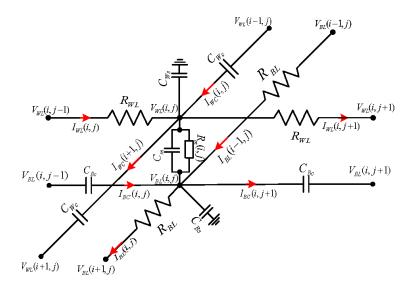

| 3.8                      | Kirchhoff's law of every cell in crossbar array.                                                                                                                                                            | 37             |

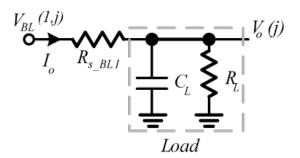

| 3.9                      | Interconnect array with loading                                                                                                                                                                             | 42             |

| 3.10                     | Kirchhoff's law at the load.                                                                                                                                                                                | 45             |

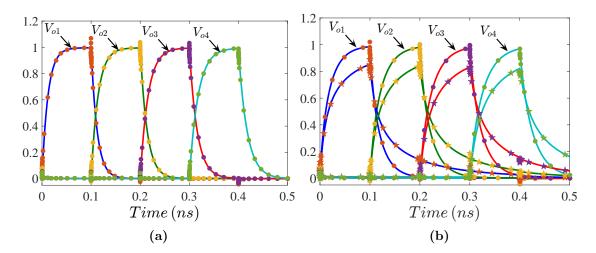

| 3.11                     | Transient verification between circuit simulation (dotted line) and analytical solution (solid lines) for $4 \times 4$ interconnect with (a) linear switching devices, and (b) parabolic switching devices. | 48             |

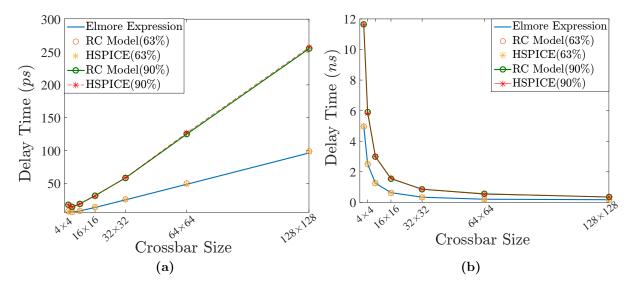

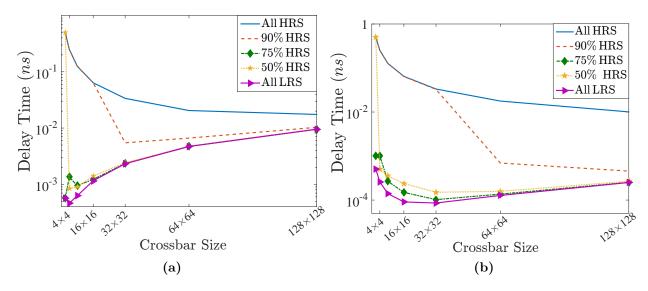

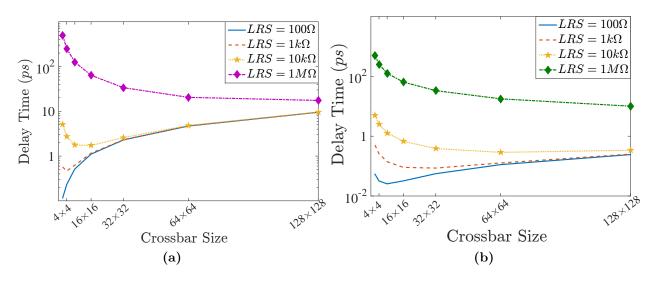

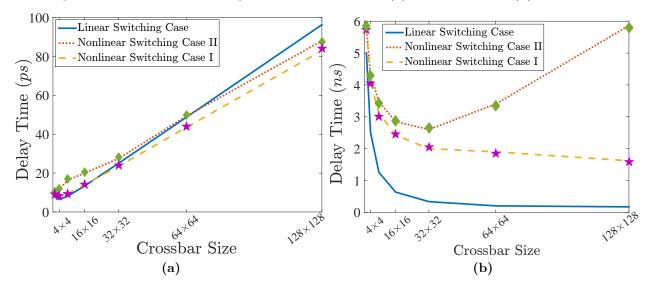

| 3.12                     | Comparison with the calculated Elmore delay expression and the transient simulation results for a) all HRS, and b) all LRS.                                                                                 | 52             |

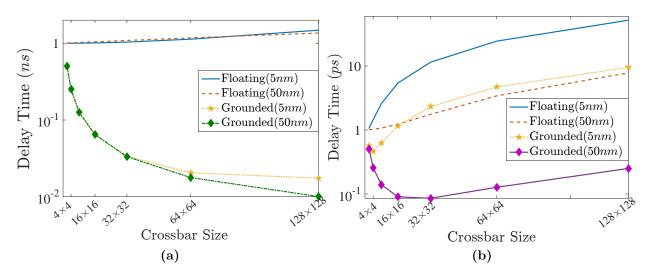

| 3.13                     | Comparison between the calculated delay of floating and grounded inputs for a) all HRS, and b) all LRS                                                                                                      | 53             |

| 3.14         | Effect of seeding the crossbar array with random data for different cases of $(a)F = 5nm$ structure and $(b) F = 50nm$ structure                                                                                  | 54                                      |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

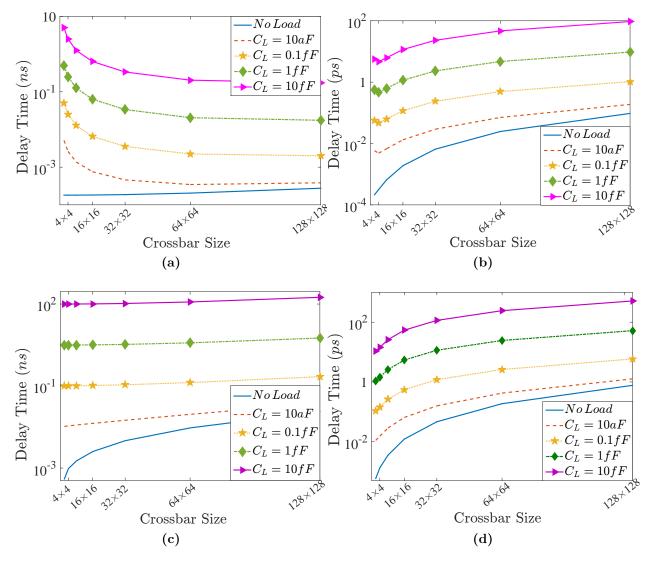

| 3.15         | Effect of changing loading capacitance for grounded inputs of $F = 5nm$ for (a) all HRS and (b) all LRS, and floating inputs for (c)all HRS, and (d) all                                                          |                                         |

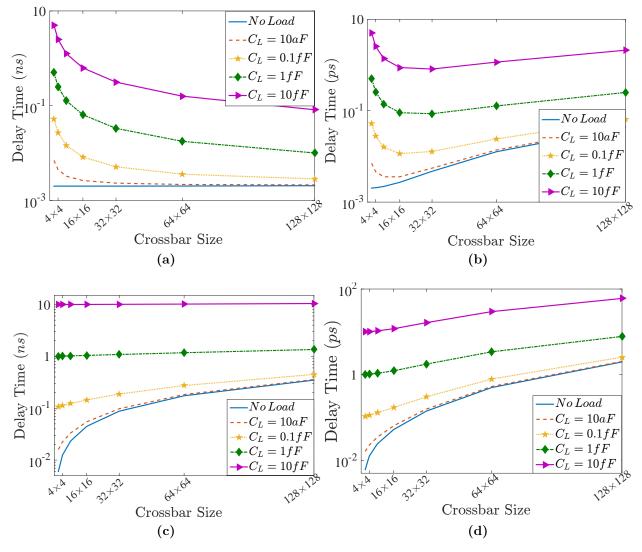

| 3.16         | LRS Effect of changing loading capacitance for grounded inputs of $F = 50nm$ for (a) all HRS and (b) all LRS, and floating inputs for (c)all HRS, and (d) all LRS                                                 | 55<br>56                                |

|              | Effect of using different devices for (a) $F = 5nm$ and (b) $F = 50nm$ Comparison between the calculated delay of crossbar array containing linear and nonlinear switching devices for a) all LRS, and b) all HRS | 50<br>57<br>57<br>58                    |

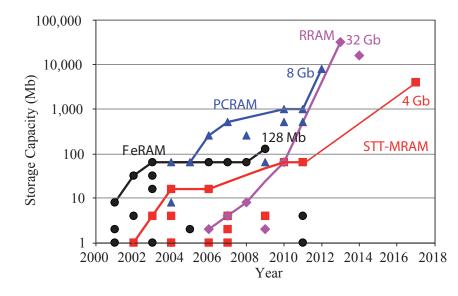

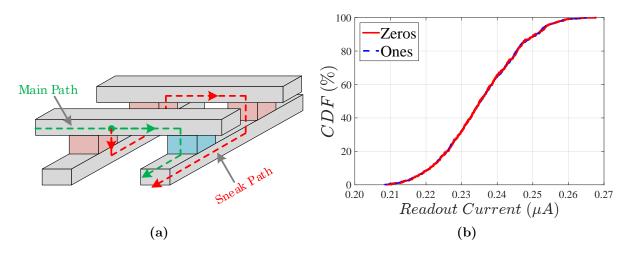

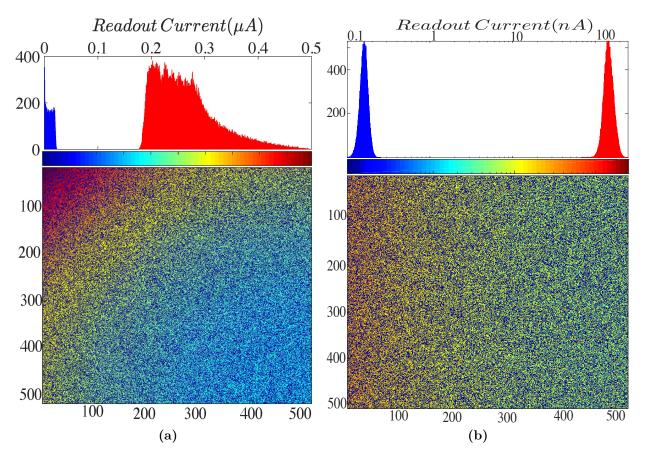

| $4.1 \\ 4.2$ | Trends in memory capacity for emerging NVMs adopted from [3] (a) Crossbar array with the sneak path problem, and (b) cumulative proba-                                                                            | 61                                      |

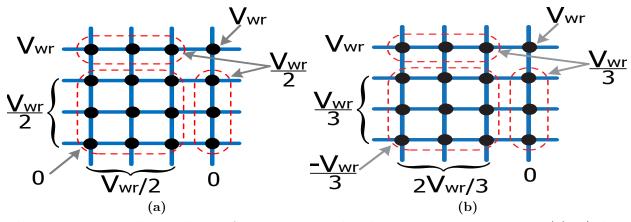

| $4.3 \\ 4.4$ | bility of reading $512 \times 512$ array                                                                                                                                                                          | 62<br>62                                |

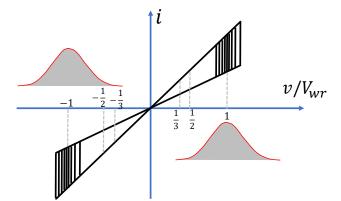

| 4 5          | scheme, and (b)1/3 bias scheme                                                                                                                                                                                    | 63                                      |

| $4.5 \\ 4.6$ | The set and reset switching behavior of RRAMs                                                                                                                                                                     | $\begin{array}{c} 64 \\ 65 \end{array}$ |

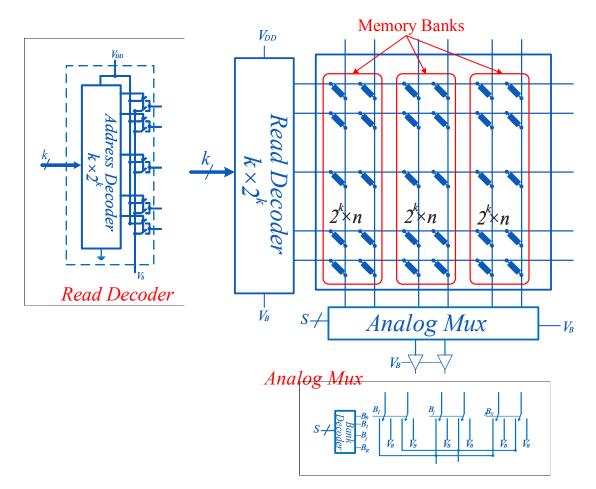

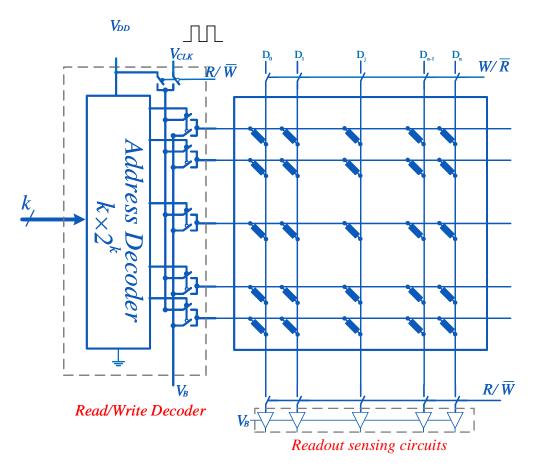

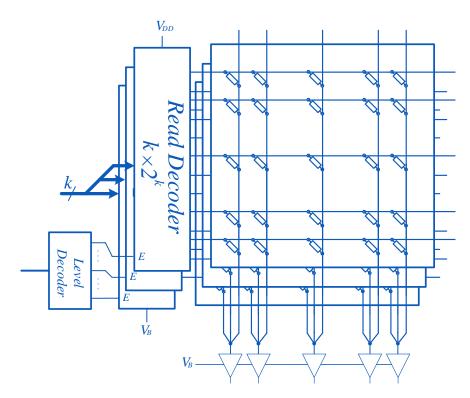

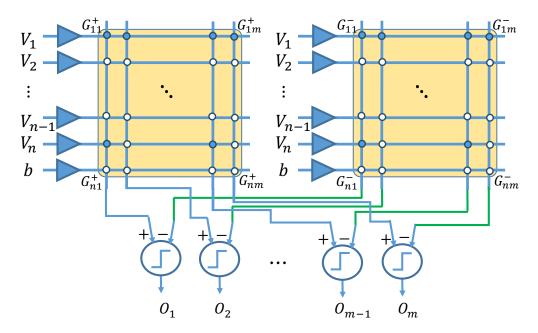

| 4.0<br>4.7   | Schematic of full single-layered crossbar array. $\dots \dots \dots$                                              | 05                                      |

|              | for (a)linear and (b) nonlinear devices.                                                                                                                                                                          | 67                                      |

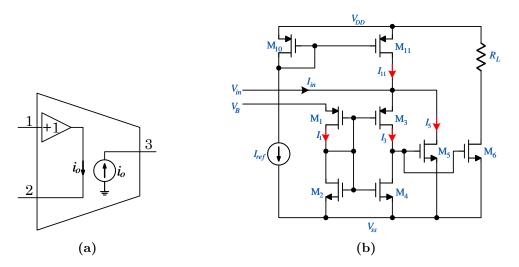

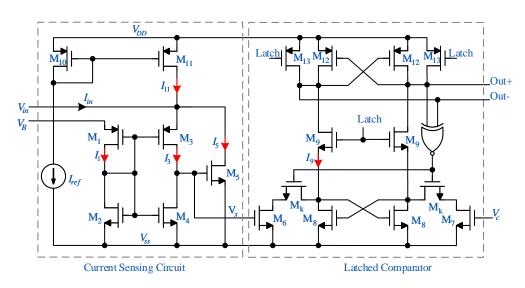

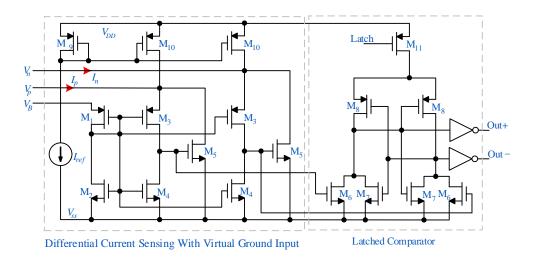

| 4.8          | (a) Current conveyor principle and (b) schematic of proposed current sensing circuit.                                                                                                                             | 71                                      |

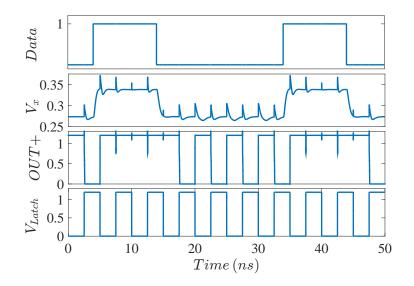

| 4.9          | Schematic of the full proposed readout circuit.                                                                                                                                                                   | 71                                      |

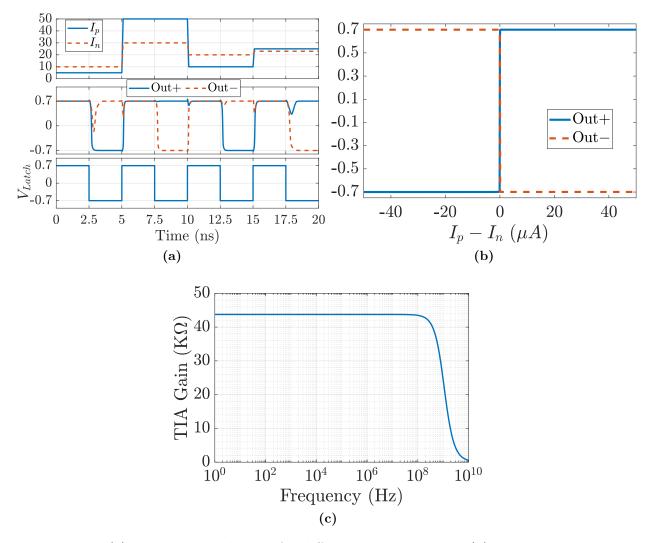

| 4.10         | Simulation results of the proposed circuit.                                                                                                                                                                       | 73                                      |

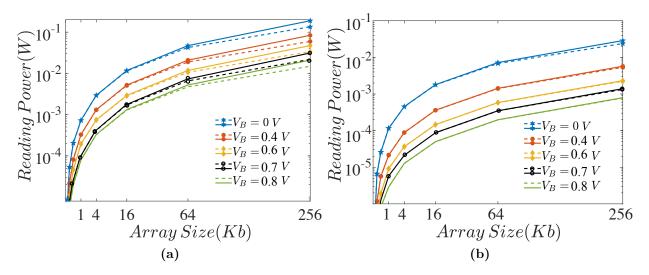

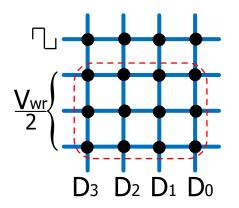

| 4.11         | Reading power versus the array size at $V_{DD} = 1.2V$ with and without wire resistance (dashed lines and solid lines) for (a) linear switching and (b) nonlinear                                                 | 10                                      |

|              | switching devices                                                                                                                                                                                                 | 74                                      |

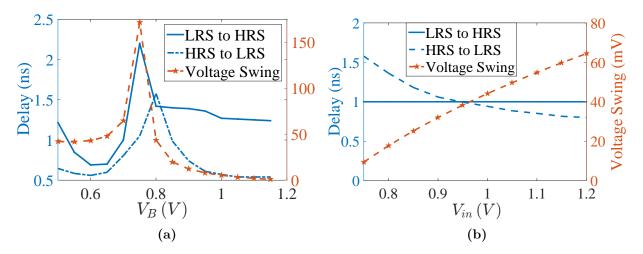

| 4.12         | Input comparator swing and delay versus (a) bias voltage with $V_{in} = 1.2V$ ,                                                                                                                                   |                                         |

|              | (b) applied voltage with $V_B = 0.7V$ .                                                                                                                                                                           | 75                                      |

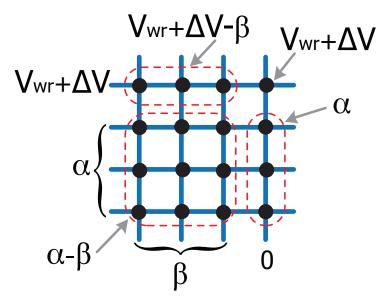

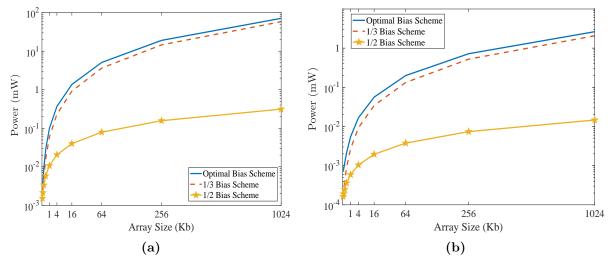

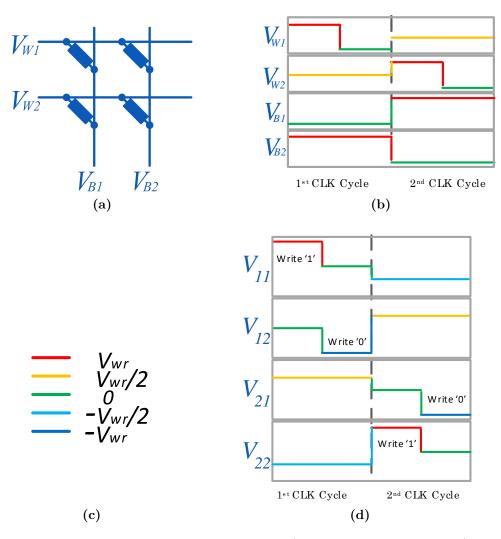

|              | General Bias scheme of writing crossbar based resistive memories                                                                                                                                                  | 80                                      |

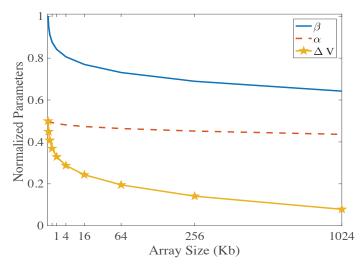

|              | Normalized optimal bias parameters versus the array size with 10% tolerance.                                                                                                                                      | 82                                      |

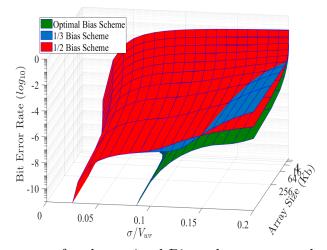

|              | Bit Error rate for the optimal Bias scheme versus the known bias schemes.                                                                                                                                         | 82                                      |

| 4.10         | Estimated power consumption of the optimal Bias scheme versus the known<br>bias schemes for (a) linear $I - V$ switching devices, and (b) nonlinear $I - V$                                                       |                                         |

|              | switching devices.                                                                                                                                                                                                | 83                                      |

|              | Bias scheme for one step writing technique.                                                                                                                                                                       | 83                                      |

| 4.18         | An illustrative example of writing a) $2 \times 2$ crossbar array; b) The wordline                                                                                                                                |                                         |

|              | and bitline voltages, and c) the voltage drop across each device. $\ldots$ .                                                                                                                                      | 84                                      |

| 4.19         | The whole schematic the resistive memory based on one step reading and                                                                                                                                            |                                         |

|              | writing techniques.                                                                                                                                                                                               | 86                                      |

| 4.20                                      | Parallel reading of the entire row in the crossbar. The columns and rows are grounded, except the row being read. The red arrow shows the sensed current                                                                                                                                                     |     |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                                           | flowing through wire resistances and RRAMs.                                                                                                                                                                                                                                                                  | 86  |

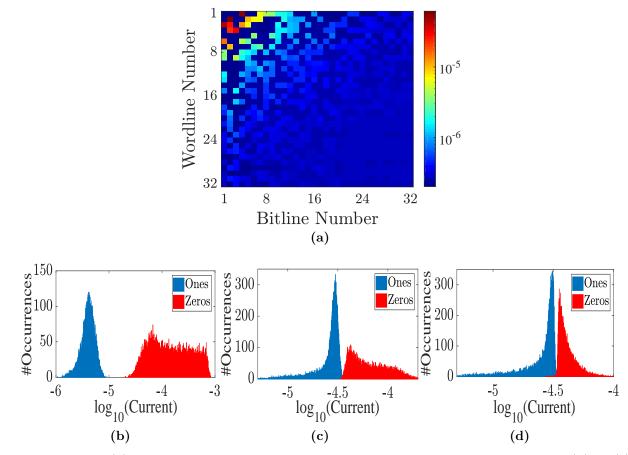

| 4.21                                      | (a) Measured current per cell, and its histogram for bitline number (b) 1, (c)                                                                                                                                                                                                                               |     |

|                                           | 16, and (d) 32                                                                                                                                                                                                                                                                                               | 87  |

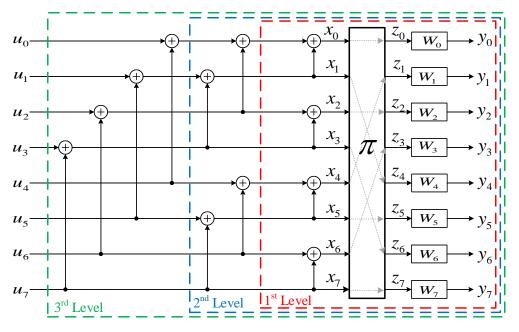

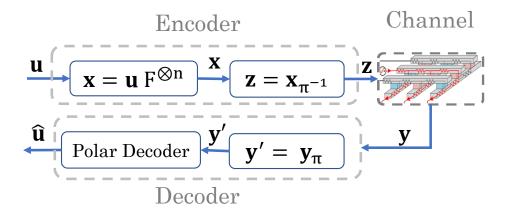

| 4.22                                      | Polar encoding with $N = 8$ channels, with permutation $\pi = [0, 4, 2, 6, 1, 5, 3, 7]$                                                                                                                                                                                                                      | 91  |

| 4.23                                      | Full system model.                                                                                                                                                                                                                                                                                           | 91  |

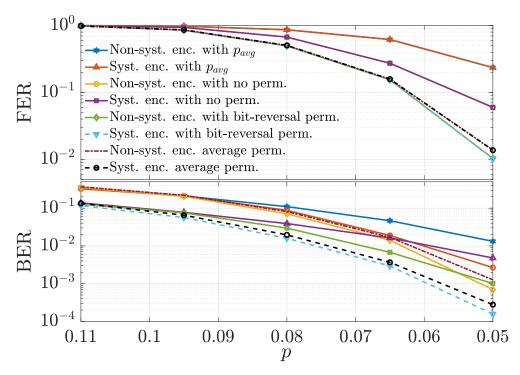

| 4.24                                      | Performance evaluation for BSCs with linearly spaced cross-over probabilities.<br>N = 1024, k = 512.                                                                                                                                                                                                         | 92  |

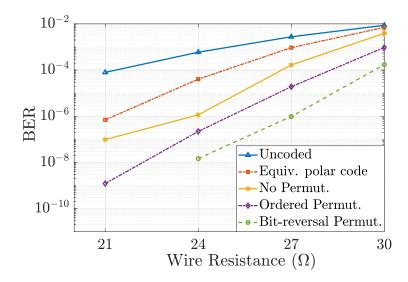

| 4.25                                      | Performance evaluation for a $(32 \times 32)$ crossbar array, code rate $k/n = 0.8$ .                                                                                                                                                                                                                        | 94  |

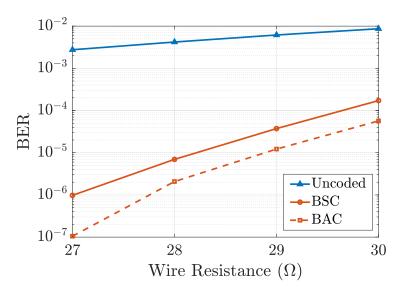

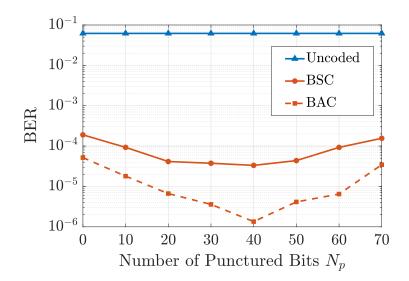

| 4.26                                      | BER performance under BSC and BAC modeling for a $(32 \times 32)$ crossbar, code rate $k/n = 0.8$ .                                                                                                                                                                                                          | 95  |

| 4.27                                      | Punctured polar encoding over the $(32 \times 32)$ crossbar array for code rate $k/n = 0.8$ .                                                                                                                                                                                                                | 96  |

| 4.28                                      | Stacked crossbar arrays sharing the readout circuitry. $\ldots$                                                                                                                                                                                                                                              | 98  |

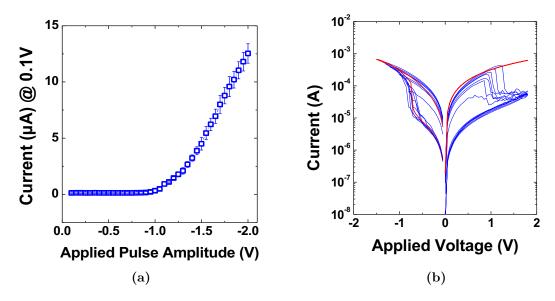

| 5.1                                       | $Au/Al_2O_2/HfO_2/TiN$ -based RRAM device adopted from [4] (a) device behavior under incremental step pulse programming and (b) current-voltage                                                                                                                                                              |     |

|                                           | characteristics.                                                                                                                                                                                                                                                                                             | 103 |

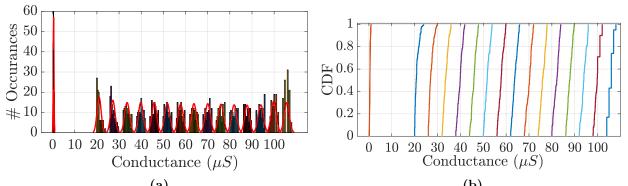

| 5.2                                       | Histogram and cumulative distribution function (CDF) of 100 measured sam-                                                                                                                                                                                                                                    |     |

|                                           | ples per state.                                                                                                                                                                                                                                                                                              | 103 |

| 5.3                                       | Matrix Vector Multiplication using separate RCAs.                                                                                                                                                                                                                                                            | 105 |

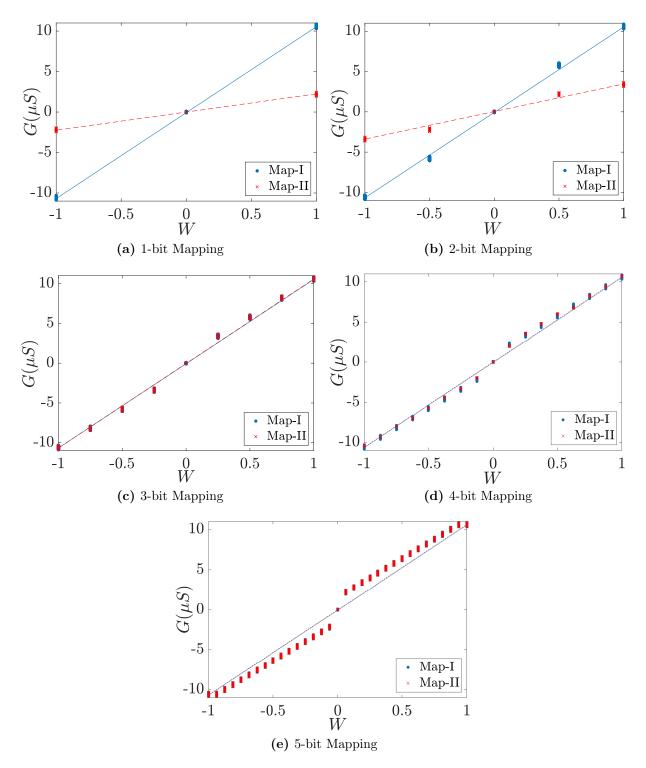

| 5.4                                       | Possible weight mappings for the used RRAM device.                                                                                                                                                                                                                                                           | 108 |

| $\begin{array}{c} 5.5 \\ 5.6 \end{array}$ | Schematic of proposed latched current sensing                                                                                                                                                                                                                                                                | 109 |

|                                           | sistance gain.                                                                                                                                                                                                                                                                                               | 110 |

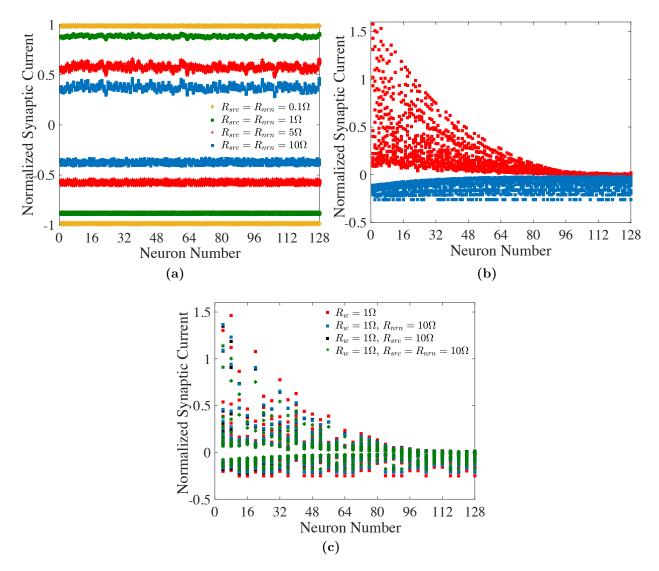

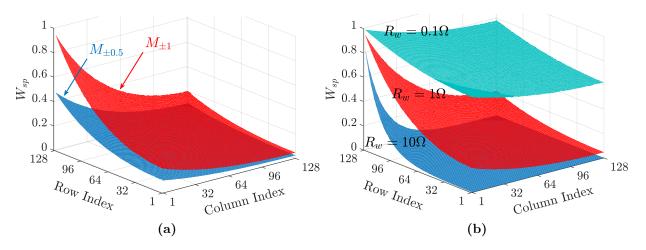

| 5.7<br>5.8                                | Effect of parasitic resistances on the normalized synaptic current Normalized root mean square deviation of the sensed current compared to the ideal case versus changing (a) the wire resistance and fixing the neuron resistance for different crossbar arrays and (b) the neuron resistance for different | 113 |

|                                           | wire resistances for $128 \times 128$ array.                                                                                                                                                                                                                                                                 | 114 |

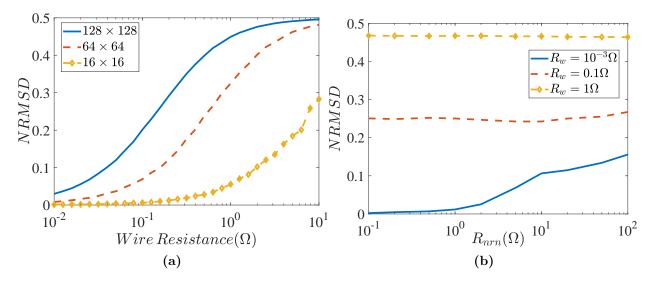

| 5.9                                       | Synaptic weight realizations using RRAMS; (a) balanced and (b) unbalanced                                                                                                                                                                                                                                    |     |

| F 10                                      | realizations.                                                                                                                                                                                                                                                                                                | 117 |

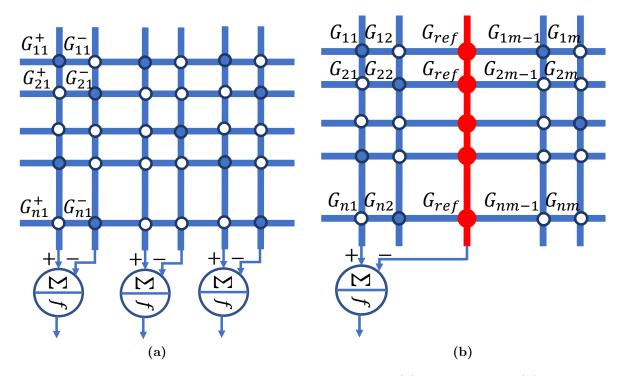

| 5.10                                      | Simulation time comparison between SPICE and numerical simulator, adopted from [5], for performing MVM of $256 \times 256$ array partitioned into $32 \times 32$ ,                                                                                                                                           | 110 |

| <b>F</b> 1 1                              | $64 \times 64$ and $128 \times 128$ and for different number of input samples                                                                                                                                                                                                                                | 119 |

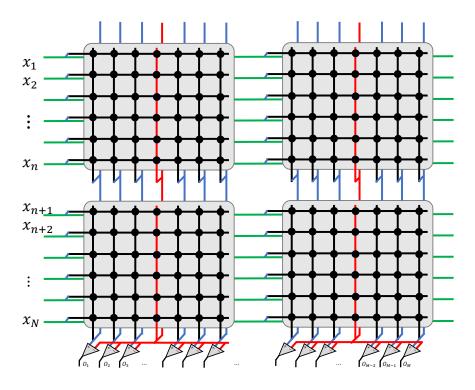

|                                           | Realization of the partitioned matrices.                                                                                                                                                                                                                                                                     | 121 |

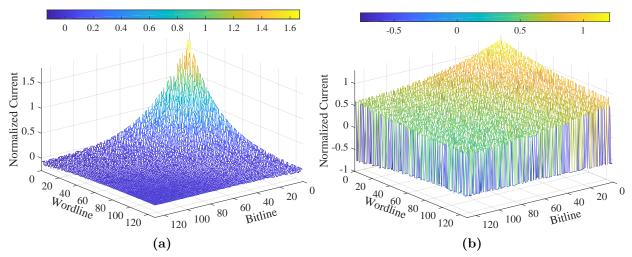

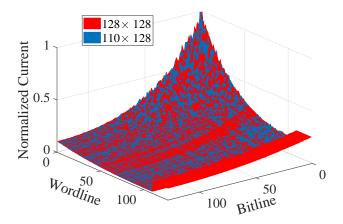

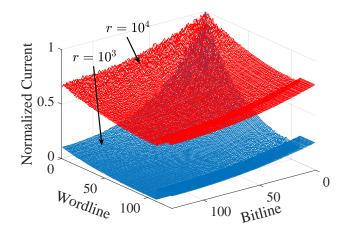

|                                           | Normalized sensed current of two crossbar arrays with a) $r = 500$ and b) $r = 10^4$ .                                                                                                                                                                                                                       | 121 |

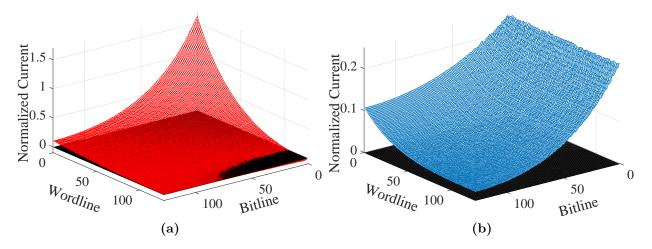

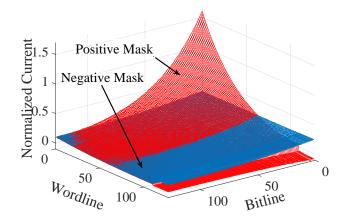

|                                           | Positive and negative masks of the 128x128 crossbar array                                                                                                                                                                                                                                                    | 127 |

| 5.14                                      | Positive and negative masks for $110 \times 128$ logical array using $128 \times 128$ physical                                                                                                                                                                                                               |     |

| <b>.</b>                                  | array                                                                                                                                                                                                                                                                                                        | 129 |

| 5.15                                      | Comparison between $128 \times 128$ physical array size and $110 \times 128$ physical array size for $110 \times 128$ logical subarray mask                                                                                                                                                                  | 129 |

| 5.16 | Effect of changing Wire resistance on the sneak path problem.                          | 130  |

|------|----------------------------------------------------------------------------------------|------|

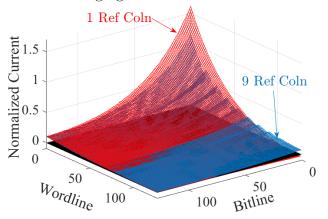

| 5.17 | Effect of changing number of reference columns on the mask                             | 130  |

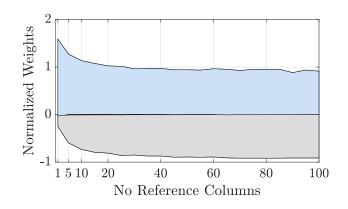

| 5.18 | Normalized measured weight with changing the number of reference columns.              | 131  |

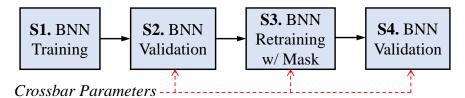

|      | DNN experiment flow $(Sn$ means Step $n)$ .                                            | 131  |

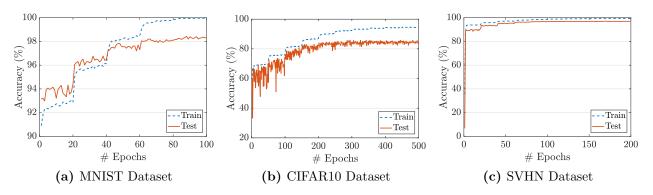

|      | DNN train and test accuracy during retraining the network.                             | 132  |

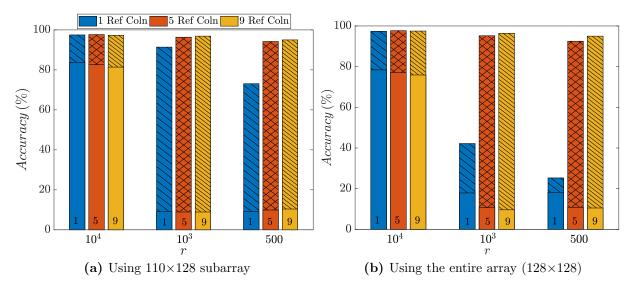

|      | DNN validation accuracy before retraining (un-hashed bars) after retraining            |      |

|      | (hashed bars)                                                                          | 132  |

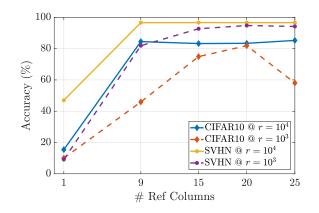

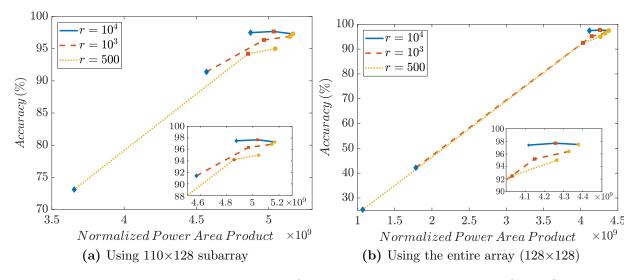

| 5.22 | Conventional neural networks validation accuracy for different reference columns       | .135 |

|      | Power dissipation comparison between proposed masks, $110 \times 128$ logical mask     |      |

|      | (un-hashed bars) and $128 \times 128$ mask (hashed bars) in the crossbar arrays used   |      |

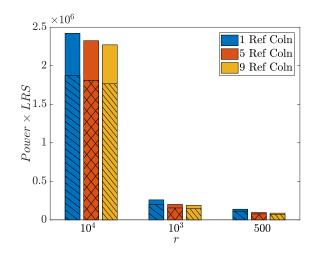

|      | for the MNIST network.                                                                 | 136  |

| 5.24 | DNN validation accuracy after retraining and validation of MNIST network               |      |

| 0    | for different $r$ values and for one (diamond), five (square) and nine (circle)        |      |

|      | reference columns                                                                      | 136  |

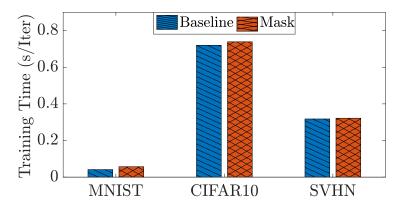

| 5.25 | Training time comparison (per iteration).                                              | 140  |

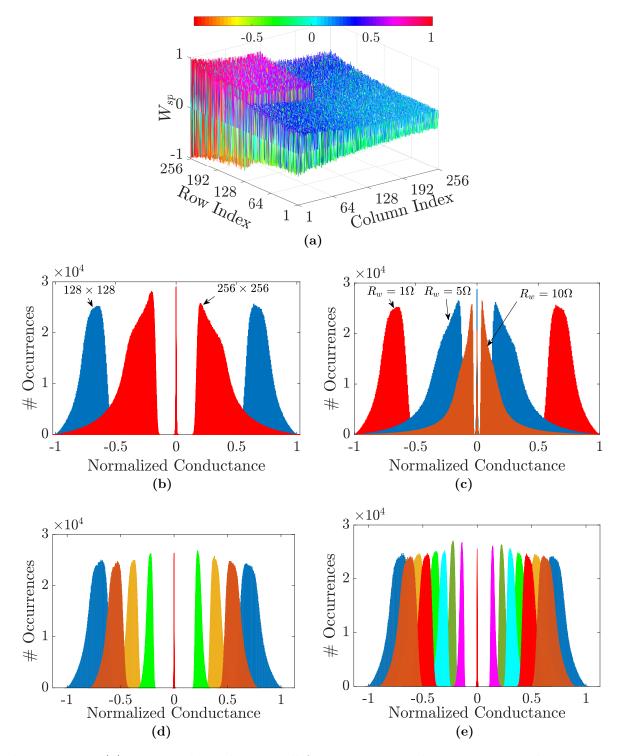

| 5.26 |                                                                                        |      |

| 0.20 | $R_w = 1\Omega$ , (b) Histogram of the measured conductance normalized to $G_{max}$ of |      |

|      | the crossbar arrays shown in (a), (c) (5) Histogram of the measured conduc-            |      |

|      | tance for 1-bit case for different wire resistance, (d) and (e) Histograms of the      |      |

|      | normalized conductance for 3-bit and 4-bit cases at $R_w = 1\Omega$ .                  | 141  |

| 5.27 | Circuit model of the crossbar array.                                                   | 142  |

|      | The generated masks for 2-bit neural network training                                  | 148  |

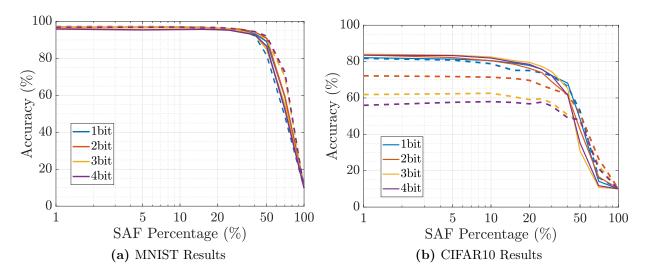

|      | Effect of changing the SAF percentage on the recognition accuracy using                | _    |

|      | mapping-I. Solid line refers to multiple mask trained network results and              |      |

|      | dashed line shows stochastic mask trained network results                              | 155  |

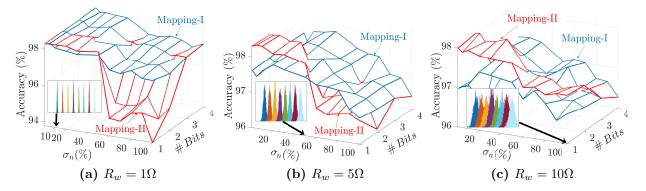

| 5.30 | Effect of changing the variability of each conductance's state on the recogni-         |      |

|      | tion accuracy using mapping II. Dashed lines show the validation accuracy              |      |

|      | drop with pre-trained weights with multiple mask technique. Solid lines show           |      |

|      | the accuracy drop after retraining with additive noise                                 | 155  |

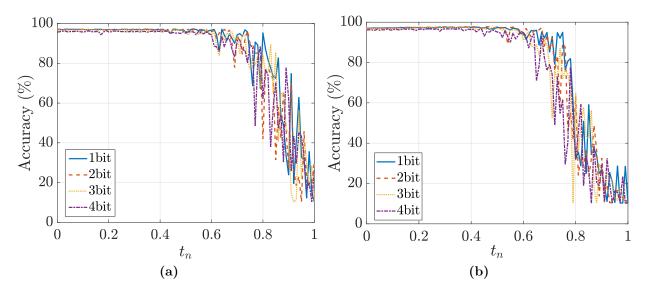

| 5.31 | MNIST Recognition Accuracy against normalized retention time for a) $v_d =$            |      |

|      | 10, and b) $v_d = 0.1$                                                                 | 158  |

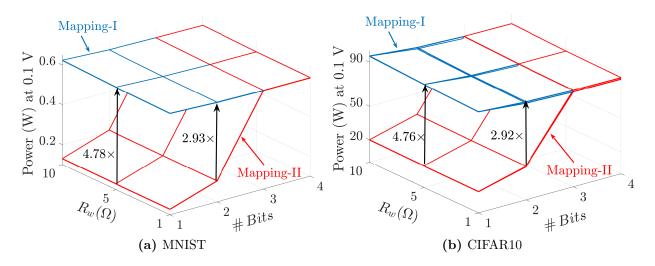

| 5.32 | Static power dissipation in RCAs per image at $0.1V$ read voltage                      | 159  |

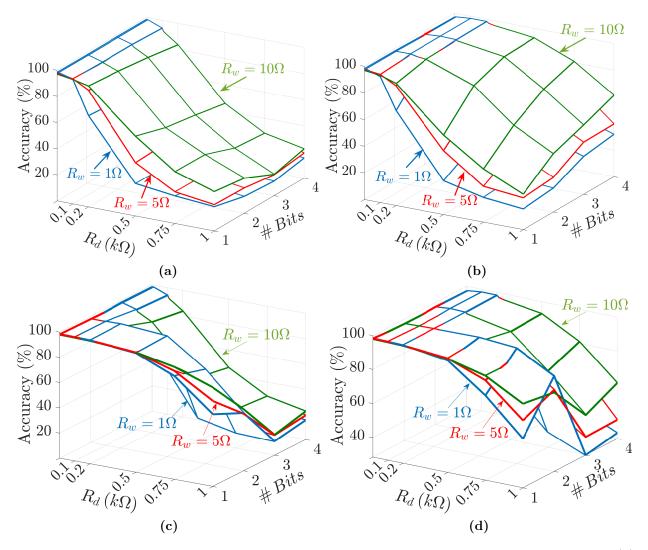

|      | Effect of the driver resistance on the performance of MNIST recognition; (a)           |      |

|      | and (b) for Mapping-I and (c) and (d) for mapping-II with multiple mask                |      |

|      | training for (a) and (c) and with stochastic mask training for (b) and (d)             | 160  |

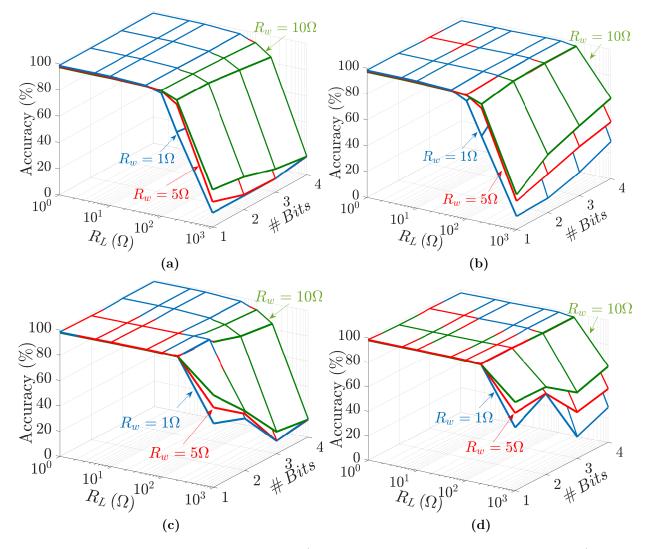

| 5.34 | Effect of the load resistance (the input resistance of the sensing circuit) on         |      |

|      | the performance of MNIST recognition; (a) and (b) for Mapping-I and (c)                |      |

|      | and (d) for mapping-II with multiple mask training for (a) and (c) and with            |      |

|      | stochastic mask training for (b) and (d).                                              | 161  |

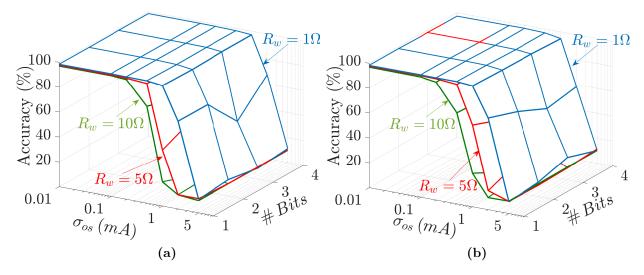

| 5.35 | Effect of the neuronal offset current deviation on the performance of MNIST            |      |

|      | recognition for Mapping-I; (a)multiple mask training and (b) stochastic mask           |      |

|      | training.                                                                              | 162  |

| 0.1  |                                                                                        | 1.0- |

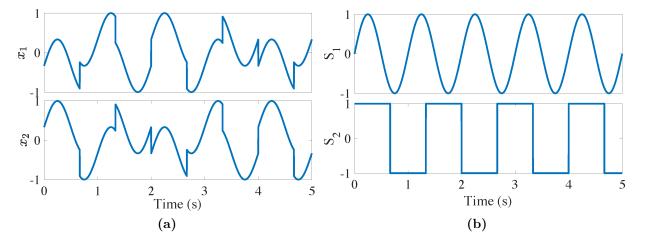

| 6.1  | (a)Observed signals (mixtures of sources), and (b) original sources                    | 167  |

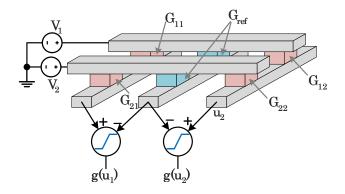

| 6.2  | Illustration of used RRAM crossbar array to realize the ICA preceptron network         | .169 |

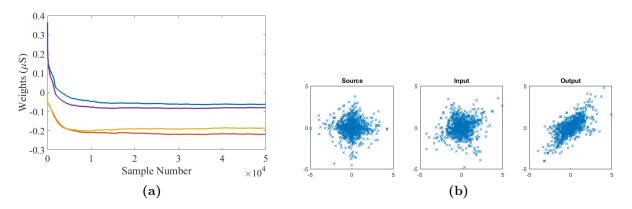

|                                                                                                | .171                                                                                                                                                         |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                |                                                                                                                                                              |

|                                                                                                | 175                                                                                                                                                          |

|                                                                                                | 110                                                                                                                                                          |

| pabilities                                                                                     | 177                                                                                                                                                          |

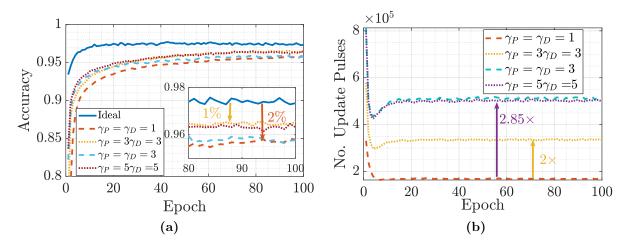

| RRAM's conductance change relation with number of pulses                                       | 179                                                                                                                                                          |

| Ideal validation with limited weight range and with stochastic rounding at                     |                                                                                                                                                              |

|                                                                                                | 180                                                                                                                                                          |

|                                                                                                |                                                                                                                                                              |

|                                                                                                | 183                                                                                                                                                          |

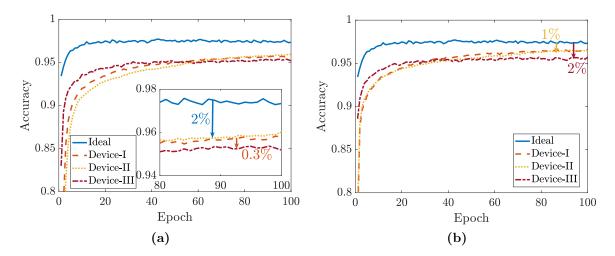

| MNIST recognition accuracy for three different devices with a) $\gamma_P = \gamma_D = 1$       |                                                                                                                                                              |

| and b) $\gamma_P = 3\gamma_D = 3$                                                              | 185                                                                                                                                                          |

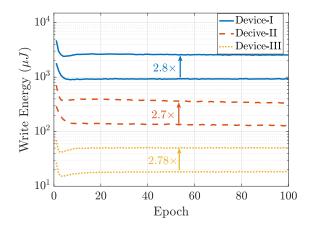

| Total Write Energy for each epoch for $\gamma_P = \gamma_D = 1$ and $\gamma_P = 3\gamma_D = 3$ | 186                                                                                                                                                          |

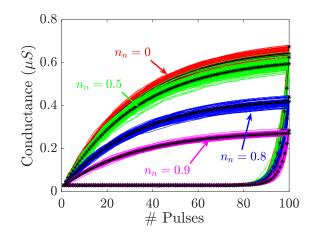

| The potentiation and depression conductance degradation for different nor-                     |                                                                                                                                                              |

| malized programming pulses                                                                     | 188                                                                                                                                                          |

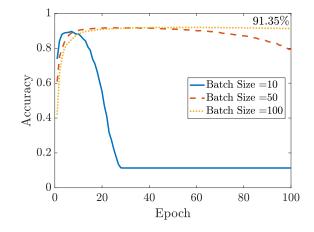

| MNIST test accuracy for different batch sizes with $10^6$ endurance value                      | 188                                                                                                                                                          |

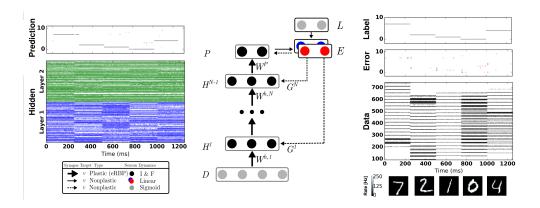

| Network Architecture for Event-driven Random Backpropagation (eRBP).                           |                                                                                                                                                              |

| Reproduced from $[6]$                                                                          | 199                                                                                                                                                          |

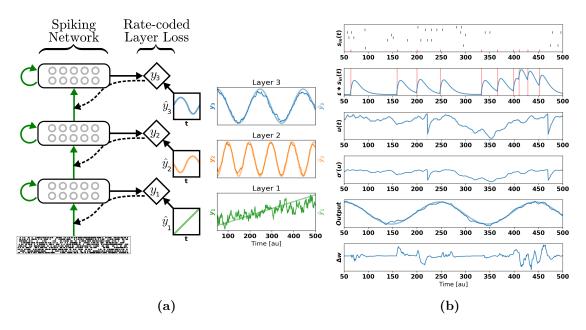

| Deep continuous local learning example. Reproduced from [7]                                    | 201                                                                                                                                                          |

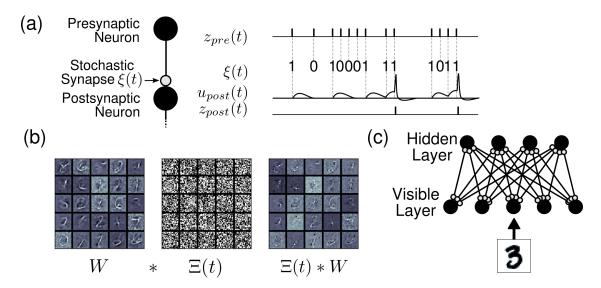

| The Synaptic Sampling Machines (SSM). (a) At every occurrence of a pre-                        |                                                                                                                                                              |

| synaptic event, a pre-synaptic event is propagated to the post-synaptic neuron                 |                                                                                                                                                              |

| with probability $p$ . (b) Synaptic stochasticity can be viewed as a continuous                |                                                                                                                                                              |

| DropConnect method [8] where weights are masked by a binary matrix $\Theta(t)$ ,               |                                                                                                                                                              |

| where * denotes element-wise multiplication. (c) SSM Network architecture,                     |                                                                                                                                                              |

| consisting of a visible and a hidden layer. Reproduced from $[9]$                              | 204                                                                                                                                                          |

|                                                                                                | RRAM's conductance change relation with number of pulses Ideal validation with limited weight range and with stochastic rounding at $K = 1/20$ and $N = 100$ |

# LIST OF TABLES

| 1.1                 | Device characteristics of mainstream and emerging memory technologies [10].                                                                                      | 4                                        |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| $2.1 \\ 2.2$        | Extracted Potentiation parameters of the $Mo/TiO_x/TiN$ device reported in[11]<br>Extracted depression parameters of the $Mo/TiO_x/TiN$ device reported in[11].  | . 23<br>23                               |

| $3.1 \\ 3.2$        | Extracted parasitic inductance of three parallel interconnect wires at 1GHz $$ . Extracted parasitic capacitance of three parallel interconnect wires at 1GHz $$ | 30<br>31                                 |

| $4.1 \\ 4.2$        | The proposed readout circuit parameters. $\dots$                                         | 72<br>76                                 |

| $5.1 \\ 5.2 \\ 5.3$ | Weight-conductance mapping for quantized states                                                                                                                  | 107<br>124                               |

| 5.4                 | figuration                                                                                                                                                       | 124                                      |

| 5.5                 | arrays configuration                                                                                                                                             | $\begin{array}{c} 125\\ 132 \end{array}$ |

| 5.6                 | MNIST validation Accuracy for different hardware configurations                                                                                                  | 134                                      |

| 5.7                 | Comparison between 1T1R and 0T1R architectures                                                                                                                   | 139                                      |

| 5.8                 | Fitted Lognormal distributions of multiplicative noise for each state                                                                                            | 147                                      |

| 5.9                 | MLP network configuration (MNIST dataset)                                                                                                                        | 150                                      |

| 5.10                | CNN configuration (CIFAR10 dataset)                                                                                                                              | 150                                      |

|                     | Validation accuracy without retraining                                                                                                                           | 151                                      |

|                     | Multiple Mask set                                                                                                                                                | 151                                      |

| 5.13                | MNIST dataset validation results using Mapping-II after retraining with stochast                                                                                 | -                                        |

|                     | tic mask and multiple mask sets.                                                                                                                                 | 151                                      |

| 5.14                | CIFAR10 dataset validation results after retraining                                                                                                              | 153                                      |

| $6.1 \\ 6.2$        | Comparison between RRAM- and transistor-based ICA realization Extracted model parameters of the three devices understudy. ANLF is the                            | 176                                      |

|                     | asymmeteric nonlinearity factor and ASF is the asymmetery factor,                                                                                                | 184                                      |

| 6.3 | Recognition Error in Idealized Spiking Neural Network Simulations Averaged |     |

|-----|----------------------------------------------------------------------------|-----|

|     | over 5 Runs                                                                | 191 |

# LIST OF ALGORITHMS

|     | Р                                  | age |

|-----|------------------------------------|-----|

| 5.1 | Modified BinaryNet algorithm       | 123 |

| 5.2 | Proposed IR-QNN Training Algorithm | 145 |

| 6.1 | Proposed Training Algorithm.       | 173 |

# ACKNOWLEDGMENTS

Firstly, I would like to express my deepest gratitude to my adviser, Professor Ahmed Eltawil, for his support and motivation throughout my PhD journey at UCI. I am thankful to him for giving me the opportunity to expand my knowledge to new and diverse research directions which are reflected in this thesis.

Secondly, I would also like to thank Prof. Fadi Kurdahi for the thoughtful discussions which always opened new doors to me and helped me overcome several challenges in my research. He always promoted my work and encouraged me to go further. I would also like to gratefully thank Prof. Emre Neftci for teaching me two courses on neuromorphic engineering in which I learned a lot about the field. The conversations with him were always exciting and motivating to explore new directions in this field.

I would also like to thank Prof. Nikil Dutt for dedicating some of his time to serve in my qualification and defense committees.

I would also like to thank our collaborators Dr. Marwen Zorgui and Prof. Zhiying Wang at UCI and Prof. Jongeun Lee and Sugil Lee at UNIST, Korea who have been actively co-worked with me on several successful projects with fruitful discussions.

I would like to thank my friends for their support and motivation especially, Mahmoud Taha, Omar Abdallah, Mohammed Eletriby, Mohammed Abdelghany, Wael Elsharkasy.

Most importantly, I would like to thank my dear parents, my twin brother, and my sisters who were always supporting me and encouraging me with their best wishes.

Last but not least, this work would not have been possible without the constant support of my beloved wife, Radwa Hanafy who sacrificed a lot of things and taking care of our son, Adam, to give me a chance to focus and finish my PhD.

Thank you all.

## Vita

### Mohammed E. Fouda

#### **EDUCATION**

| <b>Doctor of Philosophy in Electrical Engineering and Computer Sci</b><br>University of California-Irvine <i>Irvine, California</i> | ience 2020                            |

|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Master of Science in Engineering Mathematics<br>Cairo University, <i>Giza</i> , <i>Egypt</i>                                        | 2014                                  |

| Bachelor of Science in Electronics and Communications Engineeric<br>Cairo University, <i>Giza</i> , <i>Egypt</i>                    | 1000000000000000000000000000000000000 |

| RESEARCH EXPERIENCE                                                                                                                 |                                       |

| Graduate Research Assistant<br>University of California, Irvine, California                                                         | 2015 - 2020                           |

| Graduate Research Assistant                                                                                                         | 2011 - 2014                           |

Cairo University, Giza, Egypt

#### PUBLICATIONS

- 1. M. E. Fouda, S. Lee, J. Lee, A. Eltawil, and F. Kurdahi, ' ' IR-QNN Framework: An IR Drop-Aware Offline Training Of Quantized Crossbar Arrays' ', under review .

- 2. M. Payvand, **M. E. Fouda**, F. Kurdahi, A. Eltawil and E. Neftci "Error-triggered Three-Factor Learning Dynamics for Crossbar Arrays", AICAS, 2020.

- 3. S. Lee, **M. E. Fouda**, J. Lee, A. Eltawil, and F. Kurdahi, 'Efficient Sneak Path-aware Training of Binarized Neural Networks' ', DAC, Under review.

- 4. M. E. Fouda, E. Neftci, A. Eltawil and F. Kurdahi, ' 'Effect of Asymmetric Nonlinearity Dynamics in RRAMs on Spiking Neural Network Performance ' ',Asilomar Signal Processing, 2019.

- 5. M. E. Fouda, F. Kurdahi, A. Eltawil, E. Neftci, "Spiking Neural Networks for Inference and Learning: A Memristor-based Design Perspective", Memristive Devices for Brain-Inspired Computing, 2020.

- 6. M. Zorgui, **M. E. Fouda**, Z. Wang, A. Eltawil, and F. Kurdahi, ' 'Non-Stationary Polar Codes for Resistive Memories' ', Globecom, 2019.

- 7. M. E. Fouda, S. Lee, J. Lee, A. Eltawil, and F. Kurdahi, "Mask Technique for Fast and Efficient Training of Binary Resistive Crossbar Arrays", IEEE TNANO, 2019.

- 8. M. E. Fouda, A. Allagui, A. Elwakil, A. Eltawil, and F. Kurdahi ' 'Supercapacitor Discharge under Constant Resistance, Constant Current and Constant Power Loads" Journal of Power Sources, 2019

- 9. M. E. Fouda, E. Neftci, A. Eltawil, and F. Kurdahi, "Independent Component Analysis using RRAMs", IEEE Transactions on Nanotechnology, 2018.

- M. E. Fouda, A. Eltawil, and F. Kurdahi, 'Activated Current Sensing Circuit for Memristive Neuromorphic Networks' ', NEWCAS, 2019.

- 11. M. E. Fouda, J. Lee, A. Eltawil, and F. Kurdahi, "Overcoming Crossbar Nonidealities in Binary Neural Networks Through Learning", NANOARCH, 2018.

- 12. M. E. Fouda, A. Eltawil, and F. Kurdahi, ' 'One Step Row Readout Technique for High-Density Resistive Memories' ', Arxiv.

- 13. M. E. Fouda, A. Eltawil and F. Kurdahi. "Modeling and Analysis of Passive Switching Crossbar Arrays", IEEE Transactions of Circuits and systems I, 2018.

- 14. M. E. Fouda, A. E. Khorshid, I. Alquaydheb, A. Eltawil, and F. Kurdahi "Extracting the Cole-Cole Model Parameters of Tissue-mimic Materials" BIOCAS, 2018

- 15. M. E. Fouda, A. Eltawil, and F. Kurdahi, "Minimal Disturbed Bits in Writing Resistive Crossbar Memories", NANOARCH, 2018.

- 16. M. E. Fouda, A. Eltawil and F. Kurdahi. "On One Step Row Readout Technique for Gateless Resistive Arrays", MWSCAS 2017 (Selected as one of the best 10 papers).

- M. A. Bahloul, M. E. Fouda, R. Naous, M. A. Zidan, A. M. Eltawil, F. Kurdahi and K. N. Salama. "Design and Analysis of 2T-2M Ternary Content Addressable Memories", MWSCAS 2017.

- 18. H. Yantir, M. E. Fouda, A. Eltawil and F. Kurdahi, ' 'Process Variations-Aware Resistive Associative Processor Design", ICCD2016.

## ABSTRACT OF THE DISSERTATION

Efficient Offline and Online Training of Memristive Neuromorphic Hardware

By

Mohammed E. Fouda

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Irvine, 2020

Professor Ahmed Eltawil, Chair

Brain-inspired neuromorphic systems have witnessed rapid development over the last decade from both algorithmic and hardware perspectives. Neuromorphic hardware promises to be more energy- and speed- efficient as compared to traditional Von-Neumann architectures. Thanks to the recent progress in solid-state devices, different nanoscale-nonvolatile memory devices, such as RRAMs (memristors), STT-RAM and PCM, support computations based on mimicking biological synaptic response. The most important advantage of these devices is their ability to be sandwiched between interconnect wires creating crossbar array structures that are inherently able to perform matrix-vector multiplication (MVM) in one step. Despite the great potential of RRAMs, they suffer from numerous nonidealities limiting the performance, including, high variability, asymmetric and nonlinear weight update, endurance, retention and stuck at fault (SAF) defects in addition to the interconnect wire resistance that creates sneak paths. This thesis will focus on the application of RRAMs for neuromorphic computation while accounting for the impact of device nonidealities on neuromorphic hardware.

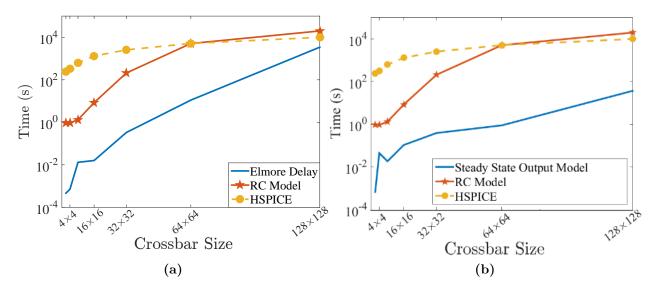

In this thesis, we first develop a compact SPICE-like framework for the resistive crossbar array that incorporates the RRAM device model and interconnect parasitics such as wire resistance, inductance, capacitance, and conductance. This framework is the corner-stone of the simulation infrastructure developed in this work, allowing for  $\geq 1000 \times$  faster simulation results as compared to SPICE. Second, we propose novel reading and writing techniques to read and write the entire word in one clock cycle with an optimized bias scheme to minimize the write errors. To complete the memory design, the required reading and writing CMOS peripheral circuits are designed as well. Due to the inevitable existence of the sneak path problem in crossbar arrays, nonstationary polar codes are designed to mitigate the effect of this problem for crossbar-based memory applications showing a significant improvement in bit-error-rate performance.