## UC San Diego UC San Diego Electronic Theses and Dissertations

#### Title

A design study on the scaling limit of ultra-thin silicon- on-insulator MOSFETs

**Permalink** https://escholarship.org/uc/item/4tc4q3zk

**Author** Lu, Wei-Yuan

Publication Date 2007

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA, SAN DIEGO

## A Design Study on the Scaling Limit of Ultra-Thin Silicon-on-Insulator MOSFETs

A dissertation submitted in partial satisfaction of the

requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Applied Physics)

by

Wei-Yuan Lu

Committee in charge:

Professor Yuan Taur, Chair Professor Peter M. Asbeck Professor Elizabeth Jenkins Professor Andrew Kummel Professor Edward Yu

2007

Copyright

Wei-Yuan Lu, 2007

All rights reserved

The dissertation of Wei-Yuan Lu is approved, and it is acceptable in quality and form for publication on microfilm:

Chair

University of California, San Diego

2007

## **DEDICATION**

This dissertation is dedicated to my wife, parents and sister.

## TABLE OF CONTENTS

| SIGNATURE PAGEiii   |

|---------------------|

| DEDICATIONiv        |

| TABLE OF CONTENTSv  |

| LIST OF FIGURES     |

| LIST OF TABLES      |

| ACKNOWLEDGEMENTS xv |

| VITAxvii            |

| PUBLICATIONSxvii    |

| ABSTRACTxviii       |

| 1 | CHA  | PTER 1    | l: Introduction                           |    |

|---|------|-----------|-------------------------------------------|----|

|   |      |           |                                           |    |

|   | 1.1  | Histor    | y and future trends of CMOS logic scaling | 1  |

|   | 1.2  | Backg     | round                                     | 5  |

|   |      | 1.2.1     | SOI CMOS                                  | 5  |

|   |      | 1.2.2     | Partially-depleted SOI MOSFETs            | 6  |

|   |      | 1.2.3     | Fully-depleted SOI vs. bulk MOSFETs       | 7  |

|   | 1.3  | Outline   |                                           |    |

|   | Refe | erences . |                                           | 12 |

|   |      |           |                                           |    |

| 2 | CHAPTER 2:   | Review | of Previous | Analytical | Models or | n Sacling of | Bulk |

|---|--------------|--------|-------------|------------|-----------|--------------|------|

|   | and SOI MOSE | ETs    | •••••       | ••••••     | •••••     |              |      |

| 2.1  | Scale-length model for bulk MOSFETs                  |    |  |  |

|------|------------------------------------------------------|----|--|--|

| 2.2  | General scale-length model for 2-and 3-layer MOSFETS | 17 |  |  |

| 2.3  | Review of other literature                           |    |  |  |

| Refe | References                                           |    |  |  |

####

| 3.1  | Device     | e structures for 2-D numerical simulation                       | 25 |  |

|------|------------|-----------------------------------------------------------------|----|--|

| 3.2  | Short-     | channel effect                                                  | 28 |  |

| 3.3  | Inappl     | icability of the general scale-length model                     | 31 |  |

|      | 3.3.1      | Correlations between scale length and lateral field penetration | 31 |  |

|      | 3.3.2      | Electric field distribution in thick buried-oxide               | 36 |  |

| 3.4  | Short-     | channel scaling in undoped FDSOI MOSFETS                        | 40 |  |

| 3.5  | Summ       | ary                                                             | 45 |  |

| Refe | References |                                                                 |    |  |

####

| 4.1  | Effect of body doping                               |    |  |  |

|------|-----------------------------------------------------|----|--|--|

| 4.2  | Effect of buried-insulator bandgap and permittivity |    |  |  |

|      | 4.2.1 Effect of bandgap                             |    |  |  |

|      | 4.2.2 Effect of permittivity                        | 61 |  |  |

| 4.3  | Effect of reverse substrate biasing                 |    |  |  |

| 4.4  | Effect of Si-BOX interface traps                    | 71 |  |  |

| 4.5  | Summary                                             |    |  |  |

| Refe | References                                          |    |  |  |

####

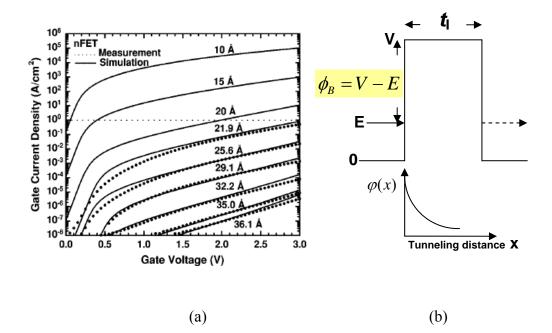

| 5.1 | Scaling limit of gate-insulator thickness | 81   |

|-----|-------------------------------------------|------|

| 5.2 | Scaling limit of silicon film-thickness   | . 83 |

| 5.2.2 Quantum effect on the short-channel behavior of FDSOI MOSFETs | 87    |

|---------------------------------------------------------------------|-------|

| 5.3 Scaling limit of ultra-thin FDSOI devices                       | 91    |

| 5.4 Mobility degradation in ultra-thin silicon film                 | 93    |

| 5.4.1 Influences of buried-oxide interface roughness on mobility    | 94    |

| 5.4.2 Quantum mechanical effects on low-field carrier mobility      | 97    |

| 5.5 Summary                                                         | 99    |

| References                                                          | . 101 |

|                                                                     |       |

| 6 | CHAPTER | 6: | Conclusion |  | 10 | 2 |

|---|---------|----|------------|--|----|---|

|---|---------|----|------------|--|----|---|

## LIST OF FIGURES

#### **CHAPTER 1**

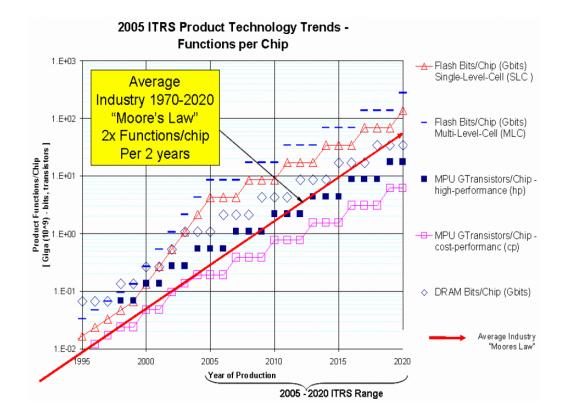

| Figure 1.1 | 2005 ITRS product technology trend: product functions/chip and industry average "Moore's Law" trends. Adapted from [1.1]                                                 | 1 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

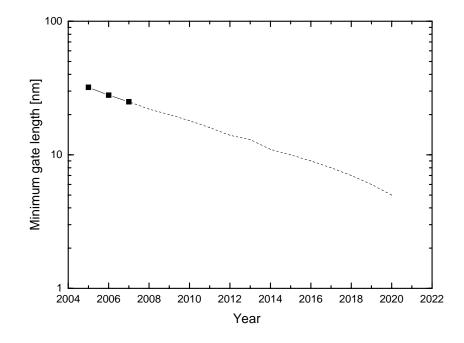

| Figure 1.2 | Predicted and observed minimum MOS gate length versus time<br>showing the exponential decreasing of physical gate length with the<br>passage of time. Adapted from [1.1] | 2 |

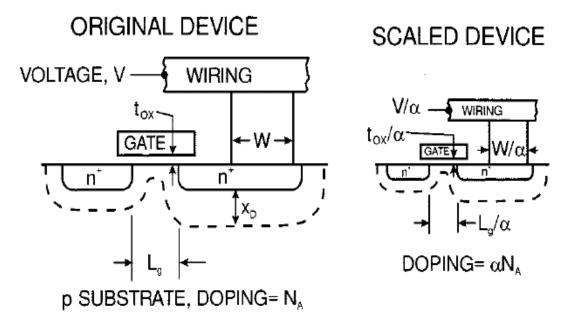

| Figure 1.3 | Schematic illustration of the scaling of Si technology by a factor $\alpha$ .<br>Adapted from [1.2].                                                                     | 3 |

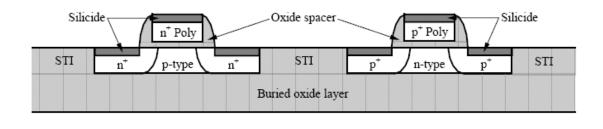

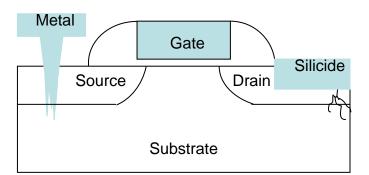

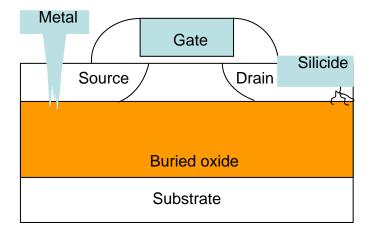

| Figure 1.4 | A schematic cross section of SOI CMOS, with shallow trench isolation (STI), dual polysilicon gates, and self-aligned silicid                                             | 6 |

| Figure 1.5 | Formation contact or silicide on shallow junctions in the case of (a) bulk silicon and (b) thin-film SOI.                                                                | 8 |

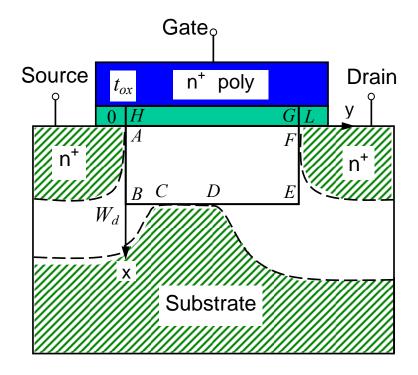

| Figure 2.1 | Simplified geometry for analytically solving Poisson's equation in a short-channel MOSFET. Adapted from [2.1]                                                                                                                                                                                         |

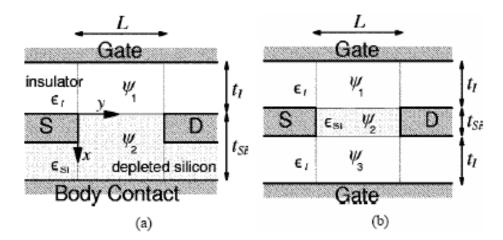

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2 | Idealized schematic cross section diagram of (a) a bulk MOSFET (b) a double-gate MOSFET, defining the insulatorthickness $t_I$ and the depleted Si thickness $t_{Si}$ . $\varepsilon_{Si}$ is the permittivity of Si and $\varepsilon_I$ is the permittivity of gate insulator(s). Adapted from [2.2] |

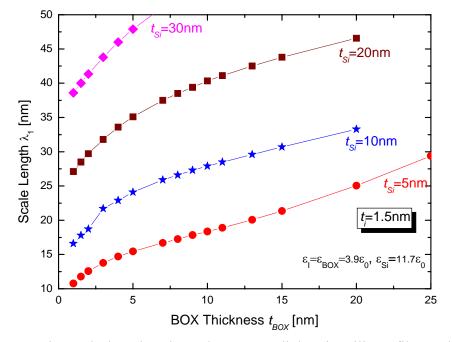

| Figure 2.3 | The scale length $\lambda_1$ depends on gate dielectric, silicon film and buried oxide thickness                                                                                                                                                                                                      |

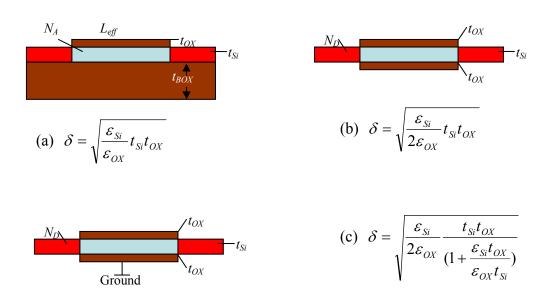

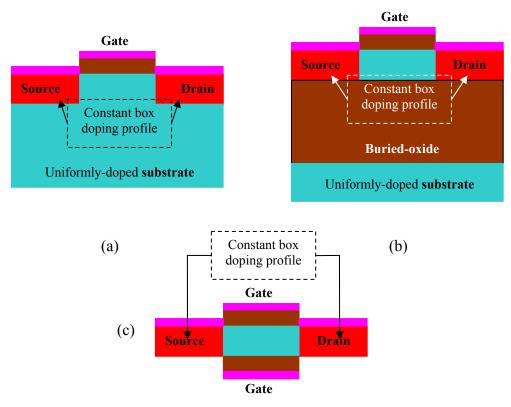

- Figure 3.1Device structures of (a) bulk, (b) SOI, and (c) double-gateMOSFETs used in 2-D numerical simulations. Box-like doping<br/>profile is assumed in our design study.26

| Figure 3.7 | Simplified geometry for analytically solving Poisson's equation in a short-channel FDSOI MOSFET. Dashed lines mean unspecified potential on the boundaries |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.8 | Simulated (a)lateral-field variation along the channel surface and (b)field pattern for a long-channel thick-BOX FDSOI device [3.4] 37                     |

- **Figure 3.9** Simulated (a)lateral-field variation along the channel surface and (b)field pattern for a short-channel thick-BOX FDSOI device [3.4]...38

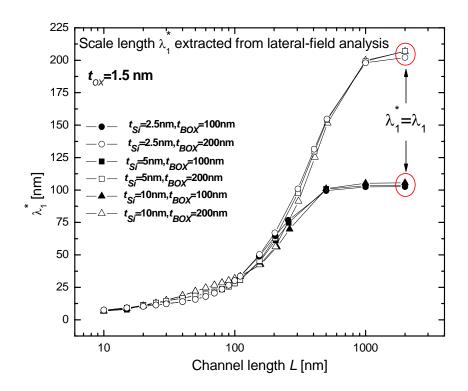

- **Figure 3.10** The extracted scale length  $\lambda_1^*$  versus channel length.  $\lambda_1^*$  is calculated by  $\frac{\pi}{|slope|}$ , where the |slope| is obtained by lateral-field analysis......39

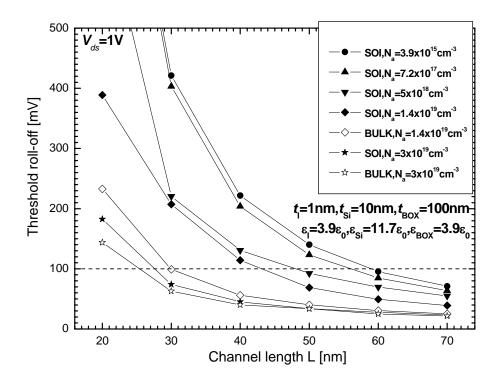

| Figure 4.1 | High-drain threshold roll-offs for FDSOI and bulk nMOSFETs with different channel doping concentrations. The $L_{min}$ of lightly doped FDSOI device can be reduced by a factor of 1.3 with a moderate channel doping concentration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

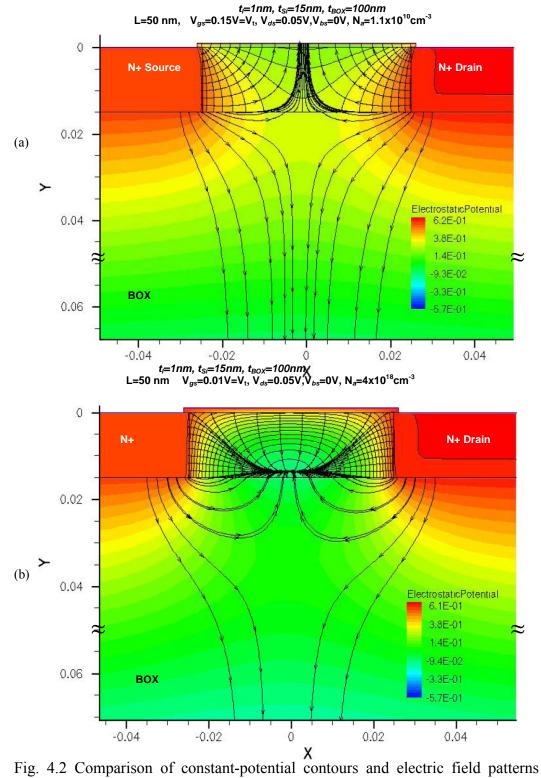

| Figure 4.2 | Comparison of constant -potential contours and electric field<br>patterns inside silicon body between (a) undoped and (b) doped<br>FDSOI MOSFETs. Both devices are biased at the same off-current<br>level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

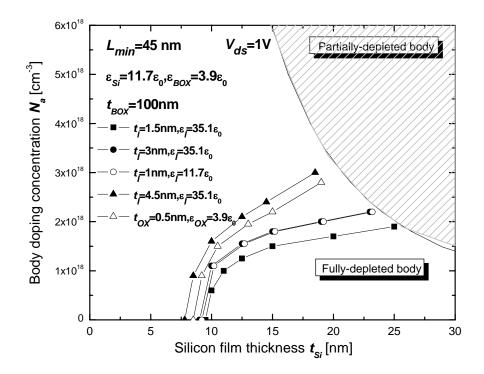

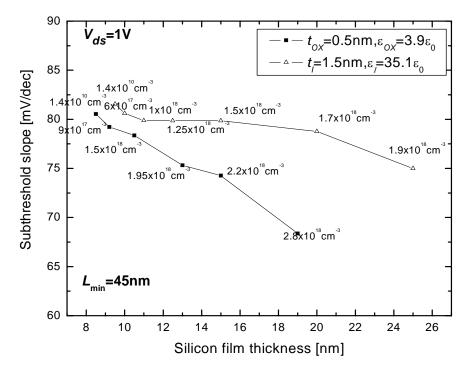

| Figure 4.3 | Constant minimum channel length ( $L_{min}$ = 45 nm) contours for doped FDSOI devices with three different gate dielectrics [4.4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 4.4 | Subthreshold slopes for the corresponding data points of the $L_{min}$ contours with $t_{OX} = 0.5$ nm and $t_I = 1.5$ nm in Fig. 4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

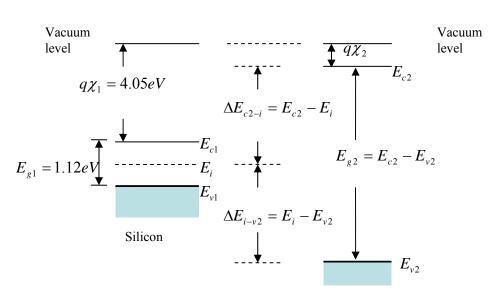

| Figure 4.5 | Buried-insulator bandgap adjustment illustrated by energy-band diagram of the silicon and buried-insulator. The conduction-band difference and valence-band difference between the buried-insulator and silicon are adjusted symmetrically ( $\Delta E_{c2-i} = \Delta E_{i-v2}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

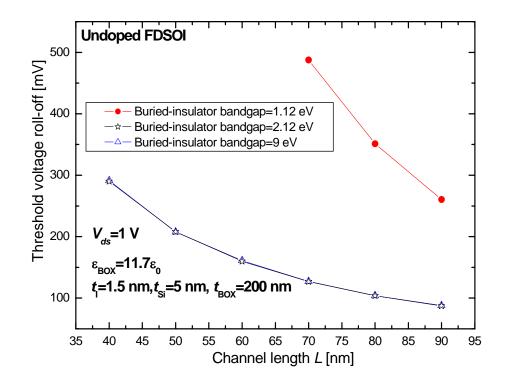

| Figure 4.6 | Threshold voltage roll-offs for different FDSOI devices with different buried-insulator bandgap values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

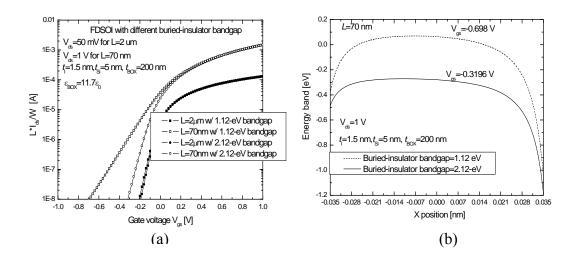

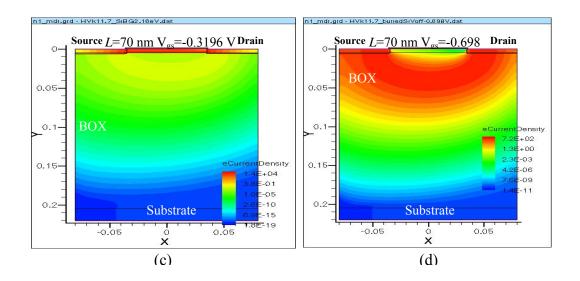

| Figure 4.7 | (a) Threshold voltage roll-off comparison between FDSOI devices with $\varepsilon_{BOX} = 11.7\varepsilon_0$ and the buried-insulator bandgap equal to 1.12eV and 2.12eV. (b) Potential barriers at device channel surface at V <sub>gs</sub> =-0.3196 V and -0.698 V for buried-insulator bandgap equal to 1.12eV and 2.12eV, separately. (c) Electron current density of <i>L</i> =70 nm SOI device conducting in the buried-insulator with a silicon dielectric constant and bandgap=2.12eV at V <sub>gs</sub> =-0.3196 V. (d) Electron current density of <i>L</i> =70 nm SOI device conducting in the buried-insulator with a silicon dielectric constant and bandgap=2.12eV at V <sub>gs</sub> =-0.3196 V. (d) Electron current density of <i>L</i> =70 nm SOI device conducting in the buried-insulator with a silicon dielectric constant and bandgap=1.12eV at V <sub>gs</sub> =-0.698 V |

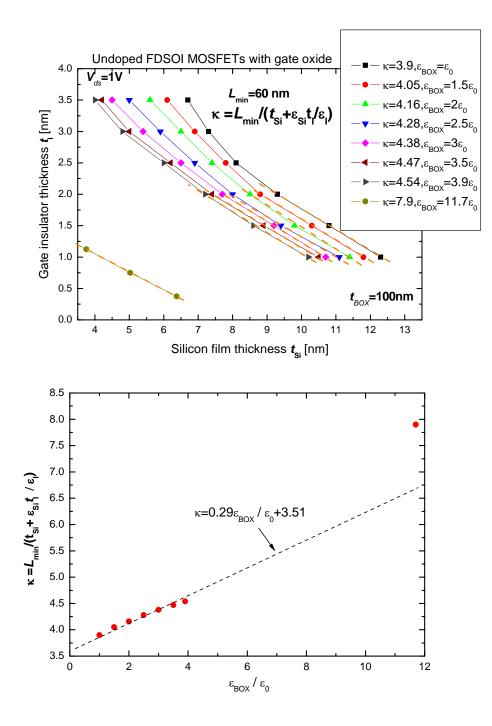

| Figure 4.8 | (a) Constant $L_{min} = 60 \text{ nm}$ contours for FDSOI devices with different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            | permittivities. (b) The linear relation between $\kappa$ and $\frac{\varepsilon_{BOX}}{\varepsilon_0}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

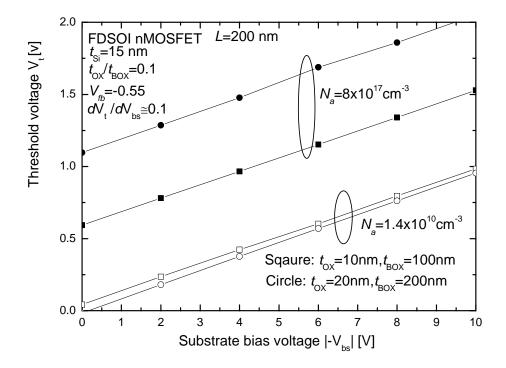

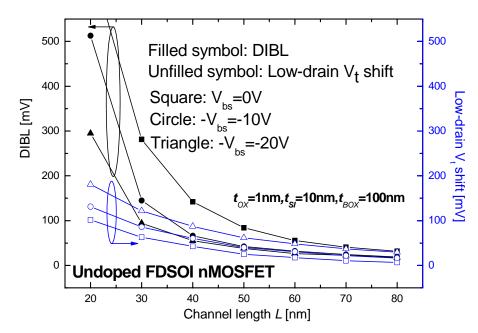

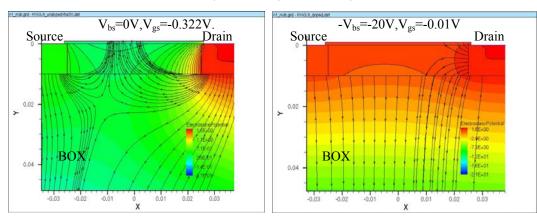

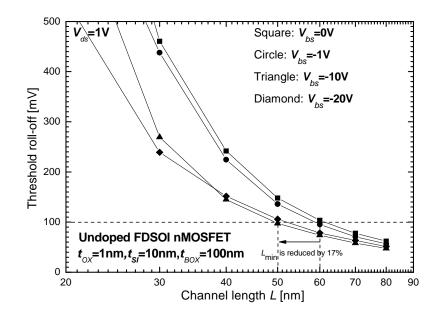

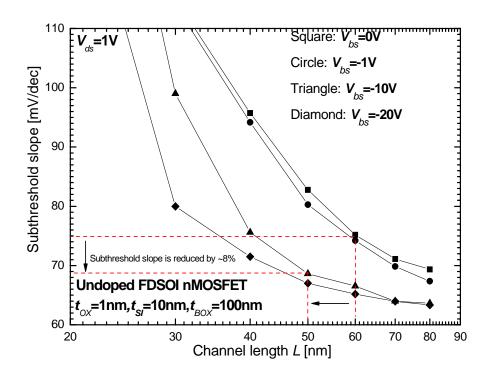

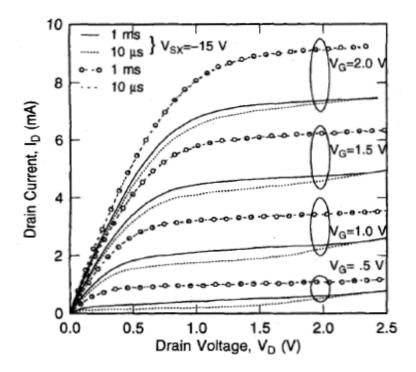

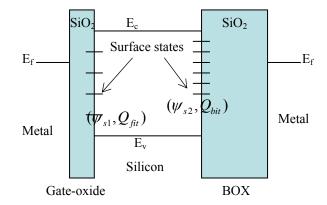

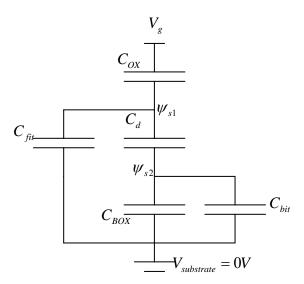

Figure 4.10 Threshold-voltage as function of reverse substrate bias voltage in thick buried-oxide FDSOI devices with constant  $t_{OX}/t_{BOX}$  ratio equal Figure 4.11 The threshold voltage of undoped FDSOI devices as a function of Figure 4.12 The effect of the reverse substrate bias voltage on low-drain V<sub>t</sub> shift and DIBL. Applying -V<sub>bs</sub> to short-channel devices acts on low-drain and high-drain short-channel behaviors in two different ways. The Comparison of the electric field pattern in the BOX between Figure 4.13 L=50nm FDSOI devices with and without reverse substrate biasing. A high-drain voltage ( $V_{ds}=1V$ ) is applied to both devices. The gate voltage is biased under the same off-current condition (normalized  $I_{ds} = 1e-8$  A) in both devices. The source/drain lateral field coupling into the channel can be reduced by applying a high reverse substrate High-drain threshold roll-offs for FDSOI nMOSFETs with the Figure 4.14 substrate reverse biased at different voltages. The  $L_{\min}$  is reduced 17% smaller from  $V_{bs}=0$  V to  $-V_{bs}=-10V$ .  $-V_{bs}=-20$  V has Figure 4.15 Subthreshold slopes for FDSOI nMOSFETs with the substrate reverse biased at different voltages. The subthreshold slope of the FDSOI device with  $L_{min}$ =60nm is reduced by 8% from V<sub>bs</sub>=0 V to -Figure 4.16 Output curves of a fully depleted nFET operated with the normally grounded substrate (backgate), and with the substrate biased below the source voltage, at two pulse periods. The device has nominal silicon thickness of 70 nm, and a channel doping of  $2x10^{17}$  /cm<sup>3</sup>. Adapted from [4.7]......70 Figure 4.17 Schematic energy-band diagram of an SOI MOS structure,

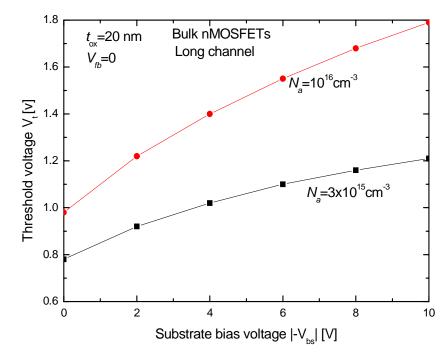

Threshold-voltage variation with reverse substrate bias for two

Figure 4.9

| Figure 4.18 | Equivalent circuit of the FDSOI MOS capacitor. Adapted from [4.8]                               |

|-------------|-------------------------------------------------------------------------------------------------|

| Figure 4.19 | Buried-oxide layer formatioin in SIMOX technology74                                             |

| Figure 4.20 | Process flow of (a) Unibond <sup>®</sup> [4.16] and (b) ELTRAN <sup>®</sup> [4.17] technology75 |

#### **CHAPTER 5**

| Figure 5.1 | (a) Measured and simulated $I_g-V_g$ characteristics under inversion<br>conditions of n-FETs with oxides. Adopted from [5.1]. (b)<br>Schematic diagram of direct-tunneling effect                                                                                                                                                                            |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

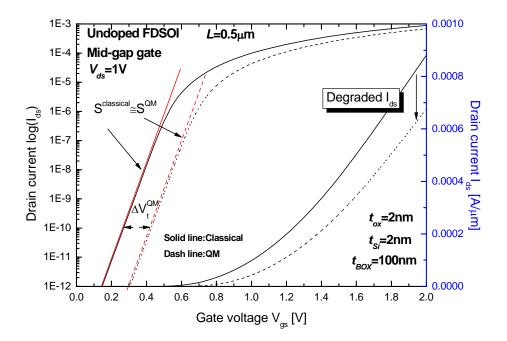

| Figure 5.2 | $I_{ds}$ - $V_{gs}$ curves of a long-channel ultra-thin body FDSOI device obtained by classical and quantum simulations in ISE                                                                                                                                                                                                                               |

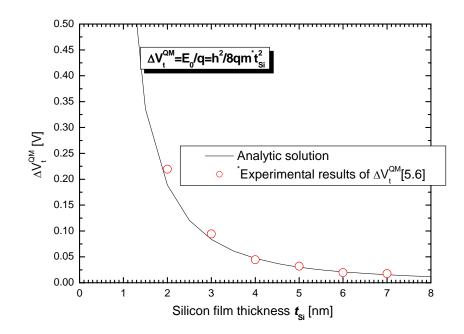

| Figure 5.3 | Comparisons between the analytic solution and the experimental data [4.8] of V <sub>t</sub> shift due to quantum confinement of electrons in a square potential well. The $\Delta V_t^{QM}$ is plotted as a function of the silicon-film thickness                                                                                                           |

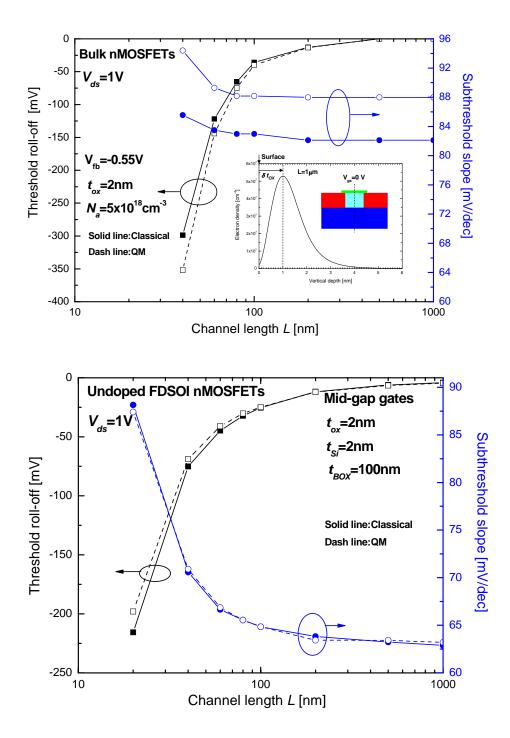

| Figure 5.4 | The threshold roll-off and subthreshold slope of (a) bulk (b) FDSOI MOSFETs obtained by classical and quantum simulations. The inset shows the QM electron density distribution along a vertical cut of the $L=1 \ \mu m$ bulk MOSFET at V <sub>gs</sub> =0 V                                                                                                |

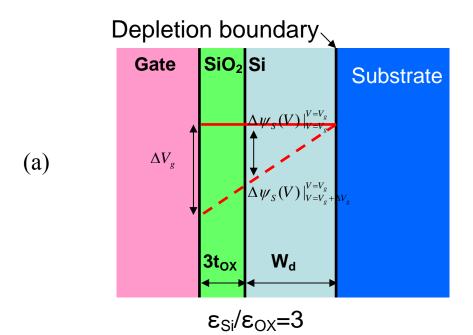

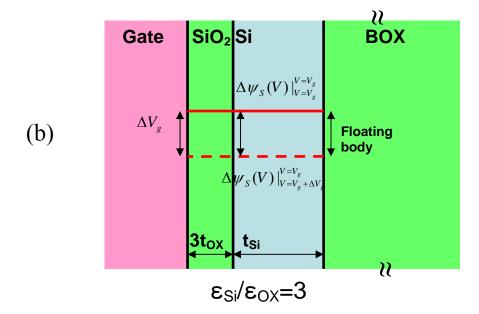

| Figure 5.5 | Illustrations of body effects in (a) bulk and (b) ultra-thin body<br>FDSOI MOSFETs                                                                                                                                                                                                                                                                           |

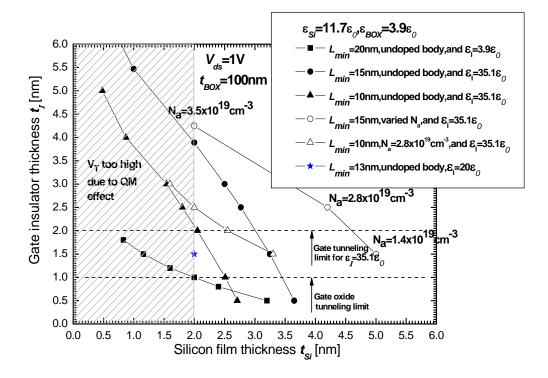

| Figure 5.6 | Design space of sub-20 nm undoped and doped body ultra-thin FDSOI nMOSFETs with gate oxide and high-k gate insulators. The lower region is forbidden by the tunneling leakage limits of gate insulators. The left region is forbidden because of excessive high threshold voltage imposed by quantum confinement of electrons in the ultra-thin silicon film |

| Figure 5.7 | (a) $E_{aff}$ dependence of electron mobility in MOS inversion layer for                                                                                                                                                                                                                                                                                     |

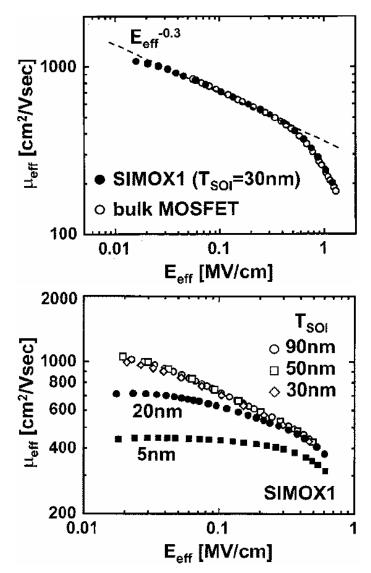

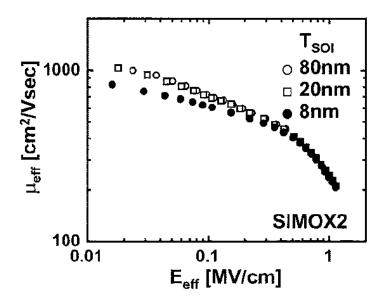

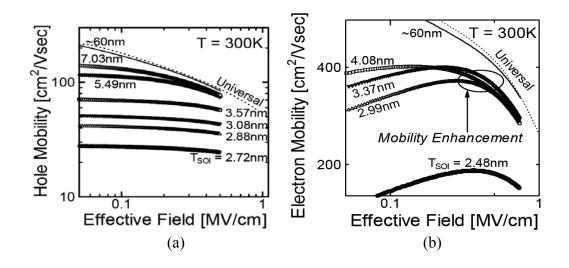

**Figure 5.7** (a)  $E_{eff}$  dependence of electron mobility in MOS inversion layer for SOI and bulk MOSFETs. (b)  $E_{eff}$  dependence of electron mobility

for different silicon film thickness in SIMOX1 transistors having poor quality of buried-oxide interface. Adapted from [5.7]......95

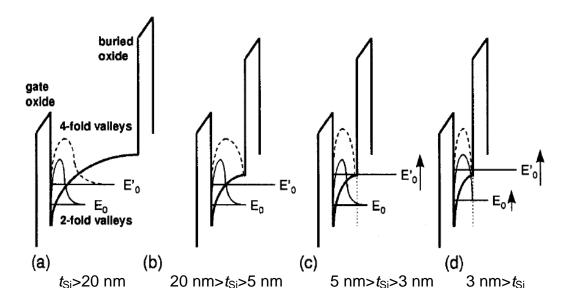

- **Figure 5.8** Schematic diagrams of the band structure of SOI MOSFETs with different silicon film thickness. Adapted from [5.10]......97

- **Figure 5.9** (a) Hole mobility versus effective field for different Si film thickness  $(T_{SOI})$  at 300 K. (b) Electron mobility versus effective field for different Si film thickness  $(T_{SOI})$ . The electron mobility enhancement is observed at  $E_{eff} \sim 0.3$  MV/cm. Adapted from [5.6]. ... 98

### LIST OF TABLES

| Table 1.1 | Technology scaling rules for three cases. Adapted from [1.3]4                               |

|-----------|---------------------------------------------------------------------------------------------|

|           | CHAPTER 5                                                                                   |

| Table 5.1 | Dielectrics permittivities and barriers. Adapted from [5.3]                                 |

| Table 5.2 | Measured interface state density for bulk Si, SIMOX1, and SIMOX2 wafers. Adapted from [5.7] |

#### ACKNOWLEDGMENTS

This dissertation would not have been possible without the love, support and guidance of many people. First and foremost, I am greatly indebted to my advisor, Professor Yuan Taur, for his advice and guidance at every step of my research and this dissertation. I would like to cordially thank him for his patience, encouragement and support over my years as a graduate student. In addition, I am deeply grateful for his advice and help on my career development. Without his love and understanding, I could not have finished my study at UCSD.

I would like to thank my committee members, Professors Peter Asbeck, Edward Yu, Elizabeth Jenkins and Andrew Kummel, for taking their precious time to review my dissertation and give me valuable comments.

Many thanks to my friends in Professor Taur's group, Huaxin, Xiaoping, Wei, Ming, Jooyoung and Minjian, for showing me their friendship, wisdom and encouragement. Special thanks to Bo for his inspiration and insightful opinions, and for endless conversations about research. Without them, my graduate life at UCSD would not have been enjoyable and rewarding.

Most of all, I would like to thank my beloved wife, Hsiao-Ling Wang. Thank her for being there for me through ups and downs of academic and real life. I am forever grateful for her encouragement and for believing in me and reaffirming me when needed. Last but not least, I thank my parents and sister who have given me endless spiritual support. This dissertation is dedicated to them. The text of Chapter 3, in part, is the reprint of the material as it appears in "On The Scaling Limit of Ultrathin SOI MOSFETs" by Wei-Yuan Lu and Yuan Taur, IEEE Transaction on Electron Devices, May 2006. The dissertation author was the primary researcher of this paper.

The text of Chapter 4, in part, is the reprint of the material as it appears in "Effect of Body Doping on the Scaling of SOI MOSFETs" by Wei-Yuan Lu and Yuan Taur, Proceedings of SISPAD, Sep. 2006. The dissertation author was the primary researcher of this paper.

The text of Chapter 5, in part, is the reprint of the material as it appears in "Scaling to 10nm-Bulk, SOI or DG MOSFETs?" by Minjian Liu, Wei-Yuan Lu, Wei Wang and Yuan Taur, Proceedings of ICSICT, Oct. 2006. The dissertation author was the co-author of this paper.

#### VITA

| 1996      | B. S. in Electrical and Computer Engineering, National Cheng Kung University, Taiwan                 |

|-----------|------------------------------------------------------------------------------------------------------|

| 1998      | M. S. in Electrical and Computer Engineering, National Cheng Kung University, Taiwan                 |

| 2000-2001 | Hardware Engineer, Philips System Lab, Taipei, Taiwan                                                |

| 2002-2003 | Research Assistant, Electrical and Computer Engineering,<br>University of Minnesota, USA             |

| 2003-2007 | Research Assistant, Electrical and Computer Engineering,<br>University of California, San Diego, USA |

| 2007      | Ph. D. in Electrical Engineering, University of California, San Diego, USA                           |

#### **PUBLICATIONS**

- 1. **W.-Y. Lu** and Y. Taur, "On the scaling limit of ultra-thin body SOI MOSFETs", *IEEE Trans. Electron Devices*, vol. 53, no. 5, May 2006.

- 2. **W.-Y. Lu** and Y. Taur, "Effect of body doping on the scaling of SOI MOSFETs", *SISPAD*, 2006.

- 3. M. Liu, W.-Y. Lu, W. Wang and Y. Taur, "Scaling to 10nm: Bulk, SOI or Double-Gate MOSFETs?", *ICSICT*, 2006.

- 4. B. Yu, **W.-Y. Lu**, H. Lu and Y. Taur, "Analytic charge and capacitance model for surrounding-gate MOSFETs", *IEEE Trans. Electron Devices*, vol. 54, no. 3, 2007.

- 5. B. Yu, H. Lu, W.-Y. Lu, and Y. Taur, "Analytic charge model for doublegate and surrounding-gate MOSFETs", to appear in Workshop on Compact Modeling, NSTI Nanotech, 2007.

- 6. B. Yu, J. Song, **W.-Y. Lu**, and Y. Taur, "A unified drain current model for multiple-gate MOSFETs", to be submitted.

#### **ABSTRACT OF THE DISSERTATION**

#### A Design Study on the Scaling Limit of Ultra-Thin

#### Silicon-on-Insulator MOSFETs

by

Wei-Yuan Lu

Doctor of Philosophy in Electrical Engineering (Applied Physics)

University of California, San Diego, 2007

Professor Yuan Taur, Chair

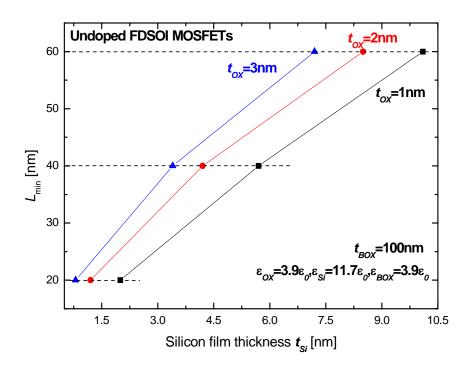

As bulk CMOS is approaching its scaling limit, SOI CMOS is gaining more and more attentions and is considered as a potential candidate for achieving 10-nm CMOS. Fully-depleted SOI MOSFETs have several inherent advantages over bulk MOSFETs-low junction capacitance, no body effect and no need for body doping to confine gate depletion. This dissertation presents a comprehensive, 2-D simulationbased design study on the scaling limit of ultra-thin silicon-on-insulator MOSFETs. Starting with the lateral-field analysis of fully-depleted (FD) SOI MOSFETs, it is shown that the general scale-length model is inapplicable for predicting the minimum scalable channel length  $L_{min}$  when the buried-oxide is very thick. The scaling of FDSOI MOSFETs is independent of the buried-oxide thickness. An empirical  $L_{min}$  prediction equation is developed by approximating the constant  $L_{min}$  contours in a design plane of silicon-film and gate-dielectric thickness. Ultimately,  $L_{min} \sim 5t_{Si}$  with a high-k gate dielectric. Other factors such as body doping, substrate biasing, and buried-insulator permittivity  $\varepsilon_{BOX}$  and bandgap affecting shortchannel scaling of FDSOI are also investigated. Empirical  $L_{min}$  prediction equations are developed for FDSOI devices with body doping and low-k buried-insulators. In principle, the  $L_{min}$  can be improved from  $\sim 5t_{Si}$  to  $\sim 2t_{Si}$  by body doping. The  $L_{min}$  can also be reduced 15% shorter from  $\varepsilon_{BOX} = 3.9\varepsilon_0$  to  $\varepsilon_{BOX} = \varepsilon_0$ .

Finally, the scaling limit of FDSOI MOSFETs is discussed. From the electrostatic perspective 10-nm FDSOI CMOS requires scaling both high-k gatedielectric and silicon-film thickness to their limits of ~2 nm. However, silicon-film thickness cannot below ~3 nm to avoid severe mobility degradation. The scaling limit of FDSOI MOSFETs with a feasible  $HfO_2$  gate dielectric is then projected to be ~17 nm. 10-nm FDSOI CMOS can be achieved only if there is a breakthrough on thin silicon-film mobility.

## **CHAPTER 1**

## Introduction

#### 1.1 History and future trends of CMOS logic scaling

Fig. 1.1 2005 ITRS product technology trend: product functions/chip and industry average "Moore's Law" trends. Adapted from [1.1].

Over the past few decades, successful attempts have been made at decreasing the physical dimensions of MOS transistors to achieve density, speed, and power improvements in CMOS technology. The number of transistors on a chip has consistently doubled every two years, as shown in Fig. 1.1, and the observation is popularly known as Moore's law. In order to sustain the historical trends of device performance improvements, continued aggressive scaling efforts have been made recently for leading-edge logic technology. The most obvious consequence of such scaling efforts is the shrinking MOS transistor gate length, as shown in Fig. 1.2, which presents the observed and predicted viable MOS transistor gate length versus time.

Fig. 1.2 Predicted and observed minimum MOS gate length versus time showing the exponential decreasing of physical gate length with the passage of time. Adapted from [1.1].

The scaling concept of MOSFETs stems from Dennard's research work published in 1974. Fig. 1.3 schematically illustrates the basic idea of constant-field scaling for MOS transistors. Scaling can achieve the same electric-field patterns in the smaller device by reducing the applied voltage along with all the key dimensions and by increasing the impurity doping concentration by the same factor  $\alpha$ . Therefore, a larger MOS transistor can then be scaled down to a smaller one with similar

Fig. 1.3 Schematic illustration of the scaling of Si technology by a factor  $\alpha$ . Adapted from [1.2].

electrostatic behavior. Table 1.1 shows scaling rules for MOSFETs and physical parameters of three different scaling behaviors. According to the constant-filed scaling rule, the circuit speed increases in proportional to the scaling factor  $\alpha$  and the circuit density increases by a factor of  $\alpha^2$ . The technology scaling principles in table 1.1 only provide a guideline how to shrink a known good design of a MOSFET. It does

not tell a device designer how short channel length of a MOSFET he can make for given doping profiles and layer thickness. Moreover, the device channel length cannot be arbitrarily scaled due to short-channel effect (SCE), i.e., threshold voltage roll-off and drain induced barrier lowering (DIBL).

|                          | Constant-      | Generalized              | Generalized                   |

|--------------------------|----------------|--------------------------|-------------------------------|

| Physical parameter       | Electric Field | Scaling                  | Selective                     |

|                          | Scaling Factor | Factor                   | Scaling Factor                |

| Channel length, Insu-    | $1/\alpha$     | 1/lpha                   | $1/\alpha_d$                  |

| lator thickness          |                |                          |                               |

| Wiring width, channel    | 1/lpha         | 1/lpha                   | $1/lpha_w$                    |

| width                    |                |                          |                               |

| Electric field in device | 1              | ε                        | ε                             |

| Voltage                  | 1/lpha         | $\varepsilon/lpha$       | $arepsilon/lpha_d$            |

| On-current per device    | 1/lpha         | $\varepsilon/lpha$       | $arepsilon/lpha_w$            |

| Doping                   | α              | εα                       | $arepsilon lpha_d$            |

| Area                     | $1/\alpha^2$   | $1/lpha^2$               | $1/lpha_w^2$                  |

| Capacitance              | 1/lpha         | 1/lpha                   | $1/lpha_w$                    |

| Gate delay               | 1/lpha         | 1/lpha                   | $1/lpha_d$                    |

| Power dissipation        | $1/\alpha^2$   | $\varepsilon^2/\alpha^2$ | $arepsilon^2/lpha_w lpha_d$   |

| Power density            | 1              | $\epsilon^2$             | $arepsilon^2 lpha_w / lpha_d$ |

Table 1.1 Technology scaling rules for three cases. Adapted from [1.3].

$\alpha$  is the dimensional scaling parameter,  $\varepsilon$  is the electric field scaling parameter, and  $\alpha_D$  and  $\alpha_W$  are separate dimensional scaling parameters for the selective scaling case.  $\alpha_D$  is applied to the device vertical dimensions and gate length, while  $\alpha_W$  applies to the device width and the wiring.

In addition to the channel length scaling limit imposed by short-channel effect, there

are nonscaling effects limiting the applicability of the scaling principles to shrink MOS transistors. For example, the nonscalability of thermal voltage KT/q leads to subthreshold nonscaling, i.e., the threshold voltage cannot be scaled down like other physical parameters. The nonscalability of the silicon energy bandgap leads to the nonscaling of the built-in potential, depletion-layer width, and short-channel effect. The scaling limit of physical dimensions is imposed by quantum mechanical effect. Details of those scaling limits are summarized in [1.3]. There are several ways to circumvent those scaling limits: employing novel device structures to further scale down MOS transistors with the SCE being under control; installing high-k gate dielectrics in MOS transistors to reduce the effective oxide thickness without scaling down the physical thickness below the quantum mechanical tunneling limit.

#### **1.2 Background**

#### 1.2.1 SOI CMOS

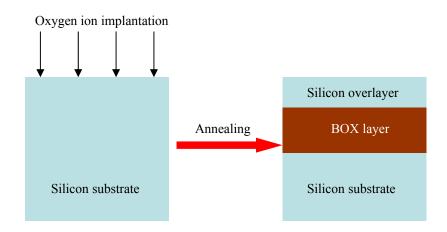

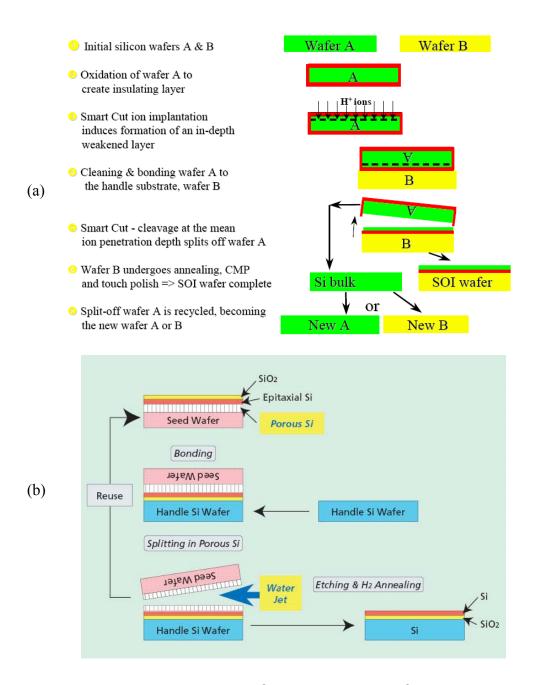

Silicon-on-insulator (SOI) CMOS involves building conventional MOSFETs on very thin layers of crystalline silicon and is illustrated in Fig. 1.4. The thin silicon layer is electrically isolated from the substrate by a thick (typically 100 nm or more) buried-oxide layer. The inherent advantages of SOI devices over bulk CMOS will be addressed in Section 1.2.3. SOI substrates fabricated by oxygen-ion implantation (SIMOX) and wafer bonding are particularly suitable for VLSI applications due to their compatibility with established CMOS processing technology.

Silicon substrate

Fig. 1.4 A schematic cross section of SOI CMOS, with shallow trench isolation (STI), dual polysilicon gates, and self-aligned silicide.

#### 1.2.2 Partially-depleted SOI MOSFETs

SOI MOSFETs are distinguished as partially-depleted (PD) when the silicon film is thicker than the maximum gate depletion width and the devices exhibit a floating-body effect [1.4], and fully-depleted (FD) when the silicon film is thin enough that the entire film is depleted before the threshold condition is reached. In PDSOI MOSFETs, there is a neutral body region below the gate depletion boundary. The body of PDSOI devices are not tied to the ground as in bulk devices and can float to different potentials depending on the drain and gate voltages. The floating-body effect occurs when carriers of the same type as the body, generated by impact ionization near the drain, are stored in the floating body, which alters the body potential and hence the threshold voltage [1.4]. This effect is especially strong in nMOSFETs, due to the higher impact ionization rate of electrons. Floating body effect is dynamic in nature since it takes some finite time, which is much longer than the device switching time, for the body to charge or discharge to a steady potential. Consequently, the body potential of PDSOI MOSFETs has significant history dependence. Depending on the history, the body potential of a PDSOI MOSFET may be at different levels in the beginning of a switching event and affects the threshold voltage and delay. History dependence of transient output characteristics of PDSOI MOSFETs has been reported in [1.5]. The body recovery time is strongly affected by the generation time (impact ionization during on-time or thermal generation during off-time). Because of the slow thermal generation process, it takes long off-time (~1ms [1.5]) to replenish holes in the body (for nMOSFET) at low-drain voltages (~<1.5 V [1.5]) which impact ionization does not take place. At high-drain voltages which impact ionization occurs, the body of a PDSOI device can be charged up within a few nanoseconds. This poses great difficulties in circuit design. The history effect can be minimized by optimizing the key PDSOI device parameters which are summarized in [1.6, 1.7]. The PDSOI CMOS technology is the most popular SOI technology at present due to its several advantages over bulk devices- reduced junction capacitances and better performance. Although it is still a technological challenge to fabricate an ultra-thin silicon film sub-20nm FDSOI device today, FDSOI technology is gaining more and more attentions and considered as a potential candidate for achieving 10-nm CMOS.

#### **1.2.3 Fully-depleted SOI vs. bulk MOSFETs**

According to the ITRS new roadmap in 2005, scaling of the conventional bulk MOSFET to the 32 nm technology generation (gate length=13 nm) will face several significant challenges due to the use of high channel doping-which leads to band-to-band tunneling across the junction, gate-induced drain leakage (GIDL), and stochastic doping variations [1.1]. Since planar bulk CMOS technology is approaching its scaling limit, ultra-thin body fully-depleted (FD) silicon-on-insulator (SOI) MOSFETs have been considered as the potential candidate for developing high performance consumer electronics. The unconventional FDSOI device structure has reduced source/drain junction capacitances, lower leakage current, and immunity to

Fig. 1.5 Formation contact or silicide on shallow junctions in the case of (a) bulk silicon and (b) thin-film SOI.

radiation-induced photocurrents and latch-up effect. It has the potential for

manufacturing a modern CMOS circuit with higher speed, and lower power dissipation.

Another advantage of using FDSOI CMOS technology is because it suppresses some yield hazard factors which have been observed in bulk CMOS [1.8]. To illustrate this, we consider fabricating shallow junctions and making electrical contact in a bulk device and a FDSOI device (Fig. 1.5). The junction depth of a FDSOI device is equal to its silicon film thickness. Electrical contact to a shallow junction can be made by metal (e.g., tungsten), an alloy (e.g., Al:Si) or metal silicide (e.g., TiSi<sub>2</sub>). In a bulk MOSFET, unwanted reactions can take place between the silicon and the metal or the silicide. The metal may punch through the junction (Fig. 1.5(a)), which can lead to uncontrolled leakage current. If the device is realized in an ultra-thin body FDSOI device structure, the source and drain active regions end at the thick buried-insulator layer. In that case, any uncontrolled metal-silicon reaction will not generate leakage current (Fig. 1.5(b)).

In addition, the short-channel effect in an ultra-thin body FDSOI MOSFET can be suppressed by thinning down the silicon body and BOX thickness. Furthermore, scaling down the BOX thickness of a FDSOI MOSFET below 5 nm can lead to a double-gate device structure on SOI substrate, although the process technology is still complex and immature. In contrast to BOX thickness scaling, the silicon film thickness scaling is more technically achievable [1.9], which generates a great deal of interest in ultra-thin body FDSOI MOSFETs. Previous published experimental studies [1.10] already showed the viability of nanoscale ultra-thin body, undoped FDSOI MOSFETs with a standard thick BOX. However, there lacks a clear guideline on the scaling of ultra-thin body FDSOI MOSFETs. To find out the scaling rules for FDSOI MOSFETs, an extensive 2-D numerical simulation-based design study is carried out and analyzed in this thesis.

#### 1.3 Outline

This thesis consists of seven chapters:

Chapter 1 introduces the scaling trend of CMOS technology, and the motivation of our design study.

Chapter 2 reviews the previous analytical models of bulk and fully-depleted SOI MOSFETs.

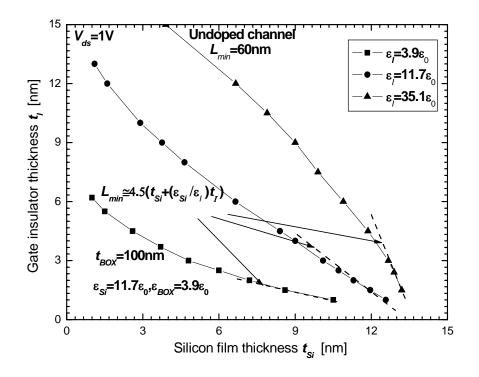

Chapter 3 discusses out the inapplicability of the general scale-length model in predicting the minimum scalable channel length of undoped FDSOI MOSFETs. Analysis of electric field distribution in the buried-oxide is carried out by 2-D numerical simulations. Constant  $L_{min}$  contours are plotted in a  $t_{si} - t_{ox}$  plane, showing the design space of undoped FDSOI MOSFETs. A simple scaling rule is obtained empirically from the constant  $L_{min}$  contours.

Chapter 4 investigates several factors affecting the short-channel behavior of FDSOI MOSFETs. They are: substrate biasing, body doping, and the dielectric

constant of the buried-insulator layer. An empirical equation for predicting the  $L_{min}$  of doped FDSOI MOSFETs is obtained from the constant  $L_{min}$  contours. Short-channel effect can also be mitigated by applying a high reverse voltage to the substrate of a FDSOI device. The drawback of such a scheme is also discussed in this chapter.

Chapter 5 explores the scaling limit of gate insulator and silicon film thickness of FDSOI MOSFETs. Quantum mechanical effect on the short-channel behavior of FDSOI MOSFETs is discussed. The design space of sub-20 nm FDSOI MOSFETs is shown subject to the gate tunneling limit and the scaling limit of silicon film thickness. Carrier mobility degradation due to surface roughness and buried-oxide interface roughness in ultra-thin body FDSOI MOSFETs is investigated based on published data. Performance degradation of an extremely-scaled FDSOI device is assessed qualitatively in the last section.

Chapter 6 summarizes the thesis with some final remarks and suggestions for future work.

#### References

- [1.1] International Technology Roadmap for Semiconductor 2005, Executive Summary.

- [1.2] B. Davari, R. H. Dennard, and G. G. Shahidi, "CMOS scaling for high performance and low power-the next ten years," *IEEE Proceedings*, vol. 83, no. 4, April 1995.

- [1.3] D. J. Frank, R. H. Dennard, E. Nowak, P. M. Solomon, Y. Taur, and H.-S. P. Wong, "Device scaling limits of Si MOSFETs and their application dependencies," *IEEE Proceeding.*, vol. 89, no. 3, March 2001.

- [1.4] M. Yoshimi *et.al.*, "Two-dimensional simulation and measurement of high-performance MOSFETs made on a very thin SOI film," *IEEE Trans. Electron Devices*, p. 493, 1989.

- [1.5] K. A. Jenkins, J. Y.-C. Sun, and J. Gautier, "History dependence of output characteristics of silicon-on-insulator (SOI) MOSFET's," *IEEE Electron Device Lett.*, vol. 17, no. 1, p7-9, 1996.

- [1.6] S. K. H. Fung, N. Zamdmer, P. J. Oldiges, J. Sleight, A. Mocuta, M. Sherony, S-H. Lo, R. Joshi, C. T. Chuang, I. Yang, S. Crower, T. C. Chen, F. Assaderaghl, and G. Shahidi, "Controlling floating-body effects for 0.13µm and 0.1µm SOI CMOS," *IEDM* Technical Digest, 2000.

- [1.7] S. Kawanaka *et.al.*, "Body voltage and history effect sensitivity to key device parameters in 90-nm PD-SOI," *IEEE International SOI conference*, 2004.

- [1.8] Jean-Pierre Colinge, "Silicon-on-insulator technology: materials to VLSI," 3<sup>rd</sup> edition, Kluwer Academic Publishers.

- [1.9] V. P. Trivedi and J. G. Fossum, "Nanoscale FD/SOI CMOS: thick or thin BOX?," *IEEE Electron Device Lett.*, vol. 26, no. 1, Jan. 2005.

- [1.10] B. Doris *et.al.*, "Device design considerations for ultra-thin SOI MOSFETs," *IEDM* Technical Digest, 2003.

## **CHAPTER 2**

# **Review of Previous Analytical Models on Scaling of Bulk and SOI MOSFETs**

#### 2.1 Scale-length model for bulk MOSFETs

Fig. 2.1 Simplified geometry for analytically solving Poisson's equation in a short-channel MOSFET. Adapted from [2.1].

The analytical model of the short-channel effect in bulk MOSFETs has been developed by Thao N. Nugyen [2.1] in 1984. With a number of approximations while retaining the basic aspects of the short-channel effect, the electrostatic potential in

bulk MOSFETs was obtained by solving Poisson's equation in the simplified MOSFET geometry shown in Fig. 2.1. The x-axis is along the vertical direction, the y-axis is along the horizontal direction, and the origin at point A. A rectangular box is used to define the simplified boundary conditions for solving Poisson's equation which substantially reduces the complexity of the problem. The analytical solution of electrostatic potential has been verified by 2-D numerical device simulation results.

The normal component of the electric field changes by a factor of  $\varepsilon_{Si}/\varepsilon_{OX} \approx 3$ across the silicon-oxide interface of a bulk MOSFET. In Nguyen's approach, the oxide is replaced by an equivalent region of the same dielectric constant as silicon, but with a thickness of  $3t_{OX}$  so that both the potential and its derivatives are continuous at the silicon-oxide interface. Therefore, the entire rectangular region of interest can be treated as a homogeneous material of silicon with length L and depth  $W_d + 3t_{OX}$ .

In the oxide region, Poisson's equation becomes Laplace equation,

$$\frac{\partial^2 \psi}{\partial x^2} + \frac{\partial^2 \psi}{\partial y^2} = 0 \tag{2.1}$$

In the depletion region in silicon, Poisson's equation is approximated by

$$\frac{\partial^2 \psi}{\partial x^2} + \frac{\partial^2 \psi}{\partial y^2} = \frac{q N_a}{\varepsilon_{si}}$$

(2.2)

Equation (2.2) is only applicable to a bulk device in the subthreshold region which mobile charges are negligible. If we assume that the source and drain junctions are abrupt and deeper than  $W_d$ , we can define the following set of simplified boundary

conditions:

$$\psi(-3t_{ox}, y) = V_g - V_{fb}$$

$0 < y < L$  (2.3)

$$\psi(x,0) = \psi_{bi}$$

$-3t_{OX} < x < W_d$  (2.4)

$$\psi(x,L) = \psi_{bi} + V_{ds} - 3t_{OX} < x < W_d$$

(2.5)

$$\psi(W_d, y) = 0$$

$0 < y < L$  (2.6)

By using the superposition principle and breaking the electrostatic potential  $\psi(x, y)$  into the following terms, one can write:

$$\psi(x, y) = \upsilon(x, y) + u_L(x, y) + u_R(x, y) + u_B(x, y)$$

(2.7)

Here v(x) is the 1-D solution to equation  $\partial^2 \psi / \partial x^2 = 0$ , and satisfies the top boundary conditions.  $u_L$ ,  $u_R$ , and  $u_B$  are solutions to the Laplace's equation and satisfy the boundary conditions at source side, drain side and bottom respectively. For example,  $u_L$  is zero on the top, bottom, and the right (drain side) boundaries, but  $v + u_L$ satisfies the left (source side) boundary condition. Similarly,  $u_R$  is zero on the top, bottom, and the left boundaries, but  $v + u_R$  satisfies the right (drain side) boundary condition.

$$\upsilon(x,y) = \begin{cases} \psi_{s}^{0} - \frac{V_{g} - V_{fb} - \psi_{s}^{0}}{3t_{OX}} x & -3t_{OX} \le x \le 0\\ \psi_{s}^{0} (1 - \sqrt{\frac{qN_{a}}{2\varepsilon_{Si}\psi_{s}^{0}}} x)^{2} & 0 \le x \le W_{d} \end{cases}$$

(2.8)

Here the long-channel surface potential  $\psi_s^0$  is related to V<sub>g</sub> by the requirement that

$\partial \upsilon / \partial x$  be continuous at x = 0.

$$\frac{V_g - V_{fb} - \psi_s^0}{3t_{OX}} = \sqrt{\frac{2qN_a\psi_s^0}{\varepsilon_{Si}}}$$

(2.9)

The rest of the solutions are in the form of a series product of hyperbolic and sinusoidal functions [1.6]:

$$u_{L}(x,y) = \sum_{n=1}^{\infty} b_{n}^{*} \frac{\sinh(\frac{n\pi(L-y)}{W_{d}+3t_{OX}})}{\sinh(\frac{n\pi L}{W_{d}+3t_{OX}})} \sin(\frac{n\pi(x+3t_{OX})}{W_{d}+3t_{OX}})$$

(2.10)

$$u_{R}(x,y) = \sum_{n=1}^{\infty} c_{n}^{*} \frac{\sinh(\frac{n\pi y}{W_{d} + 3t_{OX}})}{\sinh(\frac{n\pi L}{W_{d} + 3t_{OX}})} \sin(\frac{n\pi(x+3t_{OX})}{W_{d} + 3t_{OX}})$$

(2.11)

$$u_{B}(x,y) = \sum_{n=1}^{\infty} d_{n}^{*} \frac{\sinh(\frac{n\pi(x+3t_{OX})}{L})}{\sinh(\frac{n\pi(W_{d}+3t_{OX})}{L})} \sin(\frac{n\pi y}{L})$$

(2.12)

The high-order terms in  $u_R$  and  $u_L$  series can be neglected if the channel length is not too short. By making the thin-oxide assumption and dropping all the second-order terms in  $3t_{OX}/W_d$ , the simplified expressions for the coefficients can be obtained:

$$b_{1}^{*} = \frac{4}{\pi} \psi_{bi} - \frac{2}{\pi} (1 - \frac{4}{\pi^{2}}) (1 + \frac{6t_{OX}}{W_{d}}) \psi_{s}^{0}$$

(2.13)

$$c_1^* = \frac{4}{\pi} (\psi_{bi} + V_{ds}) - \frac{2}{\pi} (1 - \frac{4}{\pi^2}) (1 + \frac{6t_{OX}}{W_d}) \psi_s^0$$

(2.14)

The approximate analytical solution of potential in the silicon region under subthreshold conditions is

$$\psi(x,y) = \psi_s^0 (1 - \sqrt{\frac{qNa}{2\varepsilon_{s_i}\psi_s^0}})^2 + \frac{b_1^* \sinh(\frac{n\pi(L-y)}{W_d + 3t_{OX}}) + c_1^* \sinh(\frac{n\pi y}{W_d + 3t_{OX}})}{\sinh(\frac{n\pi L}{W_d + 3t_{OX}})} \sin(\frac{n\pi(x+3t_{OX})}{W_d + 3t_{OX}})$$

(2.15)

Under subthreshold condition, current conduction is dominated by diffusion, and is controlled by the highest potential barrier along the channel. The threshold voltage lowering in a short-channel device can then be expressed as

$$\Delta V_{t} = \frac{24t_{OX}}{W_{dm}} \sqrt{\psi_{bi}(\psi_{bi} + V_{ds})} e^{-\pi L/2(W_{dm} + 3t_{OX})}$$

(2.16)

The subthreshold slope of a short-channel device is approximated as

$$S \approx 2.3 \frac{W_{dm} + 3t_{OX}}{W_{dm}} \frac{kT}{q} \left(1 + \frac{11t_{OX}}{W_{dm}} e^{-\pi L/2(W_{dm} + 3t_{OX}})\right)$$

(2.17)

The simplification of boundary condition in silicon/oxide interface in Nguyen's approach is valid only when the oxide field is dominated by its normal component.

# 2.2 General scale-length model for 2- and 3-layer MOSFETs

Recently, Nguyen's model has been extended to the general scale-length model by D. J. Frank [2.2], based on a two-region (or three-region) model by matching the 2-D boundary conditions at the silicon/insulator interfaces. By using superposition, the potentials in the center of a bulk MOSFET  $\psi_1$  and  $\psi_2$  can be written as,

$$\psi_1(x, y) = \upsilon_1(x) + u_{L_1}(x, y) + u_{R_1}(x, y)$$

$$\psi_2(x, y) = \upsilon_2(x) + u_{L_2}(x, y) + u_{R_2}(x, y)$$

(2.18)

, here  $v_i(x)$  are the 1-D solutions to Poisson's equation satisfying the top, bottom and dielectric boundary conditions.  $u_{Li}$  and  $u_{Ri}$  are left and right solutions to Laplace's

Fig. 2.2 Idealized schematic cross section diagram of (a) a bulk MOSFET (b) a double-gate MOSFET, defining the insulatorthickness  $t_I$  and the depleted Si thickness  $t_{Si}$ .  $\varepsilon_{Si}$  is the permittivity of Si and  $\varepsilon_I$  is the permittivity of gate insulator(s). Adapted from [2.2].

equation and satisfy the boundary conditions at the source and drain, respectively. The u's can be written as infinite series in the form of  $\sinh(ay)\sin(bx)$ . If the channel length is not too short, the lowest order term dominates the solution. Therefore,  $u_{Li}$  and  $u_{Ri}$  can be simplified to the following expressions:

$$u_{L1} \cong b_{11} \frac{\sinh(\pi(L-y)/\lambda_1)}{\sinh(\pi L/\lambda_1)} \sin(\pi(x+t_1)/\lambda_1)$$

(2.19)

$$u_{R1} \cong c_{11} \frac{\sinh(\pi y/\lambda_1)}{\sinh(\pi L/\lambda_1)} \sin(\pi (x+t_1)/\lambda_1)$$

(2.20)

$$u_{L2} \cong b_{21} \frac{\sinh(\pi (L-y)/\lambda_1)}{\sinh(\pi L/\lambda_1)} \sin(\pi (x-t_{Si})/\lambda_1+\pi)$$

(2.21)

$$u_{R2} \cong c_{21} \frac{\sinh(\pi y/\lambda_1)}{\sinh(\pi L/\lambda_1)} \sin(\pi (x - t_{S_i})/\lambda_1) \quad .$$

(2.22)

The *b*'s, *c*'s, and  $\lambda_1$  are coefficients and can be determined by satisfying the boundary conditions. By matching the potential and field boundary conditions at the silicon-insulator interfaces, an eigenvalue equation for scale length  $\lambda_1$  can be

Fig. 2.3 The scale length  $\lambda_1$  depends on gate dielectric, silicon film and buried oxide thicknesses.

obtained:

$$\varepsilon_{Si} \tan(\pi t_I / \lambda_1) + \varepsilon_I \tan(\pi t_{Si} / \lambda_1) = 0.$$

(2.23)

The result is also generalized to any three-layer-dielectrics device with dielectric thickness  $t_1$ ,  $t_2$ , and  $t_3$  and permittivities  $\varepsilon_1$ ,  $\varepsilon_2$ , and  $\varepsilon_3$ . The corresponding eigenvalue equation is,

$$\frac{\varepsilon_2}{\varepsilon_1\varepsilon_3}\tan(\frac{\pi_1}{\lambda_1})\tan(\frac{\pi_2}{\lambda_2})\tan(\frac{\pi_3}{\lambda_3}) = \frac{1}{\varepsilon_1}\tan(\frac{\pi_1}{\lambda_1}) + \frac{1}{\varepsilon_2}\tan(\frac{\pi_2}{\lambda_1}) + \frac{1}{\varepsilon_3}\tan(\frac{\pi_3}{\lambda_1}).$$

(2.24)

For the first-order solution, the potential in the center of the channel varies as  $(b_{21} + c_{21})\sinh(\pi L/2\lambda_1)/\sinh(\pi L/\lambda_1)$ , where  $b_{21}$  and  $c_{21}$  are bias dependent. Since this gives a length dependence  $\sim \exp(-\pi L/2\lambda_1)$ , the  $L/\lambda_1$  ratio is a key measure of the short-channel effect of a scaled MOSFET. The minimum scalable channel length  $L_{\min}$  of a MOSFET is projected to be  $\sim 1.5 - 2\lambda_1$ . The general scale-length model is applicable to bulk MOSFETs, double-gate MOSFETs and long-channel SOI MOSFETs with any gate dielectrics. The scale length  $\lambda_1$  of a FDSOI MOSFET can be solved numerically from the eigenvalue equation (2.24). Fig. 2.3 shows that the scale length  $\lambda_1$  increases with increasing  $t_{BOX}$ .

#### 2.3 Review of other literature

In the 1980's, SOI technology was pioneered and advocated by J. P. Colinge [2.3]. 1-D Poisson's equation was solved to model the electrostatic behavior of SOI

MOSFETs. An ideal inverse subthreshold slope of 60mV/decade can be observed in a long-channel undoped FDSOI device. However, the ideal subthreshold slope cannot be obtained in short-channel, thick BOX FDSOI devices due to the lateral field coupling into the channel through the buried-oxide. The subthreshold slope advantages of SOI technology over bulk CMOS exist only in long-channel SOI MOSFETs. In the early 90's, R. H. Yan [2.4] followed K.K. Young's approach [2.5] and assumed a second-order polynomial function for the potential perpendicular to the channel surface. He derived a 2-D analytical potential distribution in the silicon body. The electric field inside a thick buried-oxide of a FDSOI device. The scale length associated with

Fig. 2.4 The (a) conventional, (b) gate-all-around, and (c) ground plane SOI structures and the corresponding device scale length  $\delta$ . Adapted from [2.6].

the short-channel effect for several advanced devices were developed by R. H. Yan (Fig. 2.4) [2.6]. They are proportional to the geometric mean of the oxide and silicon

film thickness. The minimum scalable channel length of a FDSOI device can be simply projected by its scale length. It was also pointed out for the first time that SOI CMOS cannot be scaled to as short a channel length as double-gate CMOS. Yan's model has large errors in minimum scalable channel length when one dielectric is much thicker than the other. Woo *et al.* [2.7] scaled up the gate oxide thickness of a FDSOI device by a factor of 3 and eliminated the boundary condition at the silicon/oxide interface by making the dielectric constant in the scaled oxide region the

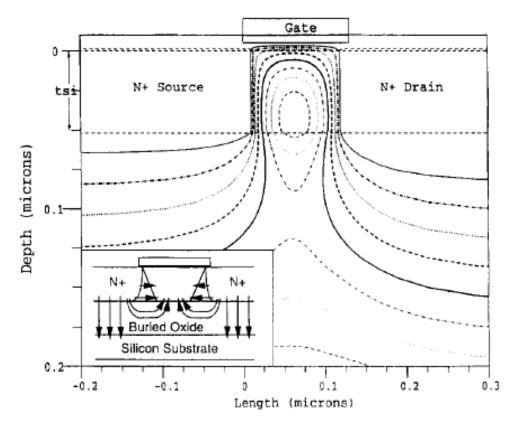

Fig. 2.5 Electric potential contours in a SOI device indicating 2-D field coupling through the buried oxide. Electric field lines (shown schematically in the inset) can be drawn perpendicular to the potential contours. Adapted from [2.8].

same as silicon. This assumes that normal electric field inside the BOX dominates. Those approximations are valid only when the gate insulator and the BOX are much thinner than the silicon region. Lisa T. Su [2.8] explored the deep-submicron SOI MOSFETs design space by 2-D numerical simulations. She showed that the additional field coupling through the SOI buried-oxide (Fig. 2.5) further aggravates the short-channel effect. H.-S. Philips Wong *et al.* [2.9] investigated the severity of short-channel effect of 25-nm SOI and double-gate MOSFETs based on 2-D simulations. Even though [2.8] and [2.9] showed poor short-channel effects in FDSOI devices, the results were not generalized and a clear guideline on the scaling of FDSOI MOSFETs is still lacking. In the next chapter, we start with a discussion on the failure of general scale-length model in SOI MOSFETs. An empirical scaling rule for undoped fully-depleted SOI MOSFETs is presented based on simulation analysis.

### References

- [2.1] T. N. Nguyen, "Small-geometry MOS transistors: Physics and modeling of surface- and buried-channel MOSFET's," Ph.D. dissertation, Stanford Univ., Stanford, CA, Tech. Rep. G545-2, 1984.

- [2.2] D. J. Frank, Y. Taur, and H.-S. P. Wong, "Generalized scale length for two-dimensional effects in MOSFETs," *IEEE Electron Device Lett.*, vol. 19, pp. 385-387, Oct. 1998.

- [2.3] Jean-Pierre Colinge, "Silicon-on-insulator technology: materials to VLSI," 3<sup>rd</sup> edition, Kluwer Academic Publishers.

- [2.4] R.-H. Yan, A. Ourmazd, and D. Y. Jeon, "Scaling the Si metal-oxide-semiconductor field-effect transistor into the 0.1-um regime using vertical doping engineering," *Appl. Phys. Lett.*, vol. 59, December 1991.

- [2.5] K. K. Young, "Short-channel effect in fully depleted SOI MOSFET's," *IEEE Trans. Electron Devices*, vol. 36, no. 3, March 1989.

- [2.6] R.-H. Yan, A. Ourmazd, and K. F. Lee, "Scaling the Si MOSFET: from bulk to SOI," *IEEE Trans. Electron Devices*, vol. 39, no. 7, July 1992.

- [2.7] Jason C. S. Woo, K. Y. Terrill, and P. K. Vasudev, "Two-dimensional modeling of very thin SOI MOSFET's," *IEEE Trans. Electron Devices*, vol. 37, no. 9, Sept. 1990.

- [2.8] Lisa T. Su, J. B. Jacobs, J. E. Chung, and D. A. Antoniadis, "Deep-submicrometer channel design in silicon-on-insulator (SOI) MOSFETs," *IEEE Electron Device Lett.*, vol. 15, September 1994.

- [2.9] H.-S. Philips Wong, D. J. Frank, and P. M. Solomon, "Device design considerations for double-gate, ground-plane, and single-gated ultra-thin SOI MOSFETs at the 25nm channel length generation," *IEDM* 1998.

# **CHAPTER 3**

# Analysis of Short-Channel Effects in Undoped SOI MOSFETs

# 3.1 Device structures for 2-D numerical simulation

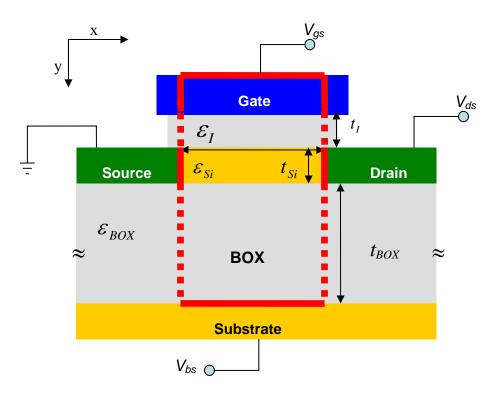

The design study of the scaling limit of SOI MOSFETs is carried out by TCAD simulation tools. TCAD is a synergistic combination of process, device and circuit simulation, and modeling tools. Instead of costly, time-consuming test wafer runs when characterizing or developing a new semiconductor device and technology, TCAD simulation tools are widely used by device engineers nowadays to efficiently support and optimize semiconductor technology and devices. The TCAD tool DESSIS used in our work is provided by SYNOPSYS. DESSIS is a device simulation tool which numerically simulates the electrical behavior of a single semiconductor device or several physical devices combined in a circuit. It solves fundamental and physical partial differential equations that describe the carrier distribution and conduction mechanism in discretized geometries, representing layer systems in a semiconductor device or small scale circuits with a few devices. This deep physical approach gives DESSIS simulation predictive accuracy.

DESSIS is used to calculate the low-drain threshold voltage shift,  $\Delta V_T$ , and

Fig. 3.1 Device structures of (a) bulk, (b) SOI, and (c) double-gate MOSFETs used in 2-D numerical simulations. Box-like doping profile is assumed in our design study.

drain-induced barrier lowering (DIBL) in the following discussions of the short-channel effect in bulk, double-gate, fully-depleted(FD) SOI MOSFETs as a function of device parameters. The simulated device structures are shown in Fig. 3.1. In our design study, we focus on FDSOI devices with a thick buried-oxide (thickness  $\sim$ 100 nm) since FDSOI devices with a thin buried-oxide (thickness <50 nm) are double-gate-like devices and the scaling limit of double-gate MOSFETs is already known. For future reference, all FDSOI devices in the rest of the thesis mean FDSOI devices with a thick buried-oxide. Box-like uniform doping profile is used in source and drain to keep the effective channel length *L* of the device at a constant value over a large range of channel doping. Since we only consider the electrostatic integrity of

bulk, double-gate, and SOI MOSFETs, constant mobility is assumed for carriers.

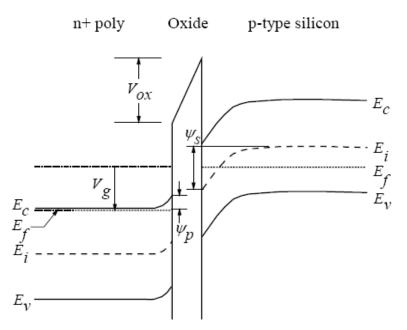

The use of polysilicon gates is a key advance in modern CMOS technology, since it allows the source and drain region to be self-aligned to the gate, thus eliminating parasitics from overlay errors [3.1]. However, the polysilicon-gate depletion effect occurs when it is not doped heavily enough in a MOSFET. The band diagram in Fig. 3.2 illustrates the polysilicon-gate depletion effect in a p-type MOS

Fig. 3.2 Band diagram showing polysilicon-gate depletion effects when a positive voltage is applied to the N+ polysilicon gate of a p-type MOS capacitor.  $\psi_s$  is the amount of band bending in the bulk silicon.  $\psi_p$  is the amount of band bending in the N+ polysilicon gate.

capacitor biased into inversion. Since the oxide field points in the direction of accelerating a negative charge toward the gate, the bands in the N+ polysilicon bend slightly upward toward the oxide interface. This depletes the surface of electrons and

forms a thin space-charge region in the polysilicon layer. The depletion charges on both sides of the gate dielectric are equal and, therefore, one can obtain the depletion width  $t_p$  in the N+ polysilicon by  $t_p = \frac{\varepsilon_{si} E_s}{qN_p}$ , where  $E_s$  is the surface field normal

to the gate dielectric, and  $N_p$  is the doping concentration of the N+ polysilicon. For example,  $t_p$  is about ~1 nm with  $E_s$  equal to ~ 1.6MV/cm and  $N_p$  equal to ~10<sup>20</sup> 1/cm<sup>3</sup>. Since one can not dope the polysilicon gate to have a gate work function which locates outside silicon bandgap,  $t_p$  can be comparable to the gate dielectric thickness in a sub-20nm MOSFET design. The polysilicon-gate depletion results in an additional capacitance in series with the gate capacitance, which in turn leads to a reduced inversion-charge density and degradation of the MOSFET intrinsic capacitance and transconductance. Therefore, to obtain low-threshold MOSFETs, a metal gate with work function between mid-gap and N+ polysilicon (for nMOSFET) gate work function is assumed to be technically available so that the threshold voltage of long-channel MOSFETs is ~0.4 V and ~0.3 V for short-channel MOSFETs in our design study.

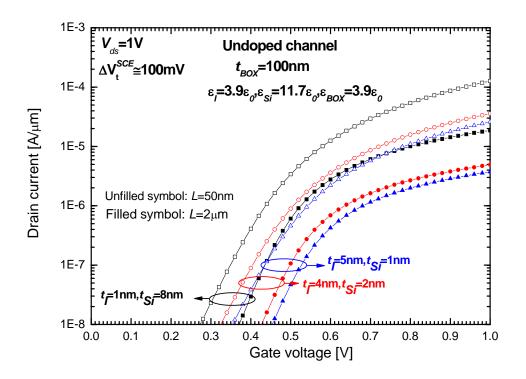

The low-drain threshold voltage shift of any short-channel device,  $\Delta V_T$ , is calculated by  $\Delta V_T = V_T$  (L=1µm)-  $V_T$  (short-channel device) and the DIBL= $V_T$  ( $V_{ds}$ =50 mV)-  $V_T$  ( $V_{ds}$ =1 V). Both  $\Delta V_T$  and DIBL are measured at  $I_{ds}$ =10<sup>-8</sup>(W/L).

#### **3.2 Short-channel effect**

Short-channel effect emerging as the channel length of a MOSFET is aggressively scaled. When CMOS VLSI systems are fabricated on a wafer, channel length of any device on the wafer varies from chip to chip statistically. Therefore, one must ensure that the threshold voltage of the minimum-channel-length device on the chip does not become too low. The physics of short-channel effect can be understood by considering the surface potential barrier (to electrons for an n-channel MOSFET) in the channel region shown in Fig. 3.3. Under off condition, the potential barrier (p-type region) prevents electron current from flowing to the drain. For a long-channel

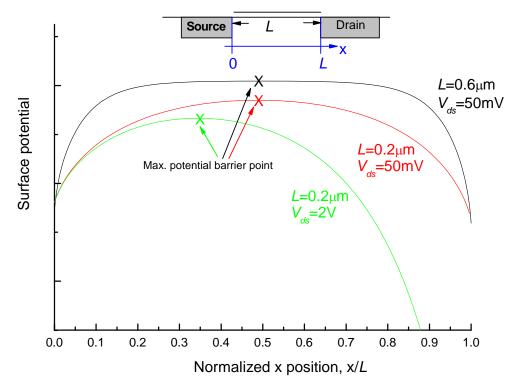

Fig. 3.3 Surface potential versus lateral distance (normalized to the channel length L) from the source to the drain for (a) a long-channel (L=0.6 µm) MOSFET biased at a low drain voltage, (b) a short-channel (L=0.2 µm) MOSFET biased at a low drain voltage, (c) a short-channel (L=0.2 µm) MOSFET biased at a high drain voltage. The gate voltage is the same for all three cases.

MOSFET, the potential barrier is flat in the most part of the channel region. Source/drain lateral-field coupling into channel only takes place in the very ends of the channel. However, for a short-channel MOSFET, the source/drain lateral fields penetrate deeply into the center of the channel and lower the potential barrier between the source and drain. The barrier-lowering in a short-channel MOSFET leads to threshold voltage roll-off and a substantial increase of the subthreshold current (Fig. 3.3). When a high drain voltage is applied to a short-channel MOSFET, the potential barrier is lowered even more, resulting in further decrease of the threshold voltage. The point of maximum barrier also shifts toward the source end as shown in Fig. 3.3.

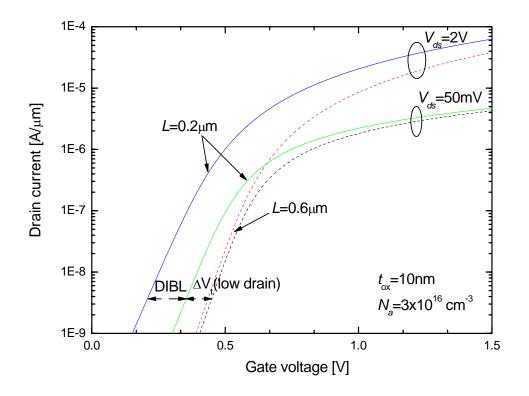

Fig. 3.4 Subthreshold characteristics of long- and short-channel MOSFETs biased at low and high drain voltages.

This effect is referred to as *drain-induced-barrier-lowering* (*DIBL*). Fig. 3.4 shows the subthreshold characteristics of long-channel (L=0.6 µm) and short-channel (L=0.2 µm) MOSFETs biased at different drain voltages. For the long-channel device, the subthreshold current is independent of drain voltage ( $\geq 2kT/q$ ). However, for the short-channel device, a parallel shift of the curve to a lower threshold voltage at a high drain voltage can be observed. The subthreshold slope starts to degrade as the surface potential is more controlled by the drain than by the gate. Eventually, a short-channel MOSFET reaches the punch-through condition when the gate totally loses control of the channel and high drain current persists independent of gate voltage.

## **3.3 Inapplicability of the general scale-length model**

#### **3.3.1** Correlations between scale length and lateral field penetration

To understand the role of the lateral field in a short-channel MOSFET, the 2-D Poisson's equation is written in terms of electric field as:

$$\frac{\partial E_x}{\partial x} + \frac{\partial E_y}{\partial y} = \frac{\rho}{\varepsilon_{s_i}}$$

(3.1)

Here  $E_x$  is the electric field in the horizontal direction and  $E_y$  is the electric field in the vertical direction. The depletion charge density  $\rho$  can be considered as being split

into two parts:  $\varepsilon_{Si} \frac{\partial E_y}{\partial y}$  is controlled by the gate field in the vertical direction, and

$\varepsilon_{si} \frac{\partial E_x}{\partial x}$  is controlled by the source-drain lateral field. The lateral field is negligible in a

long-channel device and the gate vertical field controls almost all of the depletion charge. In contrast to a long-channel device, the lateral field becomes appreciable in a short-channel device. Fig. 3.5 illustrates the magnitude of the lateral field along the channel length direction of double-gate MOSFETs obtained from 2-D numerical simulations. Examples for bulk MOSFETs can be found in [3.2]. The lateral field is highest at the source and drain junctions and decreases exponentially toward the middle of the channel. At low drain voltages, the source and drain lateral fields cancel each other right at the center of the channel. The zero-field point is shifted toward the

Fig. 3.5 Simulated lateral field as a function of lateral distance along a horizontal cut at the gate oxide/silicon body interface for two different devices biased at different drain voltages.

source side due to higher drain field as the device is biased at a high drain voltage. The curve becomes asymmetric and the lateral field intensity is increased even further by the application of a high drain voltage. The zero-field point corresponds to the point of maximum potential barrier in Fig. 3.3. The characteristic length of the exponential decay remains unchanged when the channel length becomes shorter. The magnitude of the lateral field near the middle of the device increases significantly. This depicts the penetration of source and drain fields into the channel region of a short-channel MOSFET. This magnitude of the lateral field along the channel direction is well

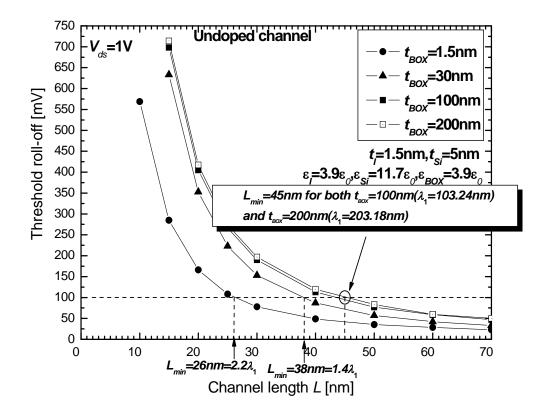

Fig. 3.6 High-drain threshold roll-offs for FDSOI MOSFETs with different BOX thickness.  $L_{min}$  is defined by setting a maximum tolerable high-drain threshold roll-off to be 100 mV. [3.4]

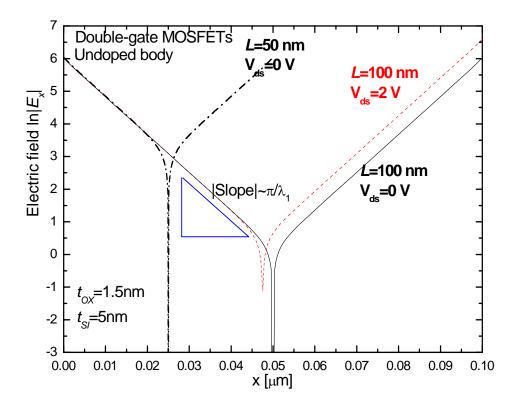

modeled by Nguyen and D. Frank in [3.2, 3.3]. By taking the first-order derivative of  $u_{L2}$  and  $u_{R2}$  in (2.21) and (2.22), one can find out that the magnitude of the lateral field is governed by the factor  $exp(-\pi x/\lambda_1)$ . The slope of the curve in Fig. 3.5 of 3-layer dielectric MOSFETs is related to the scale length by

$$|\text{Slope}| \sim \frac{\pi}{\lambda_1} \tag{3.2}$$

Presumably, one can predict the minimum scalable channel length ( $L_{\min} \cong 2\lambda_1$ ) of 2-layer or 3-layer dielectric MOSFETs by extracting the scale length  $\lambda_1$  from lateral-field analysis in a MOSFET, or by numerically solving  $\lambda_1$  from the three-tangent equation (2.24). To test the  $L_{min}$  prediction of fully-depleted SOI MOSFETs with standard thick buried-oxide in general scale-length model, an extensive two-dimensional device simulation is carried out with the results shown in Fig. 3.6. A maximum allowable high-drain threshold roll-off is set to be 100 mV to define the  $L_{\min}$  of a fully-depleted SOI device. All  $L_{\min}$ 's in the rest of the thesis are obtained by this criterion. It is indicated in Fig. 3.6 that, for  $t_{BOX}=1.5$  nm (DG-like),  $L_{\min}=26 \text{ nm} (\approx 2.2\lambda_1)$  is consistent with the  $L_{\min}\approx 1.5\lambda_1 \sim 2\lambda_1$  criterion in the general scale-length model. However, for  $t_{BOX}=30$  nm,  $L_{min}=38$  nm ( $\approx 1.4\lambda_1$ ) starts to deviate from the scale-length model. In addition, for both  $t_{BOX}=100$  nm ( $\lambda_1=103.24$  nm) and  $t_{\text{BOX}}$ =200 nm ( $\lambda_1$ =203.18 nm),  $L_{\text{min}}$  remains at 45 nm, much shorter than  $1.5\lambda_1$ . These results show that the short-channel effect in a thick-BOX fully-depleted SOI MOSFET is not as poor as predicted by the general scale-length model. The general scale-length model works well only when the buried-oxide thickness is much smaller than the

Fig. 3.7 Simplified geometry for analytically solving Poisson's equation in a short-channel FDSOI MOSFET. Dashed lines mean unspecified potential on the boundaries.

channel length. An enclosed BOX (see Fig. 3.7) with specified electrostatic potential on the boundaries can be defined for solving Poisson's equation as a 2-D boundary value problem. The potential in the insulator gap region between the source/drain and gates can be well-approximated by linear interpolation [3.4]. When the channel length of a FDSOI device is much smaller than the BOX thickness, the linear approximation fails and the potential on the boundaries of the enclosed box in the thick gap BOX region cannot be specified. To provide a further understanding of this observation, we need to do the lateral-field analysis and look into the field pattern in the buried-oxide region of long- and short-channel FDSOI devices.

#### **3.3.2** Electric field distribution in thick buried-oxide

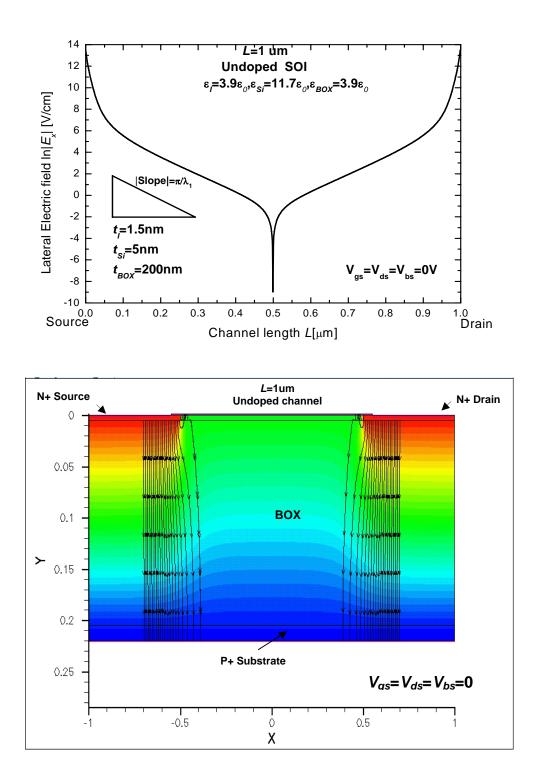

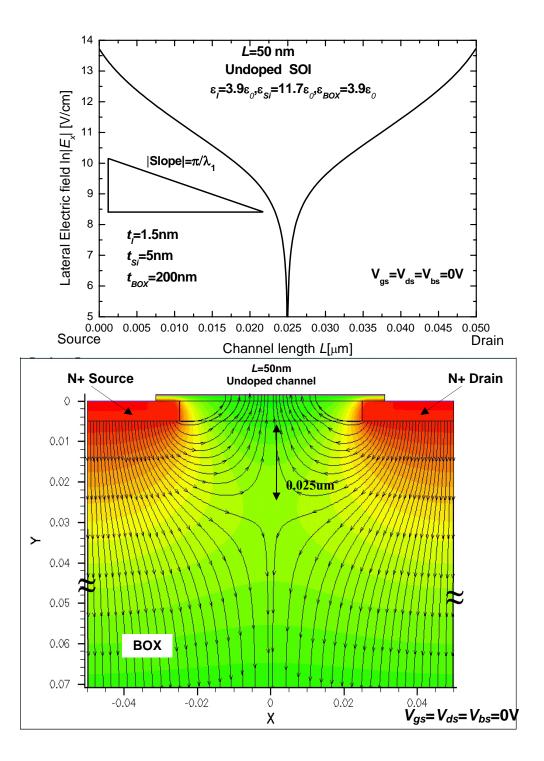

The lateral-field variation along the channel direction and the electric field pattern for long- and short-channel ultra-thin body FDSOI devices (n-channel MOSFETs) with standard thick BOX obtained from 2-D numerical simulations are shown in Fig. 3.8 and 3.9. Both cases are examined under subthreshold conditions. According to the discussion in section 3.3.1, the lateral field at the channel surface  $E_x$ is governed by the factor  $\exp(-\pi x/\lambda_1)$ . The characteristic length of the exponential decay is well-depicted by  $\lambda_1/\pi$  in long-channel FDSOI devices (Fig. 3.8(a)) because the field pattern in the BOX region is roughly one-dimensional (Fig. 3.8(b)). Source/drain-to-channel lateral-field coupling happens only near the very ends of the channel. However, the characteristic length of exponential decay for short-channel FDSOI devices (Fig. 3.9(a)) is shorter than expected from the general scale-length model. The 2-D field pattern (Fig. 3.9(b)) in the BOX suggests that the lateral-field penetration into the BOX depends on the channel length, i.e., the source-to-drain distance. This also implies that the "effective" BOX thickness (hence, the "effective" scale length) for short-channel SOI MOSFETs is much thinner than the physical thickness. To learn how the scale length varies with the channel length in FDSOI devices, the scale length  $\lambda_1^*$  of FDSOI devices with different channel lengths is calculated by  $\frac{\pi}{|slope|}$ , where the slope is measured from doing lateral-field analysis

in each device. Fig. 3.10 shows that the scale length  $\lambda_1^*$  extracted from lateral-field analysis varies with channel length. When the channel length is long (*L*~1 µm), the

Fig. 3.8 Simulated (a) lateral-field variation along the channel surface and (b) field pattern for a long-channel thick-BOX FDSOI device [3.5].

Fig. 3.9 Simulated (a) lateral-field variation along the channel surface and (b) field pattern for a short-channel thick-BOX FDSOI device [3.5].

Fig. 3.10 The extracted scale length  $\lambda_1^*$  versus channel length  $\lambda_1^*$  is calculated by  $\frac{\pi}{|slope|}$ , where the |slope| is obtained by lateral-field analysis.

curve saturates at the analytical solution of  $\lambda_1$  obtained from the general scale-length model. For short-channel FDSOI devices, the extracted scale length  $\lambda_1^*$  is independent of the standard thick BOX thickness and decreases with channel length *L*. According to the results shown in Fig. 3.10, the scale length is no longer a good indicator to know the severity of short-channel effect and the scaling limit of a FDSOI device. Therefore, extensive device simulations are needed to investigate the scaling rule and limit of ultra-thin body FDSOI MOSFETs.

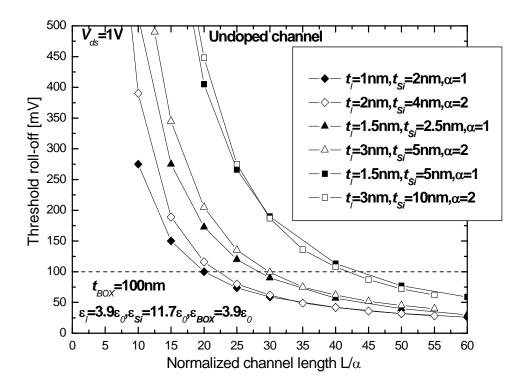

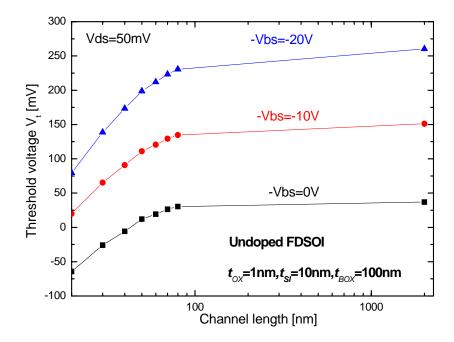

### 3.4 Short-channel scaling of undoped FDSOI MOSFETs

In the rule of generalized scaling for bulk MOSFETs, both the gate oxide thickness and the gate-controlled depletion width in silicon must be reduced in proportional to the channel length. The scaling rules of undoped FDSOI MOSFETs are governed by Poisson's equation and determined extensively by 2-D numerical simulations. According the results shown in Fig. 3.6, the high-drain threshold roll-off is independent of the buried-oxide thickness when the  $t_{BOX}$  is larger than 100 nm. From logic intuition, the short-channel scaling of FDSOI devices may depend on the

Fig. 3.11 General scaling rules of ultra-thin body FDSOI MOSFETs. For given permittivities  $\varepsilon_I$  and  $\varepsilon_{s_i}$ , if  $(t_I, t_{s_i})$  are both scaled by a factor of  $\alpha$ ,  $L_{\min}$  is scaled by the same factor  $\alpha$  [3.5], regardless of the BOX thickness.