## UC San Diego UC San Diego Electronic Theses and Dissertations

### Title

MATE, a Unified Model for Communication-Tolerant Scientific Applications

### Permalink

https://escholarship.org/uc/item/4tz5v6r6

#### Author Martin, Sergio Miguel

# Publication Date 2018

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

#### MATE, a Unified Model for Communication-Tolerant Scientific Applications

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

**Computer Science**

by

Sergio Miguel Martin

Committee in charge:

Professor Scott Baden, Chair Professor George Porter, Co-Chair Professor Tajana Rosing Professor Sutanu Sarkar Professor John Weare

2018

Copyright Sergio Miguel Martin, 2018 All rights reserved. The dissertation of Sergio Miguel Martin is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Co-Chair

Chair

University of California San Diego

2018

#### EPIGRAPH

Science! true daughter of Old Time thou art! Who alterest all things with thy peering eyes. —Edgar Allan Poe

#### TABLE OF CONTENTS

| Signature Page                                                                                        | iii                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Epigraph                                                                                              | iv                                                                                                                                                                                                                                                                                                                                                                   |

| Table of Content                                                                                      |                                                                                                                                                                                                                                                                                                                                                                      |

| List of Figures .                                                                                     | ix                                                                                                                                                                                                                                                                                                                                                                   |

| List of Tables .                                                                                      | xiii                                                                                                                                                                                                                                                                                                                                                                 |

| Acknowledgeme                                                                                         | ts                                                                                                                                                                                                                                                                                                                                                                   |

| Vita                                                                                                  | xvii                                                                                                                                                                                                                                                                                                                                                                 |

| Abstract of the I                                                                                     | ssertation                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 1 In                                                                                          | roduction                                                                                                                                                                                                                                                                                                                                                            |

| Chapter 2 B<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | Anatomy of a Supercomputer52.2.1Node Architecture62.2.2Interconnect Design7Costs of Communication82.3.1Intra-Node Communication82.3.2Network Communication10Distributed Programming Paradigms122.4.1SPMD122.4.2PGAS152.4.3Asynchronous PGAS162.4.4Dataflow18Communication Tolerant-Programming202.5.1Communication/Computation Overlap212.5.2Data Motion Reduction23 |

|                                                                                                       | e MATE Model       29         Overview       29         3.1.1       Motivating Example       30                                                                                                                                                                                                                                                                      |

| 3.3       Communication Reducing Effects         3.4       Related Work         3.4.1       MPI+KLT Model         3.4.2       MPI+MPI Model         3.4.3       MPI+ULT Model         3.4.4       Latency-Hiding Models | · · · · | • •<br>• • | 51<br>51<br>51<br>52 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|----------------------|

| 3.4.1       MPI+KLT Model                                                                                                                                                                                               | · · ·   | •          | 51<br>51<br>52       |

| 3.4.2       MPI+MPI Model                                                                                                                                                                                               | • • •   | •••        | 51<br>. 52           |

| 3.4.3MPI+ULT Model                                                                                                                                                                                                      | · · ·   | •          | . 52                 |

| 3.4.4 Latency-Hiding Models                                                                                                                                                                                             |         | •          |                      |

| , e                                                                                                                                                                                                                     |         |            | 54                   |

|                                                                                                                                                                                                                         | •••     |            | . 54                 |

| 3.5 Summary                                                                                                                                                                                                             |         | •          | . 57                 |

| Chapter 4 Design and Implementation                                                                                                                                                                                     |         | •          | . 58                 |

| 4.1 Overview                                                                                                                                                                                                            | •••     | •          | . 58                 |

| 4.2 Translation Process                                                                                                                                                                                                 | •••     | •          | . 59                 |

| 4.2.1 Step I: MPI to MATE Call Replacement                                                                                                                                                                              | •••     | •          | . 60                 |

| 4.2.2 Step II: Parsing Graph Directives                                                                                                                                                                                 | •••     | •          | 61                   |

| 4.2.3 Step III: Parsing For Loop Graphs                                                                                                                                                                                 | •••     | •          | . 63                 |

| 4.2.4 Step IV: Replacing The Main Function                                                                                                                                                                              | •••     | •          | . 64                 |

| 4.3 Runtime Support                                                                                                                                                                                                     | •••     | •          | . 66                 |

| 4.3.1 Runtime System Design                                                                                                                                                                                             | •••     | •          | . 66                 |

| 4.3.2 Execution Model                                                                                                                                                                                                   | • • •   | •          | . 68                 |

| 4.4 Communication Backend                                                                                                                                                                                               | •••     | •          | . 75                 |

| 4.4.1 Point-To-Point Communication                                                                                                                                                                                      | •••     | •          | . 76                 |

| 4.4.2 Barriers                                                                                                                                                                                                          |         |            |                      |

| 4.4.3 Collective Communication                                                                                                                                                                                          | •••     | •          | 81                   |

| Chapter 5 Test Case I: Jacobi3D                                                                                                                                                                                         |         | •          | . 83                 |

| 5.1 Overview                                                                                                                                                                                                            |         |            |                      |

| 5.1.1 Computation                                                                                                                                                                                                       |         |            |                      |

| 5.1.2 Verification                                                                                                                                                                                                      |         |            |                      |

| 5.2 Strong Scaling Studies                                                                                                                                                                                              |         | •          | . 86                 |

| 5.2.1 Cori Phase I (Haswell)                                                                                                                                                                                            |         |            |                      |

| 5.2.2 Cori Phase II (KNL)                                                                                                                                                                                               |         | •          | . 94                 |

| 5.3 Summary                                                                                                                                                                                                             |         |            |                      |

| Chapter 6 Test Case II: Cannon's Algorithm                                                                                                                                                                              |         |            | . 98                 |

| 6.1 Overview                                                                                                                                                                                                            |         |            |                      |

| 6.2 Code Variants                                                                                                                                                                                                       |         |            |                      |

| 6.2.1 Base MPI Algorithm                                                                                                                                                                                                |         | •          | . 99                 |

| 6.2.2 Overlapping MPI Algorithm                                                                                                                                                                                         |         | •          | . 102                |

| 6.2.3 MATE Variant                                                                                                                                                                                                      |         |            |                      |

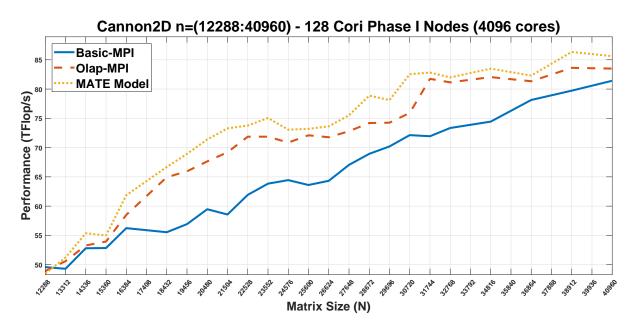

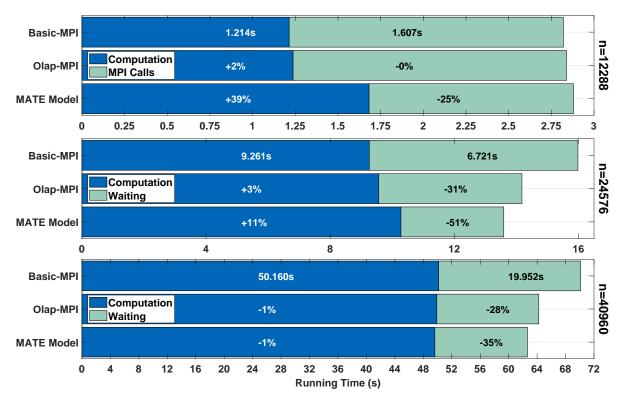

| 6.3 Size Scaling Study                                                                                                                                                                                                  |         |            |                      |

| 6.4 Weak Scaling Studies                                                                                                                                                                                                |         |            |                      |

| 6.4.1 Cori Phase I (Haswell)                                                                                                                                                                                            |         |            |                      |

| 6.4.2 Cori Phase II (KNL)                                                                                                                                                                                               |         |            |                      |

|            | 6.5 Summary                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

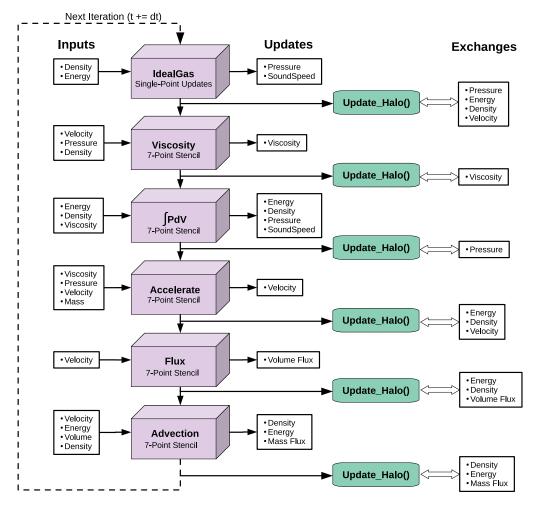

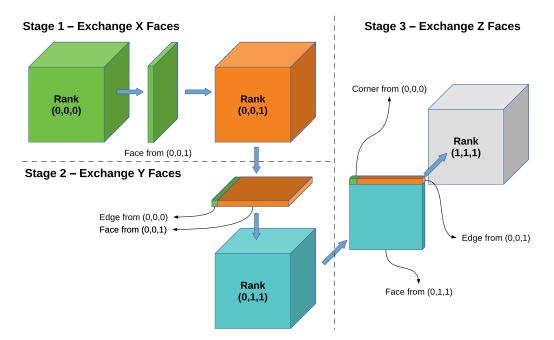

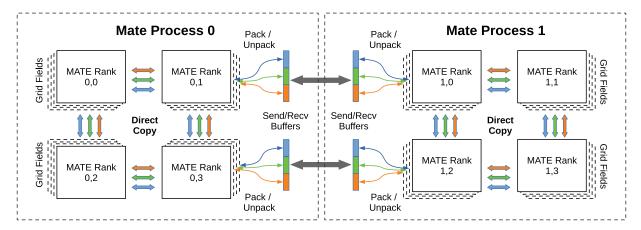

| Chapter 7  | Test Case III: Cloverleaf3D       116         7.1       Overview       116         7.2       Code Variants       117         7.2.1       Base MPI Algorithm       117         7.2.2       MATE Variant       120         7.3       Strong Scaling Studies       124         7.3.1       Cori Phase I (Haswell)       124         7.3.2       Cori Phase II (KNL)       126         7.4       Summary       128 |

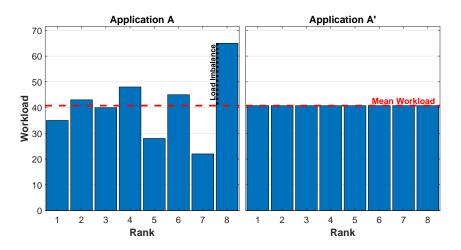

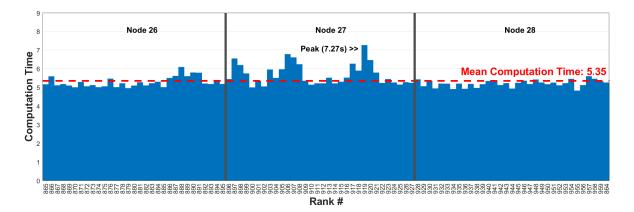

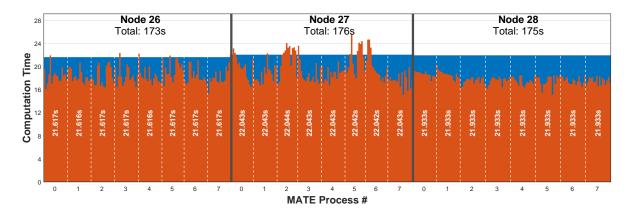

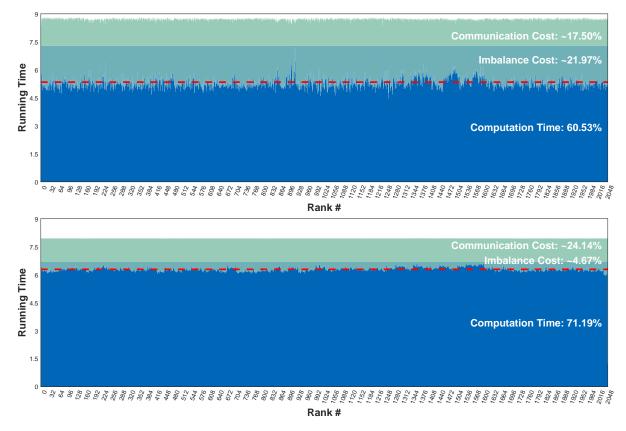

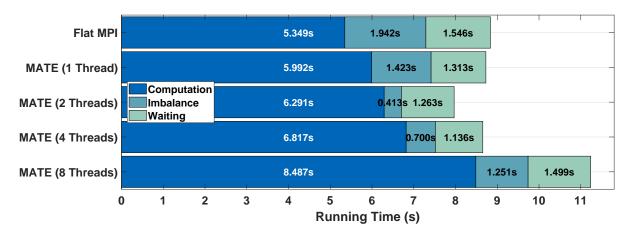

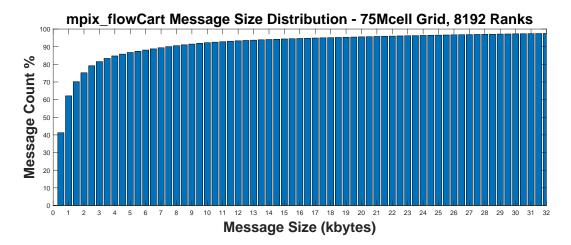

| Chapter 8  | Load Balancing1298.1Overview1298.2Example: Mpix_flowCart1328.3Rebalancing with MATE1338.3.1Mechanism I: Hierarchical Overdecomposition1338.3.2Mechanism II: Inter-Node Balancing1358.3.3Mechanism III: Intra-Node Balancing1388.4Experimental Results1398.5Concurrency Limitations1418.6Related Work1438.7Summary144                                                                                           |

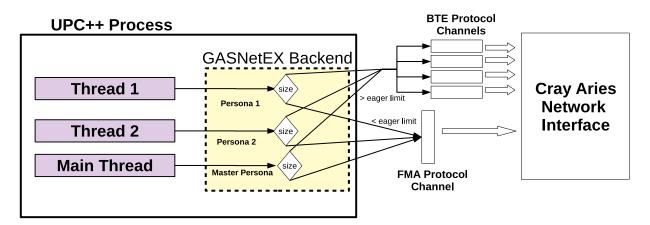

| Chapter 9  | Conclusions and Future Work1459.1Research Contributions1459.2Limitations and Future Work1469.2.1Improve Thread Concurrency1469.2.2UPC++ Integration1479.2.3CUDA Integration1479.2.4Global Variables Handling1479.2.5Lightweight Translation1489.2.6Support Fortran Annotations1489.2.7Support for Collective Communication Overlap1499.2.8Automate Graph Generation149                                         |

| Appendix A | Experimental Environment150A.1 Hardware Configuration150A.2 Software Configuration151                                                                                                                                                                                                                                                                                                                          |

| Appendix B | Code Optimizations153B.1Cache Blocking153B.2Vectorization154B.3Cubic Mapping155                                                                                                                                                                                                                                                                                                                                |

| Appendix C   | MPI Concurrency Limitation15C.1Problem 1: Thread Serialization15C.2Problem 2: Bandwidth Saturation16C.3Experimental Tests16C.3.1Possible Solution16 | 58<br>50<br>53 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Appendix D   | Load Balancing Algorithms16D.1Consecutive RebalancerD.2Shuffling Rebalancer16                                                                       | 66             |

| Appendix E   | MATE Application Programming Interface16E.1MATE Model Interface16E.2Runtime System Interface17E.3Supported MPI Functions17                          | 59<br>72       |

| Bibliography |                                                                                                                                                     | 14             |

#### LIST OF FIGURES

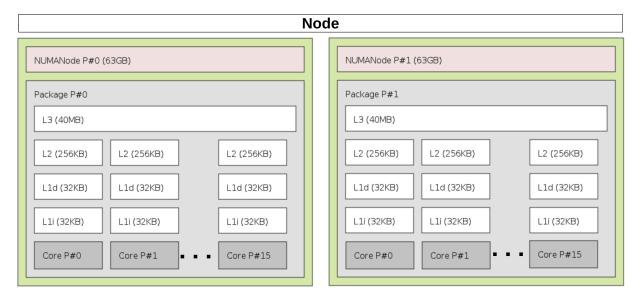

| Figure 2.1:                                                                                                                                                                                                         | Configuration of a 32-core NERSC Cori Phase I (Haswell) Node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

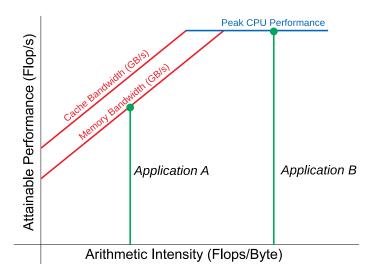

| Figure 2.2:                                                                                                                                                                                                         | Example roofline diagram that compares two applications. Application A,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                            |

|                                                                                                                                                                                                                     | limited by memory bandwidth, and Application <i>B</i> , limited by the peak CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                            |

|                                                                                                                                                                                                                     | performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9                                                                                                                                                          |

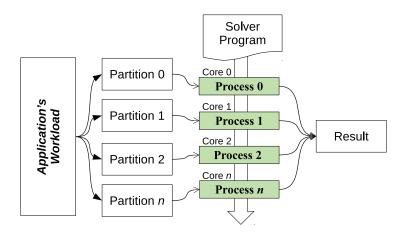

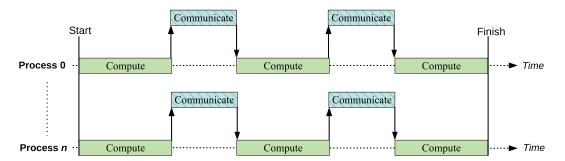

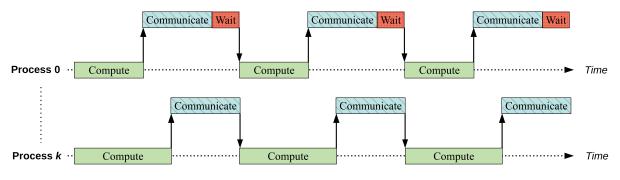

| Figure 2.3:                                                                                                                                                                                                         | Execution timeline of an SPMD application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13                                                                                                                                                         |

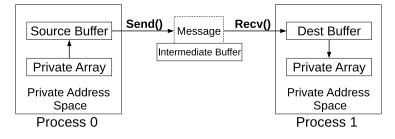

| Figure 2.4:                                                                                                                                                                                                         | Two-sided Communication Protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13                                                                                                                                                         |

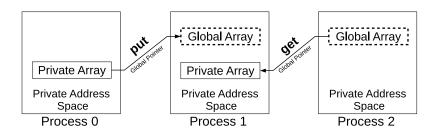

| Figure 2.5:                                                                                                                                                                                                         | One-sided Communication Protocol operations: <i>put</i> and <i>get</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14                                                                                                                                                         |

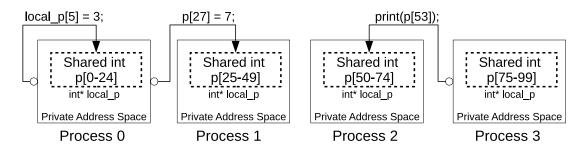

| Figure 2.6:                                                                                                                                                                                                         | Partitioning of a shared array in UPC and examples of language-enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                            |

| -                                                                                                                                                                                                                   | communication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15                                                                                                                                                         |

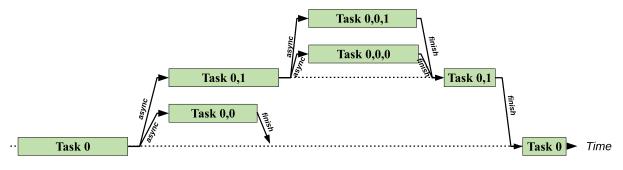

| Figure 2.7:                                                                                                                                                                                                         | Execution timeline of an asynchronous application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16                                                                                                                                                         |

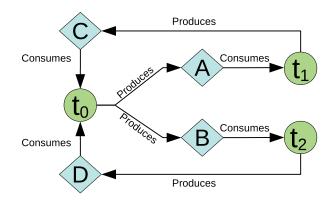

| Figure 2.8:                                                                                                                                                                                                         | Example DAG in a Dataflow application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19                                                                                                                                                         |

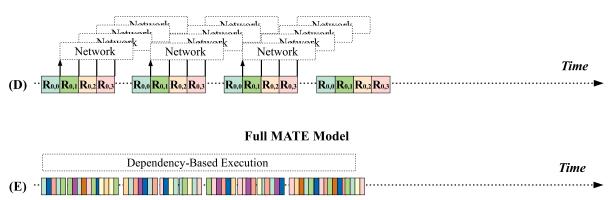

| Figure 2.9:                                                                                                                                                                                                         | Core usage timeline of a process under the bulk-synchronous model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21                                                                                                                                                         |

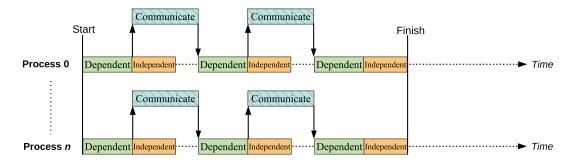

| Figure 2.10:                                                                                                                                                                                                        | Core usage timeline of a split-phase application that employs separate com-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                            |

| -                                                                                                                                                                                                                   | munication dependent and independent computation to achieve communica-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                            |

|                                                                                                                                                                                                                     | tion / computation overlap.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23                                                                                                                                                         |

| Figure 2.11:                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                            |

| -                                                                                                                                                                                                                   | to a single core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24                                                                                                                                                         |

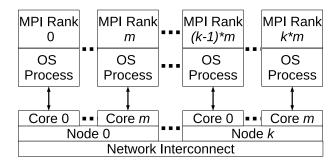

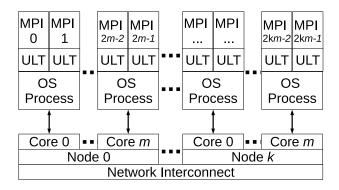

| Figure 2.12:                                                                                                                                                                                                        | A typical deployment of a hybrid MPI+KLT application where each MPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                            |

|                                                                                                                                                                                                                     | process spans a group of kernel-level threads, each mapped to a single core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25                                                                                                                                                         |

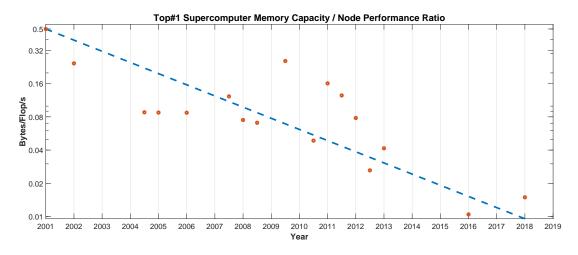

| Figure 2.13:                                                                                                                                                                                                        | Memory/Performance ratio of supercomputers since 2001. Data source: [114]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27                                                                                                                                                         |

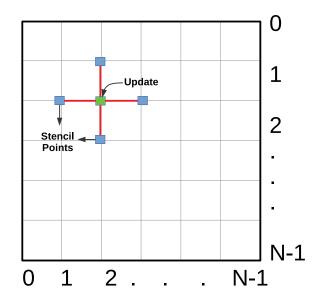

| Figure 3.1:                                                                                                                                                                                                         | Stencil solver on a 2D Grid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31                                                                                                                                                         |

|                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                            |

| 0                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                            |

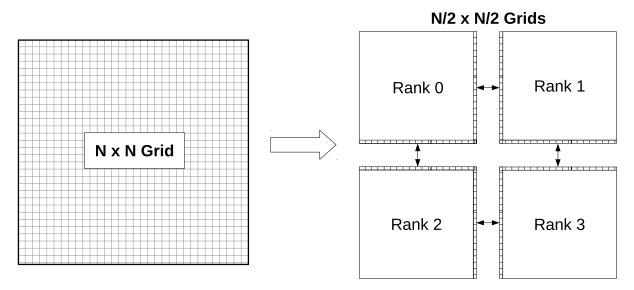

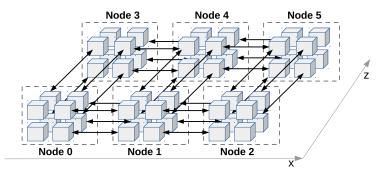

| Figure 3.2:                                                                                                                                                                                                         | SPMD Decomposition of a 2D grid into 4 MPI Ranks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32                                                                                                                                                         |

| Figure 3.2:<br>Figure 3.3:                                                                                                                                                                                          | SPMD Decomposition of a 2D grid into 4 MPI RanksMPI pseudo-code of a structured 2D grid stencil solver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32<br>33                                                                                                                                                   |

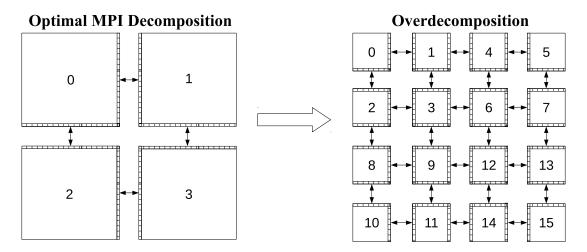

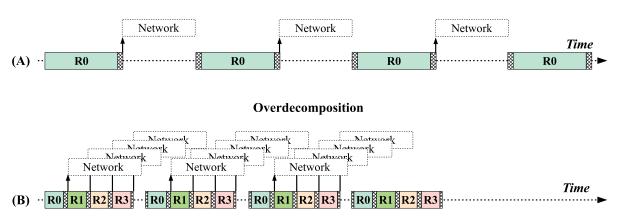

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:                                                                                                                                                                           | SPMD Decomposition of a 2D grid into 4 MPI RanksMPI pseudo-code of a structured 2D grid stencil solverTraditional Decomposition vs Overdecomposed 2D grid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32<br>33<br>34                                                                                                                                             |

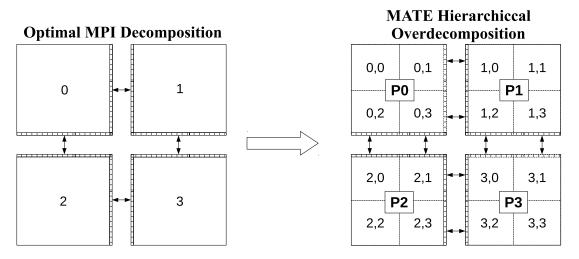

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:                                                                                                                                                            | SPMD Decomposition of a 2D grid into 4 MPI Ranks.MPI pseudo-code of a structured 2D grid stencil solver.Traditional Decomposition vs Overdecomposed 2D grid.Traditional Decomposition vs MATE Hierarchical overdecomposition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32<br>33<br>34<br>36                                                                                                                                       |

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:<br>Figure 3.6:                                                                                                                                             | SPMD Decomposition of a 2D grid into 4 MPI Ranks.MPI pseudo-code of a structured 2D grid stencil solver.Traditional Decomposition vs Overdecomposed 2D grid.Traditional Decomposition vs MATE Hierarchical overdecomposition.Simplified pseudo-code of the 13-point stencil solver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32<br>33<br>34<br>36<br>37                                                                                                                                 |

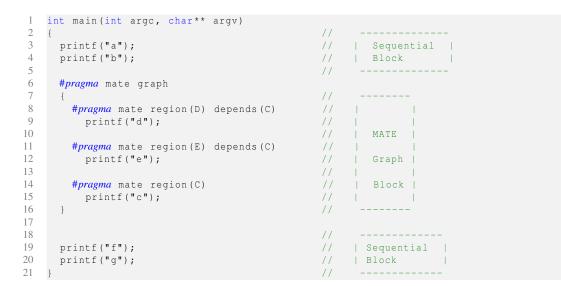

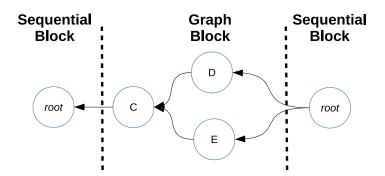

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:<br>Figure 3.6:<br>Figure 3.7:                                                                                                                              | SPMD Decomposition of a 2D grid into 4 MPI Ranks.MPI pseudo-code of a structured 2D grid stencil solver.Traditional Decomposition vs Overdecomposed 2D grid.Traditional Decomposition vs MATE Hierarchical overdecomposition.Simplified pseudo-code of the 13-point stencil solver.Simple example of a MATE-annotated program.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32<br>33<br>34<br>36                                                                                                                                       |

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:<br>Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:                                                                                                               | SPMD Decomposition of a 2D grid into 4 MPI Ranks.MPI pseudo-code of a structured 2D grid stencil solver.Traditional Decomposition vs Overdecomposed 2D grid.Traditional Decomposition vs MATE Hierarchical overdecomposition.Simplified pseudo-code of the 13-point stencil solver.Simple example of a MATE-annotated program.Dependency graph of the MATE-annotated for loop in Fig. 3.8.                                                                                                                                                                                                                                                                                                                                                                                                                            | 32<br>33<br>34<br>36<br>37<br>39                                                                                                                           |

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:<br>Figure 3.6:<br>Figure 3.7:                                                                                                                              | SPMD Decomposition of a 2D grid into 4 MPI Ranks.MPI pseudo-code of a structured 2D grid stencil solver.Traditional Decomposition vs Overdecomposed 2D grid.Traditional Decomposition vs MATE Hierarchical overdecomposition.Simplified pseudo-code of the 13-point stencil solver.Simple example of a MATE-annotated program.Dependency graph of the MATE-annotated <i>for</i> loop in Fig. 3.8.Pseudo-code example of (top) an incorrect description, and (bottom) a cor-                                                                                                                                                                                                                                                                                                                                           | 32<br>33<br>34<br>36<br>37<br>39                                                                                                                           |

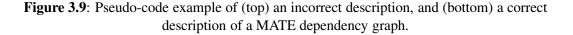

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:<br>Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 3.9:                                                                                                | SPMD Decomposition of a 2D grid into 4 MPI Ranks.MPI pseudo-code of a structured 2D grid stencil solver.Traditional Decomposition vs Overdecomposed 2D grid.Traditional Decomposition vs MATE Hierarchical overdecomposition.Simplified pseudo-code of the 13-point stencil solver.Simple example of a MATE-annotated program.Dependency graph of the MATE-annotated <i>for</i> loop in Fig. 3.8.Pseudo-code example of (top) an incorrect description, and (bottom) a correct description of a MATE dependency graph.                                                                                                                                                                                                                                                                                                | 32<br>33<br>34<br>36<br>37<br>39<br>39                                                                                                                     |

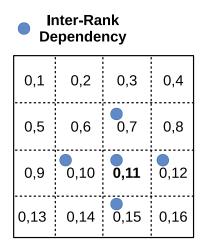

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:<br>Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 3.9:<br>Figure 3.10:                                                                                | SPMD Decomposition of a 2D grid into 4 MPI Ranks.MPI pseudo-code of a structured 2D grid stencil solver.Traditional Decomposition vs Overdecomposed 2D grid.Traditional Decomposition vs MATE Hierarchical overdecomposition.Simplified pseudo-code of the 13-point stencil solver.Simple example of a MATE-annotated program.Dependency graph of the MATE-annotated <i>for</i> loop in Fig. 3.8.Pseudo-code example of (top) an incorrect description, and (bottom) a correct description of a MATE dependency graph.Example use of MATE's inter-rank dependencies.                                                                                                                                                                                                                                                  | <ul> <li>32</li> <li>33</li> <li>34</li> <li>36</li> <li>37</li> <li>39</li> <li>39</li> <li>41</li> </ul>                                                 |

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:<br>Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 3.9:<br>Figure 3.10:<br>Figure 3.11:                                                                | SPMD Decomposition of a 2D grid into 4 MPI Ranks.MPI pseudo-code of a structured 2D grid stencil solver.Traditional Decomposition vs Overdecomposed 2D grid.Traditional Decomposition vs MATE Hierarchical overdecomposition.Simplified pseudo-code of the 13-point stencil solver.Simple example of a MATE-annotated program.Dependency graph of the MATE-annotated <i>for</i> loop in Fig. 3.8.Pseudo-code example of (top) an incorrect description, and (bottom) a correct description of a MATE dependency graph.Example use of MATE's inter-rank dependencies.Inter-rank dependencies for rank (0,11).                                                                                                                                                                                                          | <ul> <li>32</li> <li>33</li> <li>34</li> <li>36</li> <li>37</li> <li>39</li> <li>39</li> <li>41</li> <li>42</li> </ul>                                     |

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:<br>Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 3.9:<br>Figure 3.10:<br>Figure 3.11:<br>Figure 3.12:                                                | SPMD Decomposition of a 2D grid into 4 MPI Ranks.MPI pseudo-code of a structured 2D grid stencil solver.Traditional Decomposition vs Overdecomposed 2D grid.Traditional Decomposition vs MATE Hierarchical overdecomposition.Simplified pseudo-code of the 13-point stencil solver.Simple example of a MATE-annotated program.Dependency graph of the MATE-annotated <i>for</i> loop in Fig. 3.8.Pseudo-code example of (top) an incorrect description, and (bottom) a correct description of a MATE dependency graph.Example use of MATE's inter-rank dependencies.Inter-rank dependencies for rank (0,11).Example of a MATE-annotated <i>for</i> loop.                                                                                                                                                              | <ul> <li>32</li> <li>33</li> <li>34</li> <li>36</li> <li>37</li> <li>39</li> <li>39</li> <li>41</li> <li>42</li> <li>43</li> </ul>                         |

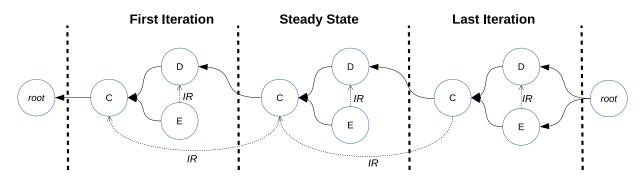

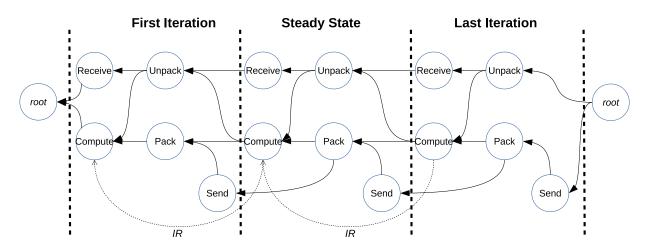

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:<br>Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 3.9:<br>Figure 3.10:<br>Figure 3.11:<br>Figure 3.12:                                                | SPMD Decomposition of a 2D grid into 4 MPI Ranks.MPI pseudo-code of a structured 2D grid stencil solver.Traditional Decomposition vs Overdecomposed 2D grid.Traditional Decomposition vs MATE Hierarchical overdecomposition.Simplified pseudo-code of the 13-point stencil solver.Simple example of a MATE-annotated program.Dependency graph of the MATE-annotated <i>for</i> loop in Fig. 3.8.Pseudo-code example of (top) an incorrect description, and (bottom) a correct description of a MATE dependency graph.Example use of MATE's inter-rank dependencies.Inter-rank dependencies for rank (0,11).Example of a MATE-annotated <i>for</i> loop.Dependency graph of the MATE-annotated <i>for</i> loop in Fig. 3.12. IR = Inter-                                                                              | <ul> <li>32</li> <li>33</li> <li>34</li> <li>36</li> <li>37</li> <li>39</li> <li>39</li> <li>41</li> <li>42</li> <li>43</li> </ul>                         |

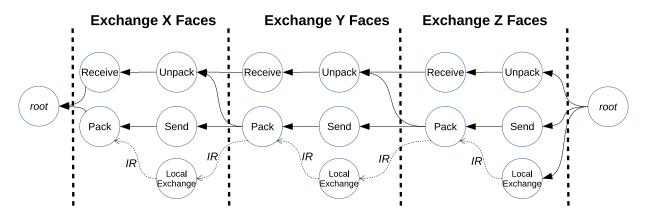

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:<br>Figure 3.6:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 3.9:<br>Figure 3.10:<br>Figure 3.11:<br>Figure 3.12:<br>Figure 3.13:                                | SPMD Decomposition of a 2D grid into 4 MPI Ranks.MPI pseudo-code of a structured 2D grid stencil solver.Traditional Decomposition vs Overdecomposed 2D grid.Traditional Decomposition vs MATE Hierarchical overdecomposition.Simplified pseudo-code of the 13-point stencil solver.Simple example of a MATE-annotated program.Dependency graph of the MATE-annotated <i>for</i> loop in Fig. 3.8.Pseudo-code example of (top) an incorrect description, and (bottom) a correct description of a MATE dependency graph.Example use of MATE's inter-rank dependencies.Inter-rank dependencies for rank (0,11).Example of a MATE-annotated <i>for</i> loop.                                                                                                                                                              | <ul> <li>32</li> <li>33</li> <li>34</li> <li>36</li> <li>37</li> <li>39</li> <li>39</li> <li>41</li> <li>42</li> <li>43</li> <li>44</li> </ul>             |

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:<br>Figure 3.6:<br>Figure 3.7:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 3.9:<br>Figure 3.10:<br>Figure 3.11:<br>Figure 3.12:<br>Figure 3.13:                 | SPMD Decomposition of a 2D grid into 4 MPI Ranks.MPI pseudo-code of a structured 2D grid stencil solver.Traditional Decomposition vs Overdecomposed 2D grid.Traditional Decomposition vs MATE Hierarchical overdecomposition.Simplified pseudo-code of the 13-point stencil solver.Simple example of a MATE-annotated program.Dependency graph of the MATE-annotated for loop in Fig. 3.8.Pseudo-code example of (top) an incorrect description, and (bottom) a correct description of a MATE dependency graph.Example use of MATE's inter-rank dependencies.Inter-rank dependencies for rank (0,11).Example of a MATE-annotated for loop in Fig. 3.12. IR = Inter-rank dependency.                                                                                                                                   | <ul> <li>32</li> <li>33</li> <li>34</li> <li>36</li> <li>37</li> <li>39</li> <li>39</li> <li>41</li> <li>42</li> <li>43</li> <li>44</li> <li>44</li> </ul> |

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:<br>Figure 3.6:<br>Figure 3.7:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 3.9:<br>Figure 3.10:<br>Figure 3.11:<br>Figure 3.12:<br>Figure 3.14:<br>Figure 3.15: | SPMD Decomposition of a 2D grid into 4 MPI Ranks.MPI pseudo-code of a structured 2D grid stencil solver.Traditional Decomposition vs Overdecomposed 2D grid.Traditional Decomposition vs MATE Hierarchical overdecomposition.Simplified pseudo-code of the 13-point stencil solver.Simple example of a MATE-annotated program.Dependency graph of the MATE-annotated <i>for</i> loop in Fig. 3.8.Pseudo-code example of (top) an incorrect description, and (bottom) a correct description of a MATE dependency graph.Example use of MATE's inter-rank dependencies.Inter-rank dependencies for rank (0,11).Example of a MATE-annotated <i>for</i> loop in Fig. 3.12. IR = Interrank dependency.Simple example of a MATE-annotated <i>for</i> loop in Fig. 3.12. IR = Interrank dependency.                           | <ul> <li>32</li> <li>33</li> <li>34</li> <li>36</li> <li>37</li> <li>39</li> <li>39</li> <li>41</li> <li>42</li> <li>43</li> <li>44</li> <li>45</li> </ul> |

| Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:<br>Figure 3.6:<br>Figure 3.7:<br>Figure 3.7:<br>Figure 3.8:<br>Figure 3.9:<br>Figure 3.10:<br>Figure 3.11:<br>Figure 3.12:<br>Figure 3.14:<br>Figure 3.15: | SPMD Decomposition of a 2D grid into 4 MPI Ranks.MPI pseudo-code of a structured 2D grid stencil solver.Traditional Decomposition vs Overdecomposed 2D grid.Traditional Decomposition vs MATE Hierarchical overdecomposition.Simplified pseudo-code of the 13-point stencil solver.Simple example of a MATE-annotated program.Dependency graph of the MATE-annotated <i>for</i> loop in Fig. 3.8.Pseudo-code example of (top) an incorrect description, and (bottom) a correct description of a MATE dependency graph.Example use of MATE's inter-rank dependencies.Inter-rank dependencies for rank (0,11).Example of a MATE-annotated <i>for</i> loop in Fig. 3.12. IR = Interrank dependency.Simple example of a MATE-annotated program.Solver section of the Code from 3.6, enhanced with a MATE dependency graph | <ul> <li>32</li> <li>33</li> <li>34</li> <li>36</li> <li>37</li> <li>39</li> <li>39</li> <li>41</li> <li>42</li> <li>43</li> <li>44</li> <li>45</li> </ul> |

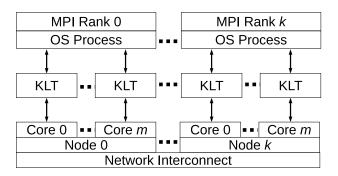

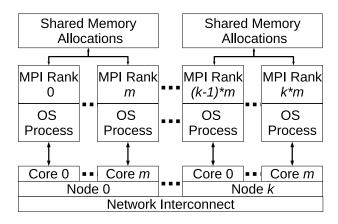

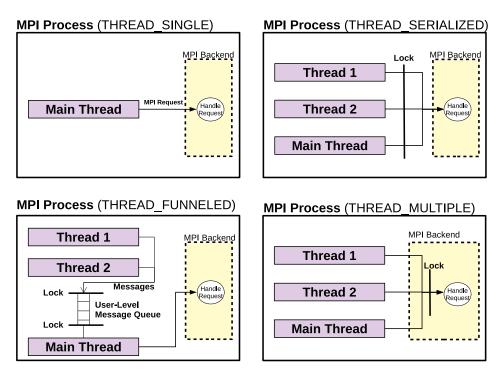

| -            | Example deployment of a hybrid MPI+SHM application where node co-<br>located MPI processes can communicate through shared memory<br>Example deployment of a hybrid MPI+ULT application where each MPI<br>process is assigned a single core, but spans multiple MPI ranks, imple- | 52  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | mented as ULTs                                                                                                                                                                                                                                                                   | 53  |

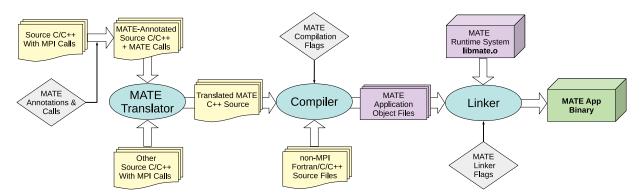

| Figure 4.1:  | Annotation and compilation flowchart of a MATE application.                                                                                                                                                                                                                      | 58  |

| Figure 4.2:  | Annotated section of the code in 3.15.                                                                                                                                                                                                                                           | 60  |

| Figure 4.3:  | Step 1 of translation replaces MPI calls with its equivalent MATE call                                                                                                                                                                                                           | 61  |

| Figure 4.4:  | Step 2 of translation creates scheduling structures for a region-level execution.                                                                                                                                                                                                | 62  |

| Figure 4.5:  | Step 3 of translation creates the structures to support <i>for</i> -loop based graphs.                                                                                                                                                                                           | 64  |

| Figure 4.6:  | The final step of translation creates a surrogate <i>main</i> function and defines                                                                                                                                                                                               |     |

|              | the dependency graphs.                                                                                                                                                                                                                                                           | 65  |

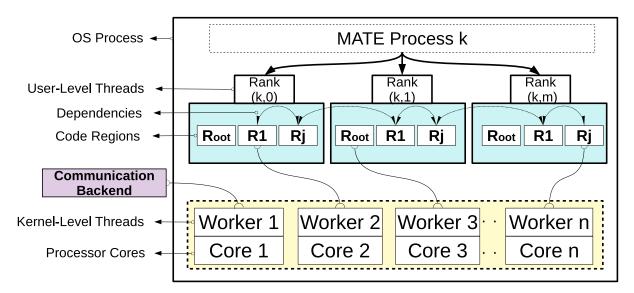

| Figure 4.7:  | Decomposition model and implementation of a MATE process.                                                                                                                                                                                                                        | 66  |

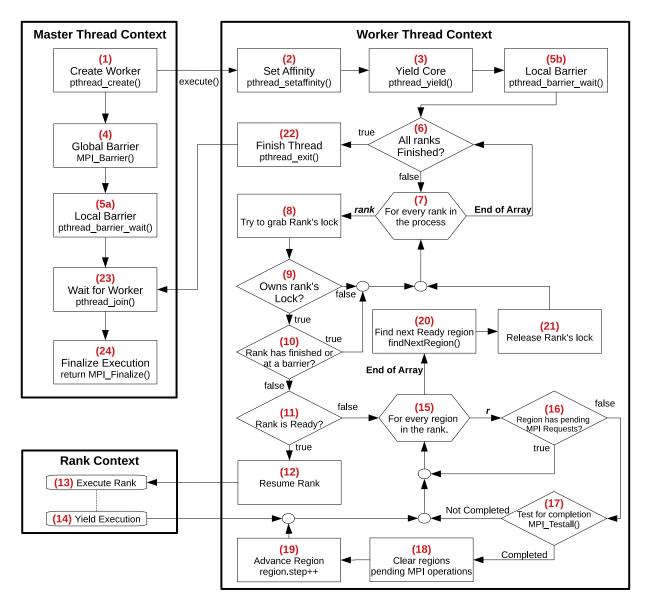

| Figure 4.8:  | Lifetime of a MATE worker.                                                                                                                                                                                                                                                       | 69  |

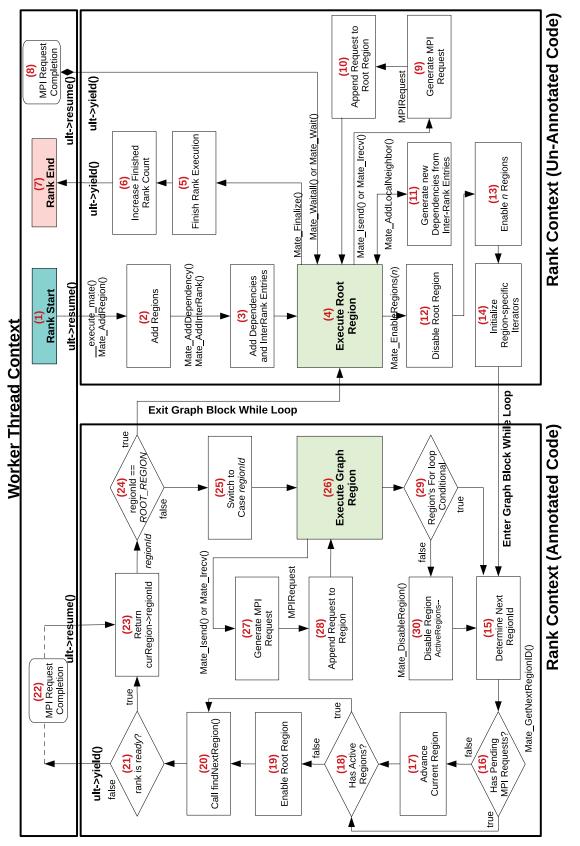

| Figure 4.9:  | Lifetime of a MATE Rank.                                                                                                                                                                                                                                                         | 71  |

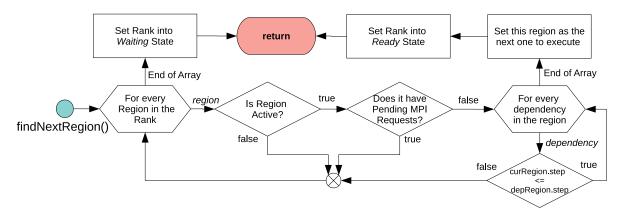

| Figure 4.10: | Flowchart of the findNextRegion method.                                                                                                                                                                                                                                          | 74  |

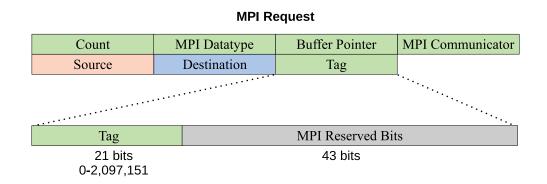

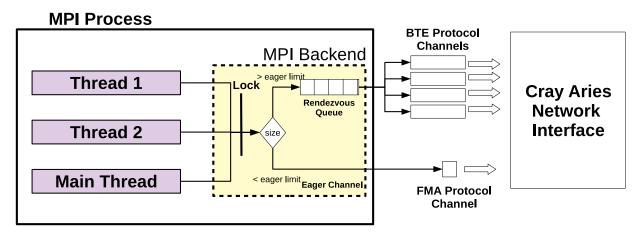

| Figure 4.11: | Structure of an MPI request.                                                                                                                                                                                                                                                     | 77  |

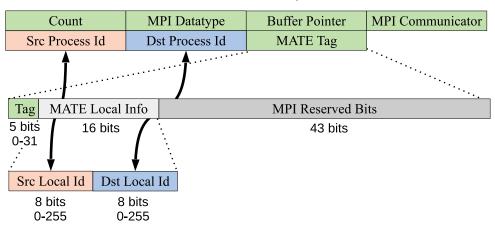

| Figure 4.12: | Structure of a MATE/MPI request, including local rank identifiers in the tag                                                                                                                                                                                                     |     |

|              | field                                                                                                                                                                                                                                                                            | 78  |

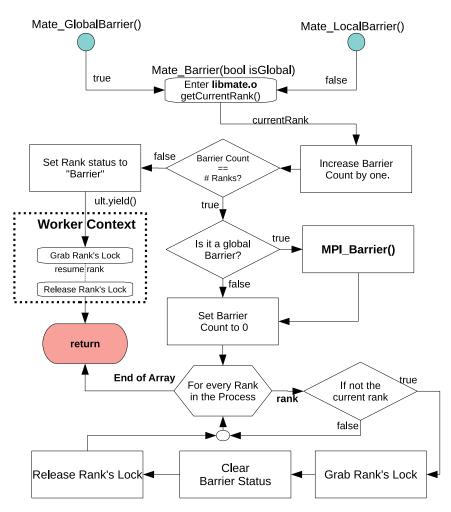

| Figure 4.13: | Flowchart of MATE barrier mechanisms.                                                                                                                                                                                                                                            | 80  |

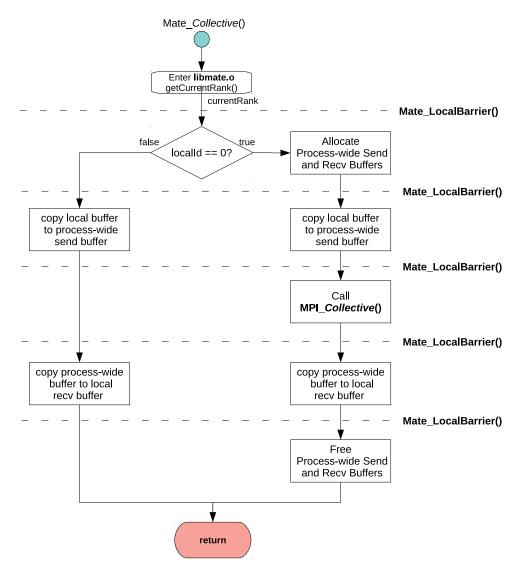

| Figure 4.14: | Flowchart of MATE collective communication operations.                                                                                                                                                                                                                           | 81  |

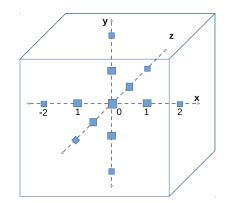

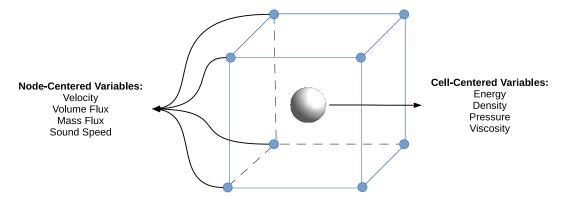

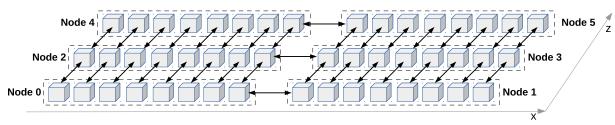

| Figure 5.1:  | 13-Point Stencil on a three-dimensional grid.                                                                                                                                                                                                                                    | 83  |

| Figure 5.2:  | Pseudo-code of the solver kernel of Jacobi3D                                                                                                                                                                                                                                     | 84  |

| Figure 5.3:  | Verification code for Jacobi3D                                                                                                                                                                                                                                                   | 85  |

| Figure 5.4:  | Pseudo-code of the manually overlapping variant of Jacobi3D                                                                                                                                                                                                                      | 87  |

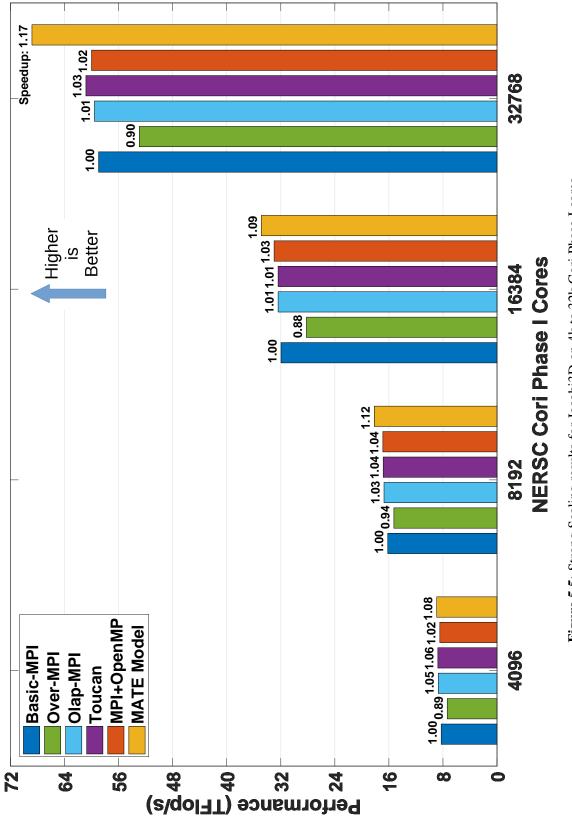

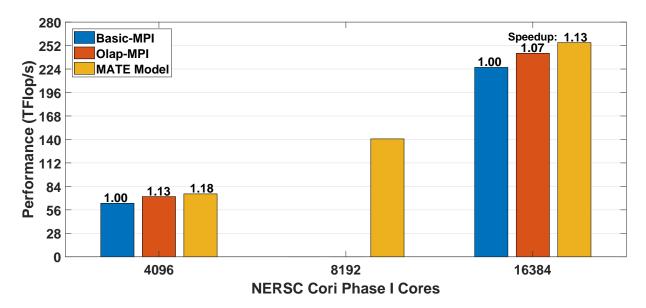

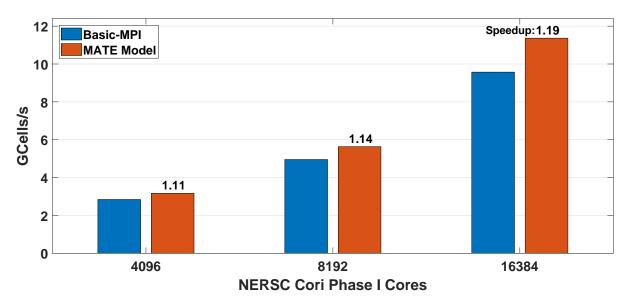

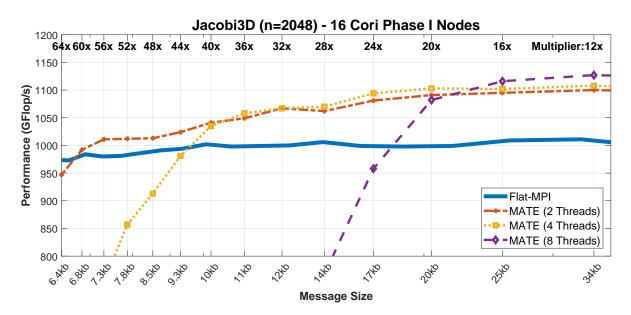

| Figure 5.5:  | Strong Scaling results for Jacobi3D on 4k to 32k Cori Phase I cores. The                                                                                                                                                                                                         |     |

|              | number above each bar represents the total speedup compared to Basic-MPI.                                                                                                                                                                                                        | 89  |

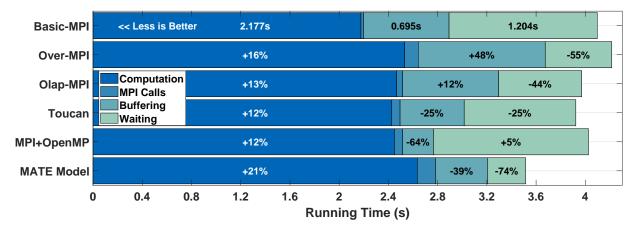

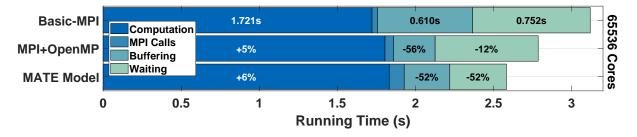

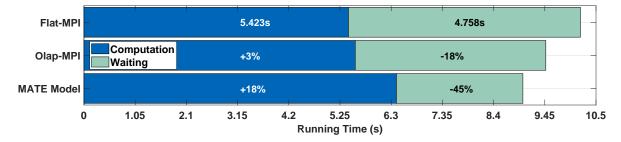

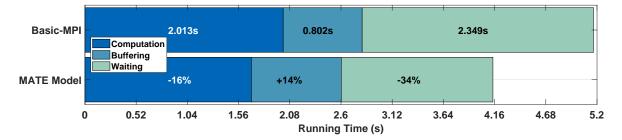

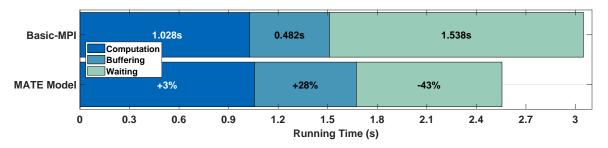

| Figure 5.6:  | Time spent on different phases of our solver on 32k Cori Phase I cores                                                                                                                                                                                                           | 90  |

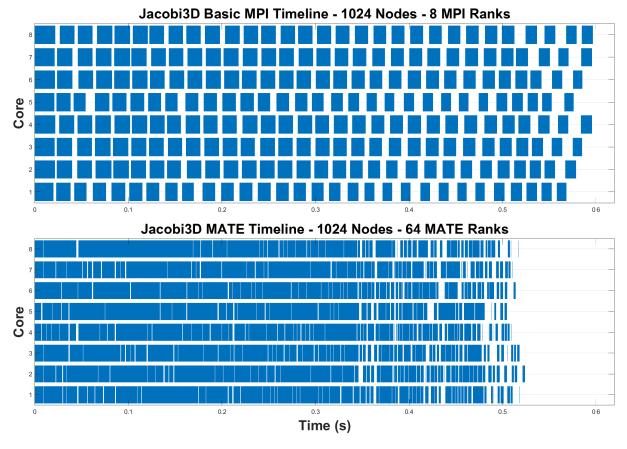

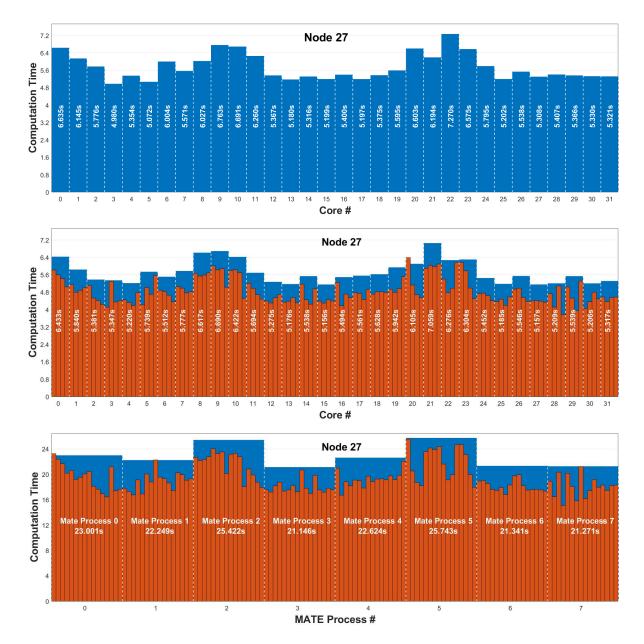

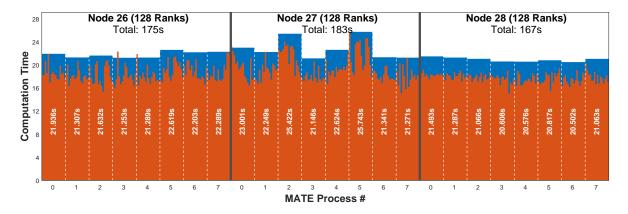

| Figure 5.7:  | Core Timelines. (Top) Basic MPI (8 Ranks), (Bottom) MATE (64 Ranks)                                                                                                                                                                                                              | 93  |

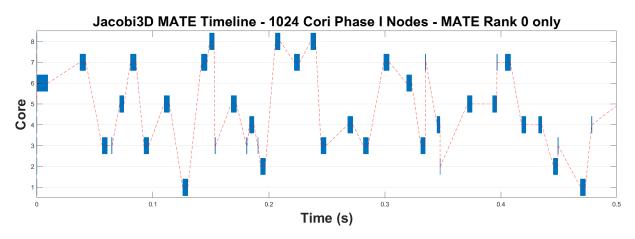

| Figure 5.8:  | Timeline of local rank 0 transitioning across the 8 cores in the MATE process.                                                                                                                                                                                                   | 93  |

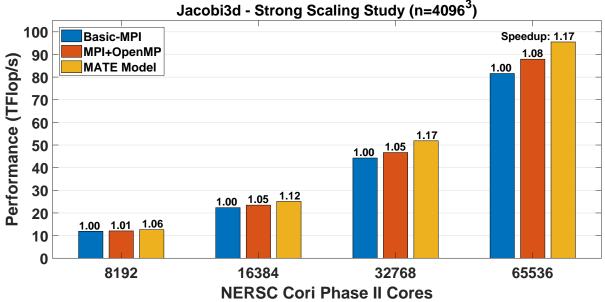

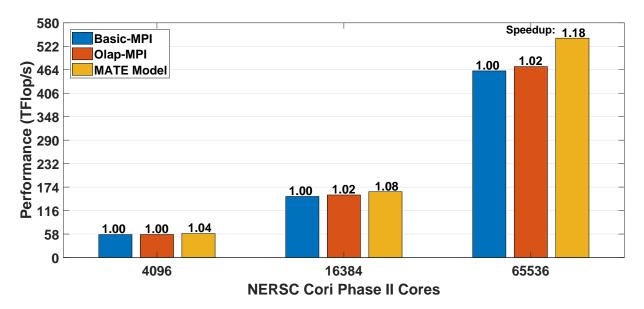

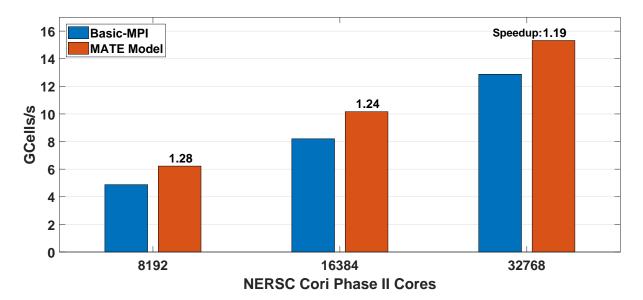

| Figure 5.9:  | Strong Scaling results for Jacobi3D on 8k to 64k Cori Phase II cores                                                                                                                                                                                                             | 94  |

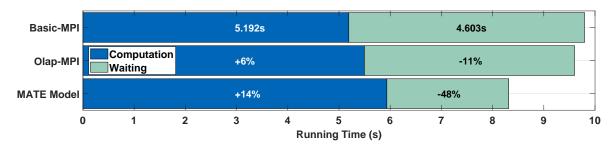

| Figure 5.10: | Time spent on different phases our solver on 64k Cori Phase II cores                                                                                                                                                                                                             | 94  |

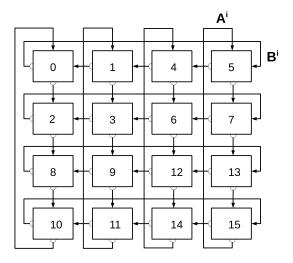

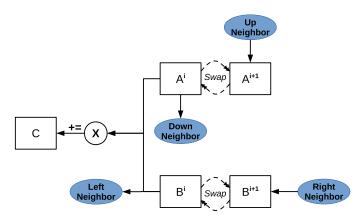

| Figure 6.1:  | Baseline Cannon2D algorithm where ranks shift the A and B submatrices                                                                                                                                                                                                            |     |

|              |                                                                                                                                                                                                                                                                                  | 100 |

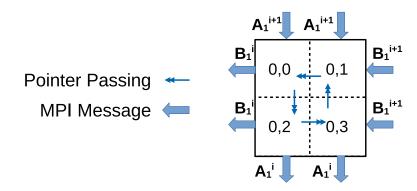

| Figure 6.2:  |                                                                                                                                                                                                                                                                                  | 101 |