Three Fingered Jack: Productively Addressing Platform Diversity

by

David Bradley Sheffield

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Kurt W. Keutzer, Chair Professor Krste Asanović Professor David Wessel

Fall 2013

#### Three Fingered Jack: Productively Addressing Platform Diversity

Copyright 2013 by David Bradley Sheffield

#### Abstract

Three Fingered Jack: Productively Addressing Platform Diversity

by

#### David Bradley Sheffield

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Kurt W. Keutzer, Chair

Moore's Law has given the application designer a large palette of potential computational substrates. The application designer can potential map his or her application onto specialized task-specific accelerators for either energy or performance benefits; however, the design space for task-specific accelerators is large. At one extreme is the conventional microprocessor, easy to program but relatively low-performance and energy inefficient. At the other extreme is custom, fixed-function hardware crafted solely for a given task. Studies have reported energy-efficiency gains using fixed-function hardware from  $2\times$  to  $100\times$  over programmable solutions. If we wish to evaluate this design space we need prototypes for the elements of it; however, constructing functional prototypes for each hardware substrate is a daunting prospect. This is because each implementation target requires a radically different set of programming and design tools.

To address the challenges of mapping applications across a broad range of targets, this thesis presents Three Fingered Jack. Three Fingered Jack is a highly productive approach to generating applications that run on multicore CPUs or data-parallel processors. Three Fingered Jack also integrates a high-level hardware synthesis engine that has the ability to generate custom hardware implementations.

Three Fingered Jack applies dependence analysis and reordering transformations to a restricted set of Python loop nests to uncover parallelism. By exploiting data parallelism, Three Fingered Jack allows the programmer to use the same Python source to target all three supported platforms. It exploits this parallelism on CPUs and vector-thread processors by generating multithreaded code with short-vector instructions. The high-level hardware synthesis engine uses the parallelism found by the system to both exploit memory-level parallelism and automatically generate multiple parallel processing engines.

On a 3.4 GHz Intel i7-2600 CPU, Three Fingered Jack generated software solutions that obtained performance between  $0.97\text{-}113.3\times$  of hand-written C++ across four kernels and two applications. Over four kernels, Three Fingered Jacks high-level synthesis results are between  $1.5\text{-}12.1\times$  faster than an optimized soft-core CPU on a Zynq XC7Z020 FPGA. When evaluated in a 45nm ASIC technology, the results of Three Fingered Jacks high-level synthesis system is  $3.6\times$  more efficient than an optimized scalar processor on the key kernels

used in automatic speech recognition. On the same speech recognition kernels, the hardware results are  $2.4\times$  more energy efficient than a highly optimized data-parallel processor.

To my family – Mom, Dad, Johnny, and last but certainly not least, my fiancee Genevieve. Thanks to Mom and Dad for building the foundation of who I am today. Genevieve, the last six years would not have been possible without you. Your encouragement and support kept me going when graduation seemed like an impossibility.

## Contents

| Li            | st of                | Figures    |                                                 |  |      |   |  | v      |

|---------------|----------------------|------------|-------------------------------------------------|--|------|---|--|--------|

| $\mathbf{Li}$ | st of                | Tables     |                                                 |  |      |   |  | xi     |

| 1             | Intr                 | oduction   |                                                 |  |      |   |  | 1      |

|               | 1.1                  | The Diver  | sity of Potential Platforms                     |  | <br> |   |  | <br>2  |

|               | 1.2                  | The Delive | ery of an Application on Diverse Platforms      |  | <br> |   |  | <br>4  |

|               | 1.3                  | Thesis Co  | ntributions                                     |  | <br> |   |  | <br>5  |

|               | 1.4                  | Thesis Ou  | tline                                           |  | <br> | • |  | <br>6  |

| 2             | Bac                  | kground a  | and Motivation                                  |  |      |   |  | 8      |

|               | 2.1                  | Explosion  | of Potential Implementation Platforms $$ . $$ . |  | <br> |   |  | <br>8  |

|               | 2.2                  | Trends in  | Hardware and Software                           |  | <br> |   |  | <br>12 |

|               |                      | 2.2.1 Mo   | bile hardware                                   |  | <br> |   |  | <br>13 |

|               |                      | 2.2.2 So   | ftware                                          |  | <br> |   |  | <br>15 |

|               | 2.3                  | Our Solut  | ion: Three Fingered Jack                        |  | <br> |   |  | <br>15 |

|               | 2.4                  | Related W  | Vork                                            |  | <br> |   |  | <br>16 |

|               |                      | 2.4.1 So   | ftware                                          |  | <br> |   |  | <br>16 |

|               |                      | 2.4.2 Ha   | rdware                                          |  | <br> |   |  | <br>17 |

|               | 2.5                  | Summary    |                                                 |  | <br> |   |  | <br>19 |

| 3             | $\operatorname{Thr}$ | ee Finger  | ed Jack: Software Approaches                    |  |      |   |  | 20     |

|               | 3.1                  | Dependen   | ce Analysis and Reordering Transforms           |  | <br> |   |  | <br>20 |

|               |                      | 3.1.1 Th   | eory of Loop Dependence                         |  | <br> |   |  | <br>21 |

|               |                      | 3.1.2 An   | alyzing Loop Dependence                         |  | <br> |   |  | <br>22 |

|               |                      |            | ordering Transforms                             |  |      |   |  | 24     |

|               | 3.2                  |            | ted Subset of Python                            |  |      |   |  | 25     |

|               |                      |            | pported Grammar                                 |  |      |   |  | 26     |

|               |                      | 3.2.2 Su   | pported Data Types                              |  | <br> |   |  | <br>27 |

|               | 3.3                  |            | rare Architecture of TFJ                        |  |      |   |  | 28     |

|               |                      |            | thon Front-End                                  |  |      |   |  | 28     |

|               |                      | v          | TJ's Dependence and Reordering Engine           |  |      |   |  | 29     |

|               |                      |            | de Generation                                   |  |      |   |  | 32     |

|               |                      |            | ctor-Thread Code Generation                     |  |      |   |  | 35     |

CONTENTS iii

|   | 3.4               | 3.3.5 Run-time                                                |

|---|-------------------|---------------------------------------------------------------|

| 4 | Thr               | ree Fingered Jack: Evaluation of Software Approaches 39       |

| • | 4.1               | Overview and Setup                                            |

|   | 4.2               | Numerical Kernels                                             |

|   | 1.4               | 4.2.1 Vector-Vector Addition                                  |

|   |                   | 4.2.2 Matrix Multiply                                         |

|   |                   | 4.2.3 Diagonal Sparse-Matrix Vector Multiply                  |

|   |                   | 4.2.4 Back Propagation Weight Adjustment                      |

|   |                   | 4.2.5 Numerical Kernel Results                                |

|   | 4.3               | Small Applications                                            |

|   | 4.0               | 4.3.1 Content-Aware Image Resizing                            |

|   |                   | 4.3.2 Horn-Schunck Optical Flow                               |

|   | 4.4               | Autotuning Using TFJ Demonstrated With Matrix Multiply        |

|   | $\frac{4.4}{4.5}$ |                                                               |

|   |                   |                                                               |

|   | 4.6               | Summary                                                       |

| 5 |                   | ree Fingered Jack: Hardware Approaches 61                     |

|   | 5.1               | The Architecture of TFJ's Processing Engine Clusters          |

|   | 5.2               | Our High-Level Hardware Synthesis Flow                        |

|   |                   | 5.2.1 Datapath Scheduling                                     |

|   |                   | 5.2.2 Generation of Non-blocking Memory Operations 71         |

|   |                   | 5.2.3 Register Binding                                        |

|   |                   | 5.2.4 A Library of Hardware Components                        |

|   | 5.3               | Evaluation of Numerical Kernels on a FPGA                     |

|   |                   | 5.3.1 Overview of Numerical Kernels                           |

|   |                   | 5.3.2 Evaluation Setup                                        |

|   |                   | 5.3.3 Results and Analysis                                    |

|   | 5.4               | Case Study: Tuning Hardware Matrix Multiply                   |

|   |                   | 5.4.1 Results                                                 |

|   | 5.5               | Summary                                                       |

| 6 | <b>A C</b>        | Case Study in Speech Recognition using Three Fingered Jack 94 |

|   | 6.1               | Challenges for Mobile Speech Recognition                      |

|   | 6.2               | Speech Recognition Background                                 |

|   |                   | 6.2.1 Profiling Our Speech Recognizer                         |

|   | 6.3               | Accelerated Speech Recognition Kernels                        |

|   | 6.4               | Hardware Verification                                         |

|   | 6.5               | Hardware and Software Evaluation                              |

|   |                   | 6.5.1 Rocket-Hwacha Data-Parallel Processor                   |

|   |                   | 6.5.2 VLSI Flow                                               |

|   |                   | 6.5.3 VLSI results                                            |

|   | 6.6               | Summary                                                       |

|   | 0.0               |                                                               |

CONTENTS iv

| 7  | Con   | nclusions and Future Work                                                 | 111 |

|----|-------|---------------------------------------------------------------------------|-----|

|    | 7.1   | Contributions                                                             | 111 |

|    |       | 7.1.1 Three Fingered Jack                                                 | 112 |

|    |       | 7.1.2 A Case Study in Mobile Speech Recognition using Three Fingered Jack | 113 |

|    | 7.2   | Future Work                                                               | 114 |

|    | 7.3   | Summary                                                                   | 115 |

| Bi | bliog | graphy                                                                    | 116 |

## List of Figures

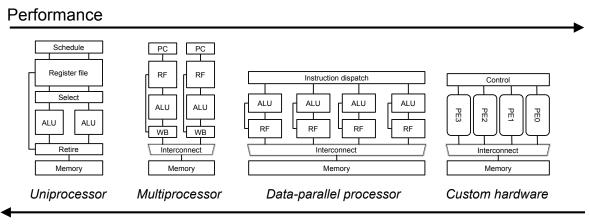

| 1.1 | The design space of hardware accelerators: Performance and energy-efficiency,   |    |

|-----|---------------------------------------------------------------------------------|----|

|     | for a given task, increases from left to right while programability decreases.  |    |

|     | Figure adapted from Fisher [54]                                                 | 3  |

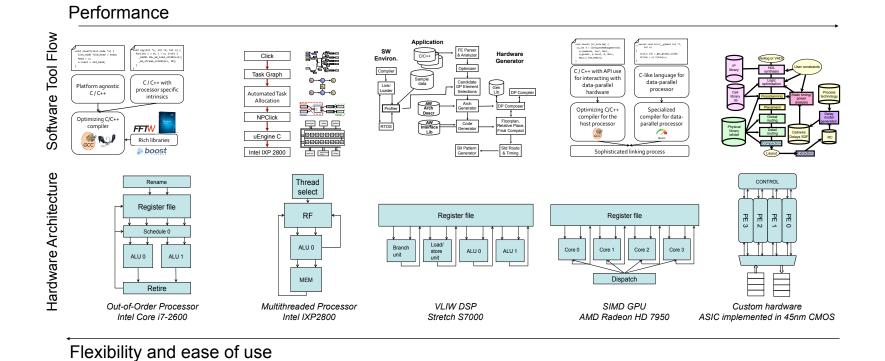

| 2.1 | Each target hardware platform has its own development environment – man-        |    |

|     | ual design-space exploration is time consuming and error-prone                  | 11 |

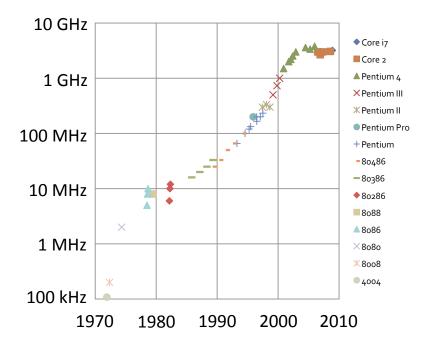

| 2.2 | Processor clock scaling trends for 40 years of Intel CPUs. Figure adapted       |    |

|     | from Bryan Catanzaro's thesis [30]                                              | 12 |

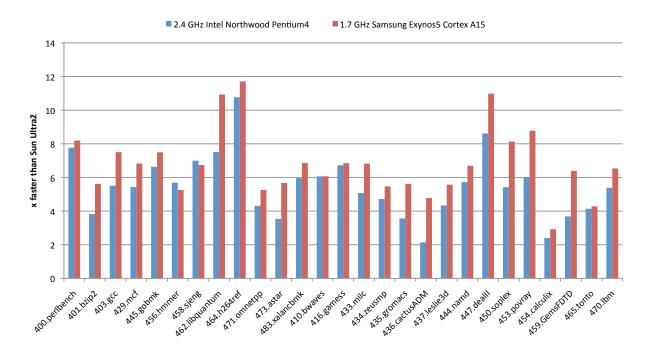

| 2.3 | Contemporary mobile devices have performance similar to high-end desktop        |    |

|     | processors from the mid-2000s. On average, the 1.7 GHz Cortex A15 is            |    |

|     | 27% faster than the 2.4 GHz Pentium 4. SPEC CPU 2006 run on Samsung             |    |

|     | Chromebook XE303 and generic Intel Pentium4 desktop. Chromebook runs            |    |

|     | Ubuntu 12.04 with GCC 4.7 while our Pentium runs Fedora 14 with GCC 4.5.        | 14 |

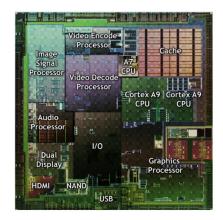

| 2.4 | Nvidia Tegra2 SoC: 49 mm <sup>2</sup> in 45 nm technology. Approximately 20% of |    |

|     | the die dedicated to dual-core ARM Cortex-A9 application processor. Figure      |    |

|     | from AnandTech [9]                                                              | 14 |

| 3.1 | The three types of dependence hazards                                           | 21 |

| 3.2 | Iteration number example: the index variable $i$ assumes iteration values       |    |

|     | 0,1,and 2                                                                       | 22 |

| 3.3 | A loop-nest used as our example for dependence testing. In this example,        |    |

|     | analysis attempts to determine if a dependence occurs between the left-hand     |    |

|     | and right-hand sides of the statement.                                          | 23 |

| 3.4 | Three legal loop orderings of Matrix-Multiply                                   | 25 |

| 3.5 | The abstract grammar rules for Three Fingered Jack's automatically paral-       |    |

|     | lelizable EDSL. In the grammar shown above, <b>object</b> is a built-in Python  |    |

|     | data type. We require all <b>objects</b> to be NumPy single-precision or 32-bit |    |

|     | integer data types. The * operator expands a list into positional arguments.    |    |

|     | We have adapted TFJ grammar rules from the Python 2 AST listing [56]            | 26 |

LIST OF FIGURES vi

| 3.6  | TFJ compiler flow: TFJ compiler flow: We start with computation expressed as a Python loop-nest. After syntactic and semantic checking in Python, |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | we convert the Python AST to an XML representation that is fed to our                                                                             |    |

|      | reordering and optimization engine. The optimization engine then generates                                                                        |    |

|      | machine executable code for high-performance execution. Detailed descrip-                                                                         |    |

|      | tions of the front-end, reordering engine, code generator, and run-time are                                                                       |    |

|      | provided in Sections 3.3.1, 3.1, 3.3.3 and 3.3.5                                                                                                  | 28 |

| 3.7  | Vector-vector addition written in Python for TFJ                                                                                                  | 28 |

| 3.8  | Vector-vector addition in TFJ's XML intermediate representation. TFJ can                                                                          |    |

|      | be quickly ported to a new programming language as the interface between                                                                          |    |

|      | the host language and TFJ is a light-weight XML representation. The XML                                                                           |    |

|      | representation abstracts host language implementation details from the core                                                                       |    |

|      | reordering engine.                                                                                                                                | 30 |

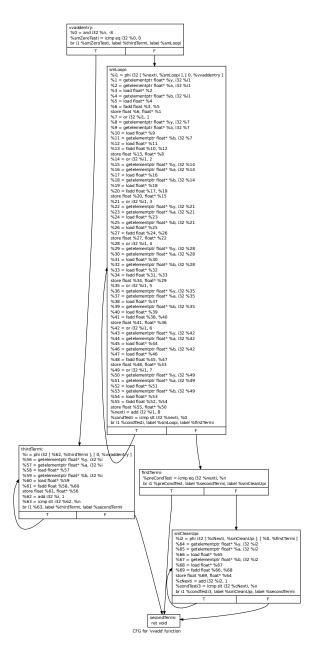

| 3.9  | A high-level sketch of the parallelization algorithm used by TFJ. The core                                                                        |    |

|      | of the algorithm is based on Allen's <b>codegen</b> algorithm; the details of the                                                                 |    |

|      | algorithm are well documented in several publications [6, 5, 4]. We have                                                                          |    |

|      | modified his algorithm to find profitable parallelism on chip-multiprocessors                                                                     |    |

|      | with vector units. In particular, we attempt to reorder loops to achieve                                                                          |    |

|      | unit-stride memory accesses for vectorization and avoid overhead of thread                                                                        |    |

|      | creation and synchronization                                                                                                                      | 31 |

| 3.10 | TFJ code generation for vector-vector addition (Figure 3.7) using LLVM.                                                                           |    |

|      | Lines 3 through 5 compute the upper loop bound of the strip-mined loop and                                                                        |    |

|      | check if the function was called with arrays of less than length 32. Lines 7                                                                      |    |

|      | through 21 perform vectorized addition for vectors of length 32. Lines 26                                                                         |    |

|      | through 37 perform scalar addition when the function is called with an array                                                                      |    |

|      | length of less than 32. Lines 39 through 55 clean-up the strip-mined vector                                                                       |    |

|      | loop by executing any remaining iterations. Note that our vector lengths (32)                                                                     |    |

|      | are longer than the hardware vector lengths of either AVX (8) or SSE/NEON                                                                         |    |

|      | (4). Using longer vectors enables a variant of software prefetching                                                                               | 33 |

| 3.11 | TFJ's C++ intrinsics for machines with four entry vectors, such Intel's SSE                                                                       |    |

|      | or ARM's Neon. We have intrinsics with eight entry vectors to map to Intel's                                                                      |    |

| 0.40 | AVX extension too.                                                                                                                                | 34 |

| 3.12 | Subset of the VTAPI classes and functions used by TFJ to generate code for                                                                        | 0= |

|      | vector-thread machines                                                                                                                            | 35 |

LIST OF FIGURES vii

| 3.13        | TFJ code generation for vector-vector addition (Figure 3.7) using the VTAPI. Line 8 configures the vector register file and line 9 configures the hardware vector length. Line 10 computes the upper loop bound for strip-mining.                                                                                                                                                                                                                                                                                                                                                                                 |          |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|             | Single-precision vector objects for the source and destination operands are declared in lines 13 through 15, while lines 16 and 17 perform the vector loads for the source operands. The lines 19 and 23 describe the output argument                                                                                                                                                                                                                                                                                                                                                                             |          |

|             | and operand type to the <b>VT_VFETCH</b> macro. Lines 21 and 25 provide the same information for the input operands. The <b>VT_VFETCH</b> macro performs the vector computation in line 27. The vector store occurs at line 29. Lines 31 through 36 handle strip-mining clean-up on the scalar CPU. Line 32 issues a memory fence to synchronize the vector unit with the scalar                                                                                                                                                                                                                                  |          |

|             | processor, and lines 34 through 36 execute the clean-up code for the strip-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.0      |

| 3.14        | mined loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36       |

|             | 3.14b to generate Figure 3.14c. Results generated on the EOS14 test chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37       |

| 4.1         | Matrix multiply written in Python for TFJ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40       |

| 4.2         | Back propagation weight adjustment kernel from the Rodinia benchmarks rewritten in Python for TFJ acceleration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 41       |

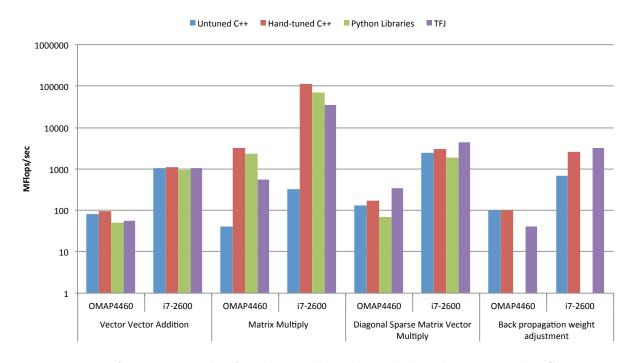

| 4.3         | Performance results for the small benchmark kernels presented in Section 4.2. Fully tabulated performance results for these benchmarks are available                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| 4.4         | in Table 4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 41       |

|             | ize/parallelize matrix multiply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42       |

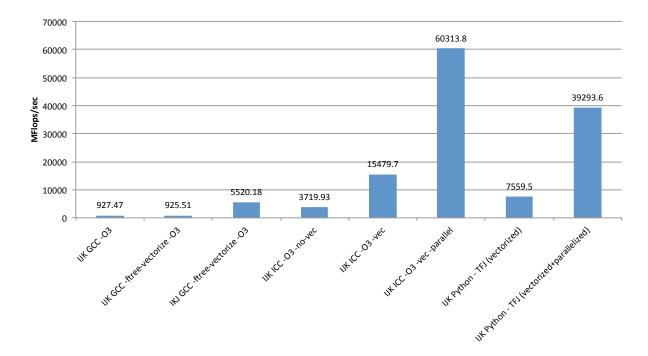

| 4.5         | 2048×2048 matrix multiply performance comparison. Results generated using GCC 4.6.4 or ICC 13.0.1 use the C source presented in Figure 4.4. TFJ results generated using the Python source shown in Figure 4.1. In the plots labels on the bar chart, "IJK" signifies the IJK loop-nest ordering while "IKJ" implies the "IKJ" ordering. The compiler flags used for the C versions of the benchmark are shown on the bar chart. Both C and Python used single-precision matrices and all experiments were run on a 3.4 GHz Intel Core i7-2600. All implementations compiled with GCC also include flags to enable |          |

| 1 C         | reordering of floating point operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43       |

| 4.6         | Matrix multiply written in C with manual loop interchange of the J and K loops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 44       |

| 4.7         | Original image and retargeted image after removal of 750 vertical seams. Original image of the Broadway Tower reproduced from Wikipedia                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 45       |

| 4.8         | A portion of the TFJ accelerated kernels used in content-aware image resizing. Run-times for the kernels used in content-aware image resizing                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45<br>46 |

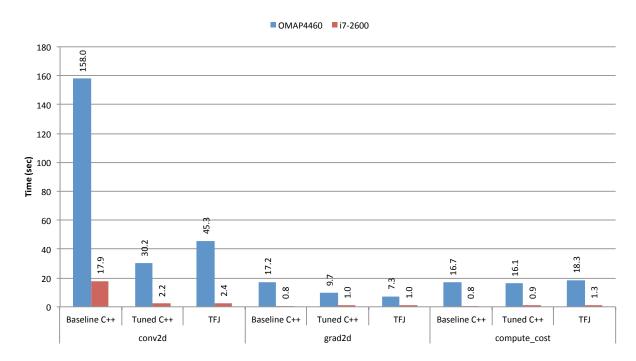

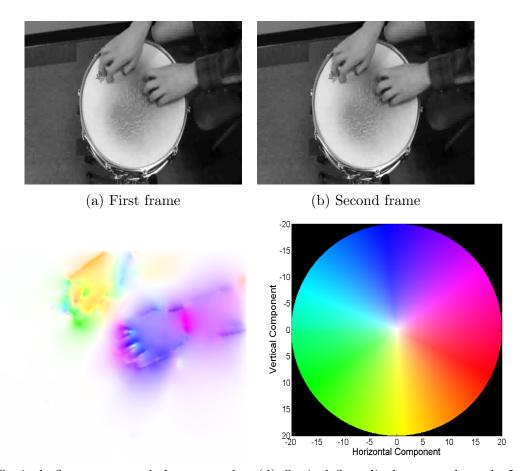

| 4.9<br>4.10 | An example of optical flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40<br>47 |

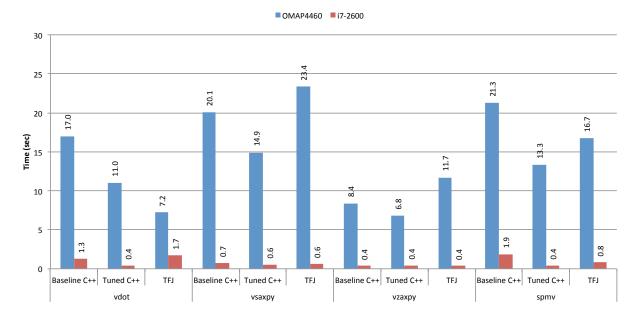

| 4.11        | Run-times for the kernels used in optical flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49       |

| 4.12        | The key kernels used in solving optical flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 51       |

LIST OF FIGURES viii

| 4.13       | A Python function to generate variants of matrix multiply with different loop tiling dimension. Lines 1 through 18 generate tiled implementations of matrix multiply. The parameters <b>iblk</b> , <b>jblk</b> , and <b>kblk</b> of <b>make_mm</b> describe the                                                 |          |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | 1 0                                                                                                                                                                                                                                                                                                             | 53       |

| 4.14       | An autotuner for matrix multiply written in Python using TFJ. Line 1 allocates a list to keep track of the best performing configuration for each problem size. The problem sizes for which we are generating solutions are shown in line 3. Lines 4 through 16 allocate matrices and then evaluate the perfor- |          |

|            | mance of the naive TFJ matrix multiply code for the current problem size.  Lines 19 through 21 define the loop tiling search space, while lines 22 through 27 generate perform code generation using make_mm and write the result-                                                                              |          |

|            | ing module to the filesystem. Line 28 imports the newly generated loop tiled matrix multiply into the Python environment. Lines 30 through 35 evaluate the performance of the generated loop tiled matrix multiply. The generated                                                                               |          |

|            | tiled matrix multiply is called on line 32 using the <b>eval</b> function. Lines 41 through 46 keep track of the best performing configuration, while Lines 47                                                                                                                                                  |          |

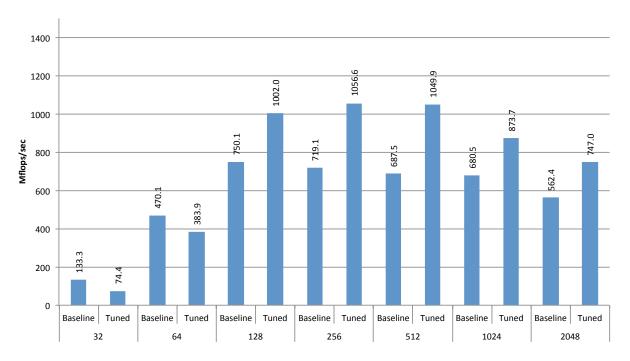

| 4 15       |                                                                                                                                                                                                                                                                                                                 | 54       |

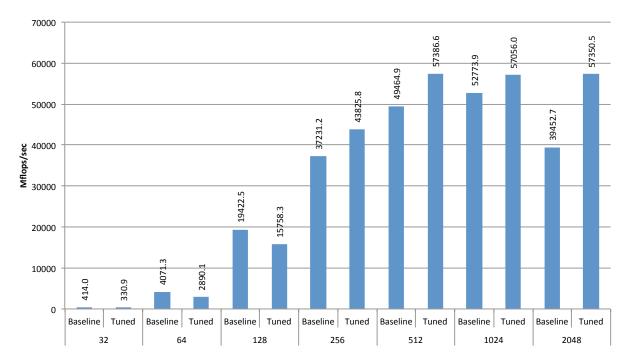

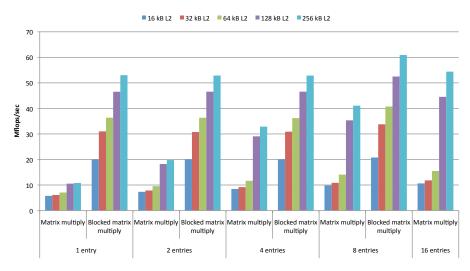

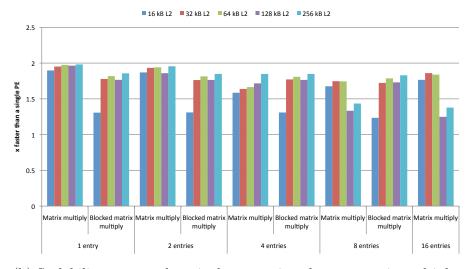

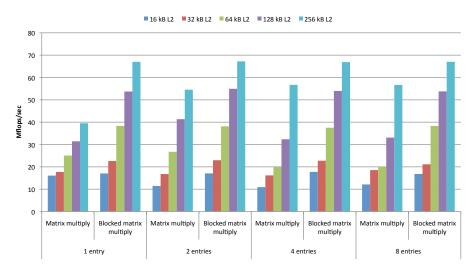

|            | present baseline and tuned results for matrices from size 32 to 2048                                                                                                                                                                                                                                            | 55       |

|            |                                                                                                                                                                                                                                                                                                                 | 55       |

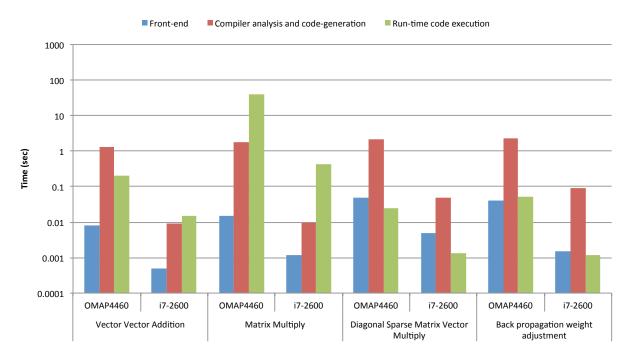

| 4.17       | Run-time breakdown for the numerical kernels described in Section 4.2. Note the logarithmic time scale on the bar chart.                                                                                                                                                                                        | 56       |

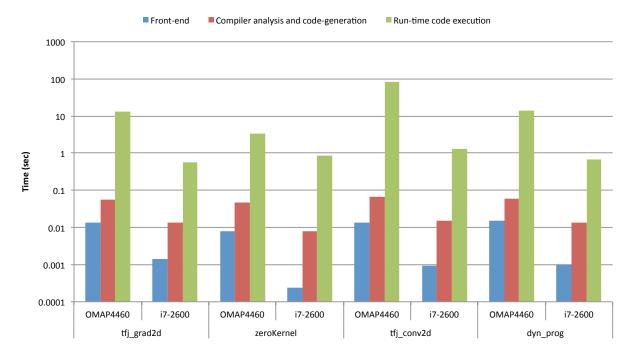

| 4.18       | Run-time breakdown for the TFJ accelerated kernels used in content-aware image resizing                                                                                                                                                                                                                         | 57       |

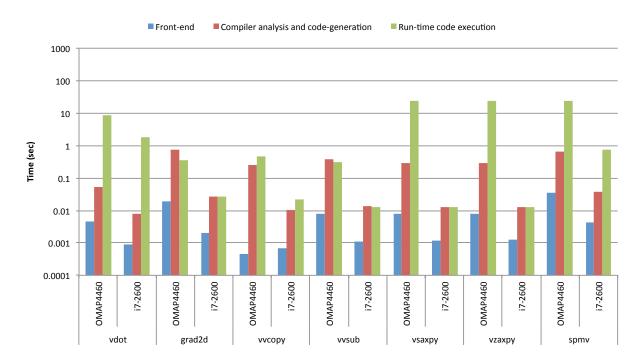

|            | Run-time breakdown for the TFJ accelerated kernels used in optical flow                                                                                                                                                                                                                                         | 58       |

|            | v -                                                                                                                                                                                                                                                                                                             | 58<br>59 |

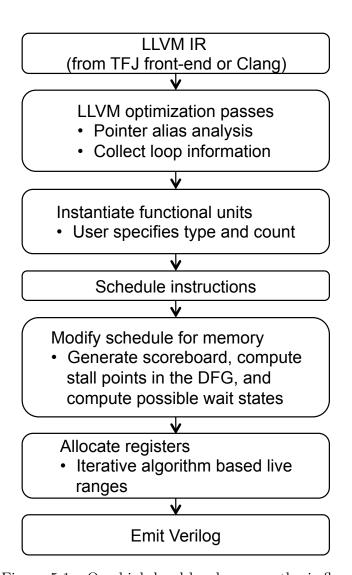

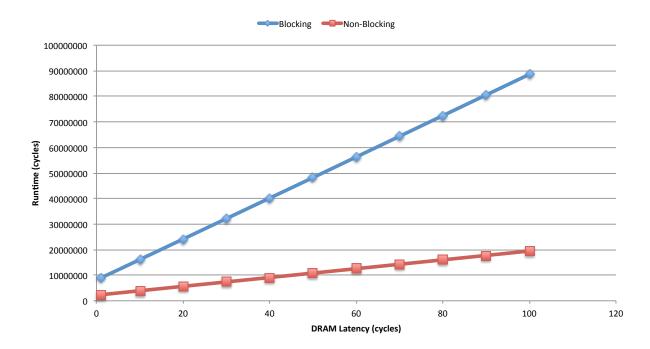

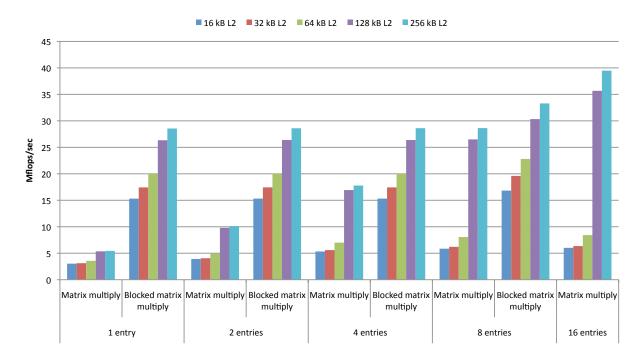

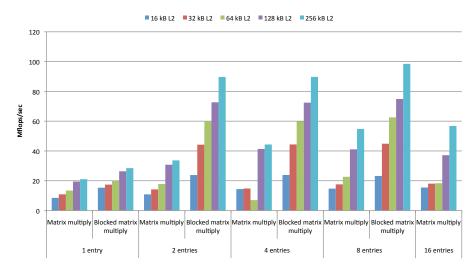

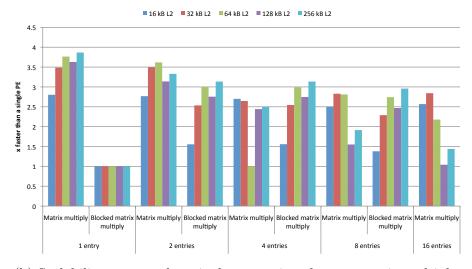

| 5.1<br>5.2 | Our high-level hardware synthesis flow                                                                                                                                                                                                                                                                          | 62       |

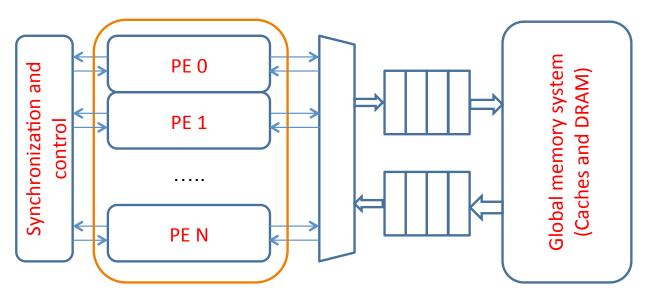

| 5.3        | greater than $4 \times$ better performance than the blocking configuration The initial architecture of our HLS processing cluster. The processing engines                                                                                                                                                       | 63       |

|            | enclosed in orange are automatically generated by our HLS framework                                                                                                                                                                                                                                             | 64       |

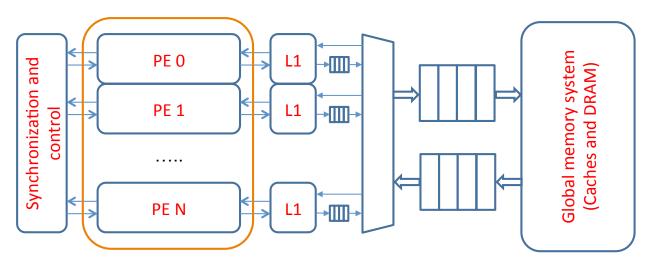

| 5.4        | The final architecture of our HLS processing cluster                                                                                                                                                                                                                                                            | 65       |

LIST OF FIGURES ix

| 5.5        | gines. The 8 processing engines are highlighted in yellow, green, orange, dark blue, burnt orange, red, light blue, and magenta. The memory subsystem is highlighted brown. Figure generated using Xilinx PlanAhead 14.1 with a | 0.0 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.6        | LLVM IR representation of the vector-vector addition kernel without au-                                                                                                                                                         | 66  |

|            | tovectorization. This kernel has 6 basic blocks. The largest basic block has                                                                                                                                                    | 00  |

| 5.7        | LLVM IR representation of the vector-vector addition kernel with autovectorization for a data-parallel operation length of 8. In contrast to Figure 5.6,                                                                        | 68  |

| <b>F</b> 0 |                                                                                                                                                                                                                                 | 69  |

| 5.8<br>5.9 | A high-level sketch of the algorithm used by TFJ to support memory-level parallelism. This algorithm allows for memory-level parallelism when mem-                                                                              | 70  |

|            | ory operations execute in the expected number of cycles. When memory operations take longer than expected, this algorithm adds additional wait                                                                                  |     |

|            | states into the control finite state machine to handle stalling the processing                                                                                                                                                  | 70  |

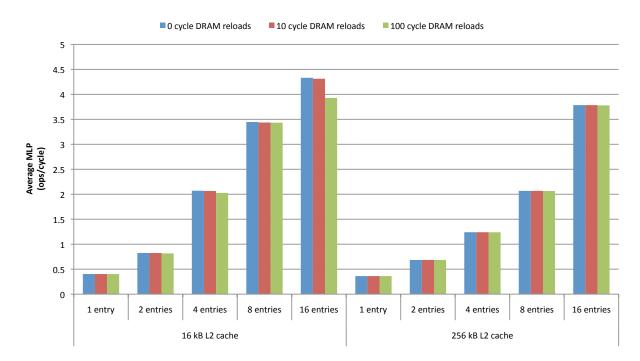

| 5 10       | element                                                                                                                                                                                                                         | 72  |

| 5.10       | 160×160 matrix-multiply memory-level parallelism for a data-parallel operation lengths from 1 entry to 16 entries and three different cache reload laten-                                                                       |     |

|            | cies. All results generated for a single custom processing element with no L1                                                                                                                                                   |     |

|            |                                                                                                                                                                                                                                 | 73  |

| 5.11       | Vector-vector addition used for HW evaluation                                                                                                                                                                                   | 77  |

|            | Color conversion kernel used for HW evaluation                                                                                                                                                                                  | 78  |

| 5.13       | Matrix multiply kernel used for HW evaluation                                                                                                                                                                                   | 78  |

| 5.14       | Gaussian mixture model evaluation kernel used for HW evaluation                                                                                                                                                                 | 78  |

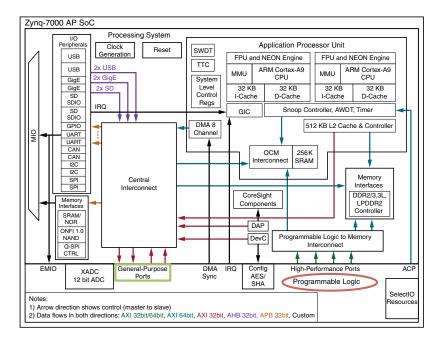

| 5.15       | Block diagram of Xilinx Zynq-7000 [145]. Our automatically generated pro-                                                                                                                                                       |     |

|            | cessing engines are implemented in the programmable logic (marked with a                                                                                                                                                        |     |

|            | red oval). The processing engines interface with the onboard ARM processors                                                                                                                                                     |     |

|            |                                                                                                                                                                                                                                 | 79  |

|            |                                                                                                                                                                                                                                 | 80  |

| 5.17       | C++ source used as glue to interface memory-mapped accelerators in Zynq FPGA fabric with ARM cores. Line 2 polls the accelerator status register.                                                                               |     |

|            | Bit zero of the status register indicates a request. As shown in line 4, the                                                                                                                                                    |     |

|            | second bit of the status register indicates if the transaction is a read or write                                                                                                                                               |     |

|            | while the memory operation address is placed in the upper 24 bits of the status                                                                                                                                                 |     |

|            | register. Lines 5 through 11 perform the actual 16-byte read or write while line                                                                                                                                                |     |

|            | 12 acknowledges a complete memory transaction. Finally, lines 14 through 16                                                                                                                                                     |     |

|            | check if the accelerator has completed executing a given computation. Using                                                                                                                                                     |     |

|            | this code, a 16-byte cache line reload takes approximately 100 cycles on the 100 MHz FPGA clock domain                                                                                                                          | 81  |

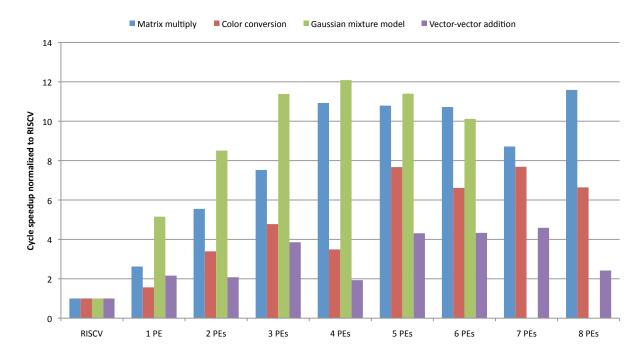

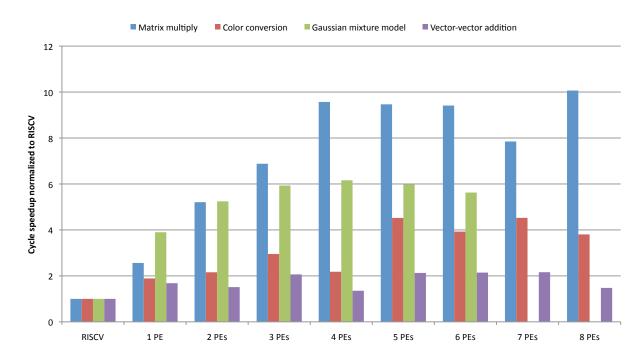

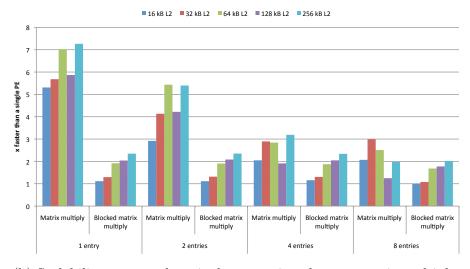

| 5 18       | Scaling with one-cycle reloads (larger speedup connotes better results)                                                                                                                                                         | 83  |

|            | Scaling with one-cycle reloads (larger speedup connotes better results)                                                                                                                                                         | 84  |

|            | $\mathcal{J}$                                                                                                                                                                                                                   | _   |

LIST OF FIGURES x

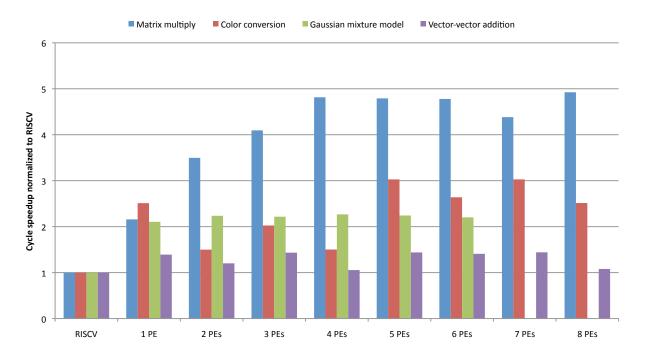

|      | Scaling with 100 cycle reloads (larger speedup connotes better results) Python implementations of the two kernels used for tuning hardware matrix multiply                                                                                                                                                                                                                           | 84<br>87          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 5.22 | Matrix multiply using a single processing element                                                                                                                                                                                                                                                                                                                                    | 89                |

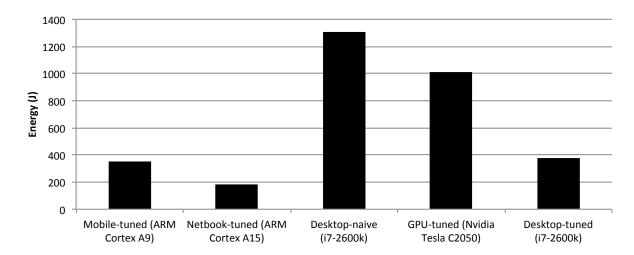

| 6.1  | Energy consumption for 60s of ASR on a menagerie of commercial platforms. All devices achieve real-time performance on Wall Street Journal 5k corpus [115]. Energy recorded using a "watts up? PRO" power meter                                                                                                                                                                      | 95                |

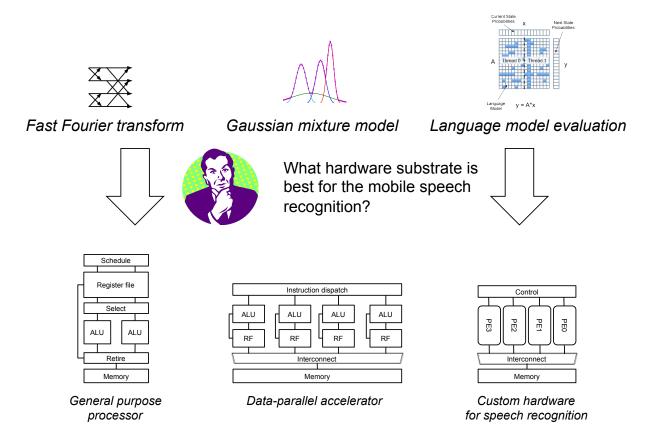

| 6.2  | There are a number of ways of providing speech recognition on mobile devices. Different target markets, performance requirements, client-computing profiles, and energy concerns motivate many different solutions. For these reasons, we need the ability to explore the entire design space of general                                                                             |                   |

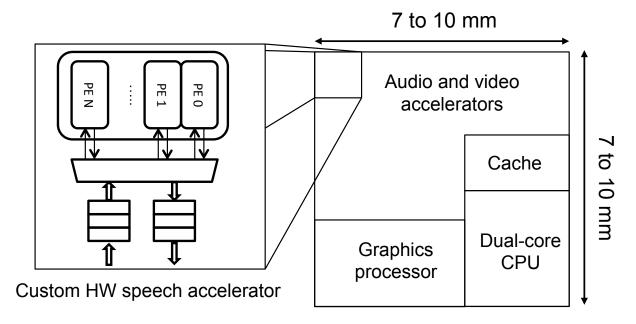

| 6.3  | purpose CPUs, data-parallel accelerators, and custom fixed-function hardware. A system on a chip: a large fraction of the SoC die area is dedicated to custom accelerators such as video encoders/decoders or image processing. The hardware speech recognition solutions presented as a possible solution for mobile ASR in this chapter are intended be a small logic block (under | 96                |

|      | $5mm^2$ ) on a SoC                                                                                                                                                                                                                                                                                                                                                                   | 97                |

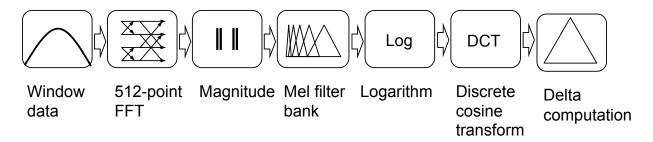

| 6.4  | An architecture for Mel-frequency cepstral coefficient generation                                                                                                                                                                                                                                                                                                                    | 98                |

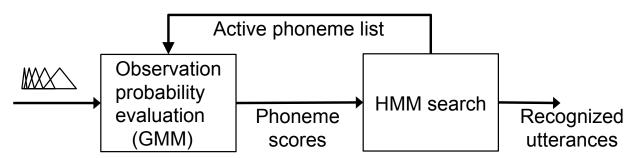

| 6.5  | Architecture of an HMM-based speech recognizer                                                                                                                                                                                                                                                                                                                                       | 98                |

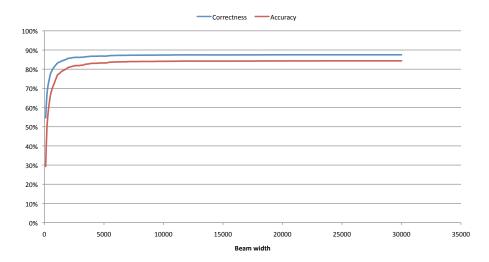

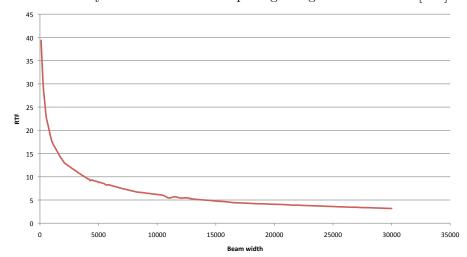

| 6.6  | Speech recognition correctness, accuracy, and real-time factor for a variety of beam widths. Experiments run on 2404 seconds of audio encapsulating 330 utterances from the Wall Street Journal 5000 word corpus. Plots generated by sweeping beam width from 100 to 10000 in steps of 100 and then from                                                                             |                   |

|      |                                                                                                                                                                                                                                                                                                                                                                                      | 100               |

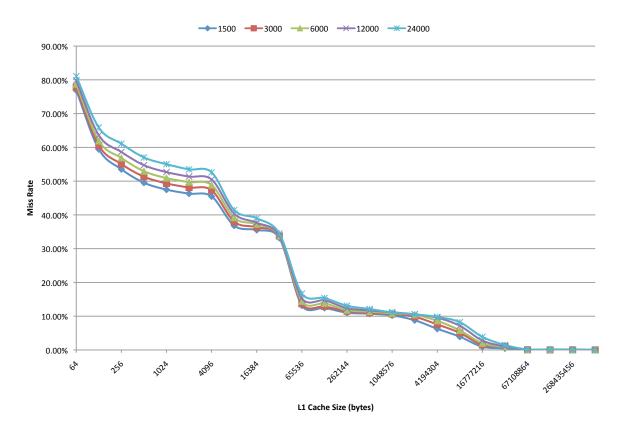

| 6.7  | Measured cache locality in our speech recognizer for a variety of beam width sizes. To measure locality, we simulate a single-level memory hierarchy and then sweep L1 cache sizes from 64 bytes to 512 mBytes. Our experiments use a direct mapped cache with 32 byte cache lines                                                                                                   | 101               |

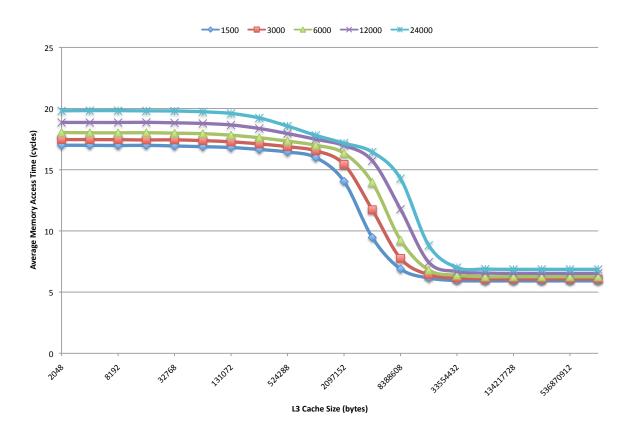

| 6.8  | Average memory access time as function L3 cache size and beam width sizes. We use 16 kByte 4-way set-associative L1 cache with 1 cycle access latency. Our L2 cache is 256 kBytes with 8-way associativity and has a 10 cycle access latency while our L3 cache has 32-way associativity and 30 cycle access latency. All 3 levels of the memory hierarchy have 32 byte cache lines  |                   |

| 6.9  | GMM-based observation probability evaluation kernel in Python for TFJ ac-                                                                                                                                                                                                                                                                                                            |                   |

| 6 10 |                                                                                                                                                                                                                                                                                                                                                                                      | $\frac{103}{104}$ |

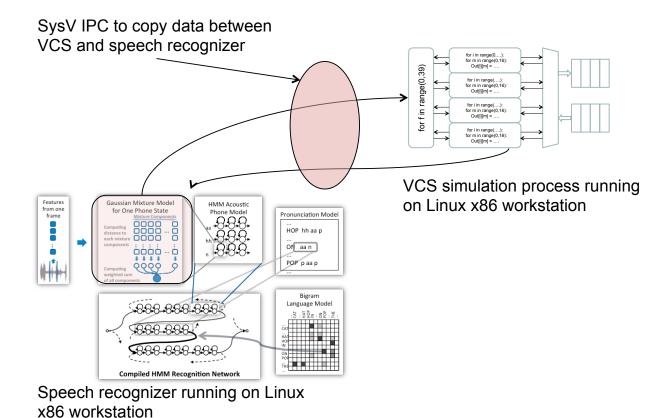

|      | Speech recognition hardware verification scheme using our decoder and Syn-                                                                                                                                                                                                                                                                                                           | τ0 <del>4</del>   |

| 0.11 |                                                                                                                                                                                                                                                                                                                                                                                      | 106               |

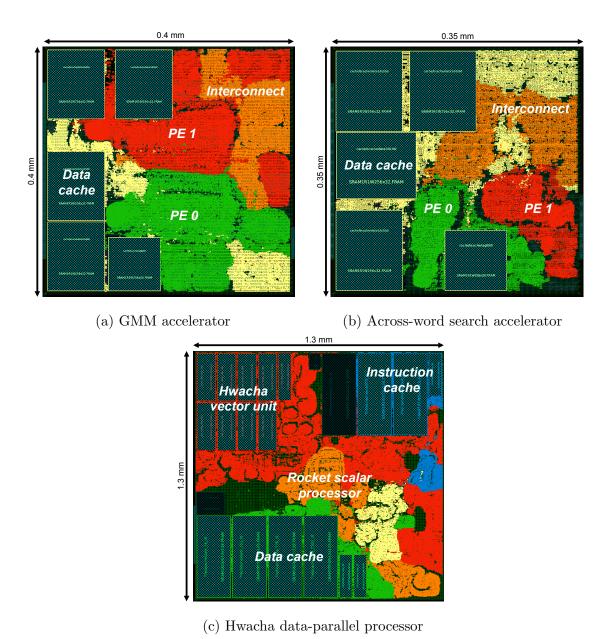

| 6.12 |                                                                                                                                                                                                                                                                                                                                                                                      | 107               |

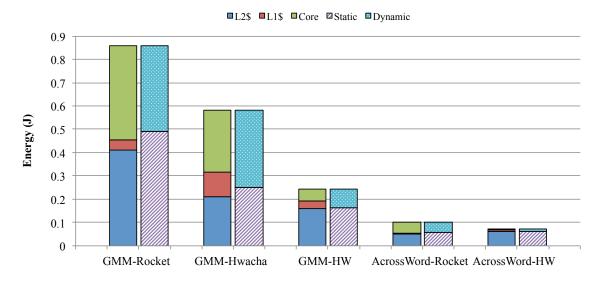

|      | Energy breakdown of GMM and across-word search kernels running on pro-                                                                                                                                                                                                                                                                                                               | -01               |

| 2.23 |                                                                                                                                                                                                                                                                                                                                                                                      | 108               |

## List of Tables

| 4.1<br>4.2<br>4.3<br>4.4 | Image resizing performance results across five different implementations Optical flow performance results across five different implementations Optical flow kernel call counts for the results shown in Table 4.2 Performance results for the 4 kernels and 2 applications. <b>Bold</b> numbers indicate best results. For the 4 kernels, larger Mflops/sec values indicate faster implementations. Application performance is reported in seconds; therefore, shorter runtimes reflect higher peformance. We have marked categories N/A | 46<br>49<br>49 |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                          | if we could not find a Python library that implements a given benchmark. On our ARM platform, several benchmarks did not complete in under 24 hours when executed as Python loop-nests                                                                                                                                                                                                                                                                                                                                                    | 60             |

| 5.1                      | A comparison of the number of 32-bit registers required by the two different                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

|                          | binding algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 74             |

| 5.2                      | FPGA statistics for our floating-point units on the Xilinx Zynq XC702 FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74             |

| 5.3                      | FPGA statistics for our direct-mapped, write-through L1 caches on the Xilinx                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| _ ,                      | Zynq XC702 FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75             |

| 5.4                      | FPGA statistics for our direct-mapped, write-back L2 caches on the Xilinx                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

|                          | Zynq XC702 FPGA. All L2 caches use 16 byte cache lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 76             |

| 5.5                      | FPGA statistics for our soft-core RISCV CPU on the Xilinx Zynq XC702 FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 79             |

| 5.6                      | FPGA statistics for the four benchmarks of Section 5.3.1 on the Xilinx Zynq                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19             |

| 5.0                      | XC702 FPGA. All processing engines were generated using the datapath re-                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

|                          | source configuration file shown in Figure 5.8a. Designs that require more                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

|                          | LUTs than provided by the FPGA are marked in red                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82             |

| 5.7                      | L2 cache reload statistics. Reload counts are identical for all three memory                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>-</b>       |

|                          | latency configurations. Configurations that do not fit in our Zynq device are                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

|                          | marked in red                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 85             |

| 5.8                      | Single-precision non-blocked matrix multiply FPGA resource statistics for                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

|                          | 256 kB L2 with data-parallel operation lengths from 1 to 16. Designs that                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

|                          | do not fit in Zynq device are marked in red                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88             |

| 5.9                      | Single-precision blocked matrix multiply FPGA resource statistics for 256 kB                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

|                          | L2 with data-parallel operation lengths from 1 to 16. Due to FPGA resource                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

|                          | limitations, the eight processing engine design uses 256 word L1 cache. All                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.5            |

|                          | other designs use 1024 word L1 cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 88             |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

LIST OF TABLES

| 6.1 | Speech recognizer performance (results presented in real-time factor) with     |     |

|-----|--------------------------------------------------------------------------------|-----|

|     | caches enabled and disabled on an Intel i7 920. Results generated using 60     |     |

|     | seconds of audio from the Wall Street Journal 5k corpus. All levels of the     |     |

|     | cache hierarchy were disabled by setting the CD flag and clearing the NW       |     |

|     | flag of CR0 and clearing the memory type range registers [75]                  | 103 |

| 6.2 | FPGA statistics for our prototype speech recognition accelerator on the Xilinx |     |

|     | Zynq xc702 FPGA. The speech recognition solution prototyped on the FPGA        |     |

|     | platform has two GMM accelerators and two across-word accelerators. The        |     |

|     | accelerators run at 50 MHz on the Zynq FPGA                                    | 105 |

| 6.3 | Design statistics for the VLSI layouts presented in Figure 6.12                | 108 |

| 6.4 | Energy results for WSJ clip 441c0201 (6.07 seconds) with TFJ generated         |     |

|     | solutions. The "rest of system" category includes all kernels not accelerated  |     |

|     | with TFJ                                                                       | 109 |

| 6.5 | Expected hours of ASR with hardware/software solutions assuming a 20 kJ        |     |

|     | battery                                                                        | 109 |

## Chapter 1

### Introduction

VLSI scaling enabled massively increased integration capabilities on single chip microprocessors for nearly 30 years. As first observed by Moore [106], the number of transistors on a monolithic silicon die doubles approximately every 18 months. For the first 20 years following Moore's observation, increased integration capabilities were used to improve singlethreaded performance on both desktop and workstation computers. During this period, the supply voltage and channel length of transistors used in CMOS VLSI chips scaled according to Denard's classic predictions [48]. In the classic (long-channel devices) CMOS scaling regime, each new process technology node reduced the minimum lithography dimensions by approximately 30% and also allowed for supply voltage scaling. Not only did each new technology node allow for more integration, but new chips consumed the same amount of power as did the previous generation due to supply voltage scaling. In this period, transistor budgets were dedicated to larger cache memories and other micro-architectural features designed to increase performance. Increased single-threaded performance enabled existing software to scale its performance with enhancements in VLSI technology. Stated simply, no changes in programming methodology were required to extract performance from new microprocessors. As an example of the significant performance improvements delivered during this era, consider two instruction-set compatible processors from Intel: the 486 and the Pentium4.

Released in 1989, the Intel 486 ran at 20 MHz and retired a maximum of one instruction per cycle. In contrast, when released in 2000, the Pentium4 ran at 1.5 GHz and retired up to three instructions per cycle [68]. In slightly more than a decade, clock frequencies increased 75× and instruction issue width increased by another factor of 3×. While clock scaling and instruction issue are correlated only with measured single-threaded performance, Intel was able to potentially unlock a 225× increase in performance during this period. Unfortunately, changes in semiconductor physics associated with deep-submicron processes have limited the applicability of aggressive clock scaling in the period after the early 2000s. In contrast to the era of classical CMOS scaling, supply voltage scaling was no longer possible due to the exponential dependence of leakage current on threshold voltage. Furthermore, the delay relationship between wires and logic changed [69, 132]. Wires had historically been fast while logic was slow. This enabled global signals to span an entire chip in a

single clock cycle. In the deep-submicron area, logic became proportionally faster than wires. This prevented global single-cycle on chip communication. The clock rates of Intel's flagship desktop microprocessors reflect the issues associated with deep-submicron processes. Specifically, the clock rate of Intel's flagship processors have been stagnated since 2004 at approximately 3.8 GHz.

While power and wiring issues have complicated computer design in the deep submicron era, CMOS scaling still provides ever increasing transistor budgets every 18 months. To increase performance without increasing clock frequencies, major microprocessor companies have turned to parallel processors by adding multiple processors cores to a monolithic silicon die. By harnessing multiple processors, software can be integer factors faster than the single-threaded equivalent; however, a move to parallel processing implies a radical shift in software engineering methodology. To effectively use parallel processors, legacy software must be rewritten to take advantage of additional processors.

While multicore processors with short-vector extensions have the potential for significant performance improvements in many common applications, writing parallel software has historically been a challenge. It has been plagued with both fundamental and engineering challenges. Traditional efficient algorithms often display little parallelism and require new approaches to find algorithms that can effectively exploit parallel resources. Compounding the parallel programming implementation challenge is the diverse nature of parallel programming models. These models are diverse and often reflect underlying differences in parallel hardware platforms. For example, a cluster of workstations often requires a message-passing programming model to obtain high-performance. This is because processors communicate by sending messages over a network. In contrast, the shared-memory programming model assumes processors communicate directly through a global shared pool of memory. These differences in hardware and programming models make portable parallel programming challenging. Furthermore, exploiting data-parallelism with short-vector units often requires reimplementing data-structures in order to satisfy strict memory alignment rules. When compounded with other issues associated with parallel computing such as scalability, load imbalance, and concurrency bugs, parallel computing has struggled to succeed outside the academic research and high-performance computing communities.

Even with the challenges of parallel programming, we must embrace it because multicore processors now span the gamut from high-end servers to smartphones and tablets. Writing parallel software is the only way to unlock high-performance on these devices. However, even with the performance benefits of multicore processors for some applications, software alone may be unable to deliver a high-performance solution that is both high-performance and energy-efficient. In these situations, algorithms must be moved from the software-domain into a more specialized task-specific accelerator in order to achieve the desired goals.

#### 1.1 The Diversity of Potential Platforms

As shown in Figure 1.1, the design space for specialized task-specific accelerators is large. At one extreme is the conventional microprocessor, easy to program but relatively low-performance and energy inefficient. At the other extreme is custom, fixed-function hardware

#### Flexibility and ease of use