# UC San Diego UC San Diego Electronic Theses and Dissertations

#### Title

Fast, Efficient, and Robust Learning with Brain-Inspired Hyperdimensional Computing

#### Permalink

https://escholarship.org/uc/item/4x35f8q8

#### **Author** Morris, Justin

# Publication Date 2022

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO SAN DIEGO STATE UNIVERSITY

Fast, Efficient, and Robust Learning with Brain-Inspired Hyperdimensional Computing

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

#### Engineering Science (Electrical & Computer Engineering)

by

Justin Morris

Committee in charge:

University of California San Diego Professor Tajana Šimunić Rosing, Co-Chair Professor Ryan Kastner Professor Farinaz Koushanfar

San Diego State University Professor Baris Aksanli, Co-Chair Professor Shangping Ren

Copyright

Justin Morris, 2022

All rights reserved.

The dissertation of Justin Morris is approved, and it is acceptable in quality and form for publication on microfilm and electronically.

University of California San Diego

San Diego State University

2022

### DEDICATION

# To my wife, Stephanie, and our family

For their endless support and encouragement to go on and complete this journey

| Disserta                     | tion Approval Page                                                                                                                                                                                                                   | iii                                                                |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Dedicati                     | on                                                                                                                                                                                                                                   | iv                                                                 |

| Table of                     | Contents                                                                                                                                                                                                                             | v                                                                  |

| List of F                    | igures                                                                                                                                                                                                                               | ix                                                                 |

| List of T                    | Cables                                                                                                                                                                                                                               | xii                                                                |

| Acknow                       | ledgements                                                                                                                                                                                                                           | xiii                                                               |

| Vita                         |                                                                                                                                                                                                                                      | XV                                                                 |

| Abstract                     | of the Dissertation                                                                                                                                                                                                                  | xviii                                                              |

| Chapter<br>1.1               | <ol> <li>Introduction</li></ol>                                                                                                                                                                                                      | 1<br>2<br>4<br>4<br>5<br>6<br>6<br>6<br>7<br>7<br>8<br>8<br>8<br>9 |

| Chapter<br>2.1<br>2.2<br>2.3 | <ul> <li>2 Adaptive Model Quantization for Hyperdimensional Computing</li> <li>Introduction</li> <li>Related Work</li> <li>AdaptBit-HD</li> <li>2.3.1 Training with AdaptBit-HD</li> <li>2.3.2 Inference with AdaptBit-HD</li> </ul> | 10<br>10<br>11<br>12<br>13<br>16                                   |

| 2.4                          | FPGA Acceleration         2.4.1       Encoding Implementation         2.4.2       Training Implementation                                                                                                                            | 19<br>19<br>20                                                     |

#### TABLE OF CONTENTS

|         | 2.4.3 Inference Implementation                                                                                  | 22 |

|---------|-----------------------------------------------------------------------------------------------------------------|----|

| 2.5     | Evaluation                                                                                                      | 23 |

|         |                                                                                                                 | 23 |

|         | 2.5.2 Energy Efficiency, Execution Time, and Accuracy of AdaptBit-HD vs                                         |    |

|         |                                                                                                                 | 23 |

|         |                                                                                                                 | 25 |

| 2.6     | 1 1                                                                                                             | 27 |

| 2.7     |                                                                                                                 | 28 |

| 2.7     | Texnow longements                                                                                               | 20 |

| Chapter | 3 A Rework of the Hyperdimensional Computing Pipeline and Acceleration on                                       |    |

|         |                                                                                                                 | 29 |

| 3.1     | Introduction                                                                                                    | 29 |

| 3.2     | Related Work & Motivation                                                                                       | 30 |

| 3.3     | Encoding with ReHD                                                                                              | 32 |

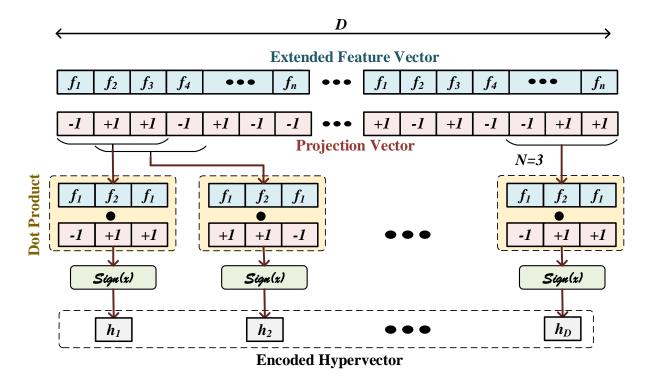

|         | 3.3.1 Random Projection                                                                                         | 33 |

|         | 3.3.2 Sparse Random Encoding                                                                                    | 34 |

|         | 3.3.3 Locality-based Sparse Random Projection                                                                   | 34 |

| 3.4     |                                                                                                                 | 37 |

|         | 3.4.1 Binary Model Quantization                                                                                 | 38 |

|         |                                                                                                                 | 38 |

|         | 3.4.3 Model Quantization Inference                                                                              | 39 |

| 3.5     |                                                                                                                 | 40 |

| 3.6     | FPGA Acceleration                                                                                               | 41 |

|         |                                                                                                                 | 42 |

|         |                                                                                                                 | 44 |

|         |                                                                                                                 | 44 |

| 3.7     | -                                                                                                               | 45 |

|         |                                                                                                                 | 45 |

|         | 1 1                                                                                                             | 46 |

|         |                                                                                                                 | 47 |

|         | 5 5 1                                                                                                           | 48 |

|         | 5                                                                                                               | 50 |

|         |                                                                                                                 | 52 |

| 3.8     |                                                                                                                 | 54 |

| 3.9     |                                                                                                                 | 55 |

| 017     | i ienne wiedgemeints i ienne in ienne i | 00 |

| Chapter | 4 Extending Hyperdimensional Computing Applications to Support Multi-                                           |    |

| 1       |                                                                                                                 | 56 |

| 4.1     | Introduction                                                                                                    | 56 |

| 4.2     |                                                                                                                 | 57 |

|         |                                                                                                                 | 57 |

|         |                                                                                                                 | 58 |

|         |                                                                                                                 | 58 |

| 4.3     |                                                                                                                 | 59 |

|         | 4.3.1   | Problem Transformation Methods                                       | 59  |

|---------|---------|----------------------------------------------------------------------|-----|

|         | 4.3.2   | Training                                                             | 60  |

|         | 4.3.3   | Inference                                                            | 62  |

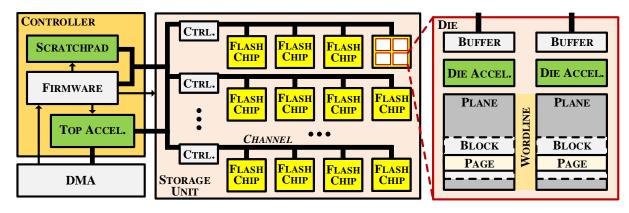

| 4.4     | Accele  | ration with 3D NAND Flash                                            | 63  |

|         | 4.4.1   | Encoding in 3D Flash                                                 | 63  |

|         | 4.4.2   | Training at Top-Level in Storage                                     | 64  |

| 4.5     | Experi  | mental Results                                                       | 65  |

|         | 4.5.1   | Experiment Setup                                                     | 65  |

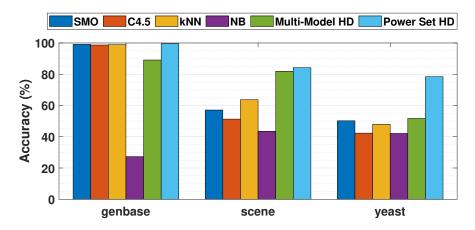

|         | 4.5.2   | Multi-label HD Comparison with State-of-the-Art                      | 66  |

|         | 4.5.3   | Multi-label HD in 3D Flash                                           | 69  |

| 4.6     | Conclu  | sion                                                                 | 70  |

| 4.7     | Acknow  | wledgements                                                          | 70  |

| Chapter | 5 Eva   | aluating and Exploiting Robustness to Create a More Efficient Analog |     |

|         | Pro     | cessing-in-Memory Accelerator for Hyperdimensional Computing Classi- |     |

|         | fica    | tion and Clustering                                                  | 71  |

| 5.1     | Introdu | uction                                                               | 71  |

|         | 5.1.1   | Related Work                                                         | 73  |

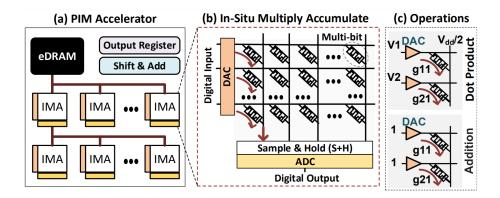

| 5.2     | HyDRE   | EA Analog PIM Architecture                                           | 75  |

|         | 5.2.1   | Architecture                                                         | 77  |

|         | 5.2.2   | Challenges                                                           | 79  |

|         | 5.2.3   | HyDREA: Analog PIM Architecture Optimiztions                         | 79  |

|         | 5.2.4   | HyDREA: Supporting HD Clustering                                     | 83  |

| 5.3     | Networ  | rk Simulation                                                        | 84  |

| 5.4     | Evalua  | tion                                                                 | 88  |

|         | 5.4.1   | Experimental Setup                                                   | 88  |

|         | 5.4.2   | HyDREA and Dimensionality                                            | 90  |

|         | 5.4.3   | HyDREA and the Impact of our Analog PIM Architecture on HD Classi-   |     |

|         |         | fication                                                             | 91  |

|         | 5.4.4   | HyDREA vs Processing in Storage and Digital Processing in Memory     | 93  |

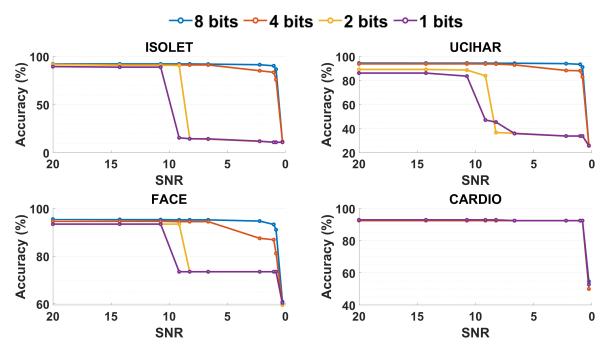

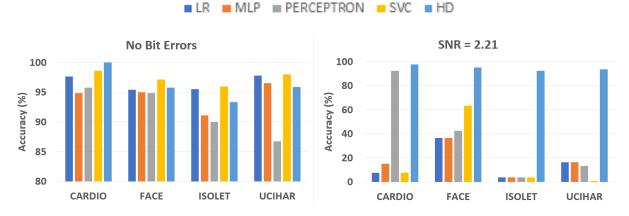

|         | 5.4.5   | HyDREA and the Impact of SNR on HD Classification                    | 93  |

|         | 5.4.6   | HD vs. Other Classifiers                                             | 95  |

|         | 5.4.7   | HyDREA vs State-of-the-Art PIM DNN Accelerator                       | 95  |

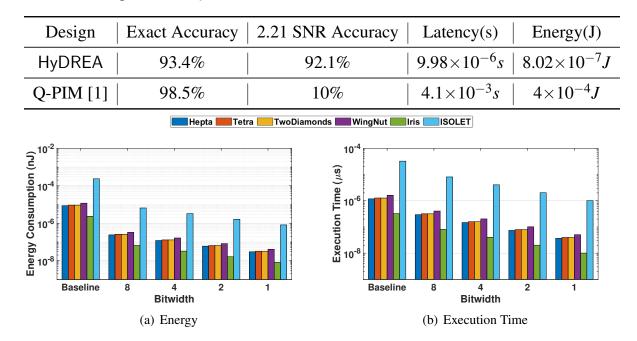

|         | 5.4.8   | HyDREA Architecture Impact on Clustering Energy Consumption and      |     |

|         |         | Execution Time                                                       | 97  |

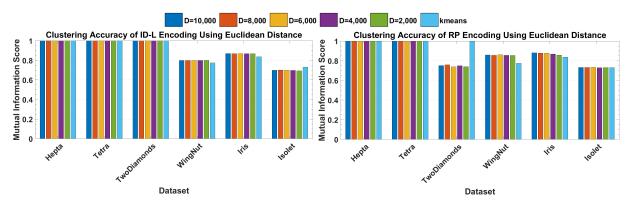

|         | 5.4.9   | HD Clustering Accuracy and Robustness vs K-means                     | 97  |

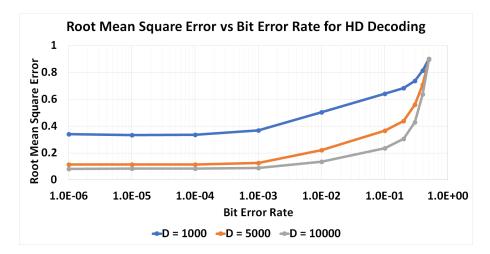

|         | 5.4.10  | Impact of Bit Error Rates on Decoding                                | 99  |

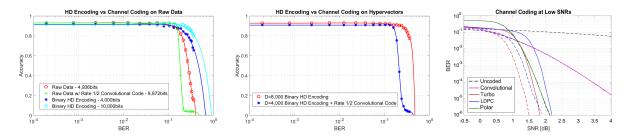

|         |         | HD Computing vs Error Correcting Codes (ECC)                         | 100 |

| 5.5     |         | ision                                                                | 102 |

| 5.6     |         | wledgements                                                          | 103 |

|         |         |                                                                      |     |

| Chapter |         | nmary and Future Work                                                | 104 |

| 6.1     |         | Summary                                                              | 104 |

|         | 6.1.1   | Adaptive Model Quantization for Hyperdimensional Computing           | 105 |

|          | 6.1.2  | A Rework of the Hyperdimensional Computing Pipeline and Accelera-      |     |

|----------|--------|------------------------------------------------------------------------|-----|

|          |        | tion on FPGA                                                           | 106 |

|          | 6.1.3  | Extending Hyperdimensional Computing Applications to Support Multi-    |     |

|          |        | Label Classification                                                   | 106 |

|          | 6.1.4  | Evaluating and Exploiting Robustness to Create a More Efficient Analog |     |

|          |        | Processing-in-Memory Accelerator for Hyperdimensional Computing        | 107 |

| 6.2      | Future | Work                                                                   | 107 |

|          | 6.2.1  | Feature Extraction and HDC                                             | 108 |

|          | 6.2.2  | Exploiting and Evaluating HDC Robustness                               | 108 |

|          |        |                                                                        |     |

| Bibliogr | aphy   |                                                                        | 110 |

#### LIST OF FIGURES

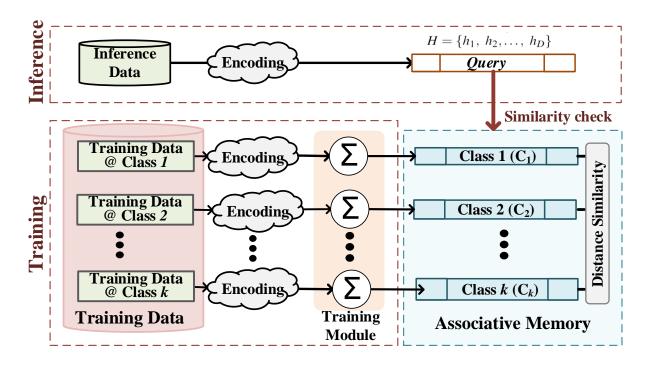

| Figure 1.1. | Overview of creating an HD model and performing inference with an HD model                                                                                                                                                                                                                                                     | 3  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

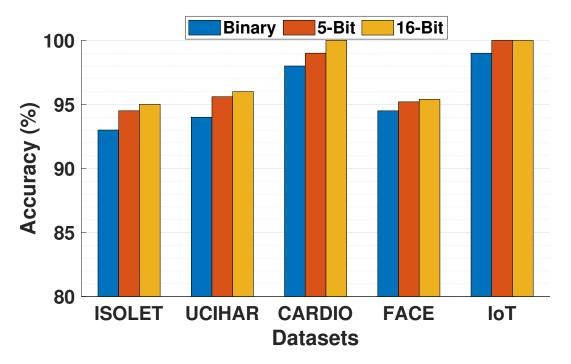

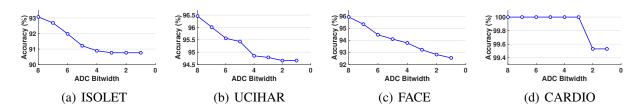

| Figure 2.1. | Difference in Accuracy with Various HD Bitwidth Representations for HD Computing                                                                                                                                                                                                                                               | 14 |

| Figure 2.2. | Overview of Creating a AdaptBit-HD Model During Retraining                                                                                                                                                                                                                                                                     | 14 |

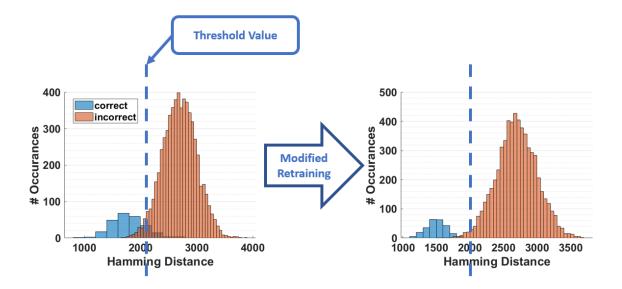

| Figure 2.3. | Distributions of Hamming Distance Calculations Before (left) and After (right) Retraining                                                                                                                                                                                                                                      | 16 |

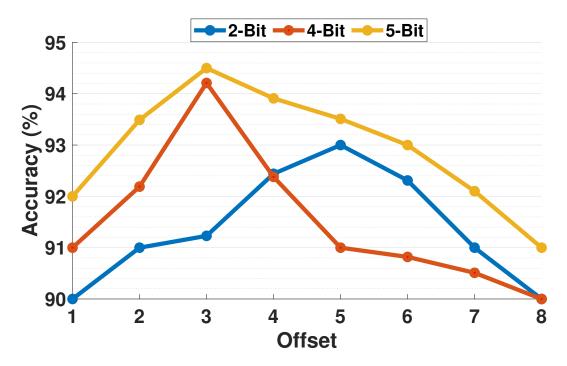

| Figure 2.4. | Effect of AdaptBit-HD Parameters on Accuracy                                                                                                                                                                                                                                                                                   | 17 |

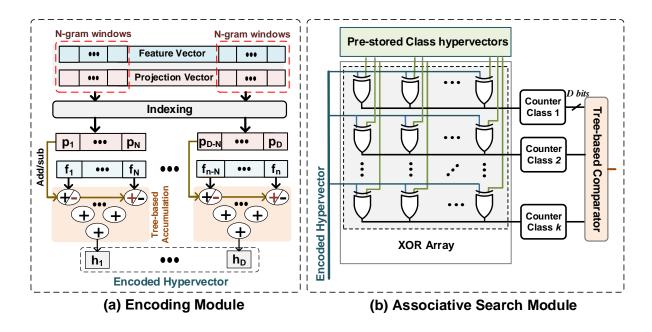

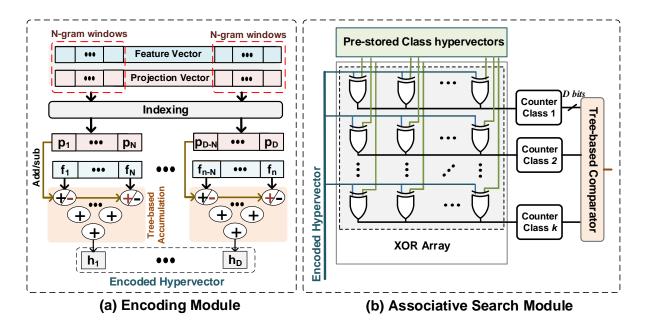

| Figure 2.5. | FPGA implementation of the encoding and associative search block                                                                                                                                                                                                                                                               | 20 |

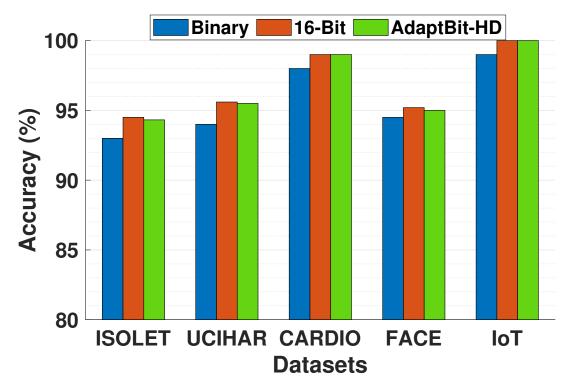

| Figure 2.6. | Comparison of the Accuracy of AdaptBit-HD to Static Model Quantization<br>Methods                                                                                                                                                                                                                                              | 24 |

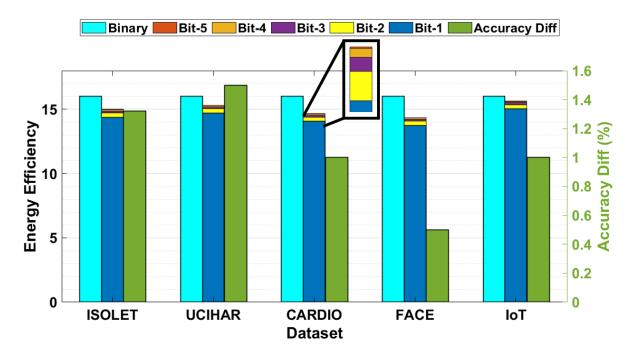

| Figure 2.7. | Energy Breakdown of AdaptBit-HD and Comparison with Static Quanti-<br>zation Methods. Energy Efficiency is Shown Relative to a 16-Bit Model.<br>Accuracy Difference is Compared to a Binary Model. The color cod-<br>ing of the different bits for AdaptBit-HD show the proportion of energy<br>consumption spent on each bit. | 26 |

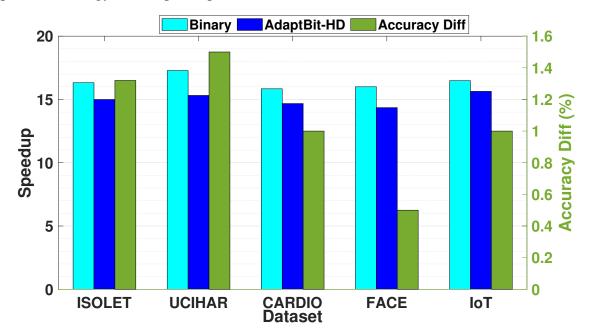

| Figure 2.8. | Speedup of AdaptBit-HD and Comparison with Static Quantization Meth-<br>ods. Speedup is Shown Relative to a 16-Bit Model. Accuracy Difference<br>is Compared to a Binary Model.                                                                                                                                                | 26 |

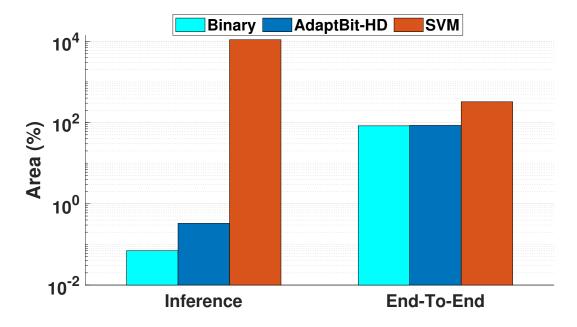

| Figure 2.9. | Area Comparison of AdaptBit-HD, Static Quantization Methods for HD, and SVMs. Area Used is Shown Relative to a 16-bit Static HD Model                                                                                                                                                                                          | 28 |

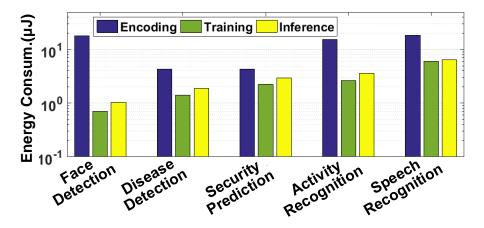

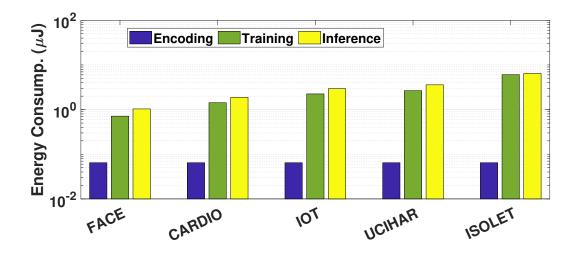

| Figure 3.1. | Energy consumption of HD encoding, training, and inference.                                                                                                                                                                                                                                                                    | 31 |

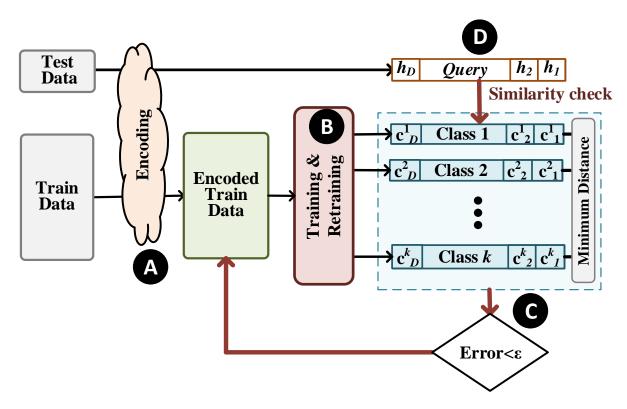

| Figure 3.2. | Overview of how ReHD is constructed and how ReHD performs inference.                                                                                                                                                                                                                                                           | 32 |

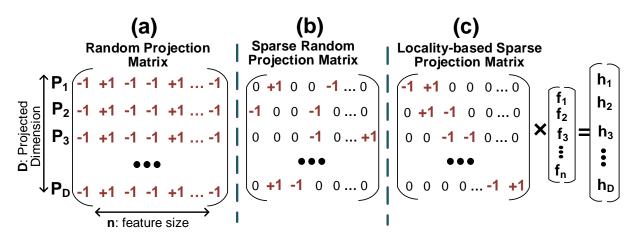

| Figure 3.3. | Random projection encoding using dense, sparse, and locality-based pro-<br>jection matrix.                                                                                                                                                                                                                                     | 36 |

| Figure 3.4. | Locality-based random projection encoding.                                                                                                                                                                                                                                                                                     | 36 |

| Figure 3.5. | Energy consumption of HD encoding, training, and inference after utilizing the proposed encoding module.                                                                                                                                                                                                                       | 37 |

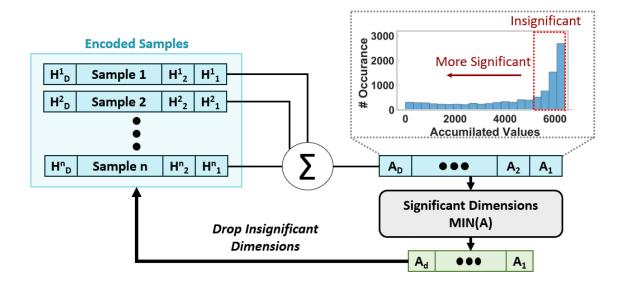

| Figure 3.6. | Online dimension reduction with absolute value                                                                                                                                                                                                                                                                                 | 42 |

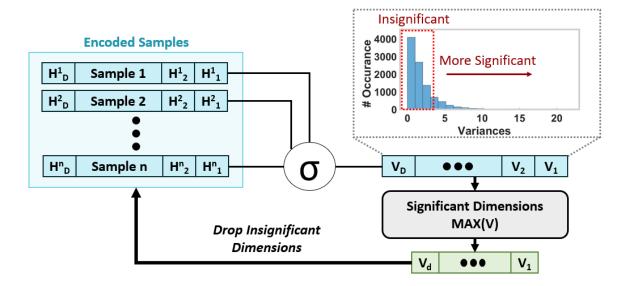

| Figure 3.7.  | Online dimension reduction with variance                                                                                                          | 43 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.8.  | FPGA implementation of the encoding and associative search block                                                                                  | 43 |

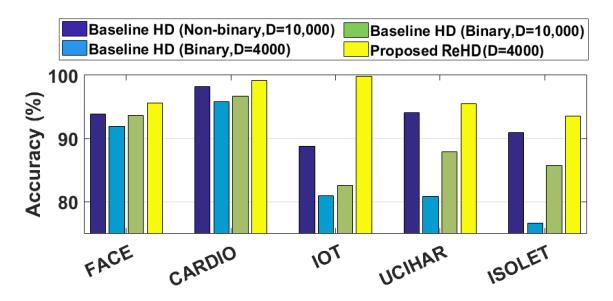

| Figure 3.9.  | Classification accuracy of ReHD and the baseline HD using binary and integer models.                                                              | 46 |

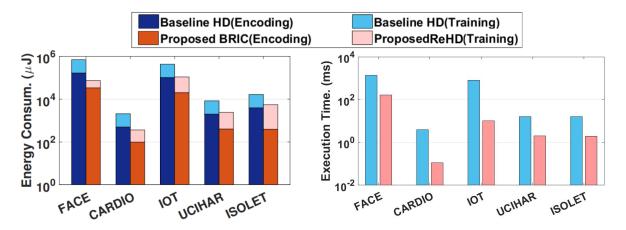

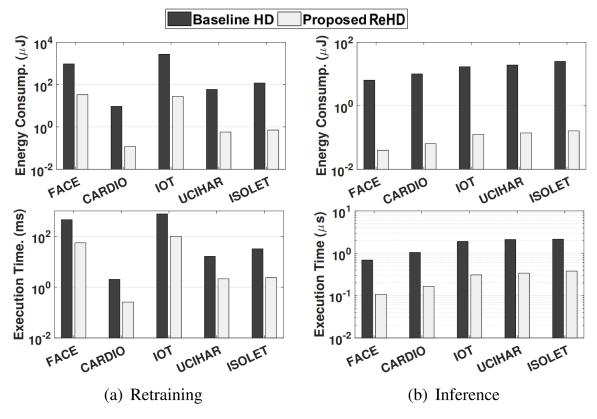

| Figure 3.10. | Energy consumption and execution time of ReHD and the baseline HD during training                                                                 | 46 |

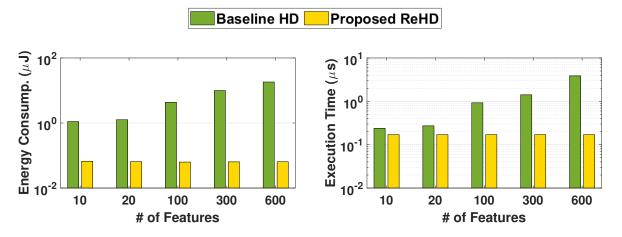

| Figure 3.11. | Scalability of the encoding module in ReHD and the baseline HD with the feature size.                                                             | 48 |

| Figure 3.12. | Energy consumption and execution time of ReHD and the baseline HD running (a) a single retraining iteration, and (b) a single query at inference. | 50 |

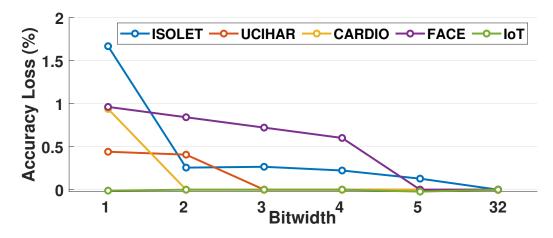

| Figure 3.13. | Accuracy loss of ReHD utilizing n-bit model quantization.                                                                                         | 51 |

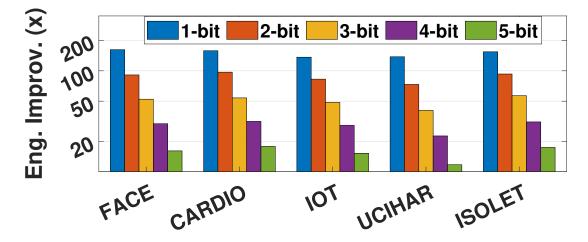

| Figure 3.14. | Energy improvement of ReHD utilizing n-bit model quantization normal-<br>ized to a 32-bit integer model.                                          | 51 |

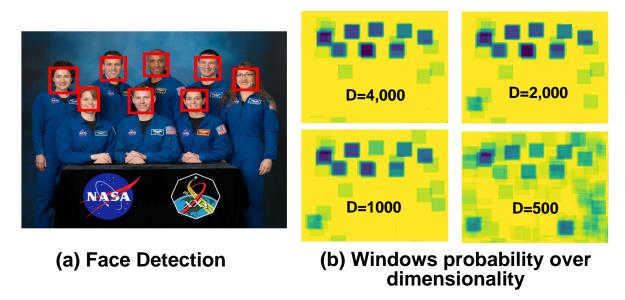

| Figure 3.15. | Visualization of ReHD face detection accuracy over different dimensionality.                                                                      | 54 |

| Figure 4.1.  | An example of how the Multi-Model HD model is created                                                                                             | 61 |

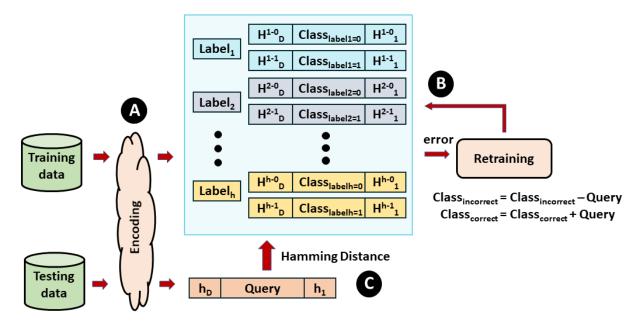

| Figure 4.2.  | Overview of how Multi-Model HD is constructed and how Multi-Model<br>HD performs inference                                                        | 62 |

| Figure 4.3.  | Overview of Multi-label HD in 3D flash-based storage. ISC enabling components of the design are shown in green.                                   | 63 |

| Figure 4.4.  | Classification accuracy of Multilabel HD and other multi-label classifica-<br>tion algorithms.                                                    | 67 |

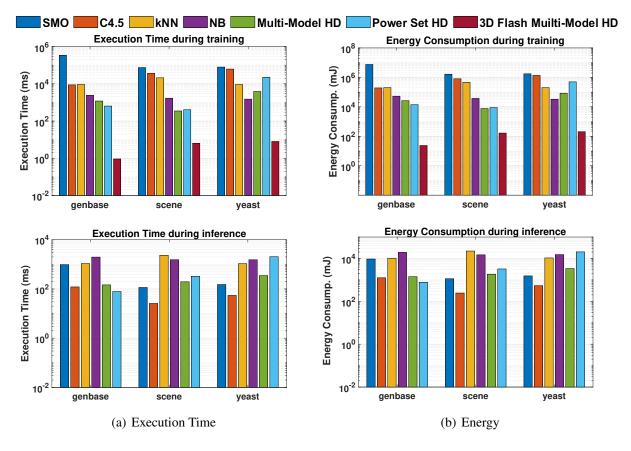

| Figure 4.5.  | Energy consumption and execution time of Multi-label HD during Encod-<br>ing and Training.                                                        | 67 |

| Figure 5.1.  | Overview of the PIM architecture used by HyDREA.                                                                                                  | 75 |

| Figure 5.2.  | Example of Inference in HyDREA.                                                                                                                   | 78 |

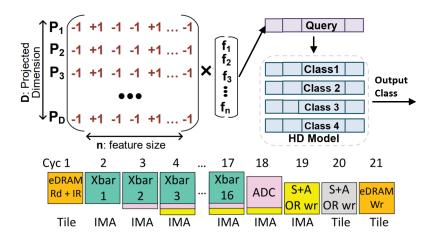

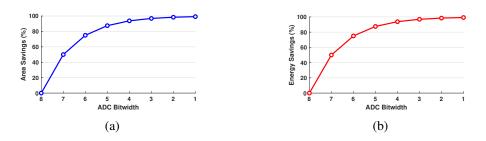

| Figure 5.3.  | Area savings (a) and energy consumption savings (b) as the bitwidth of the ADC is dropped.                                                        | 80 |

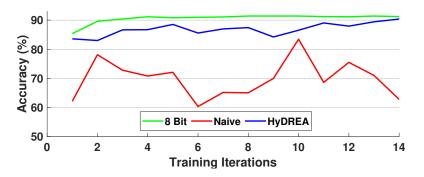

| Figure 5.4.  | Impact of HyDREA using a 4 bit model on training compared to training a naive bitwidth reduction 4 bit model and training a 8 bit model           | 81 |

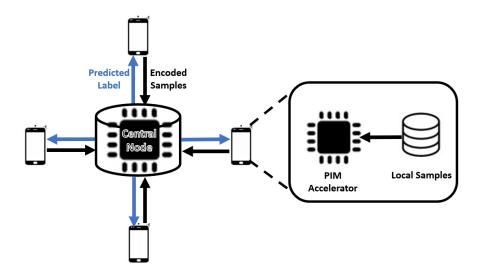

| Figure 5.5.  | An Overview of our framework for communicating in the federated learning enviroment.                                                                                                                                                                     | 85  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

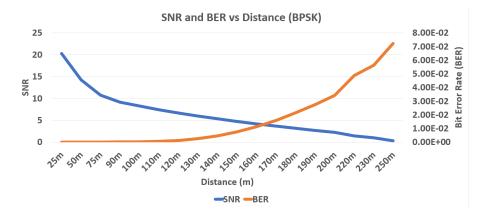

| Figure 5.6.  | SNR/BER vs distance for BPSK modulation with Friis prop. loss                                                                                                                                                                                            | 86  |

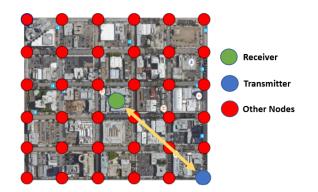

| Figure 5.7.  | Model of a Downtown Topology Represented in NS-3, Where Buildings<br>buildings have higher signal attenuation compared to open-air and they<br>block the line-of-sight when they are placed between the transmitters (blue)<br>and the receiver (green). | 87  |

| Figure 5.8.  | Impact of bitwidth reduction on accuracy of HyDREA                                                                                                                                                                                                       | 90  |

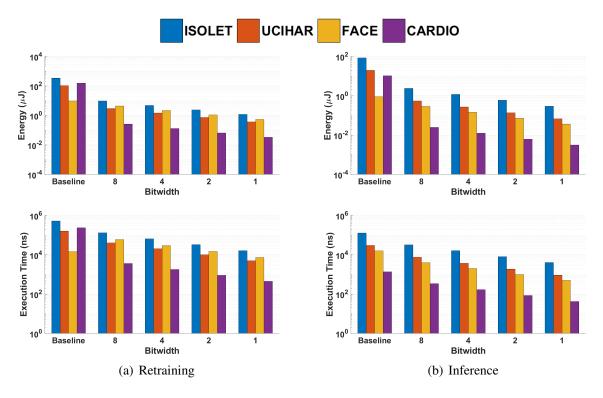

| Figure 5.9.  | Energy consumption and execution time of HyDREA using different model bitwidths during training and inference with an ADC bitwidth of 2                                                                                                                  | 90  |

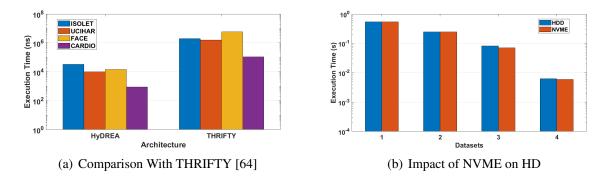

| Figure 5.10. | Execution time comparison of HyDREA with THRIFTY, a processing in storage architecture for HD Computing and the impact of higher bandwidth memories such as NVME on HD Computing.                                                                        | 92  |

| Figure 5.11. | Accuracy of Design as the SNR varies with an ADC bitwidth of 2 and varying model bitwidth.                                                                                                                                                               | 92  |

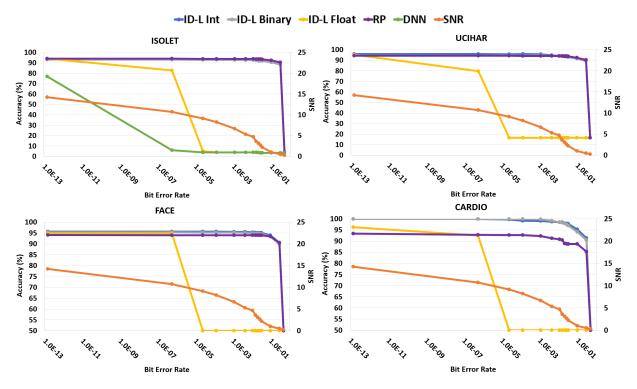

| Figure 5.12. | Accuracy of HD Classification as the SNR varies with different encodings and data representations.                                                                                                                                                       | 94  |

| Figure 5.13. | Comparison of the Robustness of HD to other Classifiers                                                                                                                                                                                                  | 96  |

| Figure 5.14. | Energy consumption and execution time of HyDREA for one Clustering iteration using different model bitwidths with an ADC bitwidth of 2                                                                                                                   | 96  |

| Figure 5.15. | Comparison of HD Clustering with K-means Accuracy With no Bit Errors                                                                                                                                                                                     | 97  |

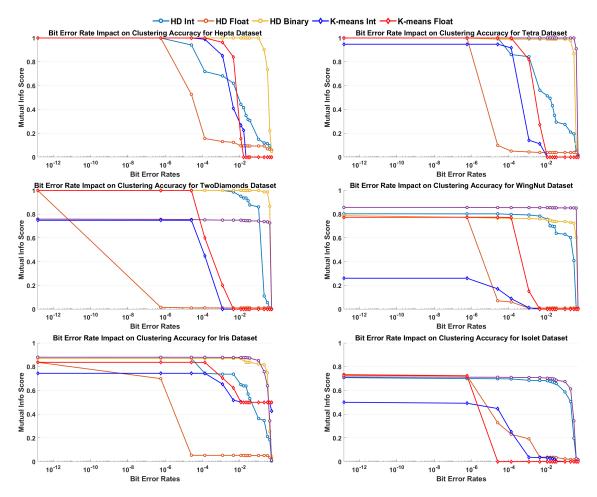

| Figure 5.16. | Accuracy of HD Clustering as the SNR varies with different encodings and data representations vs K-means                                                                                                                                                 | 98  |

| Figure 5.17. | Impact of Dimensionality on Decoding Quality.                                                                                                                                                                                                            | 99  |

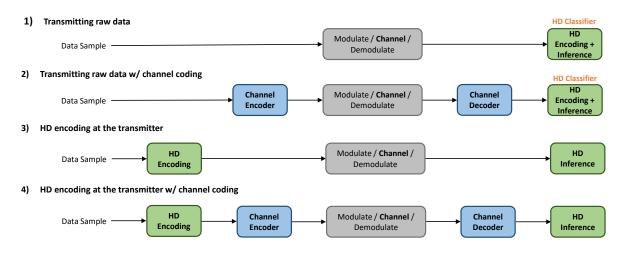

| Figure 5.18. | Simulated communication setups                                                                                                                                                                                                                           | 101 |

| Figure 5.19. | a) Comparison of HD encoding to channel coding (setup 1,2, and 3), b) combined HD encoding and channel coding (setup 3 and 4), c) channel coding performance at low SNRs, exact (dashed) and approximate (solid) decoding algorithms.                    | 102 |

#### LIST OF TABLES

| Table 3.1. | CPU-based comparison of HD and other classifiers.                                                                          | 47 |

|------------|----------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.2. | Average change in classification accuracy due to online dimension reduction.                                               | 53 |

| Table 4.1. | Multi-label HD 3D Storage Parameters                                                                                       | 66 |

| Table 5.1. | Dataset Information                                                                                                        | 89 |

| Table 5.2. | Impact of Dimensionality and Data Representation on the Robustness of HD Computing Classification and Clustering Accuracy. | 89 |

| Table 5.3. | Speedup of HyDREA over a digital PIM implementation with the same bitwidth as HyDREA with the same area.                   | 91 |

| Table 5.4. | Comparison of HyDREA with the State-of-the-art DNN PIM Accelerator Q-PIM [1]                                               | 96 |

#### ACKNOWLEDGEMENTS

I would like to first thank my advisors, Professor Tajana S. Rosing and Professor Baris Aksanli for their guidance and support during my Ph.D. I am truly grateful for their support through the past years. Tajana's enthusiasm to explore a wide range of research directions pushed me to never leave a stone unturned, as well as, learn about different fields through collaboration. I'd like to thank Baris for his support in all aspects of life throughout the years, giving me the motivation I needed to continue on and for bringing new perspectives through his experience to my research. I would also like to thank my dissertation committee members, Professors Shangping Ren, Farinaz Koushanfar, and Ryan Kastner, for their feedback and discussions related to my Ph.D. work. I would like to thank all my colleagues in SEELab for their active collaboration and continuous support. I would like to give special thanks to Mohsen Imani, Yeseong Kim, Saransh Gupta, Behnam Khaleghi, Anthony Thomas, Yilun Hao, Kazim Ergun, Minxuan Zhou, and Onat Gungor. My research was made possible by funding from the National Science Foundation (NSF) Grant 1527034, 1730158, 1826967, 1830331, 1911095, 2003279, CRISP, one of six centers in JUMP, an SRC program sponsored by DARPA, and SRC-Global Research Collaboration grant.

I owe so much to all my family for their understanding, patience, and encouragement that helped me navigate through the difficult moments during the past few years. Finally, I would like thank all my friends for their constant support.

The material in this dissertation is based on the following publications.

Chapter 2, in part, is a reprint of the material as it appears in J. Morris, S. Set, G. Rosen, M. Imani, B. Aksanli, and T. Rosing, "AdaptBit-HD: Adaptive Model Bitwidth for Hyperdimensional Computing" in IEEE International Conference on Computer Design (ICCD), 2021. The dissertation author was the primary investigator and author of this material.

Chapter 3, in part, is a reprint of the material as it appears in J. Morris, Y. Hao, R. Fernando, M. Imani, B. Aksanli, T. Rosing, "Locality-based Encoder and Model Quantization for Efficient Hyper-Dimensional Computing". *IEEE Transactions on Computer-Aided Design*

*of Integrated Circuits and Systems (TCAD)*, 2021. The dissertation author was the primary investigator and author of this material.

Chapter 4, in part, is a reprint of material as it appears in J. Morris, Y. Hao, S. Gupta, R. Ramkumar, J. Yu, M. Imani, B. Aksanli, T. Rosing, "Multi-label HD Classification in 3D Flash". IEEE/IFIP International Conference on VLSI and System-on-Chip (VLSI-SoC), 2020. The dissertation author was the primary investigator and author of this material.

Chapter 5, in part, is a reprint of material as may appear in J. Morris, K. Ergun, B. Khaleghi, M. Imani, B. Aksanli, T. Rosing, "HyDREA: Utilizing Hyperdimensional Computing For A More Robust and Efficient Machine Learning System." *ACM Transactions on Embedded Computing Systems (TECS)*, 2022. The dissertation author was the primary investigator and author of this material.

My co-authors (Prof. Baris Aksanli, Kazim Ergun, Roshan Fernando, Sarnash Gupta, Yilun Hao, Mohsen Imani, Behnam Khaleghi, Ranganathan Ramkumar, Gadi Rosen, Prof. Tajana S. Rosing, Si Thu Kaung Set, and Jeffrey Yu listed in alphabetical order) have all kindly approved the inclusion of the aforementioned publications in my dissertation.

#### VITA

| 2018 | Bachelor of Science in Computer Science and Engineering (Computer Engineer-<br>ing), University of California, San Diego, USA |

|------|-------------------------------------------------------------------------------------------------------------------------------|

|      |                                                                                                                               |

2022 Doctor of Philosophy in Engineering Science (Electrical & Computer Engineering), University of California, San Diego, USA and San Diego State University, USA

#### PUBLICATIONS

Justin Morris, Yilun Hao, Saranash Gupta, Behnam Khaleghi, Baris Aksanli, Tajana Rosing. "Stochastic-HD: Leveraging Stochastic Computing on the Hyper-Dimensional Computing Pipeline", *Frontiers in Neuroscience*, 2022.

Behnam Khaleghi, Jaeyoung Kang, Hanyang Xu, Justin Morris, Tajana Rosing "GENERIC: Highly Efficient Learning Engine on Edge using Hyperdimensional Computing", *Design Automation Conference (DAC)*, 2022.

George Armstrong, Cameron Martino, Justin Morris, Behnam Khaleghi, Jaeyoung Kang, Jeff DeReus, Qiyun Zhu et al. "Swapping Metagenomics Preprocessing Pipeline Components Offers Speed and Sensitivity Increases." *Msystems* (2022): e01378-21.

Justin Morris, Kazim Ergun, Behnam Khaleghi, Mohsen Imani, Baris Aksanli, and Tajana Rosing, "HyDREA: Utilizing Hyperdimensional Computing For A More Robust and Efficient Machine Learning System." *ACM Transactions on Embedded Computing Systems (TECS)*, 2022.

Justin Morris, Hin Wai Lui, Kenneth Stewart, Behnam Khaleghi, Anthony Thomas, Thiago Marback, Baris Aksanli, Emre Neftci, and Tajana Rosing, "HyperSpike: HyperDimensional Computing for More Efficient and Robust Spiking Neural Networks," in *Design, Automation Test in Europe Conference Exhibition (DATE)*, 2022.

Yilun Hao, Saransh Gupta, Justin Morris, Behnam Khaleghi, Baris Aksanli, and Tajana Rosing, "Stochastic-HD: Leveraging Stochastic Computing on Hyper-Dimensional Computing," in *IEEE 39th International Conference on Computer Design (ICCD)*, 2021.

Justin Morris, Si Thu Kaung Set, Gadi Rosen, Mohsen Imani, Baris Aksanli, and Tajana Rosing, "AdaptBit-HD: Adaptive Model Bitwidth for Hyperdimensional Computing," in *IEEE 39th International Conference on Computer Design (ICCD)*, 2021.

Alice Sokolova, Mohsen Imani, Andrew Huang, Ricardo Garcia, Justin Morris, Tajana Rosing, and Baris Aksanli, "MACcelerator: Approximate Arithmetic Unit for Computational Acceleration," in 22nd International Symposium on Quality Electronic Design (ISQED) 2021.

Justin Morris, Yilun Hao, Roshan Fernando, Mohsen Imani, Baris Aksanli, and Tajana Rosing, "Locality-based Encoder and Model Quantization for Efficient Hyper-Dimensional Computing," in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, 2021.

Behnam Khaleghi, Hanyang Xu, Justin Morris, and Tajana Šimunić Rosing, "tiny-HD: Ultra-Efficient Hyperdimensional Computing Engine for IoT Applications," in *Design, Automation Test in Europe Conference Exhibition (DATE)*, 2021.

Justin Morris, Kazim Ergun, Behnam Khaleghi, Mohsen Imani, Baris Aksanli, and Tajana Rosing, "Hydrea: Towards more robust and efficient machine learning systems with hyperdimensional computing," in *Design, Automation Test in Europe Conference Exhibition (DATE)*, 2021.

Yunhui Guo, Mohsen Imani, Jaeyoung Kang, Sahand Salamat, Justin Morris, Baris Aksanli, Yeseong Kim, and Tajana Rosing, "HyperRec: Efficient Recommender Systems with Hyperdimensional Computing," in *26th Asia and South Pacific Design Automation Conference (ASP-DAC)*, 2021.

Rebecca K. Fielding-Miller, Smruthi Karthikeyan, Tommi Gaines, Richard S. Garfein, Rodolfo A. Salido, Victor Cantu, Laura Kohn et al. "Wastewater and surface monitoring to detect COVID-19 in elementary school settings: The Safer at School Early Alert project." *Medrxiv* (2021).

Saransh Gupta, Justin Morris, Mohsen Imani, Ranganathan Ramkumar, Jeffrey Yu, Aniket Tiwari, Baris Aksanli, and Tajana Simunic Rosing, "THRIFTY: Training with Hyperdimensional Computing across Flash Hierarchy," in *IEEE/ACM International Conference on Computer Aided Design (ICCAD)*, 2020.

Justin Morris, Yilun Hao, Saransh Gupta, Ranganathan Ramkumar, Jeffrey Yu, Mohsen Imani, Baris Aksanli, and Tajana Simunic Rosing, "Multi-label HD Classification in 3D Flash," in *Proceedings of IFIP/IEEE International Conference on VLSI and System-on-Chip (VLSI-SoC)*, 2020.

Mohsen Imani, Justin Morris, Samuel Bosch, Helen Shu, Giovanni De Micheli, and Tajana Rosing, "Adapthd: Adaptive efficient training for brain-inspired hyperdimensional computing," in *IEEE Biomedical Circuits and Systems Conference (BioCAS)*, 2019.

Justin Morris, Mohsen Imani, Samuel Bosch, Anthony Thomas, Helen Shu, and Tajana Rosing, "CompHD: Efficient hyperdimensional computing using model compression," in *IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED)*, 2019.

Mohsen Imani, Justin Morris, John Messerly, Helen Shu, Yaobang Deng, and Tajana Rosing, "Bric: Locality-based encoding for energy-efficient brain-inspired hyperdimensional computing," in *Proceedings of the 56th Annual Design Automation Conference (DAC)*, 2019.

Mohsen Imani, Justin Morris, Helen Shu, Shou Li, and Tajana Rosing, "Efficient associative search in brain-inspired hyperdimensional computing," in *IEEE Design Test 37*, no. 1 2019 28-35.

Mohsen Imani, Tarek Nassar, Justin Morris, and Tajana Rosing, "DNA Sequencing using Braininspired Hyperdimensional Computing," in *GOMACTech Conference*, 2019.

#### ABSTRACT OF THE DISSERTATION

Fast, Efficient, and Robust Learning with Brain-Inspired Hyperdimensional Computing

by

#### Justin Morris

#### Doctor of Philosophy in Engineering Science (Electrical & Computer Engineering)

University of California San Diego, 2022 San Diego State University, 2022

Professor Tajana Šimunić Rosing, Co-Chair Professor Baris Aksanli, Co-Chair

With the emergence of the Internet of Things (IoT), devices will generate massive data streams demanding services that pose huge technical challenges due to limited device resources. Furthermore, IoT systems increasingly need to run complex and energy intensive Machine Learning (ML) algorithms, but do not have the resources to run many state-of-the-art ML models, instead opting to send their data to the cloud for computing. This results in insufficient security, slower moving data, and energy intensive data centers. In order to achieve real-time learning in IoT systems, we need to redesign the algorithms themselves using strategies that more closely model the ultimate efficient learning machine: the human brain.

This dissertation focuses on increasing the computing efficiency of machine learning on IoT devices with the application of Hyperdimensional Computing (HDC). HDC mimics several desirable properties of the human brain, including: robustness to noise, robustness to hardware failures, and single-pass learning where training happens in one-shot without storing the training data points or using complex gradient-based algorithms. These features make HDC a promising solution for today's embedded devices with limited storage, battery, and resources, and the potential for noise and variability. Research in the HDC field has targeted improving these key features of HDC and expanding to include even more features. There are four main paths in HDC research: (1) Algorithmic changes for faster and more energy efficient learning, (2) Novel architectures to accelerate HDC, usually targeting lower power IoT devices, (3) Extending HDC applications beyond classification, (4) Exploiting the robust property of HDC for more efficient and faster inference, and (5) HDC Theory, its connection to neuroscience and mathematics. This dissertation contributes to four of these research paths in HDC.

Our contributions include: (1) We introduce the first adaptive bitwidth model for HDC [2]. In this work we propose a new quantization method and during inference we iterate through the bits along all dimensions taking the hamming distance. At each iteration, we check if the current hamming distance passes a threshold similarity, if it does, we terminate execution early to save energy and time. (2) We create a redesign of the entire HDC process with a locality-based encoding, quantized retraining, and online dimension reduction during inference, all accelerated by a new novel FPGA design [3]. In this work we our locality-based encoding removes random memory accesses from HDC encoding as well as adds sparsity for more efficiency. We also introduce a general method to quantize to any desired model bitwidth. Finally, we propose a method to find any insignificant dimensions in the HDC model and remove them for more energy efficiency during inference. (3) We extend HDC to support multi-label classification [4]. We perform multi-label classification by creating a binary classification model for each label. Upon inference, our models determine if each label exists independently. This is different than prior work that took the power set of the labels to reduce the problem to a single label classification

as HDC scales poorly with this method. (4) Finally, we experimentally evaluate the robustness of HDC for the first time and create a new analog PIM architecture with reduced precision Analog to Digital Converters (ADC), exploiting that robustness [5]. We test HDC robustness in a federated learning environment where edge devices send encoded hypervectors to a central server wirelessly. We evaluate the impact of any wireless transmission errors on this data and show that HDC is  $48 \times$  more robust than other classifiers. We then use this knowledge that HDC is robust to create a more efficient analog PIM circuit by reducing the bitwidth of the ADCs.

# Chapter 1 Introduction

We live in a world where technological advances are continually creating more data than what we can cope with. With the emergence of the Internet of Things (IoT), devices will generate massive data streams demanding services that pose huge technical challenges due to limited device resources [6, 7, 8, 9]. For example, IoT devices are increasingly supporting many Machine Learning (ML) applications. However, these devices do not have the required computing resources or even battery life to support state-of-the-art ML models such as DNNs. Instead, these embedded devices send their data to a cloud server, where models are run at a data center scale. This poses multiple problems as sending data to the cloud for processing is not scalable, cannot guarantee the real-time response, and is often not desirable due to privacy and security concerns. Much of IoT data processing will need to run at least partly on devices at the edge of the Internet.

In order to achieve real-time learning in IoT systems, we need to rethink the algorithms we use for machine learning and redesign them using strategies that more closely model the ultimate efficient learning machine: the human brain. Neuromorphic, or brain-inspired, models aim to close this gap of available resources at the edge and required resources for ML applications. Hyperdimensional Computing (HDC) is one of the Neuromorphic computing models that can offer, brain-like efficiency [10]. HDC is based on a short-term human memory model, the sparse distributed memory, that emerged from theoretical neuroscience. A key benefit of HDC is its natural robustness to noise. This is of critical importance in IoT systems, where noise and high error rates are common during communication. In the rest of this chapter, we discuss an overview of the HDC algorithm, related work, and the contributions of this thesis in more detail.

# **1.1 Hyperdimensional Computing**

Our research has been instrumental in developing practical implementations of HDC a computational technique modeled after the brain [10]. The HDC system enables large-scale learning in real-time, including both training and inference. HDC is motivated by the observation that the key aspects of human memory, perception, and cognition can be explained by the mathematical properties of high-dimensional spaces. It models data using points of a highdimensional space, called hypervectors. These points can be manipulated with formal algebra operations to represent semantic relationships between objects. HDC mimics several desirable properties of the human brain, including: robustness to noise, robustness to hardware failures, and single-pass learning where training happens in one-shot without storing the training data points or using complex gradient-based algorithms. These features make HDC a promising solution for today's embedded devices with limited storage, battery, and resources, and the potential for noise and variability.

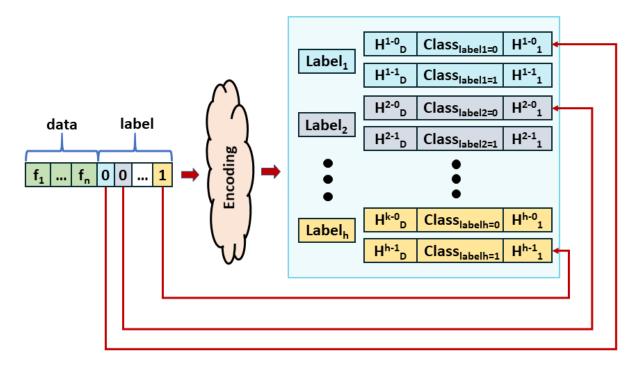

HDC has 3 main parts, encoding, training, and inference. In the next subsections we give an overview of each of these modules and the HDC algorithm for classification. Figure 1.1 shows an overview of HDC classification.

#### 1.1.1 Encoding

The first step of HDC is to math the input feature vector to high dimensional space. Consider a feature vector  $\mathbf{v} = \langle v_1, \dots v_n \rangle$ . The encoding module takes this *n*-dimensional vector and converts it into a *D*-dimensional hypervector (HV) (D >> n). We utilized the encoding module proposed in [11]. The encoding is performed in three steps, which we describe below. The first step is to create two sets of HVs, *ID* HVs and level HVs. Both ID HVs and *level* HVs

Figure 1.1. Overview of creating an HD model and performing inference with an HD model

are *D* dimensional HVs where each element is either -1 or 1. The encoding scheme assigns a unique channel *ID* HV to each feature position. *IDs* are hypervectors which are randomly generated such that all features will have orthogonal channel *IDs*, i.e.,  $\delta(ID_i, ID_j) < 5,000$ ) for D = 10,000 and  $i \neq j$ ; where the  $\delta$  measures the element-wise similarity between the vectors. The HD computing encoder also generates a set of *level* HVs to consider the impact of each feature value. To create these level hypervectors, we compute the minimum and maximum feature values among all data points,  $\mathbf{v}_{min}$  and  $\mathbf{v}_{max}$ , then quantize the range of  $[\mathbf{v}_{min}, \mathbf{v}_{max}]$  into *m* levels. Each level is then assigned a corresponding level HV:  $\mathbf{LV} = {\mathbf{LV}_1, \dots, \mathbf{LV}_m}$ . To encode a feature vector, the encoder looks at each position of the feature vector and element-wise multiplies the channel ID  $(ID_i)$  with the corresponding level hypervector  $(hv_i)$ . The following equation shows how an *n*-length feature vector is mapped into the HD space with this encoding scheme:

$$H = [hv_1 * ID_1 + hv_2 * ID_2 + \ldots + hv_n * ID_n]$$

$$hv_j \in \{LV_1, LV_2, \dots, LV_m\}, \ 1 \le j \le m$$

$ID_i \in \{-1, 1\}^D, LV_j \in \{-1, 1\}^D$

#### 1.1.2 Training

The next step in HDC is to train the model. HDC supports efficient one-pass training. To build a one-pass model, the encoder maps all training data to training HVs ( $\mathscr{H}$ ). For all training HVs within a class ({ $\mathscr{H}_i^1, \mathscr{H}_i^2, \ldots, \mathscr{H}_i^j$ }), HD computing adds them together to create a single class HV ( $\mathscr{C}_i$ ).

$$\mathscr{C}_i = \mathscr{H}_i^1 + \mathscr{H}_i^2 + \ldots + \mathscr{H}_i^j$$

Once this is done for every class, we have an HD model that can be used for inference. However, we can significantly improve the accuracy of our HD model with retraining [11]. We retrain the HD model by inputting each training data point through the HD model as a query hypervector (Q). We look at the similarity of the query hypervector to all stored class hypervectors; (i) if the query is correctly classified by the current model, our design does not change the model. (ii) If it is incorrectly matched with the i'h class hypervector ( $C_i$ ), when it actually belongs to j'h class ( $C_j$ ), our retraining procedure subtracts the query hypervector from the i'h class and adds it to j'h class hypervector:  $C_i = C_i - Q$  and  $C_j = C_j + Q$ . Retraining can run until a user-provided error threshold is met, or a maximum number of iterations is reached. After training, class HVs are stored in the classifier.

#### **1.1.3 Inference**

Upon inference, the encoder first maps the input data into a query HV ( $\mathcal{Q}$ ), using the same encoding that was used to train the HD model. A similarity metric is used to determine the strength of a match between the query HV and each class HV. The most common metric used in HD computing is cosine similarity, but note that other metrics (e.g. Hamming distance) could

be appropriate depending on the problem [12]. After the similarity is computed between the query HV and each class HV in the classifier, the class with the highest similarity is chosen as the output class.

Research on HDC has focused on five main topics: Algorithmic improvements, Hardware/Software Co-Design, Extending Applications, Exploiting Robustness, and HDC Theory, its connection to neuroscience and mathematics. In this dissertation, we focus on the first four research paths.

#### **1.1.4** Algorithmic Improvements

HDC is a relatively new topic of research in the machine learning field and has been rapidly growing since 2017 [13]. One issue with HDC is data size due to encoding to high dimensional space (D=10,000). To address this, model quantization has been proposed to reduce the bitwidth of the hypervectors and therefore, reducing the overall data size [14, 15]. There have been recent works to apply similar algorithmic techniques to improve HDC energy efficiency, execution time, and accuracy that have previously been implemented on Neural Networks as well. For instance, we proposed the first work to implement a learning rate to the HDC algorithm [16]. This work achieves an adaptive learning rate by finding the similarity difference between the incorrectly selected class and the correct class with the query. Then, inputs that difference into a lookup table to select the learning rate. Finally, the learning rate is multiplied to the query before it is used to update the model. Lastly, work has been done to reduce the dimensionality of the HDC model without significantly impacting accuracy [17]. This work proposes two methods to reduce the dimensionality by finding insignificant dimensions. The first is class-wise eliminating the dimensions in each class that are closest to 0.

#### 1.1.5 Hardware/Software Co-Design

There has also been lots of work on creating new efficient architectures with the HDC algorithm in mind. For instance, one of the main benefits of HDC is that it has highly parallel simple operations. This property makes it a perfect match for Processing in Memory (PIM) architectures. HDC has been accelerated by both analog and digital PIM [18, 5, 19]. Work has also been done to remove the reduction operations in HDC on the algorithm side to further improve the energy efficiency in PIM as PIM architectures struggle with reduction operations [20]. This work achieves this by mapping all HDC operations to the stochastic domain. In the stochastic domain, all mathematical operations are approximated by bitwise operations. With this method, the authors were able to eliminate the reduction part of the dot product, which was the main bottleneck in digital PIM. There has also been work on creating more efficient FPGA or ASIC designs for HDC [17, 21].

#### **1.1.6 Extending Applications**

Recent work has been done to extend HDC applications beyond classification. For instance, HDC has recently been extended to support clustering [22]. Furthermore, HDC has been extended to support recommender systems for the first time [23]. There is also work on using HDC for DNA classification [24]. However, there are still multiple different ML applications HDC has not been mapped to yet. For instance, in this dissertation, we introduce the first work on utilizing HDC for multi-label classification.

#### **1.1.7 Exploiting Robustness**

One of the key properties of HDC is that it is robust to noise and other sources of errors such as bitflips in hardware. Multiple previous works cite this property and utilize it indirectly to create more efficient architectures [17, 15, 25]. For instance, work in [17] attempts to remove a large portion of dimensions for more efficient inference. This can be viewed as introducing errors into the inference operation, but because HDC is robust to these errors, the HDC model is

able to maintain accuracy. However, none of these previous works explicitly demonstrated the robustness of HDC compared to other classifiers.

# **1.2** Thesis Contributions

Our contributions include: (1) The first adaptive model bitwidth for HDC [2], (2) a new hardware friendly encoding that creates a sparse locality-based encoding with a fixed memory access pattern, a general method for quantizing HDC, and a method to reduce the dimensionality of the HDC model [3], (3) extending the HDC algorithm to support multi-label classification [4], and (4) evaluating and exploiting the robustness of HDC for more efficient hardware [5].

#### 1.2.1 Adaptive Model Quantization for Hyperdimensional Computing

As mentioned in Section 1.1.4, research on HDC algorithmic changes have extended ideas from other ML algorithms to HDC, such as adding a learning rate, model quantization, and sparsity. However, all previous work on model quantization for HDC has been static quantization. For instance, work in [15] quantizes only to binary and work in [14] only supports ternary quantization. This leads to two extremes in the energy and accuracy trade-off curve. Either, highly accurate models with less aggressive quantization and more energy consumption. Or, highly efficient models with aggressive quantization, such as binary models, but at the cost of accuracy loss. In this dissertation, we propose a new model quantization method that adapatively changes the effective bitwidth for every sample [2]. We do this by iterating over the bits of the quantized numbers along all dimensions. At each iteration, we take the hamming distance and check if the highest similarity passes a threshold. If it does, we can terminate execution early saving energy and time. This enables our design to achieve energy efficiency and execution time comparable to a binary model, while also achieving a similar accuracy to the full precision model. This work is discussed in Chapter 2 of this dissertation.

## **1.2.2 A Rework of the Hyperdimensional Computing Pipeline and** Acceleration on FPGA

There are multiple different works on mapping HDC to different hardware platforms and using hardware/software co-design to achieve more efficient solutions, as mentioned in Section 1.1.5. However, previous designs to not solve the problem of encoding to HD space. Previous encoding algorithms require random memory accesses and a massive amount of element wise multiplications and additions in the dimensionality of 10,000. These encodings are inefficient to map to hardware designs [11]. In this dissertation, we propose a new hardware friendly encoding that removes random memory accesses and replaces them with a fixed memory access pattern with sparsity and a subsequent FPGA architecture that takes advantage of the changes [3]. We additionally propose a general quantization method to quantize HDC to any bitwidth. Finally, we propose a dimension reduction method to remove insignificant dimensions in the HDC model. Overall, our new architecture achieves  $64 \times$  energy efficiency and  $10 \times$  faster execution time than the previous state of the art FPGA implementation of HDC. This work is discussed in Chapter 3 of this dissertation.

# **1.2.3 Extending Hyperdimensional Computing Applications to Support** Multi-Label Classification

As mentioned in Section 1.1.6, HDC is a growing field of research and much work has been done on extending HDC to other ML applications beyond classification. However, there were no works on extending HDC to support multi-label classification. In this dissertation, we present our work on extending HDC to support multilabel classification [4]. Prior work on other classifiers map to multilabel by simply taking the power set of the possible labels and creating new labels for each combination. This reduces the multilabel problem to a single label problem. This works well for other classifiers as they don't scale as poorly with an increase in classes. However, HDC scales linearly with the number of classes, so it scales exponentially with the number of labels in a multilabel problem. Therefore, instead of using the power set idea seen in other models, we propose a binary classification model for each label. Overall, with this idea, we achieve  $47 \times$  faster execution time,  $48 \times$  better energy efficiency, and 5% higher accuracy than other multilabel classifiers. This work is discussed in Chapter 5 of this dissertation.

# **1.2.4 Evaluating and Exploiting Robustness to Create a More Efficient** Analog Processing-in-Memory Accelerator for Hyperdimensional Computing

As mentioned in Section 1.1.7, multiple works in the HDC space cite that HDC is robust to noise and hardware errors and often take advantage of that property in their designs. However, before our work in [5] there were no empirical results to back up the claims of robustness or comparisons with other ML models. We include this work in this dissertation and demonstrate experimentally that HDC is  $48 \times$  more robust to noise than other machine learning models. We furthermore demonstrate how to exploit this property with more efficient hardware. Previous analog PIM designs have a vital flaw where up to 90% of energy is used in the analog to digital conversion (ADC) [26]. However, we alleviate this issue when mapping HDC to analog PIM by reducing the ADC bitwidth. This reduces ADC energy consumption by half for every bit dropped, but results in inaccurate conversions. However, because HDC is robust to these errors, it is able to tolerate the inaccurate operations up to a point. Overall, our design is able to achieve  $289 \times$  better energy efficiency than simply mapping HDC onto the existing architecture. This work is discussed in Chapter 4 of this dissertation.

Finally, in Chapter 6, we summarize our work on HDC and discuss future directions of research in HDC. We discuss two directions of future work: 1) utilizing feature extraction with HDC and 2) further eploiting and evaluating the robustness of HDC.

# Chapter 2

# Adaptive Model Quantization for Hyperdimensional Computing

# 2.1 Introduction

Existing HD computing quantization methods have two main challenges: (i) the trade-off between accuracy and energy efficiency has to be decided before training the model, and the model would have to be retrained from scratch to change bitwidths if the accuracy and energy efficiency trade-off requirements change. (ii) Existing model quantization techniques ignore that not all samples need to be quantized with the same value. Some samples can be classified with simple binary representations, while others require higher bitwidths for accurate classification. In other words, there exists no adaptive bitwidth quantization for HD computing. Adaptive bitwidth quantization adds another level of fine tuning for systems balancing the accuracy and energy efficiency trade-off.

In this chapter, we propose AdaptBit-HD, which, to the best of our knowledge, is the the first Adaptive Model Bitwidth Architecture for accelerating HD computing. AdaptBit-HD does not change the bitwidth of the representation of the data, but operates on the bits of the quantized model in a bitserial way to save energy when fewer bits can be used to find the correct class. AdaptBit-HD can achieve both high accuracy by utilizing all bits when necessary and high energy efficiency and faster execution time by terminating execution at lower bits when our design is confident in the output. AdaptBit-HD achieves this by performing a bitseial

hamming distance operation on the query HV and class HVs. We check after each bit if we are confident enough in our current answer to terminate execution early. To achieve this, we completely redesign the HD computing algorithm including training, retraining, and inference. We accordingly design an end-to-end HD FPGA accelerator for AdaptBit-HD and compare with a state-of-the-art binary quantization FPGA accelerator for HD [15] as well as a 16-bit static quantization method. Compared to binary quantization AdaptBit-HD is 1.1% more accurate at the cost of just 10% more energy consumption and 7% more execution time. Compared to 16-bit models, AdaptBit-HD is  $14\times$  more energy efficient at the cost of 0.5% accuracy.

## 2.2 Related Work

Model quantization is a widely used technique in machine learning applications to improve energy efficiency. For instance, Google's TPU for performing inference on DNNs utilizes reduced bit representations [27]. Furthermore, [28] proposes a quantization method for SVMs. Model quantization has also been used to reduce the memory requirement for a more efficient hardware design [29]. Other methods such as model compression have also been used to improve the energy efficiency of neural networks [30]. Model quantization has also been widely used to accelerate and improve the energy consumption of HD computing [14, 31]. Although model quantization has improved other machine learning methods such as DNNs, light-weight models such as HD computing continue to be more energy efficient and for applications where energy efficiency is paramount, light-weight models should continue to be utilized.

Prior work applied high-dimensional computing to different classification problems such as language recognition, speech recognition, face detection, EMG gesture detection, humancomputer interaction, and sensor fusion prediction [32, 33, 34, 22, 35]. Although HD computing is more energy efficient than other traditional machine learning models such as DNNs and MLPs, there has been a significant amount of work on pushing the limits of HD computing to achieve even better energy efficiency. Prior work accelerated HD computing by removing dimensions of

11

the class hypervectors [17], or compressing the HD model [36]. Work in [37] also proposed a dynamic dimensionality model to improve energy efficiency.

Prior work has also shown that quantizing the class hypervectors can provide significant energy and speedup improvements at a small cost in accuracy [31, 38]. Work in [14] extended the idea of binarizing the class HV weights to using a ternary model to achieve higher accuracies. However, all of the existing work on HD computing for model quantization is static. This poses a few problems. For instance, if accuracy and energy efficiency needs change, the model needs to be completely retrained to change bitwidths. Additionally, by being static, one has to choose where they land on the accuracy and energy trade-off curve at a macro level. This often leads to leaning towards one end of the spectrum, either highly energy efficient with accuracy loss, or highly accurate with high energy consumption. This problem is exaggerated for applications with varying precision needs based on the incoming data. However, in this chapter, we propose an adaptive bitwidth quantization method that chooses the best bitwidth per sample to achieve a confident classification with minimal energy usage. This leads to an overall design that achieves both high accuracy and high energy efficiency.

# 2.3 AdaptBit-HD

In this chapter, we propose AdaptBit-HD, the first Adaptive Model Bitwidth Architecture for accelerating HD computing. HD computing consists of three main modules shown in Figure 1.1: encoding, training, and inference. The encoding module maps each data point to high-dimensional space. The HD model accumulates every encoded training hypervector (HV) to create an integer model. This integer model is then used to create a quantized model. During inference, HD computing then chooses the most similar class to the query HV as the output class. AdaptBit-HD fundamentally changes the inference phase by operating on the bits of the quantized model in a bitserial way to save energy when fewer bits can be used to find the correct class. We check after each bit if we are confident enough in our current answer to terminate execution early based on a threshold of similarity. By operating with this new inference technique, AdaptBit-HD is able to achieve the energy efficiency of binary models, while maintaining the accuracy of full precision models. To further support our proposed bitserial inference design, AdaptBit-HD accordingly proposes a training approach that trains the model to create quantized HVs and tunes the model to improve the confidence of the threshold we utilize to determine if we can terminate execution early. In the following, we explain the details of both the baseline HD functionality and AdaptBit-HD functionality.

#### 2.3.1 Training with AdaptBit-HD

Existing model quantization techniques result in faster and more efficient machine learning models. This quantization also leads to less area, because the model is represented with values smaller than 32 bits. However, all prior techniques quantize all samples to the same bitwidth. This leads to a non-optimal design as even binary quantizations have been shown to provide high accuracy. Therefore, many samples can be correctly classified with lower bitwidth representations and higher bitwidth quantizations should be reserved for samples that are more difficult to separate them. In this section, we go over how we can achieve this adaptive model quantization with HD computing.

Figure 2.1 demonstrates the idea that not all samples need the same bitwidth to be accurately labeled. For instance, in the figure, we can see that HD computing is able to achieve an average of 95.7% accuracy with binary values. Additionally, by moving to a 5 - bit representation, HD is able to improve in accuracy by 1.16% on average. Comparing the 5 - bit representations with full precision, we can see that the 16-bit precision model is only able to achieve 0.42% more accuracy than the 5 - bit models. This demonstrates that for most samples, we can get away with aggressive model quantization. However, there are some samples that require more bits to separate the data properly to maintain high accuracy. Rather then using high precision for all of the samples to achieve high accuracy, we can adaptively select the bitwidth we need for the sample during inference to balance both accuracy and energy efficiency. This

Figure 2.1. Difference in Accuracy with Various HD Bitwidth Representations for HD Computing

#### Figure 2.2. Overview of Creating a AdaptBit-HD Model During Retraining

balance is important for application where accuracy and energy efficiency are equally important such as when performing a medical diagnosis with a mobile device running on a battery.

**Initial Training:** The initial training for model quantization is very similar to the initial training for the baseline model without quantization, as we first build the full bitwidth model by combining all samples as described in 2.3.1. The training process for model quantization diverges from that of past work after the initial training. As Figure 2.2 shows, We first normalize all of the class HVs such that all of the dimensions are in the range [-1,1], but we still keep the non-normalized vectors around. We then quantize the normalized vectors to the nearest power of 2 in a list of quantized values.

The list of powers of two is defined by two parameters: *n*, the number of bits, and *o*, the offset of the powers of two. The offset is to control where in the range of values (-1,1) we want to have a higher resolution of representation. Higher offsets leads to better quantization

near 0. We first set aside one bit for representing 0. Then the rest of the  $2^{(n-1)}$  representations are defined as follows:  $2^{(r-o)}$  where  $r = -1, -2, ..., -(2^{(n-2)})$  and o is the offset. The reason we only iterate  $r 2^{(n-2)}$  times is because we additionally represent the same powers of two on the negative side. Each power of two representation is then assigned a unique n - bit binary string representation. For example, if n = 3 and o = 0, we would be able to represent the following powers of 2 in our model quantization:  $(-2^{-1}, -2^{-2}, 0, 2^{-1}, 2^{-2})$ , where each one of these values is assigned a unique 3 - bit sequence of 0s and 1s. Once we set each dimension to the closest power of two we can represent, we then have an HD model where each dimension is an n - bit value.

To encode our weights to unique n - bit values, we assign the first bit to indicate if the value is negative or positive. This ensures that the first bit hamming distance is equivalent to how binary models are created for HD. We reserve the second bit to indicate if the value is zero or not. Thus, the calculation of the hamming distance for the second bit is equivalent to counting the number of matching zeros. For the rest of the bits, because we use hamming distance as our similarity metric (which is explained in Section 2.3.2) on the binary representation of our values instead of the cosine similarity of the values themselves, it is important that values near each other have a small hamming distance score between each other. To achieve this, we use a grey code encoding to assign the last bits of the binary strings to each power of 2. This ensures that any adjacent quantized value differs by only one bit.

**Retraining:** The retraining process for model quantization is also similar to the retraining process for the baseline model without quantization. Throughout training, we store both a full precision model and an n - bit representation model of the class hypervectors. We retrain the quantized model by iterating through the training set. In a single iteration of model adjustment, HD computing checks the similarity of all training data points, say **H**, with the class hypervectors in the quantized binary model. The data point is assigned to the class with which it has the closest similarity. If the datapoint is correctly classified, normally, no model update is needed. However, in Section 2.3.2, we modify this to support adaptively stopping the similarity check in

**Figure 2.3.** Distributions of Hamming Distance Calculations Before (left) and After (right) Retraining

a bit-serial manner. If a data point is incorrectly classified by the model, HD updates the model by (i) adding the incorrectly classified hypervector to the class the input data point belongs to  $(\tilde{C}^{correct} = C^{correct} + H)$ , and (ii) subtracting it from the class to which it is wrongly matched  $(\tilde{C}^{wrong} = C^{wrong} - H)$ . These changes are made to the full precision model saved from training because adding to and subtracting from the quantized model would drastically change the model. To update the quantized model, the updated class hypervectors from the integer model are quantized via the same process described in Section 2.3.1. Saving the full precision model does incur an overhead, but after retaining is complete, we can discard the full precision model.

#### **2.3.2** Inference with AdaptBit-HD

To support our bitserial hamming distance check, the query is quantized the same way as the class HVs. Then, AdaptBit-HD calculates the hamming distance between the first bit of the class HVs and the query HV across all the dimensions. We then check to see if the class with the highest similarity passes a threshold value. If the similarity threshold is passed, then execution can stop prematurely and output the current highest similarity class. However, if the

Figure 2.4. Effect of AdaptBit-HD Parameters on Accuracy

threshold is not passed, then computation continues to the next bit and the hamming distances are accumulated. We then check the if the similarity threshold is met again and if it is not, we continue the process. If the similarity threshold is not met and we are on the last bit, the most similar class is the output.

**Bitserial Thresholding** In order to support the bitserial hamming distance, we need to create a threshold for the termination condition. To do this, after the initial training, for the first iteration of retraining, we collect the hamming distance for all samples and the class HVs. Then, we get the mean and standard deviation of all samples where our model was correct as well as the mean and standard deviation of all samples where our model was incorrect. We, additionally, separate these distributions by each class, which allows us to set a threshold per class, rather than one global threshold. We then set the threshold to be the average between the *mean - standard deviation* of the incorrect distribution and the *mean + standard deviation* of the correct distribution. This heuristic makes sense to use because the threshold should separate the two distributions. As hamming distance calculates the number of mismatches, the incorrect

samples should be clustered with higher hamming distance values and the correct samples should be clustered in a lower distribution. Therefore, averaging in this way gives us a good initial threshold that separates the two distributions. We do this process on a per class basis as the distribution of similarity values differs on a per class basis, therefore, we need a different threshold for each class.

Figure 2.3 shows the distribution of hamming distances for all samples for a single class. The graph on the left shows our initial threshold value. However, the graph shows that the initial distributions are not completely separated by the threshold. To fix this, we modified the retraining algorithm to actively create a greater separation in order to minimize outputting the incorrect class when the threshold is met. To do this we made the following change: if the datapoint is correctly classified, rather than doing nothing, because we are correct, we additionally check if the similarity threshold was met. If the threshold is met with an additional 10% guard-band, we do nothing. However if the threshold is not met with an additional 10% guard-band, we add the query hypervector to the class the input data point belongs to ( $\tilde{\mathbf{C}}^{correct} = \mathbf{C}^{correct} + \mathbf{H}$ ). As Figure 2.3 shows on the graph to the right, after retraining the distribution of incorrectly classified and correctly classified samples are further separated leading to more accurate classification when we terminate the bitserial operation early. The 10% guard-band is to help ensure we push the distribution of correct samples past the threshold value. This leads to a more accurate model when terminating early based on the threshold. As Figure 2.3 shows, when the hamming distance passes the threshold, we can be confident that it is the correct class.