# **UCLA**

## **UCLA Electronic Theses and Dissertations**

#### **Title**

Charge Trap Transistors (CTT): Turning Logic Transistors into Embedded Non-Volatile Memory for Advanced High-k/Metal Gate CMOS Technologies

#### **Permalink**

https://escholarship.org/uc/item/50v725k7

#### **Author**

Khan, Faraz

#### **Publication Date**

2019

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA

Los Angeles

## **Charge Trap Transistors (CTT):**

# Turning Logic Transistors into Embedded Non-Volatile Memory for Advanced High-k/Metal Gate CMOS Technologies

A dissertation submitted in partial satisfaction

of the requirements for the degree

Doctor of Philosophy

in Electrical and Computer Engineering

by

Faraz Khan

#### ABSTRACT OF THE DISSERTATION

Charge Trap Transistors (CTT): Turning Logic Transistors into Embedded Non-Volatile

Memory for Advanced High-k/Metal Gate CMOS Technologies

by

#### Faraz Khan

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Los Angeles, 2020

Professor Jason C. S. Woo, Co-Chair

Professor Subramanian S. Iyer, Co-Chair

While need for embedded non-volatile memory (eNVM) in modern computing systems continues to grow rapidly, the options have been limited due to integration and scaling challenges as well as operational voltage incompatibilities. Introduced in this work is a unique multi-time programmable memory (MTPM) solution for advanced high-k/metal-gate (HKMG) CMOS technologies which turns as-fabricated standard logic transistors into eNVM elements, without the need for any process adders or additional masks. These logic transistors, when employed as eNVM elements, are dubbed "Charge Trap Transistors" (CTTs). The fundamental device physics, principles of operation, and technological breakthroughs required for employing

logic transistors as eNVM are presented. Implementation of CTT eNVM in 32 nm, 22 nm, 14 nm, and 7 nm production technologies has been realized and demonstrated in this work. The emerging memory technology landscape and the space that the CTT technology occupies therein are examined.

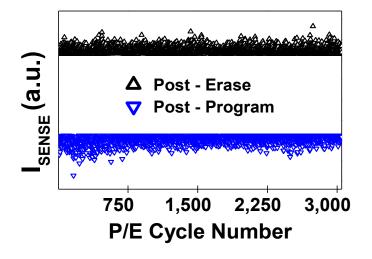

The motivation behind this work is to develop an eNVM technology that is completely process/mask-free, multi-time programmable, operable at low/logic-compatible voltages, scalable, and secure. The CTT technology satisfies all of the aforementioned criteria. CTTs offer a data retention lifetime of > 10 years at 125 °C and an operation temperature range of -55°-125° C. Hardware results demonstrate an endurance of > 10<sup>4</sup> P/E cycles which is more than adequate for most embedded applications. Hardware security enhancement, on-chip reconfigurable encryption, firmware, BIOS, chip ID, redundancy, repair at wafer and module test and in the field, performance tailoring, and chip configuration are a few of the applications of CTT eNVM. Moreover, the CTT array in its native (unprogrammed) state measures very well as an entropy source for potential PUF (Physically Unclonable Function) applications such as identification, authentication, anti-counterfeiting, secure boot, and cryptographic IP. In addition to the numerous digital applications, CTTs can also be utilized as an analog memory for applications like neuromorphic computing for machine learning (ML) and artificial intelligence (AI).

The dissertation of Faraz Khan is approved.

Chih-Kong Ken Yang

Yuanxun Wang

Jason C. S. Woo, Committee Co-Chair

Subramanian S. Iyer, Committee Co-Chair

University of California, Los Angeles

2020

# **DEDICATION**

To my wife Florence and my daughter Eliza

# TABLE OF CONTENTS

| Abstract of the Dissertationii                                                                         |

|--------------------------------------------------------------------------------------------------------|

| Dissertation Committee Approval                                                                        |

| Dedicationv                                                                                            |

| Table of Contentsvi                                                                                    |

| List of Illustrations viii                                                                             |

| Acknowledgmentsxv                                                                                      |

| VITAxvi                                                                                                |

| Chapter 1: Introduction 1                                                                              |

| 1.1 Motivation and Objectives                                                                          |

| 1.2 Dissertation Organization                                                                          |

| References                                                                                             |

| Chapter 2: Charge Trap Transistors (CTT): An Introduction and Overview 10                              |

| References                                                                                             |

| Chapter 3: Self-Heating Enhanced Charge Trapping and CTT Design Optimization 19                        |

| 3.1 Modulation of Self-Heating Enhanced Charge Trapping With Bias                                      |

| 3.2 Exploiting Device Layout-Dependent Effects for Modulation of Self-Heating Enhanced Charge Trapping |

| 3.3 Charge Injection Mechanism and the Charge Trapping Profile                                         |

| 3.4 Data Retention                                                | 33            |

|-------------------------------------------------------------------|---------------|

| 3.5 CTT OTPM Bitcell Architecture and Array Operation             | 40            |

| 3.6 Summary                                                       | 43            |

| References                                                        | 45            |

| Chapter 4: Charge Trap Transistors (CTT) as a Multi-Time Programm | able Embedded |

| Non-Volatile Memory                                               | 48            |

| 4.1 Principles of Operation                                       | 48            |

| 4.2 Program and Erase Optimization and Cycling                    | 53            |

| 4.3 "Self-heating Temperature Assisted eRase" (STAR)              | 56            |

| 4.4 Data Retention                                                | 60            |

| 4.5 Summary                                                       | 64            |

| References                                                        | 65            |

| Chapter 5: Modeling and Reliability Considerations                | 68            |

| 5.1 Modeling the CTT Characteristics                              | 68            |

| 5.2 Reliability Considerations                                    | 73            |

| 5.3 Summary                                                       | 78            |

| References                                                        | 79            |

| Chapter 6: Summary, Conclusions, and Outlook                      | 81            |

| References                                                        | 86            |

# LIST OF ILLUSTRATIONS

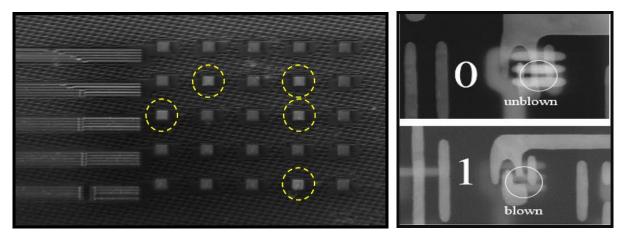

| Figure 1.1 | SEM voltage contrasting showing blown vs. unblown anti-fuses (left) and a blown                                                     |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|

|            | vs. unblown eFUSE (right), both in a 14 nm FinFET technology                                                                        |

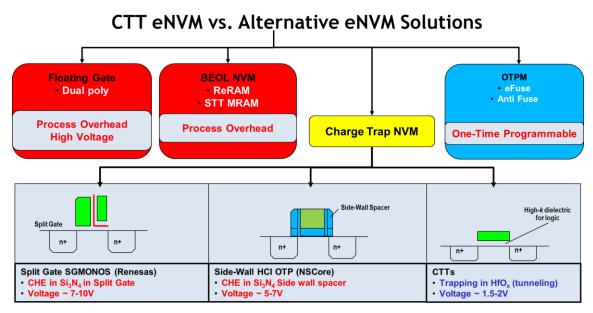

| Figure 1.2 | CTT eNVM vs. alternative eNVM solutions                                                                                             |

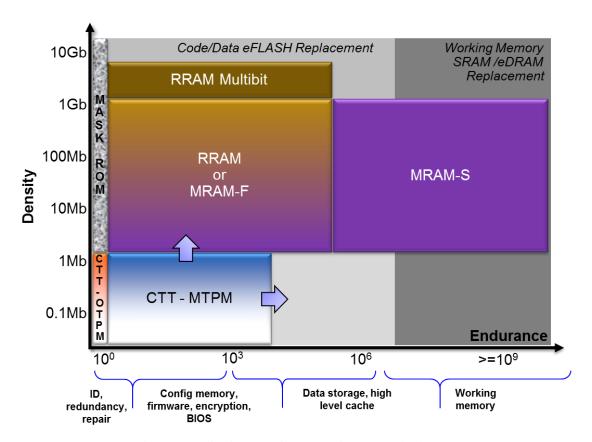

| Figure 1.3 | Application mapping: Emerging eNVM landscape                                                                                        |

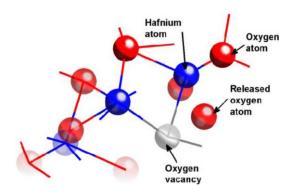

| Figure 2.1 | Oxygen vacancy in HfO <sub>2</sub> generated by oxygen atom dislocation from the HfO <sub>2</sub> molecule                          |

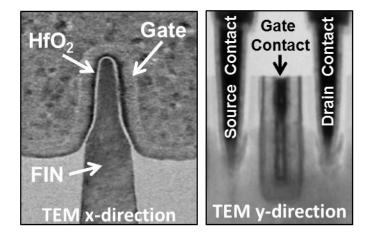

| Figure 2.2 | TEM cross-sections of a 14nm FinFET CTT in the x- and y- directions (perpendicular and parallel to the FIN direction, respectively) |

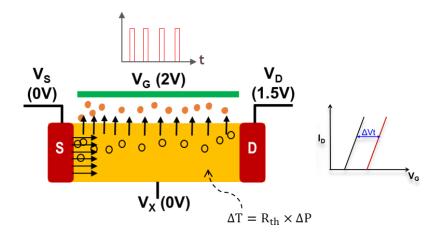

| Figure 2.3 | A schematic of the CTT programming operation                                                                                        |

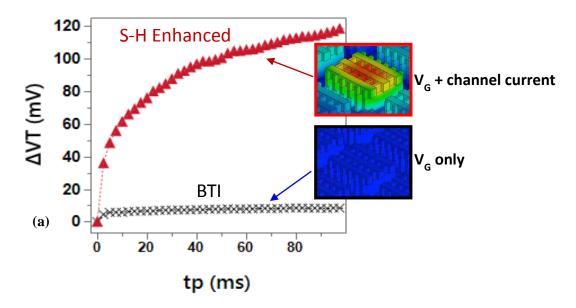

| Figure 2.4 | Measured $\Delta V_T$ from a CTT programmed with and without device self-heating                                                    |

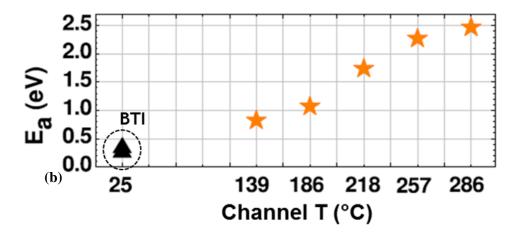

| Figure 2.5 | Measured charge de-trapping activation energies (E <sub>a</sub> ) for CTTs programmed at various device self-heating temperatures   |

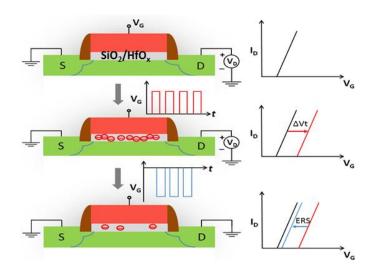

| Figure 2.6 | A schematic depicting the basic operation of a CTT memory device (equally applicable to planar FET as well as FinFET based CTTs)    |

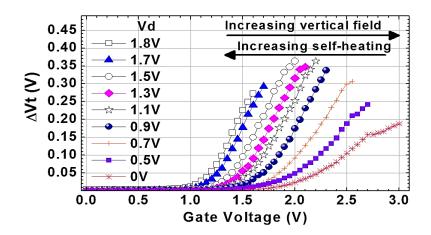

| Figure 3.1 | $\Delta V_T$ as a function of PVRS stress with 10ms pulses at various fixed $V_D$ values ( $W_{ch}$ =1.04 um, L=20 nm)              |

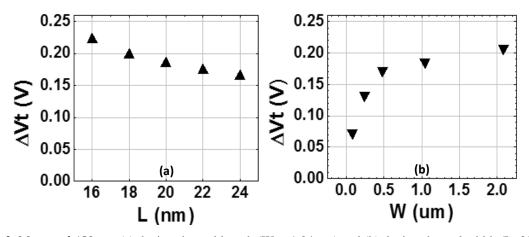

| Figure 3.2 | Measured $\Delta V_T$ vs. (a) device channel length (W <sub>ch</sub> =1.04 um) and (b) device channel width (L=20 nm)               |

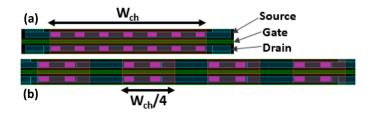

| Figure 3.3  | (a) Single-finger and (b) Multi-finger device layout                                                                                                                                                                                |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.4  | Steady-state thermal profiles for a (a) single-channel and (b) multi-channel device in the $W_{ch}$ direction, for an applied power of $4mW/um$                                                                                     |

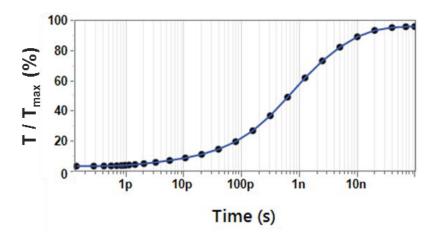

| Figure 3.5  | Rise in channel temperature vs. time for self-heating (4mW/um applied power)                                                                                                                                                        |

| Figure 3.6  | Measured $\Delta V_T$ vs. (a) applied power density and (b) channel T during programming                                                                                                                                            |

| Figure 3.7  | Top down views of (a) '1 gate × 12 fin', (b) '2 gate × 6 fin', (c) '1 gate × 12 fin' on active "island", and (d) '2 gate × 6 fin' on active "island" CTT bitcell layouts                                                            |

| Figure 3.8  | Rise in bitcell temperature vs. time during the program operation                                                                                                                                                                   |

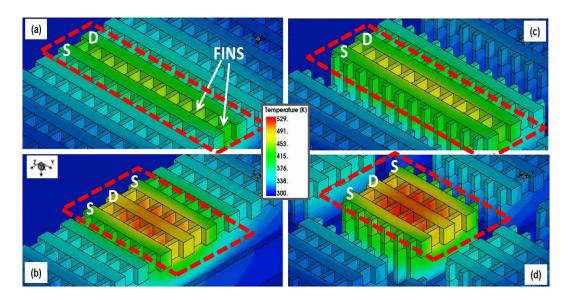

| Figure 3.9  | 3D finite element thermal simulation of the programming operation of CTT bitcell structures with (a) '1 gate×12 fin', (b) '2 gate×6 fin', (c) '1 gate×12 fin' on active "island", and (d) '2 gate×6 fin' on active "island" layouts |

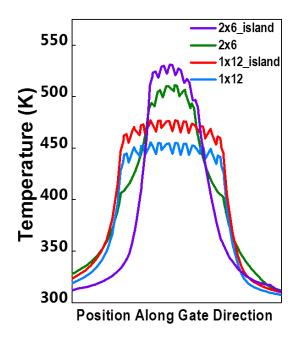

| Figure 3.10 | Thermal profiles, during programming, of the bitcell layouts shown in Fig. 3.9, along the gate direction                                                                                                                            |

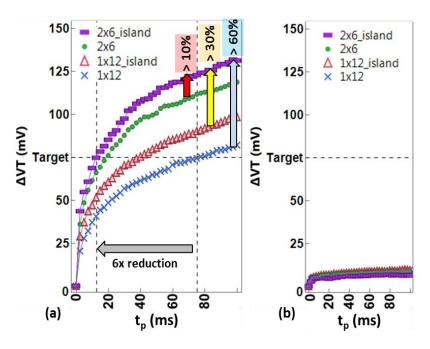

| Figure 3.11 | $\Delta V_T$ vs. $t_P$ for CTT bitcells with various layouts. The devices are programmed with (a) $V_G$ =2V, $V_D$ =1.4V, $V_S$ =0V and (b) $V_G$ =2V, $V_D$ = $V_S$ =0V                                                            |

| Figure 3.12 | Increase in charge injection current during programming vs. (a) applied power density and (b) channel T during the programming operation                                                                                            |

| Figure 3.13 | Reverse- vs. forward-mode distributions for linear and saturation (a) $V_T$ and (b) channel currents for 14 nm FinFET CTTs                                                                                                          |

| Figure 3.14 | Stochastic variation in standard deviation for normalized deltas between forward-                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | and reverse-mode reads for 14 nm FinFET CTTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 3.15 | Forward- and reverse-mode V <sub>T</sub> measured during a programming operation for 14 nm FinFET CTTs                                                                                                                                                                                                                                                                                                                                                                                                                                         |

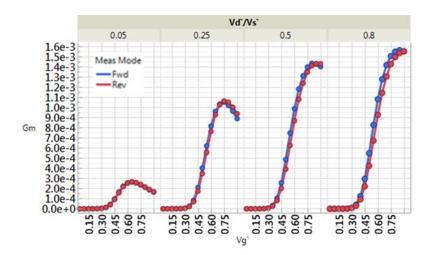

| Figure 3.16 | Device transconductance vs. $V_G$ (at various $V_D/V_S$ values) for forward- and reverse-mode reads for 14 nm FinFET CTTs                                                                                                                                                                                                                                                                                                                                                                                                                      |

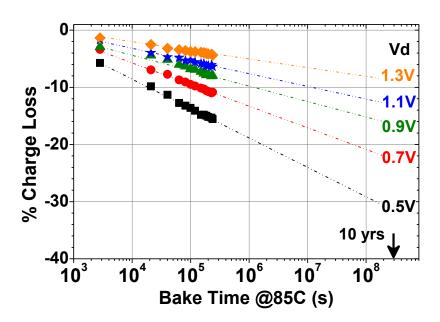

| Figure 3.17 | Percentage charge loss vs. bake time @ 85 °C, for identical devices programmed at various fixed drain biases (W <sub>ch</sub> =1.2 um, L=20 nm)                                                                                                                                                                                                                                                                                                                                                                                                |

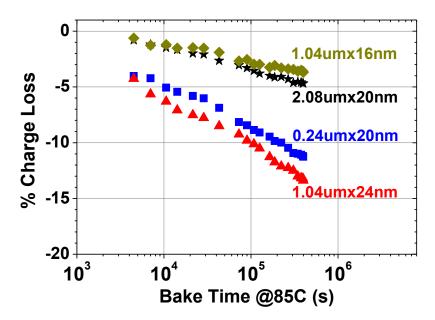

| Figure 3.18 | Percentage charge loss vs. bake time @ 85 °C, for devices with various dimensions ( $W_{ch}$ x L, as labelled) programmed at $V_D$ =1.5V                                                                                                                                                                                                                                                                                                                                                                                                       |

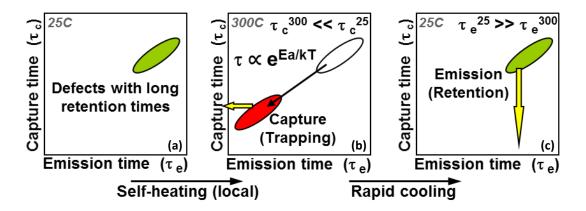

| Figure 3.19 | Schematic of 'Capture-Emission Time Maps' for self-heating assisted charge trapping. (a) Defects with long emission times / good retention also have long capture times, (b) Capture times are reduced at elevated temperatures, and (c) Rapid quenching retains charge in defects with long emission times at low temperatures.                                                                                                                                                                                                               |

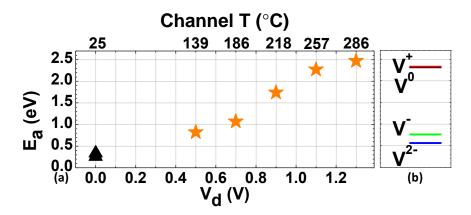

| Figure 3.20 | (a) Measured activation energies ( $E_a$ ) for charge detrapping after programming at various $V_D$ values (stars). Estimated channel temperatures (in °C) due to device self-heating during programming are indicated on the top scale. Measured $E_a$ values (triangles) for detrapping after trap filling in the absence of self-heating are shown for comparison. (b) Calculated thermal activation energies for detrapping for various charge states of $V_O$ in crystalline $m$ -HfO2, revealing values ranging from $0.56eV$ - $2.33eV$ |

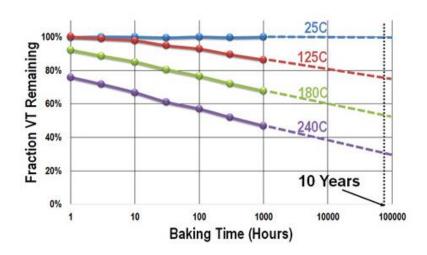

| Figure 3.21 | High-temperature data retention bake tests for 22 nm SOI CTTs. Hardware results show <25% charge loss after 10 years @ 125 °C                                                                                                                                                                                                                                                                                                                                                                                                                  |

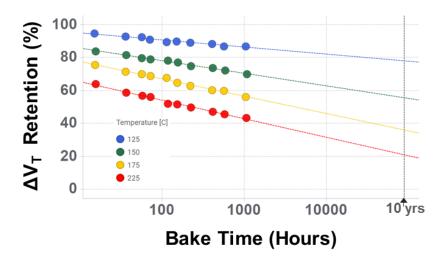

| Figure 3.22 | High-temperature data retention bake tests for 14 nm FinFET CTTs programmed                                                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | using $V_G$ =2V, $V_D$ =1.55V pulses. Hardware results show <25% charge loss after                                                                                                                                                                                                    |

|             | 10 years @ 125 $^{\circ}$ C. The charge detrapping activation energy (E <sub>a</sub> ), extracted using                                                                                                                                                                               |

|             | the conventional Arrhenius model, is ~1.85 eV                                                                                                                                                                                                                                         |

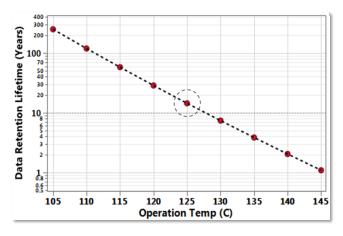

| Figure 3.23 | 14 nm FinFET CTT data retention lifetime projections for several operation temperatures                                                                                                                                                                                               |

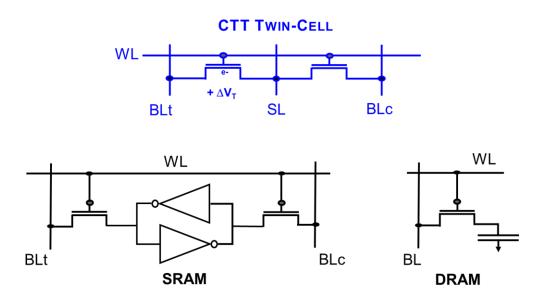

| Figure 3.24 | Schematic of the CTT twin-cell. Schematics of standard SRAM and DRAM bitcells are also shown for comparison                                                                                                                                                                           |

| Figure 3.25 | Schematics of the CTT OPTM bitcell in 'standby', 'program', and 'read' modes along with nominal operation conditions                                                                                                                                                                  |

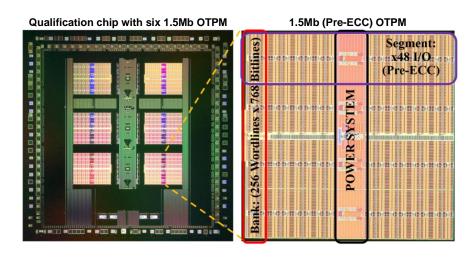

| Figure 3.26 | 9Mb (6×1.5Mb) CTT OTPM qualification chip photomicrographs                                                                                                                                                                                                                            |

| Figure 3.27 | Bitmaps of a 14 nm FinFET CTT OTPM array in its native state (unprogrammed) followed by a programmed state where a checkerboard pattern has been written                                                                                                                              |

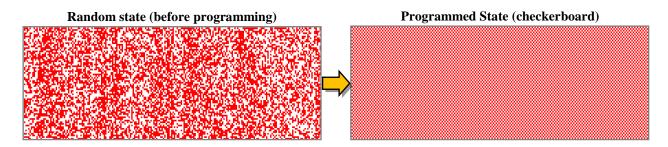

| Figure 4.1  | A schematic depicting the basic operation of a CTT memory device (equally applicable to planar FET as well as FinFET based CTTs)                                                                                                                                                      |

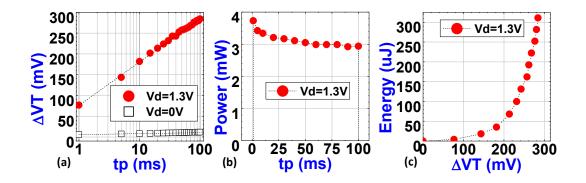

| Figure 4.2  | (a) $\Delta V_T$ vs. $t_P$ ( $V_G$ =2V, $V_D$ =1.3V). $\Delta V_T$ for PBTI @ 25°C ( $V_G$ =2V, $V_D$ =0V) is shown for comparison. (b) Power consumption vs. time during programming. (c) Total energy ( $E_p$ = $\int I_D \times V_D \times t_P$ ) required vs. target $\Delta V_T$ |

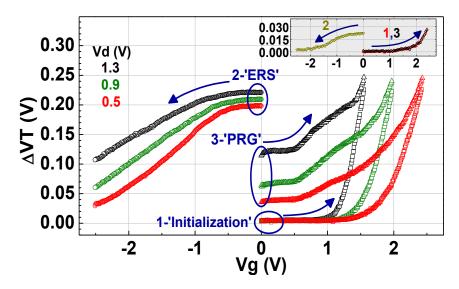

| Figure 4.3  | Measured $\Delta V_T$ during 1-'Initialization', 2-'ERS', and 3-'PRG' cycles for various $V_D$ values using PVRS. Inset shows $\Delta V_T$ for $V_D$ =0V PVRS stress (BTI)                                                                                                            |

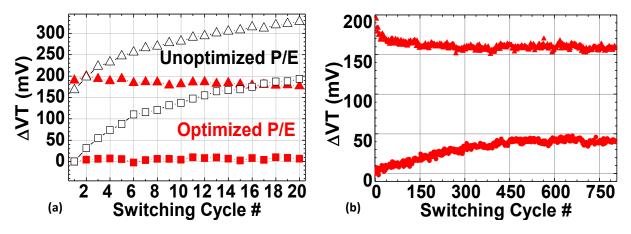

| Figure 4.4  | (a) Memory window vs. switching cycle number comparison between unoptimized P/E ( $V_{G-INIT}$ =2V, $V_{D-INIT}$ =1.3V, $V_{G-PRG}$ =2V, $V_{D-PRG}$ =1.3V, $V_{G-ERS}$ =-2V open black symbols) and optimized ( $V_{G-INIT}$ =2V, $V_{D-INIT}$ =1.3V, $V_{G-PRG}$ =2V $V_{D-PRG}$ =1.2V, $V_{G-ERS}$ =-2V, solid red symbols) P/E conditions. (b) 800× P/E cycles using optimized P/E conditions. |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.5  | 14nm FinFET CTT P/E cycling using (a) Unoptimized conditions and (b) optimized programming conditions with 'initialization' and program verify                                                                                                                                                                                                                                                     |

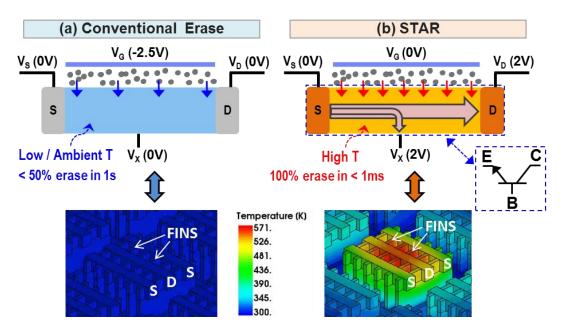

| Figure 4.6  | Schematic showing (a) conventional erase and (b) "Self-heating Temperature Assisted eRase" (STAR). Corresponding thermal profiles of the bitcells during the erase operations are also shown for comparison                                                                                                                                                                                        |

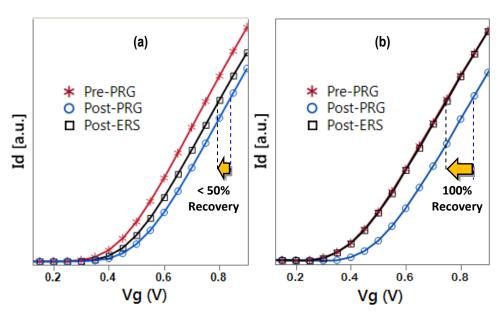

| Figure 4.7  | Measured Pre-Program, Post-Program, and Post-Erase I <sub>D</sub> -V <sub>G</sub> data with (a) conventional erase and (b) STAR                                                                                                                                                                                                                                                                    |

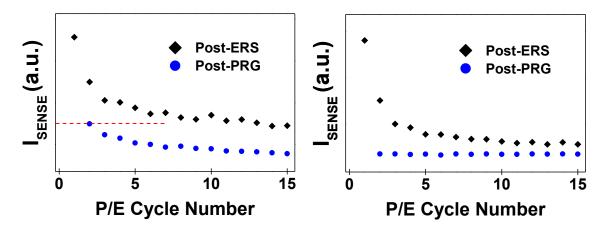

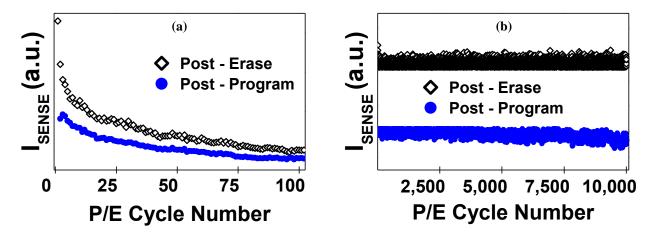

| Figure 4.8  | P/E cycling of 14 nm FinFET CTTs using (a) conventional erase and (b) STAR                                                                                                                                                                                                                                                                                                                         |

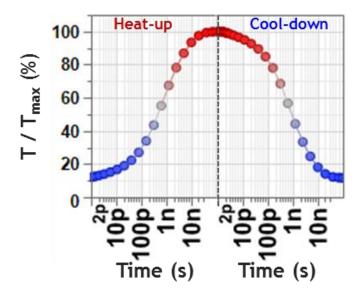

| Figure 4.9  | Transient bitcell temperature vs. time for self-heating (during erase) and subsequent cool-down                                                                                                                                                                                                                                                                                                    |

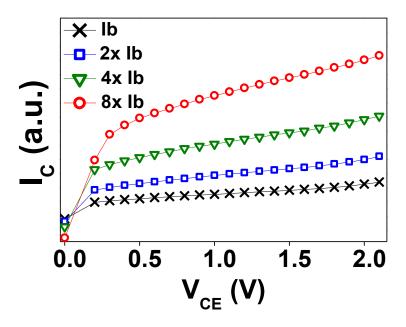

| Figure 4.10 | Measured I-V characteristics of the parasitic BJT (described in Fig 4.6(b))                                                                                                                                                                                                                                                                                                                        |

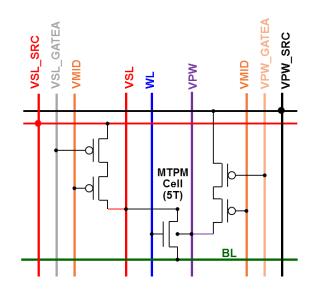

| Figure 4.11 | STAR enabled CTT bitcell design and typical operation conditions in 14 nm FinFET technology                                                                                                                                                                                                                                                                                                        |

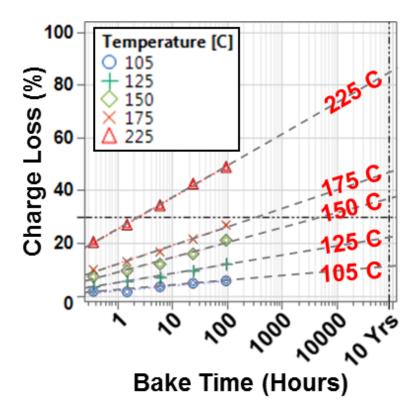

| Figure 4.12 | High-temperature data retention bake tests showing a charge loss of <25% ir years at 125 °C                                                                                                                                                                                                                                                                                                        |

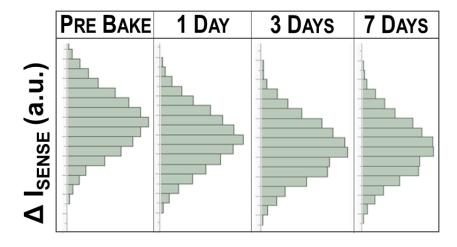

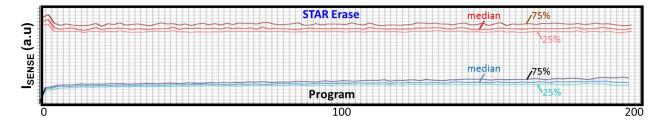

| Figure 4.13 | $\Delta$ I <sub>SENSE</sub> distributions in a 9kb CTT array baked at 125 °C, for up to 7 days 61                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

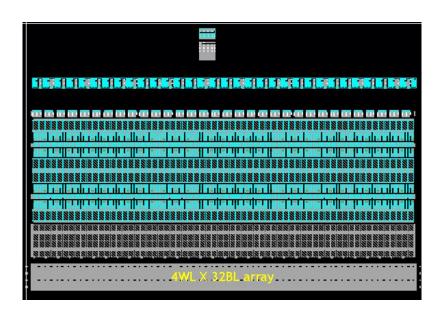

| Figure 4.14 | A 14 nm FinFET CTT array and P/E cycling using STAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

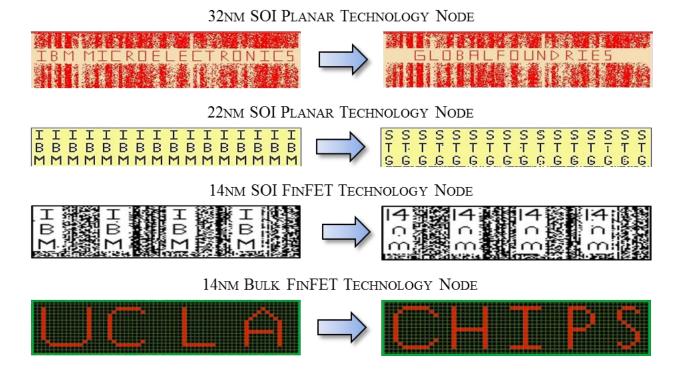

| Figure 4.15 | Fully functional CTT eNVM arrays integrated in 32 nm SOI, 22 nm SOI, 14 nm SOI, and 14 nm bulk technology platforms: Bit patterns are written followed by an erase and re-write of alternate bit patterns                                                                                                                                                                                                                                                                                                                 |

| Figure 4.16 | P/E cycling of 7 nm FinFET CTTs using STAR 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

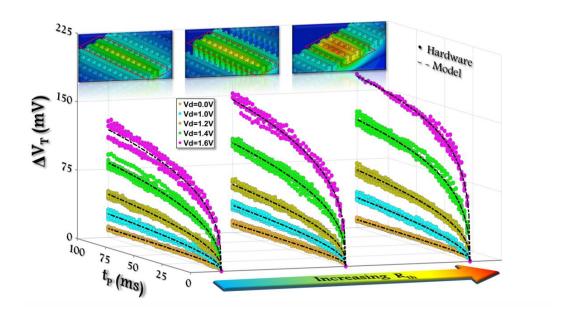

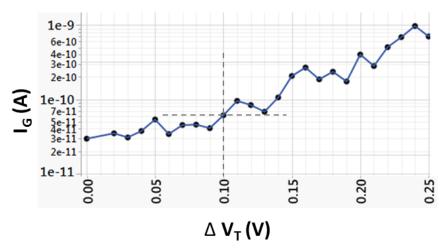

| Figure 5.1  | $\Delta V_T$ vs. $t_P$ measured from different bitcell designs (shown above their respective datasets) programmed using (a) various $V_D$ , $V_G$ =2V and (b) various $V_G$ , $V_D$ =1.4V (hardware data: colored dots, model: black dashed lines)                                                                                                                                                                                                                                                                        |

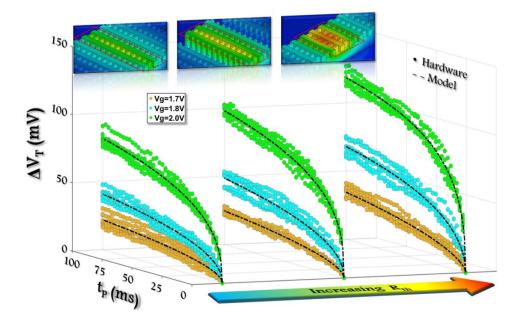

| Figure 5.2  | (a) Temperature dependence of 'A' and (b) V <sub>G</sub> dependence of 'A'                                                                                                                                                                                                                                                                                                                                                                                                                                                |

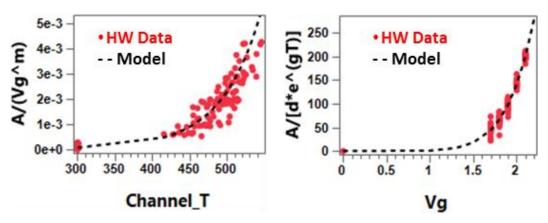

| Figure 5.3  | Off-state gate leakage current measured as a function of the CTT threshold voltage shift ( $\Delta V_T$ )                                                                                                                                                                                                                                                                                                                                                                                                                 |

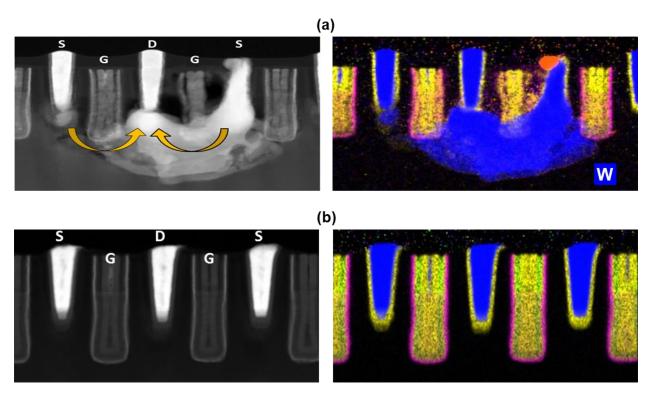

| Figure 5.4  | (a) TEM cross-section of a 14 nm FinFET CTT showing electromigration of the source contact metal (W). The electron current flows during the STAR operation are depicted by arrows. (b) A TEM cross section of a 14 nm FinFET CTT, cycled 10 <sup>4</sup> times using the AC-STAR technique, demonstrating no signs of electromigration. The bright regions in the left-side images are W. Elemental analyses of the respective cross-sections are shown in the right-side images wherein the W is displayed in blue color |

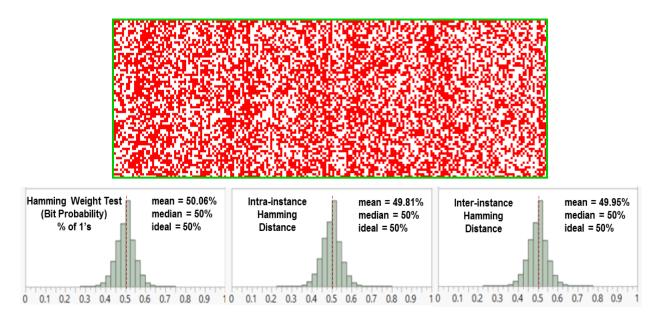

| Figure 6.1  | (Top panel) A 14 nm FinFET CTT array in its native state. (Bottom panel) Hamming weight, intra-instance hamming distance, and inter-instance hamming distance all show a nearly ideal entropy source. Tests were performed on 354 Mb of data from 59 different chips                                                                                                                                                                                                                                                      |

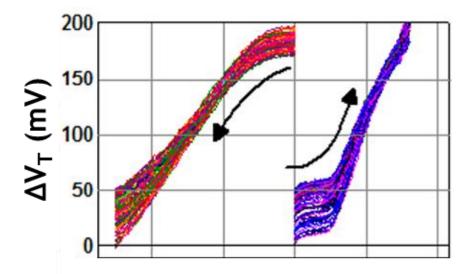

| Figure 6.2 | Demonstration of the CTT as an analog memory. $\Delta V_T$ is modulated back and        |

|------------|-----------------------------------------------------------------------------------------|

|            | forth, 1000 times, between 0 and ~200mV in ~2mV increments. Each small do               |

|            | represents a unique $\Delta V_T$ level and each color represents a different program of |

|            | erase cycle                                                                             |

#### **ACKNOWLEDGEMENTS**

I take this opportunity to express my sincere gratitude to my advisors Prof. Subramanian Iyer and Prof. Jason Woo for their invaluable guidance throughout my research work. Their constructive feedback, encouragement, and patience have been the driving forces for the successful completion of my research and dissertation.

I thank Prof. Ken Yang and Prof. Ethan Wang for providing a critical review of this work and for serving as members of my dissertation committee.

I am deeply grateful to Dr. DP Prakash (Global Head of Innovation, AI ML AR VR, CIO office at GLOBALFOUNDRIES) for his guidance and mentorship. I thank him for always taking time out for me despite his very busy schedule, encouraging me, and offering invaluable advice whenever I needed it the most.

I would like to express my sincere appreciation to Dr. Eduard Cartier (Research Staff Member at IBM T.J Watson Research Center) for his guidance and counsel. He always shared his vast technical knowledge, expertise, and experience to help me throughout my research work.

I am thankful to the management team at GLOBALFOUNDRIES, especially Mr. Norman Robson, Mr. Toshiaki Kirihata, and Mr. Daniel Berger, for supporting my research work and providing me with the necessary resources from conception to realization of the CTT eNVM technology.

I would like to thank DARPA and DMEA for their funding and support of this work.

I would like to especially thank my friend Dr. Gaurav Saraf for his encouragement and advice at every step of the way and for sharing his technical expertise throughout the course of my research work.

I express my deep sense of gratitude to my parents, my brother, and my sister for their never ending love and moral support. And finally, I thank my wife with all the appreciation in the world for always believing in me, for always being patient with me, and for never letting me give up.

#### **VITA**

#### PATENTS AND PUBLICATIONS

- F. Khan et al., "CHARGE TRAP MEMORY DEVICES", U.S. Patent application # 16/781,527.

- <u>F. Khan</u> et al., "PROGRAM AND ERASE MEMORY STRUCTURES", U.S. Patent application # 16/047,529.

- <u>F. Khan</u>, "Charge Trap Transistors (CTT): A Process/Mask-Free Secure Embedded Non-Volatile Memory for 14 nm FinFET Technologies and Beyond", *Microelectronics Reliability and Qualification Workshop (MRQW)*, 2020 (Invited).

- <u>F. Khan</u>, D. Moy, D. Anand, E. Hunt-Schroeder, R. Katz, L. Jiang, E. Banghart, N. Robson, T. Kirihata, "Turning Logic Transistors into Secure, Multi-Time Programmable, Embedded Non-Volatile Memory Elements for 14 nm FINFET Technologies and Beyond", *IEEE Symp. VLSI Technology*, Kyoto, Japan, 2019.

- <u>F. Khan</u>, M. Han, D. Moy, R. Katz, L. Jiang, E. Banghart, N. Robson, T. Kirihata, J. C. S. Woo, S. S. Iyer, "Design Optimization and Modeling of Charge Trap Transistors (CTTs) in 14 nm FinFET Technologies", *IEEE EDL*, 2019.

- <u>F. Khan</u>, E. Hunt-Schroeder, D. Moy, D. Anand, R. Katz, D. Leu, John Fifield, N. Robson, S. Ventrone, T. Kirihata, "A Multi-Time Programmable Embedded Memory Technology in a Native 14nm FINFET Process using Charge Trap Transistors (CTTs)," *GOMACTech*, 2019.

- <u>F. Khan</u>, E. Cartier, J. C. S. Woo, S. S. Iyer, "Charge Trap Transistor (CTT): An Embedded Fully Logic-Compatible Multiple-Time Programmable Non-Volatile Memory Element for High-*k*-Metal-Gate CMOS Technologies", *IEEE EDL*, 2017.

- <u>F. Khan</u>, E. Cartier, C. Kothandaraman, J. Campbell, J. Woo, S. S. Iyer, "The Impact of Selfheating on Charge Trapping in High-*k*-metal-gate nFETs", *IEEE EDL*, 2016.

- E. Hunt-Schroeder, D. Anand, D. Pontius, M. Roberge, D. Moy, E. Banghart, N. Robson,

<u>F. Khan</u>, T. Kirihata, S. Ventrone, "Design and Development Challenges of Charge Trap Transistor Memories", *GOMACTech*, 2020.

- E. Hunt-Schroeder, D. Anand, J. Fifield, M. Roberge, D. Pontius, M. Jacunski, K. Batson, M. Deming, <u>F. Khan</u>, D. Moy, A. Cestero, R. Katz, Z. Chbili, E. Banghart, J. Liu, B. Jayaraman, R. Tummuru, R. Raghavan, A. Mishra, N. Robson, T. Kirihata, "14nm FinFET 1.5Mb Embedded High-K Charge Trap Transistor One Time Programmable Memory Using Differential Current Sensing", *IEEE SSC-L*, 2019.

- B. Jayaraman , D. Leu, J. Viraraghavan, A. Cestero, M. Yin, J. Golz, R. Tummuru, R. Raghavan, D. Moy, T. Kempanna, <u>F. Khan</u>, T. Kirihata, S. S. Iyer, "80-kb Logic Embedded High-K Charge

Trap Transistor-Based Multi-Time-Programmable Memory With No Added Process Complexity", *IEEE JSSC*, 2018.

- J. Viraraghavan, D. Leu, B. Jayaraman, A. Cestero, R. Kilker, M. Yin, J. Golz, R. R. Tummuru, R. Raghavan, D. Moy, T. Kempanna, <u>F. Khan</u>, T. Kirihata, S. S. Iyer, "80Kb 10ns read cycle logic Embedded High-K charge trap Multi-Time-Programmable Memory scalable to 14nm FIN with no added process complexity", *IEEE Symp. VLSI Circuits*, 2016.

- C. Kothandaraman, X. Chen, D. Moy, D. Lea, S. Rosenblatt, <u>F. Khan</u>, D. Leu, T. Kirihata, D. Ioannou, G. LaRosa, J. B. Johnson, N. Robson, S. S. Iyer, "Oxygen vacancy traps in Hi-K/Metal gate technologies and their potential for embedded memory applications", *IEEE IRPS*, 2015.

- C. Kothandaraman, X. Chen, D. Moy, D. Lea, D. Leu, S. Rosenblatt, <u>F. Khan</u>, N. Robson, T. Kirihata, S. S. Iyer, "A secure CMOS compatible re-programmable memory element for code storage applications", *GOMACTech*, 2015.

- X. Yang, C. Ku, <u>F. Khan</u>, P. I. Reyes, C. Kuo, Y. Lu, "Sputtering of ZnO Thin Films for TFT on Polyimide Substrates", *Electronic Materials Conference*, 2010.

- C. Ku, P. I. Reyes, C. Kuo, <u>F. Khan</u>, "Annealing effects on ZnO TFTs grown by MOCVD", 6<sup>th</sup> *International Workshop on ZnO and Related Materials*, 2010.

#### **EMPLOYMENT**

### Technologist, 3D Memory R&D

Western Digital (SanDisk), Milpitas, CA Dec 2019 – Present

#### Member of Technical Staff, Advanced Technology Development

GlobalFoundries, East Fishkill, NY Jul 2015 – Dec 2019

#### Staff Scientist, Device Engineering + BEOL Technology Development

IBM, East Fishkill, NY Nov 2011 – Jul 2015

#### Researcher

Microelectronic Research Lab (MERL), Rutgers University, Piscataway, NJ Feb 2009 – Nov 2011

#### **Lead Product Engineer, NAND Flash + DRAM**

Micron Technology, Inc., Manassas, VA Feb 2005 – Feb 2009

#### 1. Introduction

#### 1.1 MOTIVATION AND OBJECTIVES

The availability of on-chip non-volatile memory for advanced high-k/metal gate (HKMG) CMOS technology nodes has been constrained by integration and scaling challenges as well as operational voltage incompatibilities, while its need continues to grow rapidly in modern computing systems. Existing embedded memory solutions for HKMG CMOS technologies such as eFUSE [1], [2] and gate breakdown anti-fuse [3], [4] are one-time programmable and face scaling challenges. 1T1R eFUSE solutions, while operable at logic-compatible voltages, require a high current during the programming operation due to which the cell size must be several times larger than that of a logic transistor making them intangible for high density applications. eFUSEs therefore do not scale well in advanced and FinFET process technologies and when larger capacity one-time programmable memory (OTPM) is needed, the required area can be considerable. With the transition from traditional polysilicon-gate CMOS logic process to HKMG CMOS logic process in advanced technology nodes, the polysilicon eFUSE has been replaced by metal fuses, where the fuses are continuous metal shapes etched on the silicon surface. eFUSEs operate on the principle of electromigration (EM) and are programmed at the time of manufacturing: application of high voltages to selected fuse metal lines causes EM and subsequently disconnects (opens) the metal lines. However, eFUSEs suffer from high leakage current in the standby mode and from re-growth issues where the same electromigration that causes the metal lines to disconnect can also result in the metal lines to unintentionally connect again, changing the data intended to be stored. On the other hand, the anti-fuse technology employs an oxide-breakdown technique known to offer higher densities at the cost of using high

voltages (>4V) which may be outside some technology limits or pose EMIR (electromigration/IR drop) concerns to periphery circuits due to the required high-density current flows. Additionally, reliably (irreversibly) breaking down ultra-thin gate oxides is becoming increasingly challenging, posing an additional constraint for anti-fuse technology scaling. Other solutions such as split-gate (SG) MONOS [5] and floating-gate (FG) type eFLASH [6], [7], [8] are multi-time programmable but require significant amount of additional masks and processing and require high voltages (up to ~10V) to operate. Moreover, scaling of FG eFLASH into FinFET technologies is unlikely due to significant process complexity and integration challenges. Emerging memory technologies such as MRAM [9], [10], [11], ReRAM [12], and PCM [13], [14], while multi-time programmable and generally operable at logic compatible voltages, require additional complex processes and masks.

The motivation of this work is to develop a multi-time programmable embedded non-volatile memory (eNVM) technology that is completely process-free/mask-free, operable at logic-compatible voltages (~2V), and scalable. The CTT technology, a novel multi-time programmable memory (MTPM) solution for advanced HKMG CMOS technology nodes which turns as-fabricated standard logic transistors into eNVM elements, satisfies all of the aforementioned criteria. While each of the technologies discussed earlier has its advantages and disadvantages, it must be noted that CTT is the only eNVM technology that is completely process- and mask-free i.e. it requires no additional processes or masks: this presents a significant time to market and cost advantage over all other memory technologies. Additionally, CTT eNVM offers a secure solution for data and hardware security. Data stored in eFUSE and anti-fuse memories can be reverse engineered (Fig. 1.1) using SEM voltage contrasting. On the

other hand, data stored as trapped charge in a very thin dielectric (physical thickness to the order of ~ 1 nm or less) is very secure from reverse engineering and security attacks.

Fig. 1.1. SEM voltage contrasting showing blown vs. unblown anti-fuses (left) and a blown vs. unblown eFUSE (right), both in a 14 nm FinFET technology.

Potential applications of the CTT technology include hardware security, on-chip reconfigurable encryption, firmware, BIOS, chip ID, configuration memory, redundancy, repair at wafer and module test and in the field, and performance tailoring. Moreover, the CTT array in its native (unprogrammed) state measures very well as an entropy source for potential PUF (Physically Unclonable Function) applications such as identification, authentication, anti-counterfeiting, secure boot, and cryptographic IP. In addition to the numerous digital applications, CTTs can also be utilized as an analog memory for machine learning (ML) and artificial intelligence (AI) applications. A comparison between the various eNVM solutions and the CTT is shown in Fig. 1.2; The CTT is the only eNVM technology that is completely process-free / mask-free and multi-time programmable, operable at logic compatible voltages, secure, and scalable in bulk/SOI/FIN technologies. Given the eFLASH complexity and scaling challenges and no clear roadmap to sub-28 nm nodes, eFLASH replacement technologies are needed. A snapshot of the eNVM landscape and the emerging technologies for potential

replacement of eFLASH for code/data storage and SRAM/eDRAM for working memory in 14 nm technology nodes and beyond, and where the CTT eNVM technology fits therein, is depicted in Fig. 1.3.

The objective of this work is to introduce the fundamental device physics and principles of operation of CTTs and to demonstrate viability of the CTT eNVM technology for advanced HKMG CMOS technology nodes. Also introduced are the technological breakthroughs required for employing CTTs as a commercially viable multi-time programmable eNVM technology, along with design and reliability considerations. Implementation of CTT eNVM in 32nm, 22nm, 14nm, and 7nm production technologies has been realized and demonstrated in this work.

Fig. 1.2. CTT eNVM vs. alternative eNVM solutions.

Fig. 1.3. Application mapping: Emerging eNVM landscape.

#### 1.2 DISSERTATION ORGANIZATION

The motivation and objectives of this work are discussed in Chapter 1. Chapter 2 provides an introduction to and overview of the Charge Trap Transistor (CTT) eNVM technology for advanced HKMG CMOS technology nodes. A detailed discussion on the fundamental principles of operation of the CTT and its implementation as a one-time programmable memory (OTPM) is included in Chapter 3. The fundamental understanding and technological breakthroughs required for employing CTTs as a multi-time programmable memory (MTPM) are presented in Chapter 4. In Chapter 5, a compact model that can be used to accurately characterize and predict the behavior of CTTs and reliability considerations in the CTT eNVM technology are discussed. A summary of this work and corresponding conclusions and outlook are presented in Chapter 6.

#### REFERENCES

- [1] C. Kothandaraman, S. K. Iyer and S. S. Iyer, "Electrically programmable fuse (eFUSE) using electromigration in silicides," *IEEE Electron Device Lett.*, vol. 23, no. 9, pp. 523–525, Sep. 2002.

- [2] S. H. Kulkarni, Z. Chen, B. Srinivasan, B. Pedersen, U. Bhattacharya and K. Zhang, "Low-Voltage Metal-Fuse Technology featuring a 1.6V-Programmable 1T1R Bit Cell with an Integrated 1V Charge Pump in 22nm Tri-gate process," *IEEE Symp. VLSI Technol. Dig. Tech. Papers*, 2015, pp. C174-C175.

- [3] S.-Y. Chou, Y.-S. Chen, J.-H. Chang, Y.-D. Chih and T.-Y. Chang, "A 10nm 32Kb Low-Voltage Logic-Compatible Anti-Fuse One-Time-Programmable Memory with Anti-Tampering Sensing Scheme," *IEEE ISSCC*, 2017, pp. 200-202.

- [4] Y. Liu, M. H. Chi, A. Mittal, G. Aluri, S. Uppal, P. Paliwoda, E. Banghart, K. Korablev, B. Liu, M. Nam, M. Eller and S. Samavedam, "Anti-Fuse Memory Array Embedded in 14nm FinFET CMOS with Novel Selector-Less Bit-Cell Featuring Self-Rectifying Characteristics," *IEEE Symp. VLSI Technol. Dig. Tech. Papers*, 2014.

- [5] S. Tsuda, T. Saito, H. Nagase, Y. Kawashima, A. Yoshitomi, S.Okanishi, T. Hayashi, T. Maruyama, M. Inoue, S. Muranaka, S. Kato, T. Hagiwara, H. Saito, T. Yamaguchi, M. Kadoshima, T. Maruyama, T. Mihara, H.Yanagita, K. Sonoda, T. Yamashita and Y. Yamaguchi, "Reliability and Scalability of FinFET Split-Gate MONOS Array with Tight Vth Distribution for 16/14nm-node Embedded Flash," *IEEE IEDM*, 2017, pp. 19.3.1–19.3.4.

- [6] R. Richter, M. Trentzsch, S. Dünkel, J. Müller, P. Moll, B. Bayha, K. Mothes, A. Henkel, M. Mazur, J. Paul, P. Krottenthaler, J. Poth, S. Jansen, R. Hüselitz, H. Kim, A. Zaka, T. Herrmannl, E.M. Bazizi, S. Beyer, P. Ghazavi, H. Om'mani, S. Lemke, Y. Tkachev, F. Zhou, J. Kim, X. Liu, V. Tiwari and N. Do, "A cost-efficient 28nm split-gate eFLASH memory featuring a HKMG hybrid bit cell and HV device," *IEEE IEDM*, 2018, pp. 428-431.

- [7] Y. K. Lee, C. Jeon, H. Min, B. Seo, K. Kim, D. Kim, K. Min, J.S. Woo, H. Kang, Y.S. Chung, M. Kim, J. Jang, K.S. Yeom, J.-S. Kim, M.H. Oh, H. Lee, S. Cho and D. Lee, "High-Speed and Logic-Compatible Split-Gate Embedded Flash on 28-nm Low-Power HKMG Logic Process," *IEEE Symp. VLSI Technol. Dig. Tech. Papers*, 2017, pp. T202-T203.

- [8] C. Jeon, J. Woo, K. Yeom, M. Seo, E. Hong, Y. Jeong, S. Lee, H. Min, D.H. Kim, H.C. Lee, S. Cho, M.H. Oh, J.-S. Kim, H. Lee, J.C. Park, C. Kim, H.J. Sung, S. Yoon, J. Kim, Y. K. Lee, K. C. Park, G. Jeong, J. Yoon and E.S. Jung, "High-speed and Ultra-low Power IoT One-chip (MCU + Connectivity-chip) on a Robust 28-nm Embedded Flash Process," *IEEE Symp. VLSI Technol. Dig. Tech. Papers*, 2019, pp. T114-T115.

- [9] K. Lee, K. Yamane, S. Noh, V. B. Naik, H. Yang, S. H. Jang, J. Kwon, B. Behin-Aein, R. Chao, J. H. Lim, S. K., K. W. Gan, D. Zeng, N. Thiyagarajah, L. C. Goh, B. Liu, E. H. Toh, B. Jung, T. L. Wee, T. Ling, T. H. Chan, N. L. Chung, J. W. Ting, S. Lakshmipathi, J. S. Son, J. Hwang, L. Zhang, R. Low, R. Krishnan, T. Kitamura, Y. S. You, C. S. Seet, H. Cong, D. Shum, J. Wong, S. T. Woo, J. Lam, E. Quek, A. See and S. Y. Siah, "22-nm FD-SOI Embedded MRAM with Full Solder Reflow Compatibility and Enhanced Magnetic Immunity," *IEEE VLSI Technol. Dig. Tech. Papers*, 2018, pp. 183-184.

- [10] K. Nishioka, H. Honjo, S. Ikeda, T. Watanabe, S. Miura, H. Inoue, T. Tanigawa, Y. Noguchi, M. Yasuhira, H. Sato and T. Endoh, "Novel Quad interface MTJ technology and its first demonstration with high thermal stability and switching efficiency for STT-MRAM beyond 2Xnm," *IEEE Symp. VLSI Technol. Dig. Tech. Papers*, 2019, pp. T120-T121.

- [11] O. Golonzka, J. -G. Alzate, U. Arslan, M. Bohr, P. Bai, J. Brockman, B. Buford, C. Connor, N. Das, B. Doyle, T. Ghani, F. Hamzaoglu, P. Heil, P. Hentges, R. Jahan, D. Kencke, B. Lin, M. Lu, M. Mainuddin, M. Meterelliyoz, P. Nguyen, D. Nikonov, K. O'brien, J. ODonnell, K. Oguz, D. Ouellette, J. Park, J. Pellegren, C. Puls, P. Quintero, T. Rahman, A. Romang, M. Sekhar, A. Selarka, M. Seth, A. J. Smith, A. K. Smith, L. Wei, C. Wiegand, Z. Zhang and K. Fischer, "MRAM as Embedded Non-Volatile Memory Solution for 22FFL FinFET Technology," *IEEE IEDM*, 2018, pp. 412-415.

- [12] O. Golonzka, U. Arslan, P. Bai, M. Bohr, O. Baykan, Y. Chang, A. Chaudhari, A. Chen, J. Clarke, C. Connor, N. Das, C. English, T. Ghani, F. Hamzaoglu, P. Hentges, P. Jain, C. Jezewski, I. Karpov, H. Kothari, R. Kotlyar, B. Lin, M. Metz, J. ODonnell, D. Ouellette, J. Park, A. Pirkle, P. Quintero, D. Seghete, M. Sekhar, A. Sen Gupta, M. Seth, N. Strutt, C. Wiegand, H. J. Yoo and K. Fischer, "Non-Volatile RRAM Embedded into 22FFL FinFET Technology," *IEEE Symp. VLSI Technol. Dig. Tech. Papers*, 2019, pp. T230-T231.

- [13] F. Arnaud *et al.*, "Truly Innovative 28nm FDSOI Technology for Automotive Micro-Controller Applications embedding 16MB Phase Change Memory," *IEEE IEDM*, 2018, pp. 424-427.

- [14] P. Zuliani, A. Conte and P.Cappelletti, "The PCM way for embedded Non Volatile Memories applications," *IEEE Symp. VLSI Technol. Dig. Tech. Papers*, 2019, pp. T192-T193.

## 2. CHARGE TRAP TRANSISTORS (CTT): AN INTRODUCTION AND OVERVIEW

HfO<sub>2</sub> used as gate dielectric in high-k/metal gate (HKMG) CMOS technologies is known to have oxygen vacancy (Fig. 2.1) related charge traps [1], [2], [3]. An oxygen vacancy is a thermo-dynamic point defect caused by the diffusion of oxygen from HfO2, which leaves behind a positively charged vacancy defect [4]. It is also known that bias stress induced charge trapping and defect generation in HfO<sub>2</sub> are strongly accelerated by temperature [5], [6]. While charge trapping in HfO<sub>2</sub> is typically considered to be a nuisance, as it is a source of variability in devices and in turn circuits, it is demonstrated in this work that this propensity for charge trapping in HfO<sub>2</sub> can indeed be utilized as a feature for embedded non-volatile memory (eNVM) applications in HKMG CMOS technologies. Charge trapping in high-k dielectrics such as HfO<sub>2</sub> for non-volatile memory (NVM) applications has been proposed before. In this work, however, it is shown that charge trapping in HfO<sub>2</sub> can be exploited for turning as-fabricated standard logic transistors into multi-time programmable (MTP) non-volatile memory elements that operate at logic compatible voltages without the need for any additional processes or masks: the fundamental device physics, principles of operation, and technological breakthroughs required are introduced. It is demonstrated that application of appropriate, logic compatible, voltages that are higher than nominal ( $\sim 0.9$ V) can lead to enhanced charge trapping in the high-k gate dielectric material of HKMG logic transistors, resulting in threshold voltage shifts ( $\Delta V_T$ ) that are large and stable enough to be utilized as a non-volatile data storage mechanism. These asfabricated standard logic transistors, when employed as eNVM elements, are dubbed "Charge Trap Transistors" (CTTs). In other words, CTTs are simply as-fabricated, standard HKMG CMOS logic transistors (Fig. 2.2) operated in an enhanced charge trapping mode.

Fig. 2.1. Oxygen vacancy in HfO<sub>2</sub> generated by oxygen atom dislocation from the HfO<sub>2</sub> molecule [4].

Fig. 2.2. TEM cross-sections of a 14nm FinFET CTT in the x- and y- directions (perpendicular and parallel to the FIN direction, respectively).

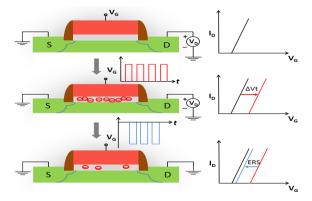

The fundamental principle of operation for programming CTTs is 'device self-heating enhanced charge trapping' [7], [8], [9]: the device threshold voltage ( $V_T$ ) is modulated by charge trapped in the high-k dielectric of the HKMG device where the magnitude as well as stability (retention) of the trapped charge has a positive correlation to the self-heating temperature. The programming is typically done using short gate bias ( $V_G$ ) pulses of ~1.8-2.0V with a drain bias ( $V_D$ ) of ~1.3-1.6V, while the source bias ( $V_S$ ) and substrate bias ( $V_X$ ) are 0V (Fig. 2.3). The pulse of high channel current causes device self-heating while the high vertical field assists the electrons to inject into the gate and be trapped in the high-k dielectric, causing  $V_T$  to increase.

While detailed discussions are included in subsequent chapters, it is worthwhile pointing out here that the magnitude as well as the stability (retention) of the trapped charge is significantly enhanced due to the (self-heating induced) high temperature during the programming operation, resulting in large and stable V<sub>T</sub> shifts suitable for NVM applications requiring high-temperature operation. The impact of device self-heating on the magnitude as well as the stability (retention) of the trapped charge is demonstrated in Fig. 2.4 and Fig. 2.5. Fig. 2.4 shows the measured  $\Delta V_T$ from a CTT programmed, using the same programming voltage (V<sub>G</sub>), with and without device self-heating and Fig. 2.5 shows the measured charge de-trapping activation energies (E<sub>a</sub>) for devices programmed at various device self-heating temperatures: it is clear that the magnitude as well as charge retention characteristics are significantly enhanced by device self-heating during the charge trapping (programming) operation. The self-heating enhanced charge trapping is demonstrated to have excellent stability for the resulting device threshold voltage shifts to be used as a mechanism for non-volatile data storage: data retention lifetime of > 10 years at 125 °C has been demonstrated. Detailed discussions on maximizing the impact of device self-heating for improved operation efficiency and data retention for CTT memory are included in subsequent chapters.

Fig. 2.3. A schematic of the CTT programming operation.

Fig. 2.4. Measured  $\Delta V_T$  from a CTT programmed with and without device self-heating.

Fig. 2.5. Measured charge de-trapping activation energies  $(E_a)$  for CTTs programmed at various device self-heating temperatures.

The device  $V_T$  is modulated by the charge trapped in the high-k dielectric, whereafter each unique  $V_T$  value can be interpreted as a unique bit e.g. "0" and "1" for two unique  $V_T$  levels. The  $V_T$  of a transistor can be expressed by the following basic equation, where  $Q_{ox}$  is the quantity that is modulated due to the charge trapped in the gate dielectric:

$$V_{T0} = 2\Phi_F + \Phi_{ms} - \frac{Q_{ox}}{C_{ox}} - \frac{Q_{dm}}{C_{ox}}$$

(2.1)

where

$\Phi_F$  is the substrate Fermi potential (difference between the Fermi Level and the Intrinsic Fermi Level)

$\Phi_{\it ms}$  is the work function difference between the gate metal and the substrate

$Q_{ox}$  is the trapped charge in the gate dielectric

$Q_{\rm dm}$  is the maximum charge held by the depletion layer at inversion

$C_{ox}$  is the capacitance of the gate dielectric

It is clear that the effective threshold voltage of the device can be altered by the amount of charge in the high-k dielectric i.e.  $V_T = V_{T0} + \Delta V_T$ , where  $\Delta V_T$  is given by  $\Delta Q_{ox}/C_{ox}$ .

The basic erase operation in CTT memory devices can be achieved by applying a negative gate-to-substrate bias, while the source, drain, and substrate are grounded, to electrostatically emit trapped charge. However, as discussed in subsequent chapters, this erase technique results in an inefficient erase: a technique called "Self-heating Temperature Assisted eRase" (STAR) has been developed [10], [11], [12] to address this issue and achieve high erase efficiency, which ultimately results in a *significant* improvement in the memory window and the program/erase cycling endurance of CTTs.

Fig. 2.6 shows a schematic depicting the basic operation of a CTT memory device. It must be noted that, while schematics of a planar device are shown for demonstration here, the phenomenon of intrinsic self-heating enhanced charge trapping is equally applicable to FinFET technologies. Self-heating in SOI planar technologies is of course higher as compared to bulk planar technologies. Self-heating in bulk FinFETs, while generally less than SOI FinFETs, is

comparable to SOI planar devices and increases considerably with scaling [13], [14]: this makes the CTT technology highly scalable. Implementation of CTT eNVM has been demonstrated in 32nm SOI planar, 22nm SOI planar, 14nm SOI FinFET, 14nm bulk FinFET, and 7nm bulk FinFET technology nodes, including fully functional product prototype memory arrays. The CTT technology offers logic voltage compatible operation, scalability, high density (~0.144µm²/bit for 22nm and ~0.082µm²/bit for 14nm technology), and excellent retention (> 10 years @ 125 °C) for a fully integrated and scalable MTP eNVM that can be implemented without the need for any added process complexity or masks. In addition to being multi-time programmable, owed to the aforementioned advantages the CTT technology offers a better alternative to existing one-time programmable (OTP) technologies like eFUSE [15] and gate breakdown anti-fuse [16] as it can be used more effectively for yield improvement, chip configuration, redundancy, repair at wafer and module test and in the field , performance tailoring, and hardware security improvements such as chip ID and on-chip reconfigurable encryption key and firmware storage with lower power, higher density, and higher scalability, at no additional processing cost.

Fig. 2.6. A schematic depicting the basic operation of a CTT memory device (equally applicable to planar FET as well as FinFET based CTTs).

#### REFERENCES

- [1] E. Cartier, B. P. Linder, V. Narayanan and V. K. Paruchuri, "Fundamental understanding and optimization of PBTI in nFETs with SiO<sub>2</sub>/HfO<sub>2</sub> gate stack," *IEEE IEDM*, Dec. 2006, pp. 1-4.

- [2] C. Kothandaraman, X. Chen, D. Moy, D. Lea, S. Rosenblatt, F. Khan, D. Leu, T. Kirihata, D. Ioannou, G. LaRosa, J. B. Johnson, N. Robson and S. S. Iyer, "Oxygen vacancy traps in Hi-K/metal gate technologies and their potential for embedded memory applications," *IEEE IRPS*, 2015, pp. MY.2.1–MY.2.4.

- [3] H. Hamamura, T. Ishida, T. Mine, Y. Okuyama, D. Hisamoto, Y. Shimamoto, S. Kimura and K. Torii, "Electron trapping characteristics and scalability of HfO<sub>2</sub> as a trapping layer in SONOS-type flash memories," *IEEE IRPS*, 2008, pp. 412–416.

- [4] A. R. Trivedi *et al.*, "A Simulation Study of Oxygen Vacancy-Induced Variability in HfO<sub>2</sub> /Metal Gated SOI FinFET," *IEEE Transactions on Electron Devices*, vol. 61, no. 5, pp. 1262-1269, May 2014.

- [5] E. Cartier and A. Kerber, "Stress-induced leakage current and defect generation in nFETs with HfO<sub>2</sub>/TiN gate stacks during positive-bias temperature stress," *IEEE IRPS*, 2009, pp. 486–492.

- [6] F. Crupi, R. Degraeve, A. Kerber, D. H. Kwak and G. Groeseneken, "Correlation between stress-induced leakage current (SILC) and the HfO<sub>2</sub> bulk trap density in a SiO<sub>2</sub>/HfO<sub>2</sub> stack," *IEEE IRPS*, 2004, pp. 181–187.

- [7] F. Khan, E. Cartier, C. Kothandaraman, J. C. Scott, J. C. S. Woo and S. S. Iyer, "The Impact of Self-Heating on Charge Trapping in High- *k* -Metal-Gate nFETs," *IEEE Electron Device Letters*, vol. 37, no. 1, pp. 88-91, 2016.

- [8] F. Khan, E. Cartier, J. C. S. Woo and S. S. Iyer, "Charge Trap Transistor (CTT): An Embedded Fully Logic-Compatible Multiple-Time Programmable Non-Volatile Memory Element for High- *k* -Metal-Gate CMOS Technologies," *IEEE Electron Device Letters*, vol. 38, no. 1, pp. 44-47, 2017.

- [9] F. Khan, M. S. Han, D. Moy, R. Katz, L. Jiang, E. Banghart, N. Robson, T. Kirihata, J. C. S. Woo and S. S. Iyer, "Design Optimization and Modeling of Charge Trap Transistors (CTTs) in 14 nm FinFET Technologies," *IEEE Electron Device Letters*, vol. 40, no. 7, pp. 1100-1103, 2019.

- [10] F. Khan et al., "Program and Erase Memory Structures", U.S. Patent app. # 16/047,529.

- [11] F. Khan et al., "Charge Trap Memory Devices", U.S. Patent app. # 16/781,527.

- [12] F. Khan, D. Moy, D. Anand, E. H.-Schroeder, R. Katz, L. Jiang, E. Banghart, N. Robson and T. Kirihata, "Turning Logic Transistors into Secure, Multi-Time Programmable, Embedded Non-Volatile Memory Elements for 14 nm FINFET Technologies and Beyond," *IEEE Symposium on VLSI Technology Digest of Technical Papers*, Kyoto, Japan, 2019, pp. T116-T117.

- [13] T. Hook, F. Allibert; K. Balakrishnan, B. Doris, D. Guo; N. Mavilla, E. Nowak, G. Tsutsui, R. Southwick, J. Strane and X. Sun, "SOI FinFET versus bulk FinFET for 10nm and below," *IEEE S3S Conf.*, 2014, pp. 1-3.

- [14] D. Jang, E. Bury, R. Ritzenthaler, M. Garcia Bardon, T. Chiarella, K. Miyaguchi, P. Raghavan, A. Mocuta, G. Groeseneken, A. Mercha, D. Verkest and A. Thean, "Self-heating on bulk FinFET from 14nm down to 7nm node," *IEEE IEDM*, 2015, pp. 6-11.

- [15] C. Kothandaraman, S. K. Iyer and S. S. Iyer, "Electrically programmable fuse (eFUSE) using electromigration in silicides," *IEEE Electron Device Lett.*, vol. 23, no. 9, pp. 523–525, Sep. 2002.

- [16] Y. Liu, M.H. Chi, A. Mittal, G. Aluri, S. Uppal, P. Paliwoda, E. Banghart, K. Korablev, B. Liu, M. Nam, M. Eller and S. Samavedam, "Anti-Fuse Memory Array Embedded in 14nm FinFET CMOS with Novel Selector-Less Bit-Cell Featuring Self-Rectifying Characteristics," *IEEE Symp. VLSI Technol. Dig. Tech. Papers*, 2014.

# 3. SELF-HEATING ENHANCED CHARGE TRAPPING AND CTT DESIGN OPTIMIZATION

In this chapter, the impact of device self-heating on the charge trapping behavior in high-k/metal-gate (HKMG) CMOS logic devices is studied, analyzed, and characterized. The magnitude of charge trapping is of course dependent on the applied gate bias i.e. the charge injection field. However, it is demonstrated that the channel temperature (T) during charge injection (programming), dictated by the device thermal resistance (R<sub>th</sub>), also plays significant and perhaps a more important role in the charge trapping behavior. The phenomenon of self-heating enhanced charge trapping has been verified and studied on CTTs in several commercial technologies including 32 nm SOI planar, 22 nm SOI planar, 14 nm SOI FinFET, 14 nm bulk FinFET, and 7 nm bulk FinFET nodes, as demonstrated and discussed in subsequent chapters. CTTs in 22 nm SOI planar and 14 nm bulk FinFET nodes are used for demonstration purposes in this chapter.

The rise in device temperature during the CTT programming operation, or during any operation of any device for that matter, is given by the product of  $R_{th}$  and the applied power (P) i.e.  $\Delta T = R_{th} \times P = R_{th} \times (I_{ch} \times V_D)$  where  $I_{ch}$  is the channel current and  $V_D$  is the applied drain-to-source bias. It is clear that the channel temperature can be increased by the applied power e.g. by increasing  $V_D$  and/or reducing the device channel length. However, in addition to an increase in self-heating temperature, a higher  $V_D$  and/or reduced channel length also results in an increased amount of hot carrier injection (HCI). In order to decouple the impact of the lateral electric field from the impact of temperature, device layout-dependent effects can be manipulated to strongly modulate and enhance the device  $R_{th}$  i.e. considerably higher device temperatures can be

achieved for the same power and applied electric fields. In other words, it is demonstrated that the charge trapping is dependent not only on the channel power density during the programming operation, which is controlled by drain bias and device channel length, but it is also strongly modulated by the device layout. Thus, identical power densities in electrically identical devices (identical channel lengths and widths) with different device layouts, and different  $R_{th}$ , result in significantly different charge trapping behaviors. While device self-heating strongly influences the magnitude of charge trapping, it is found that the self-heating temperature during the charge injection (programming) operation also significantly enhances the stability (retention) of the trapped charge.

The implications of the findings for the application of high-k/metal-gate logic devices as embedded memory elements, dubbed as "Charge Trap Transistors" or "CTTs", for non-volatile data storage in high-k/metal-gate CMOS technologies without added process complexity are discussed in this chapter. Considerations for optimization of bitcell design and operation conditions for CTT memory are also included.

## 3.1 MODULATION OF SELF-HEATING ENHANCED CHARGE TRAPPING WITH BIAS

For this study, experiments are performed on devices fabricated in a 22 nm high-performance SOI technology [1]. First, device threshold voltage shifts ( $\Delta V_T$ ) are measured during pulsed gate voltage ramp sweeps (PVRS) for various fixed drain bias ( $V_D$ ) conditions. Gate bias ( $V_G$ ) is applied using 10ms pulses of increasing magnitudes in 50mV increments. After each pulse, the device threshold voltage ( $V_T$ ) is measured within 10ms. Each device is ramped until breakdown and Fig. 3.1 shows the measured  $\Delta V_T$  values until before breakdown. Details on the PVRS technique can be found in [2]. The pre-stress  $V_T$  of each device is ~280mV. Two

observations are made; Firstly, at higher  $V_D$ 's (higher lateral field and self-heating), equivalent  $\Delta V_T$ 's are achievable at substantially lower  $V_G$ 's. This is attributed to the impact of an enhanced level of HCI and charge trapping with increasing  $V_D$  as well as to enhanced charge trapping due to device self-heating [3] with increasing  $V_D$ . Secondly, the maximum achievable  $\Delta V_T$  before device breakdown initially increases and then starts to decrease with increasing  $V_D$ . The breakdown of devices under low  $V_D$  conditions is electric field driven (high gate-to-drain bias,  $V_{GD}$ ) whereas the breakdown of devices under high  $V_D$  conditions (which happens at much lower  $V_{GD}$ ) is self-heating driven, which is a well-known phenomenon [4]. Shifts in  $\Delta V_T$  vs.  $V_G$  trends before hard breakdown may be indicative of the beginning of soft breakdown [5].

Fig. 3.1.  $\Delta V_T$  as a function of PVRS stress with 10ms pulses at various fixed  $V_D$  values ( $W_{ch}$ =1.04 um, L=20 nm).

# 3.2 EXPLOITING DEVICE LAYOUT-DEPENDENT EFFECTS FOR MODULATION OF SELF-

### HEATING ENHANCED CHARGE TRAPPING

While studying the impact of drain bias using the PVRS technique, as discussed in the previous section, is useful for understanding the dynamic charge trapping behavior as well as its bias dependence, that technique does not allow one to decouple the effect of the lateral electric

field from the self-heating effects. In order to understand and quantify the impact of device self-heating on charge trapping in CTTs and to separate the impact of electric field from the thermal effects, layout-dependent effects are exploited to modulate the  $R_{th}$  of devices, while all other electrical parameters are kept constant.

To demonstrate the layout dependence of the thermal resistance and in turn self-heating enhanced charge trapping in planar devices, 22 nm SOI [1] CTTs with various geometries are studied. Identical program pulses (35ms at V<sub>G</sub>=2V and V<sub>D</sub>=1.3V) are applied to the same channel width (W<sub>ch</sub>) but various channel lengths (L) are and the V<sub>T</sub>'s are measured within 10ms. It is seen that  $\Delta V_T$  increases as L decreases (Fig. 3.2(a)), which is expected and consistent with increasing levels of hot carriers and self-heating (due to increase in lateral field) and decreasing V<sub>T</sub> (due to short-channel effects) with decreasing L. However, when identical program pulses are applied to devices with the same L and various  $W_{ch}$ , it is observed that  $\Delta V_T$  increases with  $W_{ch}$ (Fig. 3.2(b)). This phenomenon of  $\Delta V_T$  varying with  $W_{ch}$  (while vertical and lateral fields and L are the same, and therefore the level of HCI is the same) is not readily explained by merely a field-dependent charge injection mechanism and is attributed to the impact of self-heating, which is strongly modulated by Wch. Additionally, as demonstrated and discussed in detail later in this section, the negligible asymmetry between forward- and reverse-mode measurements after device programming at nominal conditions provides further evidence that drain-side HCI is indeed *not* the dominant charge injection mechanism in CTTs. The level of asymmetry, however, can be modulated by the applied V<sub>D</sub> during the programming operation (high values of V<sub>D</sub> result in a higher level of drain-side HCI). The reader is reminded that typically  $V_G > V_D$  during the CTT programming operation. Throughout this work, the chuck temperature is always maintained at 25 °C unless otherwise stated.

Fig. 3.2. Measured  $\Delta V_T$  vs. (a) device channel length ( $W_{ch}$ =1.04 um) and (b) device channel width (L=20 nm).

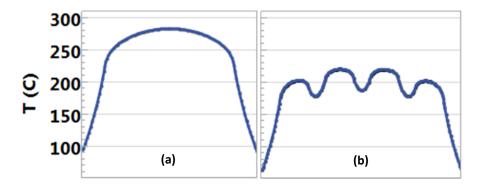

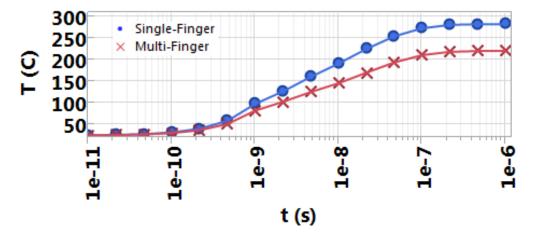

To quantify the impact of layout to the device thermal resistance and demonstrate its subsequent impact on self-heating enhanced charge trapping, single-finger devices vs. multifinger (split-channel) devices are studied. Both devices have a total W<sub>ch</sub> of 1.04 um where each channel in the multi-finger devices, separated by trench isolation, has a width of W<sub>ch</sub>/4. Both devices are identical to each other except for the channel width and have a channel length of 20 nm. Layouts of the two devices are shown in Fig. 3.3(a) and Fig. 3.3(b) respectively. First, channel thermal profiles of the two devices are analyzed. Thermal simulations have been carried out using finite element analysis (Comsol<sup>TM</sup>). Full 3D structural simulations of the devices are analyzed and solved for temperature distribution and heat flux. Fig. 3.4(a) and Fig. 3.4(b) show the channel temperature (T) profiles of the two devices for an applied power density of 4mW/um. It is clear that W<sub>ch</sub>/active area significantly modulates the device R<sub>th</sub> and in turn selfheating. In multi-finger devices, the area for vertical heat flow is effectively larger than the area for power dissipation. Additionally, the larger area for lateral heat dissipation and the higher number of contacts per unit width in multi-finger devices are also responsible for higher heat dissipation and thus a lower R<sub>th</sub> as compared to single-finger devices. The extracted R<sub>th</sub> for the single-finger device is ~1.3x compared to the multi-finger device (65.9 vs. 50.8 K/mW, respectively). Additionally, simulation results show that the devices reach thermal equilibrium within ~200 ns (Fig. 3.5).

Fig. 3.3 (a) Single-finger and (b) Multi-finger device layout.

Fig. 3.4. Steady-state thermal profiles for a (a) single-channel and (b) multi-channel device in the  $W_{ch}$  direction, for an applied power of 4mW/um.

Fig. 3.5. Rise in channel temperature  $\,$  vs. time for self-heating (4mW/um applied power).

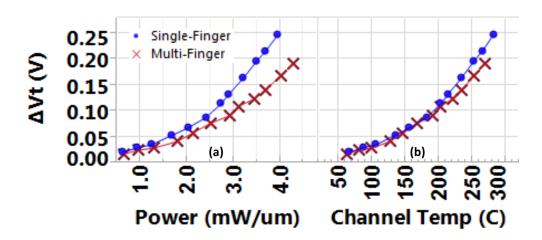

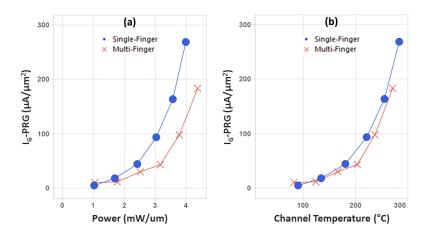

Fig. 3.6(a) shows the measured  $\Delta V_T$  vs. applied power density for devices that were used for the thermal simulations. The power is varied by varying  $V_D$  while  $V_G$ =2V. It is seen that, for the same power density,  $\Delta V_T$  for the single-channel device is considerably higher as compared to the split-channel device and the difference is greater at higher power densities. However, when plotted as a function of the calculated channel temperature (Fig. 3.6(b)), the  $\Delta V_T$  characteristics of the two devices are almost identical except at very high temperatures where the single-channel device seems to have slightly higher  $\Delta V_T$ . In other words,  $\Delta V_T$  behaviors of the devices show a very strong correlation to the self-heating temperature as opposed to the applied power density. It is clear from these results that the device self-heating temperature is a significant factor in modulating the charge trapping behavior.

Fig. 3.6. Measured  $\Delta V_T$  vs. (a) applied power density and (b) channel T during programming. It is observed that, at higher T's, the rate of increase in  $\Delta V_T$  is higher.

Thus far, it has been shown how layout-dependent effects in planar devices can be manipulated to modulate and enhance the self-heating effect and in turn the programming efficiency in CTTs - Device self-heating (or alternatively thermal resistance,  $R_{th}$ ) and therefore programming efficiency is strongly influenced by the width of each active channel in the planar

devices: a single wide channel device shows a considerably higher programming efficiency as compared to a device with multiple narrower channels in parallel.

Next, how the CTT bitcell design can be manipulated to exploit layout-dependent effects significantly enhance the programming efficiency in FinFET-based CTTs is demonstrated; experiments are performed on hardware in a 14 nm FinFET technology [6]. Nominal nFET devices with a gate length of 14 nm and EOT of ~1.3 nm are used.

Unlike planar devices, the width of each active channel in FinFET devices is quantized i.e. the channel width of a device can only be increased by connecting multiple fins, and therefore a single channel cannot be made wider to increase the device  $R_{th}$ . However, the efficiency of thermal dissipation, and in turn the  $R_{th}$ , of FinFET devices can be modulated by changing the aspect ratio of the device i.e. by reconfiguration of the number of fins-to-number of gates ratio in each device. Another way to modulate the device  $R_{th}$  is by isolating bitcells from each other.

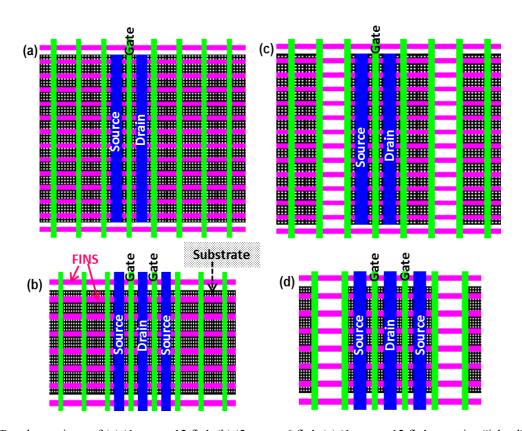

In order to optimize the bitcell layout to improve the effect of device self-heating and in turn the programming efficiency of CTTs in FinFET technologies, four different bitcell layouts are fabricated and studied. A '1 gate  $\times$  12 fin' bitcell (Fig. 3.7(a)) and a '2 gate  $\times$  6 fin' bitcell (Fig. 3.7(b)) are investigated. In addition to the bitcell aspect ratio, we investigate the impact of isolating the bitcells from each other, i.e. each bitcell is fabricated on an active "island" separated by a trench isolation. Fig. 3.7 (c) and Fig. 3.7 (d) show the isolated '1 gate  $\times$  12 fin' and '2 gate  $\times$  6 fin' bitcells, respectively. It must be noted that the only difference between each bitcell is the layout: each bitcell is composed of 12 FETs. The bitcells are programmed at  $V_G = 2V$ ,  $V_D = 1.4V$ , and  $V_S = 0V$  using 2.5 ms pulses and the  $V_T$ 's are measured after each pulse. In order to study the charge trapping behavior in the absence of self-heating (no channel current,  $I_{ch}$ ),

devices are also programmed at  $V_G = 2V$  and  $V_D = V_S = 0V$ . In order to examine the thermal dissipation properties of the corresponding bitcell designs, 3D finite element thermal simulations, using Sentaurus Interconnect, are also performed. For each bitcell, a power density of  $7.1 \times 10^{12}$  W/cm<sup>3</sup> associated with the Joule heating produced from current flow in the active fin channels during programming is applied and the respective channel temperatures and  $R_{th}$  values are extracted.

Fig. 3.7. Top down views of (a) '1 gate  $\times$  12 fin', (b) '2 gate  $\times$  6 fin', (c) '1 gate  $\times$  12 fin' on active "island", and (d) '2 gate  $\times$  6 fin' on active "island" CTT bitcell layouts.

The bitcell steady-state temperatures, achieved within  $\sim 50$  ns (Fig. 3.8), during the programming operation are shown in Fig. 3.9. The thermal profiles along the gate direction (perpendicular to the fins), at programming conditions, of each of the four bitcells (Fig. 3.10) show that the '2×6' layout has a higher  $R_{th}$  and hence, for identical power densities, a higher

channel temperature as compared to the '1×12' layout. Furthermore, isolated bitcells have a higher  $R_{th}$  as compared to their un-isolated counterparts. Measured (hardware) data for the  $V_T$  shift ( $\Delta V_T$ ) vs. programming time ( $t_P$ ) for each of the fabricated bitcell designs is shown in Fig. 3.11. From the measured hardware data and the corresponding thermal simulations, we make two key observations: First, in the presence of self-heating, bitcells with different layouts (and in turn  $R_{th}$ ) exhibit considerably different behaviors with identical programing conditions. With the isolated '2×6' bitcell,  $\Delta V_T$  for the same  $t_P$  increases > 60%, > 30%, and > 10% as compared to the unisolated '1×12' bitcell, the isolated '1×12' bitcell, and the unisolated '2×6' bitcell, respectively. The isolated '2×6' bitcell enables a 6× reduction in  $t_P$  to reach the target  $\Delta V_T$  as compared to the unisolated '1×12' bitcell (Fig. 3.11 (a)). Secondly, in the absence of self-heating (Fig. 3.11 (b)),  $\Delta V_T$  is negligible for the same  $V_G$  and that all the devices behave identically. These results are consistent with the findings in 32 and 22 nm planar SOI CTTs.

Fig. 3.8. Rise in bitcell temperature vs. time during the program operation.

Fig. 3.9. 3D finite element thermal simulation of the programming operation of CTT bitcell structures with (a) '1 gate×12 fin', (b) '2 gate×6 fin', (c) '1 gate×12 fin' on active "island", and (d) '2 gate×6 fin' on active "island" layouts.

Fig. 3.10. Thermal profiles, during programming, of the bitcell layouts shown in Fig. 3.9, along the gate direction.

Fig. 3.11.  $\Delta V_T$  vs.  $t_P$  for CTT bitcells with various layouts. The devices are programmed with (a)  $V_G$ =2V,  $V_D$ =1.4V,  $V_S$ =0V and (b)  $V_G$ =2V,  $V_D$ = $V_S$ =0V.

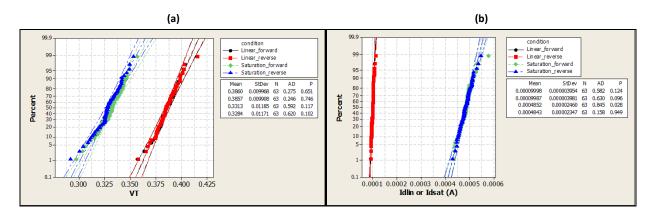

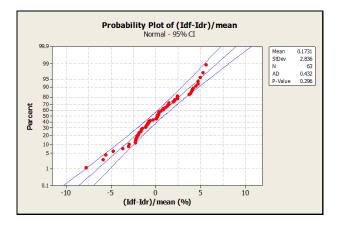

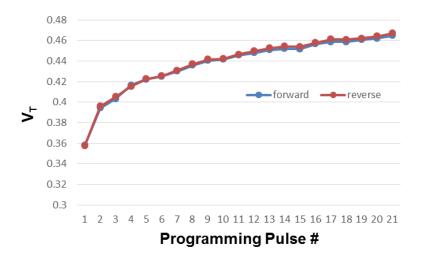

# 3.3 CHARGE INJECTION MECHANISM AND THE CHARGE TRAPPING PROFILE