# UC San Diego UC San Diego Electronic Theses and Dissertations

# Title

Algorithm-Centric Design of Reliable and Efficient Deep Learning Processing Systems

**Permalink** https://escholarship.org/uc/item/515341v3

**Author** Ozen, Elbruz

Publication Date 2023

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

Algorithm-Centric Design of Reliable and Efficient Deep Learning Processing Systems

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

#### Computer Science (Computer Engineering)

by

Elbruz Ozen

Committee in charge:

Professor Alex Orailoglu, Chair Professor Chung-Kuan Cheng Professor Sicun Gao Professor Farinaz Koushanfar Professor Tajana Rosing

Copyright

Elbruz Ozen, 2023

All rights reserved.

The dissertation of Elbruz Ozen is approved, and it is acceptable in quality and form for publication on microfilm and electronically.

University of California San Diego

2023

# DEDICATION

Dedicated to my parents, whose unwavering support and encouragement made this achievement possible, and to everyone who has guided and inspired me along the way.

# EPIGRAPH

"The one who knows all the answers has not been asked all the questions."

– Confucius

| Dissertation Approval Page                                                                                                                                                                                                                                                                                                                                                      | iii                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Dedication                                                                                                                                                                                                                                                                                                                                                                      | iv                                                       |

| Epigraph                                                                                                                                                                                                                                                                                                                                                                        | v                                                        |

| Table of Contents                                                                                                                                                                                                                                                                                                                                                               | vi                                                       |

| List of Figures                                                                                                                                                                                                                                                                                                                                                                 | xi                                                       |

| List of Tables                                                                                                                                                                                                                                                                                                                                                                  | XV                                                       |

| List of Algorithms                                                                                                                                                                                                                                                                                                                                                              | xvi                                                      |

| Acknowledgements                                                                                                                                                                                                                                                                                                                                                                | xvii                                                     |

| Vita                                                                                                                                                                                                                                                                                                                                                                            | xxi                                                      |

| Abstract of the Dissertation x                                                                                                                                                                                                                                                                                                                                                  | xiii                                                     |

| Chapter 1Introduction1.1Background1.2Problem Definition1.3Dissertation Contribution1.4Dissertation Organization1.5Acknowledgements                                                                                                                                                                                                                                              | 1<br>1<br>2<br>6<br>7<br>8                               |

| Chapter 2An Overview of Relevant Deep Neural Network Concepts2.1Common Layer Types in Deep Neural Networks2.1.1Fully Connected Layer2.1.2Convolutional Layer2.1.3Non-linear Activation Functions2.1.4Pooling2.1.5Batch Normalization2.1.6Dropout and Dropconnect2.2Loss Function and DNN Training Process2.3DNN Inference with Spatial Hardware Accelerators2.4Acknowledgements | 10<br>10<br>11<br>11<br>12<br>12<br>13<br>13<br>14<br>15 |

| Chapter 3       Literature Review         3.1       Safety, Reliability, and Testing of Deep Learning Hardware         3.1.1       Evaluating Reliability         3.1.2       Hardware Error Detection and Rectification         3.1.3       Boosting Hardware Error Resilience of Deep Neural Networks                                                                         | 17<br>17<br>18<br>20<br>21                               |

# TABLE OF CONTENTS

|         | 3.1.4 Reliability-Aware Scheduling                                     | 22 |

|---------|------------------------------------------------------------------------|----|

|         | 3.1.5 Hardware Testing and Yield Improvement                           | 22 |

| 3.2     | Improving Performance and Efficiency of Deep Learning Inference        | 24 |

|         | 3.2.1 Model Compression                                                | 24 |

|         | 3.2.2 Hardware Accelerator Design                                      | 27 |

| 3.3     | Deep Learning Inference in Computational Mediums with High Fault Rates | 28 |

|         | 3.3.1 Aggressive Hardware Optimizations in Digital CMOS Hardware       | 28 |

|         | 3.3.2 Alternative Computing Technologies                               | 29 |

| 3.4     | Acknowledgements                                                       | 30 |

| Chapter | 4 Dissertation Overview                                                | 32 |

| 4.1     | Reconsidering DNN Resilience Characteristics                           | 33 |

| 4.2     | Proactive Toleration of Hardware Errors                                | 34 |

|         | 4.2.1 Vulnerability Reduction Through Range Manipulation               | 35 |

|         | 4.2.2 Boosting Algorithmic Decentralization in Training                | 35 |

| 4.3     | Non-Perfect Restoration of Hardware Errors                             | 36 |

| 4.4     | Hardware Error Detection Through Invariants                            | 37 |

|         | 4.4.1 Hardware Error Detection Through External Invariants             | 37 |

|         | 4.4.2 Hardware Error Detection Through Internal Invariants             | 38 |

| 4.5     | Usage of DNN Plasticity and Redundancy for Relationship Construction   | 39 |

| 4.6     | Harnessing Relationships for Hardware-Friendly Sparsity Embedding      | 40 |

| Chapter | 5 Research Vision                                                      | 42 |

| 5.1     | Explored Research Questions                                            | 42 |

| 5.2     | What is Unique for Deep Learning Processing Systems?                   | 43 |

|         | 5.2.1 Unique Characteristics of Deep Neural Network Algorithms         | 43 |

|         | 5.2.2 Unique Characteristics of Deep Neural Network Hardware           | 44 |

| 5.3     | Proposed Approach                                                      | 45 |

|         | 5.3.1 Reshaping Deep Neural Networks                                   | 46 |

|         | 5.3.2 Strategic Hardware Enhancements                                  | 47 |

|         | 5.3.3 Functional Correctness Prioritization                            | 48 |

|         | 5.3.4 Harnessing the Statistical Nature of Deep Neural Networks        | 49 |

| 5.4     | Research Challenges                                                    | 49 |

|         | 5.4.1 How to Explore the Design Space?                                 | 49 |

|         | 5.4.2 How to Resolve Training Challenges?                              | 50 |

| 5.5     | Technical Progress                                                     | 53 |

| Chapter | 6 Hardware Error Detection in DNN Accelerators via External Invariants | 55 |

| 6.1     | Introduction                                                           | 56 |

| 6.2     | DNN Hardware Error Detection via Linear Checksums                      | 57 |

|         | 6.2.1 Checksums in Fully-Connected Layers                              | 58 |

|         | 6.2.2 Checksums in Convolutional Layers                                | 61 |

|         | 6.2.3 Error Detection Guarantees of the Checksums                      | 65 |

|         | 6.2.4 Impact of Numerical Inaccuracies on Checksum Calculations        | 66 |

| 6.3 Experimental Method                                                            | . 70  |

|------------------------------------------------------------------------------------|-------|

| 6.3.1 Error Injection Method                                                       | . 70  |

| 6.3.2 Sanity-Check Implementation on Software                                      | . 72  |

| 6.3.3 Sanity-Check Implementation on Hardware                                      |       |

| 6.3.4 Baseline Methods for Comparison                                              | . 76  |

| 6.4 Experimental Results                                                           | . 76  |

| 6.5 Chapter Summary                                                                | . 80  |

| 6.6 Acknowledgements                                                               | . 80  |

| Chapter 7 Hardware Error Detection in DNN Accelerators via Internal Invariants     |       |

| 7.1 Introduction                                                                   |       |

| 7.2 Error Checking with Computation Invariants                                     |       |

| 7.3 Training Balanced Output Partitions                                            |       |

| 7.4 Error Checking at Runtime                                                      | . 85  |

| 7.5 Simulating Hardware-Level Faults on the DNN Graph                              |       |

| 7.6 Experimental Method                                                            | . 87  |

| 7.7 Experimental Results                                                           | . 88  |

| 7.8 Chapter Summary                                                                | . 94  |

| 7.9 Acknowledgements                                                               | . 94  |

| Chapter 8 Cost-Effective Rectification of Hardware Errors in DNN Accelerators      | . 95  |

| 8.1 Introduction                                                                   |       |

| 8.2 Overview of Relevant Neural Network Characteristics                            | . 96  |

| 8.3 Fine-grained Internal Invariants for Error Localization in Deep Neural Network | s 98  |

| 8.4 Maintaining Neural Network Accuracy with Approximate Rectification of Error    | s 100 |

| 8.4.1 Error Rectification Through Dropping or Clipping Variables                   | . 101 |

| 8.4.2 Error Rectification Through Median Feature Selection                         | . 104 |

| 8.5 Deep Neural Network Training with Graph Constraints                            | . 110 |

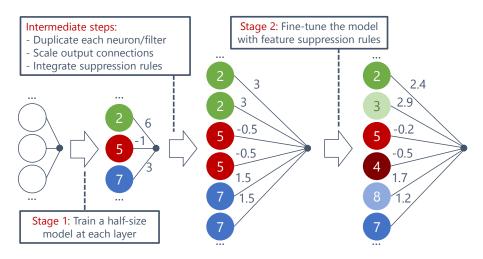

| 8.5.1 Training DNNs with Anomaly Detection and Suppression Rules                   | . 111 |

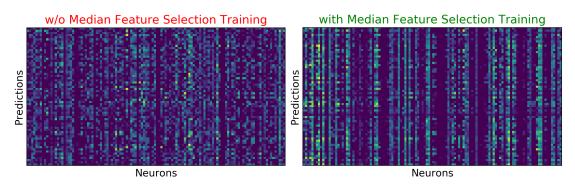

| 8.5.2 Training DNNs with Median Feature Selection Rules                            | . 115 |

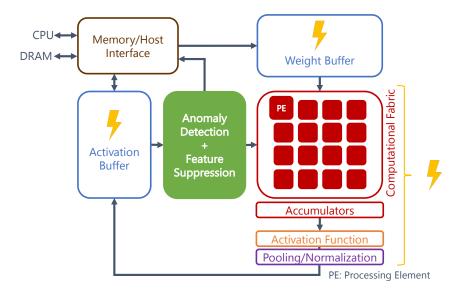

| 8.6 Hardware Design for Efficient Error Detection and Rectification                | . 117 |

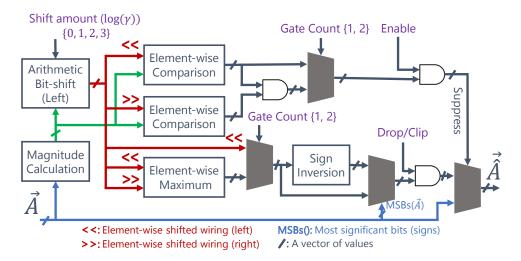

| 8.6.1 Hardware Design for Efficient Anomaly Detection and Suppression              |       |

| 8.6.2 Hardware Design for Efficient Median Feature Selection                       |       |

| 8.7 Experimental Method                                                            | . 123 |

| 8.7.1 Anomaly Detection and Suppression Experiments                                | . 123 |

| 8.7.2 Median Feature Selection Experiments                                         |       |

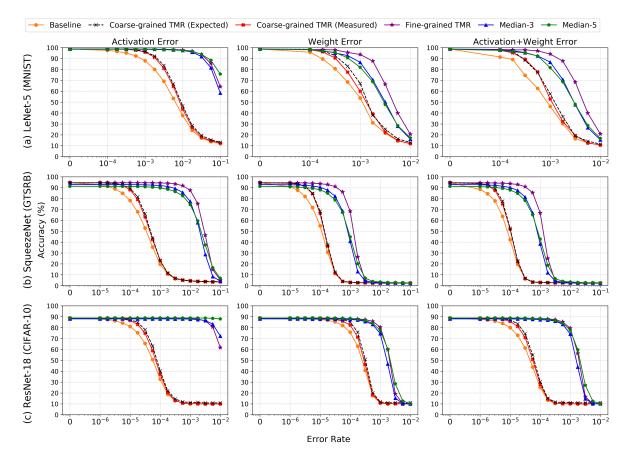

| 8.8 Experimental Results                                                           |       |

| 8.8.1 Error Resilience Improvements                                                |       |

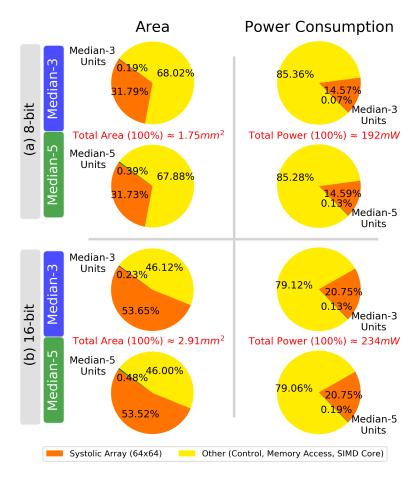

| 8.8.2 Hardware Overhead Characterization                                           |       |

| 8.9 Discussion                                                                     |       |

| 8.10 Chapter Summary                                                               |       |

| 8.11 Acknowledgements                                                              |       |

| Chapter 9 Designing Error-Resilient Deep Neural Networks                           | . 139 |

| 9.1     | Introduction 1                                                                 | 139 |

|---------|--------------------------------------------------------------------------------|-----|

| 9.2     | Overview of Model Quantization                                                 | 141 |

| 9.3     | Designing Error-Resilient Deep Neural Networks By Tightening Numerical Range 1 | 144 |

|         | 9.3.1 Tight Quantization Bounds with Layer-wise Quantization 1                 | 144 |

|         | 9.3.2 Squeezing Layer-wise Bounds with Outlier Regularization 1                | 146 |

| 9.4     | Experimental Method 1                                                          | 149 |

|         | 9.4.1 Experimental Setup 1                                                     | 149 |

|         | 9.4.2 Error Model 1                                                            | 150 |

| 9.5     | Experimental Results                                                           | 151 |

|         | 9.5.1 Impact of Regularization Terms on Training and Full-Precision (Non-      |     |

|         |                                                                                | 152 |

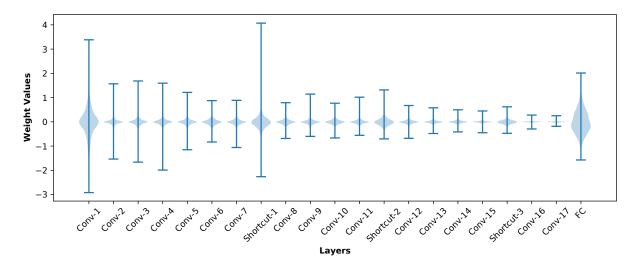

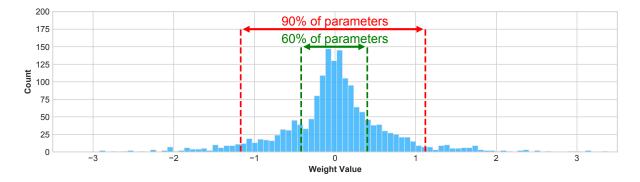

|         | 9.5.2 Impact of Regularization Term on Parameter Distributions 1               | 153 |

|         |                                                                                | 156 |

|         | 9.5.4 Impact of Regularization Term on Quantization Accuracy 1                 | 162 |

|         | 9.5.5 Observed Differences Between Max-Magnitude and Max-Squared Regu-         |     |

|         | larization Terms 1                                                             | 164 |

| 9.6     | Discussion 1                                                                   | 165 |

| 9.7     | Chapter Summary 1                                                              | 166 |

| 9.8     | Acknowledgements 1                                                             | 167 |

|         |                                                                                |     |

| Chapter | <b>č</b> 1                                                                     | 168 |

|         |                                                                                | 168 |

| 10.2    | Problem Definition                                                             | 171 |

| 10.3    | Proposed Method 1                                                              | 172 |

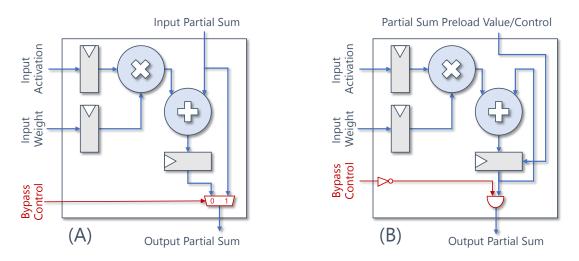

|         | 10.3.1 Isolating Faults Through Hardware Configurability 1                     | 173 |

|         | 10.3.2 Minimizing Information Loss with Decentralized DNNs 1                   | 175 |

|         | 10.3.3 Calibrating Statistical Properties of Faulty DNNs 1                     | 180 |

|         | 10.3.4 Searching for Benign Pruning Patterns 1                                 | 182 |

| 10.4    | Experimental Method 1                                                          | 184 |

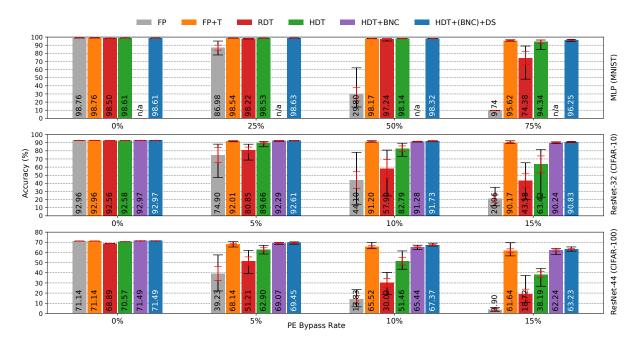

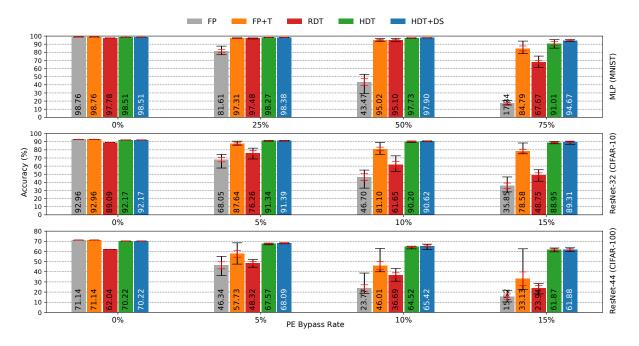

| 10.5    | Experimental Results 1                                                         | 186 |

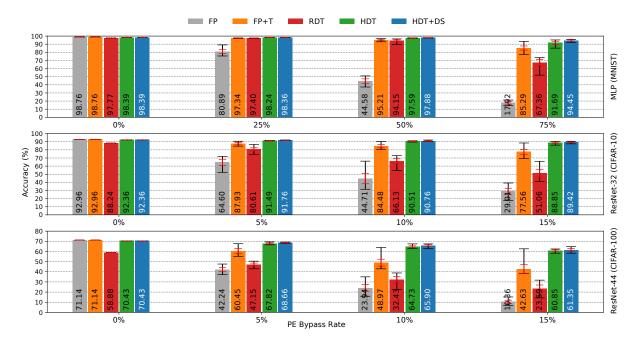

|         | 10.5.1 Resilience to Processing Element Bypassing 1                            | 186 |

|         | 10.5.2 Hardware Overhead Analysis 1                                            | 191 |

| 10.6    | Chapter Summary 1                                                              | 192 |

| 10.7    | Acknowledgements 1                                                             | 192 |

|         |                                                                                | 100 |

| Chapter |                                                                                | 193 |

|         |                                                                                | 194 |

|         | 5                                                                              | 195 |

| 11.3    | 1 0                                                                            | 197 |

|         | 1                                                                              | 197 |

|         |                                                                                | 203 |

|         | 1 1                                                                            | 204 |

|         | 1                                                                              | 205 |

| 11.5    | Experimental Results                                                           | 207 |

| 11.6 Chapter Summary                                                      | 211    |

|---------------------------------------------------------------------------|--------|

| 11.7 Acknowledgements                                                     | 211    |

|                                                                           |        |

| Chapter 12 Synergistic Co-design of Sparse DNNs and Hardware Accelerators |        |

| 12.1 Introduction                                                         |        |

| 12.2 Designing Complementary Sparsity Patterns                            | 216    |

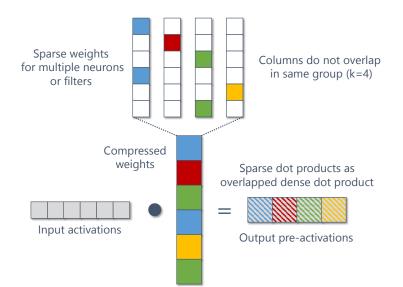

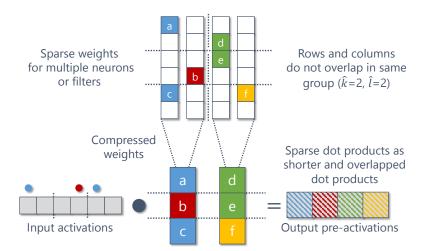

| 12.2.1 Packing Sparsity with Neuron/Filter Superposition                  | 217    |

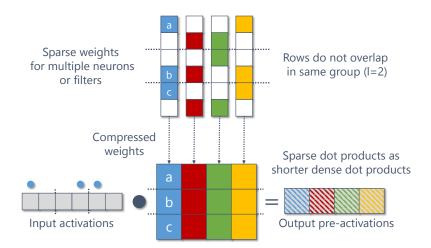

| 12.2.2 Packing Sparsity with Shortened Neurons/Filters                    | 218    |

| 12.2.3 Complementary Sparsity Patterns in Two Dimensions                  | 220    |

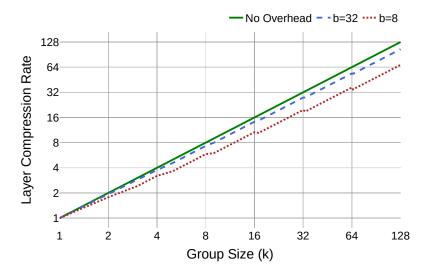

| 12.3 Evaluating Sparsity Type Expressiveness Through Analytical Models    | 221    |

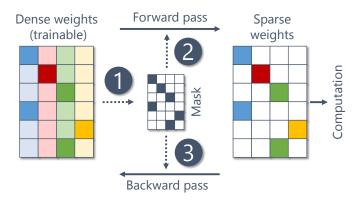

| 12.4 Evolving Sparsity Patterns in Training                               | 224    |

| 12.4.1 Overview of the Sparse Training Process                            | 225    |

| 12.4.2 Layer-wise Group Size Selection Steps                              | 226    |

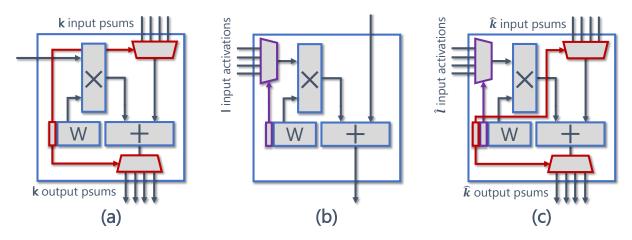

| 12.5 DNN Inference with Complementary Sparsity                            |        |

| 12.5.1 Packing Sparse Layers for Efficient Compression                    |        |

| 12.5.2 Processing Sparse Layers in the Dense Format                       |        |

| 12.6 Experimental Method                                                  |        |

| 12.6.1 Model Compression Experiments                                      |        |

| 12.6.2 Inference Performance Simulations                                  |        |

| 12.6.3 Hardware Measurements for Flow-Controlling MAC Units               |        |

| 12.7 Experimental Results                                                 |        |

| 12.7.1 Model Compression Results                                          |        |

| 12.7.2 Inference Performance Results                                      |        |

| 12.7.3 Overhead Results for Flow-Controlling MAC Units                    |        |

| 12.8 Chapter Summary                                                      |        |

| 12.9 Acknowledgements                                                     |        |

|                                                                           | . 210  |

| Chapter 13 Discussion                                                     | 247    |

| 13.1 Summary of Technical Chapters                                        |        |

| 13.2 Significance of Dissertation Research                                |        |

| 13.3 Open Questions and Future Directions                                 |        |

| 13.3.1 Comprehensive Characterization of DNN Redundancy                   |        |

| 13.3.2 Addressing Training Challenges of Proposed DNN Constraints         |        |

| 13.3.3 Exploring Interactions Between Proposed Techniques                 |        |

| 13.3.4 Harnessing DNN Resilience for Further Efficiency Improvements      |        |

| 13.3.5 Effective and Comprehensive Evaluation of DNN Reliability          |        |

| 13.3.6 Applicability to Future Algorithms and Hardware Technologies       |        |

| 13.3.7 Promoting Synergistic Avenues in DNN Processing System Design      |        |

| 13.4 Acknowledgements                                                     |        |

|                                                                           | ,. 230 |

| Chapter 14 Conclusion                                                     | 257    |

| Bibliography                                                              | 259    |

### LIST OF FIGURES

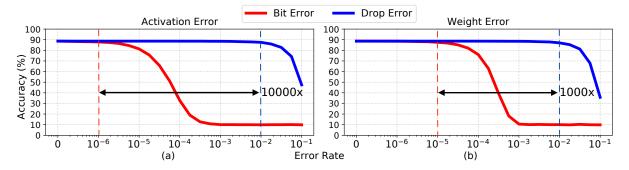

| Figure 1.1.  | DNN accuracy drop under (a) activation (b) weight bit-errors                                                                     | 4   |

|--------------|----------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 1.2.  | Misprediction examples caused by single-bit errors.                                                                              | 5   |

| Figure 2.1.  | Fully connected layer operation.                                                                                                 | 11  |

| Figure 2.2.  | Convolutional layer operation.                                                                                                   | 12  |

| Figure 2.3.  | Systolic array deep learning accelerator.                                                                                        | 15  |

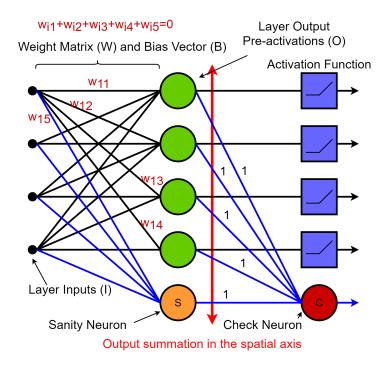

| Figure 6.1.  | Spatial checksum in the fully-connected layers                                                                                   | 59  |

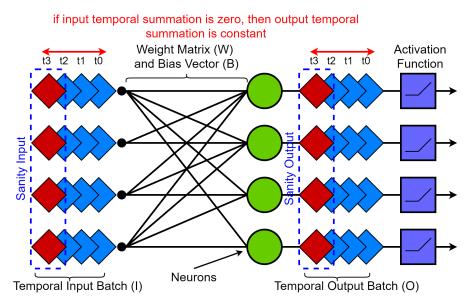

| Figure 6.2.  | Temporal checksum in the fully-connected layers.                                                                                 | 62  |

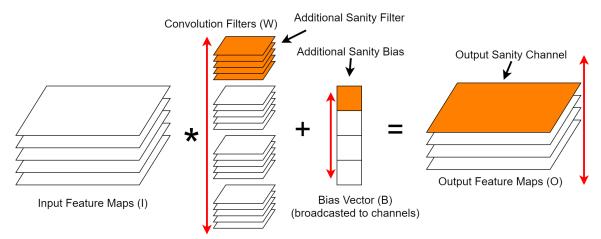

| Figure 6.3.  | Spatial checksum in the convolutional layers                                                                                     | 63  |

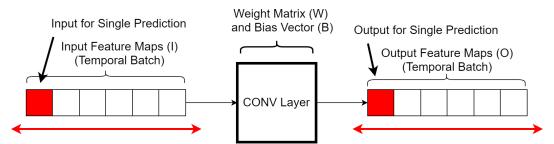

| Figure 6.4.  | Temporal checksum in the convolutional layers                                                                                    | 64  |

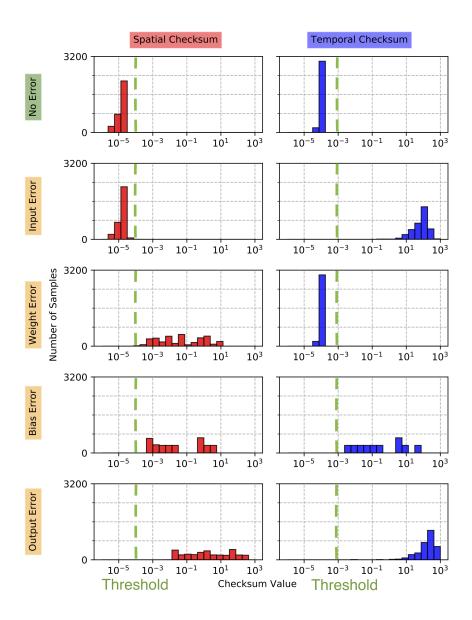

| Figure 6.5.  | The distribution of the measured checksum values                                                                                 | 68  |

| Figure 6.6.  | DNN accelerator with systolic array architecture.                                                                                | 73  |

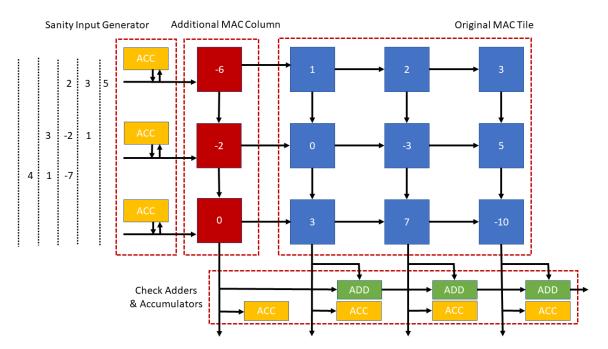

| Figure 6.7.  | Sanity-Check hardware on systolic array architecture                                                                             | 74  |

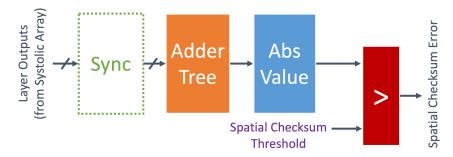

| Figure 6.8.  | Details of the spatial checksum hardware implementation                                                                          | 75  |

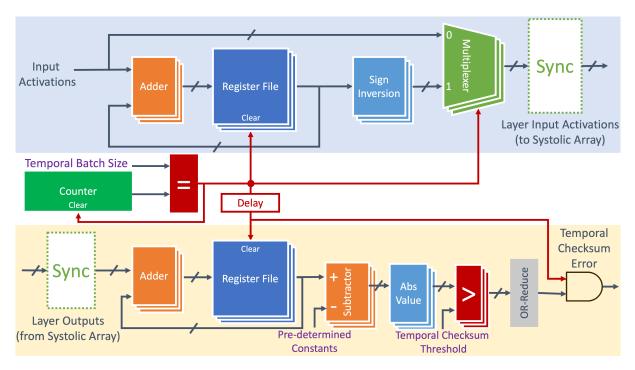

| Figure 6.9.  | Details of the temporal checksum hardware implementation                                                                         | 76  |

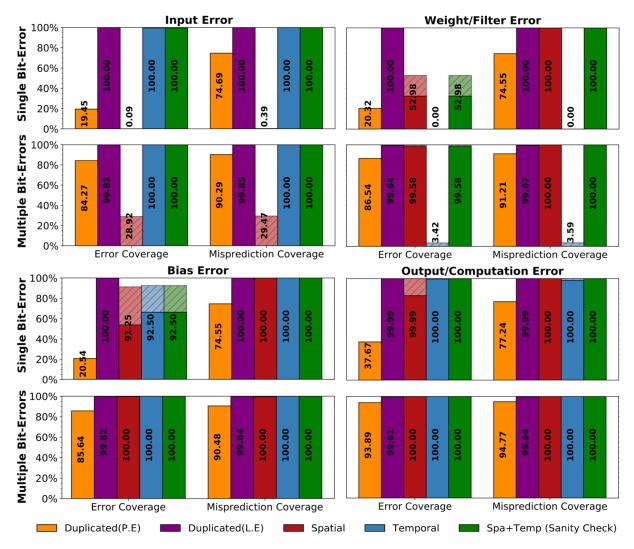

| Figure 6.10. | Error coverage and error-caused misprediction coverage rates for single and multiple bit-errors.                                 | 77  |

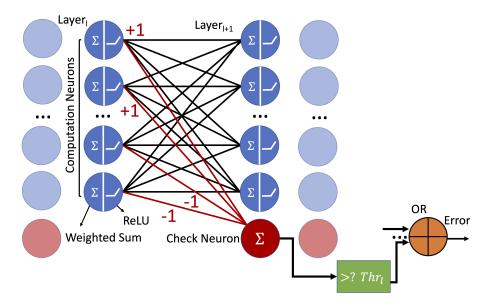

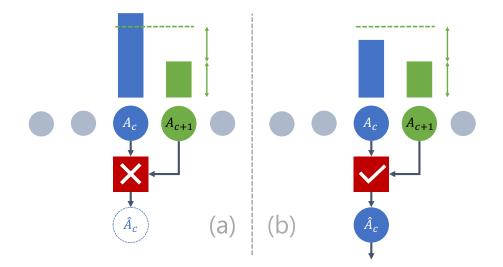

| Figure 7.1.  | Checking the balance in fully-connected layers                                                                                   | 86  |

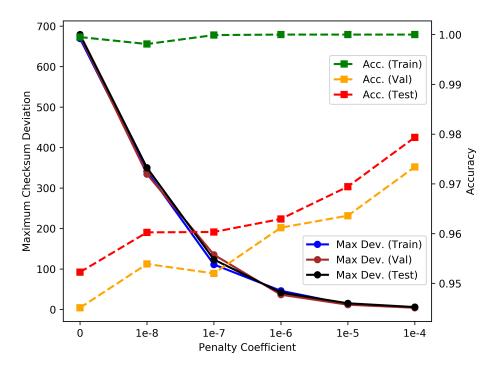

| Figure 7.2.  | Penalty coefficient vs. maximum checksum deviation and accuracy                                                                  | 88  |

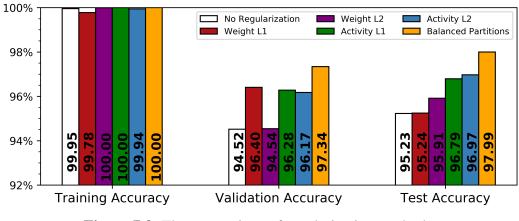

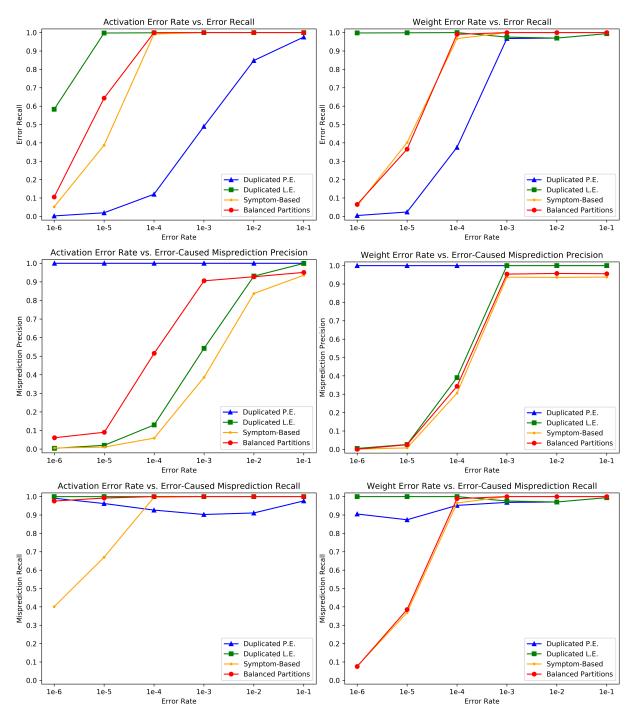

| Figure 7.3.  | The comparison of regularization methods                                                                                         | 89  |

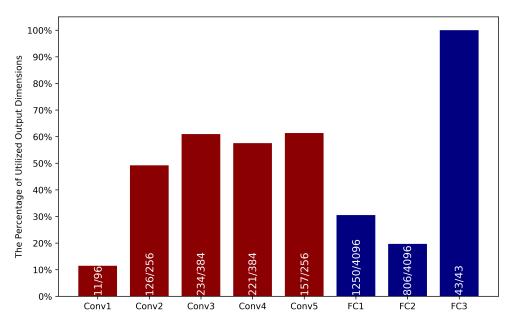

| Figure 7.4.  | The percentage of utilized output dimensions at each layer                                                                       | 90  |

| Figure 7.5.  | Error recall, error-caused misprediction precision, and error-caused mis-<br>prediction recall for activation and weight errors. | 91  |

| Figure 8.1.  | Anomaly detection with local magnitude comparison.                                                                               | 99  |

| Figure 8.2.  | Bit-errors vs. drop errors on (a) activation and (b) weight variables                                                            | 101 |

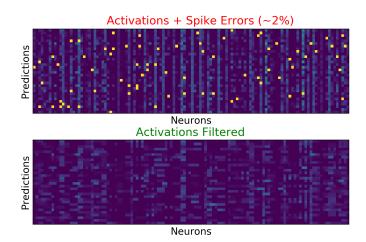

| Figure 8.3.  | Spike error removal from DNN activations with median filtering                     | 105 |

|--------------|------------------------------------------------------------------------------------|-----|

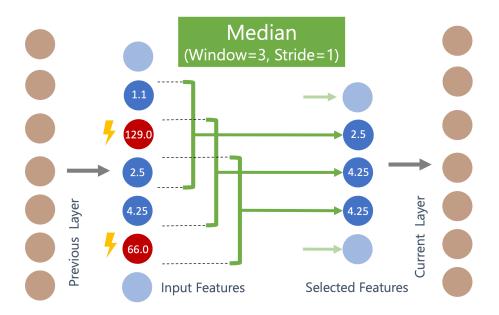

| Figure 8.4.  | Median feature selection in the fully connected layers                             | 106 |

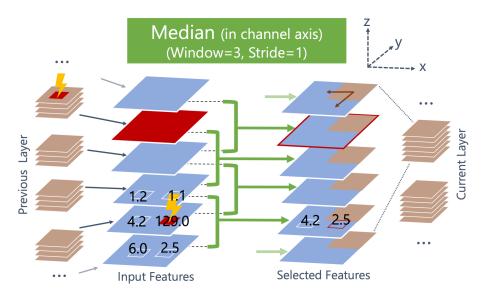

| Figure 8.5.  | Median feature selection in the channel dimension of the convolutional layers.     | 109 |

| Figure 8.6.  | Training DNNs in a two-stage process.                                              | 114 |

| Figure 8.7.  | The impact of median feature selection training                                    | 116 |

| Figure 8.8.  | Hardware implementation of anomaly detection and suppression operations.           | 118 |

| Figure 8.9.  | Anomaly detection and suppression unit integration into a DNN accelerator.         | 119 |

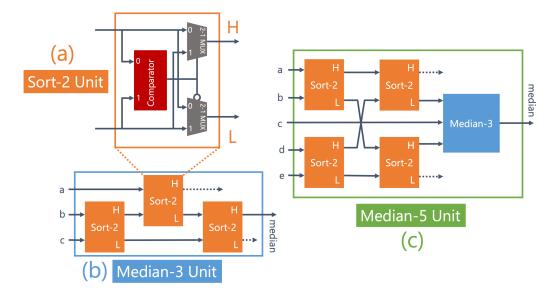

| Figure 8.10. | Sort-2, Median-3, and Median-5 hardware units                                      | 121 |

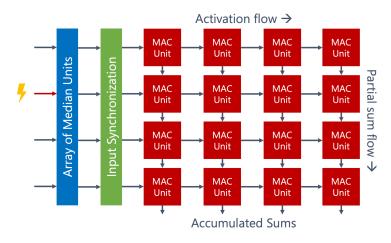

| Figure 8.11. | Median unit integration into systolic array architecture                           | 122 |

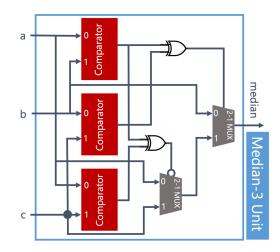

| Figure 8.12. | Optimized Median-3 unit                                                            | 123 |

| Figure 8.13. | Resilience improvements delivered by anomaly detection and suppression.            | 129 |

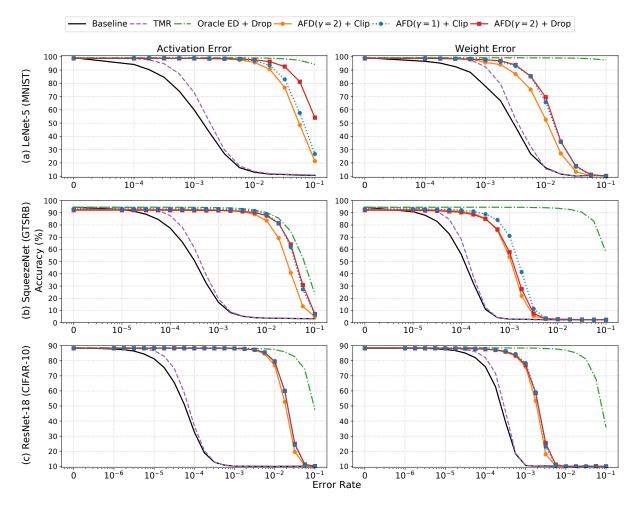

| Figure 8.14. | Resilience improvements delivered by median feature selection                      | 131 |

| Figure 8.15. | Area and power consumption of median feature selection                             | 136 |

| Figure 9.1.  | Weight distribution across neural network layers                                   | 143 |

| Figure 9.2.  | Sample weight distribution in a neural network layer                               | 144 |

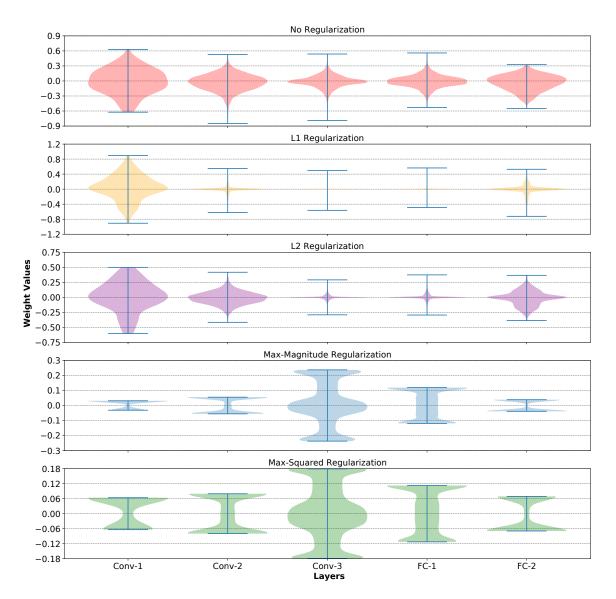

| Figure 9.3.  | Regularization effect on the numerical range of the LeNet-5 parameters             | 154 |

| Figure 9.4.  | Regularization effect on the numerical range of the ResNet-18 parameters.          | 155 |

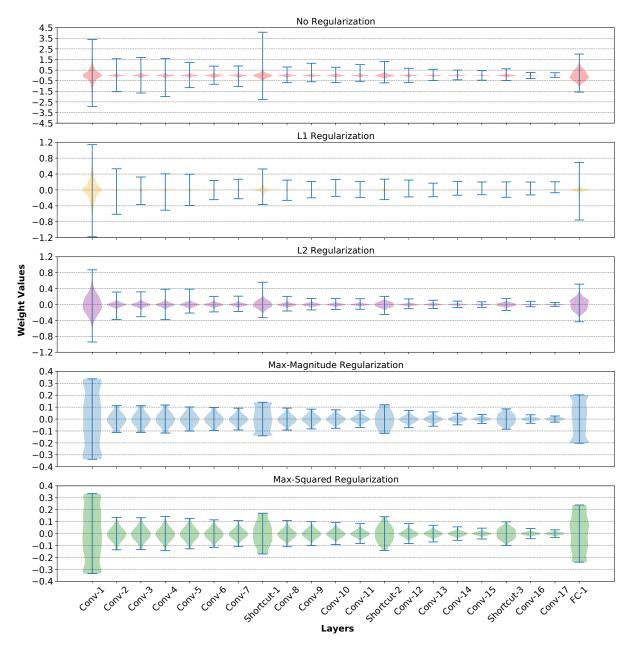

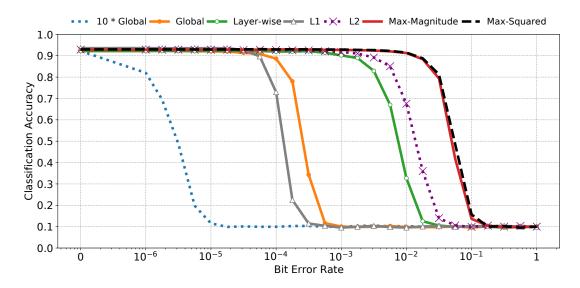

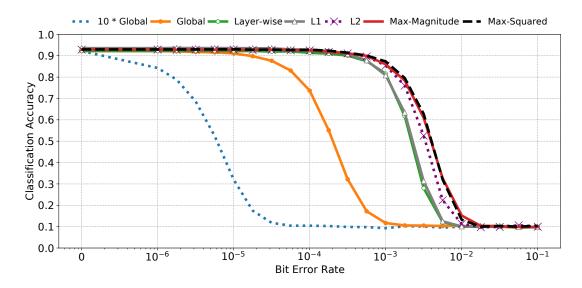

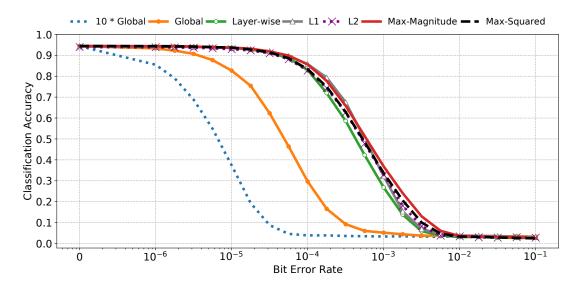

| Figure 9.5.  | Weight error rate vs. LeNet-5 test set classification accuracy on MNIST            | 156 |

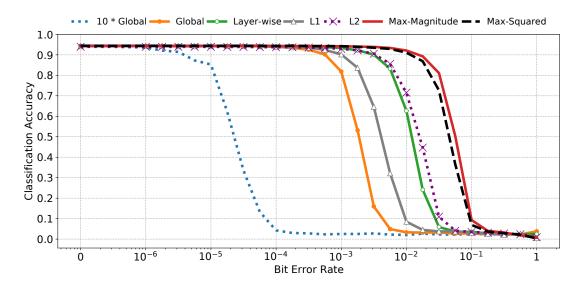

| Figure 9.6.  | Weight error rate vs. VGG-16 test set classification accuracy on CIFAR10.          | 157 |

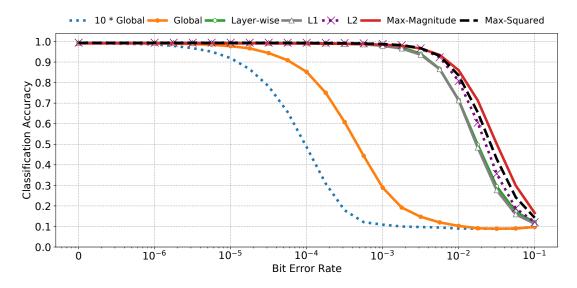

| Figure 9.7.  | Weight error rate vs. ResNet-18 test set classification accuracy on CIFAR10.       | 158 |

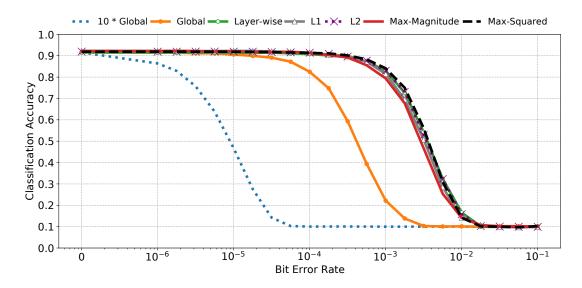

| Figure 9.8.  | Weight error rate vs. SqueezeNet test set classification accuracy on GTSRB.        | 159 |

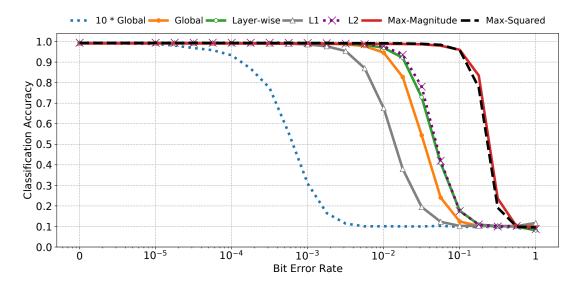

| Figure 9.9.  | Activation error rate vs. LeNet-5 test set classification accuracy on MNIST.       | 161 |

| Figure 9.10. | Activation error rate vs. VGG-16 test set classification accuracy on CI-<br>FAR10. | 162 |

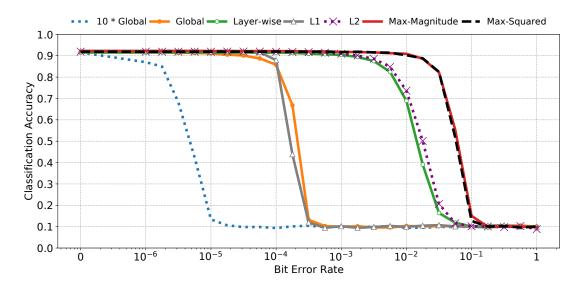

| Figure 9.11. | Activation error rate vs. ResNet-18 test set classification accuracy on CIFAR10.                                                                        | 163 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 9.12. | Activation error rate vs. SqueezeNet test set classification accuracy on GTSRB.                                                                         | 164 |

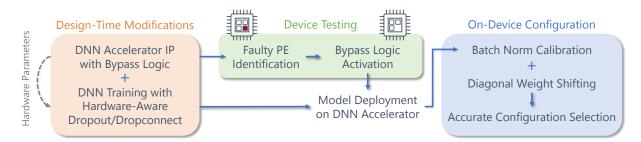

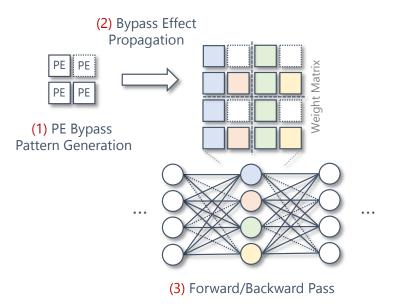

| Figure 10.1. | Overall summary of the proposed design flow                                                                                                             | 173 |

| Figure 10.2. | Bypass logic in (A) weight/input-stationary and (B) output-stationary pro-<br>cessing elements.                                                         | 175 |

| Figure 10.3. | Hardware-Aware Dropconnect in weight-stationary dataflow                                                                                                | 180 |

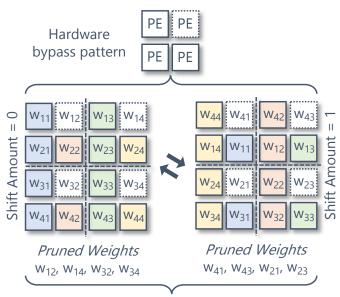

| Figure 10.4. | Diagonal shift operation in weight-stationary dataflow.                                                                                                 | 184 |

| Figure 10.5. | Resilience to bypass operations in weight-stationary dataflow                                                                                           | 187 |

| Figure 10.6. | Resilience to bypass operations in input-stationary dataflow                                                                                            | 188 |

| Figure 10.7. | Resilience to bypass operations in output-stationary dataflow                                                                                           | 189 |

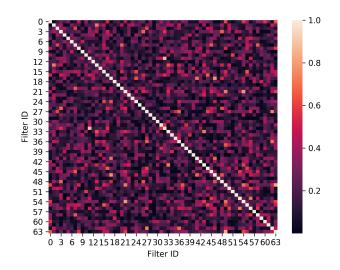

| Figure 11.1. | Pairwise output correlation magnitudes in a convolutional layer                                                                                         | 195 |

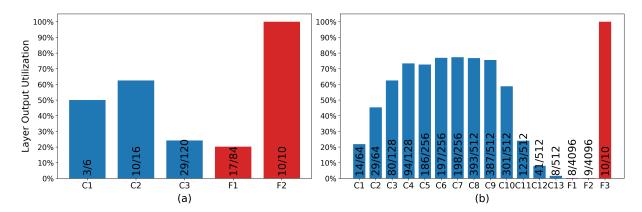

| Figure 11.2. | Layer output utilization in (a) LeNet-5 (on MNIST) and (b) VGG-16 (on CIFAR-10) architectures.                                                          | 197 |

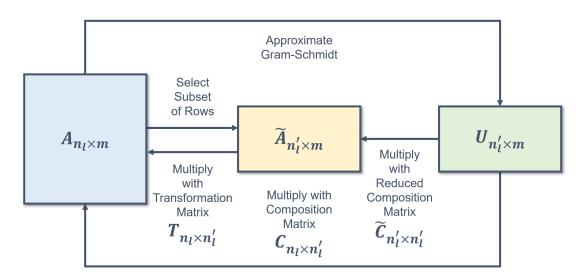

| Figure 11.3. | Relationships among the derived matrices.                                                                                                               | 201 |

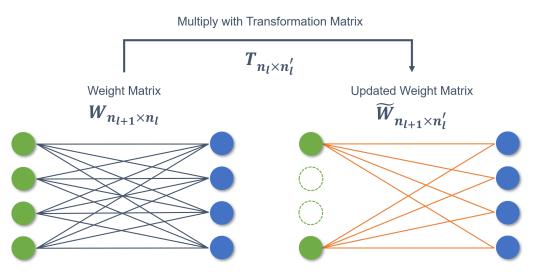

| Figure 11.4. | Weight matrix update process in the subsequent layer                                                                                                    | 203 |

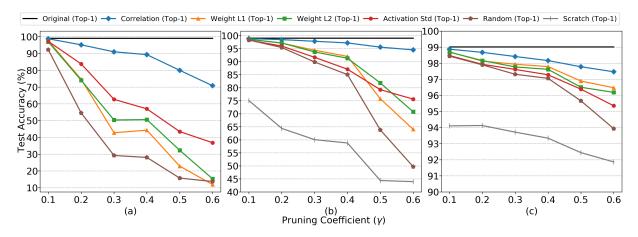

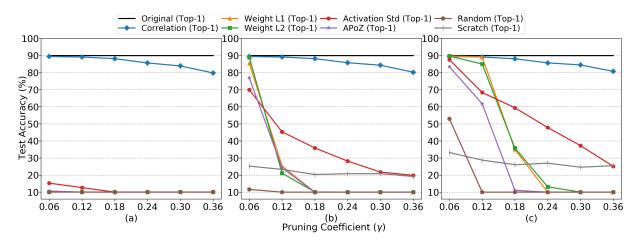

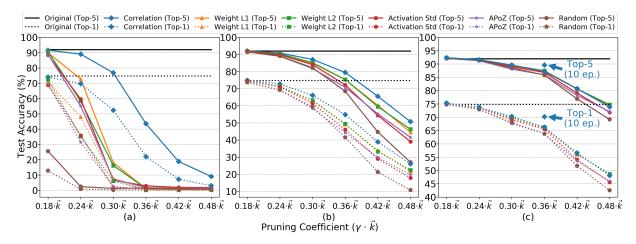

| Figure 11.5. | LeNet-5 accuracy drop (a) after one-shot pruning (b) after pruning + fine-<br>tuning (5 epochs) (c) after pruning + fine-tuning (until no improvement). | 208 |

| Figure 11.6. | VGG-16 accuracy drop (a) after one-shot pruning (b) after pruning + fine-<br>tuning (5 epochs) (c) after pruning + fine-tuning (until no improvement).  | 209 |

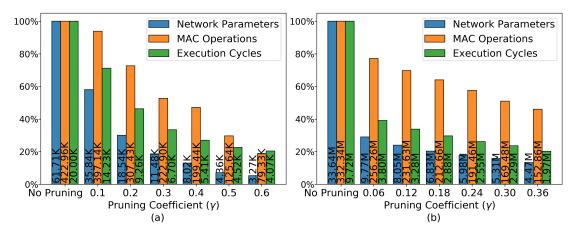

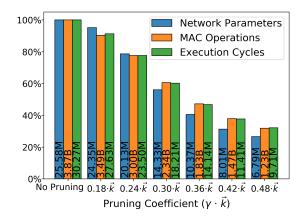

| Figure 11.7. | LeNet-5 (a) and VGG16 (b) hardware footprint after elimination                                                                                          | 209 |

| Figure 11.8. | ResNet-50 accuracy drop (a) after one-shot pruning (b) after pruning + fine-tuning (0.1 epoch) (c) after pruning + fine-tuning (1 epoch)                | 210 |

| Figure 11.9. | ResNet-50 hardware footprint after elimination                                                                                                          | 211 |

| Figure 12.1. | Neuron/filter superposition.                                                                                                                            | 218 |

| Figure 12.2. | Shortened neurons/filters.                                                                                                                              | 219 |

| Figure 12.3. | Complementary sparsity patterns in two dimensions.                                  | 220 |

|--------------|-------------------------------------------------------------------------------------|-----|

| Figure 12.4. | Sparsity generation and weight update in training                                   | 225 |

| Figure 12.5. | Packed group size vs. layer compression rate                                        | 229 |

| Figure 12.6. | Flow-controlling multiply-accumulate units for sparse inference                     | 231 |

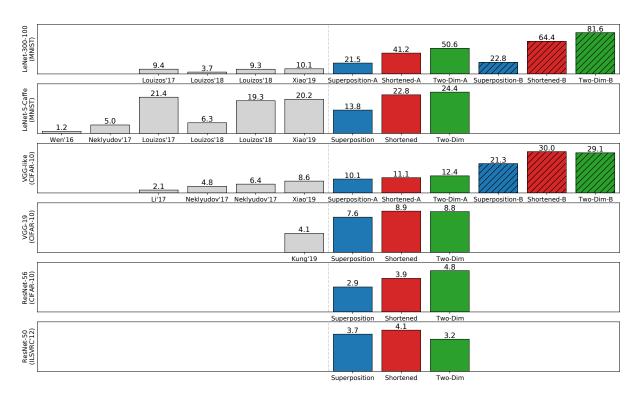

| Figure 12.7. | Inference speed-up ( $\times$ ) comparison for the complementary sparsity patterns. | 241 |

### LIST OF TABLES

| Table 6.1.   | Error detection guarantees of the Sanity-Check checksums                                                         | 65  |

|--------------|------------------------------------------------------------------------------------------------------------------|-----|

| Table 6.2.   | Memory and performance overhead for Sanity-Check checksums                                                       | 78  |

| Table 6.3.   | Area and power overhead of the Sanity-Check hardware modules                                                     | 79  |

| Table 7.1.   | Memory and performance overhead comparison.                                                                      | 93  |

| Table 8.1.   | Hardware area and power footprint for anomaly detection and suppression.                                         | 135 |

| Table 9.1.   | The impact of regularization on the full-precision (non-quantized) model accuracy.                               | 152 |

| Table 9.2.   | Tolerated BER (bit error rate) for various deep neural network resilience methods.                               | 160 |

| Table 9.3.   | The impact of regularization on the quantized model accuracy                                                     | 165 |

| Table 10.1.  | Area and power overheads of the bypass logic                                                                     | 191 |

| Table 12.1.  | Sparsity types vs. non-zero parameter configurations                                                             | 223 |

| Table 12.2.  | Group sizes enforced at each layer.                                                                              | 234 |

| Table 12.3.  | Classification error, parameter compression rate, and remaining FLOPs percentage for LeNet-300-100 on MNIST      | 236 |

| Table 12.4.  | Classification error, parameter compression rate, and remaining FLOPs percentage for LeNet-5-Caffe on MNIST.     | 237 |

| Table 12.5.  | Classification error, parameter compression rate, and remaining FLOPs percentage for VGG-like model on CIFAR-10. | 238 |

| Table 12.6.  | Classification error, parameter compression rate, and remaining FLOPs percentage for VGG-19 model on CIFAR-10.   | 238 |

| Table 12.7.  | Classification error, parameter compression rate, and remaining FLOPs percentage for ResNet-56 on CIFAR-10.      | 239 |

| Table 12.8.  | Classification accuracy, parameter compression rate, and remaining FLOPs percentage for ResNet-50 on ILSVRC'12   | 240 |

| Table 12.9.  | Area and power overheads (%) of the flow control enhancements                                                    | 243 |

| Table 12.10. | Efficiency improvements $(\times)$ for the flow-controlling MAC units                                            | 245 |

# LIST OF ALGORITHMS

| 6.1 | Details of the bit error injection procedure         | 71  |

|-----|------------------------------------------------------|-----|

| 9.1 | The methodology for error injection into DNN tensors | 151 |

#### ACKNOWLEDGEMENTS

I would like to acknowledge Professor Alex Orailoglu for his tremendous support as the chair of my committee. His guidance and efforts have been truly invaluable in the preparation of this dissertation and all associated publications.

The following chapters are re-organized re-prints of previous publications:

Chapter 6 is a re-organized reprint of the material as it appears in Elbruz Ozen and Alex Orailoglu, "Low-Cost Error Detection in Deep Neural Network Accelerators with Linear Algorithmic Checksums," *Journal of Electronic Testing (JETTA)*, vol. 36, no. 6, pp. 703–718, 2020 ([1]). The initial conference version of this manuscript is published in Elbruz Ozen and Alex Orailoglu, "Sanity-Check: Boosting the Reliability of Safety-Critical Deep Neural Network Applications," in *Proceedings of the 28th Asian Test Symposium (ATS)*, pp. 7–12, IEEE, 2019 ([2]). The dissertation author was the primary investigator and author of both papers.

Chapter 7 is a re-organized reprint of the material as it appears in Elbruz Ozen and Alex Orailoglu, "Concurrent Monitoring of Operational Health in Neural Networks Through Balanced Output Partitions," in *Proceedings of the 25th Asia and South Pacific Design Automation Conference (ASP-DAC)*, pp. 169–174, IEEE, 2020 ([3]). The dissertation author was the primary investigator and author of this paper.

Chapter 8 contains re-organized reprints of the material as it appears in Elbruz Ozen and Alex Orailoglu, "Shaping Resilient AI Hardware Through DNN Computational Feature Exploitation," *IEEE Design & Test (D&T)*, vol. 40, no. 2, pp. 59–66, 2023 ([4]), Elbruz Ozen and Alex Orailoglu, "Boosting Bit-Error Resilience of DNN Accelerators Through Median Feature Selection," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 39, no. 11, pp. 3250–3262, 2020 ([5]), and Elbruz Ozen and Alex Orailoglu, "Just Say Zero: Containing Critical Bit-Error Propagation in Deep Neural Networks with Anomalous Feature Suppression," in *Proceedings of the 39th International Conference on Computer-Aided Design (ICCAD)*, pp. 1–9, IEEE/ACM, 2020 ([6]). The dissertation author was the primary investigator and author of all three papers. Chapter 9 is a re-organized reprint of the material as it appears in Elbruz Ozen and Alex Orailoglu, "SNR: Squeezing Numerical Range Defuses Bit Error Vulnerability Surface in Deep Neural Networks," *ACM Transactions on Embedded Computing Systems (TECS)*, vol. 20, no. 5s, pp. 1–25, 2021 ([7]). The dissertation author was the primary investigator and author of this paper.

Chapter 10 is a re-organized reprint of the material as it appears in Elbruz Ozen and Alex Orailoglu, "Architecting Decentralization and Customizability in DNN Accelerators for Hardware Defect Adaptation," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 41, no. 11, pp. 3934–3945, 2022 ([8]). The dissertation author was the primary investigator and author of this paper.

Chapter 11 is a re-organized reprint of the material as it appears in Elbruz Ozen and Alex Orailoglu, "Squeezing Correlated Neurons for Resource-Efficient Deep Neural Networks," in *Proceedings of the European Conference on Machine Learning and Knowledge Discovery in Databases (ECML-PKDD) - Part II*, pp. 52–68, Springer, 2021 ([9]). The dissertation author was the primary investigator and author of this paper.

Chapter 12 is a re-organized reprint of the material as it appears in Elbruz Ozen and Alex Orailoglu, "Unleashing the Potential of Sparse DNNs Through Synergistic Hardware-Sparsity Co-Design," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 42, no. 4, pp. 1147–1160, 2023 ([10]). The initial conference version of this manuscript is published in Elbruz Ozen and Alex Orailoglu, "Evolving Complementary Sparsity Patterns for Hardware-Friendly Inference of Sparse DNNs," in *Proceedings of the International Conference on Computer-Aided Design (ICCAD)*, pp. 1–8, IEEE/ACM, 2021 ([11]). The dissertation author was the primary investigator and author of both papers.

The following chapters partially contain material from previous publications:

Chapter 1 partially contains material from Elbruz Ozen and Alex Orailoglu, "Low-Cost Error Detection in Deep Neural Network Accelerators with Linear Algorithmic Checksums," *Journal of Electronic Testing (JETTA)*, vol. 36, no. 6, pp. 703–718, 2020 ([1]), Elbruz

Ozen and Alex Orailoglu, "Concurrent Monitoring of Operational Health in Neural Networks Through Balanced Output Partitions," in *Proceedings of the 25th Asia and South Pacific Design Automation Conference (ASP-DAC)*, pp. 169–174, IEEE, 2020 ([3]), Elbruz Ozen and Alex Orailoglu, "Shaping Resilient AI Hardware Through DNN Computational Feature Exploitation," *IEEE Design & Test (D&T)*, vol. 40, no. 2, pp. 59–66, 2023 ([4]), Elbruz Ozen and Alex Orailoglu, "SNR: Squeezing Numerical Range Defuses Bit Error Vulnerability Surface in Deep Neural Networks," *ACM Transactions on Embedded Computing Systems (TECS)*, vol. 20, no. 5s, pp. 1–25, 2021 ([7]), and Elbruz Ozen and Alex Orailoglu, "Architecting Decentralization and Customizability in DNN Accelerators for Hardware Defect Adaptation," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 41, no. 11, pp. 3934–3945, 2022 ([8]).

Chapter 2 partially contains material from Elbruz Ozen and Alex Orailoglu, "Concurrent Monitoring of Operational Health in Neural Networks Through Balanced Output Partitions," in *Proceedings of the 25th Asia and South Pacific Design Automation Conference (ASP-DAC)*, pp. 169–174, IEEE, 2020 ([3]), Elbruz Ozen and Alex Orailoglu, "Boosting Bit-Error Resilience of DNN Accelerators Through Median Feature Selection," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 39, no. 11, pp. 3250–3262, 2020 ([5]), Elbruz Ozen and Alex Orailoglu, "Architecting Decentralization and Customizability in DNN Accelerators for Hardware Defect Adaptation," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 41, no. 11, pp. 3934–3945, 2022 ([8]), and Elbruz Ozen and Alex Orailoglu, "Unleashing the Potential of Sparse DNNs Through Synergistic Hardware-Sparsity Co-Design," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 42, no. 4, pp. 1147–1160, 2023 ([10]).

Chapter 3 partially contains material from Elbruz Ozen and Alex Orailoglu, "Low-Cost Error Detection in Deep Neural Network Accelerators with Linear Algorithmic Checksums," *Journal of Electronic Testing (JETTA)*, vol. 36, no. 6, pp. 703–718, 2020 ([1]), Elbruz Ozen and Alex Orailoglu, "Shaping Resilient AI Hardware Through DNN Computational Feature

Exploitation," IEEE Design & Test (D&T), vol. 40, no. 2, pp. 59–66, 2023 ([4]), Elbruz Ozen and Alex Orailoglu, "Boosting Bit-Error Resilience of DNN Accelerators Through Median Feature Selection," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 39, no. 11, pp. 3250–3262, 2020 ([5]), Elbruz Ozen and Alex Orailoglu, "Just Say Zero: Containing Critical Bit-Error Propagation in Deep Neural Networks with Anomalous Feature Suppression," in Proceedings of the 39th International Conference on Computer-Aided Design (ICCAD), pp. 1–9, IEEE/ACM, 2020 ([6]), Elbruz Ozen and Alex Orailoglu, "SNR: Squeezing Numerical Range Defuses Bit Error Vulnerability Surface in Deep Neural Networks," ACM Transactions on Embedded Computing Systems (TECS), vol. 20, no. 5s, pp. 1–25, 2021 ([7]), Elbruz Ozen and Alex Orailoglu, "Architecting Decentralization and Customizability in DNN Accelerators for Hardware Defect Adaptation," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 41, no. 11, pp. 3934–3945, 2022 ([8]), Elbruz Ozen and Alex Orailoglu, "Squeezing Correlated Neurons for Resource-Efficient Deep Neural Networks," in Proceedings of the European Conference on Machine Learning and Knowledge Discovery in Databases (ECML-PKDD) - Part II, pp. 52-68, Springer, 2021 ([9]), and Elbruz Ozen and Alex Orailoglu, "Unleashing the Potential of Sparse DNNs Through Synergistic Hardware-Sparsity Co-Design," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 42, no. 4, pp. 1147–1160, 2023 ([10]).

Chapter 13 partially contains material from Elbruz Ozen and Alex Orailoglu, "SNR: Squeezing Numerical Range Defuses Bit Error Vulnerability Surface in Deep Neural Networks," *ACM Transactions on Embedded Computing Systems (TECS)*, vol. 20, no. 5s, pp. 1–25, 2021 ([7]).

#### VITA

| 2017 | Bachelor of Science in Electrical and Electronics Engineering, İhsan Doğramacı<br>Bilkent University |

|------|------------------------------------------------------------------------------------------------------|

| 2020 | Master of Science in Computer Science (Computer Engineering), University of California San Diego     |

| 2023 | Doctor of Philosophy in Computer Science (Computer Engineering), University of California San Diego  |

#### PUBLICATIONS

Elbruz Ozen and Alex Orailoglu, "Unleashing the Potential of Sparse DNNs Through Synergistic Hardware-Sparsity Co-Design," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 42, no. 4, pp. 1147–1160, 2023.

Elbruz Ozen and Alex Orailoglu, "Shaping Resilient AI Hardware Through DNN Computational Feature Exploitation," *IEEE Design & Test (D&T)*, vol. 40, no. 2, pp. 59–66, 2023.

Elbruz Ozen and Alex Orailoglu, "Architecting Decentralization and Customizability in DNN Accelerators for Hardware Defect Adaptation," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 41, no. 11, pp. 3934–3945, 2022.

Elbruz Ozen and Alex Orailoglu, "Evolving Complementary Sparsity Patterns for Hardware-Friendly Inference of Sparse DNNs," in *Proceedings of the International Conference on Computer-Aided Design (ICCAD)*, pp. 1–8, IEEE/ACM, 2021.

Elbruz Ozen and Alex Orailoglu, "SNR: Squeezing Numerical Range Defuses Bit Error Vulnerability Surface in Deep Neural Networks," *ACM Transactions on Embedded Computing Systems* (*TECS*), vol. 20, no. 5s, pp. 1–25, 2021.

Elbruz Ozen and Alex Orailoglu, "Squeezing Correlated Neurons for Resource-Efficient Deep Neural Networks," in *Proceedings of the European Conference on Machine Learning and Knowledge Discovery in Databases (ECML-PKDD) - Part II*, pp. 52–68, Springer, 2021.

Elbruz Ozen and Alex Orailoglu, "Low-Cost Error Detection in Deep Neural Network Accelerators with Linear Algorithmic Checksums," *Journal of Electronic Testing (JETTA)*, vol. 36, no. 6, pp. 703–718, 2020.

Elbruz Ozen and Alex Orailoglu, "Just Say Zero: Containing Critical Bit-Error Propagation in Deep Neural Networks with Anomalous Feature Suppression," in *Proceedings of the 39th International Conference on Computer-Aided Design (ICCAD)*, pp. 1–9, IEEE/ACM, 2020.

Elbruz Ozen and Alex Orailoglu, "Boosting Bit-Error Resilience of DNN Accelerators Through Median Feature Selection," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 39, no. 11, pp. 3250–3262, 2020.

Elbruz Ozen and Alex Orailoglu, "Concurrent Monitoring of Operational Health in Neural Networks Through Balanced Output Partitions," in *Proceedings of the 25th Asia and South Pacific Design Automation Conference (ASP-DAC)*, pp. 169–174, IEEE, 2020.

Elbruz Ozen and Alex Orailoglu, "Sanity-Check: Boosting the Reliability of Safety-Critical Deep Neural Network Applications," in *Proceedings of the 28th Asian Test Symposium (ATS)*, pp. 7–12, IEEE, 2019.

Elbruz Ozen and Alex Orailoglu, "The Return of Power Gating: Smart Leakage Energy Reductions in Modern Out-of-Order Processor Architectures", in *Proceedings of the International Conference on Architecture of Computing Systems (ARCS)*, pp. 253–266, Springer, 2019.

#### ABSTRACT OF THE DISSERTATION

Algorithm-Centric Design of Reliable and Efficient Deep Learning Processing Systems

by

Elbruz Ozen

#### Doctor of Philosophy in Computer Science (Computer Engineering)

University of California San Diego, 2023

Professor Alex Orailoglu, Chair

Artificial intelligence techniques driven by deep learning have experienced significant advancements in the past decade. The usage of deep learning methods has increased dramatically in practical application domains such as autonomous driving, healthcare, and robotics, where the utmost hardware resource efficiency, as well as strict hardware safety and reliability requirements, are often imposed. The increasing computational cost of deep learning models has been traditionally tackled through model compression and domain-specific accelerator design. As the cost of conventional fault tolerance methods is often prohibitive in consumer electronics, the question of functional safety and reliability for deep learning hardware is still in its infancy. This dissertation outlines a novel approach to deliver dramatic boosts in hardware safety, reliability, and resource efficiency through a synergistic co-design paradigm. We first observe and make use of the unique algorithmic characteristics of deep neural networks, including plasticity in the design process, resiliency to small numerical perturbations, and their inherent redundancy, as well as the unique micro-architectural properties of deep learning accelerators such as regularity. The advocated approach is accomplished by reshaping deep neural networks, enhancing deep neural network accelerators strategically, prioritizing the overall functional correctness, and minimizing the associated costs through the statistical nature of deep neural networks. To illustrate, our analysis demonstrates that deep neural networks equipped with the proposed techniques can maintain accuracy gracefully, even at extreme rates of hardware errors. As a result, the described methodology can embed strong safety and reliability characteristics in mission-critical deep learning applications at a negligible cost. The proposed approach further offers a promising avenue for handling the micro-architectural challenges of deep neural network accelerators and boosting resource efficiency through the synergistic co-design of deep neural networks and hardware micro-architectures.

# Chapter 1 Introduction

# 1.1 Background

Deep learning techniques have revolutionized application design by providing an alternative paradigm that eliminates the need for manual software development steps [12] and offering capabilities for electronic systems that were almost unimaginable in the past decade.

The recent past has witnessed remarkable advancements in various deep learning tasks such as computer vision [13, 14, 15], speech recognition [16, 17], and natural language processing [18, 19]. Models such as ChatGPT [20] have demonstrated significant progress in text generation tasks and engaging in high-quality dialogue with humans. DALL·E 2 [21] can generate realistic images and art for the given text descriptions. Many driving assistance and FSD (full self-driving) systems heavily rely on deep learning methods [22, 23]. Deep learning has numerous practical application areas in healthcare, ranging from medical imaging to robotic-assisted surgery [24].

The outstanding success of deep learning techniques has resulted in a wide range of applications in practical domains, including but not limited to autonomous driving, healthcare, robotics, defense, and industrial automation, where intelligent systems have become an integral part of our infrastructure. Meanwhile, the practical requirements for such systems are not limited to mere algorithmic accuracy but also involve the satisfaction of strict hardware constraints such as safety, reliability, and resource efficiency.

# **1.2 Problem Definition**

It is widely recognized that DNNs (deep neural networks) incur high computational costs. Meanwhile, the continuing trend of increasing model sizes [25] is assumed to be a significant contributor behind the success of modern deep learning architectures. Numerous techniques, ranging from algorithmic model optimizations to hardware accelerator design, have been investigated in an effort to increase the resource efficiency of deep learning methods [26].

On the algorithmic side, the increasing computational cost of deep neural networks has been tackled mainly through the design of more efficient deep learning models [15, 27] and model compression methods such as pruning [28, 29, 30] and quantization [31, 32, 33, 34].

The increasing computational cost of DNNs has ignited further efforts to design hardware accelerators [26] that can deliver efficiency in the required operations. Spatial architectures such as systolic arrays are commonly used in recent DNN accelerators in industry [35] and academia [36, 37]. These architectures consist of regular tiles of PEs (processing elements) and perform tensor operations in a distributed manner by transferring variables locally among the neighboring units. The share of deep learning hardware accelerators is anticipated to grow noticeably in the semiconductor domain [38], and these architectures are expected to power billions of embedded artificial intelligence devices in the next decade.

Despite the significant efforts of the past decade, the computational cost of deep neural networks remains an important design consideration. *While isolated algorithmic and hardware optimization is capable of delivering noticeable gains in terms of efficiency, more algorithm-centric and synergistic design paradigms could offer tremendous potential for boosting resource efficiency in deep learning hardware systems.*

Both performance and energy efficiency constitute fundamental design considerations for embedded deep learning applications; strict functional safety constraints are frequently imposed furthermore in various practical application domains such as autonomous driving, healthcare devices, robotics, and industrial control systems. While operating in the field, exposure to harsh environmental conditions (e.g., high-energy particles, high temperature) over long durations increases the likelihood of hardware errors in these systems considerably. A hardware-caused error can impact functionality with potentially catastrophic consequences; thus, additional electronics safety mechanisms are an absolute requirement in these application domains. Moreover, the rise of machine intelligence systems has coincided with the recent seismic shifts in semiconductor manufacturing technology. The benefits delivered by Moore's Law [39] are expected to come to an end soon, and we have started to witness more pronounced variability between devices, heightened reliability issues such as aging effects, and increased yield loss with every new generation of semiconductor technology nodes [40, 41, 42, 43, 44].

In the context of exploring the safety of DNNs against naturally occurring [45] or adversarial [46, 47] input perturbations, the design of a robust DNN algorithm constitutes but a single aspect of a complex equation; the safety of the underlying hardware is of matching importance in ensuring an entirely trustable system. The tolerance of DNNs to noise and small numerical inaccuracies has been argued, but we are still quite a ways from figuring out the precise extent of tolerance due to their non-linear nature [48]. Even under the presumption of robustness to small numerical inaccuracies, hardware-level faults could pose a significant problem as they might result in relatively large numerical deviations up to the order of a few magnitudes larger than the original data if the significant bit positions are affected. Hardware-level faults can thus diminish accuracy to unacceptable levels, and even single-bit error incidents might compromise system safety by leading to unexpected network decisions.

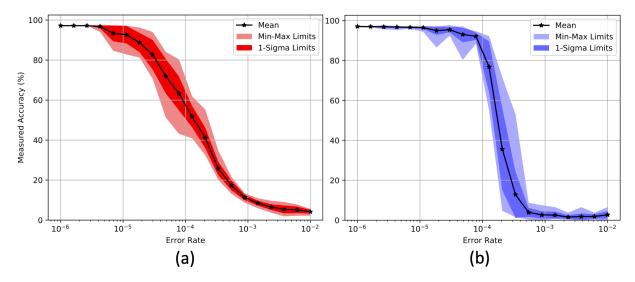

We perform an experimental analysis on AlexNet [49] (trained on the GTSRB dataset [50]) to demonstrate the issue by injecting bit errors into the activation values and the filter/weight coefficients, then measuring the expected accuracy of the network as a function of the error rate to determine the point where the DNN model experiences a noticeable accuracy drop. Figure 1.1 shows that the accuracy of the network exhibits a relatively sharp degradation at a specific error rate, and error rates surpassing this threshold noticeably distort the network decisions.

Second, we conduct another series of experiments, inspired by [47], in which we inject a

3

Figure 1.1. DNN accuracy drop under (a) activation (b) weight bit-errors.

single bit-error into the activation values and observe the cases where the neural network changes its decision. The signs pictured in Figure 1.2 have been misinterpreted to the errant commands noted on the caption above the traffic signs, clearly illustrating the havoc even single-bit errors can wreak in deep neural network outputs. In other words, DNNs demonstrate only a limited error-tolerant behavior as even a single-error occurrence may lead to unexpected decisions in DNN applications. An error detection method is consequently needed to preclude unsafe system decisions caused by possible misinterpretations stemming from such fault manifestations.

The safety-critical domains, such as the automotive industry, have been a challenging market for electronics and software designers because of extreme safety requirements [51]. As an unforeseen development can threaten human lives, automotive electronics are enhanced with strict safety features to withstand such eventualities. The state-of-the-art safety features in automotive electronics are comprised of the widely used ECC (error correction codes) to prevent SDCs (silent data corruptions) [52], and full redundancy (e.g., dual-core lockstep, or TMR (triple modular redundancy)[53]) to safeguard the execution path. Circuit-level hardening methods [54] do exist to detect and mitigate the effects of transient SEUs (single event upsets) or timing errors, but their notable area, delay, and power overheads make them a less appealing solution for consumer products.

Figure 1.2. Misprediction examples caused by single-bit errors.

Hardware safety and reliability have been studied widely since the dawn of electronic systems, and assurance of reliable operation has been an essential design consideration in numerous mission-critical application domains [55]. Meanwhile, conventional fault tolerance techniques in mission-critical electronics often interpret the correctness requirements in a rigid and structural fashion that is necessary in the context of general-purpose computing, yet the subsequent excessive costs and overheads restrict the wide-range applicability of these methods in resource-intensive and cost-sensitive commercial deep learning hardware systems. The wide-range adaptation of machine intelligence methods in consumer application domains with strict cost constraints, such as autonomous driving, has thus forced the investigation of techniques that can provide operational assurance in machine intelligence hardware at a negligible cost.

Moreover, significant efficiency and performance gains can be attained in artificial intelligence hardware if the enhanced resilience characteristics of deep neural networks are combined with aggressive hardware optimizations in CMOS (complementary metal-oxide-semiconductor) hardware devices. The outlined approach could further facilitate the adaptation of artificial intelligence devices constructed through emerging device technologies with the potential to deliver efficiency levels up to a few magnitudes higher than conventional digital computing, yet limited by the inherent imprecision and poor manufacturability problems. The outlined hardware efficiency pursuit requires innovative avenues for handling unprecedented error rates so that deep neural networks can operate accurately even under chaotic hardware conditions.

Fault tolerance is a challenging problem in the context of general-purpose computing,

as imposed safety mechanisms often remain agnostic to the possible resilience characteristics of the application. As a result, a worst-case approach ascribes even a minute change in the program variables to potential data corruption, necessitating the taking of further actions, such as correction or program re-execution, to assure the correctness of system behavior.

What makes this investigation for novel fault tolerance promising is the inherent resilience of neural networks to minor perturbations together with the learning flexibility of deep models even when constricted by imposed constraints. This flexibility of neural networks affords the construction of novel error identification mechanisms by shaping the inherent redundancy of deep learning algorithms. Moreover, the resilience of neural networks to minor perturbations opens up opportunities for approximate error mitigation without having to pay for perfect value restoration.

Algorithm-centric and synergistic design paradigms in this dissertation can offer avenues for interpreting the problem of hardware safety and reliability in a more functional manner, incorporating unique algorithmic characteristics of deep neural networks into the picture, thus enabling us to embed strong safety, reliability, and further efficiency characteristics into deep learning hardware systems often at negligible costs and overheads.

# **1.3** Dissertation Contribution

An effective approach to the outlined hardware challenges necessitates a holistic consideration of the hardware fabrics as well as the computational characteristics of deep learning algorithms to glean insights that can be harnessed for innovative solutions. The dissertation explores novel *algorithm-centric* and *synergistic* co-design techniques for converting unique algorithmic characteristics of deep neural networks, including *plasticity*, *resiliency*, and *redundancy*, as well as the hardware micro-architectural properties such as *regularity*, into significant boosts in safety, reliability, and resource efficiency to address challenging problems of hardware platforms used in artificial intelligence.

# **1.4 Dissertation Organization**

Chapter 2 presents a brief overview of related deep neural network concepts.

**Chapter 3** provides a comprehensive review of relevant studies in the prior literature. We aim to describe the current research progress in the corresponding domains and the outlined studies contribute to the shared understanding in the literature.

**Chapter 4** presents a high-level overview and motivates the unique perspectives that are explored in this dissertation.

**Chapter 5** outlines the explored research questions, introduces the unique characteristics of deep neural networks and the proposed research approach, and finally summarizes our progress within the scope of this dissertation.

The detailed technical discussion in this dissertation consists of **Chapters 6-12**:

**Chapter 6** presents an algorithmic method for the detection of hardware datapath errors in deep neural network accelerators through the use of the innate mathematical properties of deep neural network layers such as linearity.

**Chapter 7** demonstrates how the learning process can be harnessed to embed computational invariants into deep neural networks in training. Such invariants are utilized for detecting hardware datapath errors in deep neural network accelerators, even across the non-linear stages of the computations.

**Chapter 8** presents an alternative methodology to integrate fine-grained computational invariants into deep neural networks for highly precise hardware datapath error localization. The proposed error detection approach is coupled with novel and cost-effective error rectification techniques to allow algorithmic self-checking and correction of hardware errors in deep neural network accelerators.

**Chapter 9** observes the inherent resiliency of deep neural networks to small numerical perturbations and utilizes such resiliency characteristics for boosting the reliability of deep learning accelerators by restricting the numerical range in hardware and reshaping the numerical

distribution of deep neural network layers during the training process.

**Chapter 10** outlines a co-design methodology for enabling customized and cost-effective adaptation against permanent hardware defects in deep neural network accelerators through the synergistic design of the hardware platforms and decentralized deep neural network algorithms.

**Chapter 11** examines the significant output correlations among computational units within a deep neural network layer for quantitative redundancy characterization. We propose a novel deep neural network layer reduction and reconstruction process to obtain more compact and resource-efficient deep neural network architectures.

**Chapter 12** focuses on a unique hardware/software co-design methodology for boosting the synergy between sparsity patterns and hardware platforms. We demonstrate unique opportunities for performance and resource efficiency improvements in sparse deep neural network inference without suffering the micro-architectural problems posed by the irregular nature of unstructured sparsity.

**Chapter 13** incorporates a concise summary of the technical chapters and a detailed discussion about the significance of the technical results. Furthermore, we present our viewpoints regarding the open questions and potential directions in this research domain.

Chapter 14 presents the conclusion statements of the dissertation.

# **1.5** Acknowledgements

Chapter 1 partially contains material from Elbruz Ozen and Alex Orailoglu, "Low-Cost Error Detection in Deep Neural Network Accelerators with Linear Algorithmic Checksums," *Journal of Electronic Testing (JETTA)*, vol. 36, no. 6, pp. 703–718, 2020 ([1]), Elbruz Ozen and Alex Orailoglu, "Concurrent Monitoring of Operational Health in Neural Networks Through Balanced Output Partitions," in *Proceedings of the 25th Asia and South Pacific Design Automation Conference (ASP-DAC)*, pp. 169–174, IEEE, 2020 ([3]), Elbruz Ozen and Alex Orailoglu, "Shaping Resilient AI Hardware Through DNN Computational Feature Exploitation,"

*IEEE Design & Test (D&T)*, vol. 40, no. 2, pp. 59–66, 2023 ([4]), Elbruz Ozen and Alex Orailoglu, "SNR: Squeezing Numerical Range Defuses Bit Error Vulnerability Surface in Deep Neural Networks," *ACM Transactions on Embedded Computing Systems (TECS)*, vol. 20, no. 5s, pp. 1–25, 2021 ([7]), and Elbruz Ozen and Alex Orailoglu, "Architecting Decentralization and Customizability in DNN Accelerators for Hardware Defect Adaptation," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 41, no. 11, pp. 3934–3945, 2022 ([8]).

# Chapter 2

# An Overview of Relevant Deep Neural Network Concepts

The central computation unit in a DNN (deep neural network) is called a *neuron*, whose responsibility is taking a weighted sum of its inputs and processing the sum with a non-linear activation function. The neurons are organized as a sequence of layers, with the network getting deeper as the number of layers increases. Modern CNNs (convolutional neural networks) used in computer vision tasks [13, 49, 56, 57] heavily rely on two layer types, namely, *convolutional* and *fully-connected*, where the input is initially processed by a series of convolution layers to extract the useful features, with the fully-connected layers subsequently performing the final classification task. Moreover, deep neural networks frequently employ non-linear activation functions and various other layer types, including pooling, batch normalization, Dropout, and Dropconnect layers [26].

# 2.1 Common Layer Types in Deep Neural Networks

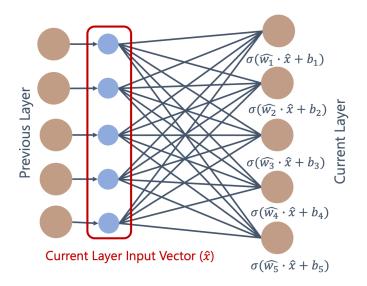

## 2.1.1 Fully Connected Layer

Fully connected layers carry out a vector-matrix multiplication operation. Layer inputs could be considered as individual vectors. Fully connected layer weights are represented in the form of a matrix where each matrix column is associated with an individual neuron. A single element in the input vector is called an *input feature*. Fully connected layers multiply input

Figure 2.1. Fully connected layer operation.

vectors with the weight matrix, include the bias vector, then process the result with the non-linear activation function to generate the layer outputs, as demonstrated in Figure 2.1.

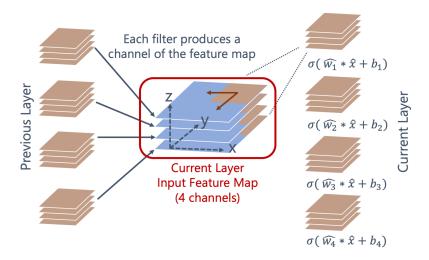

#### 2.1.2 Convolutional Layer

Unlike the fully-connected layers, convolutional layer neurons are locally connected to the previous layer, and the weight values are shared among different neurons. As a result, the layer behavior could be visualized more naturally with a convolution operation. The input feature map is convolved with several filters where each of them is responsible for producing a channel of the output feature map, as in Figure 2.2. The convolutional layer operation further involves the inclusion of the bias, and the final processing of the result by a non-linear activation function.

#### 2.1.3 Non-linear Activation Functions

Non-linear activation functions are frequently used after fully connected and convolution layers, and they are essential for the complex non-linear behavior of deep neural networks. Typical choices for the non-linear activation functions include widely-used *ReLU (rectified linear unit)*, *leaky ReLU, sigmoid*, and *tanh (hyperbolic tangent)*. Further information on non-linear activation functions can be found in [26].

Figure 2.2. Convolutional layer operation.

### 2.1.4 Pooling

Pooling is used in CNNs to reduce the dimensions of the feature maps. Pooling layers perform a down-sampling operation by dividing the feature maps into small windows (e.g.,  $2 \times 2$  window) and reducing the window into a single entry. The typically used reduction operators include selecting the maximum entry (i.e., max pooling) or computing the mean (i.e., mean pooling) at each window.

### 2.1.5 Batch Normalization

Batch normalization [58] is commonly used in deep neural networks to reduce internal covariate shift and accelerate model convergence in the training process. Batch normalization adjusts the outputs of each neuron or convolution filter in training by normalizing the outputs with their mini-batch statistics ( $\mu_B$ ,  $\sigma_B^2$ ), then scaling and shifting the normalized results with two learned coefficients  $\sigma_L$  and  $\mu_L$ , as in Equation (2.1). A small coefficient ( $\varepsilon$ ) is used to assure numerical stability.

$$\hat{x} = \frac{x - \mu_B}{\sqrt{\sigma_B^2 + \varepsilon}} \times \sigma_L + \mu_L \tag{2.1}$$

A similar normalization step is performed at inference time; however, mini-batch statistics are replaced by the static values of global mean and variance that are profiled in training.

### 2.1.6 Dropout and Dropconnect

Deep neural networks could overfit into training data and exhibit poor generalization to test examples upon deployment. Dropout [59] and Dropconnect [60] have been previously investigated, and their effectiveness has been established for mitigating the overfitting problem. The presence of a neuron under *Dropout* is subject to a predetermined probability, with the outputs of absent neurons being set to zero in a training iteration. All neurons are considered to be present at test time, yet their output contribution is re-adjusted to match the training distribution by scaling either the current layer's outputs or the next layer's weights. *Dropconnect* drops individual weights instead of neuron outputs by subjecting the presence of each weight to the given probability in the applied layer. The training distribution can be maintained at test time through a sampling process that is similar to the training phase or utilizing a scaled version of the weights with no dropping.

## 2.2 Loss Function and DNN Training Process

The training procedure involves a *loss function*, which measures the distance between the expected and produced DNN outputs. To illustrate, a commonly used loss function for single-label classification problems, categorical cross-entropy, can be expressed as follows for a batch of training examples:

$$-\frac{1}{N}\sum_{i=1}^{N}\sum_{c=1}^{C}y_{i,c}\log(p_{i,c})$$

(2.2)

In Equation (2.2), *N* and *C* denote the training batch size and the total number of classes. The true binary label is represented as  $y_{i,c}$  for the example *i* and class *c*. For single-label classification,  $y_{i,c} = 1$  holds only for a single *c* for a particular example *i*.  $p_{i,c}$  denotes the predicted output probability produced by the output layer (with *Softmax* activation) of the network. Training is carried out by calculating the gradient of deep neural network weights through the backpropagation algorithm and updating the weights of each layer to reduce the loss at each step until a minimal point is found.

## 2.3 DNN Inference with Spatial Hardware Accelerators

The analysis in [26, 61] classifies deep learning accelerators into two primary categories. The first group, *temporal architectures*, includes designs with vector-type instructions such as CPUs (central processing units) and GPUs (graphics processing units). The second group, *spatial architectures*, relies on distributed dataflow processing through a large number of processing elements.

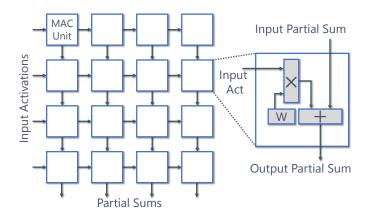

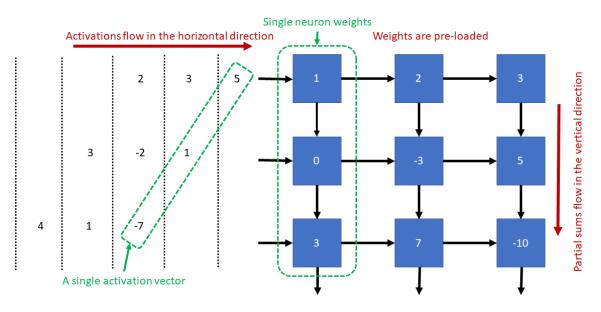

This section will focus on a typical example of spatial deep neural network accelerators, such as systolic arrays, as they will be used for analysis in the later technical chapters. Systolic arrays are widely adapted in practice to improve the inference performance and efficiency of deep neural networks [35, 36]. A systolic array consists of a 2-dimensional grid of MAC (multiply-accumulate) units as in Figure 2.3 where the weights of a single neuron or filter are mapped into a single column. When an input activation vector is provided to a column, each MAC unit acquires the accumulated sum from the neighboring MAC unit, multiplies the provided input activation with the stored weight, updates the accumulated sum, and forwards the updated sum to the next neighboring unit. The transfer of the sums allows a dot product to be computed at each column, which translates into a vector-matrix multiplication in the entire grid.

The outlined design can be classified as a *weight-stationary* architecture that maximizes weight reuse by pinning weights into processing elements during computation. Inputs and outputs are transferred through broadcasting or local communication across units. Google's TPU [35] is a well-known example of a weight-stationary architecture.

Alternative DNN accelerator dataflows discussed in [26, 62, 63] differ from weight-

Figure 2.3. Systolic array deep learning accelerator.

stationary designs based on the particularities of the data reuse type. To illustrate, *input-stationary* dataflow maximizes input reuse by tiling and pinning layer inputs into the processing elements. Layer weights and partial sums are transferred across processing elements, and the processing element design is often identical to the one used for the weight-stationary dataflow. While layer inputs and weights are transferred across processing elements in the *output-stationary* dataflow, the partial sum belonging to an output location is pinned to and updated within the same processing element.

## 2.4 Acknowledgements

Chapter 2 partially contains material from Elbruz Ozen and Alex Orailoglu, "Concurrent Monitoring of Operational Health in Neural Networks Through Balanced Output Partitions," in *Proceedings of the 25th Asia and South Pacific Design Automation Conference (ASP-DAC)*, pp. 169–174, IEEE, 2020 ([3]), Elbruz Ozen and Alex Orailoglu, "Boosting Bit-Error Resilience of DNN Accelerators Through Median Feature Selection," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 39, no. 11, pp. 3250–3262, 2020 ([5]), Elbruz Ozen and Alex Orailoglu, "Architecting Decentralization and Customizability in DNN Accelerators for Hardware Defect Adaptation," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 41, no. 11, pp. 3934–3945, 2022 ([8]), and

Elbruz Ozen and Alex Orailoglu, "Unleashing the Potential of Sparse DNNs Through Synergistic Hardware-Sparsity Co-Design," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 42, no. 4, pp. 1147–1160, 2023 ([10]).

# Chapter 3 Literature Review