#### Negative Capacitance Field-Effect Transistor Design and Machine Learning Applications in Compact Models by Ming-Yen Kao

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Chenming Hu, Chair

Professor Sayeef Salahuddin

Professor Junqiao Wu

Spring 2022

# Negative Capacitance Field-Effect Transistor Design and Machine Learning Applications in Compact Models

Copyright © 2022 by Ming-Yen Kao

#### **Abstract**

Negative Capacitance Field-Effect Transistor Design and Machine Learning Applications in Compact Models by Ming-Yen Kao

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley Dr. Chenming Hu, Chair

With the scaling of the transistor, fabrication of an actual device and modeling of an ultra-short channel transistor becomes more and more challenging. Dr. Salahuddin proposed a negative capacitance field-effect transistor (NCFET) in 2008. By utilizing the ferroelectric negative capacitance region with proper capacitance matching a ferroelectric layer with a dielectric layer, the overall effective oxide thickness could be further thinned down without affecting much of the carrier mobility.

A technique of optimization of an NCFET will be proposed in chapter 2. By utilizing process techniques like mask oxidation, a non-uniform interfacial layer can be formed to create a more uniform metal-oxide-semiconductor capacitance along the channel ( $C_{\rm mos}$ ). The overall capacitance matching of an NCFET can be improved because of a uniform  $C_{\rm mos}$  profile. Chapter 3 will introduce a simulation scheme of NCFETs variation due to dielectric grains within a ferroelectric film. This scheme can be applied to the future estimation of NCFETs variation given the grains' size and the ferroelectric parameters.

The effect and compact modeling of the polarization gradient effect will be demonstrated in Chapter 4. With the feature of polarization gradient effect in an NCFET compact model, the characteristics of an NCFET can be better captured, such as negative drain resistance and negative drain-induce barrier

effect (DIBL). Energy analysis of an NCFET will be presented in Chapter 5. The consistency between TCAD energy calculation by the integral over the grids with the Landau equation and power consumption calculation from the circuit is shown in detail.

Negative capacitance benefits on FinFET and gate-all-around (GAA) FET will be presented in chapters 6 & 7, respectively. Baseline devices of a FinFET and a GAAFET are made in technology computer-aided design (TCAD) and are calibrated to International Roadmap for Devices and Systems (IRDS) tables. NC parameters are also extracted from an experiment on metal-oxide-semiconductor capacitance (MOSCAP). How many nodes NC extends the baseline will be discussed. A compact model of an anti-ferroelectric on an NCFET will be presented in Chapter 8.

Potential applications of machine learning will be illustrated in Chapters 9 & 10. Machine learning-assisted parameter extraction will be presented in Chapter 9. In the long run, using machine learning-assisted models as an alternative to the conventional equation-based compact models will be shown in Chapter 10. In the end, Chapter 11 will conclude chapters and propose some future work.

To my family and friends: Past, Present, and Future

## Content

| Content                                                               | · ii    |

|-----------------------------------------------------------------------|---------|

| List of Figures                                                       | V       |

| List of Tables                                                        | · x iii |

| 1. Introduction                                                       | 1       |

| 1.1 Challenges of Nano-electronics                                    | 1       |

| 1.2 Theory of Negative Capacitance Field-Effect Transistor            |         |

| 1.3 Berkeley short-channel IGFET Model (BSIM)                         |         |

| 2. Optimization of NCFET by Matching Dielectric and Ferroel           |         |

| Nonuniformly Along the Channel                                        | 7       |

| 2.1 Motivation                                                        | 7       |

| 2.2 Device characterization and discussion                            | 8       |

| 2.3 Chapter Summary                                                   | 15      |

| 3. Variation Caused by Spatial Distribution of Dielectric and Ferroel | ectric  |

| Grains in a Negative Capacitance Field-Effect Transistor              | 16      |

| 3.1 Motivation                                                        | 16      |

| 3.2 Device characterization                                           | 18      |

| 3.3 Discussion                                                        | 25      |

| 3.4 Chapter Summary                                                   | 29      |

| 4. Analysis and Modeling of Polarization Gradient Effect on Neg       | gative  |

| Capacitance FET                                                       | 30      |

| 4.1 Motivation                                                        | 30      |

| 4.2 TCAD Simulation Setup                                             | 32      |

| 4.3 TCAD Analysis of Polarization Gradient Effect                     | 33      |

| 4.4 Compact Model of Polarization Gradient Effect               | 34  |

|-----------------------------------------------------------------|-----|

| 4.5 Chapter Summary                                             |     |

|                                                                 |     |

| 5. Energy Storage and Reuse in Negative Capacitance             | 43  |

| 5.1 Motivation                                                  | 43  |

| 5.2 Energy Analysis of NC-MOSCAPs                               | 46  |

| 5.3 Energy Analysis of NC-MOSFETs                               | 49  |

| 5.4 Chapter Summary                                             | 54  |

| 6. Negative Capacitance Enables FinFET Scaling Beyond 3nm Node  | 56  |

| 6.1 Motivation                                                  | 56  |

| 6.2 TCAD Simulation                                             | 57  |

| 6.3 Results and Discussion                                      |     |

| 6.4 Chapter Summary                                             | 69  |

| 7. Negative Capacitance Enables GAA Scaling Beyond 0.5nm Node   | 70  |

| 7.1 Motivation                                                  |     |

| 7.2 TCAD Simulation Setup                                       |     |

| 7.3 Results and Discussion                                      |     |

| 7.4 Chapter Summary                                             | 83  |

| 8. Compact Model and Benefits of Antiferroelectric in NCFETs    | 85  |

| 8.1 Motivation                                                  | 85  |

| 8.2 Methods                                                     | 87  |

| 8.3 Results                                                     | _   |

| 8.4 Chapter Summary                                             | 92  |

| 9. Deep Learning-Based BSIM-CMG Parameter Extraction for 10nm F |     |

| 9.1 Motivation                                                  |     |

| 9.2 Proposed Method                                             |     |

| 9.3 Results and Discussion                                      |     |

| 9.4 Chapter Summary                                             | 101 |

| 10. Deep-Learning-Assisted Physics-Driven GAAFET I-V Modeling   | 102 |

| 10.1 Motivation                                                 | 102 |

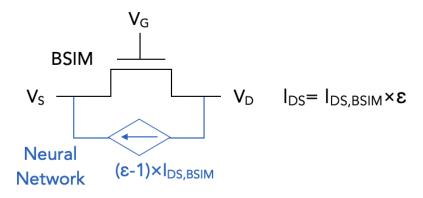

| 10.2 Deep-Learning-Assisted IV Model | 103 |

|--------------------------------------|-----|

| 10.3 Neural Network Design           | 105 |

| 10.4 Dataset                         | 107 |

| 10.5 Results and Discussion          | 107 |

| 10.6 Chapter Summary                 | 109 |

| 11. Summery                          | 110 |

| 11.1 Chapters Summary                | 110 |

| 11.2 Future Work                     | 111 |

# **List of Figures**

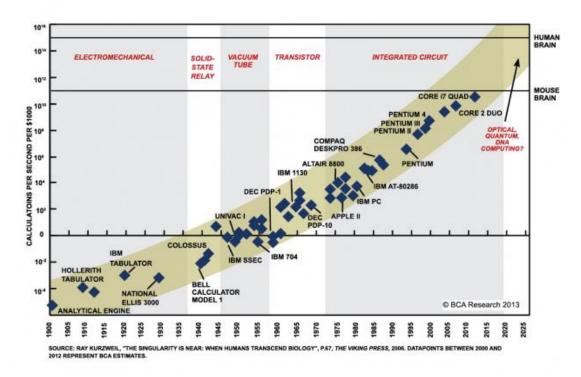

| 1.1 | Calculations per second per 1,000 USD versus time. Exponential growth can be observed throughout 100 years. [132]                                                                                                                                                                                                                                                                |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

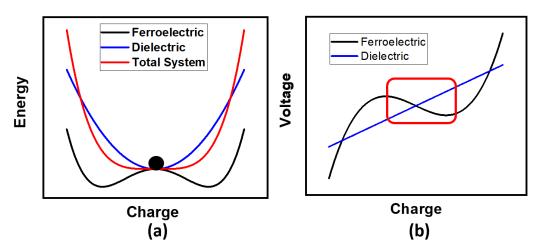

| 1.2 | (a) Energy versus charge plot of FE, DE, and the total system of FE and DE. (b) Voltage versus charge plot of FE and DE                                                                                                                                                                                                                                                          |

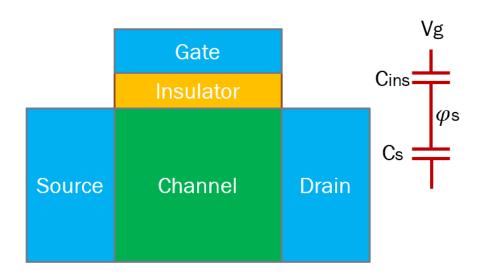

| 1.3 | Cartoon graph of a MOSFET                                                                                                                                                                                                                                                                                                                                                        |

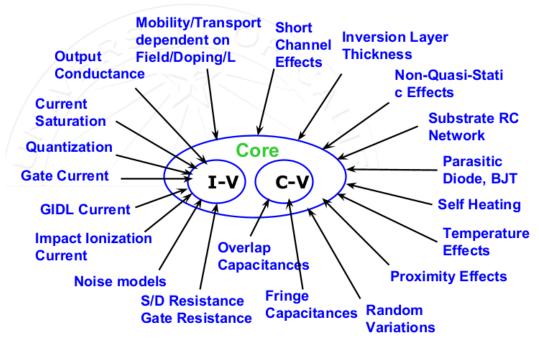

| 1.4 | Architecture of BSIM from Prof. Chenming Hu's presentation in Sep 2013.                                                                                                                                                                                                                                                                                                          |

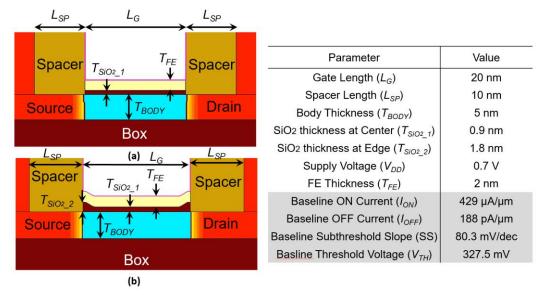

| 2.1 | The simulated device structure with (a) uniform thickness of interfacial layer and with (b) nonuniform thickness of interfacial layer. Table on the right-hand side lists important device parameters. The shaded parameters are for the baseline device. The baseline device has the same structure as (a), but without an FE layer.                                            |

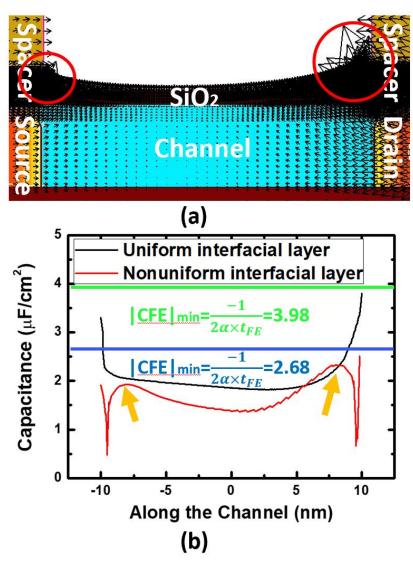

| 2.2 | (a) The electric field at $V_g = 0V$ and $V_d = 0.7V$ . The red circles highligh the higher electric field at the edges of the channel. (b) Capacitance versus position along the channel at $V_g = 0.7V$ . The green line and the black curve are the traditional capacitance matching design, and the blue line and the red curve are our proposed capacitance matching design |

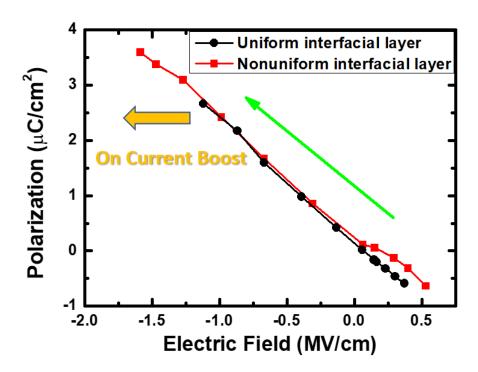

| 2.3 | Polarization and electric field of the FE right above the top of barries (TOB). The transition from bottom right (deamplification) to upper left (amplification) represents the change of the state of the FE from $Vg = 0V$ to $Vg = 0.7V$ .                                                                                                                                    |

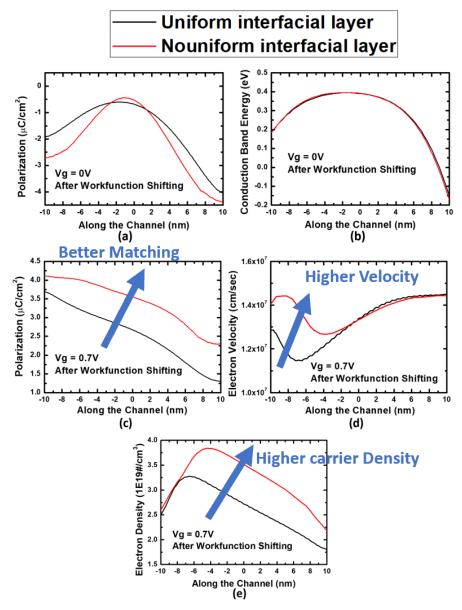

| 2.4 | (a) Polarization and (b) conduction band energy versus position along the channel in the off-state. (c) Polarization, (d) electron velocity, and (e) electron density versus position along the channel in the on-state. The black curves represent an NCFET with uniform thickness of the interfacial                                                                           |

|     | layer. The red curves represent an NCFET with a thicker interfacial layer at the edges of the channel13                                                                                                                                                                                                                                                                                                         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

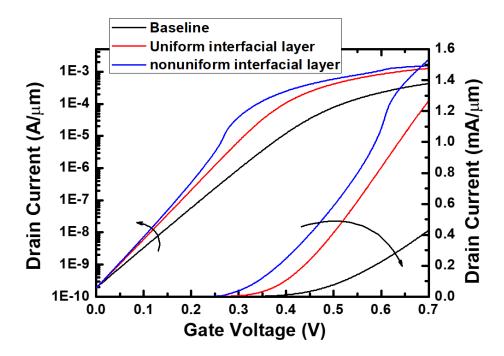

| 2.5 | Drain current versus gate voltage of baseline UTBSOI, traditional uniform-interfacial-layer NCFET, and proposed nonuniform-interfacial-layer NCFET. ————————————————————————————————————                                                                                                                                                                                                                        |

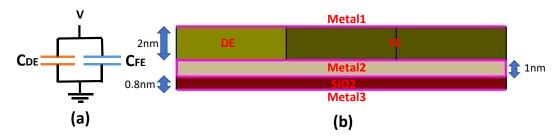

| 3.1 | (a) The circuit model used in Eq. (7) to (13) (b) MFMIM structure for TCAD 2D-simulation. ————————————————————————————————————                                                                                                                                                                                                                                                                                  |

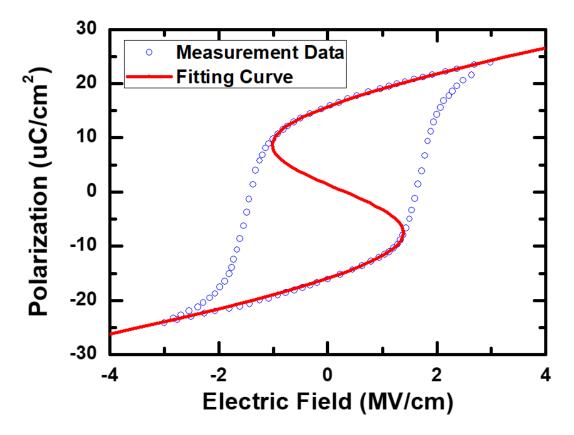

| 3.2 | Polarization-Electric Field loop of the proposed model (red line) and measured data (blue dots)19                                                                                                                                                                                                                                                                                                               |

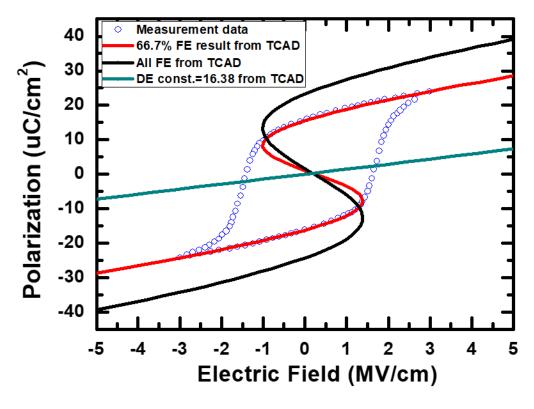

| 3.3 | Polarization versus electrical field plot20                                                                                                                                                                                                                                                                                                                                                                     |

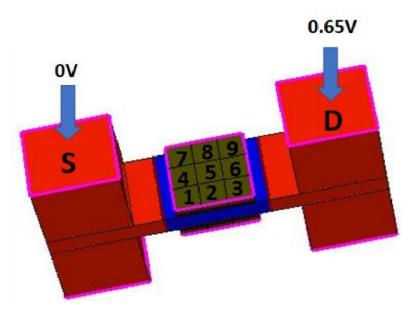

| 3.4 | NCFET structure in Sentaurus TCAD simulation. The red regions are source and drain. The blue region is 5nm-thick channel sandwiched by the gate stack, which consists of 0.8nm SiO <sub>2</sub> , 2nm segmented FE-DE mixed layer, and metal contact. The n-type source and drain doping are 2E20(#/cm <sup>3</sup> ), and the p-type channel doping is 1E17(#/cm <sup>3</sup> ). Gate work function is 4.6eV21 |

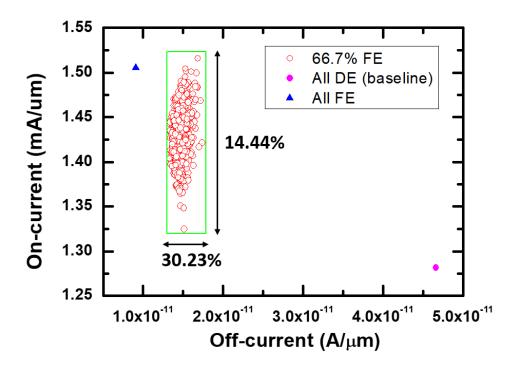

| si  | Scatter plot of the random simulation results. The red circles are random mulation results, the pink dot represents that all the segments are DE paseline), and the blue triangle represents that all the segments are FE22                                                                                                                                                                                     |

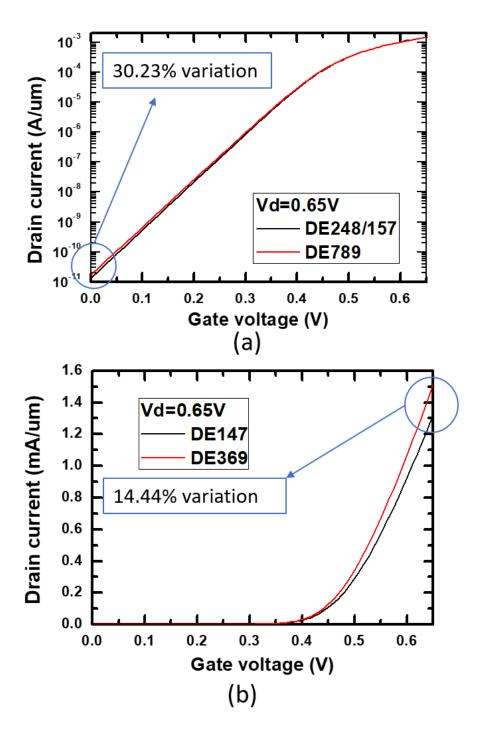

| 3.6 | Drain current versus gate voltage characteristics for (a) $I_{\text{off}}$ extreme cases with variation of 30.23% and (b) $I_{\text{on}}$ extreme cases with variation of 14.44%23                                                                                                                                                                                                                              |

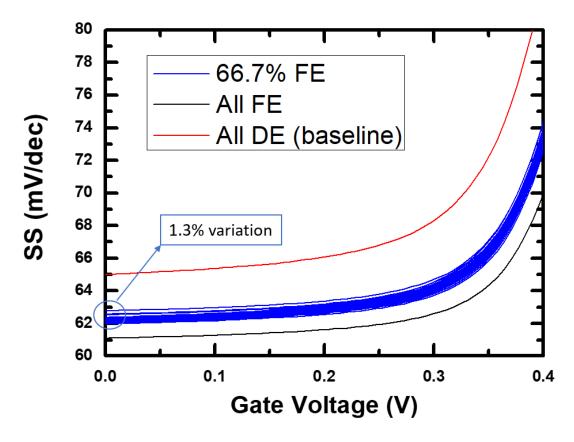

| 3.7 | The subthreshold slope versus gate voltage plot of the random DE and FE distribution simulation24                                                                                                                                                                                                                                                                                                               |

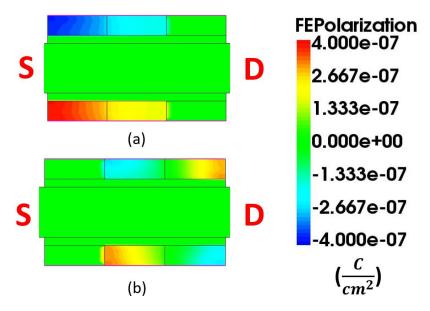

| 3.8 | Ferroelectric polarization 2-D plot at $V_{GS} = V_{DD}$ . (a) Source-side ferroelectric (location of DE at number 3, 6, and 9 in Fig. 3.4) with the highest Ion, and (b) drain-side ferroelectric (location of DE at number 1, 4, and 7 in Fig. 3.4) with the lowest $I_{on}$ 25                                                                                                                               |

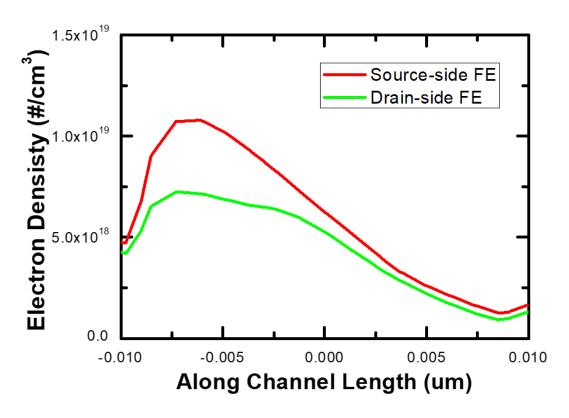

| 3.9 | Electron density near the surface along the channel26                                                                                                                                                                                                                                                                                                                                                           |

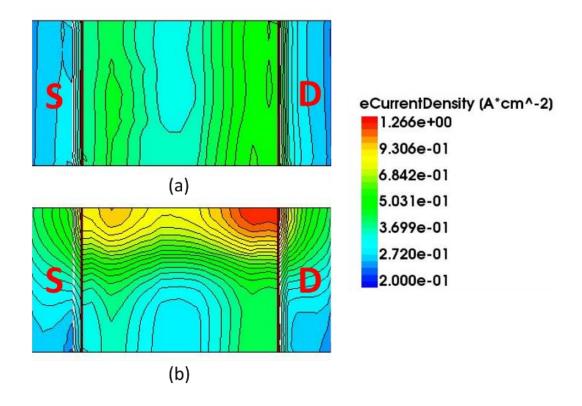

|      | Layout of DE and FE for (a) the lowest I <sub>off</sub> case (the upper triangles and the lower triangles refer to top gate and bottom gate, respectively) and (b) the highest I <sub>off</sub> case27                       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Electron current density in the middle of the channel for (a) the lowest I <sub>off</sub> case (least leakage one) and (b) the highest I <sub>off</sub> case (most leakage one).                                             |

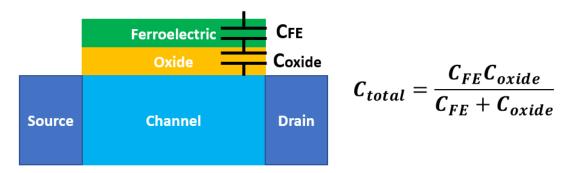

| 4.1  | Cartoon structure and equation for capacitance of NCFETs. CFE is possible to become negative according to Landau Equation, and gate control (C <sub>total</sub> ) could be improved31                                        |

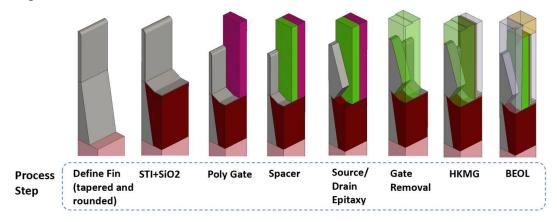

| 4.2  | Process simulation flow31                                                                                                                                                                                                    |

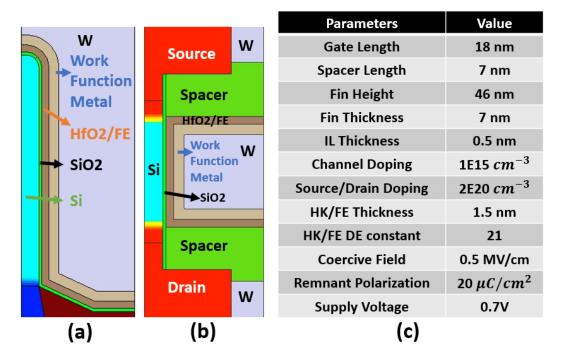

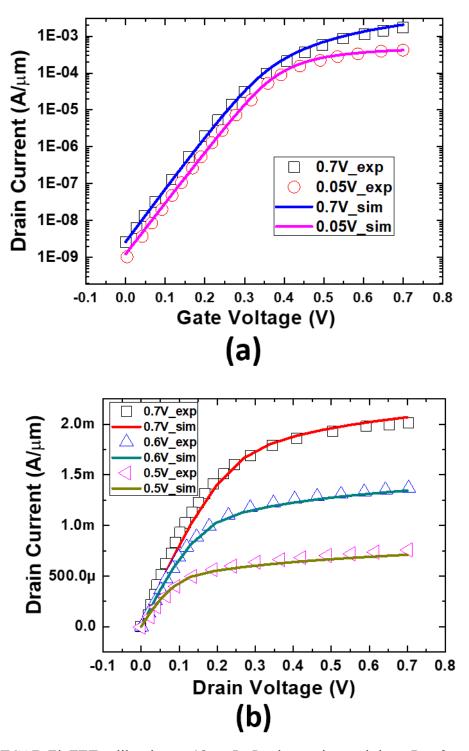

| 4.3  | (a) vertical and (b) horizontal cross sections of the half-FinFET (c) key geometry parameters of the simulated device33                                                                                                      |

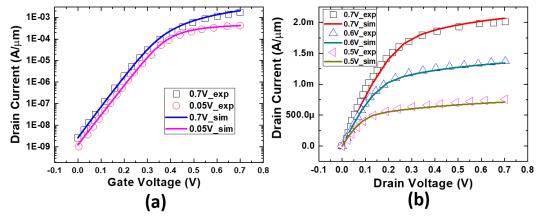

| 4.4  | (a) $I_d$ - $V_g$ curve at $V_d$ =0.05 and 0.7V. (b) $I_d$ - $V_d$ curve at $V_g$ =0.5, 0.6, and 0.7V. The data in this figure is normalized to fin pitch according to Intel's convention33                                  |

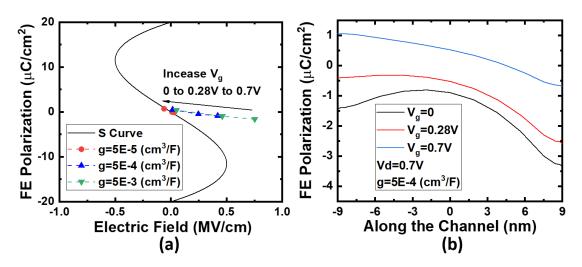

| 4.5  | (a) Polarization-Electric Field data points extracted from the middle of the channel length at $V_g$ =0, 0.28, and 0.7V. (b) FE polarization along the channel at $V_g$ =0, 0.28, and 0.7V34                                 |

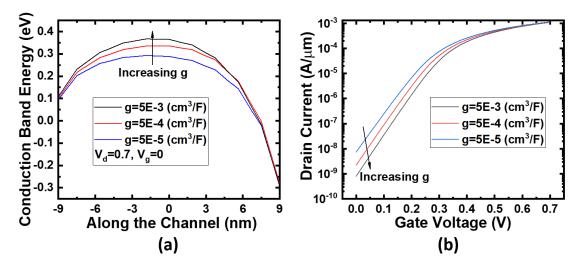

| 4.6  | (a) Conduction band energy at off-state and $V_d$ =0.7V along the channel and (b) $I_d$ - $V_g$ curve at $g$ =5 $\times$ 10 <sup>-3</sup> , 5 $\times$ 10 <sup>-4</sup> , 5 $\times$ 10 <sup>-5</sup> (cm <sup>3</sup> /F)34 |

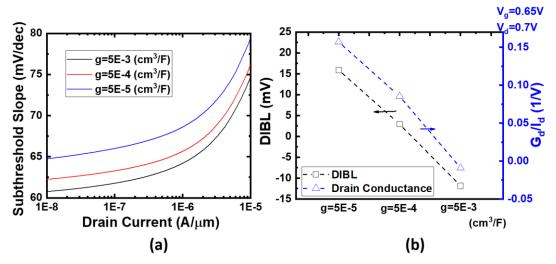

| 4.7  | (a) SS versus drain current at $g=5 \times 10^{-3}$ , $5 \times 10^{-4}$ , $5 \times 10^{-5}$ (cm <sup>3</sup> /F). (b) DIBL and drain conductance versus different g values36                                               |

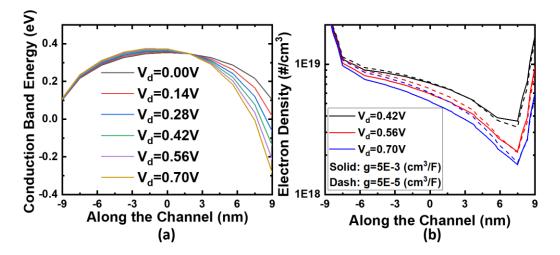

| 4.8  | (a) Conduction band energy along the channel at $V_g$ =0 and various $V_d$ . (b) Electron Density along the channel at $V_g$ =0.65V and various $V_d$ 36                                                                     |

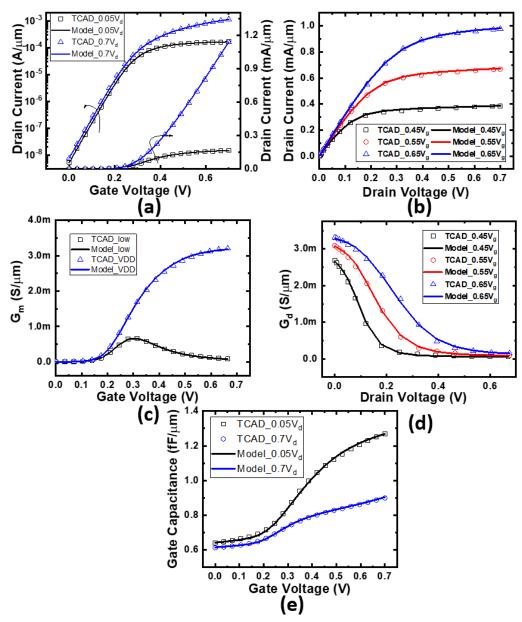

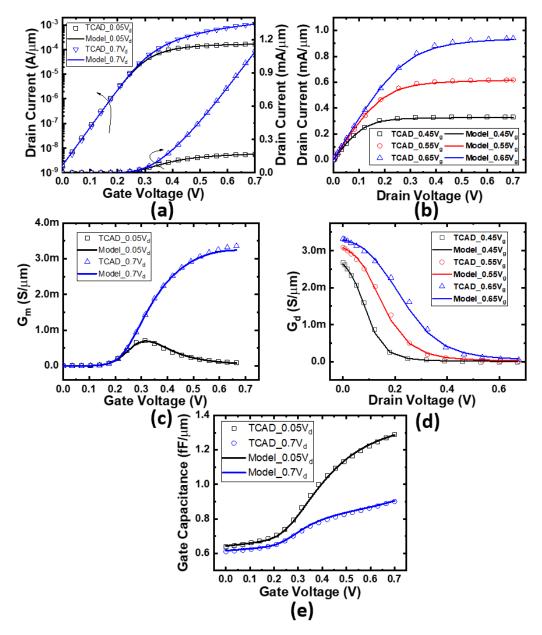

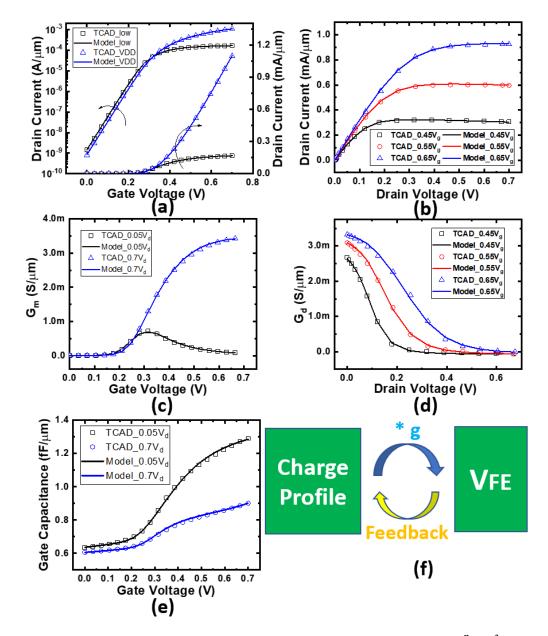

| 4.9  | Model validation with TCAD simulation data at $g=5\times10^{-6}$ cm <sup>3</sup> /F. (a) $I_d$ - $V_g$ curve, (b) $I_d$ - $V_d$ curve, (c) transconductance, (d) output conductance, and (e) gate capacitance38              |

| 4.10 | O Model validation with TCAD simulation data at $g = 1 \times 10^{-3}$ cm <sup>3</sup> /F. (a)                                                                                                                               |

|      | $I_d$ - $V_g$ curve, (b) $I_d$ - $V_d$ curve, (c) transconductance, (d) output conductance, and (e) gate capacitance39                                                                                                                                                                       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Model validation with TCAD simulation data at $g = 5 \times 10^{-3}$ cm <sup>3</sup> /F. (a) $I_d$ - $V_g$ curve, (b) $I_d$ - $V_d$ curve, (c) transconductance, (d) output conductance, and (e) gate capacitance. (f) Diagram of how charge profile and potential of FE affect each other40 |

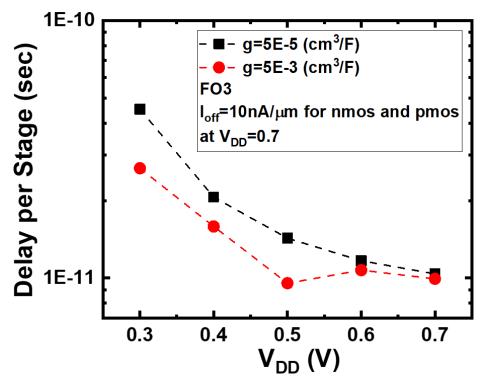

| 4.12 | 2 17-stage ring oscillator simulation with FO3 under different $V_{DD}$ . The delay per state becomes lower at larger g and $V_{DD}$ =0.5V41                                                                                                                                                 |

| 5.1  | Energy polarization plot at different HZO states without external electric field. HZO with remanent polarization has lowest energy; whereas, the energy is higher at zero polarization because lattice is distorted44                                                                        |

| 5.2  | The MOSCAP Structure used in TCAD simulation and its key parameters FE parameters will be described in the text45                                                                                                                                                                            |

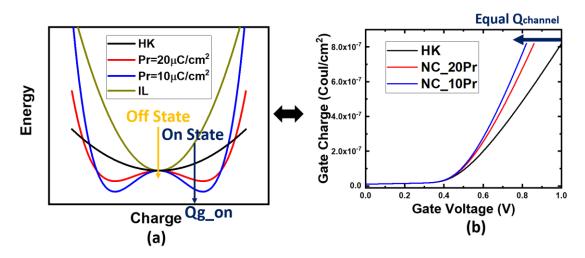

| 5.3  | (a) Energy versus charge plot of four materials. (b) Gate charge versus gate voltage of three cases45                                                                                                                                                                                        |

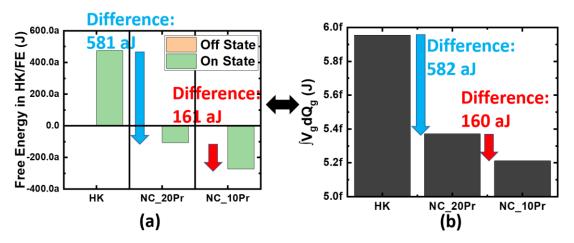

| 5.4  | (a) Static material free energy integration throughout either HK or FE. (b) Energy inflow to the gate from the off-state to the on-state48                                                                                                                                                   |

| 5.5  | The MOSFET structure used in TCAD simulation, and its key parameters. FE parameters are the same as previous section48                                                                                                                                                                       |

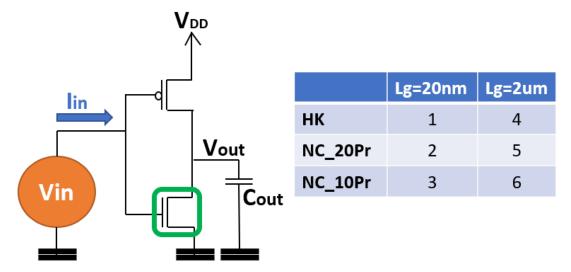

| 5.6  | The inverter circuit which will be used in TCAD simulation. The table on the right-hand side indicates there are 6 cases in this simulation50                                                                                                                                                |

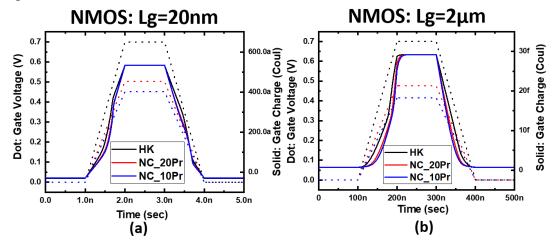

| 5.7  | Gate voltage (dash & left axis) and gate charge (solid and right axis) versus time at (a) $L_g$ = 20nm and (b) $L_g$ = 2 $\mu$ m50                                                                                                                                                           |

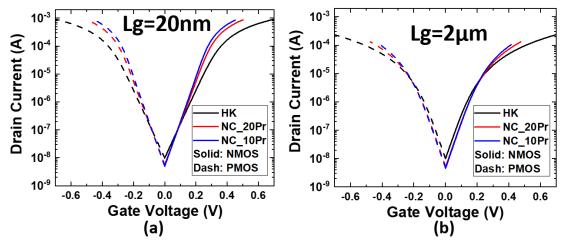

| 5.8  | $I_d\text{-}V_g$ plot at (a) $L_g\text{=}20\text{nm}$ and at (b) $L_g\text{=}2\mu\text{m}.$ 51                                                                                                                                                                                               |

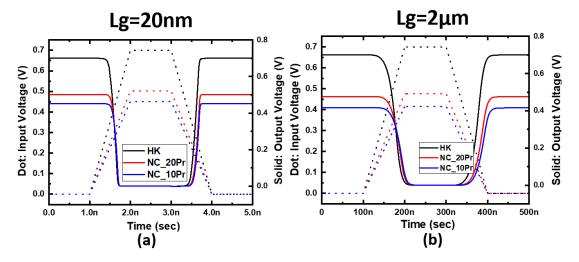

| 5.9  | Input and output voltage from the TCAD transient simulation of the circuit as shown in Fig. 6 at (a) $L_g = 20$ nm and at (b) $L_g = 2\mu$ m. Input voltage is dash line and corresponds to left axis, and output voltage is solid line and corresponds to right axis51                      |

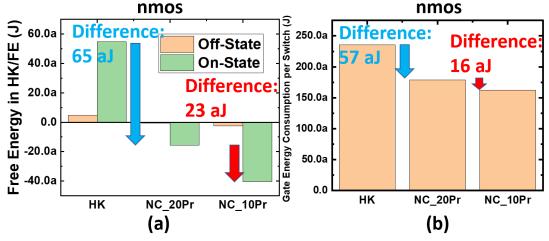

| 5.10 | (a) Static free energy of HK/FE in different cases at $Lg = 20$ nm. (b) Gate energy consumption of nmos in the inverter transient simulation per switch at $Lg = 20$ nm52                                                                                                                                                                                         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

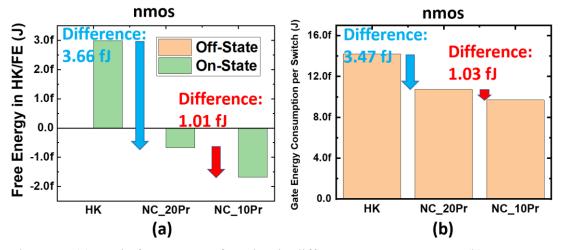

| 5.11 | (a) Static free energy of HK/FE in different cases at $L_g$ =2 $\mu$ m. (b) Gate energy consumption of nmos in the inverter transient simulation per switch at $L_g$ =2 $\mu$ m52                                                                                                                                                                                 |

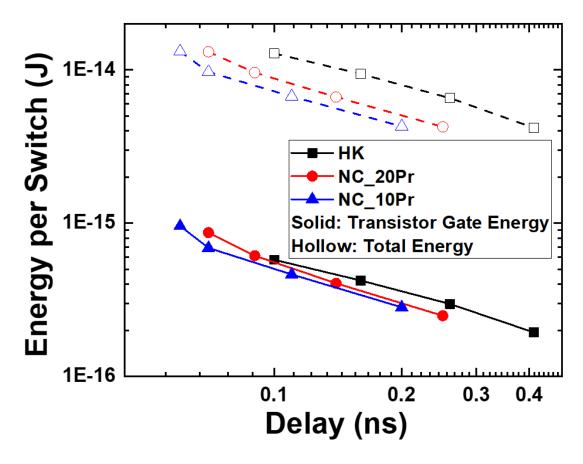

| 5.12 | Energy per switch versus delay at $L_g$ =20nm. Solid symbols only consider gate energy consumption of nmos and pmos, and hollow symbols consider the additional energy consumption due to $C_{out}$ . $C_{out}$ is set to be 50fF                                                                                                                                 |

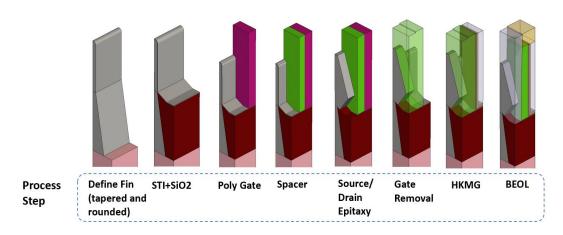

| 6.1  | Process simulation flow57                                                                                                                                                                                                                                                                                                                                         |

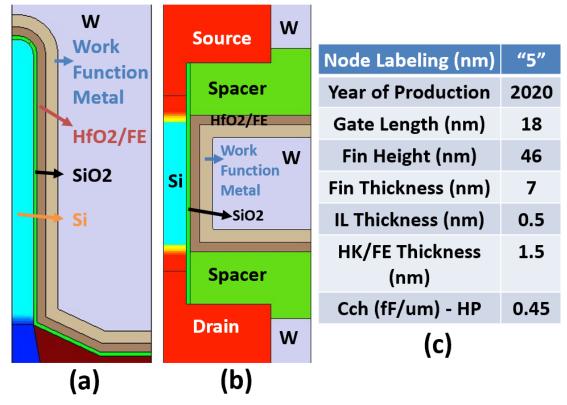

| 6.2  | (a) vertical and (b) horizontal cross sections of the half-FinFET (c) key geometry parameters of the simulated device. Note that the capacitance of the gate stack ( $C_{ch}$ ) matches with IRDS high performance (HP) requirement, $0.45 fF/\mu m$ 58                                                                                                           |

|      | TCAD FinFET calibration to $18 \text{nm L}_g$ Intel experimental data. <i>Per-foot-print</i> normalization of $I_d$ is done in this figure to match the Intel presentation. (a) $I_d$ - $V_g$ fitting plot at high and low drain voltage (b) $I_d$ - $V_d$ fitting plot at three different gate voltages, $0.7 \text{V}$ , $0.6 \text{V}$ , and $0.5 \text{V}$ 59 |

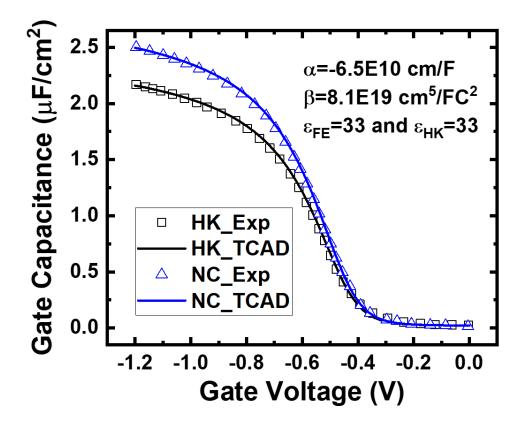

| 6.4  | C-V fitting of the experiment data of NC-MOSCAP. The extracted $\alpha$ and $\beta$ are equivalent to $P_r = 20 \mu C/cm^2$ and $E_c = 1 MV/cm$ 60                                                                                                                                                                                                                |

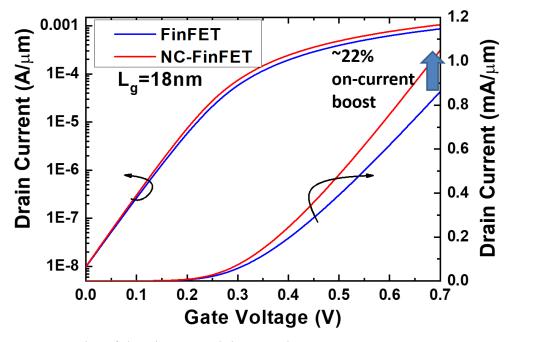

| 6.5  | $I_d$ - $V_g$ plot of the FinFET and the NC-FinFET at $L_g$ =18nm60                                                                                                                                                                                                                                                                                               |

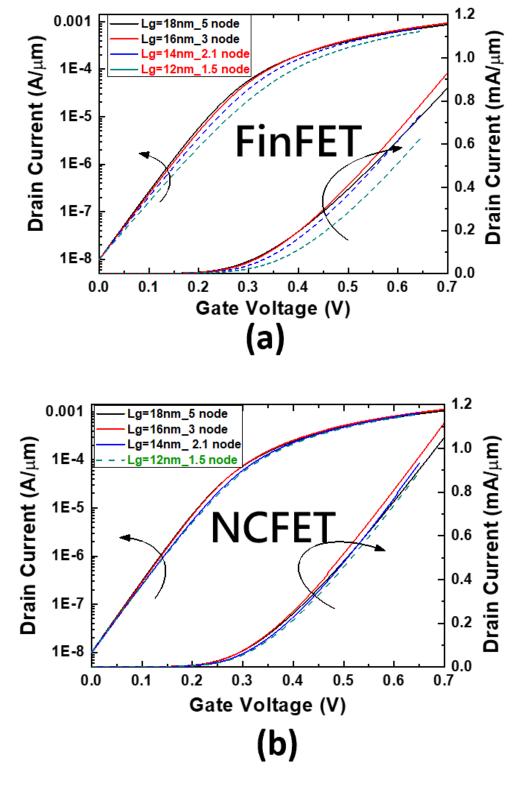

| 6.6  | $I_d$ - $V_g$ of (a) FinFETs and (b) NC-FinFETs with work functions shifted to align the off-current with the IRDS high-performance requirement62                                                                                                                                                                                                                 |

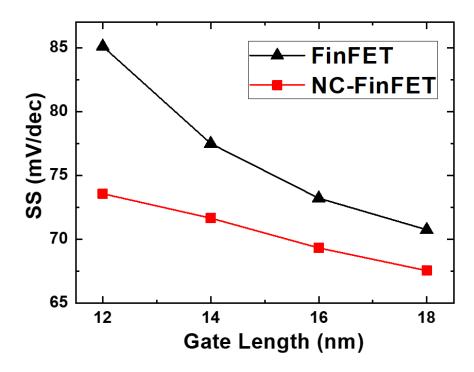

| 6.7  | SS of NC-FinFET is smaller than FinFET at $18nm\ L_g$ and rises at lower rate with decreasing $L_g$ 64                                                                                                                                                                                                                                                            |

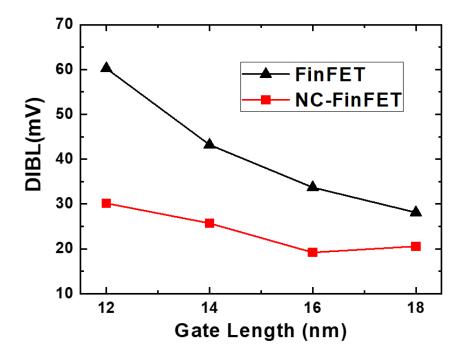

| 6.8  | DIBL versus gate lengths. DIBL is smaller in NC-FinFET and rises at lower rate as L <sub>g</sub> shrinks64                                                                                                                                                                                                                                                        |

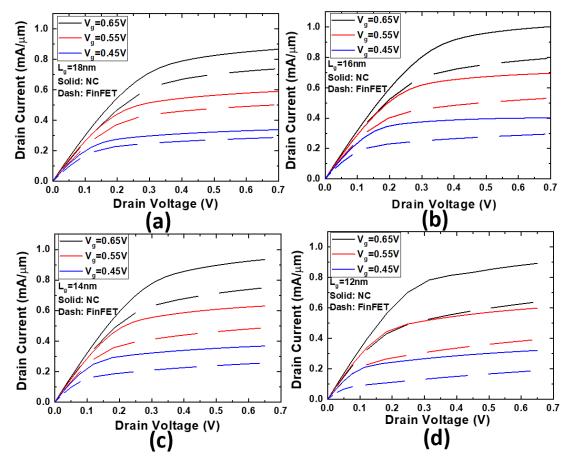

| 6.9 | $L_g$ is larger and $g_d$ is smaller in NC-FinFET than in FinFET at (a). $L_g$ =18nm, at (b) $L_g$ =16nm, at (c) $L_g$ =14nm, and at (d) $L_g$ =12nm65                                                                                                                                                                                                                                                  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

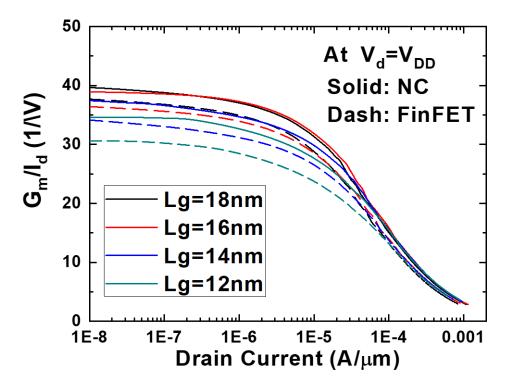

|     | Gm/Id versus drain current. NC-FinFETs have better Gm/Id performance than FinFETs overall66                                                                                                                                                                                                                                                                                                             |

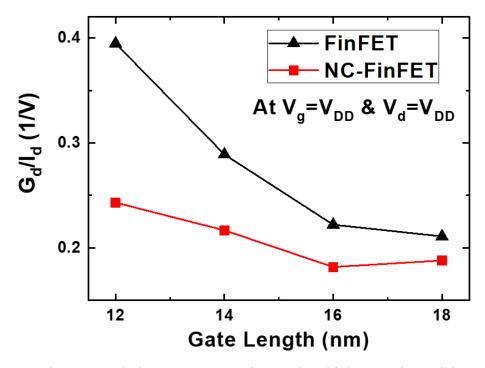

|     | $G_d/I_d$ versus drain current. NC-FinFET has higher Gm/Id and lower $G_d/I_d$ leading to better analog performance66                                                                                                                                                                                                                                                                                   |

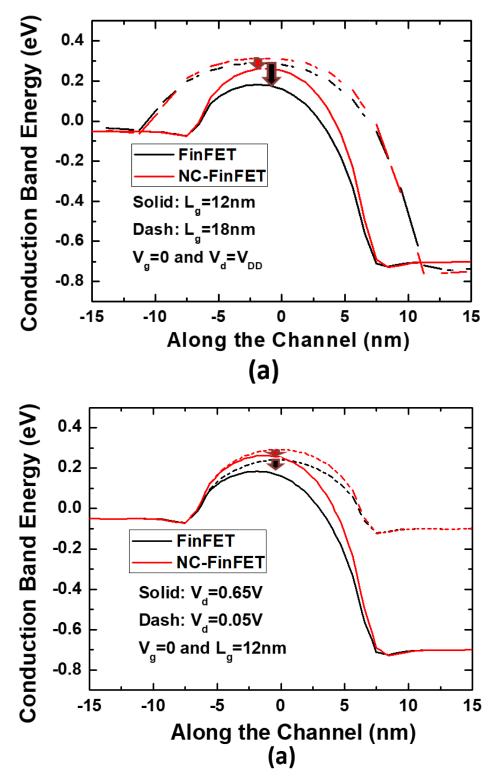

|     | (a) The potential barrier is higher in NC-FinFET (red) than in FinFET (black), and the difference is larger at Lg=12nm (solid) than at Lg=18nm (dash). (b) DIBL of NC-FinFET is smaller than FinFET. Note that the work function is not shifted in this figure. ————68                                                                                                                                  |

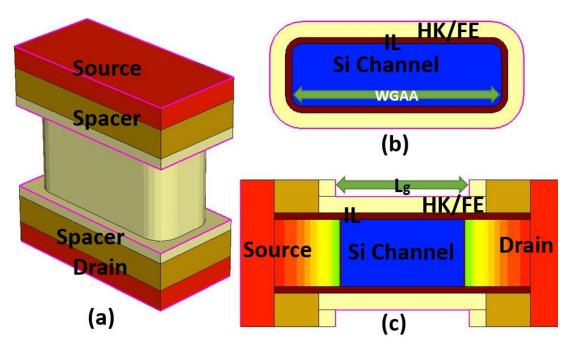

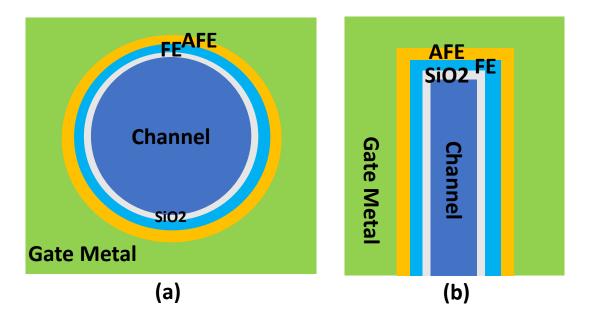

| 7.1 | (a) 3-D view of the GAA structure. The metal layer is transparent in these plots to better view the inside structure. (b) Cross section at mid-channel. The corners are rounded to make it closer to real-world devices. (c) Cross section along the channel. The diffusion of dopant from source/drain can be clearly seen. ———————————————————————————————————                                        |

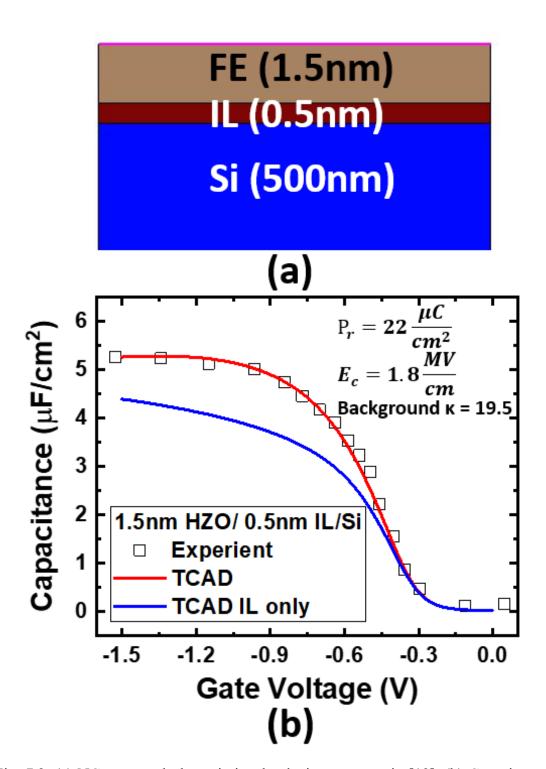

| 7.2 | (a) NC gate stack that mimics the device structure in [19]. (b) Capacitance versus gate voltage. The black square symbols are experiment data from [19], the blue curve is with only 0.5 nm IL layer, and the red curve is with 0.5 nm IL layer and 1.5 nm FE layer. The equivalent extracted P <sub>r</sub> and E <sub>c</sub> are shown on the top-right corner. ———————————————————————————————————— |

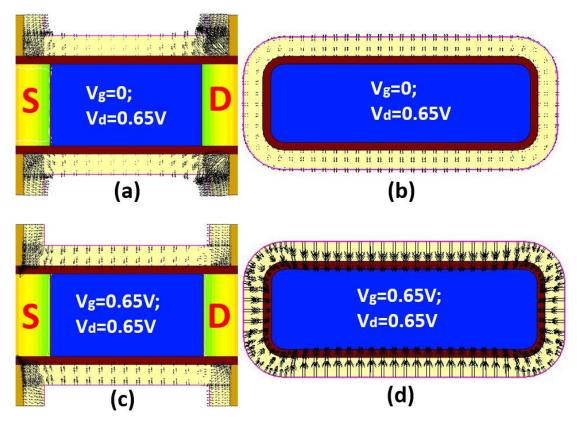

| 7.3 | 2-D FE polarization vector plot. (a) Cross section along the channel at $V_g$ = 0 and $V_d$ = 0.65V. (b) Cross section at middle of the channel at $V_g$ = 0 and $V_d$ = 0.65V. (c) Cross section along the channel at $V_g$ = 0.65V and $V_d$ = 0.65V. (d) Cross section at middle of the channel at $V_g$ = 0.65V and $V_d$ = 0.65V                                                                   |

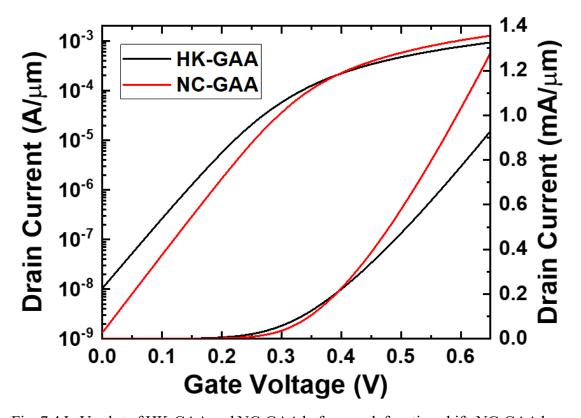

| 7.4 | I <sub>d</sub> -V <sub>g</sub> plot of HK-GAA and NC-GAA before work function shift. NC-GAA has around one order off-current reduction and around 40% on-current boost76                                                                                                                                                                                                                                |

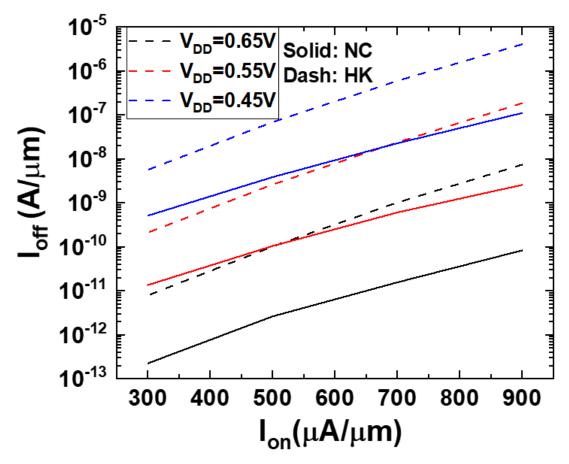

| 7.5 | $I_{\text{off}}$ - $I_{\text{on}}$ plot of HK-GAA (dash lines) and NC-GAA (solid lines) under different $V_{DD}$ conditions. NC-GAA with $V_{DD}$ of 0.55V (solid red line)                                                                                                                                                                                                                             |

|     | performs even better than HK-GAA with $V_{DD}$ of 0.65V (dashed black line in the high-performance region ( $I_{on} > 550 \mu A/\mu m$ )77                                                                                                                                                                                                |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

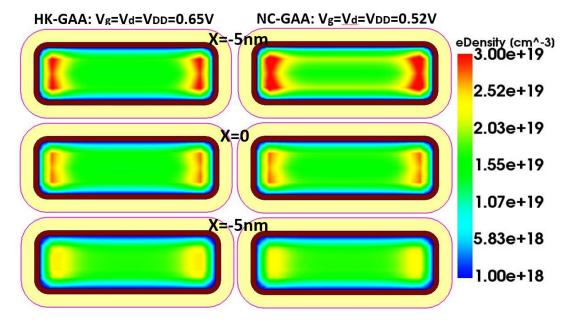

| 7.6 | Electron density plot at different cross section planes of HK-GAA and NC-GAA. The $V_{DD}$ of NC-GAA is reduced to match NC-GAA's on-current with HK-GAA's on-current79                                                                                                                                                                   |

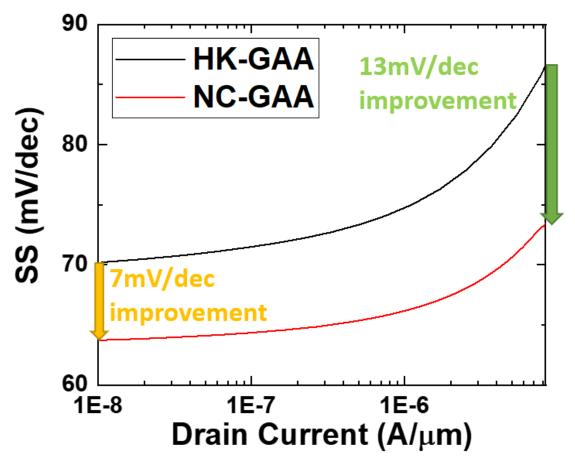

| 7.7 | Subthreshold slope versus drain current of HK-GAA (black) and NC-GAA (red)80                                                                                                                                                                                                                                                              |

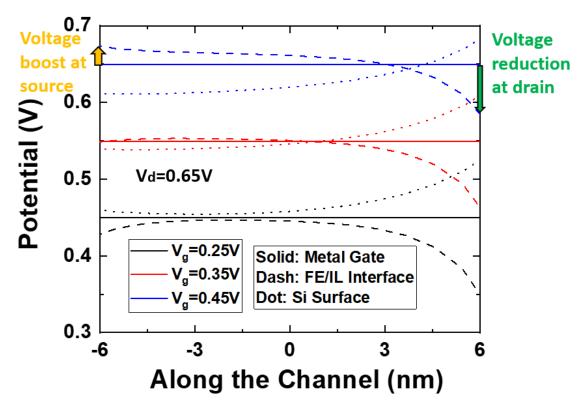

| 7.8 | Potential at metal gate, FE/IL interface, and Si surface under different V <sub>g</sub> condition along the channel81                                                                                                                                                                                                                     |

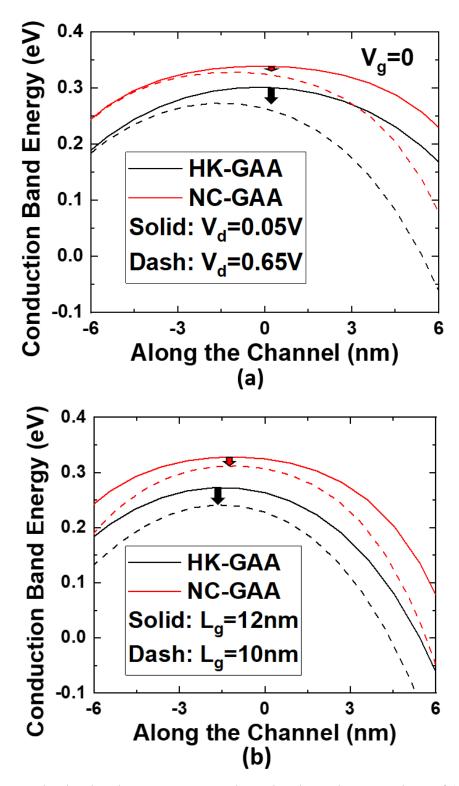

| 7.9 | Conduction band energy at $V_g$ =0 along the channel. Comparison of (a) drain-induced barrier lowering and (b) barrier lowering due to $L_g$ reduction between HK-GAA and NC-GAA82                                                                                                                                                        |

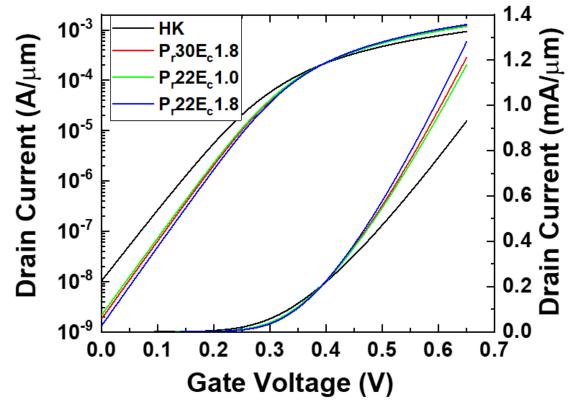

|     | $O$ $I_d$ - $V_g$ plot at $V_d$ =0.65V under different NC parameters. The black is HK-GAA baseline, the red is NC of $P_r$ = 30 $\mu$ C/cm <sup>2</sup> and $E_c$ = 1.8MV/cm, the green is NC of $P_r$ = 22 $\mu$ C/cm <sup>2</sup> and $E_c$ = 1.0MV/cm, and the blue is NC of $P_r$ = 22 $\mu$ C/cm <sup>2</sup> and $E_c$ = 1.8MV/cm83 |

| 8.1 | Schematic of the proposed model. The NC model is implemented in BSIM-CMG. BSIM-CMG has a few geometry options, including but not limited to (a) cylindrical gate and (b) FinFET86                                                                                                                                                         |

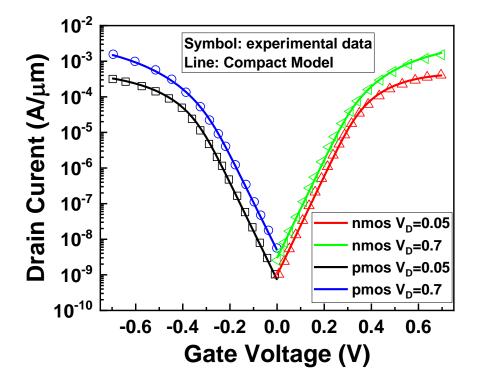

| 8.2 | Baseline model fitting with Intel 10nm high performance and low-power measurement data89                                                                                                                                                                                                                                                  |

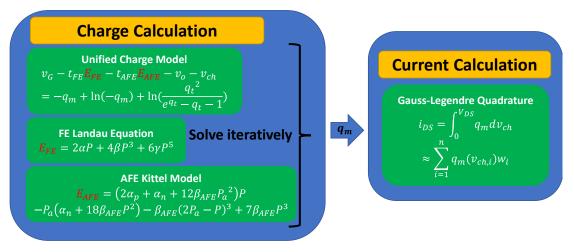

| 8.3 | Architecture of the proposed model. Source and drain side channel inversion charges are calculated first. Drain current are calculated by Gauss-Legendre Quadrature89                                                                                                                                                                     |

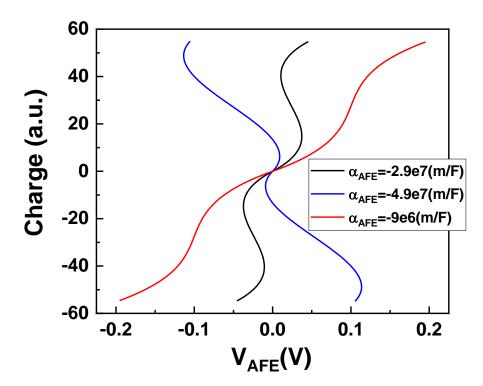

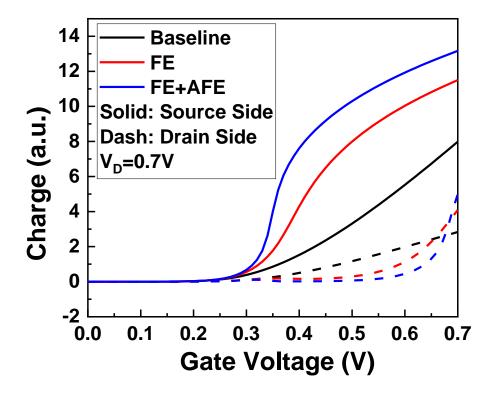

| 8.4 | Charge versus voltage relation in AFE. Different α values are simulated, and beta value is fixed89                                                                                                                                                                                                                                        |

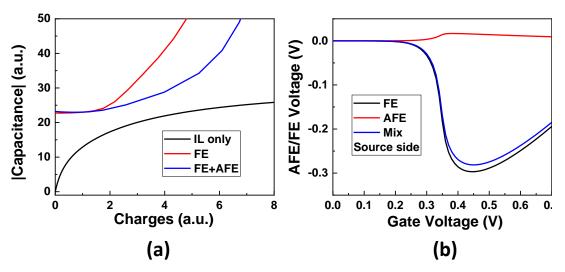

| 8.5 | (a) Absolute value of capacitance versus charge. The black curve is gate capacitance with only a 1nm SiO2 layer. The red curve is the capacitance absolute value of a 2nm FE layer with $\alpha_{FE} = -4.33 \times 10^{-2}$                                                                                                              |

| $10^9 \left(\frac{m}{F}\right)$ and $\beta_{FE} = 2.4 \times 10^{12} \left(\frac{Coul^2 m^5}{F}\right)$ . The blue curve is the                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| capacitance absolute value of a 2nm FE layer and a 0.5nm AFE layer with                                                                                                                                                                     |

| $lpha_{FE}=-5.63	imes10^9~\left(rac{m}{F} ight)$ , $eta_{FE}=2.4	imes10^{12}~\left(rac{Coul^2m^5}{F} ight)$ , $lpha_{AFE}=$                                                                                                               |

| $-3.1	imes10^{7}$ $\left(rac{m}{F} ight)$ , $eta_{AFE}=9.8	imes10^{9}$ $\left(rac{Coul^{2}m^{5}}{F} ight)$ , and $P_{a}=3	imes10^{9}$                                                                                                     |

| $10^{-2} \left(\frac{Coul}{m^2}\right)$ . (b) Voltage of AFE or FE versus gate charge. The blue curve                                                                                                                                       |

| is the sum of the black and the red curves90                                                                                                                                                                                                |

| 8.6 Charge versus gate voltage for baseline, FE, and FE+AFE cases91                                                                                                                                                                         |

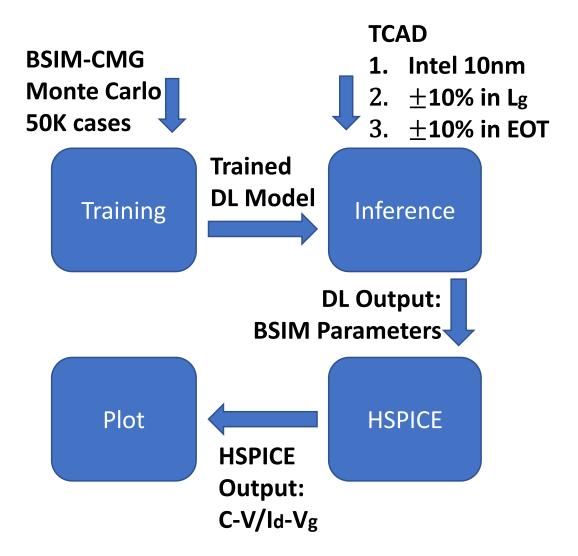

| 9.1 The framework of the deep learning-based parameter extraction94                                                                                                                                                                         |

| 9.2 The architecture of the deep learning models. (a) C <sub>gg</sub> -V <sub>g</sub> parameters extraction model (b) Id-Vg parameters extraction model96                                                                                   |

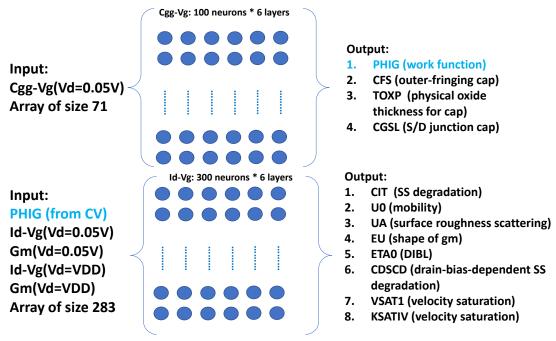

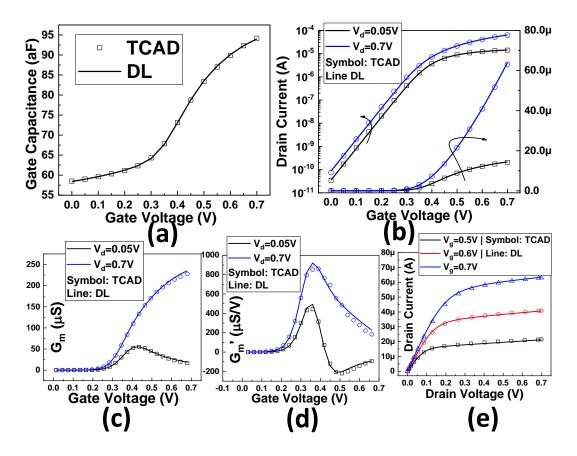

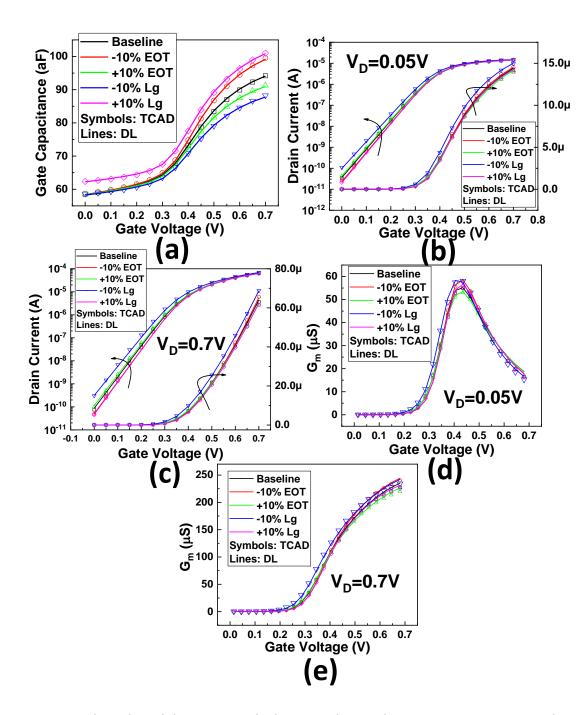

| 9.3 The DL-based paramters extraction model testing results by the TCAD data. (a) $C_{gg}$ - $V_g$ . (b) $I_d$ - $V_g$ at $V_d$ =0.05V and $V_d$ =0.7V. (c) gm at $V_d$ =0.05V and $V_d$ =0.7V. (e) $I_d$ - $V_d$ 97                        |

| 9.4 DL-based model testing results by TCAD data with 10% variation in EOT and $L_g$ . (a) $C_{gg}$ - $V_g$ . (b) $I_d$ - $V_g$ at $V_d$ =0.05V. (c) $I_d$ - $V_g$ at $V_d$ =0.7V. (d) gm at $V_d$ =0.05V. (e) gm at $V_d$ =0.7V99           |

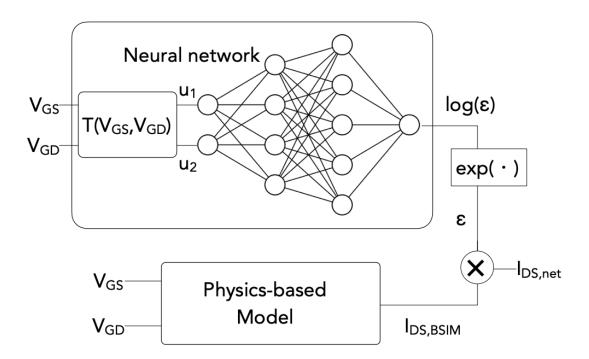

| 10.1 Deep-learning-assisted <i>IV</i> model architecture104                                                                                                                                                                                 |

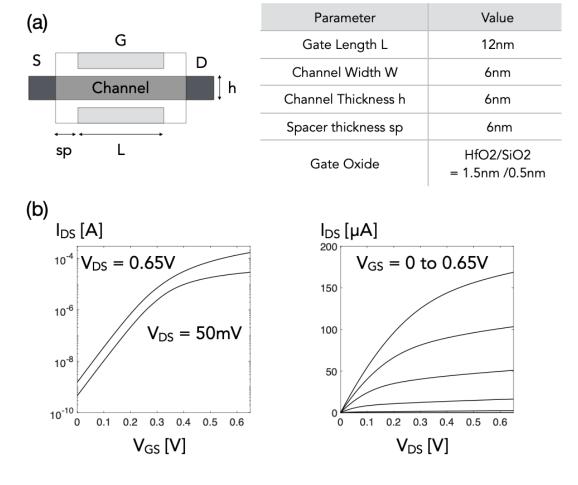

| 10.2 (a) Cross-sectional schematic of the simulated GAAFET structure and (b) simulated transfer and output <i>IV</i> characteristics106                                                                                                     |

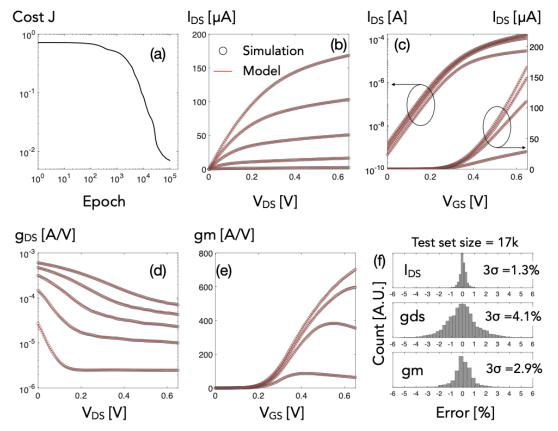

| 10.3 (a) Training error vs epoch. Model well-matches to the test dataset in (b) output and (c) transfer characteristic (d) output conductance, and (e) transconductance. (e) Percentage error distribution in $I_{DS}$ , $gds$ and $gm$ 108 |

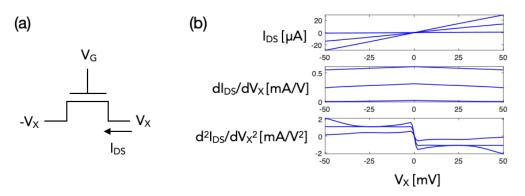

| 10.4 (a) Gummel symmetry test setup. (b) $I_{DS}$ , first and second derivative of $I_{DS}$ with respect to $V_{X}$ 108                                                                                                                     |

| 10.5 Model implementation for circuit simulations109                                                                                                                                                                                        |

### **List of Tables**

| 3.1 | Hysteresis loop fitting results17                                                                                                                                                                                                             |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1 | Simulation plan follows the IRDS 2018 roadmap. Red highlighting of the TCAD results indicate failure to meet the on-current targets at all future nodes63                                                                                     |

| 6.2 | $V_{DD}$ needed to reach IRDS target on-current ( $I_{off}$ is fixed at $10 nA/\mu m$ ) for different IRDS nodes                                                                                                                              |

| 7.1 | Key parameters of the simulated GAA device71                                                                                                                                                                                                  |

| 7.2 | Simulation results compared with IRDS specifications. The row with yellow background is NC-GAA's required $V_{DD}$ , and the column with green background is the additional predicted node which is not on the IRDS Table. ————————————————78 |

| 8.1 | Unified compact model, FE model, and AFE model parameters and variables88                                                                                                                                                                     |

| 9.1 | DL model output values under different testing cases. The colored values will be discussed100                                                                                                                                                 |

#### Acknowledgement

Firstly, I would like to thank the best advisor, Prof. Chenming Hu. He provided full support throughout my Ph.D. journey. The support is not only the financial support but also all the other aspect of support. He cares so much of students' needs. For example, I remember that he checked every question in detail during the student review to make sure I was satisfied with all the aspects of my life at Cal. Prof. Chenming Hu is also a perfect role model for juniors. He not only works hard but also enjoys his life. During these five years of my Ph.D., I tried to follow his step to increase my working efficiency to have leisure time to enjoy my life here in the US. He is an excellent textbook example of an open-minded person and a life-long learner. For instance, I started machine learning-related projects in my 5th year. He advised me along the way, and we both learned so much together from machine learning theories and applications. He is also an outstanding leader. For instance, he manages the BSIM group very well and maintains a good relationship with industry partners. Last but not least, I learned so much from Prof. Hu's presentation skills. Prof. Hu keeps instructing me on presenting an idea more interestingly. I practice every time at the annual presentation to our industry sponsors. I can even feel the improvements in my presentation, even myself. Under Prof. Hu's supervision, I went through a very fulfilling Ph.D. journey. Suppose anyone asks me if time is back to 5 years again, whether I would choose Ph.D. again. My answer is definitely yes, and I will try my best to join Prof. Hu's group.

I want to show my gratitude toward Prof. Sayeef Salahuddin. Without him, I would not have the NCFET-related research topics throughout my Ph.D. He is very generous in providing his insight on any physics/math-related problems. I feel super confident once he backs up the explanation. He also serves as my preliminary exam, qualification exam, and dissertation committee member. He appeared everywhere and always provided help when I was stuck throughout my Ph.D.

I appreciate Prof. Sayeef Salahuddin, Prof. Ana Claudia Arias, and Prof. Jeffrey Bokor serving on the oral preliminary committee. They challenged us with questions from the very fundamental to the trickiest ones. This process paves a rock-solid foundation for the following years of research. I would like

to also express my gratitude to Prof. Chenming Hu, Prof. Sayeef Salahuddin, Prof. Ali Javey, and Prof. Junqiao Wu for serving as qualification committee members. They examined my research results at the mid-point of my Ph.D. and provided much insight for my following years of research.

Yu-Hung has always been one of my classmates and best co-workers. We studied for four years together at National Taiwan University and did research together during five years of Ph.D. right here at UC Berkeley. We will also join the same group at NVIDIA in the future. Best wishes for our future journey. I would also like to thank the preliminary exam study group: Yu-Hung, Xiaoer, Saavan, Adi, and Jason. Without their help, I could not pass the preliminary exam. I would also like to show my massive gratitude toward the co-authors of my publication, Angada, Huan-Lin, Juan, Avirup, Yen-Kai, Ava, Girish, Hei, Fredo, Harshit, Pragya, Yu-Hung, Suraj, Prof. Hu, Prof. Salahuddin, and Prof. Khandelwal. They are all excellent mentors, and I learn a lot from them, from doing good research to being a good co-worker.

The Taiwanese Community at Cal is closely-connected, and staying at Berkeley is never boring. I appreciate the organization of the Berkeley Association of Taiwanese Students (BATS). While I served as the vice-president and the president of BATS, I met so many new friendly people. Some of them went back to Taiwan, and some stayed in the US for their careers. I will keep all these valuable memories forever.

My family members are always supportive. I cannot express my great appreciation toward my father, mother, and sister here. They provide everything I need to focus on what I would like to pursue. I feel that we are bounded so closely that family is still my priority when I think of anything. I would also like to thank my sister's husband; he takes good care of my sister. I would also like to express my gratitude to my father-in-law and mother-in-law. They treat me like their own son.

Last but not least, my wife, Tien-Ning, is the best person I have ever met in the world. She is kind and enthusiastic about exploring new things. I am always motivated by her to try new things. We plan a long to-do list that we would like to explore in the future. I am so excited about the future. Tien-Ning is also super supportive of whatever I would like to do. This year is our tenth anniversary. I am so passionate about our next decade's anniversary.

#### **Chapter 1**

#### Introduction

#### 1.1 Challenges of Nano-electronics

Gordon Moore proposed Moore's law in 1975, and after that, the number of components per integrated circuit doubled every 12-24 months [1]. The fast

Fig. 1.1. Calculations per second per 1,000 USD versus time. Exponential growth can be observed throughout 100 years. [132]

downscaling of the transistor benefits the whole world in many ways, including communication electronics (like iPhone and Internet routers), personal computers... For example, calculations per second per 1,000 USD of various products throughout 100 years are shown in Fig. 1.1. However, the growth of exponential is difficult to maintain at the same growth rate forever. For example, the exponential growth of the bacteria would be limited by the resources finally. There is no exception for the semiconductor industry. For a long time, the metal-oxide-semiconductor field-effect transistor (MOSFET) benefits from scaling and an increase in clock frequency. By scaling effective oxide thickness (EOT), the same charge density can be achieved at a lower gate voltage. By reducing the gate length, the same current density could be achieved at a lower drain voltage. Several great inventions, including the H-K metal gate, immersion lithography, and FinFET, keep the scaling continuing. Scaling of EOT and increase of clock frequency together increase the performance per area. Recently, scaling of EOT is slowed down because of physical limitations, including direct tunneling, oxide breakdown, and mobility degradation, and the increase of clock frequency is hindered by the difficulty of heat dissipation.

Negative Capacitance Field-Effect Transistor (NCFET) is a promising near-future solution to the slowed-down of EOT scaling. The scaling can be pushed to a few more nodes if NCFET is properly designed. The theory of NCFET will be explained in the next section.

#### 1.2 Theory of Negative Capacitance Field-Effect

#### **Transistor**

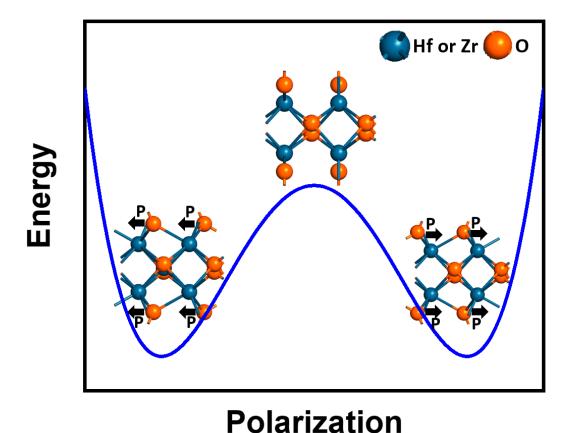

Before explaining NCFET, let's start with where negative capacitance (NC) comes from. Fig. 1.2 (a) shows the energy of energy versus charge in ferroelectric (FE) and dielectric (DE) without an external electric field [2]. The minimum energy of FE is not at zero charge, leading to ferroelectricity (remanent polarization when there is no electric field). In contrast, the minimum energy of DE is at zero charge, and the shape is parabolic. If the FE is stacked on top of the DE, the total energy is plotted as the red curve in Fig. 1 (a). The equilibrium point is the small black ball at zero electric fields, where the individual energy is not minimum for the FE, but the total energy of the system is minimum. Voltage is the derivative of energy with respect to the charge, and the voltage versus charge plot is shown in Fig. 1.2 (b). Capacitance is the derivative of voltage with respect to charge, which is the slope in Fig. (b). The slope of the black curve in Fig. 1 (b) is negative, showing the negative capacitance within the red box.

Fig. 1.3 shows the cartoon graph of a MOSFET. The capacitance from gate to channel can be simplified into two components, insulator capacitance ( $C_{ins}$ ) and semiconductor capacitance ( $C_s$ ). The total capacitance can be expressed as Eq. (1.1)

Fig. 1.2. (a) Energy versus charge plot of FE, DE, and the total system of FE and DE. (b) Voltage versus charge plot of FE and DE.

$$C_{total} = \frac{C_s C_{ins}}{C_s + C_{ins}}$$

(1.1)

If the value of  $C_{ins}$  is negative,  $C_{total}$  could be larger than  $C_s$ . It is even better than EOT -> 0 scenario. Another way to demonstrate the benefits of NCFET is by looking into the equation of subthreshold slope (SS) [3]:

$$SS = \frac{\partial V_g}{\partial (log_{10}I)} = \frac{\partial V_g}{\partial \varphi_s} \frac{\partial \varphi_s}{\partial (log_{10}I)}$$

(1.2)

The SS of the device is limited by two parts. The first part is  $\frac{\partial V_g}{\partial \varphi_s}$ , which is determined by the capacitance divider as shown in Fig. 2.

$$\frac{\partial V_g}{\partial \varphi_s} = 1 + \frac{C_s}{C_{ins}}$$

(1.3)

Fig. 1.3. Cartoon graph of a MOSFET.

From Eq. (1.3),  $\frac{\partial V_g}{\partial \varphi_s}$  is possible to be smaller than one if  $C_{ins}$  is negative. The second part is  $\frac{\partial \varphi_s}{\partial (log_{10}I)}$ , which is limited by the current control mechanism of the transistor and the temperature. For the conventional MOSFET, the minimum value of  $\frac{\partial \varphi_s}{\partial (log_{10}I)}$  is about 60 mV/dec at room temperature, and that

#### Model = Core + Real-Device Effects

Fig. 1.4. Architecture of BSIM from Prof. Chenming Hu's presentation in Sep. 2013.

is why 60mV/dec is called Boltzmann Tyranny. NC can help to overthrow the Boltzmann Tyranny by providing gain to  $\frac{\partial V_g}{\partial \varphi_s}$ .

#### 1.3 Berkeley short-channel IGFET Model (BSIM)

People in fabless design houses may not know the knowledge of semiconductor physics; people in foundries may not understand how to design a circuit. That's how a compact model comes in as a bridge to facilitate communication between fabless design houses and foundries. A good compact model has to be both computationally efficient and must predict the characteristics of transistors accurately. Berkeley short-channel insulator-gate field-effect transistors model (BSIM) is the first industry standard compact model for circuit simulation. The architecture of BSIM is demonstrated in Fig. 1.4. With the scaling of the minimum feature size of transistors. More and more non-idea effect (as shown in the peripheral in Fig. 1.4) models have to been added so the maintenance and improvement of BSIM models never stops. To achieve accurate spice/circuit simulation results, both an accurate compact

model and a good model card are needed. A model card is composed of all the necessary model parameters in order to capture the characteristics of a transistor with single or multiple geometries. The procedure of generating a model card is called parameter extraction. The package of compact models and model card are called process design kit (PDK). A PDK will be sent to design houses from foundries to represent their process technology and specifications.

#### **Chapter 2**

# Optimization of NCFET by Matching Dielectric and Ferroelectric Nonuniformly Along the Channel

A new design to overcome the nonuniformity of capacitance matching along the channel of a negative capacitance field-effect transistor (NCFET) is presented in this section. By introducing non-uniform oxidation, the thickness of SiO<sub>2</sub> at the edge regions of the channel can be increased while maintaining the thickness of SiO<sub>2</sub> at the center region of the channel. As a result, the capacitance along the channel becomes more uniform, and better capacitance matching between the dielectric (DE) and ferroelectric (FE) can be achieved. The Sentaurus TCAD results show matching improvement in the central region and a significant boost of on-current (20% improvement).

#### 2.1 Motivation

The fundamental limit imposed by the Boltzmann distribution (60 mV/decade), which hinders the scaling of CMOS technology, is referred to as the Boltzmann Tyranny [3]-[5]. Tunneling field-effect transistors (TFETs), nano-electromechanical (NEM) switches [6], and negative capacitance field-effect transistors (NCFETs) are promising ways to overcome the Boltzmann Tyranny [7]. However, the NEM switch is subject to reliability and scalability issues [5], while the TFET suffers from low on-current and other non-ideal effects [8]-[9]. NCFETs, on the other hand, can achieve an improved

subthreshold slope (SS) while maintaining high on-current (compared to TFETs) and are fabricated through CMOS-compatible processes [10]. Many NCFETs have been made experimentally [10]-[15]. Nevertheless, many demonstrate a subthreshold swing (SS) of only 50-60 mV/decade without hysteresis and an internal metal gate. An inner metal gate breaks the ferroelectric into multiple domains, causing hysteresis [16] and introducing other non-ideal effects like charge trapping, leading to problems during device operation. Despite this, NCFETs without an internal metal gate usually demonstrate worse performance than NCFETs with an inner metal gate [17] because of bad capacitance matching in the center region of the channel. A possible solution to this problem will be proposed in this study. Many papers have discussed the nonuniformity in electric field, nonuniformity in FE [18]-[21], and methods of improving the degree of capacitance matching [22]-[23].

This study will demonstrate the difficulty of further reducing the SS below 60 mV/decade of hysteresis-free NCFETs without an internal metal gate in B (i) and B (ii). The fringing field from the source and drain plays a vital role in the capacitance matching in the subthreshold region, but the fringing field also limits the capacitance matching at the center of the channel. A possible solution will be proposed in B (iii) to improve the performance of NCFETs further.

#### 2.2 Device Characterization and Discussion

#### **Baseline UTB-SOI Device Structure**

The baseline structure and design parameters are shown in Fig. 2.1 but without the FE layer. The electric field at  $V_g = 0V$  and  $V_d = 0.7V$  is plotted in Fig. 2.2 (a). The electric field is stronger at the edges of the gate oxide, as indicated by the red circles. The stronger electric field at the edges is caused

Fig. 2.1. The simulated device structure with (a) uniform thickness of interfacial layer and with (b) nonuniform thickness of interfacial layer. Table on the right-hand side lists important device parameters. The shaded parameters are for the baseline device. The baseline device has the same structure as (a), but without an FE layer.

by both the inner-fringing field (passing through the Si channel) and outer-fringing field (passing through the  $Si_3N_4$  spacer) [24], leading to nonuniform capacitance along the channel as shown in Fig. 2.2 (b) and imposing the limitation on capacitance matching. Note that the capacitance is shown in Fig. 2.2 (b) is from the structures with an FE layer, and the vertical electric field in the  $SiO_2$  (perpendicular to the FE) right below the FE layer is used to extract the nonuniform  $C_{mos}$  by using Eq. (2.1)

from the TCAD results.

$$C_{mos} = \frac{dQ}{dV} = \frac{d(E_{\perp FE} \times \epsilon_{SiO2})}{dV(x)}$$

(2.1)

where  $E_{\perp FE}$  is the electric field perpendicular to and right below the FE,  $\epsilon_{SiO2}$  is the permittivity of SiO<sub>2</sub>, and dV(x) is the step size of electric potential at the interface of SiO<sub>2</sub> and FE as a function of position along the

Fig. 2.2. (a) The electric field at  $V_g = 0V$  and  $V_d = 0.7V$ . The red circles highlight the higher electric field at the edges of the channel. (b) Capacitance versus position along the channel at  $V_g = 0.7V$ . The green line and the black curve are the traditional capacitance matching design, and the blue line and the red curve are our proposed capacitance matching design.

channel. To avoid hysteresis, the data in Fig. 2.2 (b) is extracted at  $V_g = 0.7V$  and  $V_d = 0.7V$ , where the minimum absolute value of FE capacitance is not smaller than any value of the curve.

#### **Uniform interfacial layer NCFET**

In traditional NCFET design, a uniform thickness of the interfacial layer

along the channel is assumed, and the corresponding ferroelectric capacitance ( $C_{FE}$ ) is matched to its limit with  $C_{mos}$ . In HfO<sub>2</sub>-based NCFETs, the remanent polarization ( $P_r$ ) is more sensitive to ferroelectric doping concentration than the coercive field ( $E_c$ ) [25]. Therefore,  $E_c$  is fixed to 2MV/cm, and  $P_r$  is decreased until  $C_{FE}$  touches the largest  $C_{mos}$  along the channel. The smallest  $P_r$  reached in the TCAD simulation is 11.5  $\mu$ C/cm<sup>2</sup>, which is equivalent to -3.98  $\mu$ F/cm<sup>2</sup> (dielectric constant = 16 is included from [26]) by using Eq. (2.2). The physics models used in TCAD include the Ginzburg-Landau model for ferroelectric materials, Fermi Statistics, velocity saturation, Philips unified mobility model, Shockley-Read-Hall process, and quantum potential [27]. The Ginzburg-Landau model is shown in Eq. (2.3).

$$C_{FE} = \frac{1}{2\alpha t_{FE}} + \frac{16\varepsilon_0}{t_{FE}} (2.2)$$

$$E = 2\alpha P + 4\beta P^3 + 6\gamma P^5 - 2g\Delta P + \rho \frac{dP}{dt} (2.3)$$

In Eqs. (2.2) and (2.3), |CFE| is the estimation of the minimum absolute value of FE capacitance;  $t_{FE}$  is the thickness of the FE;  $\varepsilon_0$  is vacuum permittivity;  $\alpha$ ,  $\beta$ ,  $\gamma$  are the parameters for the FE; g is the strength of the polarization gradient (domain coupling) which is set to be 8E-5 cm<sup>3</sup>/F in this study (on the same order as [27]); and  $\rho$  is the viscosity that represents the finite time required for the polarization to switch.  $\alpha$ ,  $\beta$ , and  $\gamma$  are related to  $P_r$  and  $E_c$  by  $\alpha = -\frac{3\sqrt{3}}{4} \times \frac{E_c}{P_r}$  and  $\beta = \frac{3\sqrt{3}}{8} \times \frac{E_c}{P_r^3}$ , and  $\gamma = 0$  [29]. K. Chatterjee et al. reports that the intrinsic delay of a doped hafnium oxide-based ferroelectric is negligible in digital circuits [30], so  $\rho$  is set to be zero in this study.

#### Proposed nonuniform interfacial layer NCFET

An NCFET with a nonuniform interfacial layer is proposed, as shown in Fig. 2.1 (b). By tuning the thermal gradient or introducing mask oxidation techniques during processing, a thicker  $SiO_2$  can be grown at the edge regions of the channel without affecting the thickness of the  $SiO_2$  at the center region

Fig. 2.3. Polarization and electric field of the FE right above the top of barrier (TOB). The transition from bottom right (deamplification) to upper left (amplification) represents the change of the state of the FE from Vg = 0V to Vg = 0.7V.

of the channel. The  $P_r$  of the FE is now reduced to  $10.1~\mu\text{C/cm}^2$ , which is equivalent to  $-2.68~\mu\text{F/cm}^2$  (using dielectric constant = 16 from [24]) by using Eq. (2.2). The improvement from the perspective of polarization and electric field in the FE is shown in Fig. 2.3. Note that the metal gate work functions of the two cases are shifted to match the off-current of the baseline, so at  $V_g = 0.7$  V (bottom right), there is not much difference in the bias points. At  $V_g = 0.7$  V, the bias point of the proposed NCFET demonstrates an improvement via a

Fig. 2.4. (a) Polarization and (b) conduction band energy versus position along the channel in the off-state. (c) Polarization, (d) electron velocity, and (e) electron density versus position along the channel in the on-state. The black curves represent an NCFET with uniform thickness of the interfacial layer. The red curves represent an NCFET with a thicker interfacial layer at the edges of the channel.

left-shift as indicated by the yellow arrow (more voltage amplification).

Fig. 2.4 (a) plots polarization versus position along the channel at  $V_g = 0V$  (off-state). The profile of FE polarization changes because the capacitance matching condition along with the channel changes. Fig. 2.4 (b) shows conduction band energy versus position along the channel. The barrier heights

are the same because the metal gate work function is shifted to match the offcurrent of the baseline. Note that the position of the TOB is at the middle of the channel, which is why the matching between the FE and DE in the center of the channel is also critical. Fig. 2.4 (c) shows the FE polarization, higher in the NCFET with a nonuniform interfacial layer (more voltage amplification) than the normal NCFET. Fig. 2.4 (d) and 2.4 (e) show the carrier density and carrier velocity at a depth where the carrier concentration is highest (which is not close to the surface due to the quantum confinement effect). A higher current can be supported by higher electron velocity at the source side, as shown in Fig. 2.4 (d). On the other hand, carriers at the drain side have already reached velocity saturation, so the carrier concentration increases more significantly near the drain side, as shown in Fig. 2.4 (e). It is evident from Fig. 2.5 that the proposed NCFET has better ON current (20% improvement) and better SS (minimal SS is 33 mV/decade). In Fig. 2.5, two bias points show a surge in current. The first is around 0.265V, and the second is around 0.615V. Better capacitance matching happens at these two gate voltages. Two gold arrows indicate areas with better capacitance matching in Fig. 2.2 (b). Better capacitance matching over the two areas accounts for the surge in the current of the blue curve in Fig. 2.5 at 0.265V (which corresponds to the left hump of the red curve in Fig. 2.2(b)) and at 0.615V (which corresponds to the right hump of the red curve in Fig. 2.2(b)). Note that these three cases are confirmed to be hysteresis-free by running the transient forward and reverse sweeping test. In comparison, the traditional design has no current surge because the "good matching" parts are not in the channel and therefore contribute little current to the channel.

Fig. 2.5. Drain current versus gate voltage of baseline UTBSOI, traditional uniform-interfacial-layer NCFET, and proposed nonuniform-interfacial-layer NCFET.

#### 2.3 Chapter Summary

The difficulty of capacitance matching due to the nonuniformity of capacitance along the channel is pointed out first in Fig. 2.2. To overcome this difficulty, a new design scheme utilizing a thicker interfacial SiO2 at the edges of the channel is proposed. The results show that the performance of the NCFET can be significantly boosted with this scheme. Therefore, the nonuniform capacitance caused by fringing fields should be considered when NCFETs are designed.

#### **Chapter 3**

# Variation Caused by Spatial Distribution of Dielectric and Ferroelectric Grains in a Negative Capacitance Field-Effect Transistor

A new scheme to consider the dielectric (DE) phases inside polycrystalline ferroelectric (FE) materials will be proposed in this section. The scheme extracts material parameters from experimental Polarization-Electric Field (P-E) measurements from the literature. A Sentaurus TCAD structure is constructed with the extracted parameters, and the simulated P-E curve is in good agreement with experimental data. Furthermore, variation of the device performance in a negative capacitance field-effect transistor (NCFET) due to the spatial distribution of DE and FE phases is studied using Sentaurus TCAD. It is found that the resultant variations of ON and OFF currents can be up to 14.44% and 30.23%, respectively, thus showing the impact of inhomogeneous crystalline phases of the FE material on device performance.

#### 3.1 Motivation

Power consumption becomes the most critical issue as CMOS technology is aggressively scaled. To mitigate this issue, high mobility channel materials and three-dimensional transistors have been explored [31],

[32]. However, the Boltzmann distribution poses a fundamental limit for lowering the energy dissipation in conventional electronics, and this limit is often referred to as the Boltzmann Tyranny [3]-[5], [9]. Negative capacitance FETs (NCFETs) are promising devices to overcome the subthreshold swing limit (60 mV/decade) imposed by the Boltzmann Tyranny and to achieve high Ion [3], [11]-[13], [33]-[39]. Although NCFETs experimentally exhibit sub-60 mV/decade performance [10]-[15], the non-uniformity effects of phases inside the ferroelectric (FE) haven't been investigated. To properly design NCFETs, the non-uniformity effects of phases should be carefully addressed. For example, X-ray diffraction (XRD) experimental data of HfO<sub>2</sub>-based ferroelectric thin films [10] shows that, other than the ferroelectric orthorhombic phase, there also exist cubic and monoclinic phases, which are dielectric (DE). Lun Xu et al. also reported the existence of monoclinic phases in ferroelectric HfO<sub>2</sub> films [40]. In previous work [41]-[42], the ferroelectric layer is assumed to be homogeneous. The Landau equation can solely predict its properties in the simulation, which fails to consider the essential physics in real devices.

| Symbol         | Quantity   | Unit                 |

|----------------|------------|----------------------|

| DE %           | 33.3       | %                    |

| FE %           | 66.7       | %                    |

| α              | -5.810E+10 | cm/F                 |

| β              | 3.286E+19  | $cm^5/(F \cdot C^2)$ |

| γ              | 2.165E+28  | $cm^9/(F \cdot C^4)$ |

| $\mathbf{P}_0$ | 0.307      | μC/cm <sup>2</sup>   |

| $\mathbf{E_0}$ | 0.185      | MV/cm                |

| € r            | 16.38      | unit less            |

Table 3.1. Hysteresis loop fitting results

Fig. 3.1. (a) The circuit model used in Eq. (7) to (13) (b) MFMIM structure for TCAD 2D-simulation.

In this section, we investigate how the locations of the dielectric grains affect the behavior of NCFETs using Sentaurus TCAD after extracting the material parameters from experimental data. The percentage of the dielectric phase in the ferroelectric is assumed to be the same under the same process conditions. Still, the position of the dielectric grains varies, which further affects the behavior of NCFETs. This random dielectric distribution imposes an additional variation on top of the variation from fabrication. This variation should be adequately understood to evaluate and minimize the impact on NCFET performance.

#### 3.2 Device Characterization

### Ferroelectric parameters extraction

To set up the NCFET simulation using Sentaurus TCAD, the measured hysteresis loop of a 10nm ferroelectric from [14] is used to extract the ferroelectric parameters. As mentioned earlier, there are dielectric grains in the ferroelectric thin film, so only using the Landau equation to fit the hysteresis loop is insufficient. The expression for the Polarization-Electric Field (P-E) relation should include a dielectric component in addition to the Landau equation in the simulation. Therefore, the model should consist of a negative and positive capacitor in parallel (Fig. 3.1 (a)). Note that the dielectric response is incorporated into the model to extend the sixth-order-polynomial approximation of Landau theory which has limited fitting capability in positive capacitance regions (the first and the third quadrants). This dielectric constant value is assumed to be the same as DE grains. Therefore, the polarization for a ferroelectric-dielectric-mixed thin film can be expressed as the following equations:

$$E_{FE} = 2\alpha \times P_{LD} + 4\beta \times P_{LD}^{3} + 6\gamma \times P_{LD}^{5}$$

$$P_{FE} = P_{LD} + E_{FE} \times \varepsilon_{r} \times \varepsilon_{o}$$

$$E_{mix} = E_{FE}$$

(3.1)

(3.2)

(3.3)

$$P_{\text{mix}} = Area_{DE} \times E_{\text{mix}} \times \varepsilon_r \times \varepsilon_o + Area_{FE} \times P_{FE}$$

(3.4)

where  $E_{FE}$  is the electric field across negative capacitance;  $\alpha$ ,  $\beta$ , and  $\gamma$  are Landau coefficients;  $P_{LD}$  is the polarization of ferroelectric given by Landau Equation;  $P_{FE}$  is the polarization of FE part with built-in dielectric constant;

$\varepsilon_r$  is the dielectric constant;  $\varepsilon_o$  is the permittivity of vacuum;  $E_{mix}$  is the electric field across the thin film;  $P_{mix}$  is the total polarization with units of  $C/cm^2$ ;  $Area_{DE}$  and  $Area_{FE}$  are the area percentages of DE and FE in total area.

Two assumptions have to be made in order to extract the material parameters properly. It is assumed that the ferroelectric layer consists of 66.7% ferroelectric grains and 33.3% dielectric grains: a reasonable assumption because it has been reported [40] that the percentage of the monoclinic phase inside HfO2-based ferroelectric layers can range from 10% to 50%, depending on the processing conditions; furthermore, there are cubic, tetragonal, and orthorhombic-dielectric phases possibly coexisting in the ferroelectric thin film. Another assumption is that the dielectric constants of

Fig. 3.2. Polarization-Electric Field loop of the proposed model (red line) and measured data (blue dots).

all the grains are the same. Based on these assumptions, we can rewrite the polarization equation from (3.1), (3.2), (3.3), and (3.4):

$$E_{mix} = 2\alpha \times (P_{LD} - P_0) + 4\beta \times (P_{LD} - P_0)^3 + 6\gamma \times (P_{LD} - P_0)^3 + (P_{LD} - P_0$$

$$(P_{LD} - P_0)^5 + E_0 \qquad (3.5)$$

$$P_{FE} = P_{LD} + E_{mix} \times \varepsilon_r \times \varepsilon_o \quad (3.6)$$

$$P_{mix} = 33.3\% \times E_{mix} \times \varepsilon_r \times \varepsilon_o + 66.7\% \times P_{FE} \quad (3.7)$$

where  $P_0$  and  $E_0$  are the offset polarization and electric field due to the leakage in the thin film [43]. The extracted parameters are listed in Table 3.1, and the fitting results are shown in Fig. 3.2.

#### **Sentaurus TCAD MFMIM structure verification**

To study the impact of the dielectric positions on NCFETs, the ferroelectric model (Landau equation) adopted in Sentaurus TCAD should be carefully calibrated. The physical models used in TCAD include the Ginzburg-Landau model for ferroelectric materials, mobility degradation due to carrier-carrier scattering, coulombic scattering, interface scattering, velocity saturation, and the Shockley-Read-Hall process [27]. The structure

Fig. 3.3. Polarization versus electrical field plot.

for TCAD simulation is shown in Fig. 3.1 (b). In Fig. 3.1 (b), a FE-DE mixed layer consists of 2/3 FE and 1/3 DE sandwiched by metal 1 and metal 2. The SiO<sub>2</sub> layer stabilizes the ferroelectric in the negative capacitance region. The

$\alpha$ ,  $\beta$ , and  $\gamma$  values of ferroelectric here are the same as the values in TABLE 3.1. Note that it is assumed no leakage in the FE layer in TCAD, so  $P_o$  and  $E_o$  are not used here. In Fig. 3.3, the curve generated by TCAD is shifted by  $P_o$  and  $E_o$  in the y-direction and x-direction, respectively, to align with experimental data.

Fig. 3.4. NCFET structure in Sentaurus TCAD simulation. The red regions are source and drain. The blue region is 5nm-thick channel sandwiched by the gate stack, which consists of 0.8nm SiO<sub>2</sub>, 2nm segmented FE-DE mixed layer, and metal contact. The n-type source and drain doping are 2E20(#/cm<sup>3</sup>), and the p-type channel doping is 1E17(#/cm<sup>3</sup>). Gate work function is 4.6eV.

To mimic the P-E loop from experimental measurement, the voltage of metal 1 is swept with metal 2 floating. The P-E loop is measured by sandwiching the FE layer with two metal electrodes, so an internal metal to metal is added in the TCAD simulation. The P-E curve can be extracted by plotting the charge density in metal 1 ( $P_{mix}$ ) versus the potential difference of metal 1 and metal 2 over the thickness of FE film ( $E_{mix}$ ). The P-E curve result from TCAD is shown in Fig. 3.3. In Fig. 3.3, the actual remnant polarization is higher because the ferroelectric accounts for only 66.7% of the whole FE-DE mixed layer. At zero electric field, the DE portion contributes zero polarization. The FE part needs 1.5 times of average remnant polarization to build up one time of average remnant polarization, showing that mixed FE-DE phases in the thin

film would degrade the ferroelectricity.

#### **Sentaurus NCFET DE-FE mixed simulation**

Fig. 3.5. Scatter plot of the random simulation results. The red circles are random simulation results, the pink dot represents that all the segments are DE (baseline), and the blue triangle represents that all the segments are FE.

The ferroelectric layers of the n-channel double-gate NCFET with a gate length of 18 nm and a channel thickness of 5 nm are segmented into 3-by-3 matrix elements in the Sentaurus TCAD simulation, as shown in Fig. 3.4. It is known that the grain size of HZO is in the same order as HZO thin film thickness from the experiment [44], so grain size of 6nm by 6nm by 2nm is a reasonable assumption. Each element is either ferroelectric or dielectric with the same material parameters obtained from section B (ii). The gate stack is the same as the previous MFMIM structure in Fig. 3.2 except the removed intermediate metal layer. Note that without the middle metal layer, the spatial

Fig. 3.6. Drain current versus gate voltage characteristics for (a)  $I_{\rm off}$  extreme cases with variation of 30.23% and (b)  $I_{\rm on}$  extreme cases with variation of 14.44%.

distribution of FE and DE matters. That is why the same characterized FE film can bring out different characteristics in this part.

Fig. 3.7. The subthreshold slope versus gate voltage plot of the random DE and FE distribution simulation.

As mentioned in the previous section, 66.7% of the FE-DE layers are ferroelectric, which means two-thirds of segments/grains are ferroelectric. The double-gate NCFET has top and bottom gate stacks with independent DE and FE grains distributions, but 66.7% of each stack consists of FE grains. A random simulation is carried out to examine how the distribution of the DE and FE grains would affect the current of the NCFET. There are 1128 possible combinations by considering two symmetric planes, and 1128 cases are simulated. For each case,  $V_{DD}$  is fixed at 0.65V.  $I_{off}$  and  $I_{on}$  are defined at  $V_{GS}$  = 0 and  $V_{DD}$  at  $V_{DS}$  = $V_{DD}$ , respectively. The results are shown in the scatter plot in Fig. 3.5.

In Fig. 3.5, the green box encloses the boundary of variation due to the different locations of FE and DE grains. Note that the all-FE case means there is no dielectric, but  $\alpha$ ,  $\beta$ , and  $\gamma$  are modified to fit the experimental P-E loop.

The highest and lowest of  $I_{\rm off}$  and  $I_{\rm on}$  are shown in Fig. 3.6 (a) and (b), respectively. The highest  $I_{\rm off}$  (red curve in Fig. 3.6 (a)) happens when the DE grains on both gates are at the positions of 7, 8, and 9, whereas the lowest  $I_{\rm off}$  (black curve) happens when the DE grains are at 2, 4, and 8 on the top gate and at 1, 5, and 7 on the bottom gate. In Fig. 3.6 (b), the highest  $I_{\rm on}$  is obtained when the DE grains are at 3, 6, and 9 on both the top and bottom gates,

Fig. 3.8. Ferroelectric polarization 2-D plot at  $V_{GS} = V_{DD}$ . (a) Source-side ferroelectric (location of DE at number 3, 6, and 9 in Fig. 3.4) with the highest Ion, and (b) drain-side ferroelectric (location of DE at number 1, 4, and 7 in Fig. 3.4) with the lowest Ion.