# UC Merced UC Merced Electronic Theses and Dissertations

### Title

Characterization and Modeling of Error Resilience in HPC Applications

#### **Permalink** https://escholarship.org/uc/item/59k7464g

**Author** Guo, Luanzheng

Publication Date

### **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, MERCED

#### **Characterization and Modeling of Error Resilience in HPC Applications**

by

Luanzheng Guo

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Electrical Engineering and Computer Science

Committee in charge:

Professor Dong Li, Chair Professor Mukesh Singhal Professor Florin Rusu Dr. Ignacio Laguna

Summer 2020

Copyright Luanzheng Guo, 2020 All rights are reserved. The dissertation of Luanzheng Guo is approved:

| Professor Mukesh Singhal  |                                  | Date |  |

|---------------------------|----------------------------------|------|--|

|                           |                                  |      |  |

| Professor Florin Rusu     |                                  | Date |  |

| Dr. Ignacio Laguna        |                                  | Date |  |

| Professor Dong Li (Chair) |                                  | Date |  |

|                           | University of California, Merced |      |  |

Summer 2020

To the ones I love.

# Contents

| Si | gnatu   | re Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | iii |

|----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| De | edicat  | ion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | iv  |

| Li | st of l | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ix  |

| Li | st of ' | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xi  |

| Ac | cknov   | vledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xii |

| Cı | urricu  | ılum Vitae                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | xiv |

| Al | ostrac  | et in the second s | xvi |

| 1  | Intr    | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1   |

| -  | 1.1     | Research Problems and Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2   |

|    |         | 1.1.1 Characterization of Error Resilience in HPC Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2   |

|    |         | 1.1.2 Modeling Error Resilience in HPC Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2   |

|    |         | 1.1.3 Modeling Fault Tolerance to Process/Node Failures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4   |

|    | 1.2     | Research Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5   |

|    | 1.3     | Research Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6   |

|    | 1.4     | Organization of the Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7   |

| 2  | Bac     | kground and Literature Survey                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8   |

|    | 2.1     | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8   |

|    |         | 2.1.1 Transient Fault Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8   |

|    |         | 2.1.2 MPI Failure Recovery Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9   |

|    | 2.2     | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10  |

| 3  | Und     | erstanding Natural Error Resilience in HPC Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14  |

|    | 3.1     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14  |

|    | 3.2     | Design of FlipTracker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15  |

|    |         | 3.2.1 Application Code Region Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15  |

|    |         | 3.2.2 Tracing Code Region Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16  |

|    |         | 3.2.3 Analyzing Corrupted Variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17  |

|    |         | 3.2.4 Identifying Resilience Patterns from Code Regions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 18  |

|    | 3.3     | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19  |

|    |         | 3.3.1 Parallel Tracing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19  |

|   |      | 3.3.2    | DDDG Generation and Usage                                                       | . 19 |

|---|------|----------|---------------------------------------------------------------------------------|------|

|   |      | 3.3.3    | Fault Injection and Statistical Significance                                    | . 20 |

|   | 3.4  | Evalua   | ation                                                                           | . 20 |

|   |      | 3.4.1    | Experimental Setup                                                              | . 20 |

|   |      | 3.4.2    | Parallel Tracing Overhead                                                       | . 21 |

|   |      | 3.4.3    | Code Region Fault Injection Results                                             | . 22 |

|   | 3.5  | Resilie  | ence Computation Patterns                                                       |      |

|   | 3.6  | Case S   | Studies                                                                         | . 27 |

|   |      | 3.6.1    | Use Case 1: Resilience-Aware Application Design                                 | . 27 |

|   |      | 3.6.2    | Use Case 2: Predicting Application Resilience                                   |      |

|   | 3.7  | Concl    | usions                                                                          | . 32 |

| 4 | Mod  | leling A | Application Resilience to Transient Faults on Data Objects                      | 33   |

|   | 4.1  |          | uction                                                                          |      |

|   | 4.2  | Error '  | Tolerance Modeling                                                              | . 34 |

|   |      | 4.2.1    | General Description                                                             |      |

|   |      | 4.2.2    | aDVF: A New Metric                                                              | . 36 |

|   |      | 4.2.3    | Operation-Level Analysis                                                        | . 38 |

|   |      | 4.2.4    | Error Propagation Analysis                                                      | . 39 |

|   |      | 4.2.5    | Algorithm-Level Analysis                                                        | . 41 |

|   | 4.3  | Implei   | mentation                                                                       |      |

|   | 4.4  | Evalua   | ation                                                                           | . 43 |

|   |      | 4.4.1    | Evaluating Application Resilience to Transient Faults on Data                   |      |

|   |      | 4 4 2    | Objects Using aDVF                                                              |      |

|   |      | 4.4.2    | Model Validation                                                                |      |

|   |      | 4.4.3    | Comparing aDVF Calculation with the Traditional Random Fault<br>Injection (RFI) |      |

|   | 4.5  | Case S   | Study                                                                           | . 49 |

|   | 4.6  |          | ssions                                                                          |      |

|   |      | 4.6.1    | Program Optimization by aDVF                                                    |      |

|   |      | 4.6.2    | Beyond Single-Bit Errors                                                        |      |

|   |      | 4.6.3    | Impact of Input Problems                                                        | . 52 |

|   | 4.7  | Concl    | usions                                                                          | . 52 |

| 5 | Prec | dicting  | Application Resilience Using Machine Learning                                   | 53   |

|   | 5.1  | -        | uction                                                                          |      |

|   | 5.2  |          | iew                                                                             |      |

|   | 5.3  |          | n                                                                               |      |

|   |      | 5.3.1    | Feature Construction                                                            |      |

|   |      | 5.3.2    | Introducing Instruction Execution Order (IEO)                                   |      |

|   |      | 5.3.3    | Feature Selection                                                               |      |

|   |      | 5.3.4    | Model Construction                                                              |      |

|   | 5.4  |          | mentation                                                                       |      |

|   | 5.5  | -        | ation                                                                           |      |

|   | 5.5  | 5.5.1    | Prediction Accuracy                                                             |      |

|   |      | 5.5.2    | Feature Selection and Analysis                                                  |      |

|   |      | 0.0.2    |                                                                                 | . 00 |

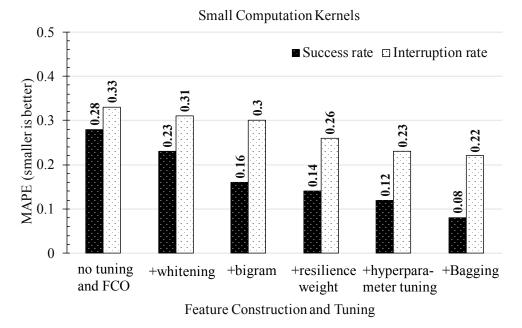

|   |      | 5.5.3    | Evaluation of Model Tuning and Feature Construction Opti-     |            |

|---|------|----------|---------------------------------------------------------------|------------|

|   |      |          | mization                                                      | 70         |

|   |      | 5.5.4    | Efficiency Study-Comparing PARIS to Random Fault Injection    |            |

|   |      |          | and Trident                                                   | 71         |

|   | 5.6  |          | ssions                                                        | 72         |

|   | 5.7  | Conclu   | usions                                                        | 73         |

| 6 | Eva  | luating  | the Performance of Global-Restart Recovery Methods For        |            |

|   | MPI  | [Fault ] | Tolerance                                                     | 74         |

|   | 6.1  | Introdu  | uction                                                        | 74         |

|   | 6.2  | Overv    | iew                                                           | 74         |

|   |      | 6.2.1    | Existing Approaches for MPI Recovery                          | 74         |

|   | 6.3  |          | ++                                                            | 75         |

|   |      | 6.3.1    | Design                                                        | 75         |

|   |      | 6.3.2    | Implementation                                                | 78         |

|   | 6.4  |          | mentation Setup                                               | 81         |

|   | 6.5  | Evalua   | ntion                                                         | 83         |

|   |      | 6.5.1    | Comparing total execution time on a process failure           | 83         |

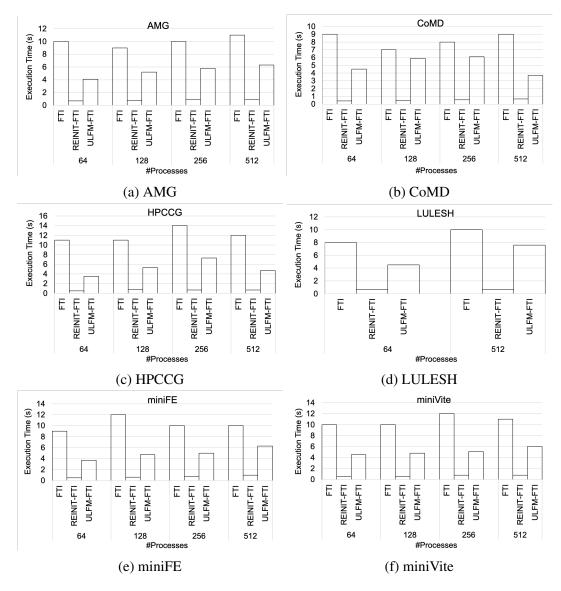

|   |      | 6.5.2    | Comparing pure application time under different recovery ap-  |            |

|   |      |          | proaches                                                      | 84         |

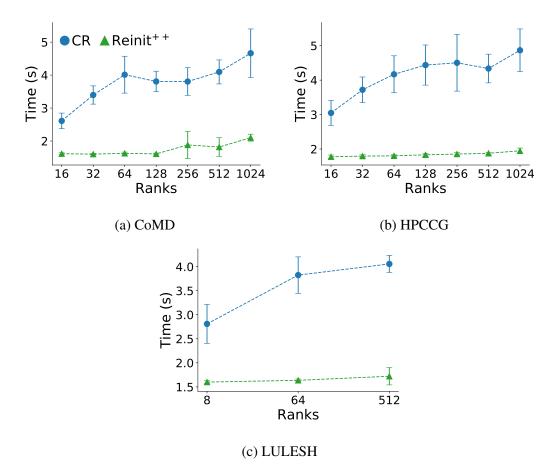

|   |      | 6.5.3    | Comparing MPI recovery time recovering from a process failure | 85         |

|   |      | 6.5.4    | Comparing MPI recovery time recovering from a node failure .  | 86         |

|   | 6.6  |          | usion                                                         | 86         |

|   | 6.7  | Ackno    | wledgment                                                     | 87         |

| 7 | A Be | enchma   | rk Suite to Characterize and Model MPI Application Resilience | 88         |

|   | 7.1  | Introdu  | uction                                                        | 88         |

|   | 7.2  | Overv    | iew                                                           | 89         |

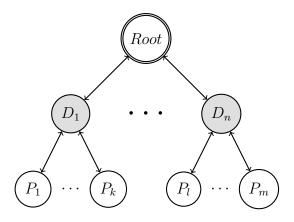

|   |      | 7.2.1    | МАТСН                                                         | 89         |

|   |      | 7.2.2    | Workloads                                                     | 89         |

|   |      | 7.2.3    | Checkpointing Interface - FTI                                 | 90         |

|   | 7.3  | Design   | 1                                                             | 90         |

|   |      | 7.3.1    | Find Data Objects for Checkpointing                           | 90         |

|   | 7.4  | Impler   | mentation                                                     | 92         |

|   |      | 7.4.1    | FTI Implementation                                            | 92         |

|   |      | 7.4.2    | FTI with Reinit Implementation                                | 93         |

|   |      | 7.4.3    | FTI with ULFM Implementation                                  | 93         |

|   |      | 7.4.4    | Fault Injection                                               | 94         |

|   | 7.5  | Evalua   | ation                                                         | 95         |

|   |      | 7.5.1    | Artifact Description                                          | 95         |

|   |      | 7.5.2    | Experimentation Setup                                         | 96         |

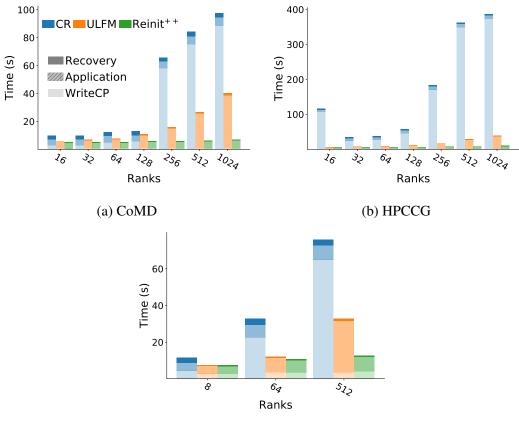

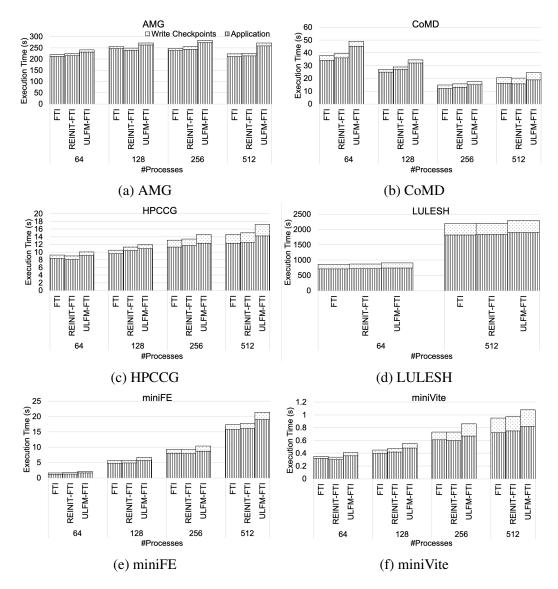

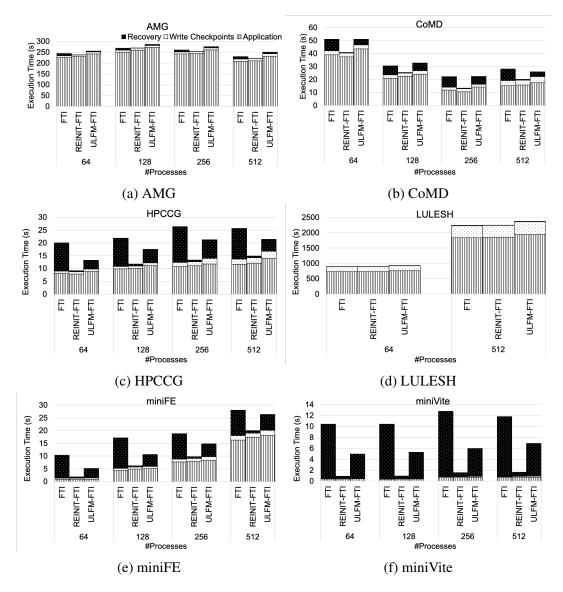

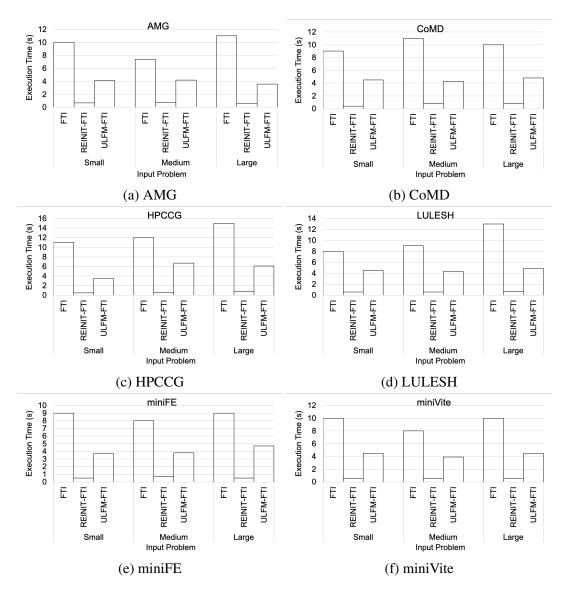

|   |      | 7.5.3    | Performance Comparison on Different Scaling Sizes             | 96         |

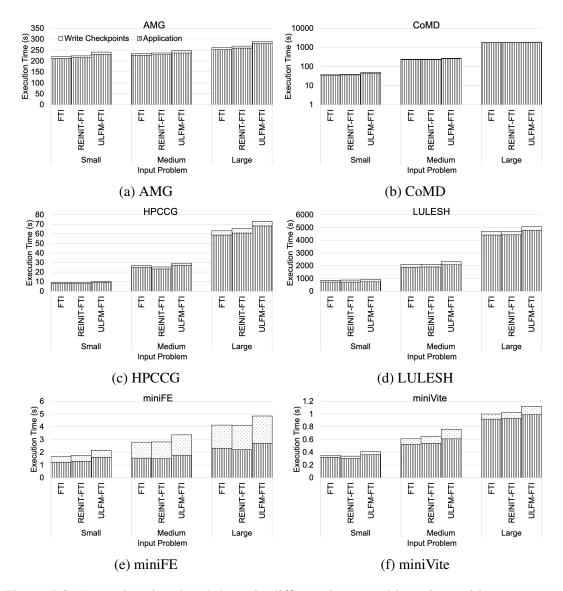

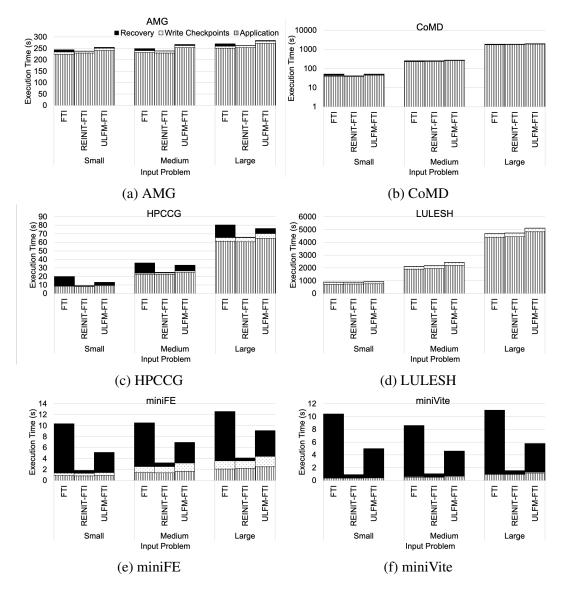

|   |      | 7.5.4    | Performance Comparison on Different Input Sizes               | 101        |

|   |      |          |                                                               |            |

|   | 7.6  | Conclu   | usions                                                        | 103        |

| 8 |      |          |                                                               | 103<br>104 |

|           |       | Work  |     |

|-----------|-------|-------|-----|

|           | 8.2.2 | works |     |

| Bibliogra | aphy  |       | 107 |

# **List of Figures**

| 1.1  | System failures caused by transient faults.                                                | 1  |

|------|--------------------------------------------------------------------------------------------|----|

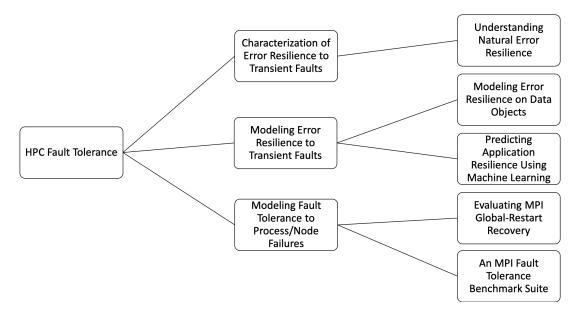

| 1.2  | The overview diagram of my dissertation works                                              | 6  |

| 3.1  | An example HPC application (CG) with iterative structures                                  | 16 |

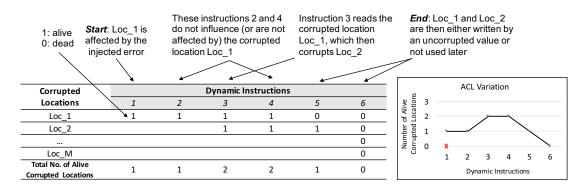

| 3.2  | An example of the ACL table.                                                               | 17 |

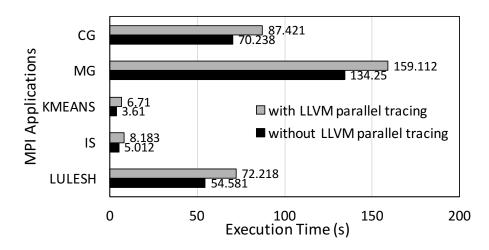

| 3.3  | LLVM parallel tracing performance (64 processes on 8 nodes)                                | 21 |

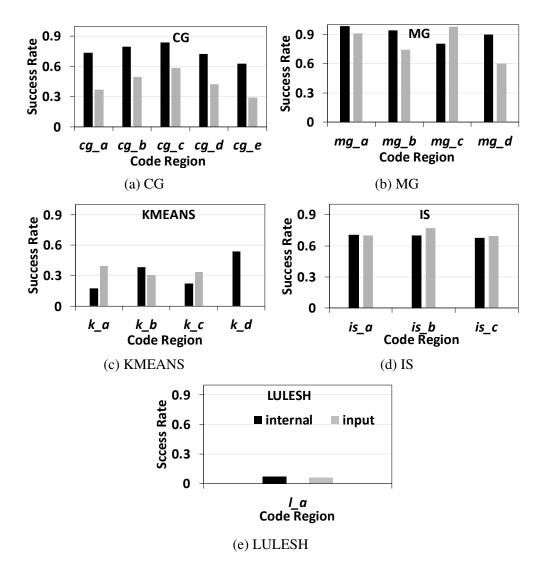

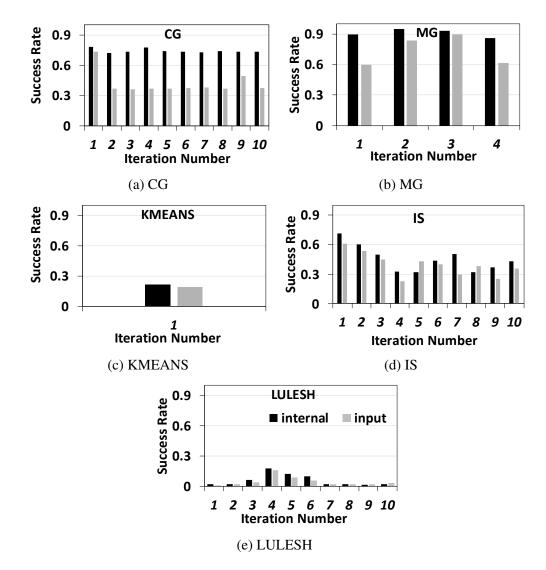

| 3.4  | Fault injection results for code region instances at iteration 0                           | 22 |

| 3.5  | Fault injection results for individual iterations of the main loop                         | 23 |

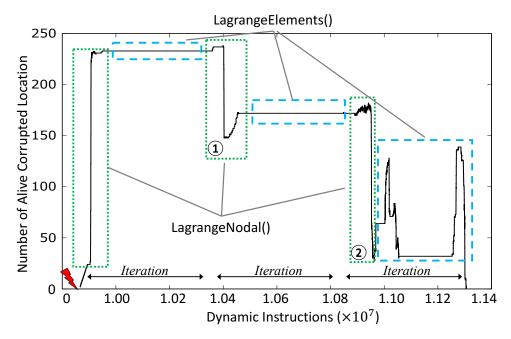

| 3.6  | A real case of ACL table. It shows the number of ACL-s in LULESH after                     |    |

|      | a fault is injected into the last third iteration of the main loop                         | 24 |

| 3.7  | Example of the Dead Corrupted Locations in LULESH                                          | 25 |

| 3.8  | Example of the Repeated Additions pattern in MG                                            | 25 |

| 3.10 | Example of the shifting pattern in IS                                                      | 26 |

| 3.9  | Example of the Conditional Statement pattern in KMEANS                                     | 26 |

| 3.11 | A code excerpt from the function <i>sprnvc</i> () in CG for the Use Case 1. (a) shows      |    |

|      | the original code excerpt before patterns are applied; (b) shows the code excerpt          |    |

|      | when dead corrupted location and data overwriting are applied                              | 29 |

| 3.12 | A code excerpt from the function $conj\_grad()$ in CG for the Use Case 1. (a)              |    |

|      | shows the original code excerpt before the truncation pattern is applied; (b) shows        |    |

|      | the code excerpt when the truncation is applied.                                           | 30 |

| 4.1  | The example code to show error masking that happens to a data object, <i>par_A</i> .       | 35 |

| 4.2  | A code segment from LU.                                                                    | 38 |

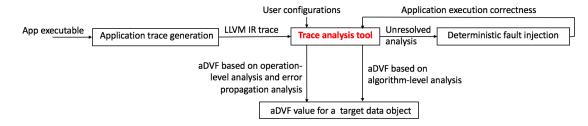

| 4.3  | MOARD, a tool for modeling application resilience to transient faults on                   |    |

|      | data objects                                                                               | 41 |

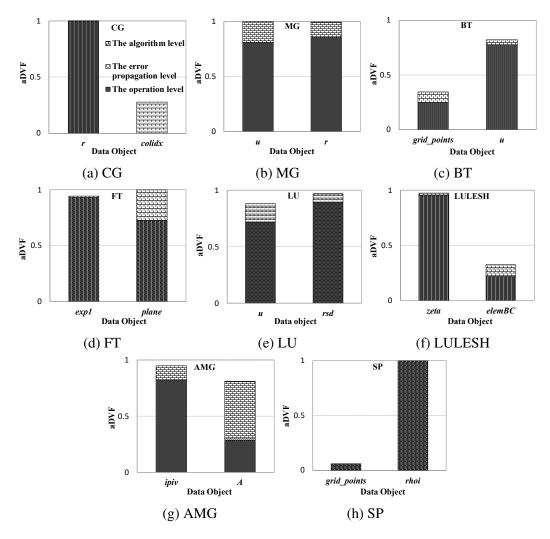

| 4.4  | The breakdown of aDVF results based on the three level analysis. The $x$                   |    |

|      | axis is the data object name.                                                              | 44 |

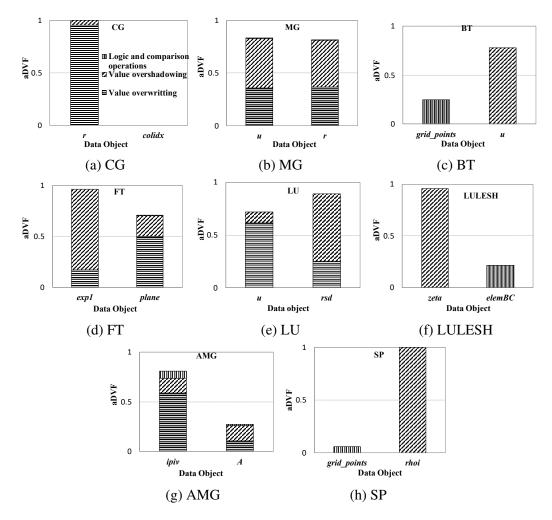

| 4.5  | The breakdown of aDVF results based on value overwriting, value over-                      |    |

|      | shadowing, and logic and comparison operation at the levels of operation                   |    |

|      | and error propagation. The $x$ axis is the data object name. <i>zeta</i> and <i>elemBC</i> |    |

|      | in LULESH are <i>m_delv_zeta</i> and <i>m_elemBC</i>                                       | 45 |

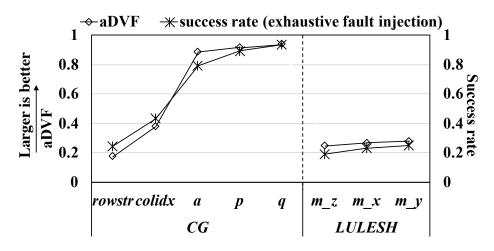

| 4.6  | Model validation against exhaustive fault injection. The x axis shows the                  |    |

|      | data object name.                                                                          | 47 |

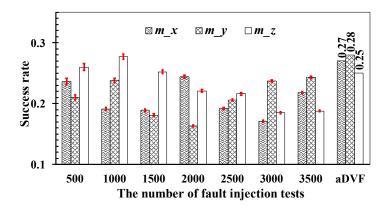

| 4.7  | The RFI results with the margin of error (the confidence level 95%) and                    |    |

|      | aDVF results. The results are for three data objects $(m_x, m_y, and m_z)$                 |    |

|      | from CalcMonotomicQRegionForElems() of LULESH                                              | 48 |

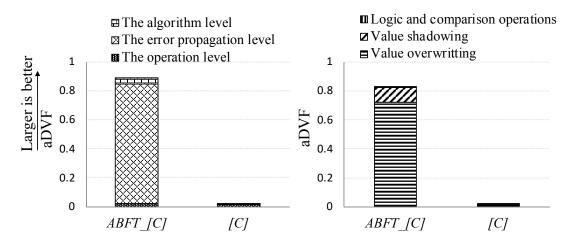

| 4.8<br>4.9 | Using aDVF analysis to study application resilience to transient faults on $C$ in matrix multiplication (MM). Notation: [C] is MM without applying ABFT on $C$ ; ABFT_[C] is MM with ABFT taking effect Using aDVF analysis to study the effectiveness of ABFT for a data object $xe$ in PF. [ $xe$ ] has no protection of ABFT; ABFT_[ $xe$ ] has ABFT taking effect on $xe$ | 50<br>50 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

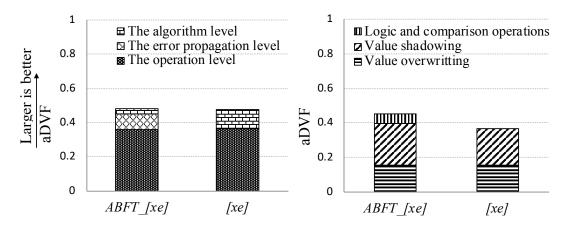

| 5.1        | Overview of PARIS and the workflow of the training process in our ML                                                                                                                                                                                                                                                                                                          |          |

|            | method                                                                                                                                                                                                                                                                                                                                                                        | 55       |

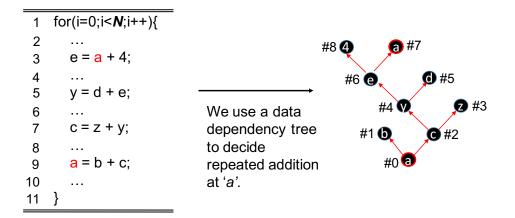

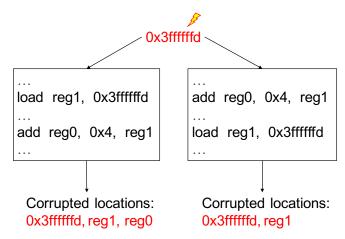

| 5.2        | An example to detect repeated additions.                                                                                                                                                                                                                                                                                                                                      | 59       |

| 5.3        | An example to show that the instruction execution order matters to error                                                                                                                                                                                                                                                                                                      | 60       |

| 5.4        | propagation                                                                                                                                                                                                                                                                                                                                                                   | 00       |

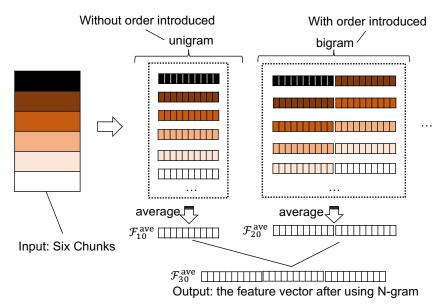

| 011        | information.                                                                                                                                                                                                                                                                                                                                                                  | 61       |

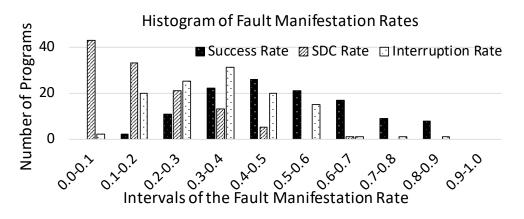

| 5.5        | Histogram of the three fault manifestation rates.                                                                                                                                                                                                                                                                                                                             | 64       |

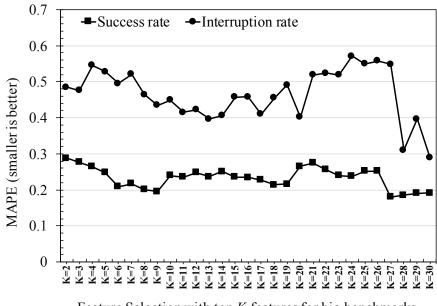

| 5.6        | The ablation study result: the average prediction error for predicting the rates of success and interruption when the best $k$ features are selected ( $k$                                                                                                                                                                                                                    |          |

|            | ranges from 2 to 30)                                                                                                                                                                                                                                                                                                                                                          | 68       |

| 5.7        | Evaluating the impact of model tuning and feature construction optimiza-                                                                                                                                                                                                                                                                                                      |          |

|            | tion on the prediction error for the two fault manifestation rates. FCO = "feature construction optimization". In terms of MAPE, Lower is better                                                                                                                                                                                                                              | 70       |

|            |                                                                                                                                                                                                                                                                                                                                                                               |          |

| 6.1        | The programming interface of Reinit <sup>++</sup> $\dots \dots \dots \dots \dots \dots \dots$                                                                                                                                                                                                                                                                                 | 76       |

| 6.2<br>6.3 | Sample usage of the interface of Reinit <sup>++</sup>                                                                                                                                                                                                                                                                                                                         | 76<br>77 |

| 6.4        | Total execution time breakdown recovering from a process failure                                                                                                                                                                                                                                                                                                              | 84       |

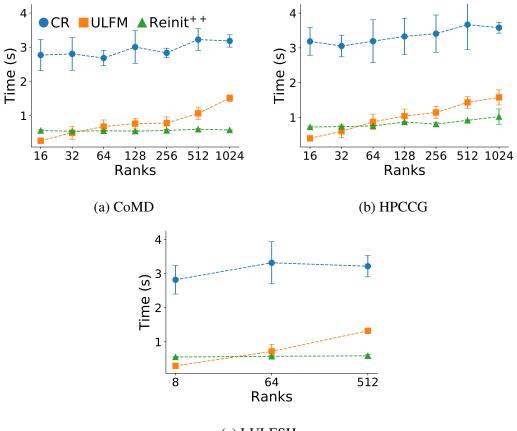

| 6.5        | Scaling of pure application time                                                                                                                                                                                                                                                                                                                                              | 85       |

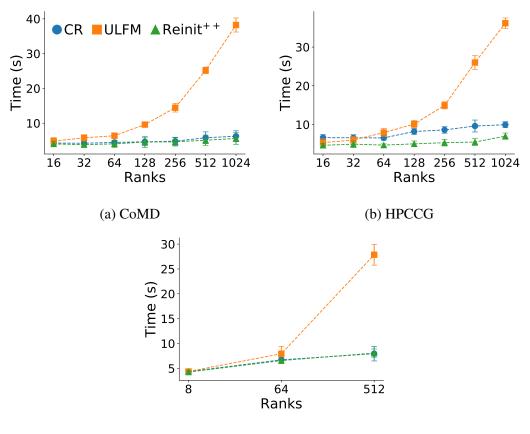

| 6.6        | Scaling of MPI recovery time recovering from a process failure                                                                                                                                                                                                                                                                                                                | 86       |

| 6.7        | Scaling of MPI recovery time recovering from a node failure                                                                                                                                                                                                                                                                                                                   | 87       |

| 7.1        | A sample implementation of FTI                                                                                                                                                                                                                                                                                                                                                | 92       |

| 7.2        | A sample implementation of Reinit.                                                                                                                                                                                                                                                                                                                                            | 93       |

| 7.3        | A sample implementation of ULFM non-shrinking recovery.                                                                                                                                                                                                                                                                                                                       | 94       |

| 7.4        | A sample implementation of fault injection                                                                                                                                                                                                                                                                                                                                    | 95       |

| 7.5        | Execution time breakdown recovering in different scaling sizes with no pro-                                                                                                                                                                                                                                                                                                   | . –      |

| 7 (        | cess failures                                                                                                                                                                                                                                                                                                                                                                 | 97       |

| 7.6        | Execution time breakdown recovering from a process failure in different                                                                                                                                                                                                                                                                                                       | 98       |

| 7.7        | scaling sizes                                                                                                                                                                                                                                                                                                                                                                 | 90<br>99 |

| 7.8        | Execution time breakdown in different input problem sizes with no process                                                                                                                                                                                                                                                                                                     | ,,       |

|            | failures                                                                                                                                                                                                                                                                                                                                                                      | 100      |

| 7.9        | Execution time breakdown recovering from a process failure in different                                                                                                                                                                                                                                                                                                       |          |

|            | input problem sizes                                                                                                                                                                                                                                                                                                                                                           | 101      |

| 7.10       | Recovery time for different input problem sizes                                                                                                                                                                                                                                                                                                                               | 102      |

# **List of Tables**

| 3.1 | Resilience computation patterns in code regions of the HPC programs. DCL, RA, DO represent dead corrupted locations, repeated additions and data |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | overwriting, respectively.                                                                                                                       | 20 |

| 3.2 | The repeated additions pattern takes effect in MG                                                                                                | 25 |

| 3.3 | Results after applying resilience patterns to CG                                                                                                 | 27 |

| 3.4 | The quantification of resilience patterns and the prediction accuracy. SR=succe                                                                  | SS |

|     | rate, OW=overwrite.                                                                                                                              | 31 |

| 4.1 | Benchmarks and applications for the study                                                                                                        | 43 |

| 5.1 | Four groups of instruction types and four resilience computation patterns                                                                        |    |

|     | as features to build our ML model                                                                                                                | 57 |

| 5.2 | The detailed prediction results for 16 big benchmarks. Notation: SR=Success                                                                      |    |

|     | Rate; SDCR=SDC Rate; IR=Interruption Rate; Pred.=Prediction; Meas.=Meas                                                                          |    |

|     |                                                                                                                                                  | 65 |

| 5.3 | Feature voting scores for each dimension of the feature vector $\mathcal{F}_{30}^{ave}$                                                          | 67 |

| 5.4 | The efficiency comparison between FI, Trident, and PARIS. The table in-                                                                          |    |

|     | cludes breakdown of execution time for the PARIS workflow and speedup (using EL as the headling)                                                 | 72 |

|     | (using FI as the baseline)                                                                                                                       | 12 |

| 6.1 | Proxy applications and their configuration                                                                                                       | 82 |

| 6.2 | Checkpointing per recovery and failure                                                                                                           | 82 |

| 7.1 | Experimentation configuration for proxy applications (default scaling size:                                                                      |    |

|     | 64 processes; default input problem: small)                                                                                                      | 95 |

#### Acknowledgments

Foremost, I want to express my sincere gratitude to my Ph.D. advisor Professor Dong Li. First, I want to thank him for bringing me to the University of California-Merced. Professor Dong Li has been a great advisor in the past years. Without his consistent guidance and generous help, I cannot imagine how I could work out these projects, cultivate these publications, and prepare these presentations all by myself. Professor Dong Li has offered me the freedom to explore new research ideas and encouraged me to become an independent researcher. I am always inspired by his continuing motivation, persistence, dedication, diligence, and enthusiasm for science and his humility. I still remember these long and short free rides Professor Dong Li shared with me in these early days and these unforgettable conversations we had in the 50th Celebration of the Turing Award.

I would also like to thank my dissertation committee—Professor Mukesh Singhal, Professor Florin Rusu, and Dr. Ignacio Laguna for serving in my dissertation committee, for their time and effort on reviewing my dissertation and attending my defense, and for their continuous help, constructive comments, and immense knowledge that help significantly advance the quality of this dissertation.

I want further to thank my mentor at Lawrence Livermore National Laboratory, Dr. Ignacio Laguna for always being nice to me. I have been a student summer intern at the Center for Applied Scientific Computing, Lawrence Livermore National Laboratory for four times since 2016. I have learned a lot from Dr. Ignacio Laguna during the past years. I have learned not only how to choose an interesting but essential research problem, how to conduct excellent research, and how to write a good research paper in computer science, but also learned from his patience, kindness, humility, intelligence, and faith in science. Dr. Ignacio Laguna is an example to me, where I can always draw strength to continue my research when feeling frustrated. I also thank Dr. Ignacio Laguna for his generous help in my job hunting and for writing countless recommendation letters.

Furthermore, I would like to thank other colleagues at the lab. My sincere thanks go to Dr. Martin Schulz, my host at the lab and a co-author of my first paper. I have learned good writing styles through his amending to my manuscripts. I appreciate Dr. Martin Schulzs patience and generous help in the past years, for writing recommendation letters for me, for introducing me to his friends, and for his encouragement. I also want to thank Dr. Kathryn Mohror for being my host at the lab, and for passing my resume around for my job hunting. My sincere appreciation goes to Dr. Giorgis Georgakoudis, who is a co-author of my most recent paper, and has helped me a lot for reviewing my code, and for providing insightful comments to my proposals and manuscripts. I am always inspired by his extensive knowledge and constructive considerations. I am very grateful to Dr. Kento Sato for being a good friend who is always nice and offers me many good opportunities, and for sharing research ideas and insights with me. I want to thank Dr. Murali Emani for sharing research insights with me and passing my resume around. I thank Dr. Naoya Maruyama for his help and support on my application to the Livermore Graduate Scholar Program and his help with my job hunting. I thank Dr. Stephanie Brink for her help and support on my application to the Livermore Graduate Scholar Program. I also want to thank my sincere friends and roommates—Dr. Stephen Herbein, Dr. Michael Wyatt, Dr. Dylan Chapp, Dr. William Killian, Dr. Johannes Brust, and Dr. Qunwei Li for these memorable days having fun together and biking to work. Also, I want to thank my officemates at Lawrence Livermore National Laboratory. They are Dr. Teng Wang, Dr, Lai Wei, Dr. Yue Zhu, Dr. Furong Sun, Dr. Jiyuan Zhang, Dr. Cuiyu He, Dr. Zhimin Li, Dr. Christopher Wright, Mr. Duong Hoang, Mr. Ayush Patwari, Ms. Hui Guo, and Mr. Mano Rm.

I want to thank my labmates and friends at UC Merced. Many thanks for these exciting moments and frustrating days we get together. They are Mr. Yingchao Huang, Mr. Himanshu Pillai, Ms. Hanlin He, Mr. Wei Liu, Mr. Kai Wu, Mr. Jing Liang, Ms. Ying Ding, Ms. Wenqian Dong, Ms. Jie Ren, Mr. Letian Kang, Mr. Jiawen Liu, Mr. Jie Liu, Mr. Zhen Xie, Mr. Xin He, Mr. Andrés Torres García, Mr. Jun Hyung Shin, Dr. Tom Kim, Mr. Shattik Rubaiyat Muhammad, Dr. Mina Naghshnejad, Dr. Yijun Li, Mr. Zhixun He, Ms. Belinda Braunstein, Mr. Xin Zhang, Dr. Maryam Shadloo, and Ms. Mahshid Montazer, and many others. I am so grateful to have them in my life in the past five years.

Moreover, I want to thank my mentors, colleagues, and friends I made in conferences for their friendship, inspiration, encouragement, and memorable moments. They are Dr. Christine Harvey, Dr. Jay Lofstead, Dr. Joel Fuentes, Professor Dorian Arnold, Professor Michela Taufer, Mrs. Jenett Tillotson, Dr. Xin Liang, Dr. Sihuan Li, Mr. Tony Liu, Professor Jack Dongarra, Dr. James Rome, Dr. Christian Engelmann, Dr. Hal Finkle, Mr. Mike Lee, Barbara Horner-Miller, Dr. Sean Peisert, Dr. Min Si, Dr. Zhengji Zhao, Professor Sunita Chandrasekaran, Dr. Hongzhang Shan, Dr. Guido Juckeland, Professor Jon Calhoun, Professor Suzanne McIntosh, Dr. Dana Bruson, Dr. Patrick Widener, Professor Ewa Deelman, Dr. Patrick McCormick, Mr. Kevin Walsh, Professor Vladimir Getov, Mr. Eugene Miya, Ms. Tiffany Trader, Dr. Dana Freiburger, Ms. Anna Loup, and many others.

Special thanks go to my advisors during my Master's study who inspired and enlightened my interests in doing research. They are Professor Jun Chu, Professor Chunhong Pan, Professor Shiming Xiang, Professor Guimei Zhang, Professor Jiexian Zeng, Professor Lingfeng Wang, Professor Huaiyu Wu, Professor Gaofeng Meng, Professor Jun Bai, Professor Yin Wang, and Professor Bin Fan. It is my pleasure to begin my journey in academia with them.

Last but not least, I want to express my gratitude to my family for their constant source of inspiration. They are my parents Qiying Lu and Yaohua Guo, my adopted parents Patricia Hachten and Brad Hachten, my paternal grandparents Qiuxiang Xu and Maohuan Guo, and my maternal grandparents Xuemei Huang and Keli Lu. Special thanks to my partner, Qijun Zhang, for the support and love in the past years.

# Curriculum Vitae

### Education

| Ph. D. in Electrical Engineering and Computer Science, University of California-Merced, USA |

|---------------------------------------------------------------------------------------------|

| M. S. in Computer Science, Nanchang Hangkong University, China                              |

| B. S. in Computer Engineering, Nanchang Hangkong University, China                          |

|                                                                                             |

#### Publications

#### **Conference Papers:**

Giorgis Georgakoudis, *Luanzheng Guo*, and Ignacio Laguna. Practical MPI Resilience: A Performance and Correctness Evaluation. ISC HPC Conference (ISC), Frankfurt 2020

*Luanzheng Guo* and Dong Li. MOARD: Modeling Application Resilience to Transient Faults on Data Objects. The 33rd IEEE International Parallel and Distributed Processing Symposium (IPDPS), Rio, Brazil 2019

*Luanzheng Guo*, Dong Li, Ignacio Laguna, and Martin Schulz. FlipTracker: Understanding Natural Error Resilience in HPC Applications. The 30th ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis (SC) 2018

#### **Papers In-submission:**

*Luanzheng Guo*, Dong Li, and Ignacio Laguna. PARIS: Predicting Application Resilience Using Machine Learning. Submitted to Journal of Parallel and Distributed Computing 2020

*Luanzheng Guo*, Dong Li, and Ignacio Laguna. Cross-Architecture Resilience Characterization: Predicting GPU Resilience Using CPU Code. Submitted to XXX20

*Luanzheng Guo*, Giorgis Georgakoudis, Ignacio Laguna, Dong Li. MATCH: An MPI Fault Tolerance Benchmark Suite. Submitted to IISWC'20

#### **Ph.D. Forum Papers:**

*Luanzheng Guo*, Dong Li. Characterization and Modeling of Error Resilience in HPC Applications. The 31st ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis (SC), Denver, CO 2019

*Luanzheng Guo*, Dong Li. Characterization and Modeling of Error Resilience in HPC Applications. The 33rd IEEE International Parallel and Distributed Processing Symposium (IPDPS), Rio, Brazil 2019

#### **Posters:**

Lawrence Livermore National Laboratory Summer Poster Symposium Posters:

Understanding Use of ULFM in MPI Resilience, 2019

Which Fault Injection Tool Should We Use for GPU Programs? 2018

Understanding the Resilience of Fundamental Data Types, 2017

Understanding Resilience Patterns of Algorithms via Application-Level Fault Injection, 2016

*Luanzheng Guo*, Jing Liang, and Dong Li. Understanding Ineffectiveness of Application-Level Fault Injection. The 28th ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis (SC) 2016

#### Honors

| 2020      | Trusted CI Fellow by the NSF Cybersecurity Center of Excel-<br>lence       |

|-----------|----------------------------------------------------------------------------|

| 2019      | UC Merced GSA Travel Award for SC19                                        |

| 2019      | IEEE CS TCHPC Travel Award for SC19                                        |

| 2019      | UC Merced Graduate Dean's Dissertation Fellowship                          |

| 2019      | UC Merced Graduate Fellowship Incentive Program Award                      |

| 2019      | IEEE TCPP Travel Award for IPDPS19                                         |

| 2018      | Research highlighted by HPCwire in its Whats new in HPC re-<br>search?     |

| 2018      | SC18 Outstanding Student Volunteer                                         |

| 2018      | SC18 Outstanding Lightning Talk                                            |

| 2018      | Outstanding reviewer award by Elsevier                                     |

| 2017      | ACM SIGHPC Travel Award to attend the 50th celebration of the Turing Award |

| 2016      | Best poster finalist in SC16                                               |

| 2015-2017 | Bobcat Fellowship at UC Merced                                             |

#### Abstract

#### Characterization and Modeling of Error Resilience in HPC Applications by Luanzheng Guo Doctor of Philosophy in Electrical Engineering and Computer Science University of California, Merced Professor Dong Li, Chair

HPC systems are widely used in industrial, economical, and scientific applications, and many of these applications are safety- and time-critical. We must ensure that the application execution is reliable, and the scientific simulation outcome is trustworthy. As HPC systems continue to increase computational power and size, next-generation HPC systems are expected to incur a higher failure rate than contemporary systems. How to ensure scientific computing integrity in the presence of an increasing number of system faults is one of the grand challenges (also known as the resilience challenge) for large-scale HPC systems.

This dissertation focuses on characterizing, modeling, developing, and advancing resilience strategies and tools in HPC systems to allow scientific applications to survive system failures better. In particular, in this dissertation we systematically characterize HPC applications to find reasons accounting for nature error resilience of HPC applications by tracking error propagation and also by capturing application properties according to their significance to application error resilience using machine learning. We further model application error resilience at different granularities, including individual data objects, small computation kernels, and the whole application. Also, we develop an error resilience benchmark suite to comprehensively evaluate and comparatively study different error resilience designs in the presence of MPI process or node failures. With the knowledge learned from characterization and modeling of application error resilience, we propose a collection of new methodologies and tools that can guide HPC practitioners to find the most effective and efficient error resilience designs, provide helps to advance effectiveness and efficiency of the existing error resilience designs, and build inspiration foundations to future error resilience designs aiming at higher effectiveness and efficiency of HPC systems.

# Chapter 1 Introduction

The continued growth of large-scale high-performance computing (HPC) systems is fueled by two trends: continued integration of additional functionality onto system nodes, and the increased number of nodes (and components) in the systems. As a result, these large-scale systems are jeopardized by potentially increasing faults in hardware and software [143, 132, 140, 77, 142, 139]. Ensuring scientific computing integrity and correctness of application execution in the presence of faults remains one of the grand challenges (also known as the resilience challenge) for large-scale HPC systems [31, 32].

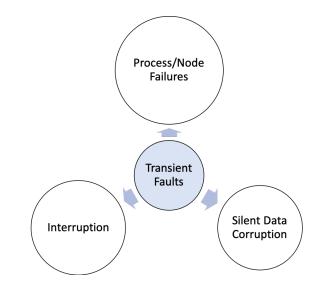

We focus on transient faults and the cascading failures caused by transient faults [62, 49]. Transient faults [14] due to high energy particle strikes, wear-out, and other factors are expected to become a critical contributor to in-field system failures of high-performance computing (HPC). As illustrated in Figure 1.1, transient faults can lead to not only interruptions, but also silent data corruption (SDC), which can impact scientific results without users realizing it. Furthermore, transient faults are considered a critical contributor to system process/node failures according to a recent investigation [62]. As the number of transient faults grows, it becomes increasingly necessary to develop more efficient and effective fault tolerance mechanisms to protect application execution from

Figure 1.1: System failures caused by transient faults.

transient faults and system failures caused by transient faults.

In this dissertation, we propose a composition of techniques, algorithms, and tools to characterize and model error resilience in HPC applications by analytical and machine learning models from a variety of aspects, and at different granularities.

### **1.1 Research Problems and Challenges**

We face a range of challenges on characterization and modeling of application error resilience in HPC applications. We discuss the research problems and challenges below.

#### **1.1.1** Characterization of Error Resilience in HPC Applications

Previous work on fault tolerance, which typically focused on individual applications, demonstrates that a number of applications can transparently tolerate transient faults before they affect the application's numerical output. Examples of such applications are algebraic multi-grid solvers (AMG) [34], Conjugate Gradient (CG) solvers [129], GMRES iterative solvers [55], Monte Carlo simulations [11], and machine learning algorithms, such as clustering [94] and deep-learning neural networks [9, 123].

While previous work attributes this natural resilience at a high-level to either the probabilistic or iterative nature of the application, the community still lacks the fundamental understanding of the program constructs that result in such natural error resilience. Fundamentally, we do not have clear answers to questions, such as: Are there any common computation patterns (i.e., combinations or sequences of computations) that lead to natural error resilience? If so, how can these patterns be found? How can future application design benefit from patterns exhibiting natural resilience?

Finding answers to these questions is critical for error detection and recovery to avoid overprotecting regions of code that are naturally resilient.

#### **1.1.2 Modeling Error Resilience in HPC Applications**

#### Analytical modeling: Understanding Resilience on Data objects

If transient faults manifest in architecturally visible states (e.g., registers and the memory) and those states hold values of a data object, then we have transient faults on the data object. Transient faults on a data object impact application outcome correctness. Understanding application resilience to transient faults on data objects is critical to ensure computing integrity in future large-scale systems.

Furthermore, many common application-level fault tolerance mechanisms focus on data objects. Understanding application resilience to transient faults on data objects can be helpful to direct those mechanisms. Application-level checkpointing is an example of such an application-level fault tolerance mechanism. By periodically saving the correct values of some data objects into persistent storage, application-level checkpoint makes application resumable when a failure happens. Some algorithm-based fault tolerance methods [39, 45] are other examples. They can detect and locate errors in specific data objects. However, those application-level fault tolerance mechanisms can be expensive (e.g., 35% performance overhead in [53]). If data corruptions of a data object are easily tolerable by the application, then we do not need to apply those mechanisms to

protect the data object, which will improve performance and energy efficiency. Hence, understanding application resilience to transient faults on data objects is useful to direct those application-level fault tolerance mechanisms.

However, we do not have a method or a tool to quantify application resilience to transient faults on data objects. The current common practice to understand application resilience to transient faults in HPC is application-level random fault injection [28, 96, 97, 34, 156, 153, 40, 28, 150, 61, 88, 79]. Although random fault injection is useful, it makes it difficult to study application resilience to transient faults on data objects because of the following two reasons.

First, random fault injection loses application semantics (data semantics). Random fault injection randomly selects instructions and triggers random bit flip in input or output operands of the instructions. Typically, random fault injection performs a large amount of random fault injection tests, and then calculates that among all fault injection tests, how many of them succeed (i.e., having correct application outcomes). However, random fault injection gives us little knowledge of *how* and *where* errors are tolerated [69]. Understanding "how" and "where" is necessary to identify why the application is vulnerable to the value corruption of some data objects, and provides feedback on how to apply application-level fault tolerance mechanisms effectively and efficiently.

How can we model and measure application resilience to transient faults on data objects without doing fault injection? How can we model the application resilience to data objects at individual operations? How can we model the application resilience to data objects during the error propagation? Can we track the error propagation on data objects to the end of the execution?

#### Machine learning modeling: Predicting Application Resilience

While random fault injection works in practice and is widely used in resilience studies, a key problem of this approach is that it is highly time consuming, and as a result, it is usually applied to limited scenarios, for example, on applications that run for a short period of time and/or single-threaded codes. To illustrate the problem, consider an application that runs for 6 hours—a typical execution time for a large-scale scientific simulation. Using statistical analysis (e.g., using [95]), the number of random fault injections to obtain a low margin of error (e.g., 1%-3%) is in the order of thousands of injections. Thus, the total fault injection campaign could last several days. For multi-threaded or multi-process applications, this time is much higher since random faults must be injected in different threads or processes.

To address the limitations of FI, researchers have built error-propagation analytical models [98], which are faster than FI in estimating application resilience. However, they lack accuracy as they estimate application resilience to errors based on the analysis of possible errors in individual instructions. The analysis inaccuracy at individual instructions is accumulated, causing low accuracy to estimate the whole application resilience. Furthermore, these models do not consider the effects of resilience computation patterns (e.g., dead corrupted locations and repeated addition [65]). Studying those patterns demands analyzing multiple instructions together, while most existing analytical models analyze instructions in isolation. In summary, the community lacks a fundamental approach that enables fast and accurate evaluation of application resilience.

Can we propose an approach to predict application resilience that can solve above problems efficiently and effectively? Is machine learning a solution to these problems?

If yes, what characteristics can we use as features to make the prediction? What machine learning model can fit into our case?

#### **1.1.3** Modeling Fault Tolerance to Process/Node Failures

Next-generation HPC systems are expected to incur a much higher failure rate than contemporary systems. For example, the Sequoia supercomputer located in Lawrence Livermore National Laboratory (LLNL) reported a mean time between node failures to be 19.2 hours in 2013 [51]. After that, in 2014 the Blue Waters supercomputer reported a mean time between node failures to be 6.7 hours [49]. Most recently, the Taurus system located in TU Dresden reported a mean time between node failures to be 3.65 hours [62].

This trend raises concerns in the HPC community for MPI applications running on tens of thousands of processes and nodes to fail when facing an increasing number of process and node failures. An MPI application execution can fail on node failures because of a variety of reasons, such as transient faults and Byzantine faults [62]. These underneath faults may not directly make the application execution fail, whereas they can cause a process or node failure to the node where the application is running. The process or node failure can further cause the entire MPI application to fail.

These crucial facts lead to an increasing importance of and challenges for developing efficient and effective fault tolerance designs for scaling HPC systems. There are numerous fault tolerance techniques proposed to protect MPI application execution from system failures. Checkpointing [84, 71, 23, 8, 89], commonly used in HPC applications, is one type of fault tolerance technique that saves application execution states periodically. Checkpointing helps MPI applications to quickly restore application states from the latest checkpoints. The other type of MPI fault tolerance technique focuses on restoring MPI states in the occurrence of MPI process and node failures. Restarting is a baseline solution for restoring MPI states, which immediately restarting an application after execution collapses due to a failure. Later, researchers realize the inefficiency of restarting an application, and propose MPI process recovery mechanisms to restore MPI states in real-time. User-Level Fault Mitigation (ULFM) [19] and Reinit [91, 35, 60] are the two pioneer MPI process recovery frameworks in this effort. ULFM provides extended MPI interfaces to programmers to detect failures and restore MPI states, which enables the execution to continue with the same number of processes or only with the survivor processes. Reinit also supports real-time MPI recovery, but transparently implement detecting failures and fixing MPI states to the MPI runtime.

Although there has been a large bibliography [19, 35, 91, 20, 102, 120, 73, 84, 71, 23, 89] discussing the programming model and prototypes of those MPI recovery approaches, no study has presented an in-depth performance evaluation of them–most previous works either focus on individual aspects of each approach or perform limited scale experiments. Can we design an extensive evaluation framework to fairly compare the two leading MPI recovery approaches? Can we understand the fault tolerance behavior difference in ULFM and Reinit recovery?

Furthermore, there is not a standard paradigm to follow for developing efficient MPI fault tolerance. The traditional practices [19, 35, 91, 20, 102, 120, 73] in MPI fault tolerance either focus on only checkpointing mechanisms or only MPI recovery techniques. Later, researchers realize the efficiency of combining the two aspects to achieve higher

efficiency of MPI fault tolerance. For example, FENIX [57] and CRAFT [134] both design and develop a checkpointing interface that supports data recovery for ULFM shrinking and non-shrinking process recovery. However, they request developers to explicitly manage and redistribute the restored data among survivor processes in case of a non-shrinking recovery. This can easily cause load imbalance problems. Also, they only evaluate their frameworks on two applications, and do not compare their fault tolerance frameworks to other fault tolerance designs. For example, using Reinit for process recovery, and testing different checkpointing interfaces. In conclusion, there is not a structured way in existing works that either benchmark the design and implementation of MPI fault tolerance, or comprehensively compare the performance efficiency of different combinations or configurations of fault tolerance designs. Can we develop a comprehensive evaluation framework which enables an effective comparison of distinct MPI fault tolerance configurations?

# **1.2 Research Objectives**

The dissertation seeks to characterize representative fault tolerance frameworks to research and identify fundamentally new ways to design and build effective and efficient fault tolerance theorems, mechanisms, and tools for HPC by leveraging domain-specific characteristics at both the system- and application-level.