## **UC Berkeley**

### **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Energy-efficient and High-bandwidth Density Monolithic Optical Transceivers in Advanced CMOS Processes

#### **Permalink**

https://escholarship.org/uc/item/5c17z5w8

#### **Author**

Moazeni, Sajjad

#### **Publication Date**

2018

Peer reviewed|Thesis/dissertation

# Energy-efficient and High-bandwidth Density Monolithic Optical Transceivers in Advanced CMOS Processes

by

Sajjad Moazeni

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Vladimir Stojanović, Chair Professor Ming C. Wu Professor Liwei Lin

Summer 2018

# Energy-efficient and High-bandwidth Density Monolithic Optical Transceivers in Advanced CMOS Processes

Copyright 2018 by Sajjad Moazeni

#### Abstract

Energy-efficient and High-bandwidth Density Monolithic Optical Transceivers in Advanced CMOS Processes

by

Sajjad Moazeni

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley

Professor Vladimir Stojanović, Chair

Today's conventional cloud computing and mobile platforms have been challenged by the advent of Machine Learning (ML) and Internet of Things (IoT). The performance and diversity requirements of these applications demand the shift towards hyper-scale data centers, Exascale high-performance computing (HPC), energy-efficient edge computing, and new sensing and imaging modalities. My research goal is to design and implement large-scale and energy-efficient integrated systems that answer these technological changes by merging state-of-the-art electronics with photonics.

This thesis developes several monolithic photonics platforms in advanced CMOS technologies that were designed as key enablers for the next-generation of integrated systems: (1) Using unmodified CMOS in 32/45 nm SOI nodes places photonics next to one of the fastest transistors and enhances integrated system applications beyond the Moore-scaling, while being able to offload major communication tasks from more deeply-scaled compute and memory chips without the complications of 3D integration approaches. (2) Poly-silicon based photonics in bulk CMOS as a path for embedding photonics in the most advanced CMOS nodes (sub-10 nm). We demonstrate system results using these platforms for the immediate application area of high-performance optical transceivers. We elaborate on the electronicphotonic co-optimization opportunities on the example of optical interconnect application, a 40 Gb/s optical transmitter achieving the world record energy and bandwidth density. Furthermore, we explain how deep insight into details of an advanced CMOS process can leverage photonic device design, enabling new degrees of freedom in a seemingly constrained environment. Lastly, we demonstrate the first monolithic integrated photonics platform in a commercial 300 mm-wafer bulk CMOS technology. We implemented the photonic systemon-chip (SoC) in this platform for *in-situ* device characterization and process development, and demonstrated wavelength division multiplexed (WDM) optical transceivers. These integrated platforms and system design methodologies can unlock new functionalities in many applications such as HPC, high-bandwidth wireless connectivity, LiDAR, bio-sensing, etc.

To My Family

# Contents

| C  | onter              | nts                                                                                                                                                                                   | ii                                                                                                                        |

|----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Li | st of              | Figures                                                                                                                                                                               | iv                                                                                                                        |

| Li | st of              | Tables                                                                                                                                                                                | iv  ix  1  4  7  7  10  12  13  15  17  19  22  24  25  27  28  31  39  39  39  39  39  39  40  Optical Links  41  44  46 |

| 1  | <b>Intr</b><br>1.1 | roduction Thesis Organization and Contributions                                                                                                                                       |                                                                                                                           |

| 2  | Pre                | liminaries                                                                                                                                                                            | -                                                                                                                         |

|    | 2.1                | Optical Interconnects                                                                                                                                                                 | 10<br>12                                                                                                                  |

|    | 2.2                | 2.1.3 Laser Sources and Integration                                                                                                                                                   | 15<br>17                                                                                                                  |

|    | 2.3<br>2.4<br>2.5  | Zero-change 45nm SOI CMOS Platform  2.3.1 Waveguides  2.3.2 Grating Couplers  2.3.3 Modulators  2.3.4 Photodetectors  Photonic SoC Design Flow  Energy-efficiency & Bandwidth-density | 22<br>24<br>25<br>27<br>28<br>31                                                                                          |

| 3  | Elec               | etronic-Photonic Co-optimization                                                                                                                                                      | 39                                                                                                                        |

|    | 3.1<br>3.2         | Motivation                                                                                                                                                                            | 40<br>41<br>44                                                                                                            |

|    | 3.3                | Ring-resonator based Optical DAC                                                                                                                                                      | 46<br>46                                                                                                                  |

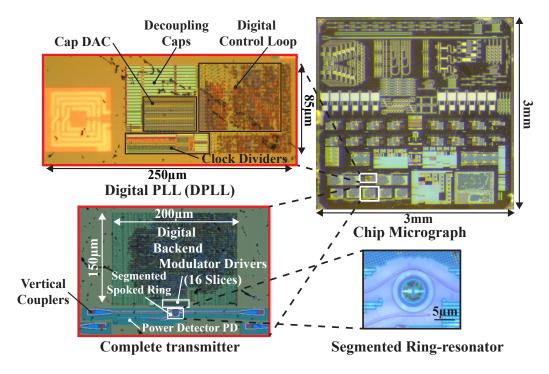

|    |       | 3.3.2 Segmented Ring-resonator ODAC in zero-change 45nm SOI platform | 49  |

|----|-------|----------------------------------------------------------------------|-----|

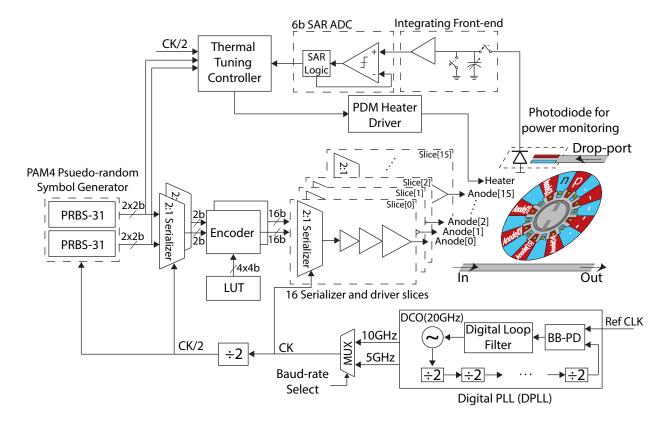

|    | 3.4   | PAM-4 Optical Transmitter Building Blocks                            | 50  |

|    |       | 3.4.1 Transmitter Data-path                                          | 50  |

|    |       | 3.4.2 Digital PLL (DPLL)                                             | 52  |

|    |       | 3.4.3 Thermal Tuning                                                 | 53  |

|    | 3.5   | Complete Transmitter Design                                          | 59  |

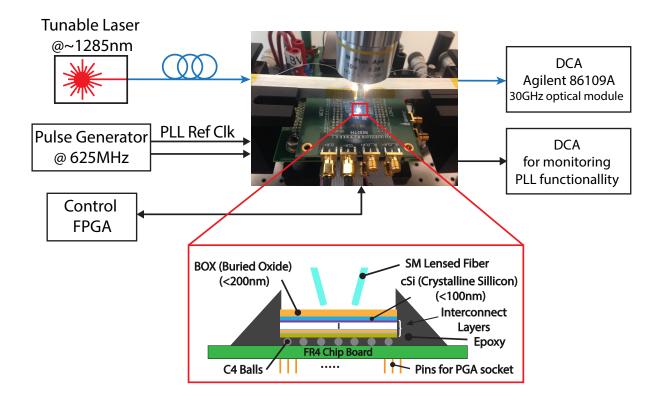

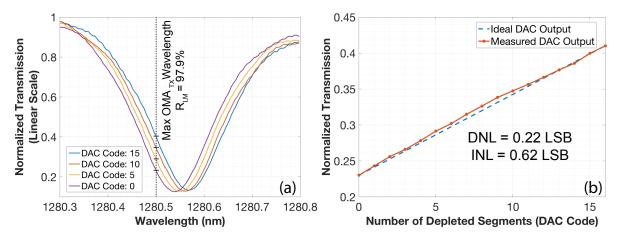

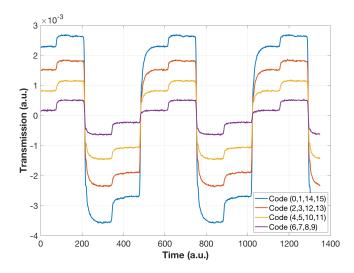

|    | 3.6   | Experimental Demonstration                                           | 60  |

|    | 3.7   | Summary                                                              | 65  |

| 4  | Moi   | nolithic Photonics in 32nm SOI CMOS                                  | 70  |

|    | 4.1   | Monolithic Photonic Platform in Zero-change 32nm SOI CMOS            | 71  |

|    | 4.2   | Photonic Device Design                                               | 73  |

|    |       | 4.2.1 Passive Photonic Devices                                       | 73  |

|    |       | 4.2.2 Active Photonic Devices                                        | 76  |

|    | 4.3   | Electronic-Photonic Optical Tranceivers                              | 80  |

|    | 4.4   | Summary                                                              | 83  |

| 5  | Pho   | otonic SoCs in Bulk CMOS                                             | 85  |

|    | 5.1   | Monolithic Photonic Platform in 65nm Bulk CMOS                       | 87  |

|    | 5.2   | Photonic Devices                                                     | 92  |

|    |       | 5.2.1 Loss Mechanisms in Polysilicon Waveguides                      | 93  |

|    |       | 5.2.2 Defect States based Photodetection in Polysilicon              | 95  |

|    |       | 5.2.3 Passive Devices                                                | 96  |

|    |       | 5.2.4 Active Devices                                                 | 98  |

|    | 5.3   | Design of a Photonic SoC in Bulk CMOS                                | 102 |

|    |       | 5.3.1 Chip Implementation                                            | 103 |

|    |       | 5.3.2 Electrical Performance Evaluation                              | 104 |

|    |       | 5.3.3 Electronic-Photonic WDM Transceivers                           | 104 |

|    | 5.4   | Summary                                                              | 108 |

| 6  | Con   | nclusion                                                             | 110 |

|    | 6.1   | Thesis Summary                                                       | 110 |

|    | 6.2   | Next-generation Electronic-Photonic Integrated Systems               | 112 |

| Bi | bliog | graphy                                                               | 114 |

# List of Figures

| 1.1  | (a) Evolution of the average top 10 supercomputers normalized to year 2010 (top500–June rankings), (b) Evolution of the top 10 systems average node com- |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | puter power, node bandwidth, and resulting byte/flop aspect ratio [1]                                                                                    | 2  |

| 1.2  | Processor-memory bandwidth trend for high-performance CPU/GPUs                                                                                           | 3  |

| 1.3  | (a) Advanced heterogeneous GPU/CPU packaging (AMD GPU), (b) Emerging                                                                                     | 0  |

| 1.0  | high-performance computing systems (Nvidia DGX-2 supercomputer)                                                                                          | 3  |

|      | mon performance companies systems (1111ans 2 cir 2 supercompassi).                                                                                       |    |

| 2.1  | Electrical transceivers power efficiency vs. copper channel loss (from ISSCC                                                                             |    |

|      | Trends 2018)                                                                                                                                             | 8  |

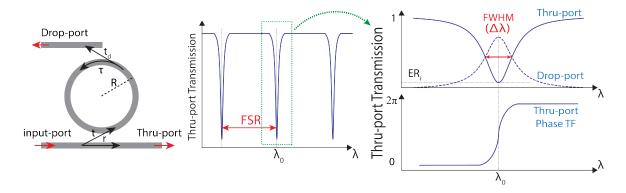

| 2.2  | Ring-resonator characteristics and transfer functions                                                                                                    | 10 |

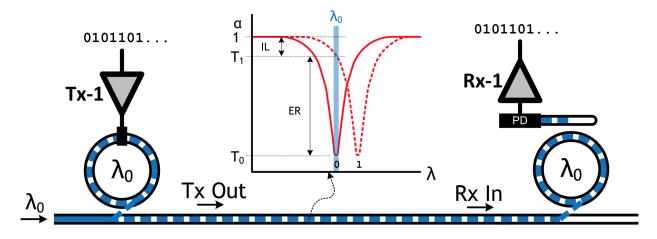

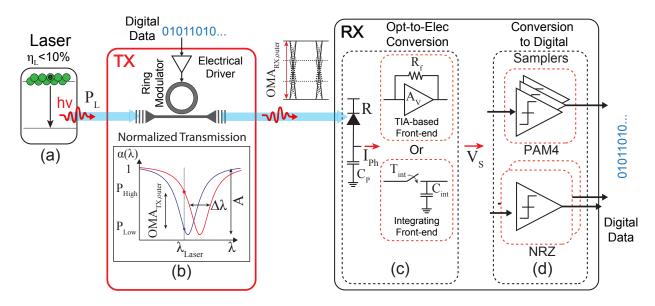

| 2.3  | A ring resonator based optical link [2]                                                                                                                  | 13 |

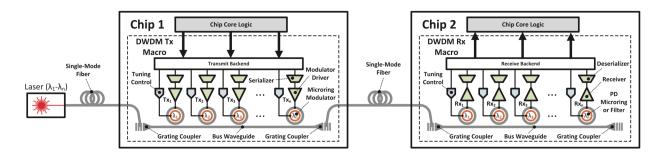

| 2.4  | An example of a WDM link using ring resonators [2]                                                                                                       | 14 |

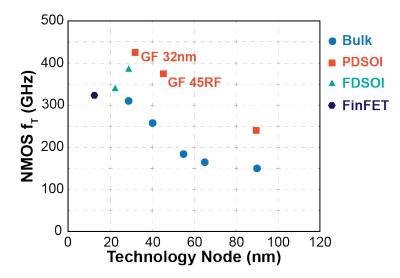

| 2.5  | Unity current gain frequency $(f_T)$ of NMOS devices in IBM/GF processes                                                                                 | 18 |

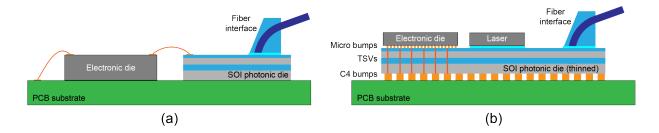

| 2.6  | Hybrid and 3D integration methods: (a) Wire-bond packaging, (b) Next-generation                                                                          |    |

|      | 3D micro bump packaging with Through-silicon vias (TSVs) [3]                                                                                             | 19 |

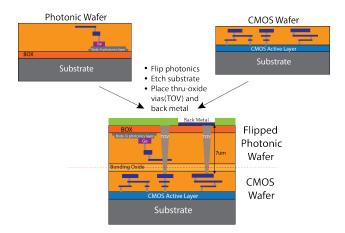

| 2.7  | Wafer-level 3D integration via through-oxide vias (TOV) [4]                                                                                              | 20 |

| 2.8  | Commercial fabrication platforms for the CMOS technology                                                                                                 | 21 |

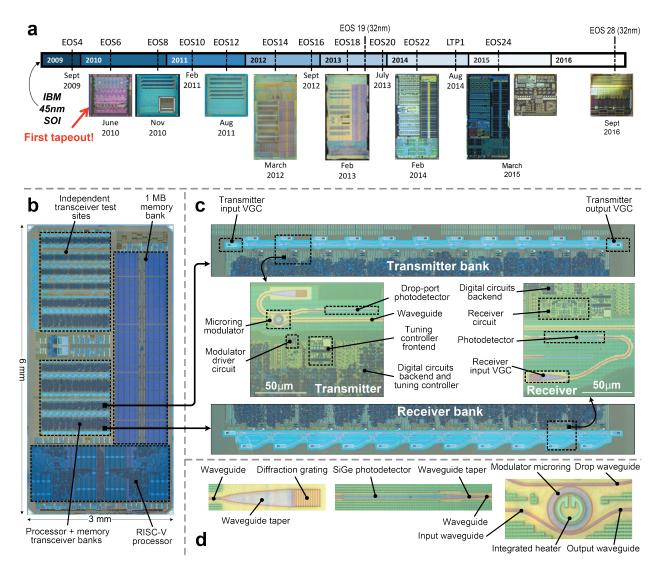

| 2.9  | Zero-change SOI platform evolution; (a) Development timeline, (b) EOS22 die                                                                              |    |

|      | photo, (c) WDM transceivers, (d) Key photonic devices of an optical link                                                                                 | 23 |

| 2.10 | Cross-section of the zero-change 45 nm SOI platform [5]. (Figure is not drawn to                                                                         |    |

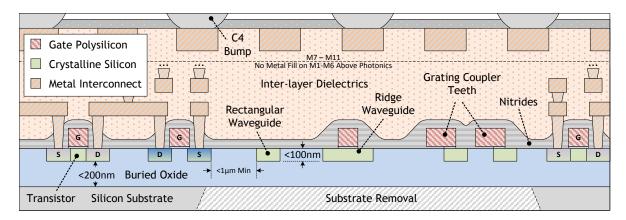

|      | scale)                                                                                                                                                   | 24 |

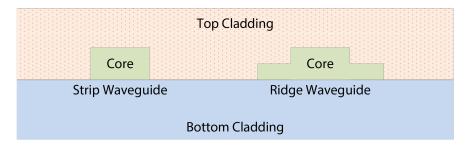

| 2.11 | Simplified diagrams of two major waveguide geometries in silicon-photonics (strip                                                                        |    |

|      | and ridge waveguides)                                                                                                                                    | 25 |

| 2.12 | Scanning electron micrographs (SEM) of a strip waveguide in the zero-change                                                                              |    |

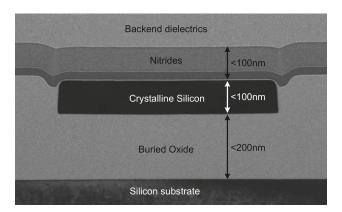

|      | 45 nm SOI platform [6]                                                                                                                                   | 25 |

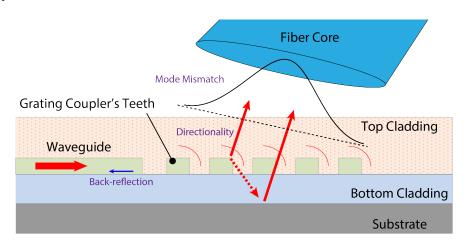

|      | Simple diagrams of a diffraction grating coupler indicating loss mechanisms                                                                              | 26 |

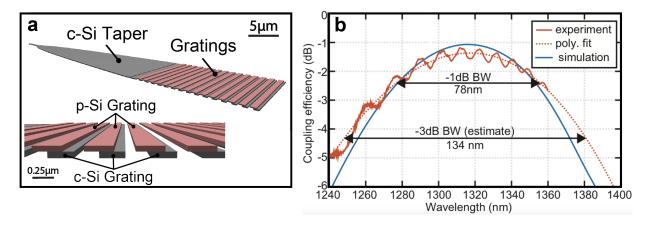

| 2.14 | (a) 3D layout of a unidirectional grating coupler, (b) Optical transmission at 10.5                                                                      |    |

|      | degree vertical angle [7]                                                                                                                                | 27 |

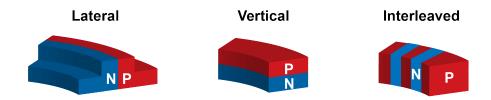

| 2.15 | Major $p$ - $n$ junction configurations in depletion-mode modulators                                                                                     | 28 |

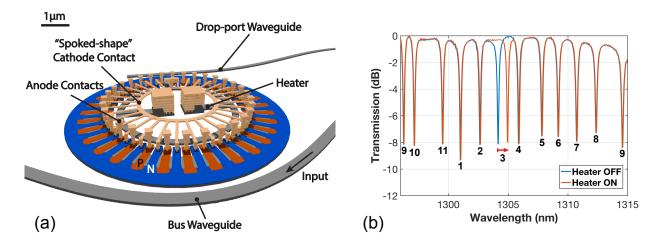

| 2.16       | (a) 3D layout of a spoked-ring modulator, (b) Optical transmission of a WDM transmitter row with 11 channels (numbers indicate channel ordering) over 3.2 THz FSR. Channel 3's heater is turned on by 20% strength to show the individual resonance tuning functionality [7]                                                           | 29         |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

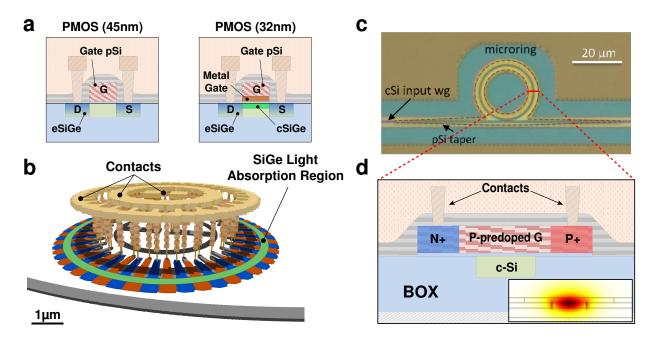

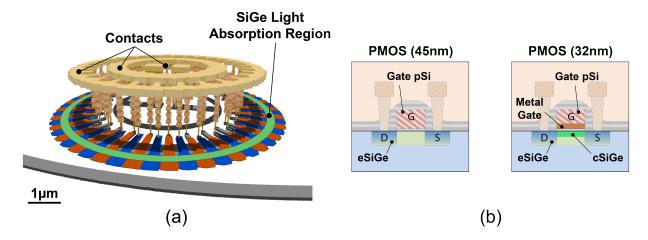

| 2.17       | Photodetectors in zero-change platforms: (a) PMOS cross-sections in 45 nm and 32 nm processes and their features used for O-band light detection, (b) 3D layout of a resonant SiGe PD in 32 nm, (c) and (d) Micrograph and cross-section of the defect-based resonant PD for L-band [7].                                               | 30         |

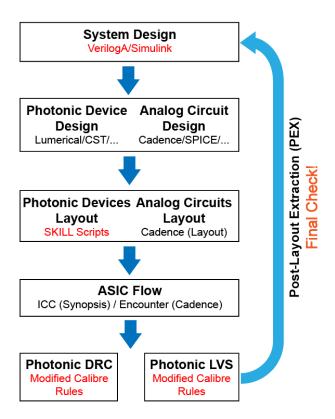

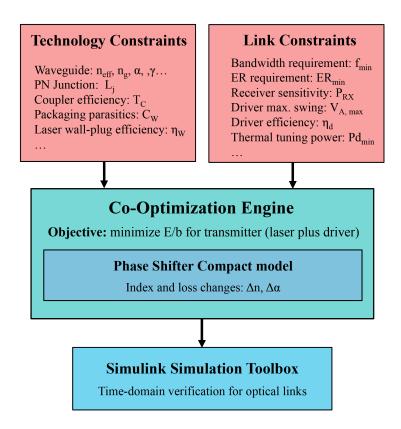

|            | Photonic SoC design flow.  The flowchart of the Simulink co-optimization framework for silicon-photonic transmitters [8]                                                                                                                                                                                                               | 32         |

|            | Estimated energy breakdown for today's commercial silicon-photonic transceivers. Optical power flow in an optical link                                                                                                                                                                                                                 | 35<br>37   |

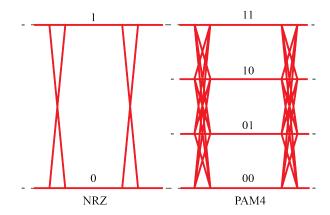

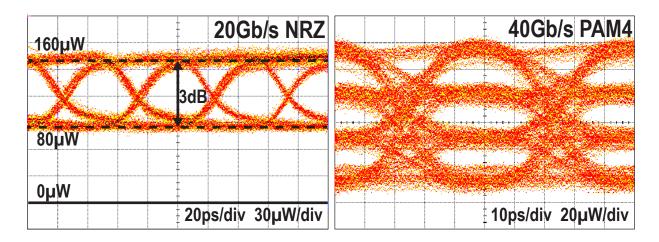

| 3.1        | PAM-4 versus NRZ modulation eye-diagrams.                                                                                                                                                                                                                                                                                              | 41         |

| 3.2        | A ring-resonator based optical link.                                                                                                                                                                                                                                                                                                   | 42         |

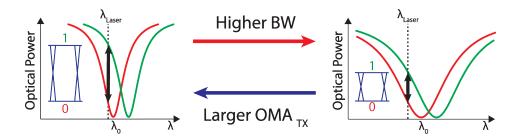

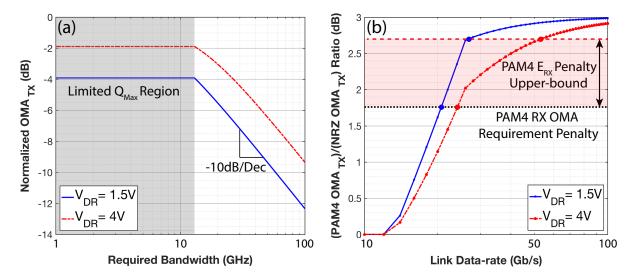

| 3.3<br>3.4 | Trade-off between $OMA_{TX,outer}$ and ring resonator's available optical bandwidth.<br>(a) Normalized achievable $OMA_{TX,outer}$ of a ring-modulators versus the required bandwidth and (b) the ratio of PAM-4 $OMA_{TX,outer}$ over NRZ. The energy-efficiency improvement at any data rate is determined by the difference of this | 43         |

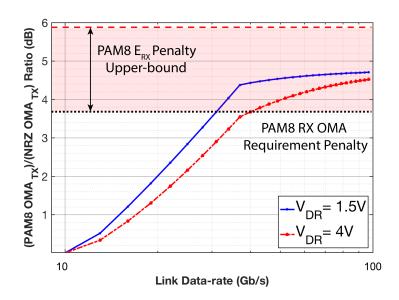

| 3.5        | curve and the PAM-4 receivers' energy penalty (red dashed lines) The ratio of PAM-8 $OMA_{TX,outer}$ over NRZ. The energy-efficiency improvement at any data rate is determined by the difference of this curve and the PAM-8                                                                                                          | 44         |

|            | receivers' energy penalty (red dashed lines)                                                                                                                                                                                                                                                                                           | 46         |

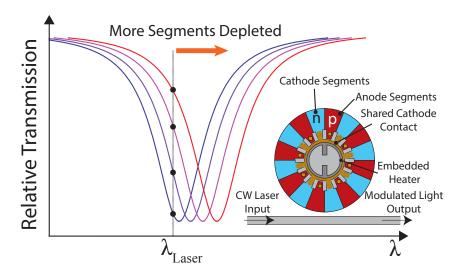

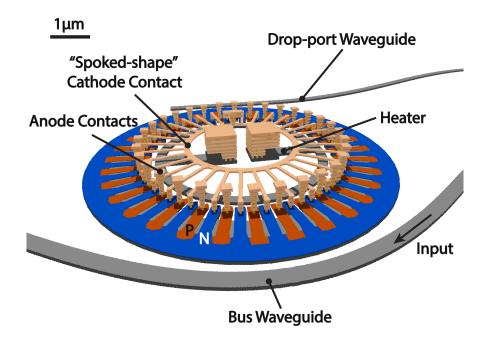

| 3.6        | Segmented ring-resonator optical DAC concept                                                                                                                                                                                                                                                                                           | 47         |

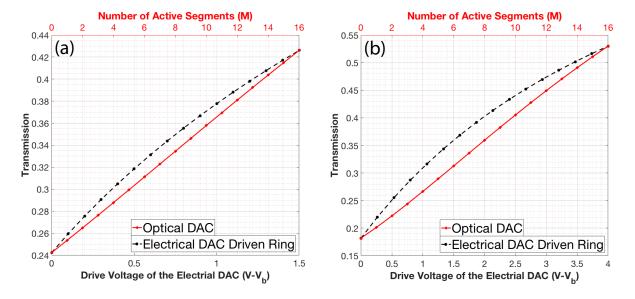

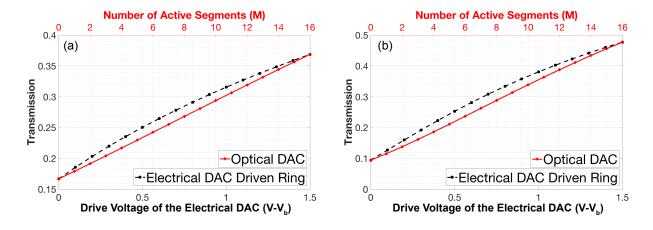

| 3.7        | Linearity comparison of the proposed optical DAC versus an ideal electrical DAC driven microring modulator for driver's voltage swings of 1.5 V (a) and 4 V (b).                                                                                                                                                                       | 48         |

| 3.8        | Linearity comparison of the proposed optical DAC versus an ideal electrical DAC driven microring modulator for Q-factors of 7.5 k (a) and 15 k (b)                                                                                                                                                                                     | 49         |

| 3.9        | 3D layout of a segmented ring-resonator based ODAC in zero-change $45\mathrm{nm}$ SOI                                                                                                                                                                                                                                                  | <b>E</b> 1 |

| 9 10       | platform                                                                                                                                                                                                                                                                                                                               | 51<br>52   |

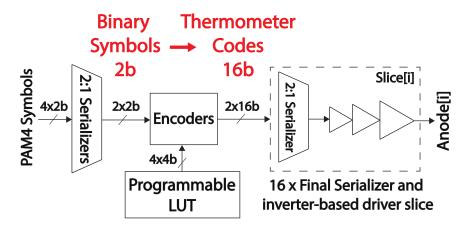

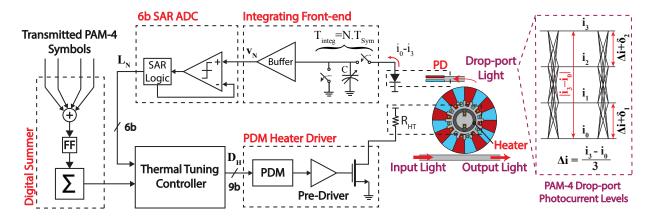

|            | Block-diagram of the transmitter's data-path                                                                                                                                                                                                                                                                                           | 52<br>53   |

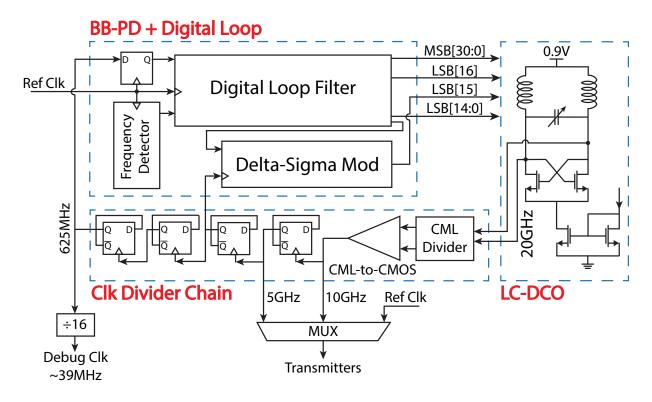

|            | 20 GHz Digital PLL's block-diagram.                                                                                                                                                                                                                                                                                                    | 99         |

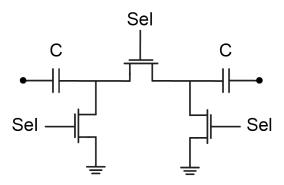

| 5.12       | Circuit diagram of a CDAC unit cell (total of 48 unit cells are connected to the LC-DCO differential output nodes)                                                                                                                                                                                                                     | 54         |

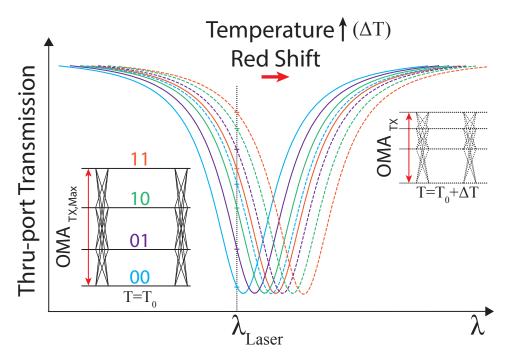

| 3.13       | Thermal sensitivity of the resonance wavelength and its effects on a PAM-4 transmit eye. PAM-4 levels are uncoded while any coding can be applied through the                                                                                                                                                                          |            |

|            | LUT.                                                                                                                                                                                                                                                                                                                                   | 55         |

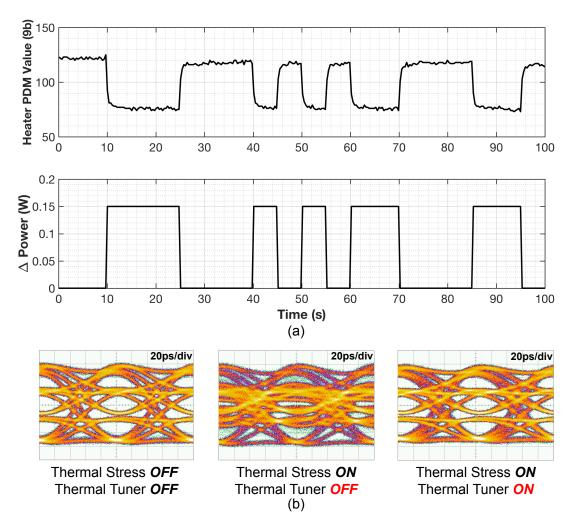

|            | PAM-4 transmitter's thermal tuning feedback loop block-diagram Simulated thermal tuning procedure; the optimum heater value that maximizes                                                                                                                                                                                             | 56         |

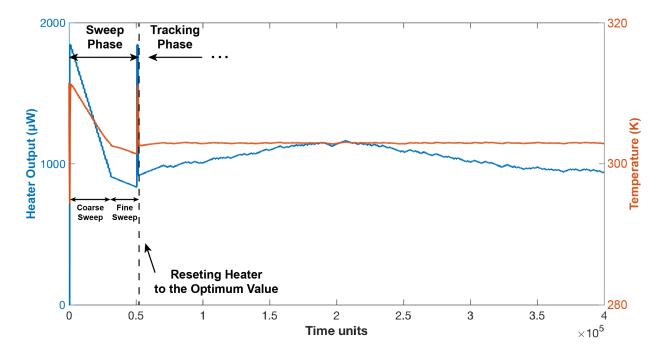

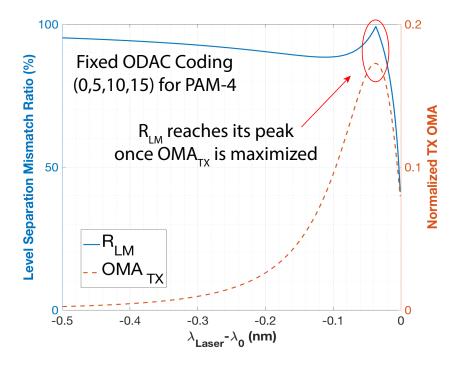

|            | eye-openings is found ( $Sweep\ Phase$ ) and resonance is locked to the corresponding wavelength by tracking $i_3$ level ( $Tracking\ Phase$ )                                                                                                                                                                                         | 59         |

| 3.16       | Simulated heater output power and ring's temperature during the thermal tuning                                                                                                                                                                                                                                                                                                                                                                       |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 17       | process                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0.11       | ring's resonance and laser's wavelength                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3 18       | PAM-4 transmitter's full block-diagram                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.19       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            | Test setup and packaging scheme of the test chip.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.21       | (a) Optical DAC static measurement at low optical input power to avoid thermal drifts. Notice the resonance is shifted down to 1280 nm as cavity's optical power and consequently temperature is lower than the eye-diagram measurement. (b) Normalized optical output for each DAC code compared with an ideal linear DAC (Code 1's output is derived from Codes 0 and 2 transmissions since it is skipped in transmitter's 16b thermometer coding) |

|            | Transient waveforms with all possible ODAC codes in order to measure linearity. Measured transmit eye-diagrams. The highest and lowest optical levels are the same in both cases since the operating point remains the same                                                                                                                                                                                                                          |

| 3 24       | same in both cases since the operating point remains the same                                                                                                                                                                                                                                                                                                                                                                                        |

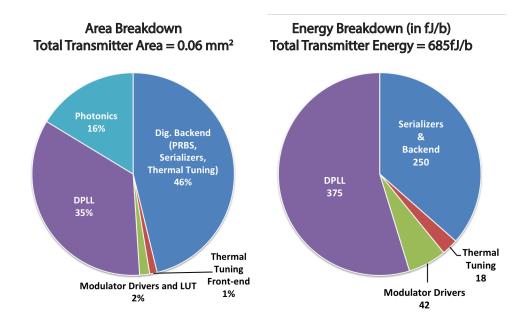

| 3.24       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.25       | tuning and (b) 20 Gb/s PAM-4 transmit eye-diagrams with thermal tuning on and                                                                                                                                                                                                                                                                                                                                                                        |

|            | off                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

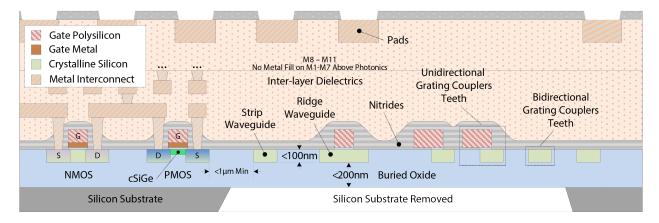

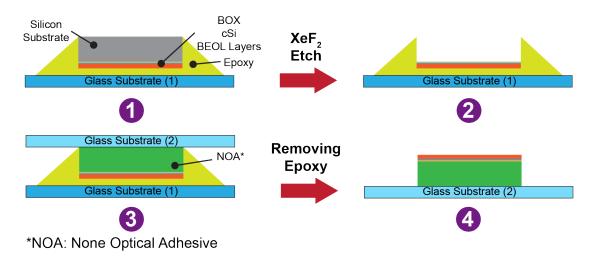

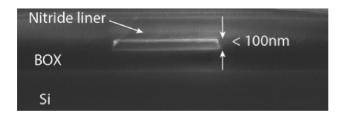

| 4.1<br>4.2 | Cross section of the 32 nm SOI CMOS process                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.3        | Post-processing steps to release silicon substrate in the case of flip-chip packaging on the PCB.                                                                                                                                                                                                                                                                                                                                                    |

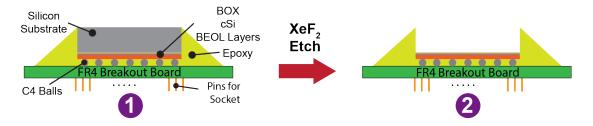

| 4.4        | Micro-graphs of substrate released chips from top and bottom views                                                                                                                                                                                                                                                                                                                                                                                   |

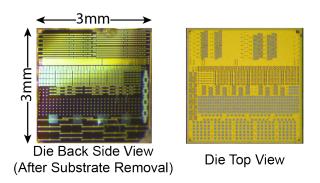

| 4.5        | SEM of a strip waveguide before substrate release step                                                                                                                                                                                                                                                                                                                                                                                               |

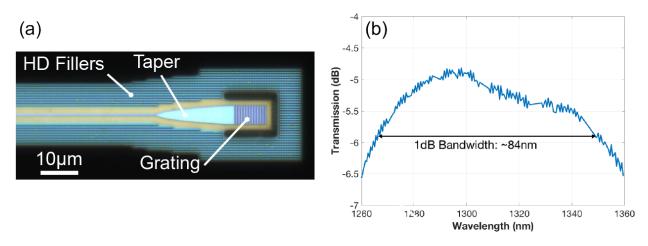

| 4.6        | Diffraction grating couplers in 32 nm zero-change platform. (a) 3D layout, (b) Optical transmission with fibers coupled from the bottom side of the die at 12.5                                                                                                                                                                                                                                                                                      |

| 1 7        | degree coupling angle                                                                                                                                                                                                                                                                                                                                                                                                                                |

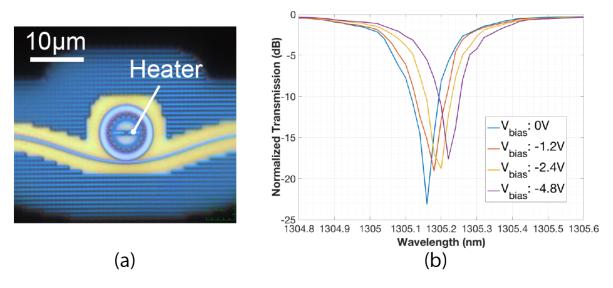

| 4.7        |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.0        | lator for different biases in the depletion mode                                                                                                                                                                                                                                                                                                                                                                                                     |

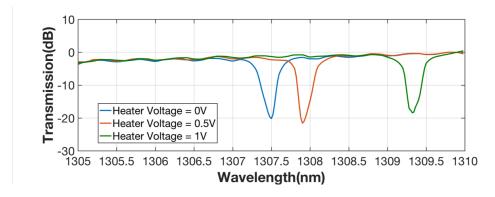

| 4.8        | An example of a heater shifting the microring's resonance wavelength for various                                                                                                                                                                                                                                                                                                                                                                     |

| 4.0        | heater strengths                                                                                                                                                                                                                                                                                                                                                                                                                                     |

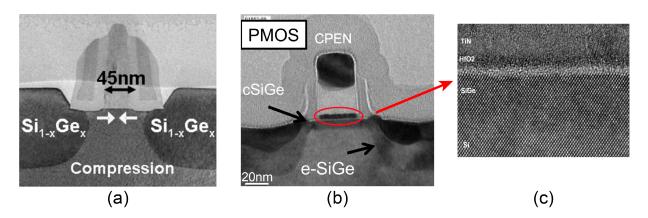

| 4.9        | (a) SEM of a PMOS in 45 nm SOI process highlighting embedded SiGe (eSiGe) available as a source/drain material [9], (b) SEM of a PMOS in 32 nm SOI process                                                                                                                                                                                                                                                                                           |

|            | showing additional channel SiGe (cSiGe) material available as a channel of this                                                                                                                                                                                                                                                                                                                                                                      |

| 1 10       | device [10], (c) PMOS device's channel SEM                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.10       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 111        | 32 nm processes indicating available SiGe layers for photodetection                                                                                                                                                                                                                                                                                                                                                                                  |

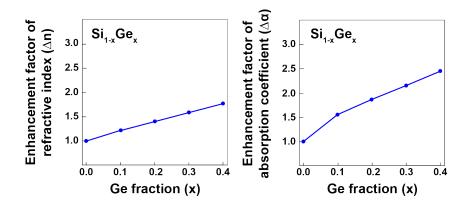

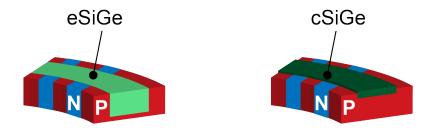

| 4.11       | SiGe optical characteristics dependency on the concentration of Ge fraction                                                                                                                                                                                                                                                                                                                                                                          |

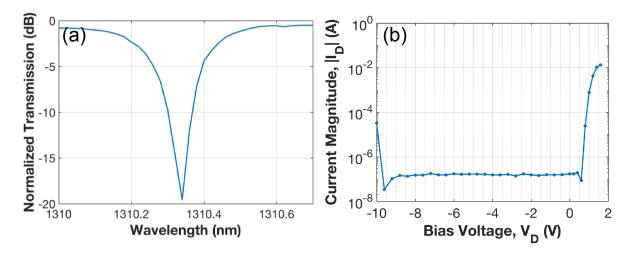

| 4.12       | Cross-section of eSiGe- and cSiGe-based resonant PDs in the zero-change 32 nm platform.                                                                         | 80  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

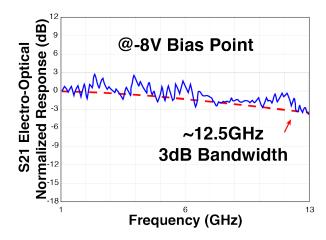

| 4.13       | cSiGe-based resonant PD measured characteristics: (a) optical transmission, (b)                                                                                 | 00  |

|            | I-V curve.                                                                                                                                                      | 80  |

| 4.14       | cSiGe-based resonant PD's electro-optical frequency response                                                                                                    | 81  |

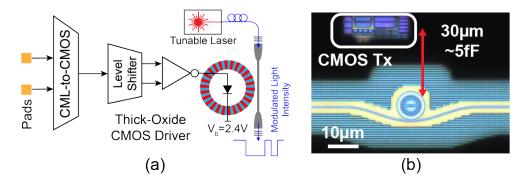

|            | (a) Optical transmitter's block-diagram and (b) micro-graph                                                                                                     | 81  |

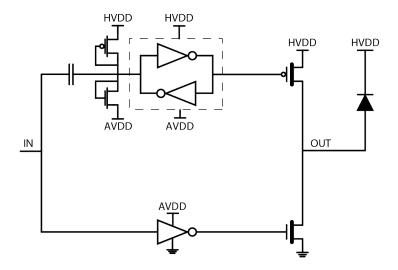

|            | High-swing modulator driver circuit.                                                                                                                            | 82  |

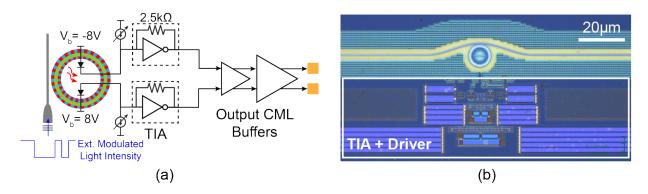

| 4.17       | (a) Optical receiver's block-diagram and (b) micro-graph                                                                                                        | 83  |

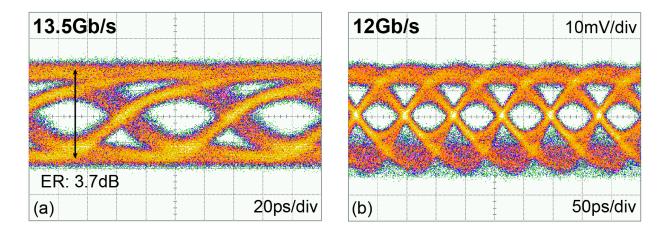

| 4.18       | (a) Transmitter's eye-diagram captured via commercial photo-detector and elec-                                                                                  |     |

|            | trical scope, (b) Receiver's eye-diagram tested by externally modulated input                                                                                   |     |

|            | light.                                                                                                                                                          | 84  |

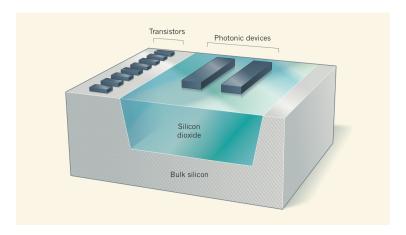

| 5.1        | Our technique for integrating electronic and photonic devices on a single silicon                                                                               |     |

|            | microchip by adding isolated patches (islands) of the insulator material silicon                                                                                |     |

|            | dioxide to a bulk silicon substrate [11]                                                                                                                        | 86  |

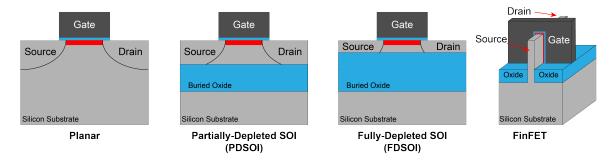

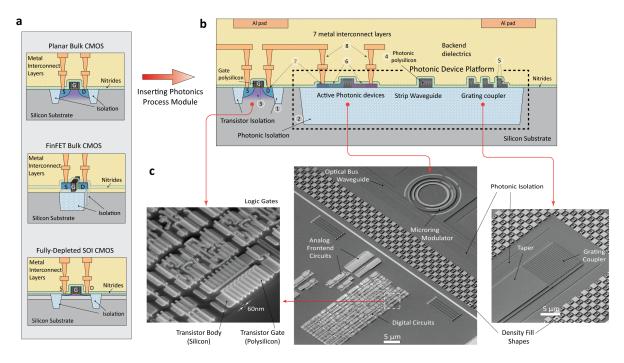

| 5.2        | Photonic integration with nano-scale transistors. (a) Illustration of three major                                                                               |     |

|            | deeply-scaled CMOS processes: planar bulk CMOS, FinFET bulk CMOS, and                                                                                           |     |

|            | fully-depleted SOI CMOS, (b) Integration of photonics process module into planar                                                                                |     |

|            | bulk CMOS, (c) SEM of different photonic and electronic blocks in our monolithic                                                                                | 0.0 |

| <b>r</b> 0 | platform.                                                                                                                                                       | 88  |

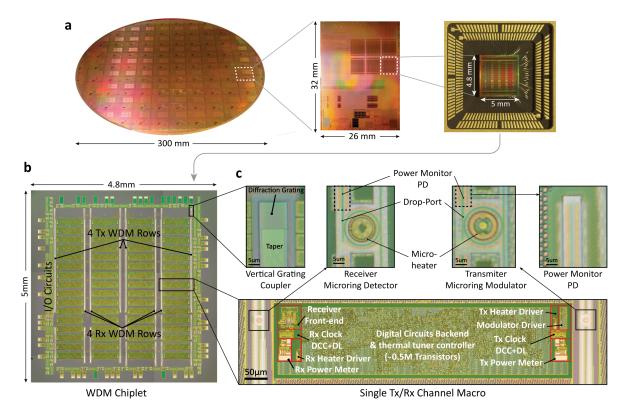

| 5.3        | Monolithic electronic-photonic platform in 65 nm bulk CMOS. (a) Photograph of                                                                                   |     |

|            | a fully fabricated 300 mm wafer with monolithic electronics and photonics, and close-ups of a reticle on this wafer, and a packaged WDM chiplet, (b) Micrograph |     |

|            | of a WDM chiplet, (c) Close-up of a single transceiver macro and its photonic                                                                                   |     |

|            | and electronic circuit components                                                                                                                               | 90  |

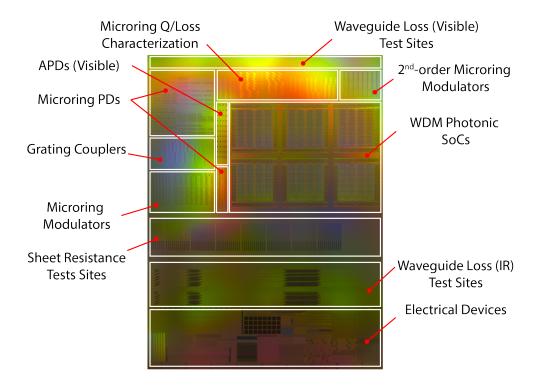

| 5.4        | Photo of a reticle showing various device/system test structures                                                                                                | 92  |

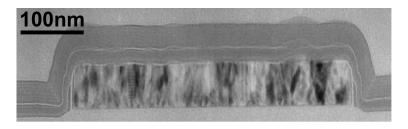

| 5.5        | Cross-sectional TEM of a gate polysilicon waveguide integrated in a 28 nm bulk-                                                                                 | 32  |

| 0.0        | CMOS process. The core thickness is approximately 73 nm with the surface                                                                                        |     |

|            | roughness of 5 nm RMS with a 100 nm correlation length [12]                                                                                                     | 94  |

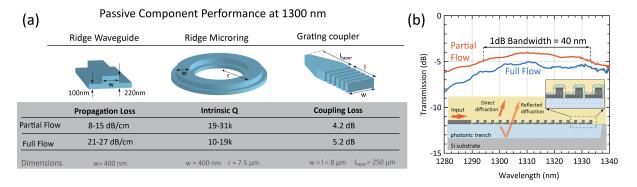

| 5.6        | Photonics Platform Performance. (a) Passive components specifications at 1300 nm                                                                                |     |

|            | for partial- and full-flow wafers, (b) Transmission spectrum and the longitudinal                                                                               |     |

|            | cross-section of grating couplers                                                                                                                               | 97  |

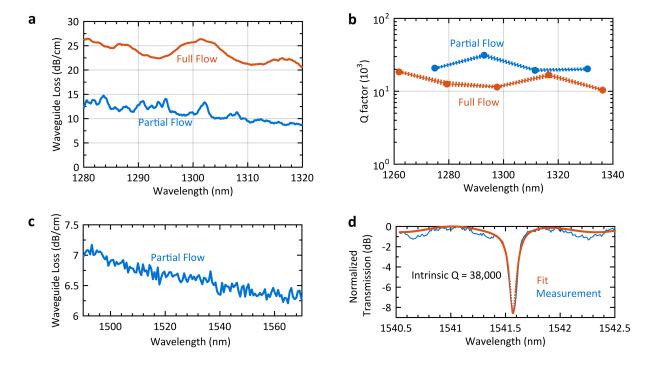

| 5.7        | Passive photonic performance at 1300 nm and 1550 nm. (a) Waveguide prop-                                                                                        |     |

|            | agation loss at 1300 nm. Waveguide loss drops with wavelength because of a                                                                                      |     |

|            | combination of lower absorption and scattering by polysilicon, (b) Q-factor of a                                                                                |     |

|            | 15 μm diameter microring resonator, (c) Waveguide propagation loss at 1550 nm,                                                                                  |     |

|            | (d) One resonance of a 17 µm diameter microring near 1540 nm with a Q-factor                                                                                    |     |

|            | of 38,000                                                                                                                                                       | 97  |

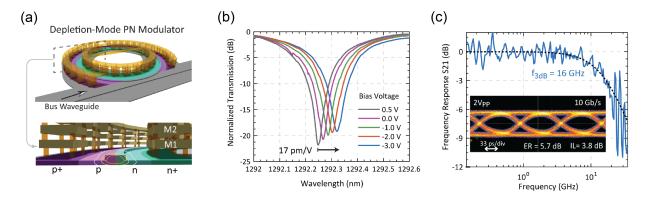

| 5.8        | Photonics Platform Performance. (a) Microring modulator 3D layout, (b) Trans-                                                                                   |     |

|            | mission spectrum of a modulator resonance with loaded Q-factor of 5,000, (c)                                                                                    |     |

|            | Modulator electro-optic frequency response (S21) and the eye-diagram obtained                                                                                   |     |

|            | with 2 Vpp drive voltage                                                                                                                                        | 100 |

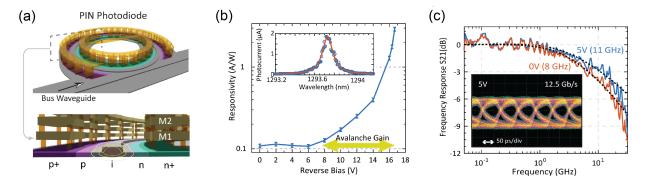

| 5.9  | Photonics Platform Performance. (a) Microring photodiode 3D layout, (b) Re-                           |     |

|------|-------------------------------------------------------------------------------------------------------|-----|

|      | sponsivity vs. reverse bias voltage. Avalanche gain is observed at biases above                       |     |

|      | 8 V, (c) Photodiode frequency response (S21) under 0 V and 5 V reverse bias with                      |     |

|      | 3 dB bandwidths of 8 GHz and 11 GHz, respectively. Inset shows the eye diagram                        |     |

|      | obtained under 5 V bias                                                                               | 100 |

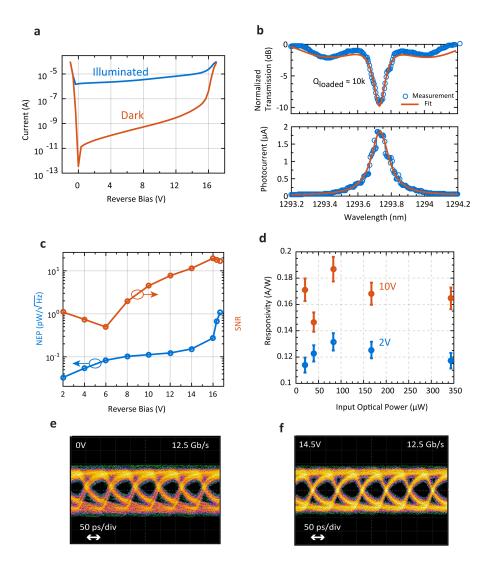

| 5.10 | v · · · · · · · · · · · · · · · · · · ·                                                               |     |

|      | diode under dark and illumination for input optical power of $20\mu\mathrm{W}$ . Dynamic              |     |

|      | range is $\sim 60 \text{dB}$ and $\sim 10 \text{dB}$ at 0 V and 16 V, respectively. (b) One microring |     |

|      | photo-detector resonance and the corresponding photo-current as the wavelength                        |     |

|      | is swept across the resonance. (c) NEP (blue curve) of the photo-diode esti-                          |     |

|      | mated based on the dark-current shot noise, which dominates the detector noise.                       |     |

|      | Avalanche gain is 13 at 16 V bias, with an NEP of 0.27 pW/ $\sqrt{\rm Hz}$ . Simulated SNR            |     |

|      | (red curve) at the output of the optical receiver, assuming 1 $\mu$ W optical signal,                 |     |

|      | and a receiver circuit input-referred noise spectral density of 1 pA/ $\sqrt{\rm Hz}$ . (d) The       |     |

|      | responsivity of the photo-diode vs. input optical power, showing minimal power                        |     |

|      | dependency. (e) and (f) Eye-diagrams at 12.5 Gb/s at 0 V and 14.5 V reverse bias.                     |     |

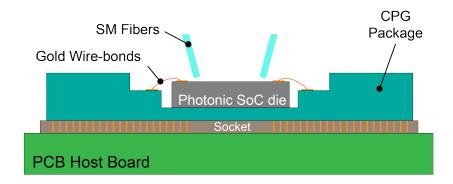

|      | Cross-section of a WDM photonic SoC packaging                                                         | 102 |

| 5.12 | WDM photonic SoC top-level (CMOS clock distribution networks for transmit                             |     |

|      | and receive clocks are shown in red)                                                                  | 103 |

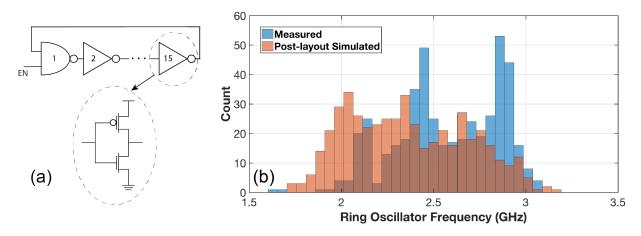

| 5.13 |                                                                                                       |     |

|      | performance and variation ispection, (b) Histogram comparison of measured fre-                        |     |

|      | quencies with Monte-carlo simulation results from the original PDK of 65 nm                           | 405 |

| - 11 | CMOS process.                                                                                         | 105 |

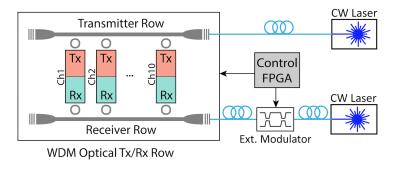

| 5.14 | Electro-optical test setup of WDM transceiver chips and block diagram of one                          | 100 |

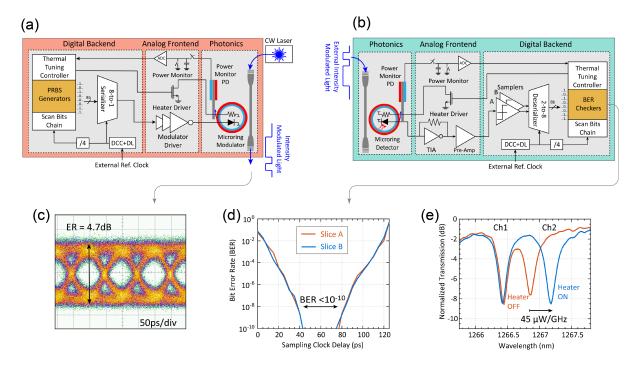

| F 1F | WDM transmit-receive row                                                                              | 106 |

| 5.15 | , , ,                                                                                                 |     |

|      | (c) 10 Gb/s transmit eye-diagram using the on-chip PRBS generator, (d) 7 Gb/s                         |     |

|      | receiver bathtub curve, (e) Thermal tuning of one WDM channel using the inte-                         | 100 |

| F 10 | grated micro-heater.                                                                                  | 106 |

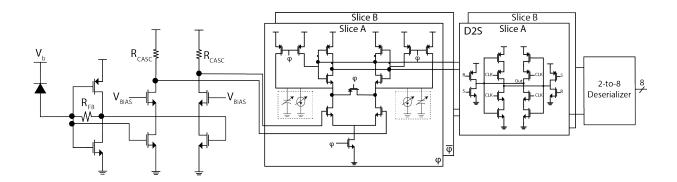

|      | Block-diagram of the receiver's analog front-end                                                      | 107 |

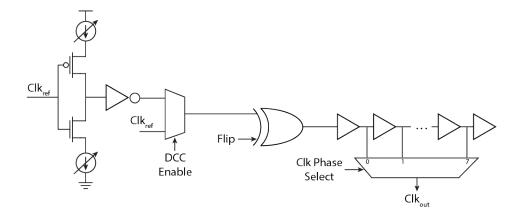

| 5.17 | Block-diagram of the duty-cycle corrector (DCC) and delay line (DL)                                   | 108 |

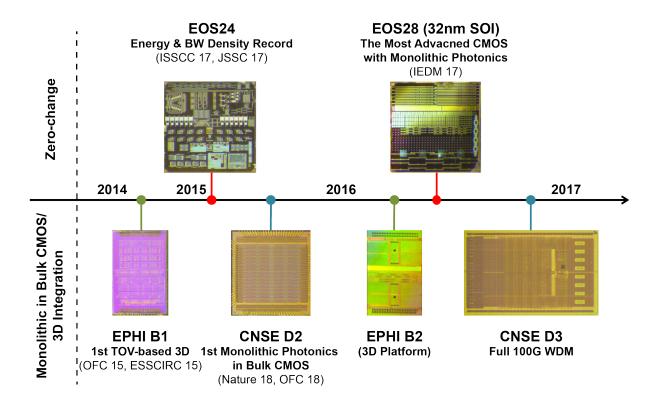

| 6.1  | Summary and time-line of all integrated systems described in this thesis                              | 112 |

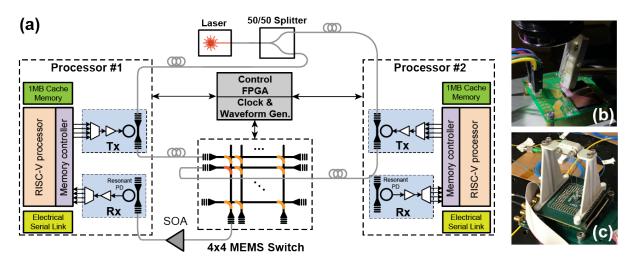

| 6.2  | (a) Block-diagram of the microsecond optical switching network demonstration,                         |     |

|      | (b) Silicon photonics MEMS switch chip, (c) Electro-optically packaged processor                      |     |

|      | SoC [13]                                                                                              | 113 |

# List of Tables

|     | Summary and comparison of non-monolithic silicon photonic platforms Summary and comparison of monolithic silicon photonic platforms |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Summary and comparison of the ODAC-based PAM-4 transmitter with prior high-speed optical transmitters                               | 67 |

| 4.1 | Photonic devices in zero-change platforms performance summary                                                                       | 84 |

#### Acknowledgments

Looking back on the last 5 years of my life in Berkeley, I cannot imagine having a better time and experience, and I owe this to my great advisor, collaborators, colleagues, friends, and family.

First and foremost, I would like to thank my advisor, Professor Vladimir Stojanović. He taught me countless invaluable lessons in research and academia. His guidance, passion in research, versatile expertise in different areas, and unique perspective at problem solving fueled my achievements and inspired my future career directions. His level of optimism always amazed me, and proved to me that nothing is impossible! Vladimir was always more than just an academic advisor to me, more like a true role model in life and I want to thank him for always having faith in me and letting me lead many projects in his group.

Most of the work during my Ph.D. was performed in collaboration with other academic and industrial research groups. I would like to thank Professor Rajeev Ram (MIT), Professor Milos Popović (Boston University), and Professor Ming C. Wu (UC Berkeley) for their technical guidance, leadership, and support. During these team efforts, I really enjoyed learning and working alongside many talented post-docs and students. In particular, Chen Sun mentored me when I just joined Vladimir's group and passed on many essential skills and knowledge, from design to hands-on experiments in the lab. On the photonics side, I had the privilege of working with Amir Atabaki, Fabio Pavanello, and Mark Wade, for whom I am deeply thankful for their mentorship and guidance. I would also like to thank Christopher Baiocco from College of Nanoscience and Engineering (CNSE) for providing technical knowledge and fabrication support for many of the projects I was involved in.

I also had the pleasure of sharing this memorable journey with the Integrated Systems Group's students. Special thanks to Krishna Settaluri, Sen Lin, Nandish Mehta, Pavan Bhargava, Taehwan Kim, Sidney Buchbinder, Panagiotis Zarkos, and Christos Adamopoulos for providing everlasting friendships and proving me either right or wrong through our interesting discussions.

The work in this thesis and many other projects I worked on during my Ph.D. would not be possible without the assistance of the amazing administrators and top-notch technical staff at Berkeley Wireless Research Center (BWRC). Fred Burghardt, Brian Richards, Candy Corpus, Amber Sanchez, and many others did such a fantastic job supporting me and other students at BWRC by providing the best imaginable work environment and facilities. I am extremely grateful to be a member of BWRC and enjoy their support.

Special thanks to all my friends for supporting me and being there for me during one of the most stressful and enjoyable moments of my life. In particular, thank you to Ahmad Zareei, Sina Akhbari, Pouria Kourehpaz, Zhaleh Amini, Salar Fattahi, and Ali Moin, with all of whom I was blessed to have a chance of sharing this unforgettable and wonderful time.

Finally, I would like to thank my parents and sisters for their unwavering support and endless encouragement through my whole life. For many years, they patiently tolerated thousands of miles between us created by unfair visa laws. I owe a special thanks to my

sister, Somayeh, who was a great inspiration in my life and a main reason for me to continue my graduate studies.

**Support.** The work in this thesis is funded in part by DARPA, NSF, and BWRC. I would also like to thank the CNSE, Trusted Foundries, MOSIS and the IBM/Global Foudries staff involved in handling the design submissions.

# Chapter 1

## Introduction

Today's conventional cloud computing and mobile platforms have been challenged by the advent of Machine Learning (ML) and Internet of Things (IoT). The performance and diversity requirements of these applications demand hyper-scale data centers and Exascale high-performance computing (HPC). Powerful HPC was always the major drive force behind solving complex and large models leading to great scientific discoveries, solving environmental problems, and inventions in life sciences. Hyper-scale data centers also played important roles in cloud-computing in many applications and providing global connectivity. Additionally, hyper-scale data centers help us alleviate the energy consumption issue of data centers as large-scale data centers normally operate with significantly higher energy-efficiency [14]. However, a major hurdle in scaling up data centers and enabling next generations of HPC is the energy, cost, and areal bandwidth density of optical transceivers.

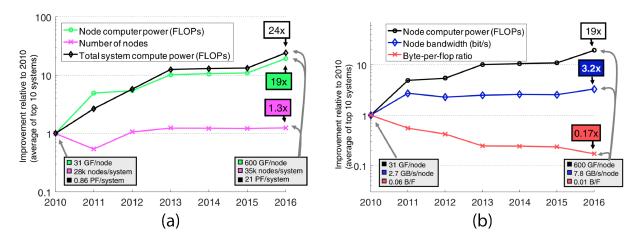

Figure 1.1a presents the trend of average top 10 supercomputers normalized to year 2010 [1]. These curves show that the improvement of compute power for these last years was almost solely owing to the boost in the single node compute power caused by massive parallelization and development of more advanced CMOS nodes. On the other hand, the network size has not been proportionally increased. As we are approaching the end of Moore's law, energy/area enhancements of new CMOS nodes are plateauing and we cannot rely on a single-node compute power enhancement for long. Furthermore, this significantly slower trend of the available bandwidth per node relative to the evolution of compute power per node could not provide the adequate memory resources and data exchange per FLOP (floating point operation). Consequently, the byte/FLOP ratio has been declining by almost a factor of  $6\times$ , while the FLOPs/node metric, which has progressed by nearly  $20\times$  (Fig. 1.1b). Smaller byte/FLOP ratios negatively impacted the parallel efficiency and/or harden the burden on programmers.

One of major reasons for this stagnation of the network size and performance is the energy-efficiency and cost of optical transceivers. Today's silicon photonic optical transceivers are operating at around  $30\,\mathrm{pJ/b}$  energy consumption with the cost of \$5/Gbps. These numbers are prohibiting us from building the next generations of data centers and HPC. For instance in the case of HPC for reaching to the next milestone of Exascale node ( $10^{18}$  FLOPS)

Figure 1.1: (a) Evolution of the average top 10 supercomputers normalized to year 2010 (top500–June rankings), (b) Evolution of the top 10 systems average node computer power, node bandwidth, and resulting byte/flop aspect ratio [1].

by 2020, we need to provide about 40 Pb/s bisection network bandwidth. Supporting this bandwidth using the existing silicon photonics demands around 6.8 MW electrical power [1] with the cost of \$200 M. Considering the fact that the total projected energy and cost budget for the whole systems is 25 MW and \$250 M, respectively, we have to find an alternative solution to drastically improve the energy and cost of optical modules. Thus, building the next generations of supercomputer and hyper-scale data centers depends on significant improvement in the energy-efficiency, bandwidth density, and cost of optical transceivers for inter- and intra-rack communication at high-data rates.

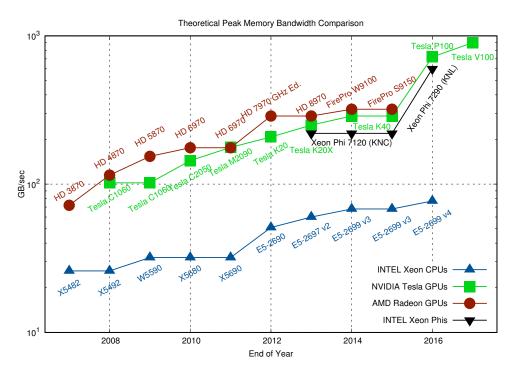

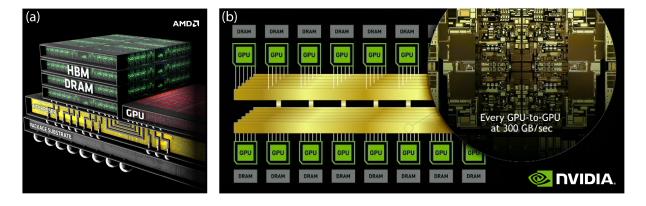

Moreover, the advent of computationally intensive applications such as machine learning (ML) demand larger memory sizes and processor-memory bandwidths (Fig. 1.2). These memory bandwidth requirements (on the orders of TB/s) were achieved by heterogeneous packaging of high-bandwidth memories (HBM) with CPU/GPUs on the interposers providing high-density and ultra-short reach electrical interconnects for processor-memory links (Fig. 1.3a). However, enough off-chip interconnect bandwidth should be also supported to provide adequate data for processing. For instance latest Nvidia DGX-2 (Fig. 1.3b) utilizes 16 interconnected GPUs, each demanding 2.4 Tb/s off-chip bandwidth via electrical NVLinks. As these data-rates are also increasing, supporting them via electrical signaling is becoming more and more challenging due to increased channel losses, limited I/O pins and allocated power for off-chip communication on CPU/GPUs. Furthermore, these applications require distributed computation scaling and communication over multiple racks of such boxes, necessitating efficient optical interconnects. These area and energy-efficient optical interconnects should be realized either through co-packaging or direct integration into SoC computing chips.

In order to solve the area, energy, and cost efficiency issues of optical transceivers, we should notice that the electronic-photonic integration platform always sets and limits these

Figure 1.2: Processor-memory bandwidth trend for high-performance CPU/GPUs.

Figure 1.3: (a) Advanced heterogeneous GPU/CPU packaging (AMD GPU), (b) Emerging high-performance computing systems (Nvidia DGX-2 supercomputer).

performance metrics. There are two major approaches to merge electronics and photonics; while hybrid/3D silicon photonics technologies utilize advanced CMOS microelectronics, the density and parasitic capacitances of interconnection in between electronics and photonics impacts the performance and energy-efficiency of the final system. On the other hand, monolithic solutions were all demonstrated in old CMOS nodes (older than 90 nm) leading to poor energy-efficiency and speed.

This thesis describes two monolithic photonics platforms in advanced CMOS processes to solve the above mention trade-off. Starting from the 45 nm, we present how we can implement a full photonic transmitter in this process without any change or modification (zero-change) to the original CMOS process. A ring-resonator based 40 Gb/s PAM-4 optical transmitter has been demonstrated in this platform achieving the energy and bandwidth density world record by using a novel photonic device configuration (an optical digital-to-analog converter (ODAC)) and co-optimizing electronic and photonics. To show the extendability of the zero-change approach to a more complex and advanced CMOS node, we applied our zero-change scheme to a 32 nm silicon-on-insulator (SOI) CMOS node as well. Here, we will elaborate on the new opportunities for improving the photonics performance by exploiting new features of this process. These platforms can be "sweet-spots" for placing photonics monolithically next to one of the fastest CMOS processes demonstrated so far. Achieving ultra high bandwidth densities of around 0.5 Tb/s/mm² makes these photonic transceivers suitable for in-package heterogeneous integration with high-performance system-on-chip (SoC).

Finally, we develop a monolithic electronic-photonic platform in a 300 mm-wafer commercial bulk CMOS process for the first time. This milestone opens up the path for embedding photonics monilithically in sub-32 nm CMOS nodes which are all fabricated in bulk CMOS or thin-body SOI technologies. Consequently, we can implement monolithic electronic-photonic SoCs in the most advanced CMOS nodes of sub-32 nm. As with the 32/45 nm zero-change platforms, we are already in the regime that photonics only takes less than 10% of energy and area, moving to a more advanced CMOS node is the only solution to boost the energy-efficiency and bandwidth density of the optical transceiver further. Additionally, today's high-performance SoCs are mainly fabricated in sub-20 nm nodes due to higher transistor energy-efficiency and densities (>20 MTr/mm²). Thus, our approach can unlock embedding optical transceivers directly in the CPU/GPU chips by enabling photonics in bulk CMOS platforms. In doing so, we can alleviate the issue of limited I/O pins of modern SoCs in addition to achieving energy, area, and cost performance metrics necessary for the future of computing.

### 1.1 Thesis Organization and Contributions

Chapter 2 of this thesis provides an overview of micro-ring resonator based optical links and integrated photonics technologies. We discuss the trade-offs and challenges of electronic-photonic integration platforms and introduce introduce our zero-change 45 nm SOI CMOS monolithic photonics. Finally, summarize the achieved photonic device performances in that technology and discuss the importance of energy-efficiency and bandwidth density in optical transceivers. Parts of this chapter appear in:

• [7] V. Stojanović, R. J. Ram, M. Popović, S. Lin, S. Moazeni, M. Wade, C. Sun, L. Alloatti, A. Atabaki, F. Pavanello, N. Mehta, and P. Bhargava, "Monolithic Silicon-

Photonic Platforms in State-of-the-art CMOS SOI Processes," *Optics Express*, vol. 15, no. 19, pp. 11798–11807, 2018

Chapter 3 describes the opportunities of electronic-photonic co-design and co-optimization. We will introduce an optical digital-to-analog (ODAC) and discuss the implementation methodology and benefits of this new device. Using this element, we will demonstrate a multi-level optical transmitter and address the thermal stability issue of micro-rings for higher-order modulations. Chapter 3 has the following references:

- [15] S. Moazeni, S. Lin, M. Wade, L. Alloatti, R. Ram, M. Popović, and V. Stojanović, "A 40Gb/s PAM-4 Transmitter Based on a Ring-Resonator Optical DAC in 45nm SOI CMOS," (Invited Paper) IEEE Journal of Solid-State Circuits (JSSC), vol. 52, no. 12, pp. 3503–3516, Dec 2017

- [16] S. Moazeni, S. Lin, M. T. Wade, L. Alloatti, R. J. Ram, M. A. Popović, and V. Stojanović, "A 40Gb/s PAM-4 transmitter based on a ring-resonator optical DAC in 45nm SOI CMOS," in 2017 IEEE International Solid-State Circuits Conference (ISSCC), Feb 2017, pp. 486–487

Although CMOS processes seem to be very constrained environments for optical devices, we can always exploit new features of these platforms to open up the new degrees of freedom in device design and improve the performance of our devices. Chapter 4 elaborates on how we extended the zero-change monolithic photonic approach to a more advanced process node of 32 nm and exploited features of this process in our advantage to boost up system's performance. While we recently showed microring modulators in this process [17], here we will demonstrate the full electronic-photonic capabilities and SiGe photodetectors in this platform as well. This chapter has the following reference:

• [18] S. Moazeni, A. Atabaki, D. Cheian, S. Lin, R. J. Ram, and V. Stojanović, "Monolithic Integration of O-band Photonic Transceivers in a "Zero-change" 32nm SOI CMOS," in 2017 IEEE International Electron Devices Meeting (IEDM), 2017

Zero-change monolithic photonics in  $45/32\,\mathrm{nm}$  approach drastically improved the energefficiency and bandwidth density of optical transceivers, however further improvement can be only done by using more advanced CMOS technologies as we are in the regime where less than 10% of area/energy consumed by photonics. However, enabling monolithic photonics in sub-32 nm CMOS nodes is challenging and has not been demonstrated so far. In Chapter 5, we demonstrate a monolithic photonic platform in a 300 mm wafer bulk CMOS process for the first time. Parts of this chapter appear in:

• [19] A. H. Atabaki\*, S. Moazeni\*, F. Pavanello\*, H. Gevorgyan, J. Notaros, L. Alloatti, M. T. Wade, C. Sun, S. A. Kruger, H. Meng, K. Al Qubaisi, I. Wang, B. Zhang, A. Khilo, C. V. Baiocco, M. A. Popović, V. M. Stojanović, and R. J. Ram, "Integrating

photonics with silicon nanoelectronics for the next generation of systems on a chip," *Nature*, vol. 556, no. 7701, pp. 349–354, 2018

- [20] S. Moazeni\*, A. Atabaki\*, F. Pavanello\*, H. Gevorgyan, J. Notaros, L. Alloatti, M. T. Wade, C. Sun, S. A. Kruger, H. Meng, K. A. Qubaisi, I. Wang, B. Zhang, A. Khilo, C. Baiocco, M. A. Popović, R. Ram, and V. Stojanović, "Integration of Polysilicon-based Photonics in a 12-inch Wafer 65nm Bulk CMOS Process," in 2017 Fifth Berkeley Symposium on Energy Efficient Electronic Systems (E3S), 2017

- [21] A. Atabaki\*, S. Moazeni\*, F. Pavanello\*, H. Gevorgyan, J. Notaros, L. Alloatti, M. T. Wade, C. Sun, S. A. Kruger, H. Meng, K. A. Qubaisi, I. Wang, B. Zhang, A. Khilo, C. Baiocco, M. A. Popović, V. Stojanović, and R. Ram, "Monolithic Optical Transceivers in 65 nm Bulk CMOS," Optical Fiber Communications Conference and Exhibition (OFC), 2018

Chapter 6 summarizes the results and outlines the future opportunities and applications of developed electronic-photonic platforms and integrated systems. Parts of this chapter appear in:

• [13] S. Moazeni, J. Henriksson, T. J. Seok, M. T. Wade, C. Sun, M. C. Wu, and V. Stojanović, "Microsecond Optical Switching Network of Processor SoCs with Optical I/O," Optical Fiber Communications Conference and Exhibition (OFC), 2018

$<sup>{}^*\</sup>mathrm{These}$  authors contributed equally.

# Chapter 2

### **Preliminaries**

Silicon photonics is a promising technology to realize low-cost and energy-efficient optical links for emerging short-reach intra-rack and rack-to-rack interconnects in data-center and high-performance computing applications [22]. This technology also enables high-radix network switches, scalable interconnect fabric for future memory systems, and core-to-core cross-bars [23, 24, 25] once it is integrated with the large-scale electronic system-on-chips. The high performance in all of the above mentioned applications requires tightly integrated electronic-photonic circuits. Various integration strategies have been utilized to meet these demands including hybrid [26], heterogeneous via 3D-stacking [4, 27, 28], and monolithic [6, 29, 30, 31] integration. Among these, monolithic integration has the potential for reliable, low-cost, and large-scale integration, while being most promising in terms of energy-efficiency and bandwidth density.

In this chapter, we first give a brief review of various approaches to build an optical link and explain the advantages of micro-ring resonator based optical links over other schemes. Next, we describe basics of modeling micro-ring resonators and optical links. Section 2.2 compares hybrid and monolithic integration platforms and compares the state-of-the-art platforms for electronic-photonic integration. Details of our recently developed monolithic photonic platform in zero-change 45 nm SOI CMOS is presented in Section 2.3. Due to a high-level of integration and complexity of emerging electronic-photonic integrated systems including our photonic SoCs in this thesis, we developed various tools for modeling, simulation, and implementing such integrated systesm. This automated photonic SoC design flow and our toolkits for this aim are explained in Section 2.4. Finally, we discuss the critical role of energy-efficiency and bandwidth density in future optical interconnects in Section 2.5.

### 2.1 Optical Interconnects

Light-based data transfer and communication have been firstly deployed about 30 years ago in transatlantic links connecting Europe and America. The low loss of fiber optics  $(0.2 \, \mathrm{dB/km} \ \mathrm{at} \ 1550 \, \mathrm{nm} \ \mathrm{wavelength})$  compared with copper wires was the main attraction for

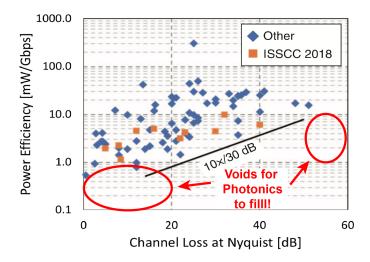

Figure 2.1: Electrical transceivers power efficiency vs. copper channel loss (from ISSCC Trends 2018).

optical links. As the demand for higher-data rates grew, the copper channel losses (which are frequency dependent) drastically increased even at short distances and this caused considerable energy penalties in electrical transceivers. As an example, a 5 m copper cable with 50 dB loss has been deployed for 28 Gb/s data communication and the transceiver energy-efficiency of 15 pJ/b [32]. Just to compare with optical links, with almost the same energy-efficiency and data-rate, we can communicate data over more than 2 km. Furthermore, more advanced CMOS nodes could not alleviate this issue as the limit is imposed by the channel loss mechanisms. Today, even on-board electrical signaling for distances of 12-inch traces is facing serious challenges as demand for data-rates increases above 25 Gb/s typically consuming around 10 pJ/b. Optical interconnects achieving high energy-efficiency and bandwidth density can break the electrical signaling barriers and empower future computing and communication systems. The target opportunities for optical links in regard to the electrical channel loss is shown in Fig. 2.1. Designing energy-efficient photonic transceivers with high-bandwidth density can revolutionize the interconnection paradigms in applications where copper wires cannot reach. Additionally, achieving ultra-high energy efficiencies of sub-1 pJ/b for shortreach links such as on-board signaling can also brings the new opportunities for optical links as well.

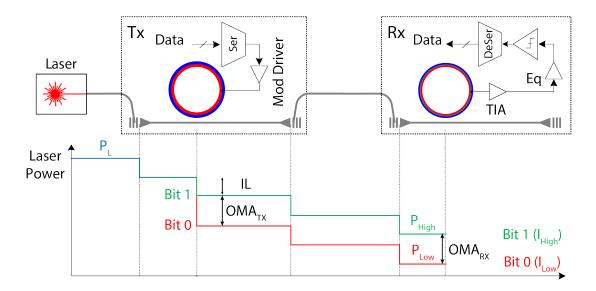

Overall, we can categorize optical links into two main types: (1) Directly Modulated Lasers (DML), or (2) Externally Modulated Laser (EML). The receiver in both methods have the same architecture where a photodiode converts optical intensity (or phase in coherent links) into electrical photocurrents. Afterwards, receiver restores the electrical currents into the digital domain via thresholding electrical circuitry. On the transmitter side, the laser diode is directly modulated by applying a modulated electrical signal in DML links. On the other hand, the laser acts as an optical continuous wavelength (CW) source and transmitter

imprints digital data on the light stream via an optical modulator in EML approach.

DML links require laser sources with high relaxation frequencies. However implementing such laser is very challenging and they still underlie frequency chirping. Despite the demonstrations of distributed feedback lasers (DFB) operating at 56 Gb/s data-rates [33], DML optical links have very limited usage due to various issues. One of the major issues is that lasers cannot be monolithically integrated with CMOS driver chips and that sets an upper energy-efficiency limit due to the parasitic capacitances of interconnection in between laser and electrical drive which shoule be driven at the datar-rate speed. Moreover, lasers' threshold and performance depends greatly on their temperature. As using thermo-electrical cooling (TEC) is extremely power and area inefficient, DML should operate in an uncooled mode. This also prohibit them from being co-packaged with high-performance SoCs running at 80-100 °C normally. Finally, multi-wavelength operations like wavelength division multiplexing (WDM) links require extra optical MuX/DeMux that add extra optical path loss and area overhead.

Today DML optical links are only used for short-reach optical links via vertical-cavity surface-emitting lasers (VCSEL). They are multi-mode sources at 850 nm leading to limited working distances of up to 300 m. Data-rates of up to around 40 Gb/s have been reported with transmitter energy-efficiency of 0.5-1 pJ/b [34]. One of the advantages of VCSELs is their cost efficiency, however due to challenges for achieving higher speeds and lower power consumption, their application and usage may shrink by the advent of future EML optical transceivers. Thus, here we only focus our analysis on the EML-based photonic transceivers.

EML optical interconnects bring many opportunities to improve energy-efficiency and bandwidths of optical transceivers. Separating laser sources from the transmitter module solves all the issues of frequency chirping and relaxes the laser frequency metrics. Also, there's no need to drive the parasitic capacitance of laser's anode/cathodes at high-data rates and we only use DC currents to bias the laser (whether laser is 3D integrated or deployed as a separate module). Due to the temperature dependency of laser sources and also relatively low utilization of optical links in data-centers, separating laser modules from the transceiver module can eventually improve the energy-efficiency and bandwidth density as the transceivers can now be placed very close to high-performance SoCs (like in package or directly embedded on CPU/GPU die). One of the main disadvantages of EML links is the inevitable extra optical loss of coupling laser light into the transmitter chip. This can be alleviated by devising low-loss fiber-to-chip or chip-to-chip optical coupling mechanisms.

The key device in EML links is an optical modulator that can operate based on any of the following principles: (1) Pockels effect, (2) Thermo-optics, (3) Electro-absorption, (4) Carrier-plasma effect. Pockels electro-optic effect, changes or produces birefringence in an optical medium induced by an electric field. However, since materials showing Pockels effect cannot be easily integrated with silicon platforms, using this type of optical modulators for silicon-photonics is still under research [35]. Thermo-optical effects are normally slow (<1 GHz) and cannot be used for high data-rate modulation. Ge-based electro-absorption modulators have been demonstrated at data-rates up to 50 Gb/s with relatively compact footprints. However, 100% Ge is hard to integrate into a CMOS process and the insertion

Figure 2.2: Ring-resonator characteristics and transfer functions.

loss of these devices is still large (5 dB) due to the intrinsic absorption of Ge even at low bias voltages. Thus electro-optical phase shifters based on carrier-plasma effect [36] are the most promising approach for CMOS integration, which can be utilized in the either forms of a Mach-Zehnder interferometer (MZI) or a ring-resonator.

Todays, MZIs are the workhorse modulators in commercial optical transceivers. However, MZIs with high-enough extinction ratio (ER) are inherently millimeter-sized devices, which leads to high energy consumption, high insertion loss (IL), and large footprints. These transmitters have energy-efficiencies around 5 pJ/b, which ironically dominates the total link power budget. MZIs with improved phase shifters [37, 38] also cannot alleviate this issue as their fabrication in advanced monolithic CMOS processes is problematic, requiring hybrid integration which in turn reduces energy-efficiency. Compared to traditional Mach-Zehnder interferometer-based modulator structures, which even the smallest are hundreds of micrometers long, the resonant structure of rings increases the optical length, allowing them to perform modulation in a much smaller form factor. Thus, this thesis focuses on developing high-speed ring-resonator based optical transceivers and addresses their thermal sensitivity and non-linearity issues for multi-level modulations.

### 2.1.1 Micro-ring Resonators

The micro-ring resonator is a ring shaped waveguide that can trap the input light from the bus waveguide coupled into its cavity. In other words, whenever the circumference of the ring is an integer multiple of the input light wavelength, namely  $\lambda_0$ , the coupled light wave from the bus port will interfere constructively in the ring cavity by traveling through the ring circumference and building up the optical power. Consequently, through-port intensity will be reduced significantly. This behavior can be translated as a set of notches in the wavelength domain, shown in Fig. 2.2.

Resonance spacings are called free spectral range (FSR) and rings with smaller radius have larger FSR. Since any multiple wavelengths can satisfy constructive interference condition,

FSR can be quantitatively derived:

$$\lambda_0 = \frac{n_{eff}L}{m}, m = 1, 2, 3, \dots$$

(2.1)

$$FSR = \frac{\lambda^2}{n_g L} \tag{2.2}$$

where L is the circumference of the ring,  $n_{eff}$  is the effective refractive index, and  $n_g$  is the group index, which takes the dispersion of the silicon waveguide into account. In multi-wavelength communication systems such as WDM links, all the channels should fit in one FSR and generally larger FSRs are preferable for modulators in optical communications. We can also define the quality factor (Q-factor) of the resonance as the ratio of the resonance wavelength to its bandwidth:

$$Q = \frac{\lambda_0}{\Delta \lambda} \tag{2.3}$$

where  $\Delta\lambda$  is microring's full-width half-maximum (FWHM) bandwidth, which is indicative of the sharpness of the resonance notch. The ratio of the FSR to  $\Delta\lambda$  is also called finesse of the resonator denoted by  $\mathcal{F}$ . The finesse represents the number of round-trips (within a factor of  $2\pi$ ) made by light in the ring before its energy is reduced to 1/e of its initial value.

In order to derive through-port transfer  $(\alpha)$ , we define the quantities r (the self-coupling of the bus waveguide), t (the cross-coupling between the bus waveguide and the microring waveguide), and  $\tau$  (the total round trip loss (which includes the drop-port coupling loss,  $t_d$ )). Note that  $r^2 + t^2 = 1$  as  $r^2$  and  $t^2$  are the power splitting ratios of the coupler and we suppose the coupling region is lossless. Thus, through-port transfer function can be derived as a function of cross-coupling coefficients between the bus waveguide and ring cavity and also the round trip loss along the ring [39], as follows:

$$\alpha = \frac{I_{through}}{I_{inmut}} = \frac{\tau^2 - 2r\tau\cos\phi + r^2}{1 - 2r\tau\cos\phi + r^2\tau^2}$$

(2.4)