## Better Embedded Design Tools with Automated Reasoning

Ву

#### Rohit Ramesh

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Prabal Dutta, Chair Alice Agogino Bjoern Hartmann Sanjit Seshia

Fall 2023

# Better Embedded Design Tools with Automated Reasoning

Copyright 2023 By Rohit Ramesh

#### Abstract

Better Embedded Design Tools with Automated Reasoning

By

#### Rohit Ramesh

Doctor of Philosophy in Computer Science

University of California, Berkeley

Prabal Dutta, Chair

Contemporary tools for the design of embedded systems, task-specific electronic devices, are built on a paradigm that has not fundamentally changed since the era of pen-and-paper drafting despite new computational tools that enable new, better workflows for designers and engineers. Embedded systems are the glue we use to connect the digital and physical worlds, letting us leverage the connectivity and automation of computers to solve problems from home automation to battlefield awareness. More user friendly tooling would reduce skill requirements, speed up design cycles, and allow more people to solve their problems with embedded systems. Contemporary Electronic Design Automation (EDA) tools are designed around a single step in the design process, board layout, where an electrical schematic is turned into a design for a printed circuit board, the copper and fiberglass base that connects all the other components in a system. However, engineers go through a series of phases before they reach board layout: exploring the problem they are trying to solve, sketching out a high-level system architecture, and refining that into a well-defined electrical circuit. Better EDA tools would fit more naturally into this workflow, existing to support users in earlier phases, presenting them with information as it becomes relevant, and automating routine or repetitive work.

This dissertation describes two such tools, both built by formulating the design process in mathematical terms and using algorithms to reason about our formalisms, all while wrapped in user-friendly interfaces. The first tool, Embedded Design Generation (EDG) is a proof-of-concept system meant to push the limits of automation in the embedded design process. Given a high-level specification for a device it uses satisfiability solvers to synthesize, from whole cloth, a design meeting that spec. The second, Polymorphic Blocks, uses block diagrams to represent designs in arbitrary stages of construction and propagator semantics for error checking, predictive suggestions, and other features.

# Contents

| Contents |              |        |                                    |           |  |  |  |

|----------|--------------|--------|------------------------------------|-----------|--|--|--|

| 1        | Introduction |        |                                    |           |  |  |  |

|          | 1.1          |        | odern Embedded Development Process | 1<br>3    |  |  |  |

|          |              | 1.1.1  | Specification Finding              | 4         |  |  |  |

|          |              | 1.1.2  | System Architecture Development    | 5         |  |  |  |

|          |              | 1.1.3  | Schematic Capture                  | 7         |  |  |  |

|          |              | 1.1.4  | •                                  | 10        |  |  |  |

|          | 1.2          | Evalua |                                    | 11        |  |  |  |

|          | 1.3          |        | -                                  | 12        |  |  |  |

|          | 1.4          | _      |                                    | 13        |  |  |  |

|          | 1.5          |        | ·                                  | 14        |  |  |  |

| 0        | ъ 1          | 11 1   |                                    |           |  |  |  |

| 2        |              |        | o .                                | 15        |  |  |  |

|          | 2.1          |        |                                    | $15_{17}$ |  |  |  |

|          | 2.2          |        |                                    | 17        |  |  |  |

|          |              | 2.2.1  |                                    | 17        |  |  |  |

|          | 0.0          | 2.2.2  | 1                                  | 18        |  |  |  |

|          | 2.3          | 00     |                                    | 19        |  |  |  |

|          | 2.4          |        | V 1                                | 22        |  |  |  |

|          |              | 2.4.1  | , , ,                              | 23        |  |  |  |

|          |              | 2.4.2  |                                    | 23        |  |  |  |

|          |              | 2.4.3  | <u> </u>                           | 25        |  |  |  |

|          |              | 2.4.4  | G/                                 | 26        |  |  |  |

|          | 2.5          |        | · 0                                | 26        |  |  |  |

|          |              | 2.5.1  | 8                                  | 26        |  |  |  |

|          |              | 2.5.2  |                                    | 27        |  |  |  |

|          |              | 2.5.3  | •                                  | 28        |  |  |  |

|          | 2.6          |        |                                    | 29        |  |  |  |

|          |              | 2.6.1  | V                                  | 31        |  |  |  |

|          |              | 2.6.2  | Inferring Missing Design Elements  | 32        |  |  |  |

|          |              | 2.6.3  | Preservation of Function           | 32        |  |  |  |

|   |     | 2.6.4 Performance                                    |

|---|-----|------------------------------------------------------|

|   | 2.7 | Discussion                                           |

|   |     | 2.7.1 Performance and Optimization                   |

|   |     | 2.7.2 Type System Fidelity                           |

|   |     | 2.7.3 Usability                                      |

|   | 2.8 | Conclusion                                           |

| 3 | Pol | ymorphic Blocks 37                                   |

| _ | 3.1 | Introduction                                         |

|   |     | 3.1.1 Statement on Author Contributions              |

|   | 3.2 | Related Work                                         |

|   |     | 3.2.1 Electronics and HCI                            |

|   |     | 3.2.2 PCB Design Tools                               |

|   |     | 3.2.3 Chip Design and Hardware Description Languages |

|   | 3.3 | System Design                                        |

|   |     | 3.3.1 Block Diagram Model                            |

|   |     | 3.3.2 Electronics Model and Libraries                |

|   |     | 3.3.3 Hardware Description Language                  |

|   |     | 3.3.4 Visualization and Refinement Interface         |

|   |     | 3.3.5 Board Generation                               |

|   | 3.4 | System Implementation                                |

|   |     | 3.4.1 Compiler Structure                             |

|   |     | 3.4.2 Block Diagram Layout                           |

|   | 3.5 | Example Applications                                 |

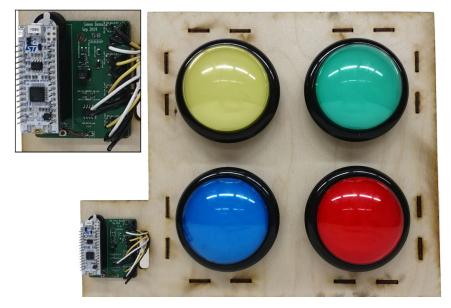

|   |     | 3.5.1 Simon                                          |

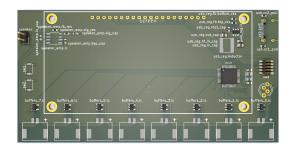

|   |     | 3.5.2 Datalogger                                     |

|   | 3.6 | User Study: Methodology                              |

|   |     | 3.6.1 Participants                                   |

|   |     | 3.6.2 Structure                                      |

|   | 3.7 | User Study: Results                                  |

|   |     | 3.7.1 Project: Power Meter                           |

|   |     | 3.7.2 Project: Thermistor Reader                     |

|   |     | 3.7.3 Project: Multifunction Instrument              |

|   |     | 3.7.4 Advantages                                     |

|   |     | 3.7.5 Limitations                                    |

|   |     | 3.7.6 Part Building                                  |

|   |     | 3.7.7 Graphical Interfaces                           |

|   |     | 3.7.8 Design Time                                    |

|   | 3.8 | Limitations and Future Work                          |

|   |     | 3.8.1 Library-Based Approach                         |

|   |     | 3.8.2 Electronics Model                              |

|   |     | 3.8.3 Users and User Study                           |

|              |                            | iii      |  |  |  |

|--------------|----------------------------|----------|--|--|--|

|              | 3.8.4 Graphical Interfaces | 58<br>58 |  |  |  |

| 4            | 4 Conclusion               |          |  |  |  |

| Bibliography |                            |          |  |  |  |

### Acknowledgments

I would like to start by thanking Prabal Dutta, my advisor for the whole of my nine years as a PhD student. His support and advice has been invaluable. I would not have made it this far without his insight into research topics, engineering decisions, and making my work presentable to an audience.

Professors Sanjit Seshia and Edward A. Lee also have my thanks for taking the time to speak to me about the more formal, mathematical side of my work. Their efforts shaped my approach to modeling messy, real-world problems in a rigorous, efficient way.

Of my fellow students, I would like start by singling out Richard Lin. He has focused on the same problems as me but approached them from a very different, yet highly complementary, direction. His dedication to usability and user testing has meant our joint work is more approachable to a wider audience. Without his influence I would likely be building technically interesting tools that nobody outside of a small circle would be able to use. Instead, I've been able to contribute to a platform that has the potential to help a wide audience.

Lastly, I'd like to thank my fellow members of Lab11. The lab has helped keep me grounded and pulled me out of my shell when I've needed it most. In particular Meghan Clark, Pat Panutto, and Branden Ghena took it upon themselves to mentor and support me whenever I was having a difficult time. I wouldn't have made it here without them all and I am immensely grateful.

This work was supported in part by STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA; the National Science Foundation under grant(s) CPS-1239031; the NSF/Intel Partnership on Cyber-Physical System Security and Privacy under award proposal title "Synergy: End-to-End Security for the Internet of Things: NSF Proposal No. 1505684"; DARPA CRAFT; ExCAPE: Expeditions in Computer Augmented Program Engineering (NSF grant CCF-1139138); NSF CNS 1505773, CNS 1822332, Synergy: Collaborative: CPS-Security: End-to-End Security for the Internet of Things; the CONIX Research Center, one of six centers in JUMP, a Semiconductor Research Corporation (SRC) program sponsored by DARPA; and in part with funds from the Paul and Judy Gray Alumni Presidential Chair in Engineering Excellence.

# Chapter 1

# Introduction

Embedded systems are a critical part of the modern world because they are the interface between digital systems and the physical environment, appearing in a massive array of forms and with many diverse uses. Programmatic observation and control of the real world is now a near-ubiquitous fact of life. Even the simplest modern microwave is an embedded system; it contains electronic components that sense and manipulate the environment, those components are controlled by a processor, and the device as a whole exists to do a small set of tasks. Unlike general purpose systems like computers and smartphones, which are built to run arbitrary applications, embedded systems are built to perform a narrow range of tasks. This focus means that an embedded system for home automation, while still interacting with the environment and containing a processor, will look nothing like a drone or a robot.

Embedded development tools have to handle not just diversity in system design, but the corresponding diversity in approaches to design. What matters to a developer can vary wildly based on their project. Common metrics like system cost and time-to-market exist alongside metrics that appear less frequently, like aesthetic beauty. Developers also choose to prioritize different decisions; where one developer might start by dividing their design into high-level building blocks, another may zoom in on one critical component and expand outwards from there. Even critical elements like testing vary based on factors such as required turn-around time, budget, or availability of simulation tools.

Modern embedded development tools are built around a single, easily-modeled phase in the design process, ignoring the creative core of embedded development. Tools like KiCad [29], Eagle [3], and Altium [1] exist to support the design of printed circuit boards (PCBs), while most of the creative decision making happens as users design circuits. Contemporary embedded tooling provides only bare-bones assistance with parts selection, error checking, design organization, and other aspects of circuit design. This lack of meaningful support means that users require more knowledge and skill to design embedded systems than is otherwise necessary.

Embedded development tools built using techniques from automated reasoning can better serve designers by intelligently presenting useful information, and automating rote work while preserving their freedom in how to approach the design process. We propose a methodology that accomplishes this by modeling system designs mathematically, such that an incomplete or in-progress design simply corresponds to an unfinished model. Automated reasoning, built to analyze general mathematical models, can be incorporated into a backend that sees no difference between designs in any state of completion and produces inferences regardless. Embedded development tools can then manage the correspondence between an easy-to-use, user-facing frontend and the underlying mathematical model. This allows us to present inferences from the backend in the form of auto-completion suggestions, context-aware search, robust error checking, and other desirable features without artificially limiting how users interact with our tools or forcing them into a narrow workflow.

We evaluate our methodology along three core axes: automation, salience and ergonomics. Automation is the degree to which the user has to do unnecessary or repetitive work, with more wasted effort meaning a less automated tool. Salience considers what information is presented to the user and how useful it is. Tools with good salience proactively show the user information as it is needed, without polluting their environment with noise. Ergonomics looks at how well the tool fits a user's workflow and mental models, specifically whether they have to divert from a "natural" process in order to accommodate a tool's idiosyncrasies.

Our methodology can improve on contemporary practice because automated reasoning tools can work with a design flexibly, without introducing artificial constraints that would be reflected onto users. The field of automated reasoning broadly covers algorithms that can perform mathematical reasoning tasks without human intervention. This runs the gamut from tools that evaluate and simplify systems of equations to more complex algorithms that can search for proofs or solve constraint satisfaction problems. Our work relies on the fact that, if a complete design can be expressed as a set of mathematical statements, incomplete designs can be seen as sets missing some of those statements. Automation comes from tools that can look at a set of statements and generate new statements, pushing an incomplete design closer to completion. Certain inferences, like the existence of an error, are produced only when salient because the very fact that you can derive an error is evidence that the error is relevant. Different approaches to the design process present as different ways to assemble a set of statements; ergonomic tools are then a byproduct of how any set is a valid target for automated reasoning. Automated reasoning is a fundamental part of how our methodology produces usable design tools.

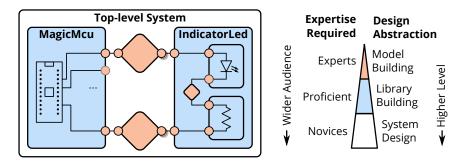

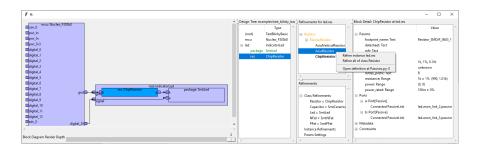

This dissertation covers two tools built with this philosophy. The first, Embedded Design Generation (EDG), is a proof-of-concept tool meant to push the boundaries of automation by translating high-level requirements and a space of possible designs into a constraint satisfaction problem that a satisfiability solver can solve. The second, Polymorphic Blocks (PolyBlocks), builds a design support tool around block diagrams, translating those diagrams into equational relationships that a propagator network can evaluate in order to provide features like auto-complete and robust error checking.

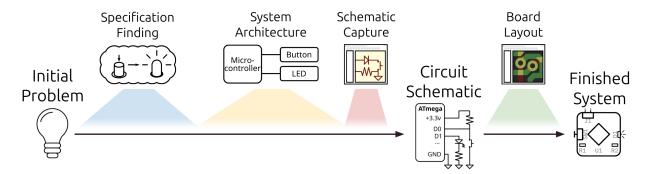

Figure 1.1: The contemporary embedded development process consists of four major steps. Specification Finding explores an initial problem statement, making the project goals more explicit and evaluating possible implementation strategies. System Architecture is the meat of the design process where a high-level sketch of a design is refined into a concrete circuit schematic. Schematic Capture has designers performing data-entry, digitizing the schematic for later use. Finally, Board Layout is when the schematic is turned into a design for a Printed Circuit Board (PCB), suitable for manufacture. In practice there is some flexibility in the process, with backtracking being common and board layout sometimes dropped entirely when no PCB is needed.

# 1.1 The Modern Embedded Development Process

The existing paradigm for circuit design follows the same flow as any other design process, moving from a highly-abstract initial conception of a device through ever more concrete steps until the device is sufficiently well defined that it can be fabricated. The process, as shown in figure fig. 1.1, flows from an initial problem statement or specification, usually rendered in non-formal, human-readable language, that defines what the designer is trying to achieve. This problem statement usually is not sufficiently well defined to serve as a specification for the rest of the work. During specification finding designers gather information and explore possible solutions, producing requirements that define a high-level strategy for future engineering efforts. Commonly this leads to a system architecture design phase where a high-level, abstract sketch of the target system, usually in the form of a block diagram, is refined into a circuit diagram that explicitly defines all the components used and how they are electrically connected. This is where much of the creative and skilled work in the embedded design process lies; engineers draw on information from datasheets, component libraries, and other sources, as well as their own skill and experience, to ensure they produce a functioning design that satisfies their requirements. Schematic capture is where Electronic Design Automation (EDA) tool suites like Eagle and KiCad enter the development process. These initial tools act an entry point, allowing designers to digitize their circuits for future steps in the process. Such suites provide tools to design Printed Circuit Boards (PCBs): fiberglass panels which components can be soldered into, with copper traces connecting those

components as specified by the schematic. PCB designs (also called board layouts) can then be manufactured, providing the physical medium to which components are soldered, creating a finished embedded system.

Our model of the design process is based on Lin et al. [35], where we interviewed 15 participants in a semi-structured manner. Starting with background information, including motivations, designs, and views on the EDA process, we questioned them on their process as they moved from idea to final device. Based on those responses, we then went into depth on each step of that process, examining tools used, pain points, references used, and general suggestions or comments. Interviews averaged 90 minutes with a standard deviation of 29 minutes, and were conducted either in-person at the participant's workplace or through videoconference. Utilizing the principles of contextual inquiry [6], we asked for an example design to ground discussions when possible. A majority of participants were able to do so, but some could not because of confidentiality or lost files; we asked them to either visualize their designs or consider stock schematic and board layout images. Interviews were conducted by one interviewer and audiotaped with the participant's consent. One researcher, experienced with board design and familiar with most of the tools discussed, then conducted an open coding phase over the transcriptions, and further grouped codes into related topics [58]. From these, we looked for themes that both had design implications for EDA tools and either had support among multiple participants or were notable outliers, distilling them into the model in fig. 1.1.

## 1.1.1 Specification Finding

A project's initial problem statement will rarely be well-defined enough for implementation work to begin. Instead designers start by gathering preliminary information in a process we call *Specification Finding*. The goal is to go from a broad idea—for example, wanting to measure crop growth in a farm—to a more concrete set of requirements—say, measuring stalk height and water retention at least once every day. Better defined requirements guide future steps in the development process and shape the implementation of the target device.

Projects go about choosing requirements and specifications in myriad ways, as no one technique or class of techniques, is universally appropriate. Someone designing a cash register may build cardboard mockups and test how comfortable they are to use. Someone else, designing industrial automation systems, might spend time taking measurements in a factory to know what extremes of temperature and vibration their device has to survive. The requirements important to a project vary wildly, leading to a diversity of techniques for discovering them.

No one tool or descriptive format can capture a useful range of high-level specifications while also connecting to lower-level tools that are more aware of the electronic domain. Instead, we find that participants use a wide variety of representations that don't directly connect to lower level tools, like lists, whiteboard drawings, and slide decks. Participants often used multiple representations, spanning multiple abstraction levels, in concert; one project's

specifications included, for instance, checklists in shared documents alongside datasheets for parts that needed to be in the final design.

Importantly, specification finding is not a static process and the requirements themselves change over time. Participants noted that specifications should be treated as living documents that are updated as the design process unearths new complications. Some changes, like those triggered when designers discover a requirement is impractical, can result in backtracking that touches every part of a project. In other situations, participants described realizing that a requirement they chose didn't actually solve their ultimate problem, forcing them to rethink what needed to be in their specification.

Our participants were skeptical of domain specific tools for specification finding because of its fluid nature and how it touches every other step in the design process. Such a tool would have to be able to encode broad requirements for a system, reason about how an implementation affects those requirements, and deal with a constant process of back-and-forth as user observations, the current system's design, and a living specification influence each other. While this might be possible for a carefully chosen subset of requirements, it is not possible for the general case. This becomes obvious when you consider some of the more novel requirements our participants discussed, like aesthetic beauty and ease-of-use. Allowing designers to handle these concerns themselves is better than trying to force specification finding into the more rigid framework a support tool would require.

## 1.1.2 System Architecture Development

System architecture is the meat of the embedded development process; going from a sketch of a system to a finalized circuit requires repeatedly evaluating design alternatives, incorporating external information, ensuring system correctness, and making creative choices. Engineers start this phase with a vague idea of how to implement their device. Most of the details are left undefined and what is known can vary wildly based on the designer and project. System architecture starts a process of gradual refinement where details of implementation are incrementally filled in: splitting a design into separate regions, choosing components, connecting interfaces, and so on. By the end, they will have a complete, unambiguous circuit design, which serves as a bottleneck for the rest of the embedded design process. During system architecture, designers are constrained by their specification, available resources, the results of testing, and a wide variety of other concerns they must balance. After the system architecture step, designers are constrained by their circuit design, with other factors playing comparatively small roles.

Despite the multifaceted balancing act that designers must perform, they represented designs in the same way across projects with system architecture diagrams. Architecture diagrams are, fundamentally, block diagrams. Blocks themselves can range from capturing a single component, such as a resistor or LED, to representing large portions of a design, like the power circuitry or all of the sensors in a system. Links between blocks represent connected interfaces, flows of some resource between the connected blocks, like power through some

wires or data on a bus. As with blocks, links can be precise, capturing single wires in the circuit, or more general, as with an interface for some "data" that has been left unspecified.

Architecture diagrams, and the elements within them, exist on a spectrum from abstract and ambiguous, with critical information missing, to complete and concrete, unambiguous, with all the information needed for future steps. At their most abstract one finds blocks for "power" and links carrying "signals". This is common during the early system architecture phase, where ambiguous parts of a diagram serve as placeholders for later work. Over the course of the design process, architecture diagrams become more concrete. Abstract blocks are replaced with better defined versions, until they represent individual electronic components. The same applies for links, which become individual wires connecting pins. A finished design contains a schematic within it, like the one in fig. 1.2a, that can be extracted for use elsewhere.

For many of our participants, the process of designing a circuit is the process of changing and refining the architecture diagram. Each of the creative choices made by a designer are captured in incremental changes to the diagram. Designing a power architecture is the same as going into the corresponding block and populating it with sub-blocks for battery management, voltage regulation, or anything else needed to handle the parent power block's responsibilities. Choosing a communications bus is the same as annotating a connection for "sensor data" with a specific protocol, possibly even splitting it into the individual wires that protocol uses. Picking parts is the same as changing a block's name from something more abstract, like "microcontroller" or "camera", to the part number for a specific component. Over time, an architecture diagram will slowly change from a gross overview of a design to a fully-specified representation of the final circuit with all the information needed for board layout.

As with specification finding, participants worked with the system architecture using unspecialized tools like whiteboards, graphics software, PowerPoint, or Vizio. Even those participants who used schematic capture tools here mentioned that they did so in a non-functional capacity, as block diagram drawing tools, rather than tools that could assist in any domain specific way.

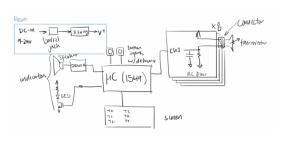

However, unlike specification finding, which requires generic tools because of the diversity of forms a specification can take, participants near-universally represented the system architecture as a block diagram. The example diagrams provided by our study participants tended to be very similar both structurally and representationally. Participants tended to divide designs into similar functional components; blocks for power supplies, processing, sensors, and actuators were extremely common. Likewise, participants chose to capture similar information in their diagrams; the data moving over a bus was usually preserved, while details like the bus' full protocol and connections to ground were often dropped. Given this relative homogeneity, at least when compared to a project's specifications, it is surprising that assistive tools for system architecture are not in common use.

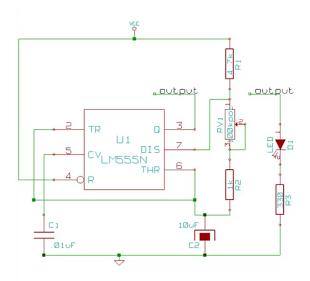

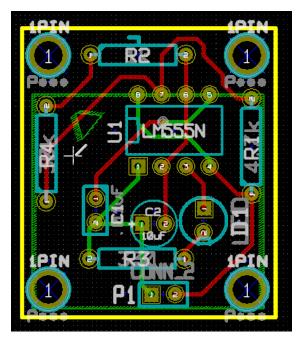

(a) Circuit Schematic

(b) Board Layout

Figure 1.2: **A blinking LED circuit** [50]. The schematic (a) is depicted with standard symbols for the components (red, blue labels); their interfaces, here called pads (red); and the connections between them, here wires (green). The corresponding board (b) also has components (blue, grey labels); interfaces, here pads (gold); and connections, here traces (red and green).

# 1.1.3 Schematic Capture

Once a circuit has been designed in the system architecture phase, it needs to be digitized for later steps with schematic capture software. Schematic editors are usually the first EDA specific tool a designer encounters in any project. During *schematic capture* developers extract the electrical circuit from their architecture diagram, retaining only basic part choice and connectivity information devoid of higher order structure, as in fig. 1.2a. Our participants considered it a "neccesary evil", an unavoidable step stopping further progress until completed.

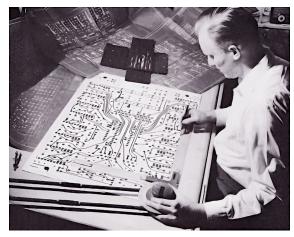

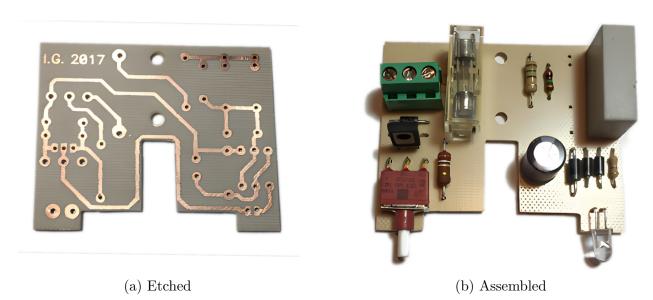

This focus on the lowest layer of abstraction is a product of the historical development of EDA tools. In the 1950s, most PCBs were drafted by hand, as in fig. 1.3a. By the '60s electrical engineers were moving away from pen-and-paper drafting for electrical circuits and printed circuit boards, adopting a workflow that used partially transparent photomasks in the board lithography process. These photomasks were created in photoplotters that printed images onto trasparent sheets of plastic. These images, the board layout, were specified as a series of commands: draw a line of X thickness from coordinate Y to coordinate Z, expose an annulus centered at A with inner radius B and outer radius C, and so on. Added together, these commands allowed engineers to define the structure of circuit boards in a repeatable,

(b) Gerber Interface Ad

Figure 1.3: Early techniques for board layout. Before photoplotters and computer aided design tools most printed circuit boards (PCBs) were drawn by hand, as seen in subfigure (a) [55]. Photoplotters gave engineers a less errorprone, more repeatable way to create layouts, one amenable to computer control. Subfigure (b) shows an advertisment from the Gerber Scientific Company showcasing a photoplotter designed for PCB manufacturing along with an interface for computer control [56].

modifiable way, one amenable to computer automation and tooling.

Figure 1.3b shows an advertisement for a series of products that connect a computer to a photoplotter, something that was becoming more common by the 1970s. Modern board layout tools have their start in the software of this time, but circuit design, and schematic drafting, were largely still pen-and-paper tasks. Schematic capture tools were designed as an entry point to the digital design process, where one would take their hand drawn circuits and, in a largely data-entry task, convert them to a digital form for use in board layout. Modern schematic capture tools like Eagle, Altium, and KiCad fill the same role, allowing the design work that has happened elsewhere to be imported into the board layout process. They have incorporated new features, like copy-and-paste, but the fundamental paradigm has remained the same, shunning interaction with the conceptually richer system architecture phase of design.

Schematic capture tools, being contrained to a thin slice of the development process, have other problems. A major one is enabling reuse of previous designer work in new projects without introducing significant manual effort or necessitating error prone integration of old subsystems into new designs. When a net of electrical connections is copied into a project it often needs to be tweaked to ensure compatibility with a different set of sibling systems or design requirements. It is easy to miss a necessary change or incorrectly integrate components because this process is largely manual, with the designer having to keep track of all relevant

concerns themselves. Modern tools can only provide limited assistance when most of the relevant context from the system architecture phase was never digitized in order to minimize data-entry effort. This means that parametric designs, which have internal logic to change the underlying circuit based on the environment in which they're used, can't meaningfully exist because there's insufficient knowledge about the environment. A better approach would need to capture this missing information without disrupting designers' workflow so more advanced features, like parametric design elements, can exist.

Figure 1.4: An electrical rules checking (ERC) pin compatibility matrix. Schematic capture tools try to provide error checking by assigning schematic pins to a small set of classes and using a matrix, like the one shown, to determine whether each connection is valid. Schematic editors lack the information needed for more substantive checks. This simplified model creates many false positives and false negatives.

One place where modern EDA tools do try to move beyond the pen-and-paper model is with their implementations of Electrical Rules Checking (ERC). ERC attempts to provide a series of automated checks that catch design mistakes early, before they cause problems in prototypes or finished devices. Sadly, a large proportion of our respondents simply turn ERC off or enable it only intermittently. Electrical rules checks, as they exist in major EDA suites, produce too many false positive and false negative alerts to keep active during the majority of schematic capture. Figure 1.4 shows why, ERC is usually defined by a matrix of

pin types that only check the compatibility of point-to-point connections based on a small list of possible classes. With only an electrical connectivity network it is hard to do more. The higher-order context that would be required to validate voltage compatibility, power consumption, bus protocols, and other properties spanning one or more wires isn't available to modern EDA tools.

In the current design paradigm, schematic capture is a thin data-entry layer only meant to get information into a format suitable for board layout and physical design. To make this feasible, it strips away the rich context of the system architecture phase, leaving designers to encode only the *much* smaller electrical connectivity of their design. This focus on the electrical net, while reasonable given its historical origins, leaves schematic capture software with too little information for more transformative changes to the embedded design process.

### 1.1.4 Board Layout

Figure 1.5: **Printed Circuit Boards (PCBs) before and after assembly** [17]. Processes for manufacturing PCBs use board layouts, like the one in fig. 1.2b, to specify where copper should remain on the final product. Traces on the PCB, visible in subfig. (a), are electrical connections that correspond to wires in the circuit diagram. When populated with components, as in subfig. (b), the device is complete.

During board layout engineers convert their schematics into designs for printed circuit boards (PCBs), which physically and electrically connect components in the final device. Engineers begin by importing a schematic into board layout tools. They assign each schematic symbol a footprint, the copper designs on the final PCB that components can be soldered to. Footprints are annotated with pads, the specific locations on the footprint that correspond to

pins so the layout tool will know how to map parts of the schematic to locations on the board. Each pad is an electrical interface. When the device is manufactured, it will be soldered to a component, connecting that component to the rest of the system. Because they have access to the schematic, board layout tools can keep track of which pads need to be connected. Engineers draw traces between pads, matching them to wires in the schematic. When every component and wire is represented by a footprint or trace, the layout is complete and can be used to manufacture a PCB. Figure 1.5 shows the end result, both after immediately manufacturing and once the PCB is populated with components.

Board layout is well suited for computerization. Both bookkeeping and error checking are computationally simple but tedious to perform manually. Ensuring that each part of the schematic has a corresponding element in the board layout amounts to checking items off a list. Error checking mostly focuses on the physical properties of the board; for example, ensuring traces don't intersect and pads have sufficient empty space surrounding them. These measurements are easy for a layout tools to perform when they are built to keep track of shapes and locations.

The effect of Computer Aided Design on board layout is immediately visible when comparing old boards with new. Old, manually-drafted designs, like the one in fig. 1.3a, tend to have traces with wide sweeping curves. This is because traces were drawn with tape, to ensure a consistent width, and sharp turns would make the tape bunch up, keeping the sheet from lying flat. The modern style, visible in figs. 1.2b and 1.5a is markedly different. Instead of smooth curves, traces are drawn with straight lines and a distinct preference for 45 degree angles, a byproduct of how early layout tools snapped traces to a grid, trading artistic freedom for computational simplicity.

We do not focus on board layout in this dissertation, taking the existing tools as given and targeting them directly. Instead of rewriting them for marginal gains, our work produces netlists, stripped schematics that layout tools can use as inputs. The relative robustness of existing software means that we can focus on underserved portions of the embedded design process.

# 1.2 Evaluating Embedded Development Tools

Evaluating our methodology requires judging how our tools affect the development process, something we do by looking at the different types of costs designers pay to design something. We can see the design process as one of sequential decision making; the user makes one choice, then another, then another, until they have a complete design. This framing gives us a way of looking at the costs inherent in the design process, three of which we use to evaluate design tools: time, attention, and momentum. Tools shape which decisions a user has to make and each decision takes some *time*, so a good tool allows a user to accomplish a task with fewer, quicker decisions. Likewise, users need information in order to make each decision. This information can be managed by either the user, spending their attention, or by their tools, minimizing their burden. Finally, users will want to make these decisions in some

order that feels natural to them. A bad tool won't accommodate this and forces the user to make decisions in some other order, sapping their *momentum*. These costs correspond directly to the three criteria we use to judge design tools, respectively: automation, salience, and ergonomics.

Automation compares the decisions users have to make when using a tool. Less automated tools forces more decision points, especially ones which are more complex or redundant. More automated tools minimize redundancy, complexity, and wasted work. Automation saves users time, which is usually directly valuable. An extreme example of automation is design synthesis, where all of the decisions needed to move from a specification to a design are made by the tool without human intervention. Less extreme cases include features like parameterized designs which allow the user to perform a task once and reuse that work elsewhere.

Salience assesses the information presented to the user. Tools with worse salience require the user to dig for necessary information. Tools with better salience are proactive, presenting the user with information that is immediately relevant without overwhelming their attention. Features which notify the user can make or break salience. For instance, a tool's error alerts and auto-complete suggestions can be timely and useful or they could be noise the user has to filter out.

Ergonomics looks at how flexible the tool is and whether it requires change in how users think. Less ergonomic tools force their users to make decisions in a certain order. They have a significant gap between the user's mental model and the tool's model of the problem. More ergonomic tools present abstractions in the ways that a user naturally reaches for, and are not tied to any one order of operations. A very ergonomic tool 'disappears' in the user's experience. It just does what the user wants it to; without needing them to spend time or effort on figuring out how to wrestle it into a useful shape.

# 1.3 Using Automated Reasoning

Our methodology relies on how automated reasoning tools can make inferences about mathematical models in a generic and flexible way, independent of the domain being modeled. Automated reasoning covers a variety of different algorithms from logic programming, theorem proving, and constraint solving. These algorithms work on sets of mathematical statements, examining them to produce inferences, new statements that are consistent with the input set. Depending on choice of logic, the axioms a tool understands. Different tools can be used to reason about different logics: boolean logic, linear algebra, predicate logic, and others. Different tools also produce different types of inferences; one might produce proofs that some statement is true, while another might rewrite statements into more elegant forms. This dissertation focuses on two such tools, satisfiability-modulo-theory solvers [5] (SMT solvers) and propagators, along with a logic of real numbers and boolean variables.

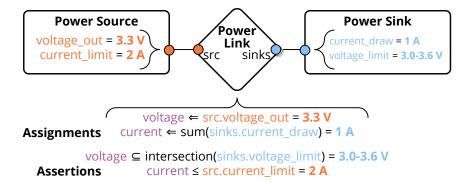

Our work builds on this framework by translating architecture diagrams into sets of statements within a chosen logic. Every property a design has, from the clock speed of a microcontroller to the color of an LED, is translated into a variable in our model. Constraints within a block or relationships represented by links become statements relating those variables to each other. These systems of equations are models of the design that tools can reason over. Much of our methodology's power comes from how automated reasoning tools simply see a bag of statements. It does not matter if some statements are missing—for instance due to an abstract or incomplete design—the reasoning tools will produce inferences regardless.

SMT Solvers, used in EDG, try to solve systems of constraints, i.e. find assignments to every variable such that every constraint is satisfied. They do not support multi-step interactions; transactions are all or nothing. If you can encode a complex problem in a system of constraints, then an SMT solver can find a solution in a single step. As they search for a solution, SMT solvers will, internally, speculate. They will try making choices one way, and if that does not work, try another. EDG leans on this decision making capacity, using the solver for choices that would normally fall to the user.

Propagators, used in PolyBlocks, view a system of equations as a network and push values around as they're discovered. When a variable is given a fixed value, all the equations it appears in are updated and, where applicable, simplified. When equations are simplified enough to be solvable, they are and the answers substituted into other equations. So, when a new piece of information is added it can trigger waves of updates that propagate through the model. If there is a conflict, then the propagation engine can detect that and raise an error. This allows for easy automation to ensure a design stays consistent as the user makes changes, and inconsistencies caught just as they appear. While not as powerful as a SAT solver, propagators are sufficient for implementing many designer support features.

# 1.4 Summary

We seek to show that automated reasoning tools working with mathematical models of embedded systems can be used to build development tools that better support users. Embedded Design Generation (EDG) is a proof-of-concept meant to show that our methodology is powerful enough to cover the entire embedded design process and can make every decision needed to go from specification to final design. Polymorphic Blocks (PolyBlocks) shows that the techniques from EDG can, with some modification, be used in a practical embedded development tool suitable for a general audience of embedded developers. By extending EDG's electronics model, PolyBlocks shows that its core approach of representing embedded systems as constraints can work on the types of problems designers encounter in the real world. PolyBlocks also shows how our methodology can be made tractable enough for an interactive development tool by replacing EDG's powerful but slow backend with a simpler form of automated reasoning that is significantly faster. Together EDG and PolyBlocks serve as evidence for our thesis and as a foundation for future design tools.

## 1.5 Statement of Prior Publication

This thesis is based on, and incorporates material from, these prior published works:

- Turning Coders into Makers: The Promise of Embedded Design Generation [46] (SCF '17), co-authored with Richard Lin, Antonio Iannopollo, Alberto Sangiovanni Vincentelli, Prabal Dutta, and Björn Hartmann

- Polymorphic Blocks: Unifying High-level Specification and Low-level Control for Circuit Board Design [34] (UIST '20), primarily authored by Richard Lin with other co-authors Connie Chi, Nikhil Jain, Ryan Nuqui, Prabal Dutta, and Björn Hartmann. Also used in Richard Lin's PhD thesis [33].

None of this work would have been possible without the effort of all the co-authors, including my advisor Prabal Dutta, graduate student colleagues Richard Lin and Antonio Iannopollo, and all the undergraduates who have worked with us over the years.

# Chapter 2

# **Embedded Design Generation**

## 2.1 Introduction

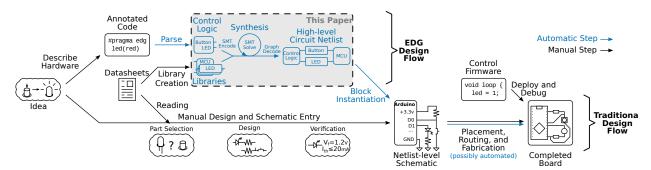

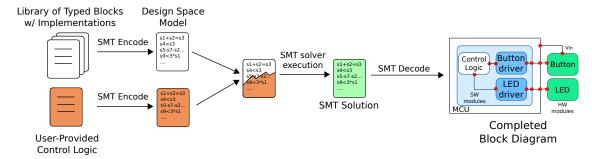

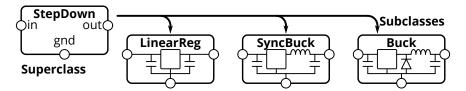

Figure 2.1: The Embedded Design Generation (EDG) Methodology. In contrast with traditional embedded development methods, which rely on significant user skill, EDG only requires a high-level specification to generate an electrically correct circuit that satisfies user requirements. Whole-cloth synthesis serves as a test of this dissertation's thesis that an approach centered around automated reasoning is capable of building powerful and usable embedded development tools. By completely automating the design process, with no human in the loop, we show that automated reasoning tools are capable of capturing and reasoning about the design process in all its complexity. As a proof-of-concept our prototype only implements those portions of the system that directly interact with the synthesis step. We both manually generate the specification needed, instead of extracting it from existing code, and manually create a circuit netlist from the output block diagram.

Embedded design is a process of sequential decision making that requires skill, knowledge, and judgment. At each step, the designer is weighing their specification against the current state of the project, gathered information, and the options in front of them. These judgment calls slowly add up until they have a finished schematic.

A good support tool has to understand and assist with these decisions in whole or in part. To know whether an error is salient the tool must know about the parts involved, have an understanding of how "complete" the design is, and be aware of other factors that feed into whether a user should be shown some error. An ergonomic work surface requires understanding how well defined the design is at any point in time. Knowing when to trigger automation requires differentiating between decisions requiring user input and those completely implied by other decisions.

Synthesis, the process of going from a specification to a finished design without user interaction, is an extreme test of understanding. A tool capable of synthesis must have a powerful enough model and powerful enough reasoning to handle the smaller choices. A model that can determine whether a full design works can also be used to detect smaller errors. A synthesis tool that can use minimal or partial designs as a specification can reason about designs no matter how the user approaches them. Synthesis is an example of the maximum possible automation, with most other automation operations existing within.

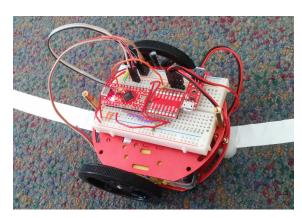

Synthesis is also a valuable feature in its own right, especially for novices lacking in background knowledge or skills. This is shown by the widespread interest in small-scale fabrication of embedded devices by non-professionals. We see a proliferation in other tools designed to make embedded development more approachable by using encapsulated hardware modules. Arduino, Raspberry Pi, Gumstix and others provide off-the-shelf modules that trade flexibility of design for ease of use. A synthesis tool would allow novices to subvert that trade-off by making it easier for them to develop systems optimized for their exact goals.

To that end, we propose a novel methodology, *Embedded Design Generation* (EDG), which exploits advances in constraint solvers to allow the automated generation of functionally correct-by-construction<sup>1</sup> board-level designs from a high level specification. EDG serves as a test of the applicability of automated reasoning tools to embedded design, as successful synthesis implies EDA tools can perform any of its sub-tasks with the same approach.

Tools based on EDG would only require that the user annotate their embedded software with simple requirements and, from that specification, synthesize the final circuit diagram, bill of materials, and firmware. Software APIs, electrical properties of circuits (e.g. Kirchhoff's current and voltage laws), and other low level details are combined with the user input into a system of constraints.

Existing constraint solvers can then generate designs which are functionally correct, electrically sound, and satisfy the user specification. To show that this both works and is computationally feasible, we build a prototype tool and test it with a variety of examples from different domains.

Figure 2.1 provides an overview of our proposed design flow and compares it to current embedded design practices. EDG abstracts away, through automation, much of the electronics expertise needed for tasks like parts selection, circuit design, and verification. In addition, figs. 2.2 to 2.6, 2.9 and 2.10 are all a part of a running example where we describe the

<sup>&</sup>lt;sup>1</sup>We do not consider timing or other performance constraints in this paper as the focus is to empower designers who do not have to produce industrial strength boards.

construction of a simple device with a single LED and button.

### 2.2 Related Work

EDG builds on prior work in "electronic design automation" (EDA) by specializing the Platform-Based Design (PBD) methodology [48] for maker-scale embedded development. PBD is a methodology which has been successfully used to create synthesis tools in a number of domains, including integrated circuit (IC) development and automotive engineering. EDA community has incrementally raised the abstraction level of many embedded development tasks and by using insights from PBD and synthesis tools in other domains, we contribute to that progress.

#### 2.2.1 General EDA

General-purpose board-level circuit design tools have largely not moved beyond graphical schematic capture, where users place electronic components and connect their pins together. In mainstream tools, hierarchical blocks allow some degree of abstraction by grouping low-level components together, but their lack of parameterization limits re-use. Additionally, while electronic design automation (EDA) tools feature electrical verification checks, these are of limited utility to makers. Matrix-based connection legality checks (for example, checking input-output directionality), though ubiquitous in design suites, are rarely used, non-extensible, catch only small classes of bugs, and have a high false-positive rate. Higher-end design suites often feature technologically advanced checks, like electromagnetic compatibility (EMC) or radio frequency interference (RFI), but these generally require significant skill to operate.

There has been some work towards building board design tools better suited for makers. For instance, PHDL [44] is a Verilog-like language for describing netlists that allows some parameterization of blocks and better designentry. However, like Verilog, it is only a static description of a circuit.

JITPCB [4] takes the concept further and embeds a hardware construction language in a general purpose programming language, allowing circuit generators instead of simple parameterized blocks. However, like PHDL, it does not have a model of the underlying design space, preventing it from catching many errors. JITPCB also does not reason over voltage, current, bandwidth, or other properties needed to perform useful verification of a design, something our tool does.

EDASolver [15] aims to be a synthesis tool for microcontroller based embedded systems. When given a tree that describes the basic structure of an embedded device, EDASolver can choose specific components to generate a circuit fitting that broad structure. Unlike JITPCB, it does have some understanding of the electrical properties of an embedded system, and can use that to choose valid components from a pool of parts. As EDASolver has neither published source code nor a technical paper, we are unable to fully characterize its capabilities

and limitations, but its modeling of electronics does not appear to be extensible beyond voltage and current limits.

While both JITPCB and EDASolver have some ability to choose specific components from vague specifications and automate the assignment of individual pins, these features are constrained by their inability to reason over the *topology* of a circuit. Our tool, and likely any tool that follows the EDG methodology, is capable of not only choosing components as needed but also adding elements to the topology of a circuit. This means our tool can create new power domains, insert amplifiers and buffers, and infer the need for IO expanders whenever required to create a valid design. Fundamentally, we reason over the space of possible designs and the requirements without the need to tightly constrain the topology of possible solutions. As a result, even our rudimentary tool can compensate for limitations in parts or complexities in a specification in much the same way that an engineer might.

## 2.2.2 PBD and Domain-Specific Tools

In Platform-Based Design's (PBD) terminology, our methodology maps user input to a set of library components according to well-defined composition rules that can be verified statically. PBD-based tools solve the synthesis problem by opportunistically composing elements from a library to generate systems of constraints which can be solved by external solvers. For instance, METRO II [12] allows for general model integration and architecture exploration, where the mapping process between specification and platform is validated through simulation. Likewise, PYCO [23] synthesizes a complete specification for a system from a partial set of Linear Temporal Logic (LTL) constraints and a library of components with LTL contracts. Although reminiscent of these techniques, the approach taken for EDG does not require the use of LTL or other logic languages.

Some techniques related to our approach have been also used in program synthesis. Brahma [26, 18] synthesizes loop-free programs over bitvectors out of a library of simpler functions. This allows Brahma to generate software from a sparse specification of boolean logic constraints. [20] propose the use of types in a program to synthesize valid expressions which are then suggested to the programmer.

Robotics-oriented design tools like EMLab [7] and ROSLab [37, 38] solve similar problems to EDG in that domain. EMLab is a block-level development tool for robotic electronics that uses an SMT based verification mechanism similar to our own, however it does not extend that to provide synthesis. ROSLab provides a similar pathway from code to circuitry, however unlike our tool, it is limited to custom-made hardware elements that support their custom chaining protocol. In contrast, EDG works with off-the-shelf electronics in order to reduce the cost of creating a library of parts and enable the fast integration of new components.

Finally, tools aiding interactive device design largely also follow the pattern of automatically figuring out details from a high-level design, albeit in more constrained domains. For instance Midas [49] automatically designs capacitive touch layouts given user-specified sensor type, shape, and position. Likewise, PaperPulse [45] adds interactive electronics elements to paper crafts from a library of widgets.

# 2.3 Methodology

The goal of Embedded Design Generation is to create better abstractions for developing embedded devices and tools that can perform robust verification of device designs. However, better verification requires our tool to reason about the relationship between hardware and software. Verifying the electrical properties of a thermometer does no good if that thermometer has no way to send its data to the designer's software. Our key insight is that many of the design's hardware requirements are reflected in the code, for example in required libraries and pin assignments. Yet the fundamental logic of the device, how it functions at runtime, is rarely reflected in the hardware. This asymmetry suggests that higher level abstractions for embedded development should be similar to embedded code.

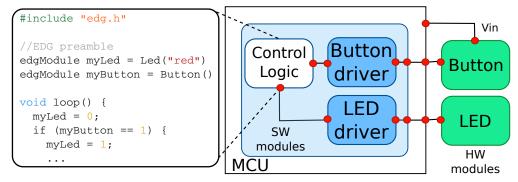

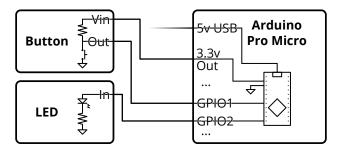

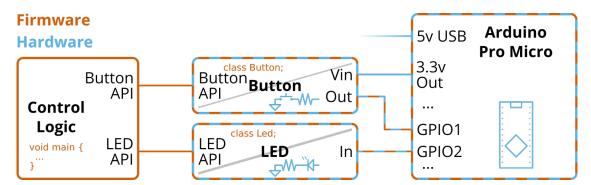

Figure 2.2: Code can be a specification for a device. The code to the left, the control logic, specifies a device in which a light blinks when a button is pressed. It is also the software that is eventually run on that device, the annotations in the EDGPreamble specify the hardware infrastructure needed to make the software function as intended. The block diagram to the right describes one possible device that matches that specification, by meeting all the hardware requirements in and being able to run the control logic. Due to our focus on the synthesis process, the code shown here is a mockup that shows one possible structure for a specification.

If we want to be able to describe the device at a higher level, we can capture the most important parts of its function and construction in its code. We can specify how the device acts at runtime, as well as the hardware infrastructure needed for the device to function. Figure 2.2 shows a stylized example of this, where many of the implicit hardware requirements that are expressed in user code are rendered as explicit declarations for a design generation tool to use. The software in fig. 2.2 is a specification for the hardware and the runtime operation of the device.

To make this kind of high-level abstraction useful, we must be able to compile it into the firmware and circuitry needed to construct an embedded device. However, firmware and circuit diagrams are too low-level for efficient synthesis. Instead we represent the result as a block diagram, like the one in fig. 2.2, which can be easily turned into a final design. Likewise, we need to be able to tell if those block diagrams actually describe correct devices, so that

Figure 2.3: **Design Generation at a High Level.** EDG tools use existing constraint solvers to perform synthesis. The tools convert knowledge about the design space and control logic specification into constraint satisfaction problems whose solutions are block diagrams describing valid device designs. These block diagrams completely specify the design of an embedded device and can be easily converted to more useful formats.

we do not generate broken or invalid designs. A *type system* gives us a way to construct the blocks for real-world parts and an algorithm to decide whether any given block diagram is correct. Finally, we need to choose a single valid device from the space of possible devices. We do this by constructing a *design space model*, which captures a wide range of possible designs in ways that existing constraint solvers can reason about.

The Embedded Design Generation methodology is built around these three core concepts:

Block Diagrams capture the conceptual structure of a device across both hardware and software boundaries, by taking elements of the final design and representing them as blocks with connectivity information. These diagrams are an intuitive yet powerful model for working with systems, and can capture device structure, resources, and many of the other relationships found between elements of a design.

**The Type System** defines rules for how we transcribe the real world properties of circuits and software into blocks and their *type signatures*. It also gives us *type checking*, a process that determines whether any block diagram describes a valid device.

The Design Space Model is a system of constraints suitable for general-purpose solvers, built from a library of blocks and their type signatures. This model can then be used to generate a complete, working, block diagram for a device from a specification.

Figure 2.3 shows our methodology for design generation, which exploits the growing speed and increasing expressive power of constraint satisfaction problem (CSP) solvers. We convert a library of blocks, with corresponding type signatures, into a monolithic set of constraints that model the space of potential designs made up of those blocks. These constraints are then composed with constraints derived from the control logic to produce a CSP whose space of valid solutions is the space of valid block diagrams that meet our specification. We then pass this CSP to the solver and decode the result into a block diagram that will successfully typecheck.

Figure 2.4: Convert a block diagram into circuitry by linking implementations together. Instantiating the block diagram from fig. 2.2 requires taking implementation details associated with each block, in this case a relevant sub-circuit, and connecting them together based on the links between their blocks.

(a) Original Control Logic

Figure 2.5: Convert a block diagram to firmware by filling in templates. Instantiating software is a simple template replacement operation. Figure 2.5a is a mockup of user-provided control logic for the device. Figure 2.5b is the code after we replace the EDG-provided template elements with the concrete implementations provided by other blocks. Note that the code outside of these templates is unmodified.

(b) Instantiated Firmware

Block diagrams are ideal representations because they are easy to convert into the design files needed to fabricate a device. Figure 2.4 shows how the final circuit can be created by connecting individual block implementations along the links between them. Similarly, fig. 2.5 shows how the firmware can be instantiated with template replacement operations that pull from code snippets provided by connected blocks.

Block diagrams also work at many levels of fidelity. In general, blocks can be composed of smaller blocks until one recurses down to single instructions or individual circuit elements. Our current tool works with relatively large blocks made up of entire libraries or breakout boards. This allows us to abstract away questions of timing delay, electromagnetic interference, and many other phenomena that become evident at smaller scales. Large blocks also mean there is a smaller space of possible configurations for solvers to reason over, making their

immediate use more feasible. As solvers grow faster and more expressive, EDG tools can move to using finer granularity models with smaller blocks.

We structure each block diagram around the notions of blocks, ports, and links. As we have seen, *blocks* represent realizable elements of our final design and each has a number of *ports* which represent specific capabilities, relationships, or resources a block may have. *Links* are then the connections between ports that represent the transfer of resources, usage of capabilities, or other relationships between blocks. For instance, the connection of a serial line or the use of a software API.

A block diagram must have all the information needed to instantiate a device but many parts have properties and settings that are not solely defined by their connections. Consider the LED in fig. 2.4, which could be annotated with information about its color. To allow the block diagram to represent this information, blocks, ports, and links all have *concrete types*, which are structures made up of named primitives—like integers, boolean values, and strings—or nested substructures. Concrete types allow each block to specify the information needed to instantiate it as well as additional properties useful in other phases of design generation.

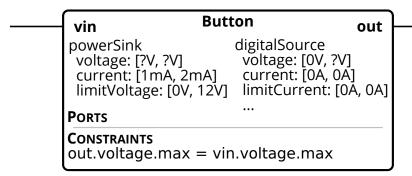

The block diagram alone is not enough for synthesis, since we require a way to determine whether any given block diagram will result in a valid device. The *type system* gives us a way to generate blocks and their *type signatures*, constraints over those blocks, so that we can check the correctness of an entire block diagram. As in fig. 2.6, type signatures annotate blocks, ports and links with constraints that limit the concrete types they may have within in a block diagram. Then, type checking ensures that each element of the design satisfies its type signature. In section 2.4.2 we explore how we constructed a type system for our prototype tool that accurately detects and rejects invalid designs with this procedure.

Finally, Embedded Design Generation requires that we are able to turn a library of blocks and type signatures into a design space model that our tools can reason over. In practice, we expect this to take the form of a monolithic constraint satisfaction problem to which we can add the specifications, usually in the form of a control logic block, for any particular synthesis task. This single model can then be optimized or added to, as new parts become available or new limitations in the design space are found. We build the Design Space Model by generating a CSP for each block that might be included in an output design, and then adding variables that determine whether any pair of ports is connected. The solver can then choose which connections exist and give us the final block diagram, with valid concrete types for each block, link, and port. While optimizations can be layered over this, we believe that any design space model will have this core structure.

# 2.4 EDG Prototype Architecture

Our prototype tool implements the EDG methodology described in the previous section, with a focus on synthesizing devices from relatively large blocks at a level high above individual

Figure 2.6: **Type signatures are constraints on their elements.** While elements of a design are given concrete types, the blocks on their own are usable in a variety of settings. Type signatures are simply the conditions under which a block will work as intended, presented as constraints over the concrete type of a block. A type system is the set of rules for how to map real-world properties into types and type signatures, such that a block diagram which typechecks can be instantiated into a working device. In this case we constrain the expected input and output voltages of a button to be equal, a limitation on the possible concrete types that button may have.

resistors and ICs. We implemented our tool in Haskell and used Z3 [13] as the underlying constraint solver.<sup>2</sup>

## 2.4.1 Blocks, Links, and Ports

As in the general methodology, our prototype uses blocks, links, and ports to represent possible designs for embedded devices. Figures 2.7 and 2.8 illustrate the principal data structures used in our tool. The user provides their input in the form of control logic which we manually encode as a block that must appear in the final design.

# 2.4.2 Type Signatures

Each block, link, and port in our library contains a type signature, i.e. a set of bounds on the concrete type an element may have in a valid block diagram. In a block diagram concrete types are data structures composed of named fields, each linked to a value. These values can be boolean, integers, floats, strings, UIDs or another nested set of field-value pairs.

Our tool's internal representation for type signatures is shown in figs. 2.7 and 2.8. These structures capture all the pieces of information needed to generate the SMT representation of a design element, with the majority of the constraints simply being stored as expressions that translate directly into SMT constraints. As in fig. 2.6 each constraint provides a way

<sup>&</sup>lt;sup>2</sup>Our code and the results of our experiments are available at https://lab11.github.io/edg-sat-prototype/appendix/scf2017.

```

PORT p:

used :: Bool:

Indicates whether the port is used in the final design

Indicates whether the port is connected to another port

connected :: Bool:

class :: String:

Identifier used to constrain which ports can connect to each other

type :: [fields]:

List of fields to be translated to SMT variables

List of formulas over the type of the port.

constraints::[expr]:

Must be true for system to typecheck

IMPLICIT CONSTRAINTS:

connected => used:

Ensures that a port is part of the design if connected to any other port

forall c in constraints, used => c:

```

Only requires the solver to satisfy the constraints if the port is being used

Figure 2.7: Ports use implicit constraints to capture connectivity. The implicit constraints in each port allow us to relax the constraints on the SMT solver. The first constraint says that if the port is connected to another then the port must be used in the output block diagram. Along with the corresponding constraints from fig. 2.8, this ensures that every element has a flag to show whether it is used in the final design. The second implicit constraint tells the SMT solver that none of the type signature's constraints need to be satisfied if the element is not used , minimizing its work.

```

BLOCK/LINK b:

UID :: String:

Unique identifier for the block

used :: Bool:

Indicates whether the block is in the final design

ports :: [port]:

List of ports attached to this block

type :: [fields]:

List of fields to be translated as SMT variables

constraints::[expr]: List of formulas over the type of the block and its ports.

Must be true for system to typecheck

IMPLICIT CONSTRAINTS:

forall p in Ports, p.used => used:

Ensures that a block is part of the design if any of its ports are part of the design.

forall c in constraints, used => c:

Only requires the solver to satisfy the constraints if the block is being used

```

Figure 2.8: Blocks and links have identical representations in our tool. Despite their stylistic differences, both blocks and links capture relationships between ports, along with some internal data and constraints. This allows us to turn connections between modules via links into one-to-one relationships between ports on modules and ports on links, simplifying the process of constructing an SMT problem.

to express the ambiguity in a type signature, since each block has many valid concrete types and can therefore work in a variety of different designs. The constraints are arbitrary expressions consisting of boolean expressions, ordering operators, linear arithmetic operators, and references to values found in the concrete type of that element.

In other cases the constraints can be used to specify that a value falls in some range, that there exists an equality which must be preserved, or any other condition that is representable as an expression in our solver. These expressions can capture many complex behaviors, like the assignment of pins to functions on a microcontroller, ranges of voltages and currents, and even the nesting of interfaces where our tool has to infer additional parts.

We choose to limit constraints on numerical values to linear arithmetic because non-linear relationships that cannot be conservatively approximated by linear ones are relatively rare given the fidelity of our tool. Since Z3 and other SMT solvers are much slower when working with non-linear constraints, we choose to limit ourselves to the faster option.

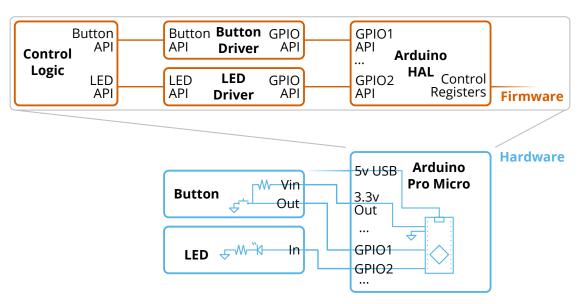

Figure 2.9: There are symmetries between the hardware and firmware elements of a design. Many of the hardware elements of a design are paired with corresponding firmware elements, as in the case of an LED and its driver code. These pairs tend to have identical structure in both domains, even if there are other components that only exist in one domain.

# 2.4.3 Design Space Model

Our prototype naively constructs a design space model from its library of blocks and links. We rely on the fact that constraints in type signatures are almost identical to the equivalent SMT expression.

All the type signature fields in figs. 2.7 and 2.8 are transformed into sets of constraints. Each flag in the element and value in the type becomes a variable the SMT solver is capable of assigning. Then we add constraints between those variables to match those in the type signatures. From this state, we generate a large adjacency matrix where each cell is an unassigned boolean value that determines whether a particular pair of ports is linked. If ports are linked, their types are set equal and they are marked as being connected. This lets us simulate a one-to-one connection between ports on a block and ports on a link. We then extract this adjacency matrix from the SMT solver's solution and use it to construct the block diagram by walking the resulting graph and recovering each block's concrete type.

### 2.4.4 SMT encoding, solving, and decoding

Working from the control logic and the design space model, our tool encodes the complete synthesis problem as a system of boolean and linear arithmetic constraints which are then solved by an SMT solver. Blocks, links and ports are all translated to equivalent SMT constraints as described in the previous subsection. The control logic is treated like any other block and added to the CSP, though with the additional requirement that it be used in the final design.

Once the encoding is complete, our tool generates an SMT-LIB v2.0 compatible file which is then passed to the SMT solver. If the solver is able to find a solution to the system of constraints, it is decoded into data structures where all the type signatures have been resolved to concrete types. Finally, the resulting network of blocks is presented to the user as a block diagram describing a device that can run the control logic.

# 2.5 Type System Design

As connection legality essentially drives circuit synthesis, the properties and constraints captured in the type signatures are especially important. In our prototype, we attempt to model the parameters needed to ensure that the circuit is electrically valid, programatically valid, and meets user requirements.

# 2.5.1 Software and Hardware Modeling

As a complete embedded design tool, our prototype must model both the hardware (circuits) and software (user code and drivers). While it is common to think of them as completely separate domains, as in fig. 2.9, they are usually heavily intertwined in practice.

Most peripherals ultimately expose a firmware API and most electrical components are controlled to some degree by the firmware. As in fig. 2.10, our representation combines the hardware and firmware domains in ports and blocks when appropriate.

Compared to separate representations, this reduces the number of ports and blocks that the solver needs to search through, improving performance. This combined model accurately

Figure 2.10: Our representation with an integrated view of hardware and firmware. This combines the circuit design and firmware drivers of each peripheral from fig. 2.9 into a single block. In this case the firmware and hardware blocks for the Arduino, button, and LED are combined into a single block representing each component. Note that pure hardware and firmware elements still do exist.

represents how many APIs control electrical connections and drivers are usually associated with a device, without additional complicated constraints to tie domains together.

#### 2.5.2 Ports and Links

As synthesis is interface driven, components are almost completely defined by their ports. Our type system models common electrical ports, including several digital communications networks, as well as arbitrary firmware APIs.

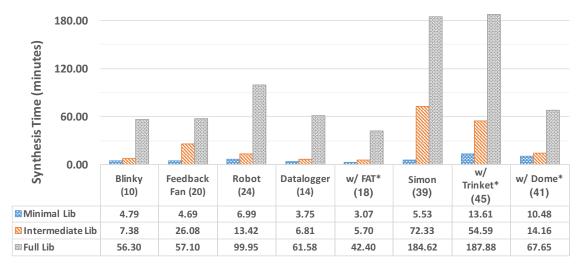

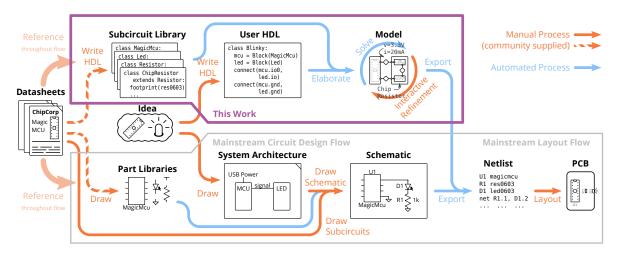

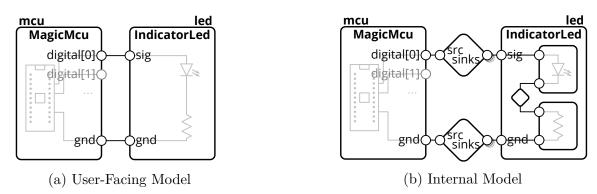

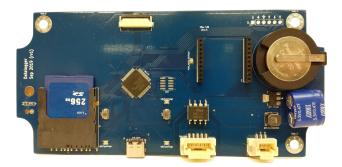

#### 2.5.2.1 Firmware Ports