### UNIVERSITY OF CALIFORNIA RIVERSIDE

Improving Energy Efficiency of Basic Linear Algebra Routines on Heterogeneous Systems With Multiple GPUs

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

by

Hadi Zamani Sabzi

March 2023

#### Dissertation Committee:

Prof. Laxmi Bhuyan, Chairperson

Prof. Nael Abu-Ghazaleh

Prof. Zizhong Chen

Prof. Daniel Wong

| The | Di | ssertation | of Hadi | Zamani | Sabzi | is approved:          |

|-----|----|------------|---------|--------|-------|-----------------------|

|     |    |            |         |        |       |                       |

|     |    |            |         |        |       |                       |

|     |    |            |         |        |       |                       |

|     |    |            |         |        |       |                       |

|     | •  |            |         |        |       |                       |

|     |    |            |         |        |       |                       |

|     |    |            |         |        |       |                       |

|     | -  |            |         |        |       |                       |

|     |    |            |         |        |       | Committee Chairperson |

University of California, Riverside

#### Acknowledgments

Finishing this dissertation marks the end of a major chapter of my life and the beginning of a new innings. I thank you all from the bottom of my heart, for your unquestionable support, continuous encouragement and endless patience, that helped me navigate my PhD Journey.

First of all, I would like to thank my advisor, Dr. Laxmi Bhuyan for his unconditional support. His technical, editorial and general advice, and mentoring was pivotal in the completion of the dissertation. I would also like to thank my dissertation committee members, Zizhong Chen and Dr. Daniel Wong for their support and endless help in my research, and Dr. Nael Abu-Ghazaleh for his support and guidance as this dissertation shaped from a proposal to a complete study. Their constructive feedback has helped me immensely to improve the quality of this dissertation.

Next, I would like to thank my amazing collaborators, Dr. Zizhong Chen, Dr. Daniel Wong, Devashree Tripathy, and Ali Jahanshahi. I would like to thank all the professors, mentors, co-workers, teachers, students, friends in my life for being there for me and believing in me. I thank my labmates and fellow graduate researchers: Devashree Tripathy, Liang Zhou, Ali Jahanshahi, And Sourav Panda.

Finally, most importantly, I would like to express my gratitude towards my family for their unconditional support during my pursuit of this arduous journey. Especially, I thank my parents for providing me a strong education foundation to begin with and rowing the seeds of research aptitude since childhood, my brothers and sister, Shahram, Babak, Hamed, and Roya for always motivating me, for their love, support and encouragement.

#### ABSTRACT OF THE DISSERTATION

Improving Energy Efficiency of Basic Linear Algebra Routines on Heterogeneous Systems With Multiple GPUs

by

#### Hadi Zamani Sabzi

Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, March 2023 Prof. Laxmi Bhuyan, Chairperson

The current trend of ever-increasing performance in high performance computing (HPC) applications comes with tremendous growth in energy consumption. Because existing libraries are mainly concerned with performance, they do not make efficient use of heterogeneous computing systems, resulting in energy inefficiency. Hence, improving the energy efficiency of critical applications running on HPC systems is necessary to deliver better performance at a given power budget. The aim of this dissertation is to develop techniques and frameworks to improve the energy efficiency of the high performance applications on heterogeneous system with GPUs while maintaining the reliability and performance requirements.

In our first approach, we present GreenMM framework for matrix multiplication, which reduces energy consumption in GPUs through undervolting without sacrificing the performance. The idea is to undervolt the GPU beyond the minimum operating voltage  $(V_{min})$  to save maximum energy while keeping the frequency constant. Since such undervolting may give rise to faults, we design an Algorithm Based Fault Tolerance (ABFT) algorithm

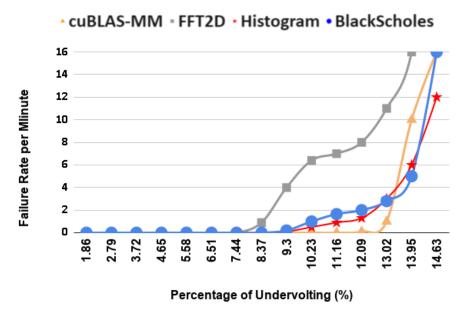

to detect and correct those errors. We target Matrix Multiplication (MM), as a key kernel used in many scientific applications. Empirically, we explore different errors and derive a fault model as a function of undervolting levels and matrix sizes. Then, using the model, we configure the proposed fault tolerant MM algorithm. We show that energy consumption is reduced up to 19.8%. GreenMM also improves the GFLOPS/Watt by 9% with negligible performance overhead.

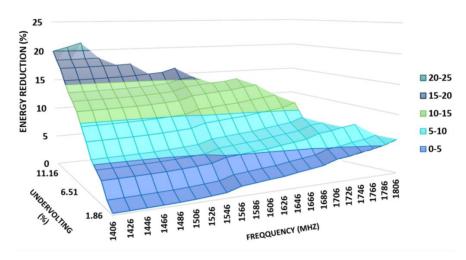

In our second study, we present a framework for GPU applications, which reduces energy consumption in GPUs through Safe Overclocking and Undervolting (SAOU) without sacrificing performance. The idea is to increase the frequency beyond the safe frequency  $f_{safeMax}$  and undervolt below  $V_{safeMin}$  to get maximum energy saving. Since such overclocking and undervolting may give rise to faults, we employ an enhanced checkpoint-recovery technique to cover the possible errors. Empirically, we explore different errors and derive a fault model that is used to determine the appropriate undervolting and overclocking level for maximum energy saving. Similarly, we target MM kernel for error correction using the checkpoint and recovery (CR) technique as an example of scientific applications. In case of MM, SAOU achieves up to 22% energy reduction through undervolting and overclocking without sacrificing the performance.

In our third study, we introduce GreenMD, an energy-efficient framework for heterogeneous systems for LU factorization utilizing multi-GPUs. LU factorization is a crucial kernel from the MAGMA library, which is highly optimized. The aim is to apply DVFS by leveraging slacks intelligently on both CPU and multiple GPUs. To predict the slack times, accurate performance models are developed separately for CPUs, GPUs, and

PCIe bus based on the algorithmic knowledge and manufacturer's specifications. We also determine the appropriate level of undervolting for both CPUs and GPUs through offline profiling. Reducing voltage below threshold values may give rise to errors; hence we extract the minimum safe voltages  $(V_{safeMin})$  for the CPUs and GPUs utilizing a low overhead profiling phase and apply them before execution. It is shown that GreenMD improves the CPU, GPUs, and total energy about 59%, 21%, and 31%, respectively, while delivering similar performance to the state-of-the-art linear algebra library MAGMA.

In our fourth study, we introduce a fault tolerant algorithm for LU factorization on heterogeneous systems with GPUs. We have developed a fault tolerant algorithm by constructing a local and global checksums. The local checksums are used to detect the errors and the global checksums are used to correct the errors. Using the local checksums, we can detect the errors in the middle of the computation which enables us to tolerate more number of faults during the whole execution. LU factorization has three main phases. These phases have different sensitivity to the error. For each phase, we introduce an appropriate level of fault tolerance to prevent the error propagation to other phases. Since, we check the correctness of the computation in each iteration, if there is any error in the system, only the small fraction of the computation is affected and can be covered easily in compared to the previous works such as ABFT.

### Contents

| Li       | st of      | Figures                                                                                                                                         | X   |

|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Li       | st of      | Tables                                                                                                                                          | xii |

| 1        | Intr       | roduction                                                                                                                                       | 1   |

|          | 1.1<br>1.2 | GreenMM: Energy Efficient GPU Matrix Multiplication Through Undervolting SAOU: Safe Adaptive Overclocking and Undervolting for Energy-Efficient | 2   |

|          |            | GPU Computing                                                                                                                                   | 6   |

|          | 1.3        | GreenMD: Energy-Efficient Matrix Decomposition on Heterogeneous Multi-                                                                          |     |

|          |            | GPU Systems                                                                                                                                     | 9   |

|          | 1.4        | Fault Tolerant Matrix Decomposition on Heterogeneous Multi-GPU System                                                                           | 13  |

|          | 1.5        | Dissertation Organization                                                                                                                       | 16  |

| <b>2</b> | Gre        | enMM: Energy Efficient GPU Matrix Multiplication Through Under-                                                                                 |     |

| _        | volt       | -                                                                                                                                               | 17  |

|          | 2.1        |                                                                                                                                                 | 17  |

|          |            | 2.1.1 Fault Distribution in GPU                                                                                                                 | 18  |

|          |            | 2.1.2 GPU Fault Model                                                                                                                           | 20  |

|          | 2.2        | GreenMM: Energy Saving Methodology                                                                                                              | 22  |

|          |            | 2.2.1 Offline Profiling                                                                                                                         | 23  |

|          |            | 2.2.2 Offline FT-cuBLAS-MM                                                                                                                      | 29  |

|          |            | 2.2.3 Online FT-cuBLAS-MM                                                                                                                       | 30  |

|          | 2.3        | Evaluation                                                                                                                                      | 34  |

|          |            | 2.3.1 Experimental Setup                                                                                                                        | 34  |

|          |            | 2.3.2 Performance and Energy Saving Evaluation of FT-cuBLAS-MM                                                                                  | 35  |

|          |            | 2.3.3 Performance/Watt and Total Energy Consumption Evaluation                                                                                  | 39  |

| 3        | SAC        | OU: Safe Adaptive Overclocking and Undervolting for Energy-Efficient                                                                            |     |

|          |            | U Computing                                                                                                                                     | 41  |

|          | 3.1        | Fault Model                                                                                                                                     | 41  |

|          | 3.2        | Checkpoint and Recovery                                                                                                                         | 48  |

|          |            | 3 2 1 Implementation Details                                                                                                                    | 50  |

|   | 3.3                 | Evaluation                                                           | 54  |

|---|---------------------|----------------------------------------------------------------------|-----|

|   |                     | 3.3.1 Experimental Setup                                             | 54  |

|   |                     | 3.3.2 Results                                                        | 54  |

| 4 | $\operatorname{Gr}$ | eenMD: Energy-Efficient Matrix Decomposition on Heterogeneou         | s   |

|   | Mu                  | lti-GPU Systems                                                      | 56  |

|   | 4.1                 | Background And Motivation                                            | 56  |

|   |                     | 4.1.1 LU Factorization Overview                                      | 56  |

|   |                     | 4.1.2 Profiling Observations                                         | 57  |

|   | 4.2                 | Slack Predictor                                                      | 60  |

|   |                     | 4.2.1 Performance Model Of LU Factorization On The CPU               | 61  |

|   |                     | 4.2.2 Performance Model of the GPU Kernel                            | 64  |

|   |                     | 4.2.3 Performance Model Of Data Transfer                             | 67  |

|   | 4.3                 | DVFS-Based Slack Reclamation                                         | 70  |

|   | 4.4                 | Undervolting                                                         | 75  |

|   | 4.5                 | Evaluation                                                           | 77  |

|   |                     | 4.5.1 Implementation Details                                         | 77  |

|   |                     | 4.5.2 Results                                                        | 79  |

| 5 | Fau                 | lt Tolerant Matrix Decomposition On Heterogeneous Multi-GPU Sys      | S-  |

|   | tem                 |                                                                      | 86  |

|   | 5.1                 | Background And Motivation                                            | 86  |

|   |                     | 5.1.1 Fault Model                                                    | 87  |

|   |                     | 5.1.2 Challenges Of Fault Tolerant LU Factorization                  | 87  |

|   |                     | 5.1.3 Error Propagation In LU Factorization                          | 88  |

|   | 5.2                 | Proposed Methodology                                                 | 90  |

|   |                     | 5.2.1 Checksum Setup                                                 | 92  |

|   |                     | 5.2.2 Local Checksum After Panel Factorization                       | 95  |

|   |                     | 5.2.3 Proof Of Checksum Correctness During The Right Looking LU Fac- |     |

|   |                     | torization                                                           | 96  |

|   | 5.3                 | Evaluation                                                           | 97  |

|   |                     | 5.3.1 Checksum Setup And Detection Phase                             | 97  |

| 6 | Rel                 | ated Work                                                            | 102 |

|   | 6.1                 | GreenMM                                                              | 102 |

|   | 6.2                 | SAOU                                                                 | 104 |

|   | 6.3                 | GreenMD                                                              | 106 |

|   | 6.4                 | Fault Tolerant LU Decomposition                                      | 108 |

| 7 | Cor                 | nclusion And Future Work                                             | 111 |

| R | hlior               | vranhv                                                               | 115 |

### List of Figures

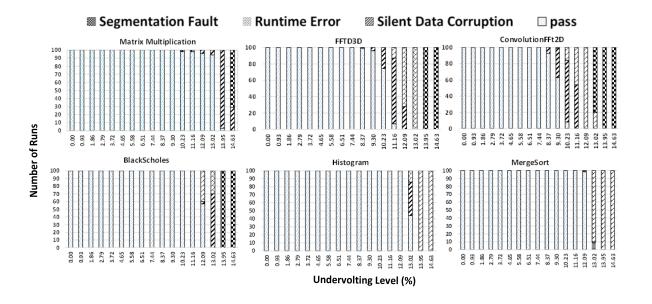

| 2.1  | Error distribution below nominal voltage for different benchmarks using GTX 980              | 19 |

|------|----------------------------------------------------------------------------------------------|----|

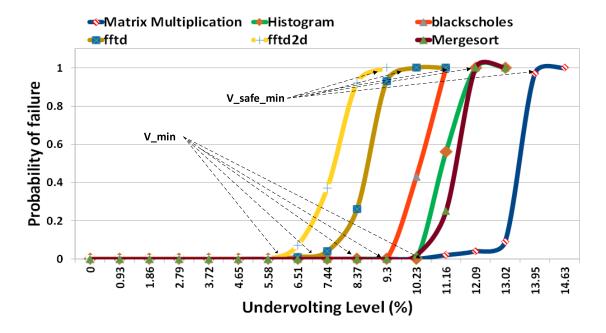

| 2.2  | Probability of failure for different Rodinia benchmarks and cuBLAS-MM from                   | 20 |

| 2.3  | cuBLAS library                                                                               | 22 |

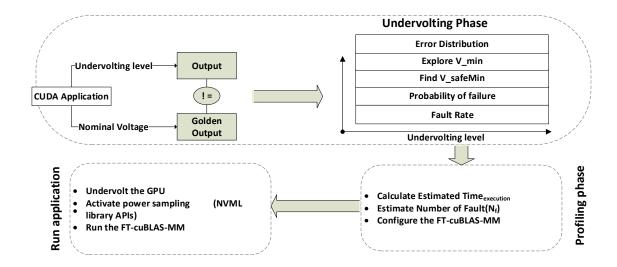

| 2.4  | GreenMM overview                                                                             | 24 |

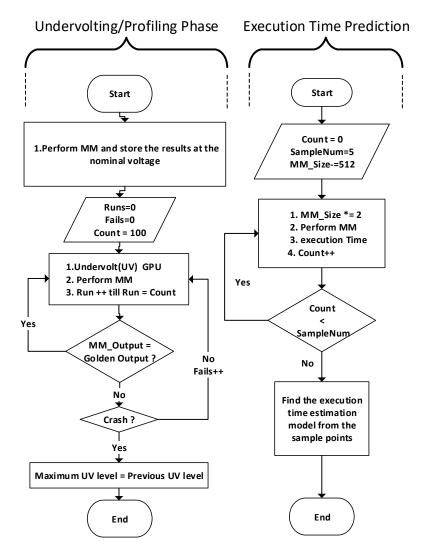

| 2.5  | Overview of offline profiling                                                                | 25 |

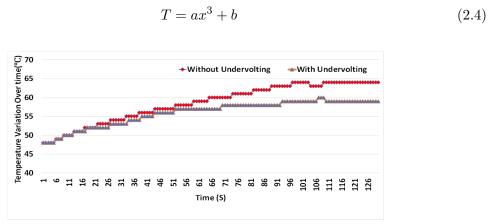

| 2.6  | Temperature variation over time without and with maximum level of undervolting               | 26 |

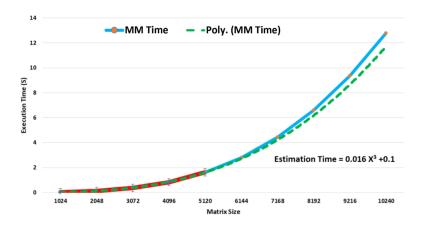

| 2.7  | Execution time estimation model vs. the real execution time                                  | 27 |

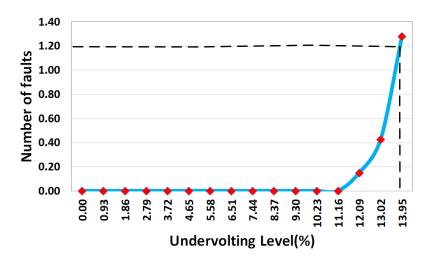

| 2.8  | Number of faults according to the undervolting level for matrices with size of               |    |

|      | 10K on NVIDIA GTX 980                                                                        | 28 |

| 2.9  | Estimated Number of faults for different matrix sizes given the undervolting levels          | 29 |

| 2.10 | Performance overhead of matrix multiplication for different matrix sizes in                  |    |

|      | presence of two errors                                                                       | 36 |

| 2.11 | Performance evaluation of the FT-cuBLAS-MM                                                   | 37 |

| 2.12 | Energy saving in the FT-cuBLAS-MM versus the original cuBLAS-MM given                        |    |

| 2.13 | different undervolting levels and number of faults                                           | 38 |

| _,,  | in presence of different number of faults                                                    | 39 |

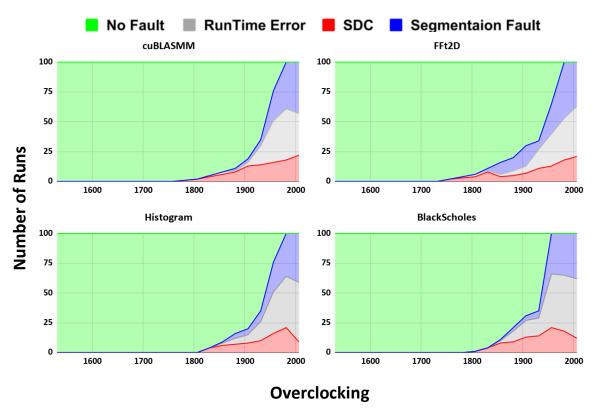

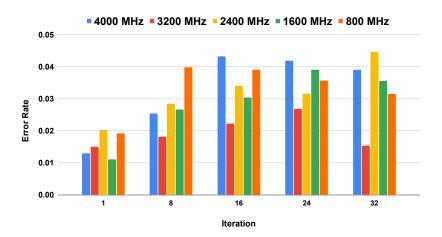

| 3.1  | Fault distribution w.r.t. overclocking                                                       | 42 |

| 3.2  | Failure rate of different Rodinia benchmarks and cuBLAS-MM from cuBLAS                       |    |

|      | library w.r.t overclocking                                                                   | 45 |

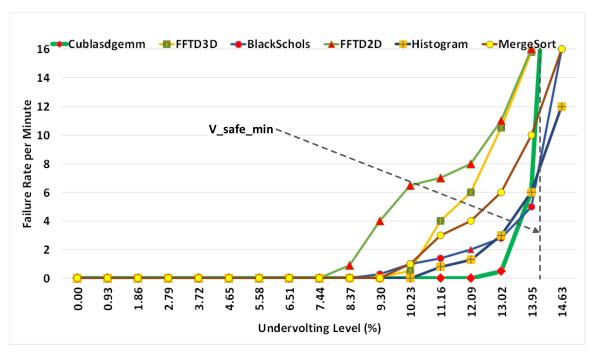

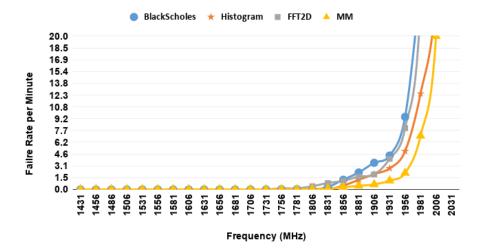

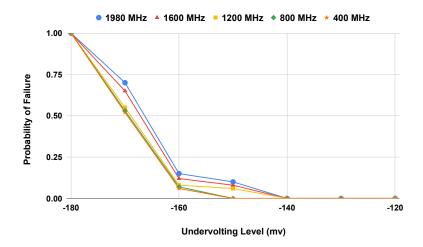

| 3.3  | Failure rate w.r.t undervolting                                                              | 46 |

| 3.4  | Number of faults in regard to overclocking and undervolting for matrix with                  |    |

|      | size of 10K                                                                                  | 47 |

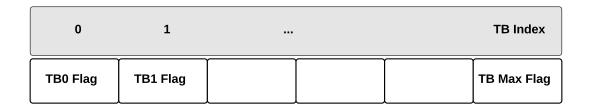

| 3.5  | Thread block level synchronization using array of global variables                           | 51 |

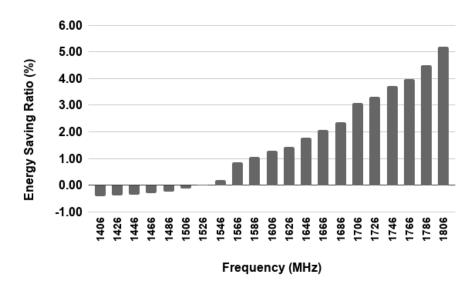

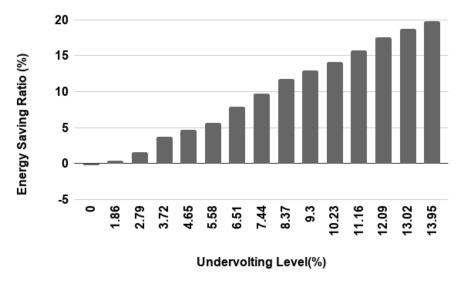

| 3.6  | Energy saving ratio in regard to overclocking in presence of $\operatorname{CR}$ algorithm . | 52 |

| 3.7  | Energy saving ratio in regard to undervolting in presence of CR algorithm .                  | 53 |

| 3.8        | Energy reduction for given frequencies and voltages                            | 55       |

|------------|--------------------------------------------------------------------------------|----------|

| 4.1<br>4.2 | Overview of the blocked LU factorization                                       | 58       |

|            | tion for a matrix of size 18K                                                  | 59       |

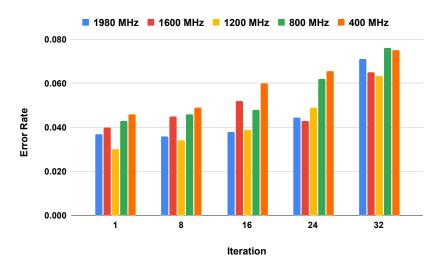

| 4.3        | The estimated time of CPU w.r.t various frequencies                            | 61       |

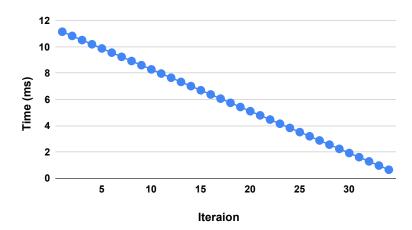

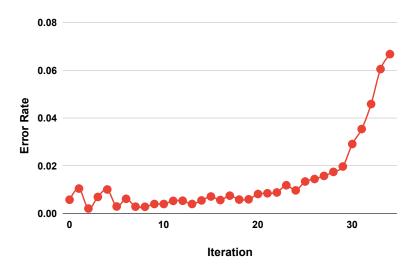

| 4.4        | Error rate in performance model on the underlying CPU                          | 64       |

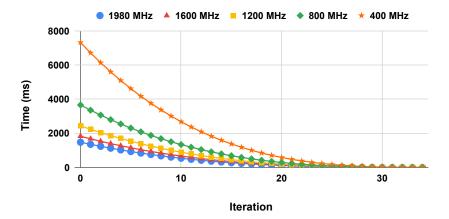

| 4.5        | The estimated time of single GPU w.r.t various frequencies using Equation 4.10 | 66       |

| 4.6        | Error rate of GPU performance model provided in equation 4.10                  | 67       |

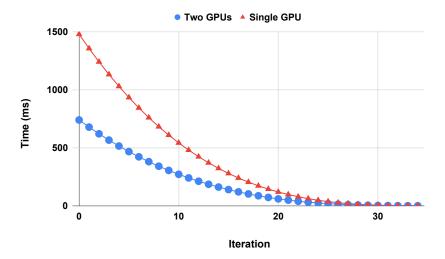

| 4.7        | Estimated GPU time with single and Two GPUs at default frequency of 1980       | 0.0      |

| 4.0        | MHz                                                                            | 68       |

| 4.8        | The estimated copy time of double precision LU factorization for a matrix of   | 00       |

| 4.0        | size 18K                                                                       | 69       |

| 4.9        | The error rate of the PCIe model for a matrix of size 18K                      | 70<br>71 |

|            | An overview of slack reclamation                                               | 76       |

|            | CPU's probability of failure w.r.t undervolting                                | 77       |

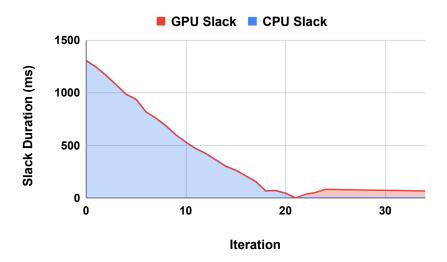

|            | The amount of CPU and GPU slack for double precision LU factorization          | ' '      |

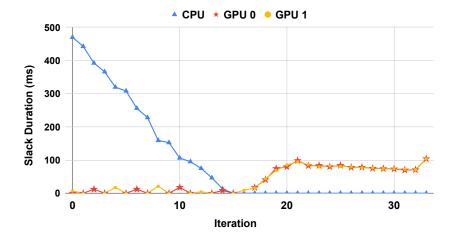

| 4.10       | with one GPU and matrix of size 18K                                            | 79       |

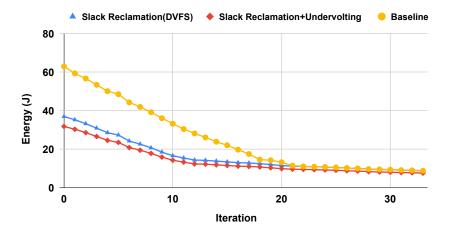

| 4 14       | The CPU energy improvement of double precision LU factorization with single    | 1.0      |

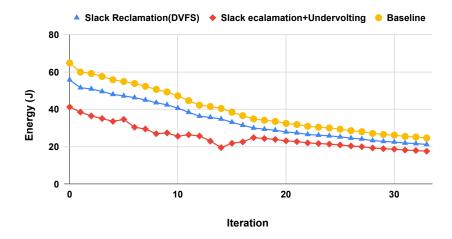

| 1.11       | GPU for a matrix of size 18K                                                   | 80       |

| 4.15       | GPU Energy improvement of double precision LU factorization in presence of     |          |

|            | single GPUs for a matrix of size 18k                                           | 81       |

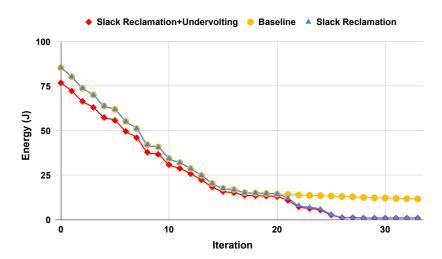

| 4.16       | The amount of slack for double precision LU factorization in presence of Two   |          |

|            | GPUs for matrix of size 18K                                                    | 81       |

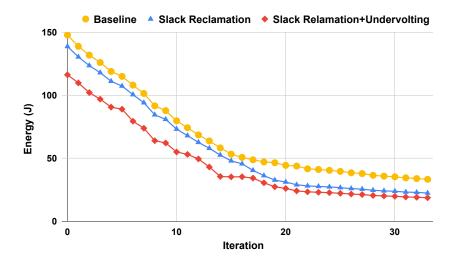

| 4.17       | The CPU energy improvement of double precision LU factorization with two       |          |

|            | GPUs for a matrix of size 18K                                                  | 82       |

| 4.18       | Total CPU and GPU energy improvement of double precision LU factorization      |          |

|            | with two GPUs for a matrix of size 18k                                         | 82       |

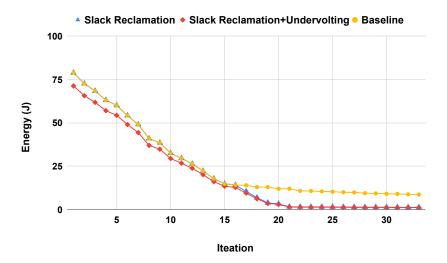

| 4.19       | GPU energy improvement of double precision LU factorization in presence of     |          |

|            | Two GPUs for a matrix of size 18k                                              | 83       |

| 4.20       | Total CPU and GPU energy improvement of double precision LU factorization      |          |

|            | with single GPUs for a matrix of size 18k                                      | 84       |

| 5.1        | Error propagation scheme of error in different sections of the matrix          | 89       |

| 5.2        | Overview of the Fault Tolerant LU factorization                                | 91       |

| 5.3        | Original input matrix with block size of $4 \times 3 \dots \dots \dots$        | 92       |

| 5.4        | Original input matrix with local checksums added to each block. Block width    |          |

|            | is increased by 1                                                              | 93       |

| 5.5        | Original input matrix with local and global checksums added                    | 94       |

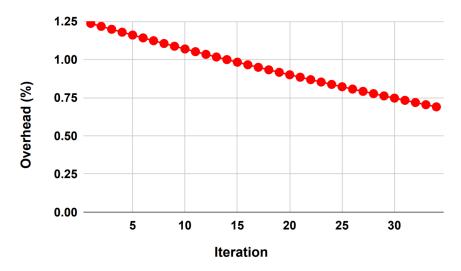

| 5.6        | The checksum verification overhead of panel factorization                      | 98       |

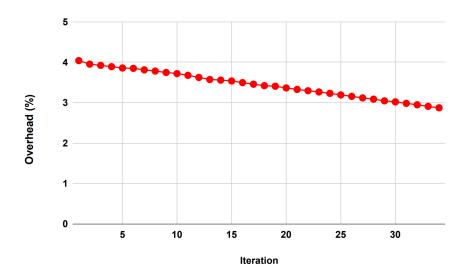

| 5.7        | The checksum verification overhead of row panel update                         | 96       |

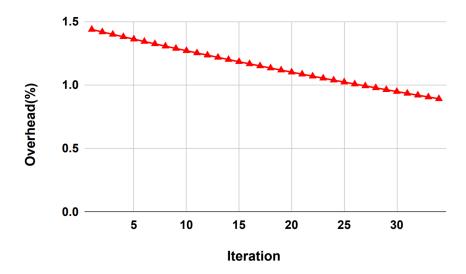

| 5.8        | The checksum setup and verification overhead of panel factorization            | 100      |

| 5.9        | The checksum verification overhead of trailing matrix update                   | 100      |

### List of Tables

| 2.1 | Power management commands using the NVML library                      | 35 |

|-----|-----------------------------------------------------------------------|----|

| 2.2 | NVIDIA GTX 980 specifications                                         | 36 |

| 4.1 | Experimental setup configuration                                      | 77 |

| 4.2 | Power management and undervolting APIs                                | 79 |

| 4.3 | Energy improvement of CPU, GPU/GPUs in heterogeneous systems with one |    |

|     | GPU and two GPUs                                                      | 85 |

| 5.1 | Experimental setup configuration                                      | 97 |

### Chapter 1

### Introduction

High Performance Computing (HPC) applications like molecular dynamics, weather prediction and drug discovery demand parallel processing environments. General Purpose Graphics Processing Units (GPGPUs) have evolved as high performance accelerators due to their SIMD (Single Instruction Multiple Data) processing architecture. Modern GPUs with hundreds of computing cores are capable of  $7.8\ TFLOP/s$  of double precision floating-point (FP64) and  $15.7\ TFLOP/s$  of single precision (FP32) [57]. Moreover, GPUs are equipped with huge memory bandwidth as high as  $1\ TB/s$ . These characteristics make them well-suited for use as accelerators in HPC applications, especially for numerical computations and vector processing. Given their high computational capabilities, the GPUs consume a significant portion of the total system energy. Because existing libraries are mainly concerned with performance, they do not make efficient use of heterogeneous computing systems, resulting in energy inefficiency. Hence, improving the energy efficiency of critical applications running on HPC systems is necessary to deliver better performance at a given

power budget. Matrix multiplication (MM), and Matrix decomposition algorithms are heavily used in many important numerical computations. The matrix-multiplication kernel, referred to as GEMM in the Basic Linear Algebra Subroutines (BLAS) [56], is frequently used as a basic numerical calculation library in CPUs. GEMM and LU decomposition routines are critical to the performance of High Performance LINPACK benchmark (HPL) and many software packages solving problem in linear algebra such as LAPACK, ScaLAPACK, MUMPS and SuperLU. Improving the energy efficiency usually comes with degrading the reliability. For instance reducing the operating voltage will result in experiencing more faults in the system. Soft errors can occur in heterogeneous computing systems that use GPUs. Recent studies have revealed that GPUs are susceptible to soft errors and any error in long running kernels, if not solved, could cause restart that considerably rises the GPU workload. According to the previous works, soft error rate increases as the voltage reduces more [46]. Hence, there is trade-off between performance, energy efficiency, and reliability. Previous works have not considered the impact of energy efficiency, reliability, performance together. In this thesis we aim to improve the energy efficiency of the heterogeneous systems while marinating the performance and reliability requirements.

## 1.1 GreenMM: Energy Efficient GPU Matrix Multiplication Through Undervolting

Over the past few years, there have been significant efforts to study different techniques improving energy efficiency of GPUs such as Dynamic Voltage and Frequency Scaling (DVFS) [34] [60], and load balancing in the CPU-GPU heterogeneous systems [59]

[79]. However, DVFS techniques result in performance degradation due to lowering of the frequency.

GPUs are designed to operate in worst case operating conditions in terms of process, temperature and voltage variation. A comprehensive study has been done on several commercial GPU cards showing that there exists about 20% voltage guardband on different GPU cards, which, when utilized, can result in up to 25% energy saving on GPU cards [46].

The impact of undervolting for energy saving has thoroughly been analyzed recently by reducing the voltage down to the safe minimum voltage [46] [49]. Leng et al. [46] explore energy benefits of reducing voltage of the GPU chip down to the safe limit. We aim to save even more energy through undervolting the GPU beyond the safe minimum operating voltage and tackling the possible GPU faults by employing a configurable low-overhead fault tolerant (FT) algorithm. According to [46] and our observations, different applications affect the  $V_{min}$  at which the program executes correctly but fails when the voltage is reduced any further. The errors can be classified into Silent Data Corruption (SDC), Run-time Faults, Segmentation Faults, and Operating System (OS) crash. Some types of errors lead to divergence in the application control flow, and as a result, increase the execution time and even in some rare cases end up in an infinite loop [46]. The most predominant error is SDC. In Fast Fourier Transform (FFT), Matrix Multiplication and Hotspot benchmarks, the SDC errors lead to 24%, 42% and 55% faulty executions, respectively [69].

The reliability loss due to undervolting is not acceptable for most scientific computing cases. There are software level fault tolerant techniques such as DMR (dual modular redundancy) [66] and TMR (triple modular redundancy) [58], which take advantage of

redundancies for handling erroneous cases, and checkpointing that tolerate errors in a checkpoint-restart manner [74]. These techniques are not very efficient for large scale scientific applications due to large energy and performance overheads [29]. In such cases, algorithm based fault tolerance (ABFT) [41], which tolerates errors at the application level, plays a crucial role in error detection and correction in the systems. ABFT techniques in GPUs were introduced for MM [27], Cholesky [16] and Fast Fourier Transform [73]. Tan et al. [93] proposed a technique for undervolting CPUs and correcting errors through ABFT techniques.

In our first study, we introduce an energy efficient and ABFT framework, GreenMM, which tolerates system errors due to undervolting. In our proposed framework, we use a combination of undervolting and ABFT for GPUs to guarantee energy, power, reliability, and performance efficiency of the system. First, we experimentally determine  $V_{safeMin}$ , which is the undervolting level beyond which the Operating System crashes for different applications. The proposed GreenMM framework exploits the voltage slack between  $V_{min}$  and  $V_{safeMin}$  using a lightweight offline profiling to accurately predict the needed fault coverage capability as a function of matrix size, undervolting level and architectural details. We modify the offline ABFT algorithm by incorporating a number of faults. Online ABFT algorithms have also been proposed to reduce the overhead for detection and correction of large number of faults [41]. The basic idea is to decompose the large matrix into several blocks, which are individually protected through checksums. Unlike the offline algorithm, the overhead is lower and faults are not propagated to the output. GreenMM framework is developed for both offline and online algorithms. GreenMM achieves comparable performance (with 1.5%

performance overhead) to highly optimized cuBLAS-MM in the cuBLAS library, but needs a lot less energy, which enhances the performance per watt of the GPU.

To summarize, GreenMM has two parts, GPU Undervolting model and Fault Tolerant MM. In GPU Undervolting model we determine the fault rate,  $V_{min}$  and  $V_{safeMin}$  for MM. The undervolting is started from nominal voltage till  $V_{min}$ , during which no fault is encountered. However, when we undervolt further from  $V_{min}$  till  $V_{safeMin}$ , FT-MM corrects the errors on the fly. GreenMM makes the following contributions:

- We experimentally determine the Vmin and  $V_{safeMin}$  for different applications, including matrix multiplication.

- We develop a fault model for GPU undervolting and determine number of faults as a function of matrix size and degree of undervolting.

- We design a fault tolerant framework, "GreenMM", for matrix multiplication that

provides peak performance on GPUs. We incorporate the number of faults and modify

the original MM to implement offline and online FT-MM algorithms.

- GreenMM is transparent to applications which utilize the matrix multiplications, i.e.

it uses the same programming interface as cuBLAS-MM and GreenMM users do not

need to modify source code of the cuBLAS.

- GreenMM is portable, i.e. it can be used with any GPU architecture just by changing some architecture specific parameters in the model.

- We present various experimental results in terms of energy, power, performance and reliability. GreenMM achieves up to 19.5% energy reduction compared to the original MM. Beside that, it improves the GFLOPS/Watt of the GPU up to 9%.

### 1.2 SAOU: Safe Adaptive Overclocking and Undervolting for Energy-Efficient GPU Computing

Ever-increasing performance demands have led to the GPU-based acceleration in a wide range of computing systems from mobile devices to super computers. While GPUs deliver high computational capability, they consume a significant portion of total system energy. As technology advances towards deep sub-micron level, the static power becomes a serious problem. Several techniques including Dynamic Voltage and Frequency Scaling (DVFS) and power gating techniques have improved energy efficiency of the GPUs [26,34,60]. However, DVFS and power gating techniques usually degrade performance due to lowering the frequency or putting the components into sleep mode.

GPUs are designed to operate in worst case operating conditions in terms of process, temperature and voltage variation. A comprehensive study has been done on several commercial GPU cards showing that there exists about 20% voltage guardband on different GPU cards, which, when utilized, can result in up to 25% energy saving on GPU cards [46]. Through GreenMM framework, we have explored undervolting to save energy for GPUs for a Matrix Multiplication (MM) algorithm [105]. GreenMM saves the energy through undervolting beyond the  $V_{safeMin}$  and employing algorithm based fault tolerant (ABFT) technique to correct the errors [105].  $V_{safeMin}$  is identified as the minimum voltage for a GPU to operate without generating any fault. However, ABFT can be applied to only very regular algorithms, like matrix multiplication [42]. On the other hand, checkpoint and recovery (CR) is a general technique that can be applied to both regular and irregular applications. In SAOU, as an example, we have built our framework on top of GreenMM by

enabling the CR technique. We aim at using the voltage guardband to save energy while preserving performance. Since the GPU is undervolted at a fixed frequency, it does not incur any performance degradation.

Overclocking is another technique that reduces the execution time through boosting the frequency to a higher level. Even though the power consumption increases, the total energy can be saved due to the reduction in the execution time. However, overclocking beyond  $f_{safeMax}$  may raise errors due to having less time for charging and discharging transistors. We experimentally determine the safe values for the maximum safe frequency for different applications, similar to the undervolting experiments done earlier [46, 105].

We develop an undervolting and overclocking model and validate with several applications. We specifically target cuBLAS Matrix Multiplication (cuBLAS-MM), a key kernel used in many scientific applications and implement checkpoint and recovery (CR) on top of cuBLAS-MM.

CR is a general resilience technique that is often used to handle hard errors but it can also recover soft errors. Several CR mechanisms are developed for CPUs [64, 98]. However, none of them is feasible on NVIDIA GPUs due to the absence of particular runtime APIs to extract computation state inside the kernel. Considering these limitations, a handful of GPU CR schemes are developed [35,68,76,90]. CheCuda [90] is built on top of checkpoint and recovery library called BLCR [35] to store the system state. Since the BLCR does not support CUDA contexts, before checkpointing, it stores and destroys CUDA contexts, then runs BLCR to reallocate all destroyed GPU contexts. These extra phases, incur a huge performance overhead to the system. NVCR is another checkpoint and recovery library

which is transparent to the applications [68]. CheCL is another checkpoint and recovery technique that follows CheCuda but it is designed for OpenCL-based applications [88]. All these checkpoint and recovery techniques reload GPU state and re-launch kernels from the beginning which incurs huge performance overhead.

We propose application specific incremental CR to preserve the computation state. Our technique is similar to the in-kernel, in-memory, and incremental CR technique, employed in [76]. However, we specifically target the cuBLAS-MM library and extend it to handle faults arising from undervolting and overclocking. Through a detailed fault model based on our experiments, we determine the locations of checkpoints in the kernel. SAOU preserves computation states in the GPU device memory to eliminate transfer time between CPU and GPU. We also adopt an incremental CR that only saves the variables that have been modified since the last checkpoint. It can improve the performance but requires us to keep track of the modified variables. Once a failure happens, the preserved computation state will be loaded and the execution will be resumed from the last checkpoint. Clearly, the cost of a checkpoint will vary with the amount of states required to be saved and the bandwidth available to the storage mechanism being used to preserve the state.

This work presents performance and energy consumption using the combination of overclocking, undervolting and FT algorithm. Through experiments, we show that SAOU achieves up to 22% energy reduction for a  $10K \times 10K$  matrix multiplication. SAOU makes the following contributions:

- First, we empirically find  $f_{safeMax}$  and  $V_{safeMin}$  for different applications.

- Next, based on our overclocking and undervolting results, we develop a fault model to determine the number of checkpoints and their locations in the application.

- We design an incremental in-kernel and in-memory CR technique to overcome any transient faults during the execution.

- We verify the operation by applying the proposed technique to cu-BLAS-MM library and executing it on a NVIDIA GTX 980 GPU.

SAOU framework makes the following contributions:

- First, we empirically find  $f_{safeMax}$  and  $V_{safeMin}$  for different applications.

- Next, based on our overclocking and undervolting results, we develop a fault model to determine the number of checkpoints and their locations in the application.

- We design an incremental in-kernel and in-memory CR technique to overcome any transient faults during the execution.

- We verify the operation by applying the proposed technique to highly optimized MM kernel and executing it on a NVIDIA GTX 980 GPU.

### 1.3 GreenMD: Energy-Efficient Matrix Decomposition on Heterogeneous Multi-GPU Systems

HPC systems are increasingly using heterogeneous systems, FPGAs and GPUs, with multicore processors to boost the performance of scientific applications. GPUs, in particular, have been widely employed for HPC due to their extraordinarily high compute capability and easy programmability. High performance GPUs, on the other hand, with large

power consumption [63]. Because existing libraries are mainly concerned with performance, they do not make efficient use of heterogeneous computing systems, resulting in energy inefficiency. Hence, improving the energy efficiency of critical applications running on HPC systems is necessary to deliver better performance at a given power budget.

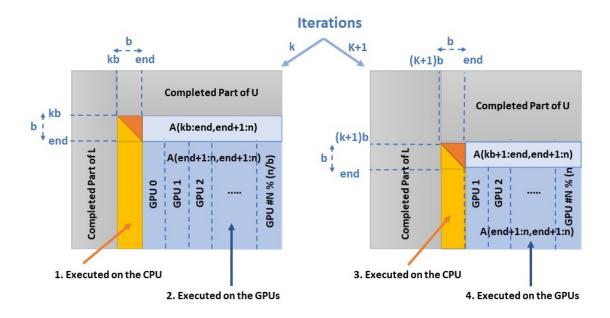

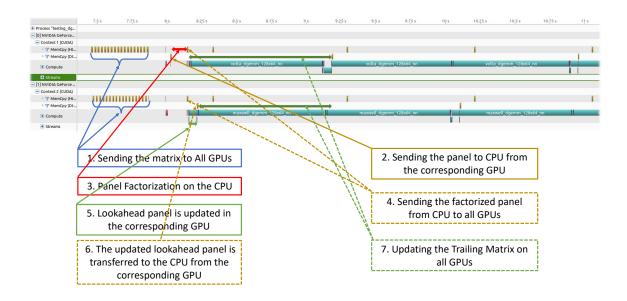

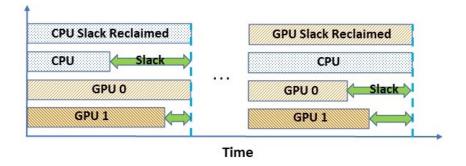

LU factorization is an algorithm used for solving dense linear algebra problems, and is widely used in many scientific and engineering applications [55]. It is included in several popular linear algebra libraries, such as Linear Algebra Package (LAPACK) [6] and Linpack [72] benchmarks. Existing LU factorization implementations are concerned primarily with performance, ignoring the potential for energy savings that do not have a negative impact on performance. When LU factorization is running on heterogeneous system equipped with GPU, it divides the workload between CPUs and GPUs. CPU handles the panel factorization, which is sequential in nature. The GPUs update the row panel and trailing matrix because they involve large computation that is highly parallelized. During the execution, either the CPU or the GPUs could be on non-critical paths that can experience idle time, or slack. These slacks can be exploited for energy savings, by exploring the power-aware techniques such as the Dynamic Voltage and Frequency Scaling (DVFS).

Over the last few years, significant efforts have been made to apply various techniques, such as Dynamic Voltage and Frequency Scaling (DVFS) [32] [61] and undervolting [105]. DVFS approaches have been employed to save energy during underutilized execution phases of the execution, called slack, on CPU [53] [5] [81] [80], and GPU [33] [95] [105] [19]. Using algorithmic knowledge, the amount of slack on different components can be estimated to determine the appropriate level of DVFS so that all the components finish execution

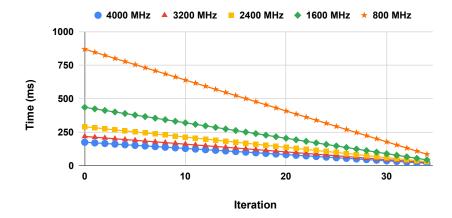

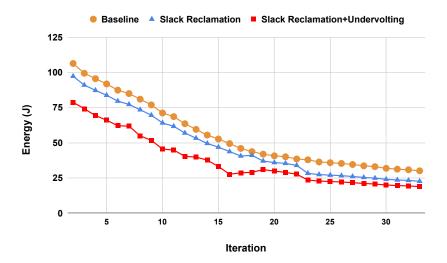

at the same time. Hence, the main task is to accurately predict the slack during the execution so that the exact frequency can be computed and DVFS can be enabled. A prior research on LU factorization utilized the slack using a simple performance model in a single GPU environment [19]. It profiled the application to determine the execution time of the first iteration, and then estimated the slack for the next iterations based on the prior iteration. However, we develop a more accurate performance model based on the amount of computation extracted from the algorithmic knowledge for heterogeneous systems with multiple GPUs that does not need profiling phase and performance overhead. Also, we extend the DVFS technique to multiple GPUs and present both performance and energy saving results with two GPUs. We derive the execution times of a multicore CPU and multiple GPUs separately and verify the results through experiment. Then the amount of slack is determined at every iteration of the LU factorization, frequency is calculated, and DVFS is enabled at runtime. Our measurement shows that DVFS reduces the energy consumption by 15%.

DVFS techniques are mainly focused on the dynamic power. Static power can be reduced only through the voltage reduction, called undervolting. However undervolting below the threshold value will introduce errors. Manufacturers specify large safety margins in the nominal frequency-voltage operating points of CPUs, up to 30% [31] [22]. As a result, they are inherently conservative and not energy efficient [10]. Leng et al. investigate the voltage guardband of the GPUs and they observe that there is about 20% voltage guardband on different GPU architectures [47]. There are many efforts to operate hardware at sub-nominal voltage levels on the CPUs [31] [22] [70] [108] and GPUs [94] [50] [47] [105]. However, most

of this work focuses on applying undervolting in a conservative way, based on the worst voltage constraint across all workloads and running frequencies. This limits the potential gains since some applications can operate at a higher degree of undervolting. Hence, we empirically extract the minimum safe voltage  $(V_{safeMin})$  of the underlying CPU/GPUs for various running frequencies while executing the LU factorization. Using the extracted  $V_{safeMin}$  for both CPU and GPUs, we apply the undervolting during the execution of the LU factorization. It is shown that undervolting reduces the energy consumption by 16% beyond DVFS.

GreenMD propose a framework that improves the energy efficiency of heterogeneous multi-GPU systems while maintaining the reliability and performance requirement of LU factorization. GreenMD is built on top of the LU factorization from the highly optimized linear algebra library MAGMA. First, we develop accurate performance models for CPU, GPU, and PCIe bus based on the algorithmic knowledge and underlying hardware details and verify through rigorous experiments. Then we predict the slack, and employ the DVFS on both the CPU and GPUs during the slack periods to save energy. GreenMD also extracts and utilizes the maximum level of undervolting at a fixed frequency to improve the energy efficiency of the system without sacrificing performance. GreenMD is portable, which means it can be used with any GPU and CPU architecture by simply adjusting a few architecture specific parameters. In summary, GreenMD makes the following contributions:

• Using algorithmic knowledge and hardware configuration, we develop a more accurate performance model for both CPU, GPUs, and the PCIe bus to estimate the execution time of the LU factorization during the different iterations of the execution.

- We implement DVFS in CPU, single and multiple GPUs based on the accurate performance models.

- We implement undervolting in CPU, single and multiple GPUs based on the empirical observations.

- We evaluate the performance, energy saving, and reliability through real implementation and achieve 31% total energy saving for double precision LU factorization with a matrix of size 18K\*18K.

# 1.4 Fault Tolerant Matrix Decomposition on Heterogeneous Multi-GPU System

With scaling down the technology and employing more number of computing cores in the hardware accelerators, they become more prone to different types of faults and errors. Hence, with increasing the number of cores, the probability of fault increases and as a result, it is vital to employ an fault tolerant algorithm for the long running applications. However, employing the appropriate method of fault tolerance with a reasonable overhead is critical to recover the application from the error. The general fault tolerant algorithms incur huge amount of performance overhead. So it is necessary to employ a proper FT algorithm to reduce the performance penalty.

LU factorization is one of the key kernels in high performance computing and soft errors or computation errors are the errors we aim to cover during the LU factorization. A single error in the LU factorization can spread to large sections of the matrix. Thus it is essential to often verify the matrix for correctness to prevent the errors from spreading to the point where they are no longer recoverable. We have discovered that different matrix sections demonstrate varying degrees of sensitivity to errors, resulting in certain sections requiring less frequent verification and some sections more frequent verification. The LU factorization has been powered by the global matrix checksum to recover from fail-stop failures [25]. With this approach, just one checksum was used, and it was assumed that failure details would come from another source. If one of the processes fails to run, the system can quickly indicate the process' location. Therefore, the error detection step is not necessary when a fail-stop failure must be addressed. On the other hand, soft errors typically leave no sign that an error has happened. An inaccurate computation result may be the only indication of a soft error.

To tolerate the soft errors, algorithm-based fault tolerance (ABFT) is a known technique that applies a checksum to a matrix and ensures that the sum will remain accurate even after performing an operation on the matrix [39]. When the sum is incorrect at the end of the computation, there has been a mistake. The sum may be used to determine the correct values or the computation may be repeated, depending on the approach and the type of error. To detect and correct a single soft error using ABFT, we need to add both row and column checksum which incurs a performance overhead. For more number of faults, we need to apply more number of weighted checksum vectors. For instance to tolerate two errors, we should append two weighted checksum vectors in each dimension of the matrix.

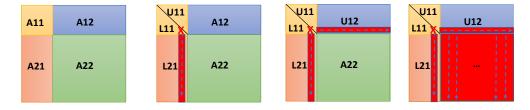

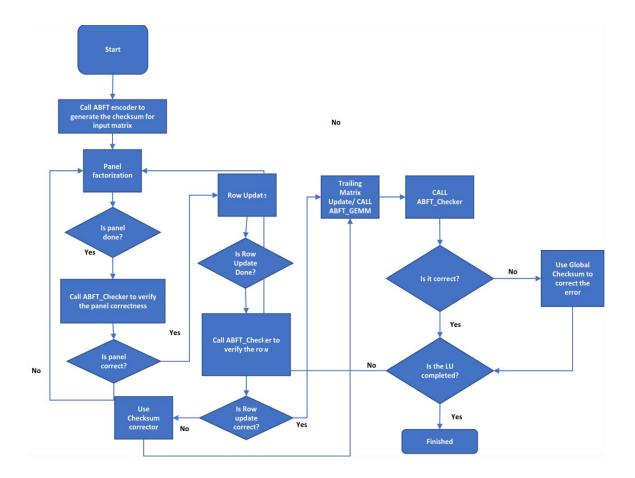

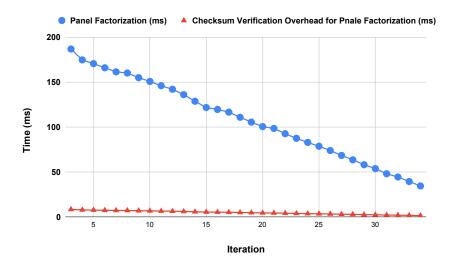

In case of LU factorization, we have developed the idea of a checksum on a matrix by figuring out how to construct it so that it is correct throughout the entire LU factorization. We are able to provide fault tolerance for the right looking LU factorization by utilizing a local and global checksum. For local checksum, we append the checksum to each block of input matrix. For global checksum, we construct the additional blocks that consist of sums of the local blocks in a row. Error detection is done using the local checksum and error correction is done using either the global checksum or repeating the computation. LU factorization has three main steps. Panel factorization, row panel update and trailing matrix update. If any error is detected in the panel factorization, the whole computation will be repeated. This phase is done on the CPU side due to its sequential nature. If the error occurs in the row panel update or the trailing matrix update phase, the global checksum will be used to recover from the error. With this approach, we check the correctness of the computation in each iteration and if there is any error in the system, the small fraction of the computation needs to recovered either using the global checksum or repeat the faulty fraction.

In summary, our proposed fault tolerant LU factorization makes the following contributions:

- Introducing the local and global checksum for the multi-GPU implementation of right looking LU factorization.

- Reducing the overhead of the fault tolerant algorithm by reducing the number of checksum vectors and verifying the correctness of the computation in the middle of the computation to reduce the performance overhead of the recovery.

- Implementing the local and global checksum in a way that the checksum relationship

is maintained during the execution.

#### 1.5 Dissertation Organization

The rest of the dissertation is organized as follows: In chapter 2, we describe GreenMM framework that improves the energy efficiency of GPUs while running highly optimized matrix multiplication (MM) kernel. Chapter 3 introduces the fault tolerant SAOU framework which employs undervolting along with overclocking to improve the energy efficiency of the GPUs. Chapter 4 discusses the GreenMD framework that uses the slack reclamation technique along with undervolting to improve the energy efficiency of heterogeneous systems equipped with multiple GPUs. Chapter 5 discusses fault tolerant LU factorization that uses both local and global checksum in a blocked LU factorization on heterogeneous systems with multiple GPUs. And finally, Chapter 6 discusses the related work and chapter 7 concludes this dissertation by giving a summary of our work.

### Chapter 2

GreenMM: Energy Efficient GPU

Matrix Multiplication Through

### Undervolting

#### 2.1 GPU Undervolting Model

Microprocessor manufacturers usually append an operating guard-band (a static voltage margin) as high as 20% of the nominal voltage, to ensure that the microprocessor functions reliably over varying load and environmental conditions [107]. The guard-bands also account for errors occurring from the load line, aging effects, noise and calibration error [78]. The guard-band grows with increase in variations in technology scaling. However, because we do not encounter these errors every time; significant energy saving can be achieved by reducing guard-band to a much lower supply voltage [45]. In our work, we

aim at using the voltage slack between the nominal voltage and the actual OS safe voltage to save energy while preserving the performance. We use a similar approach as in [46] to reach  $V_{safeMin}$ , we also build a fault model empirically as a function of the undervolting level and matrix size. In GreenMM, we go a step further by aggressively undervolting and correcting subsequent errors using the ABFT. Shrinking microprocessor feature size and diminishing the noise guard-band increase the transient fault rate. We undervolt till the safe minimum voltage  $V_{min}$  without experiencing any faults. Going beyond  $V_{min}$ , system may experience soft errors. Although, GreenMM works for all kinds of soft errors, main focus is specifically on transient and computation errors such as SDCs [46]. SDC occurs when the program finishes its execution normally without any error message but results in a wrong output. These errors can be covered at the application level. CUDA run-time errors such as driver faults or segmentation faults caused by memory management drivers can be detected by inspecting the standard error output. Operating System crash occurs after a specific undervolting level (application-dependent), and it is not possible to undervolt the GPU below the "OS crash point voltage" or  $V_{safeMin}$ .

#### 2.1.1 Fault Distribution in GPU

In order to determine the number of faults to tolerate, we profile the application. We perform sensitivity analysis of different applications by reducing the voltage beyond  $V_{min}$  and by recording the faults at each voltage. The sensitivity analysis results help us to reach the minimum voltage at which we can tolerate errors for a given application. First, we execute an application at nominal voltage and record the output as "golden output". Then, starting from base voltage of 1.075V, the underlying GPU (GTX 980) is undervolted

Figure 2.1: Error distribution below nominal voltage for different benchmarks using GTX 980

in step sizes of 10mV. The application is executed 100 times for each level of undervolting and the corresponding output is compared with the golden output to verify correctness. If the output does not match with the golden output, then the application has experienced a failure for that execution. To force the GPU to reduce its voltage at a fixed frequency, we reduce the target power limit of GPU. Fault distribution of different applications such as FFTD3D, FFTD2D, Histogram, MergeSort and BlackScholes on NVIDIA GTX 980 are shown in Figure 2.1. Applications that belong to Rodinia benchmark, are used extensively for performance evaluation of GPU architectures [11]. X-axis denotes the undervolting level starting at 1.075V, and Y-axis denotes the fault types along with their frequencies. Each application experiences different types of errors at different voltages. Some applications such as FFT2D, and FFTD3D show more number of SDC errors as compared to BlackScholes

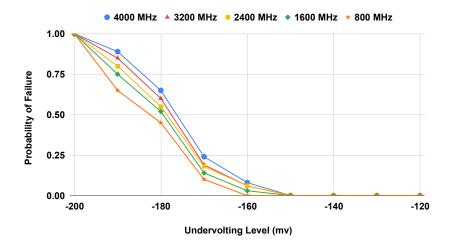

Figure 2.2: Probability of failure for different Rodinia benchmarks and cuBLAS-MM from cuBLAS library

and MergeSort benchmarks. Since SDC errors can be handled at the application level, we only focus on SDC errors.

#### 2.1.2 GPU Fault Model

The probability of failure is given by,

$$P_f = \frac{Number\ of\ failures}{Number\ of\ application\ runs} \tag{2.1}$$

$P_f$  is derived by counting number of failures in Figure 2.1. Figure 2.2 shows  $P_f$  for different applications as a function of undervolting.  $V_{min}$  is the minimum voltage at which the program executes correctly.  $(V_{safeMin})$  refers to theoretical lowest safe supply voltage under which the system can operate without crashing. As shown in Figure 2.2, applications

have different undervolting levels for  $V_{min}$  and  $V_{safeMin}$ , which means different amounts of energy can be saved through undervolting while working with different applications. We observe a significant voltage guard-band whose margin varies from one application to another. As shown in Figure 2.2, we have more voltage guard-bands in Matrix Multiplication in when compared with the guard bands in other applications which means we can save more energy in case of MM.

Reliability of application R(t) at time t is the probability that there is no failure in the system until time t. We find R(t) where t is the execution time in equation 3.2.

$$R(t) = 1 - P_f(t) \tag{2.2}$$

The failure rate is obtained using Weibull lifetime reliability model, a well-accepted model for transient and permanent soft errors as in equation 3.3 [65]. Since we consider undervolting at a fixed frequency, the failure rate model is a function of supply voltage [93].

$$R(t) = e^{-\lambda t} \tag{2.3}$$

The failure rate calculated for different applications is shown in Figure 2.3, where X-axis represents the undervolting level and Y-axis represents the failure rate per minute. The failure rate of applications BlackScholes, FFTD2D, Histogram, FFTD3D, Mergesort and cuBLAS-MM are obtained experimentally. As shown in Figure 2.3,  $V_{min}$  for CUDA applications at a specific level of undervolting are different. In [46], it is observed that programs have different activity patterns which can lead to different voltage droops. The

Figure 2.3: Failure rate of different Rodinia benchmarks and cuBLAS-MM from cuBLAS library

voltage droop is the main reason of GPU voltage noise. So, at a specific voltage, different intra and inter-kernel activities can lead to different failure rates. It is shown that the voltage noise, and specifically  $\frac{di}{dt}$  droop, has the largest impact on  $V_{safeMin}$  in [46]. Microarchitectural events, such as cache misses, cause pipeline stalls and large  $\frac{di}{dt}$  droops lead to different guardbands and  $V_{safeMin}$ . Because cuBLAS-MM is highly optimized, and all GPU components are active most of the time, there is no large  $\frac{di}{dt}$  droop which could lead to lower voltage noise margin and larger guard-band.

#### 2.2 GreenMM: Energy Saving Methodology

GreenMM introduces an adaptive FT-cuBLAS-MM algorithm; which aggressively saves energy and power on GPUs through undervolting with a negligible performance over-

head. GreenMM works with NVIDIA GPUs irrespective of the underlying GPU architecture. Figure 2.4 shows the overview of GreenMM. GreenMM finds the maximum level of undervolting for the underlying GPU and configures the adaptive FT-cuBLAS-MM to tolerate the potential faults with regards to the failure rate of the underlying GPU at the maximum level of undervolting. To find the failure rate of cuBLAS-MM, GreenMM reduces the voltage of GPU progressively up to  $V_{safeMin}$  and according to the fault model which is described in Section 2.1 find the failure rate of the GPU at each undervolting level. Then, based on the failure rate and execution time of given matrix, estimates the number of faults. Since these phases should be done before MM computation, execution time of MM is not determined. So, GreenMM uses an estimation model to predict the execution time of any arbitrary size. With multiplying the estimate execution time and failure rate of the GPU, the number of faults is determined and now we can configure the FT-cuBLAS-MM. It uses NVML library commands to reduce voltage of the GPU by changing the GPU target power limit and voltage offset.

#### 2.2.1 Offline Profiling

GreenMM finds the optimum working voltage of the GPU for cuBLAS-MM, going beyond the  $V_{min}$  and correcting the potential errors. Incorporating fault tolerance mechanism increases the execution time, which in turn increases the energy consumption. GreenMM, carefully calibrates the level of undervolting so that the energy saving is more than the energy overhead. Optimum working voltage is found through an offline profiling phase which is done only once for each GPU. Offline profiling creates the failure rate model and MM

Figure 2.4: GreenMM overview

execution time estimation model to estimate the number of faults for any MM sizes with regards to the underlying GPU. The offline profiling phase which is shown in Figure 2.5 is split into two parts:

## Phase 1: Determine The Maximum Undervolting Level $(V_{safeMin})$ And Fault Rate $(\lambda)$

We execute matrices of small sizes on the GPU to minimize the profiling time and obtain maximum undervolting level  $(V_{safeMin})$  and fault rate  $(\lambda)$ , as described in Section 2.1.

In GreenMM, the offline profiling phase takes into account the aging effect. Also, the effects due to process variation and temperature were explored on various applications on different GPU cards in [46]. They concluded that process variation and temperature have a relatively uniform impact on  $V_{safeMin}$  across all applications in a given GPU card; and the

Figure 2.5: Overview of offline profiling

effect of aging is negligible (1-2 % in the long term). Moreover, The effect of temperature rise is already included in the number of faults, as plotted in Figures 2.1 and 2.9, because our fault model already considers the increase in temperature during long executions. However, we performed additional experiments to measure temperature while undervolting. Due to limited resources, we run MM in a loop to have enough time to observe the temperature changes. The variation in temperature of the GPU over time with and without undervolting

is shown in Figure 2.6. It is observed that, after running kernel continuously, the temperature of GPU remains the same after a period of time and there is only about 11 °C variation in the temperature in presence of maximum level of undervolting. Ref. [46] shows that  $V_{safeMin}$  at 70 °C is about 20mV higher than the values at 40 °C for various GPU cards. Temperature variation in GreenMM is about 11 °C which is not big enough to make a sensible change on  $V_{safeMin}$ .

#### Phase 2: Estimate Number Of Faults Based On Matrix Size And Fault Rate $(\lambda)$

The number of faults in an application can be obtained by multiplying  $\lambda$  with the execution time, as shown in equation 3.5. Failure rate remains same irrespective of the input data size for a given application as in equation 3.3. Hence, we estimate the execution time of MM for a given matrix size on a specific GPU through a simple profiling.

Figure 2.6: Temperature variation over time without and with maximum level of undervolting

Figure 2.7: Execution time estimation model vs. the real execution time

$$F = \lambda * T \tag{2.5}$$

Due to different compute resources like SM, register file size, cache sizes and shared memory size, execution time of the MM for a given size could be vary in different GPUs. Due to memory constraints, the GPU cannot handle matrix multiplication of any arbitrary size. The time complexity of cuBLAS-MM as a function of matrix size is provided in equation 3.4, where a and b are architecture-specific constants [86] [77]. We run MM for different sizes to calculate the values of a and b for the underlying GPU. Figure 2.7 shows the experimental execution time (blue) and the execution time calculated theoretically from equation 3.4. Moreover, the red line shows sample points that were used to derive values of a and b which can be used for prediction of execution time for larger matrices, shown as green dashed line. Then, we compare the estimated execution time with the real experimental results for bigger matrices. As the results show, the estimation error is negligible.

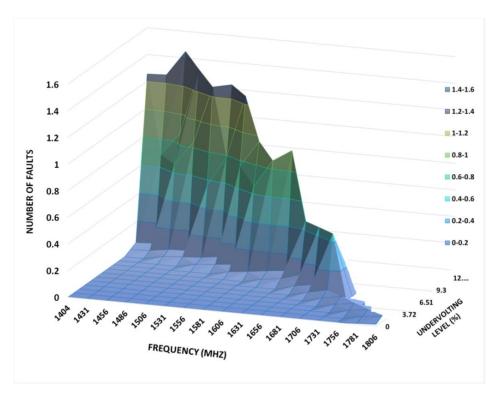

Figure 2.8: Number of faults according to the undervolting level for matrices with size of 10K on NVIDIA GTX 980

Due to memory constraints on NVIDIA GTX 980, we use matrix of size 10K for GreenMM. The  $V_{safeMin}$  is 86.05% of nominal voltage (undervolting level is 13.95%); the number of faults is 1.2 as shown in Figure 2.8. Hence, FT-cuBLAS-MM should tolerate at least 2 faults with the input size of 10K \* 10K. If GPU memory supports matrices bigger than 10K \* 10K, they may experience more number of faults.

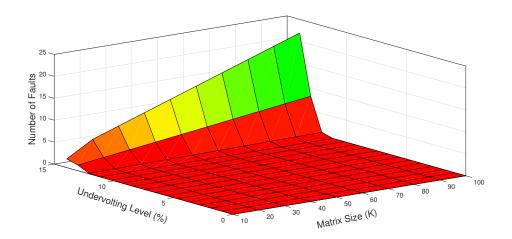

As the size of the matrix increases, the execution time as well as the number of faults also increase as shown in Figure 2.9. The matrix size varies between 10K and 100K as the undervolting level is changed from 0% to 13.95% in Y-axis; Z-axis shows the number of faults. For a given undervolting level, the number of faults for large matrix sizes is more than the number of faults in small matrices.. In the following, we propose an adaptive FT algorithm than can be configured to handle different number of faults.

Figure 2.9: Estimated Number of faults for different matrix sizes given the undervolting levels.

#### 2.2.2 Offline FT-cuBLAS-MM

The ABFT for Matrix Multiplication has a very low performance overhead when compared with other techniques [8]. The basic idea of ABFT is to encode input matrices with checksums to detect and correct the corrupted data. The traditional ABFT introduced by Huang et al. [41] is capable of correcting one fault by checking correctness at the very end of computation. In our work, we introduce an enhanced offline version, FT-cuBLAS-MM, which is capable of tolerating any arbitrary number of faults by increasing the number of weighted check-sum vectors. Algorithm 7 describes the pseudo-code for the offline FT-cuBLAS-MM.

Generating the weights of the checksum vectors, encoding the column checksums, and the row checksum are done according to algorithms into the matrix is done according algorithms 2, 3 and 4 respectively. The result of  $C^f = A^c * B^r$  is a full checksum matrix. At the end of computation, we check full checksum relationship again and if the relationship

#### **Algorithm 1** The pseudo-code for Detection Phase

- 1: Generate checksum weights vectors  $v_1$  and  $v_2$

- 2: Encode  $A \to A^c$

- 3: Encode  $B \to B^r$

- 4:  $C^f = A^c \times B^r$

- 5: Recompute the checksum for  $C^f$

- 6: Verify full checksum relationship of  $C^f$

does not hold, then our result is faulty; thereafter, faults are detected and corrected using equation 2.6.

$$C_{ij} = \sum_{j=1}^{n} c_{ij}^{f} - \sum_{k=1, k \neq j}^{n} c_{ik}^{f}$$

(2.6)

#### 2.2.3 Online FT-cuBLAS-MM

Offline FT-cuBLAS-MM only checks correctness of results at the end of computation. We design an online version of FT-cuBLAS-MM to check correctness of MM during computation, so that we can prevent faults to be propagated. We introduce an Online FT-cuBLAS-MM that can handle different number of faults. Fault coverage capability of FT-cuBLAS-MM is determined before starting the MM computation. However, the key problem here is that we must use MM algorithm such that it maintains the checksum

Algorithm 2 Generating weighted checksum vectors for each block

- 1: **for** i = 0, 1, ..., nb **do**

- 2:  $v_1[i] = 1$

- 3: end for

- 4: **for** i = 0, 1, ..., nb **do**

- 5:  $v_2[i] = 1 + i$

- 6: end for

relationship even in the middle of the computation. In [20], it is proved that outer product Matrix Multiplication maintains checksum relationship in each iteration of computation. For a matrix with size of N, we have at most N opportunities to tolerate faults during the entire MM computation. The fault detection phase, which is always active, increases the performance overhead. So, to achieve high performance, we can invoke the FT-cuBLAS-MM routine once in every several iterations. There is a trade-off between the number of iterations and overhead of online FT-cuBLAS-MM. The number of iterations to invoke FT-cuBLAS-MM is closely related to the number of faults that may happen during the computation. If the failure rate of system increases, then we should check more frequently, otherwise, there is no need to employ an algorithm with higher fault coverage capability. The algorithm to perform MM has several steps. The detailed steps of the algorithm are shown in algorithm 5.

During each iteration, we update checksum of the result matrix to maintain full checksum relationship. Then, we compute sum of each row and column in the result matrix and compare it with the row and column checksum. If the check is passed we move to the next iteration, otherwise, if any checksum does not match, we locate the exact position of error through comparing the checksums. To correct the error  $(C_{ij})$ , we simply add the difference of  $j_{th}$  checksum column and the sum of  $j_{th}$  column to the result matrix element at location (i, j). GreenMM corrects two errors at the same time regardless of the error patterns. Also, it corrects any number of errors which may happen in the same row or column.

#### **Algorithm 3** Column checksum update for A(m \* k)

```

1: for j = 0, 1, ..., k - 1 do

2: for i = 0, 1, ..., m - 1 do

3: ColChk_{v1}[j] = \sum_{i=0}^{m-1} V_1[i] * A[i][j]

4: ColChk_{v2}[j] = \sum_{i=0}^{m-1} V_2[i] * A[i][j]

5: end for

6: end for

```

As shown in algorithm 5, online FT-cuBLAS-MM algorithm consists of following steps:

- 1. Move input matrices to the GPU using cudaMemCpy API.

- 2. Generate checksum weights vectors in the CPU and move them to the GPU. The weights are generated according to algorithm 2. Due to frequent accesses to weights vector in GPU, to get peak performance, pitched device memory is allocated using cudaMallocPitch API that allocates linear memory space for better efficiency in terms of performance and power.

- 3. Divide input matrices into blocks given the number of faults and do MM without checksums.

- 4. Invoke cuBLAS-MM to update column checksum for each block according to algorithm 3.

```

Algorithm 4 Row checksum update for B(k * n)

```

```

1: for i = 0, 1, ..., k - 1 do

2: for j = 0, 1, ..., n - 1 do

3: RowChk_{v1}[i] = \sum_{j=0}^{n-1} V1[j] * B[i][j]

4: RowChk_{v2}[i] = \sum_{j=0}^{n-1} V2[j] * B[i][j]

5: end for

6: end for

```

#### Algorithm 5 Pseudo-code for online FT-cuBLAS-MM

```

1: Initialization

NB = N (Matrix Size) / B (Block Size)

2: for i = 1, ..., NB do

A_B, B_B \to GPU

3:

Update C_B \rightarrow \text{cuBLAS-MM}(A_B, B_B, C_B)

4:

Update A_B{}^c \rightarrow \text{cuBLAS-MM}(A_B, ColChk_v, A_B^c)

5:

6:

Update C_B^c \to \text{cuBLAS-MM}(A_B^c, B_B, C_B^c)

Update B_B^r \to \text{cuBLAS-MM}(B_B, RowChk_v, B_B^r)

7:

Update C_B^r \to \text{cuBLAS-MM}(A_B, B_B^r, C_B^r)

8:

Recalculate \rightarrow C_B-ColChk2

9:

while C_B-ColChk1 \neq C_B-ColChk2 do

10:

Do Correction

11:

end while

12:

Recalculate \rightarrow

C_B_RowChk2

13:

while C_B-RowChk1 \neq C_B-RowChk2 do

14:

Do Correction

15:

end while

16:

Update C

17:

18: end for

19: C \to CPU

```

- 5. Invoke cuBLAS-MM to update C

- 6. Invoke cuBLAS-MM to update row checksum of B given the equations described in algorithm 4.

- 7. Update row checksum of C by invoking cuBLAS-MM

- 8. Recalculate column and row checksums of C by invoking a simple kernel which adds elements of the result matrix.

- 9. Compare recalculated checksums and old checksums to locate the potential error. Any potential errors can be located by comparing the column and the row checksums. Since computers do floating point calculations in finite precision, the checksum relationship can not hold exactly due to round-off errors. So, we need a threshold to distinguish

between round-off errors and computation errors. Too large thresholds may hide the computation errors, while, too small thresholds may interrupt correct computation. In comparison phase, according to [99],  $e^{-10}$  has been chosen as a conservative threshold to distinguish between round-off and computation errors.

10. Correct any potential errors according to equation 2.6

#### 2.3 Evaluation

#### 2.3.1 Experimental Setup

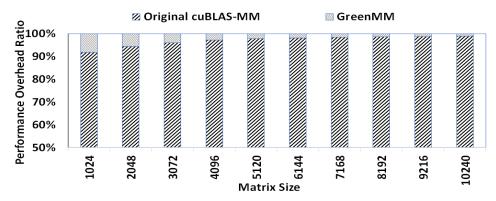

All experiments are performed on NVIDIA GTX 980, the architectural specifications can be found in Table 2.2. Given the limited memory size of the GPU, we were able to evaluate the results for up to a matrix size of 10K. We reduced nominal voltage of the GPU in step sizes of 10 - 12mV until the V<sub>OSCrashpoint</sub> using the MSI After Burner [46]. By decreasing the target power limit of the GPU, we can enforce specific operating voltage. We use NVIDIA System Management Interface (Nvidia-smi), a widely used command line utility on top of NVIDIA Management Library (NVML), to measure power consumption of the GPU at 10ms intervals. Some important commands on power management in NVIDIA GPUs are shown in Table 2.1. The execution times of cuBLAS-MM and FT-cuBLAS-MM are shown in Figure 2.10. The overhead of fault tolerance is large for small matrices, however, the overhead decreases with increase in the matrix size. For small matrices, there is 8% performance overhead, while in case of bigger matrices (10K), performance overhead of FT-cuBLAS-MM comes down to 1.5%.

There is no need for fault tolerance till  $V_{min}$  as the probability of error occurrence is zero. The detection phase is activated when undervolting beyond  $V_{min}$  to detect potential errors, however, the correction phase is activated only if an error is detected in the detection phase. The detection phase accounts for majority of the overhead in the FT-cuBLAS-MM. For instance, when the matrix size is 10K, the detection phase takes 139ms while the correction phase takes only 0.24ms, which means the number of faults to be corrected has low impact on the performance. In case of 10K matrix size, the maximum number of faults we need to tolerate is 1.2 as shown in Figure 2.8; which can be handled by offline FT-cuBLAS-MM. Offline FT-cuBLAS-MM is a special case of online FT-cuBLAS-MM when the number of faults is less than or equal to 2. Here, the block size is the same as the matrix size.

#### 2.3.2 Performance and Energy Saving Evaluation of FT-cuBLAS-MM

When the matrix size increases, the failure rate remains the same. However, the number of errors increases. To evaluate the overhead of FT-cuBLAS-MM, faults are injected directly into partial sum results at random locations and in random iterations according to fault model described in Section 2.1. Fault injection in a controlled manner emulates the impact of hardware transient faults on MM computation. We observed errors in the

Table 2.1: Power management commands using the NVML library

| Command                           | Description                                                                                 |

|-----------------------------------|---------------------------------------------------------------------------------------------|

| nvmlDeviceGetPowerUsage           | Retrieves power usage for the GPU and its associated circuitry in milliwatts                |

| nvmlDeviceSetPersistenceMode      | Enables persistent mode to prevent driver from unloading                                    |

| nvmlDeviceSetPowerManagementLimit | Sets new power limit for the device                                                         |

| nvmlDeviceSetApplicationsClocks   | Sets clocks that applications will lock to                                                  |

| Accuracy                          | Power Measurement Accuracy & Reading is accurate to within +/- 5% of the current power draw |

Figure 2.10: Performance overhead of matrix multiplication for different matrix sizes in presence of two errors

output, however, they were detected and corrected by the offline or online FT-cuBLAS-MM depending on the size of matrix and the number of faults.

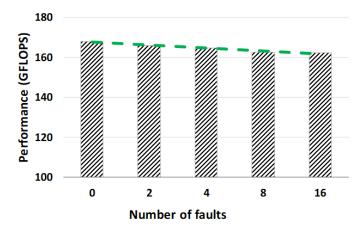

FT-cuBLAS-MM as described in Section 2.2, improves the reliability of computation and tolerates any arbitrary number of faults. This is because, we check correctness of the partial results in each iteration. There is a trade-off between reliability of computation, energy consumption and performance overhead. We measure the performance (GFLOPS) of the cuBLAS-MM and FT-cuBLAS-MM on NVIDIA GTX 980 in the presence of different number of faults for a 10K matrix. Since the actual number of faults at  $V_{safeMin}$  (i.e. 13.95%) undervolting level is 1.2, we evaluate the performance overhead by manually injecting faults

Table 2.2: NVIDIA GTX 980 specifications

| 2048 CUDA-core NVIDIA   |  |

|-------------------------|--|

| Maxwell GeForce GTX 980 |  |

| 4.6  TFLOPs             |  |

| $4~\mathrm{GB~GDDR5}$   |  |

| $1126~\mathrm{MHz}$     |  |

| $1216~\mathrm{MHz}$     |  |

| $7~\mathrm{GHz}$        |  |

| $1.075~\mathrm{V}$      |  |

|                         |  |

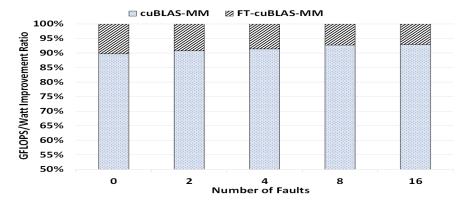

into 10K matrix. Increase in the number of faults results in increased performance overhead, as shown in Figure 2.11. The performance is 165 *GFLOPS* in presence of 2 errors and 162 *GFLOPS* in presence of 16 faults. On average, the performance overhead for different number of faults is 1.5%.

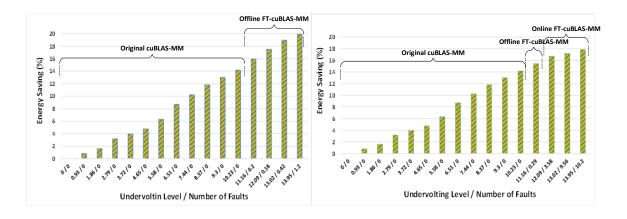

The energy consumption of the GPU is calculated by multiplying power (at each undervolting level) with the execution time of MM. Figure 2.12 shows the energy saving in FT-cuBLAS-MM versus the original cuBLAS-MM in presence of different undervolting levels and number of faults. Since no fault occurs till  $V_{min}$ , fault detection phase is disabled.

The fault detection and correction phases are activated when we undervolt from  $V_{min}$  till  $V_{safeMin}$ . The X-axis denotes the undervolting level and the corresponding number of faults. Figure 2.12 (a) shows the energy saving at different undervolting levels for matrix size of 10K with and without fault tolerance. Undervolting level at  $V_{min}$  for the original cuBLAS-MM is 10.23% without any faults. Undervolting beyond  $V_{min}$  results in faults; and the maximum number of faults is 1.2 at undervolting level of 13.95% as shown in Figure 2.8. So, offline FT-cuBLAS-MM is used to correct the faults. For a matrix of size 10K,

Figure 2.11: Performance evaluation of the FT-cuBLAS-MM