# UC San Diego UC San Diego Electronic Theses and Dissertations

#### Title

D-Band Wafer-Scale IF beamforming Transmit and Receive Phased-Array Systems with On-Chip Antennas

#### Permalink

https://escholarship.org/uc/item/5m69361x

#### Author

Li, Siwei

## **Publication Date**

2021

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

#### D-Band Wafer-Scale IF beamforming Transmit and Receive Phased-Array Systems with On-Chip Antennas

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Siwei Li

Committee in charge:

Professor Gabriel M. Rebeiz, Chair Professor Kam Arnold Professor Gert Cauwenberghs Professor Drew Hall Professor Tzu-Chien Hsueh

2021

Copyright Siwei Li, 2021 All rights reserved. The dissertation of Siwei Li is approved, and it is acceptable in quality and form for publication on microfilm and electronically.

University of California San Diego

2021

## DEDICATION

To my beloved family and friends

#### EPIGRAPH

The people, and the people alone, are the motive force in the making of world

history.

-Chairman Mao

#### TABLE OF CONTENTS

| proval Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| xvii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Dissertation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ntroduction1.1140 GHz.2140 GHz Phased-Array Systems2.3140 GHz Beamforming Architecture5.4Challenges in D-band Power Amplifiers6.5Thesis Overview7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| An Eight-Element 140-GHz Wafer-Scale IF Beamforming Phased-Array<br>Receiver with 64-QAM Operation in CMOS RFSOI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.3       High-Efficiency On-Chip Differential Patch Antenna On Quartz Superstrate       13         2.4       Ultra Low-Noise RF Front-End Design       17         2.4.1       Device Optimization       17         2.4.2       Capacitive Neutralization Technique       18         2.4.3       Equivalent Noise Model       20         2.4.4       LNA       23         2.4.5       Mixer       24         2.5       LO Chain, IF Beamformer and Combiner Design       27         2.5.1       Channel LO Chain       27         2.5.2       IF Beamformer and Combiner       27         2.6       Phased-array System Analysis       31         2.7       Phased-array Element and System Measurements       33 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| with $32$ dBm Peak EIRP and > 16 Gbps 16QAM and 64QAM Operation473.1Introduction473.2Wafer-Scale Phased-array IF beamforming transmitter architecture493.3140 GHz power amplifier503.3.1Transistor-Level Analysis with Neutralization503.3.2PA Design523.4Other Key Circuit Blocks Design553.4.1Upconversion Mixer553.4.2Image Rejection Filter563.4.3IF VGA with Wideband Input Matching593.4.4Other System Blocks593.5Phased-Array Tx System Analysis603.6Phased-Array Tx Channel Measurements623.7Phased-Array Measurements663.7.2Array EIRP and Linearity693.7.3Array LIC Leakage703.7.4Communication-links713.8Conclusion743.9Acknowledgment774.1Introduction774.1Introduction774.1Introduction774.1Introduction774.3Eight-way Common-Source Power Combined PA884.3.3Eight-way Cascede Power Combined PA844.3.4Eight-Way Cascede Power Combined PA894.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                         |           |      | 2.7.1 Receive Electronic Gain and Pattern                            | 4 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|----------------------------------------------------------------------|---|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |      |                                                                      | 8 |

| 2.9Appendix I422.10Appendix II452.11Acknowledgment452.11Acknowledgment45Chapter 3An Eight-Element 136-147 GHz Wafer-Scale Phased-Array Transmitterwith 32 dBm Peak EIRP and > 16 Gbps 16QAM and 64QAM Operation473.1Introduction473.2Wafer-Scale Phased-array IF beamforming transmitter architecture493.3140 GHz power amplifier503.3.1Transistor-Level Analysis with Neutralization503.3.2PA Design523.4Other Key Circuit Blocks Design553.4.1Upconversion Mixer553.4.2Image Rejection Filter563.4.3IF VGA with Wideband Input Matching593.5Phased-Array Tx System Analysis603.6Phased-Array Tx System Analysis603.6Phased-Array Tx Channel Measurements623.7Phased-Array Tx Channel Measurements623.7.1Transmit Electronic Gain and Patterns663.7.2Array EIRP and Linearity693.7.3Array Lo Leakage703.7.4Communication-links713.8Conclusion774.1Introduction774.2Technology804.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-Way Coscode Power Combined PA844.3.4PA Simulations92 </td <td></td> <td></td> <td>8</td>                                                                                                                                                                            |           |      |                                                                      | 8 |

| 2.9Appendix I422.10Appendix II452.11Acknowledgment452.11Acknowledgment45Chapter 3An Eight-Element 136-147 GHz Wafer-Scale Phased-Array Transmitterwith 32 dBm Peak EIRP and > 16 Gbps 16QAM and 64QAM Operation473.1Introduction473.2Wafer-Scale Phased-array IF beamforming transmitter architecture493.3140 GHz power amplifier503.3.1Transistor-Level Analysis with Neutralization503.3.2PA Design523.4Other Key Circuit Blocks Design553.4.1Upconversion Mixer553.4.2Image Rejection Filter563.4.3IF VGA with Wideband Input Matching593.5Phased-Array Tx System Analysis603.6Phased-Array Tx System Analysis603.6Phased-Array Tx Channel Measurements623.7.1Transmit Electronic Gain and Patterns663.7.2Array EIRP and Linearity693.7.3Array LO Leakage703.7.4Communication-links713.8Conclusion774.1Introduction774.2Technology804.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-Way Coscode Power Combined PA844.3.3Eight-Way Cascode Power Combined PA844.3.4PA Simulations93<                                                                                                                                                                                                              |           | 2.8  | Conclusion                                                           | 1 |

| 2.10Appendix II452.11Acknowledgment45Chapter 3An Eight-Element 136-147 GHz Wafer-Scale Phased-Array Transmitter<br>with 32 dBm Peak EIRP and > 16 Gbps 16QAM and 64QAM Operation473.1Introduction473.2Wafer-Scale Phased-array IF beamforming transmitter architecture493.3140 GHz power amplifier503.3.1Transistor-Level Analysis with Neutralization503.3.2PA Design523.4Other Key Circuit Blocks Design553.4.1Upconversion Mixer553.4.2Image Rejection Filter563.4.3IF VGA with Wideband Input Matching593.4Other System Blocks593.5Phased-Array Tx System Analysis603.6Phased-Array Tx System Analysis603.7Phased-Array Tx Channel Measurements623.7.1Transmit Electronic Gain and Patterns663.7.2Array LQ Leakage703.7.3Array LQ Leakage713.8Conclusion743.9Acknowledgment75Chapter 4D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and<br>12% Peak PAE in 45-nm CMOS RFSOI774.1Introduction774.2Technology804.3Leight-way Common-Source Power Combined PA844.3.2Eight-Way Cascode Power Combined PA864.3.4PA Simulations924.4Small Signal Measurements93 </td <td></td> <td>2.9</td> <td>Appendix I</td> <td>2</td>                                                                                            |           | 2.9  | Appendix I                                                           | 2 |

| 2.11Ar.45Chapter 3An Eight-Element 136-147 GHz Wafer-Scale Phased-Array Transmitter<br>with 32 dBm Peak EIRP and > 16 Gbps 16QAM and 64QAM Operation<br>3.1473.1Introduction473.2Wafer-Scale Phased-array IF beamforming transmitter architecture493.3140 GHz power amplifier503.3.1Transistor-Level Analysis with Neutralization503.3.2PA Design523.4Other Key Circuit Blocks Design553.4.1Upconversion Mixer553.4.2Image Rejection Filter563.4.3IF VGA with Wideband Input Matching593.4Other System Blocks593.5Phased-Array Tx System Analysis603.6Phased-Array Tx Channel Measurements623.7Phased-Array Tx Channel Measurements623.7.1Transmit Electronic Gain and Patterns663.7.2Array EIRP and Linearity693.7.3Array LO Leakage703.7.4Communication-links713.8Conclusion743.9Acknowledgment774.1Introduction774.2Technology804.3Eight-Way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA844.3.4PA Simulations924.4.1Small Signal Measurements93                                                                                                                                                                                                                                                  |           | 2.10 | **                                                                   | 5 |

| with $32$ dBm Peak EIRP and > 16 Gbps 16QAM and 64QAM Operation473.1Introduction473.2Wafer-Scale Phased-array IF beamforming transmitter architecture493.3140 GHz power amplifier503.3.1Transistor-Level Analysis with Neutralization503.3.2PA Design523.4Other Key Circuit Blocks Design553.4.1Upconversion Mixer553.4.2Image Rejection Filter563.4.3IF VGA with Wideband Input Matching593.4.4Other System Blocks593.5Phased-Array Tx System Analysis603.6Phased-Array Tx Channel Measurements623.7Phased-Array Measurements663.7.2Array EIRP and Linearity693.7.3Array LIC Leakage703.7.4Communication-links713.8Conclusion743.9Acknowledgment774.1Introduction774.1Introduction774.1Introduction774.1Introduction774.3Eight-way Common-Source Power Combined PA884.3.3Eight-way Cascede Power Combined PA844.3.4Eight-Way Cascede Power Combined PA894.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                         |           |      | 11                                                                   |   |

| 3.1       Introduction       47         3.2       Wafer-Scale Phased-array IF beamforming transmitter architecture       49         3.3       140 GHz power amplifier       50         3.3.1       Transistor-Level Analysis with Neutralization       50         3.3.2       PA Design       52         3.4       Other Key Circuit Blocks Design       55         3.4.1       Upconversion Mixer       55         3.4.2       Image Rejection Filter       56         3.4.3       IF VGA with Wideband Input Matching       59         3.4.4       Other System Blocks       59         3.5       Phased-Array Tx System Analysis       60         3.6       Phased-Array Tx System Analysis       60         3.7       Phased-Array Measurements       62         3.7       Phased-array Measurements       66         3.7.1       Transmit Electronic Gain and Patterns       66         3.7.2       Array LO Leakage       70         3.7.4       Communication-links       71         3.8       Conclusion       74         3.9       Acknowledgment       77         4.1       Introduction       77         4.1       Introduction       77                                                                               | Chapter 3 | An H | Eight-Element 136-147 GHz Wafer-Scale Phased-Array Transmitter       |   |

| 3.2       Wafer-Scale Phased-array IF beamforming transmitter architecture       49         3.3       140 GHz power amplifier       50         3.3.1       Transistor-Level Analysis with Neutralization       50         3.3.2       PA Design       52         3.4       Other Key Circuit Blocks Design       55         3.4.1       Upconversion Mixer       56         3.4.2       Image Rejection Filter       56         3.4.3       IF VGA with Wideband Input Matching       59         3.4.4       Other System Blocks       59         3.5       Phased-Array Tx System Analysis       60         3.6       Phased-Array Tx Channel Measurements       62         3.7       Phased-array Measurements       66         3.7.1       Transmit Electronic Gain and Patterns       66         3.7.2       Array EIRP and Linearity       69         3.7.3       Array LO Leakage       70         3.7.4       Communication-links       71         3.8       Conclusion       74         3.9       Acknowledgment       75         Chapter 4       D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and       12% Peak PAE in 45-nm CMOS RFSOI       77         4.1       Introduction<                         |           | with | 32 dBm Peak EIRP and > 16 Gbps 16QAM and 64QAM Operation 4           | 7 |

| 3.3       140 GHz power amplifier       50         3.3.1       Transistor-Level Analysis with Neutralization       50         3.3.2       PA Design       52         3.4       Other Key Circuit Blocks Design       55         3.4.1       Upconversion Mixer       56         3.4.2       Image Rejection Filter       56         3.4.3       IF VGA with Wideband Input Matching       59         3.4.4       Other System Blocks       59         3.5       Phased-Array Tx System Analysis       60         3.6       Phased-Array Tx Channel Measurements       62         3.7       Phased-array Measurements       66         3.7.1       Transmit Electronic Gain and Patterns       66         3.7.2       Array EIRP and Linearity       69         3.7.3       Array IO Leakage       70         3.7.4       Communication-links       71         3.8       Conclusion       74         3.9       Acknowledgment       77         4.1       Introduction       77         4.2       Technology       80         4.3       Design and Analysis       83         4.3.1       Neutralized Transistor Pair Analysis       83                                                                                              |           | 3.1  | Introduction                                                         | 7 |

| 3.3.1       Transistor-Level Analysis with Neutralization       50         3.3.2       PA Design       52         3.4       Other Key Circuit Blocks Design       55         3.4.1       Upconversion Mixer       55         3.4.2       Image Rejection Filter       56         3.4.3       IF VGA with Wideband Input Matching       59         3.4.4       Other System Blocks       59         3.5       Phased-Array Tx System Analysis       60         3.6       Phased-Array Tx Channel Measurements       62         3.7       Phased-array Measurements       65         3.7.1       Transmit Electronic Gain and Patterns       66         3.7.2       Array EIRP and Linearity       69         3.7.3       Array LO Leakage       70         3.7.4       Communication-links       71         3.8       Conclusion       74         3.9       Acknowledgment       75         Chapter 4       D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and       12% Peak PAE in 45-nm CMOS RFSOI       77         4.1       Introduction       77       4.2       Technology       80         4.3       Design and Analysis       83       4.3.1       Neutralized Transistor                                    |           | 3.2  | Wafer-Scale Phased-array IF beamforming transmitter architecture . 4 | 9 |

| 3.3.2       PA Design       52         3.4       Other Key Circuit Blocks Design       55         3.4.1       Upconversion Mixer       55         3.4.2       Image Rejection Filter       56         3.4.3       IF VGA with Wideband Input Matching       59         3.4.4       Other System Blocks       59         3.5       Phased-Array Tx System Analysis       60         3.6       Phased-Array Tx Channel Measurements       62         3.7       Phased-Array Measurements       65         3.7.1       Transmit Electronic Gain and Patterns       66         3.7.2       Array EIRP and Linearity       69         3.7.3       Array LO Leakage       70         3.7.4       Communication-links       71         3.8       Conclusion       74         3.9       Acknowledgment       75         Chapter 4       D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and       12% Peak PAE in 45-nm CMOS RFSOI       77         4.1       Introduction       77       4.1       Introduction       77         4.3       Design and Analysis       83       4.3.1       83       4.3.2       83         4.3.3       Eight-way Cosmono-Source Power Combined PA<                                            |           | 3.3  | 140 GHz power amplifier                                              | 0 |

| 3.4       Other Key Circuit Blocks Design       55         3.4.1       Upconversion Mixer       55         3.4.2       Image Rejection Filter       56         3.4.3       IF VGA with Wideband Input Matching       59         3.4.4       Other System Blocks       59         3.5       Phased-Array Tx System Analysis       60         3.6       Phased-Array Tx Channel Measurements       62         3.7       Phased-array Measurements       62         3.7.1       Transmit Electronic Gain and Patterns       66         3.7.2       Array EIRP and Linearity       69         3.7.3       Array LO Leakage       70         3.7.4       Communication-links       71         3.8       Conclusion       74         3.9       Acknowledgment       75         Chapter 4       D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and       12% Peak PAE in 45-nm CMOS RFSOI       77         4.1       Introduction       77       74       1       Introduction       77         4.3       Design and Analysis       83       4.3.1       Neutralized Transistor Pair Analysis       83         4.3.1       Neutralized Transistor Pair Analysis       84       4.3.3       Eight-                           |           |      | 3.3.1 Transistor-Level Analysis with Neutralization                  | 0 |

| 3.4.1       Upconversion Mixer       55         3.4.2       Image Rejection Filter       56         3.4.3       IF VGA with Wideband Input Matching       59         3.4.4       Other System Blocks       59         3.5       Phased-Array Tx System Analysis       60         3.6       Phased-Array Tx Channel Measurements       62         3.7       Phased-array Measurements       65         3.7.1       Transmit Electronic Gain and Patterns       66         3.7.2       Array LO Leakage       70         3.7.4       Communication-links       71         3.8       Conclusion       74         3.9       Acknowledgment       75         Chapter 4       D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and       12% Peak PAE in 45-nm CMOS RFSOI       77         4.1       Introduction       77       83       4.3.1       Neutralized Transistor Pair Analysis       83         4.3       Design and Analysis       83       83       4.3.2       Eight-way Common-Source Power Combined PA       84         4.3.3       Eight-Way Cascode Power Combined PA       86       4.3.4       PA Simulations       93         4.4.1       Small Signal Measurements       93       93                  |           |      | 3.3.2 PA Design                                                      | 2 |

| 3.4.2       Image Rejection Filter       56         3.4.3       IF VGA with Wideband Input Matching       59         3.4.4       Other System Blocks       59         3.5       Phased-Array Tx System Analysis       60         3.6       Phased-Array Tx Channel Measurements       62         3.7       Phased-array Measurements       65         3.7.1       Transmit Electronic Gain and Patterns       66         3.7.2       Array EIRP and Linearity       69         3.7.3       Array LO Leakage       70         3.7.4       Communication-links       71         3.8       Conclusion       74         3.9       Acknowledgment       75         Chapter 4       D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and       12% Peak PAE in 45-nm CMOS RFSOI       77         4.1       Introduction       77       4.2       Technology       80         4.3       Design and Analysis       83       4.3.1       Neutralized Transistor Pair Analysis       83         4.3.1       Neutralized Transistor Pair Analysis       83       4.3.2       Eight-way Common-Source Power Combined PA       84         4.3.3       Eight-Way Cascode Power Combined PA       86       4.3.4       PA Simulations |           | 3.4  | Other Key Circuit Blocks Design                                      | 5 |

| 3.4.3IF VGA with Wideband Input Matching593.4.4Other System Blocks593.5Phased-Array Tx System Analysis603.6Phased-Array Tx Channel Measurements623.7Phased-array Measurements653.7.1Transmit Electronic Gain and Patterns663.7.2Array EIRP and Linearity693.7.3Array LO Leakage703.7.4Communication-links713.8Conclusion743.9Acknowledgment75Chapter 4D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and<br>12% Peak PAE in 45-nm CMOS RFSOI774.1Introduction774.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |      | 3.4.1 Upconversion Mixer                                             | 5 |

| 3.4.3IF VGA with Wideband Input Matching593.4.4Other System Blocks593.5Phased-Array Tx System Analysis603.6Phased-Array Tx Channel Measurements623.7Phased-array Measurements653.7.1Transmit Electronic Gain and Patterns663.7.2Array EIRP and Linearity693.7.3Array LO Leakage703.7.4Communication-links713.8Conclusion743.9Acknowledgment75Chapter 4D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and<br>12% Peak PAE in 45-nm CMOS RFSOI774.1Introduction774.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |      | 3.4.2 Image Rejection Filter                                         | 6 |

| 3.5Phased-Array Tx System Analysis603.6Phased-Array Tx Channel Measurements623.7Phased-array Measurements653.7.1Transmit Electronic Gain and Patterns663.7.2Array EIRP and Linearity693.7.3Array LO Leakage703.7.4Communication-links713.8Conclusion743.9Acknowledgment75Chapter 4D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and774.1Introduction774.2Technology804.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |      |                                                                      | 9 |

| 3.6Phased-Array Tx Channel Measurements623.7Phased-array Measurements653.7.1Transmit Electronic Gain and Patterns663.7.2Array EIRP and Linearity693.7.3Array LO Leakage703.7.4Communication-links713.8Conclusion743.9Acknowledgment75Chapter 4D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and<br>12% Peak PAE in 45-nm CMOS RFSOI774.1Introduction774.2Technology804.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |      | 3.4.4 Other System Blocks                                            | 9 |

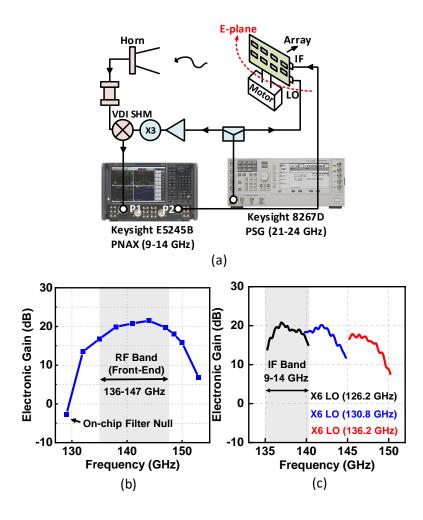

| 3.7Phased-array Measurements653.7.1Transmit Electronic Gain and Patterns663.7.2Array EIRP and Linearity693.7.3Array LO Leakage703.7.4Communication-links713.8Conclusion743.9Acknowledgment75Chapter 4D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and774.1Introduction774.1Introduction774.2Technology804.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | 3.5  | Phased-Array Tx System Analysis                                      | 0 |

| 3.7Phased-array Measurements653.7.1Transmit Electronic Gain and Patterns663.7.2Array EIRP and Linearity693.7.3Array LO Leakage703.7.4Communication-links713.8Conclusion743.9Acknowledgment75Chapter 4D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and774.1Introduction774.1Introduction774.2Technology804.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | 3.6  | Phased-Array Tx Channel Measurements                                 | 2 |

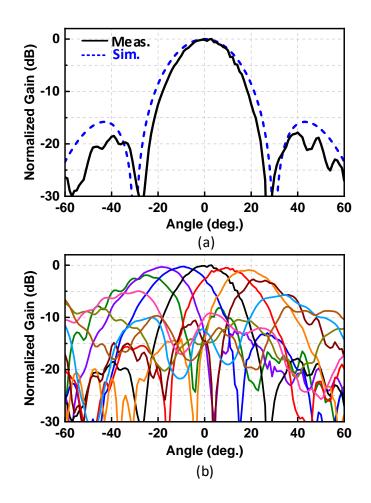

| 3.7.1Transmit Electronic Gain and Patterns663.7.2Array EIRP and Linearity693.7.3Array LO Leakage703.7.4Communication-links713.8Conclusion743.9Acknowledgment75Chapter 4D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and774.1Introduction774.2Technology804.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | 3.7  |                                                                      | 5 |

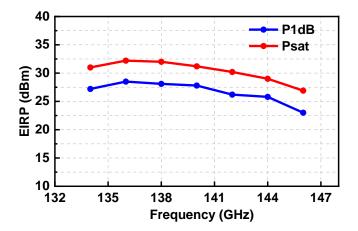

| 3.7.2Array EIRP and Linearity693.7.3Array LO Leakage703.7.4Communication-links713.8Conclusion743.9Acknowledgment75Chapter 4D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and7712% Peak PAE in 45-nm CMOS RFSOI774.1Introduction774.2Technology804.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |      |                                                                      | 6 |

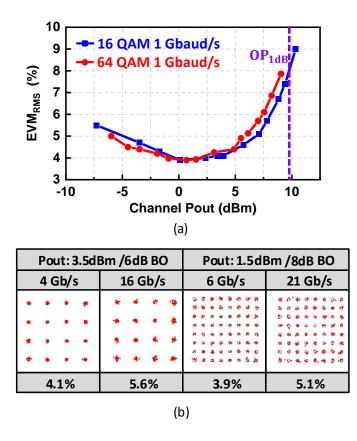

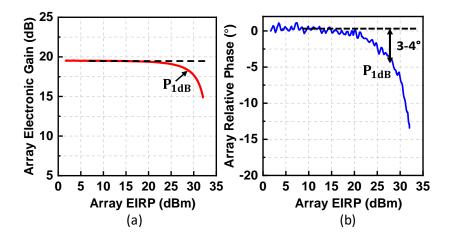

| 3.7.3Array LO Leakage703.7.4Communication-links713.8Conclusion743.9Acknowledgment75Chapter 4D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and75Chapter 4D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and774.1Introduction774.1Introduction774.2Technology804.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |      |                                                                      | 9 |

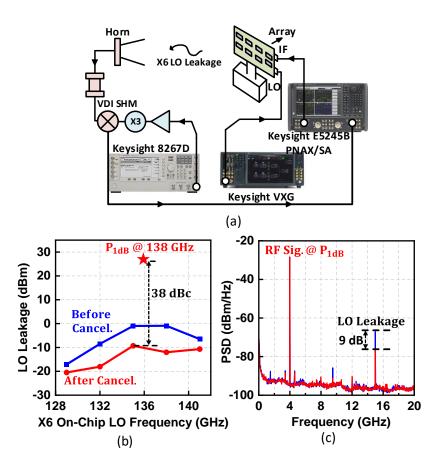

| 3.7.4Communication-links713.8Conclusion743.9Acknowledgment75Chapter 4D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and<br>12% Peak PAE in 45-nm CMOS RFSOI774.1Introduction774.2Technology804.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |      |                                                                      | 0 |

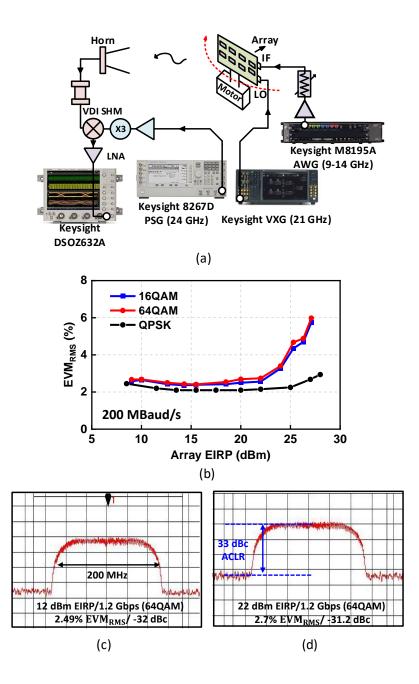

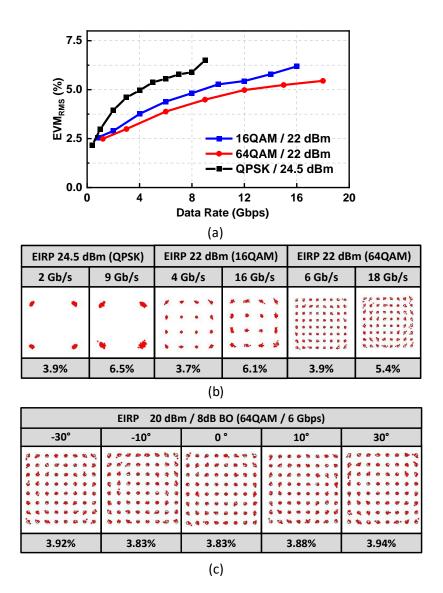

| 3.8Conclusion743.9Acknowledgment75Chapter 4D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and<br>12% Peak PAE in 45-nm CMOS RFSOI774.1Introduction774.2Technology804.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |      |                                                                      | 1 |

| 3.9Acknowledgment75Chapter 4D-Band Multi-Way Power Combined Amplifiers with 19-dBm Psat and<br>12% Peak PAE in 45-nm CMOS RFSOI774.1Introduction774.2Technology804.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | 3.8  |                                                                      | 4 |

| 12% Peak PAE in 45-nm CMOS RFSOI774.1 Introduction774.2 Technology804.3 Design and Analysis834.3.1 Neutralized Transistor Pair Analysis834.3.2 Eight-way Common-Source Power Combined PA844.3.3 Eight-Way Cascode Power Combined PA864.3.4 PA Simulations924.4 Measurements934.4.1 Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | 3.9  |                                                                      |   |

| 12% Peak PAE in 45-nm CMOS RFSOI774.1 Introduction774.2 Technology804.3 Design and Analysis834.3.1 Neutralized Transistor Pair Analysis834.3.2 Eight-way Common-Source Power Combined PA844.3.3 Eight-Way Cascode Power Combined PA864.3.4 PA Simulations924.4 Measurements934.4.1 Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Chapter 4 | D-Ba | and Multi-Way Power Combined Amplifiers with 19-dBm Psat and         |   |

| 4.2Technology804.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ĩ         |      | • 1                                                                  | 7 |

| 4.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | 4.1  | Introduction                                                         | 7 |

| 4.3Design and Analysis834.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | 4.2  | Technology                                                           | 0 |

| 4.3.1Neutralized Transistor Pair Analysis834.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           | 4.3  |                                                                      | 3 |

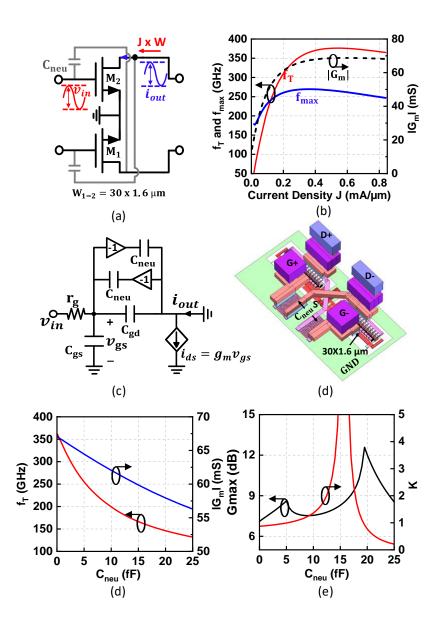

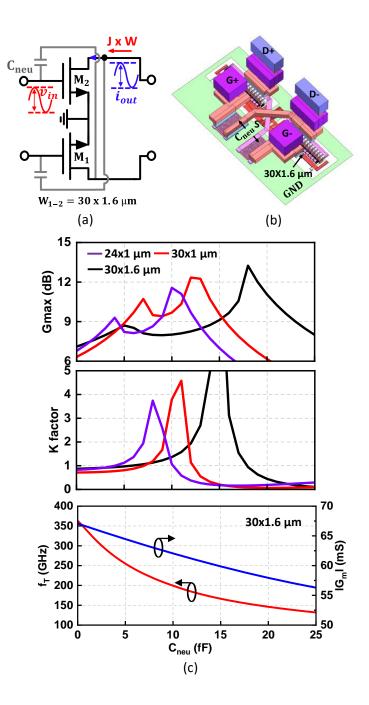

| 4.3.2Eight-way Common-Source Power Combined PA844.3.3Eight-Way Cascode Power Combined PA864.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |      | e i                                                                  |   |

| 4.3.3 Eight-Way Cascode Power Combined PA864.3.4 PA Simulations924.4 Measurements934.4.1 Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |      | -                                                                    | 4 |

| 4.3.4PA Simulations924.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |      |                                                                      |   |

| 4.4Measurements934.4.1Small Signal Measurements93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |      |                                                                      |   |

| 4.4.1 Small Signal Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           | 4.4  |                                                                      |   |

| e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           | -    |                                                                      |   |

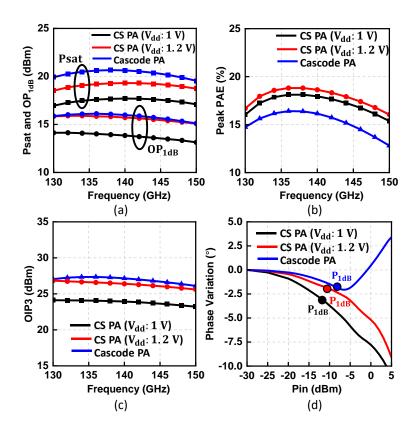

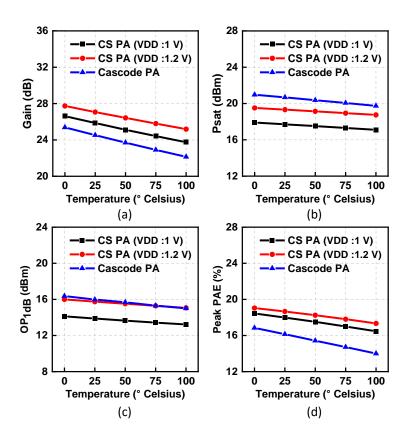

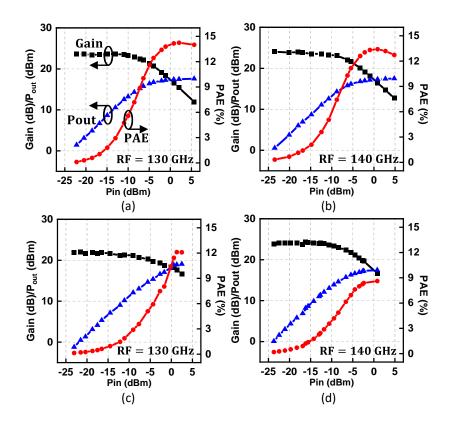

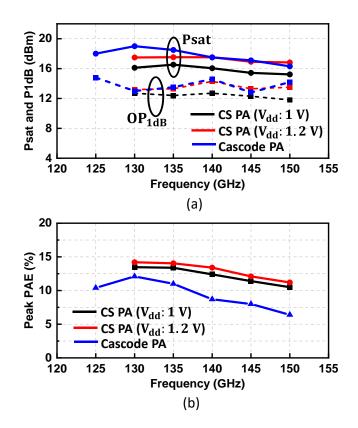

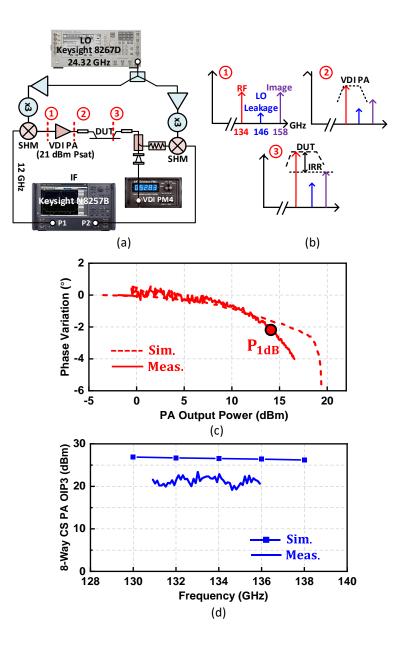

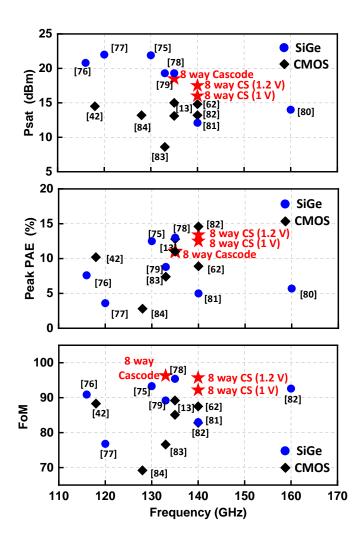

| 4.4.2 Large Signal Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |      | e                                                                    |   |

| 4.5 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | 4.5  | 6 6                                                                  |   |

|              | 4.6  | Acknowledgment         | <br>• | • | <br>• | • | <br>• | • | • | • | • | • | • | • | <br>• | • | • | 103 |

|--------------|------|------------------------|-------|---|-------|---|-------|---|---|---|---|---|---|---|-------|---|---|-----|

| Chapter 5    | Conc | lusion and Future Work |       |   |       |   |       | • |   | • | • | • |   |   | <br>• | • |   | 104 |

|              | 5.1  | Dissertation Summary   | <br>• |   |       | • |       |   |   |   | • |   |   |   | <br>• | • |   | 104 |

|              | 5.2  | Future Work            | <br>• | • | <br>• | • |       | • |   | • | • | • | • | • |       | • | • | 106 |

| Bibliography |      |                        | <br>• |   |       | • | <br>• | • |   | • | • | • | • | • |       |   | • | 108 |

#### LIST OF FIGURES

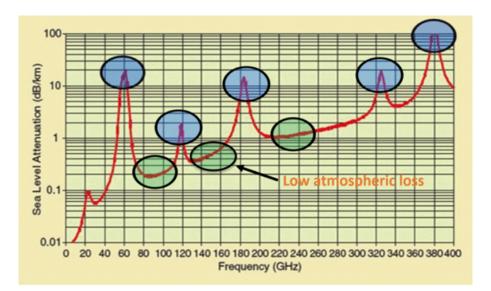

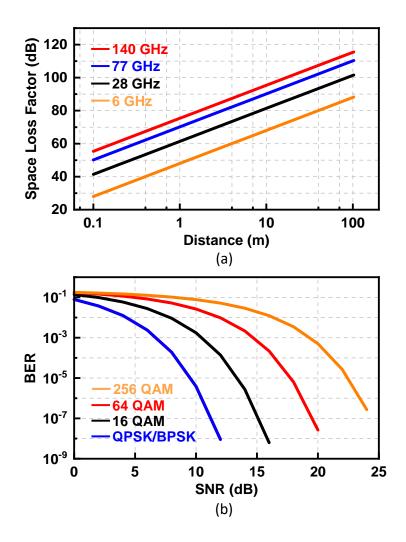

| Figure 1.1:<br>Figure 1.2: | Atmospheric absorption of electromagnetic waves                                                                                                                                                                                                | 2        |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

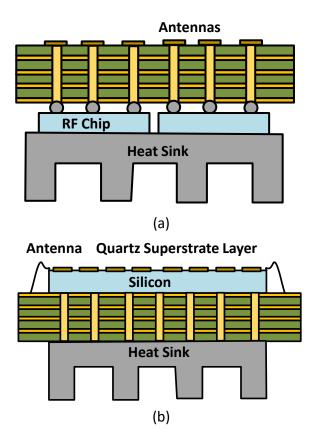

| Figure 1.3:                | <ul><li>(a) Phased-array systems with antennas on PCB and chips mounted on PCB</li></ul>                                                                                                                                                       | 3        |

| 119010 1.5.                | directly. (b) Wafer-scale phased-array systems with antennas on quartz<br>superstrate                                                                                                                                                          | 4        |

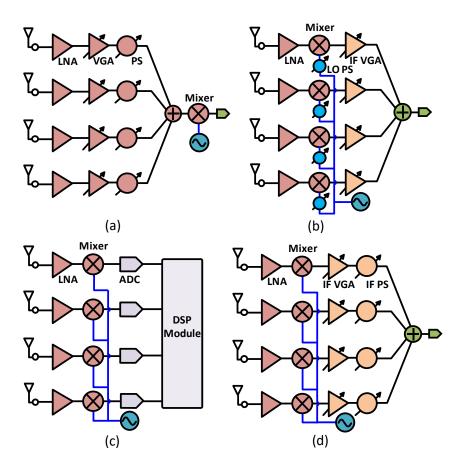

| Figure 1.4:                | Beamforming architectures: (a) RF beamforming, (b) LO beamforming, (c) digital beamforming, (d) high-IF beamforming.                                                                                                                           | 5        |

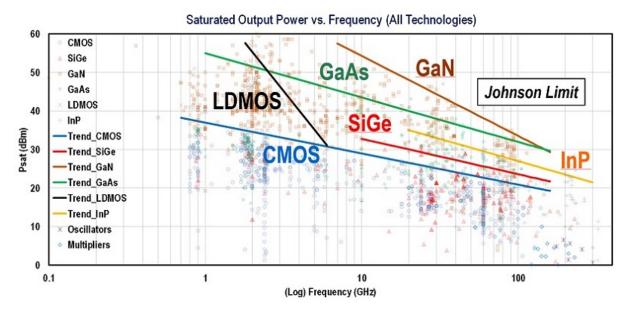

| Figure 1.5:                | Power Amplifiers Performance Survey 2000-Present.                                                                                                                                                                                              | 7        |

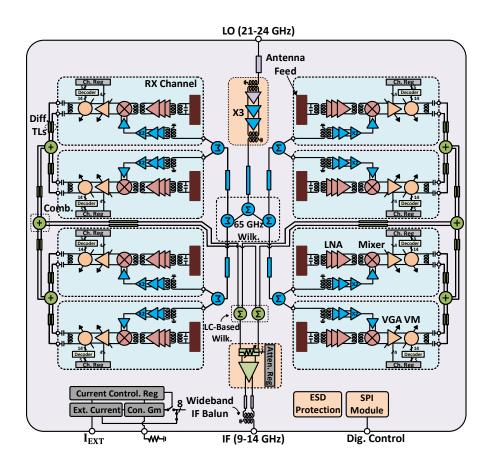

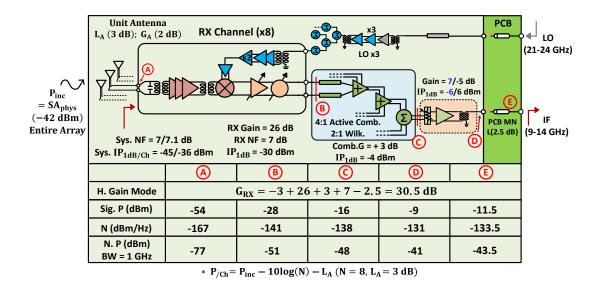

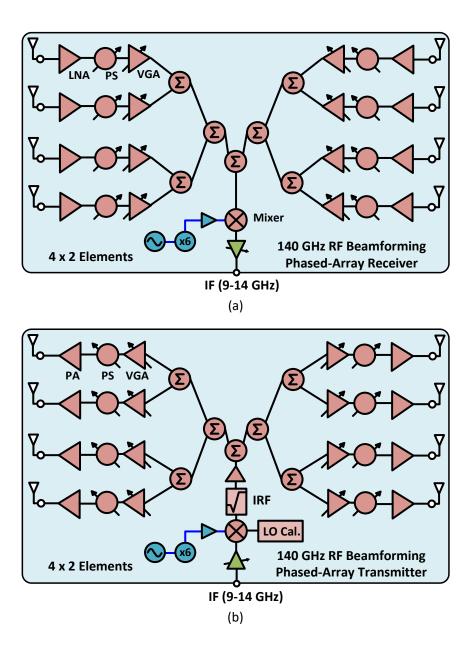

| Figure 2.1:                | Block diagram of 8-element wafer-scale IF beamforming phased array receiver chip at 140 GHz.                                                                                                                                                   | 12       |

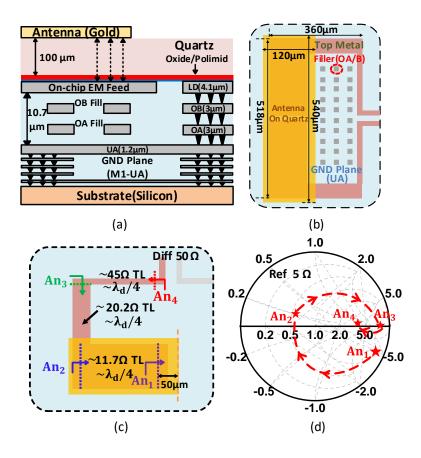

| Figure 2.2:                | (a) On-chip EM-coupled feed stackup and antenna structure. (b) High-<br>efficiency EM-coupled differential patch antenna unit cell. Single-ended<br>representation of the (c) impedance transformation network and (d) that in<br>smith chart. | 14       |

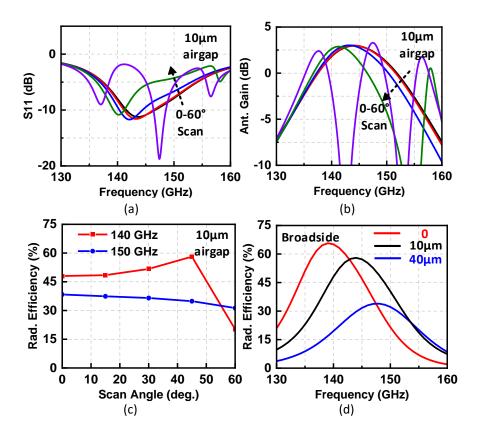

| Figure 2.3:                | Simulated quartz superstrate antenna (a) impedance matching and (b) antenna gain with different scan angles in the $E$ -plane. (c) Simulated antenna radiation efficiency versus scan angle at 140 and 150 GHz. (d) Effect of the air gap      |          |

| E' 0.4                     | between the quartz and the chip (design is optimized for a $10-\mu m$ airgap).                                                                                                                                                                 | 15       |

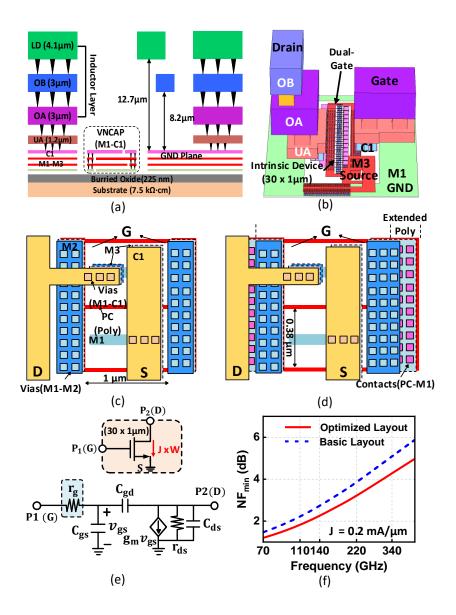

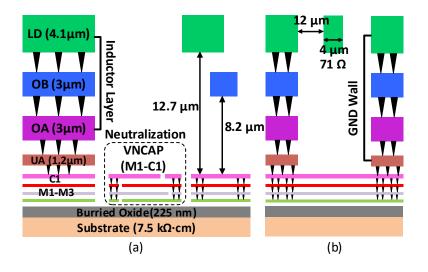

| Figure 2.4:                | Layer stackup in GF45RFSOI and transistor layout and its optimization                                                                                                                                                                          | 16       |

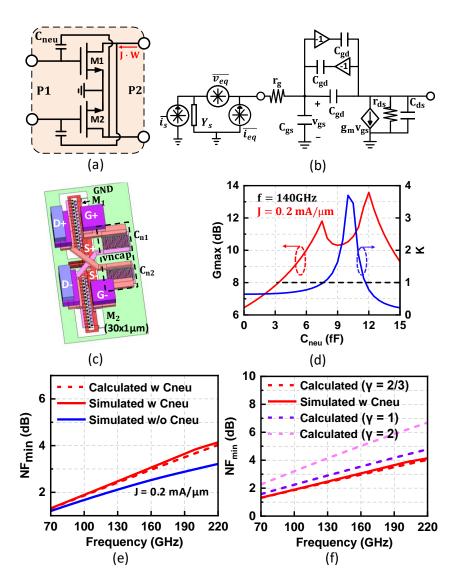

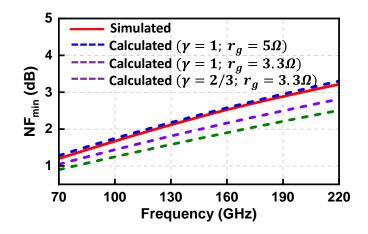

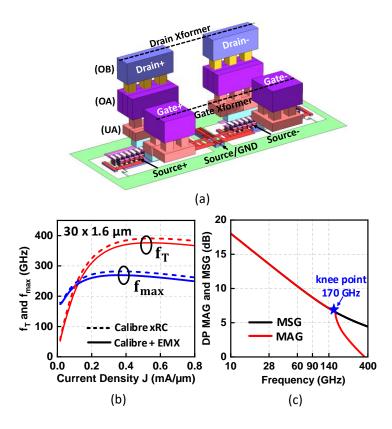

| Figure 2.5:                | Neutralized differential transistor pair model, analysis and simulations                                                                                                                                                                       | 18<br>22 |

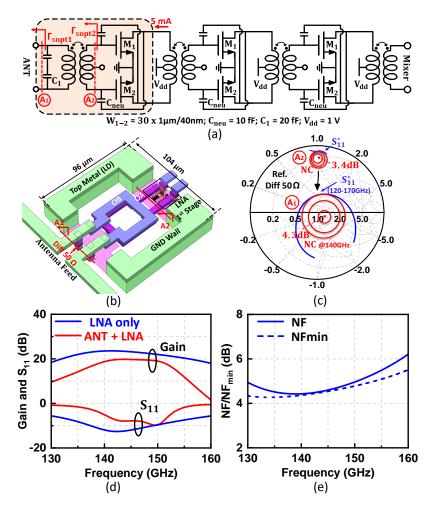

| Figure 2.6:                | Design of 3-stage fully differential transformer coupled LNA                                                                                                                                                                                   | LL       |

| Figure 2.7:                | (a) Single-channel receiver die photo. (b) LNA (test chip with input/output balun for probing) simulated and measured S-parameters. (c) Measured NF                                                                                            | 24       |

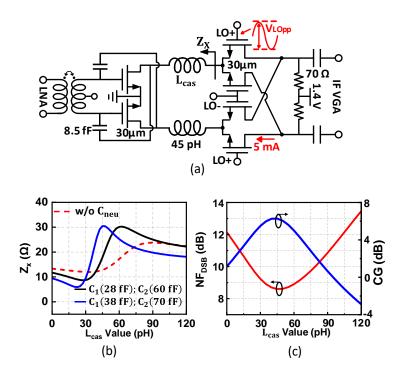

| Figure 2.8:                | for the single-channel receiver                                                                                                                                                                                                                | 24       |

|                            | conversion gain with different $L_{cas}$ values.                                                                                                                                                                                               | 25       |

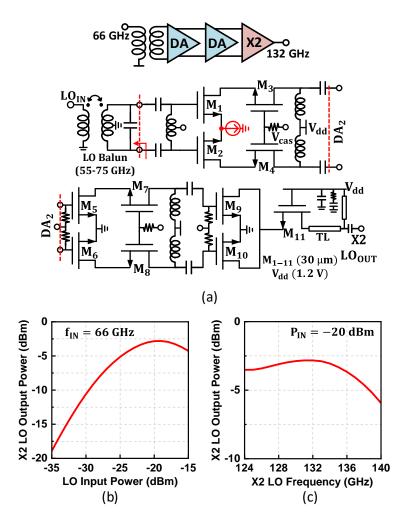

| Figure 2.9:                | (a) Channel LO chain schematic. Simulated LO output power versus (b) input power level and (c) output LO frequency.                                                                                                                            | 26       |

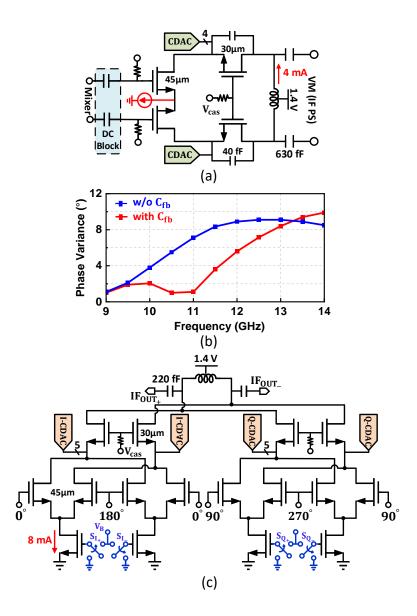

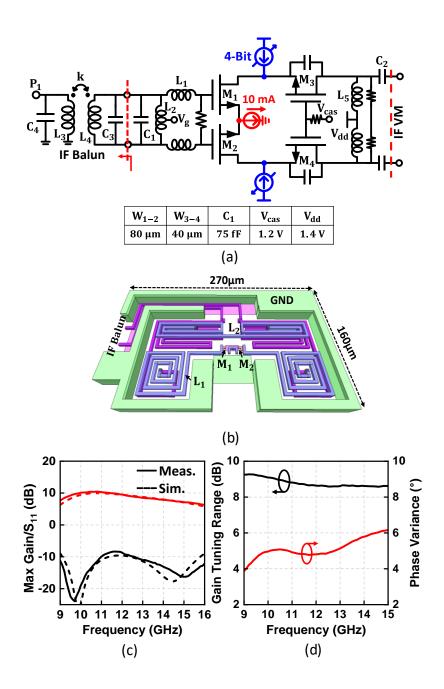

| Figure 2.10:               | (a) Schematic of the IF 4-bit VGA. (b) Simulated VGA maximum phase variance for 10-dB gain control versus frequency. (c) Schematic of the vector                                                                                               |          |

|                            | modulator with 5-bit phase. control.                                                                                                                                                                                                           | 28       |

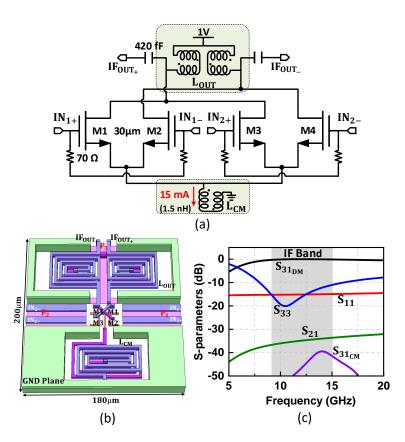

| Figure 2.11:               | Wideband compact active IF combiner (a) schematic, (b) layout EM model and (c) simulated S-parameters.                                                                                                                                         | 29       |

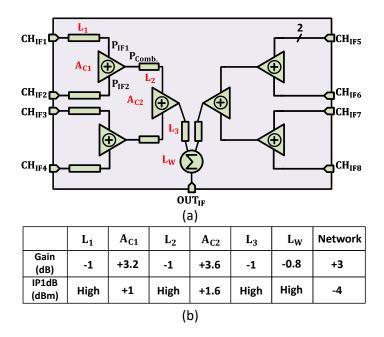

| Figure 2.12.               | IF combiner network: (a) block diagram and (b) gain and linearity perfor-                                                                                                                                                                      |          |

|                            | mance analysis (all ports and transmission lines are differential).                                                                                                                                                                            | 30       |

| Figure 2.13:               | System-level calculation for the 8-element phased-array receiver at $P_{inc} =$                                                                                                                                                                | 20       |

| 6                          | -42 dBm                                                                                                                                                                                                                                        | 31       |

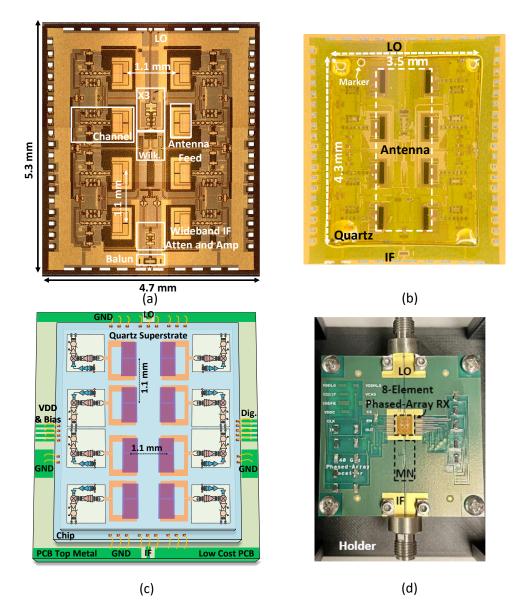

| Figure 2.14:               | (a) 8-element phased-array receiver chip die photo. (b) Receiver chip with antenna and quartz (100 µm thickness superstrate) attached. (c) Block dia-<br>gram of the 140 GHz phased array receiver system assembled on a low-cost PCB. (d) Photograph of the assembled PCB.                                                                                                                      | 33             |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

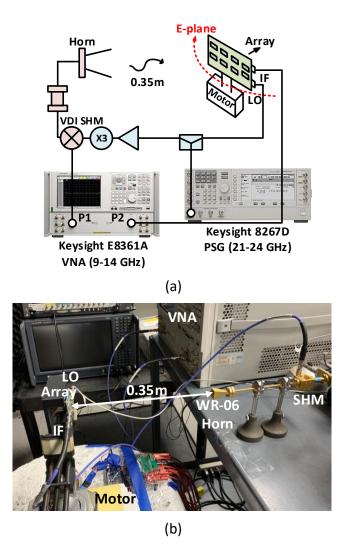

| Figure 2.15:               | (a) Measurement setup for the array small signal. (b) Photograph of the measurement setup.                                                                                                                                                                                                                                                                                                       | 35             |

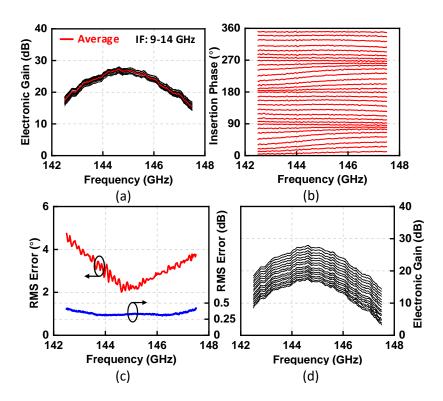

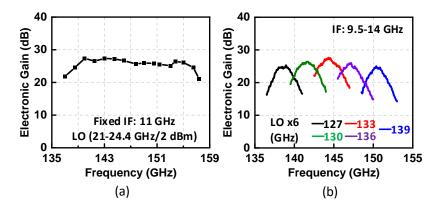

| Figure 2.16:               | Measured 142.5-147.5 GHz element (a) phase states electronic gain, (b) phase states phase, (c) RMS errors and (d) electronic gain states tuned by                                                                                                                                                                                                                                                | 36             |

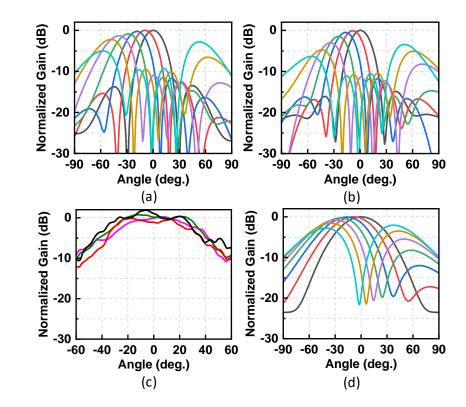

| Figure 2.17:               | 4-bit IF VGA                                                                                                                                                                                                                                                                                                                                                                                     | 36             |

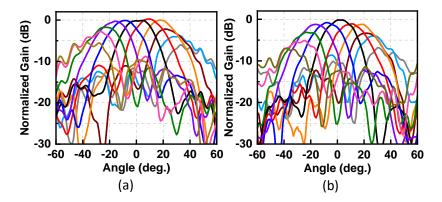

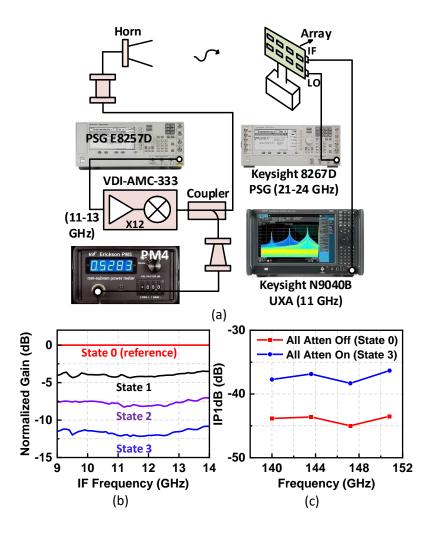

| -                          | Measured $E$ -plane beam patterns at (a) 140 GHz and (b) 150 GHz (a) Measurement setup for the array linearity. (b) Measured 2-bit IF attenuator states normalized gain. (c) Measured array input P1dB with attenuator fully                                                                                                                                                                     | 37             |

| Figure 2.20:               | on and off versus RF frequency                                                                                                                                                                                                                                                                                                                                                                   | 39             |

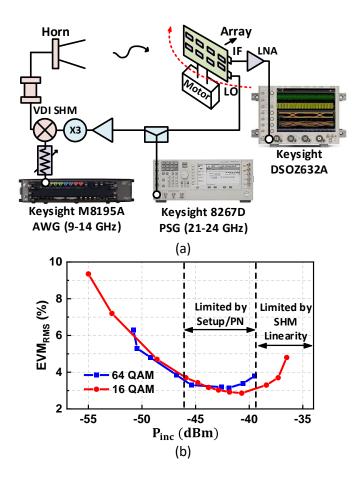

| Figure 2.21:               |                                                                                                                                                                                                                                                                                                                                                                                                  | 40             |

| -                          | angles and modulations at $P_{inc} = -42 \text{ dBm.}$<br>Simulated and calculated DP $NF_{min}$ without $C_{neu}$<br>Simulated finite array E-plane scanning patterns at (a) 140 GHz and (b) 150 GHz. 140 GHz (c) measured array element patterns and (d) simulated finite array H-plane scanning patterns.                                                                                     | 41<br>43<br>44 |

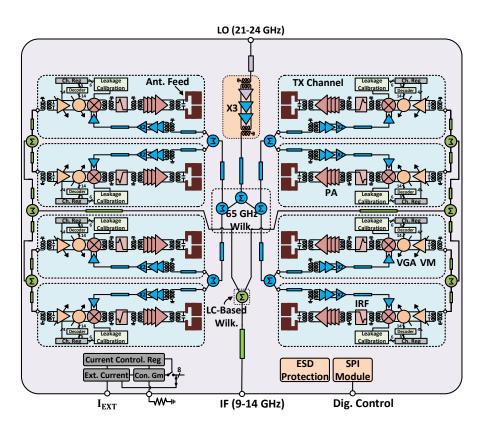

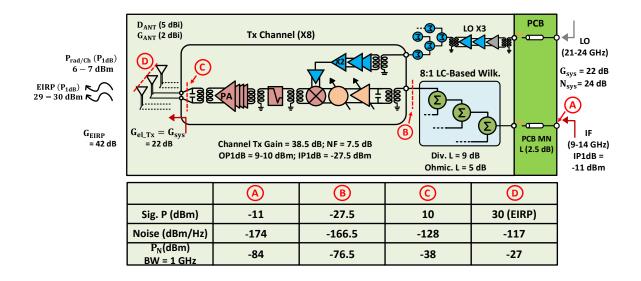

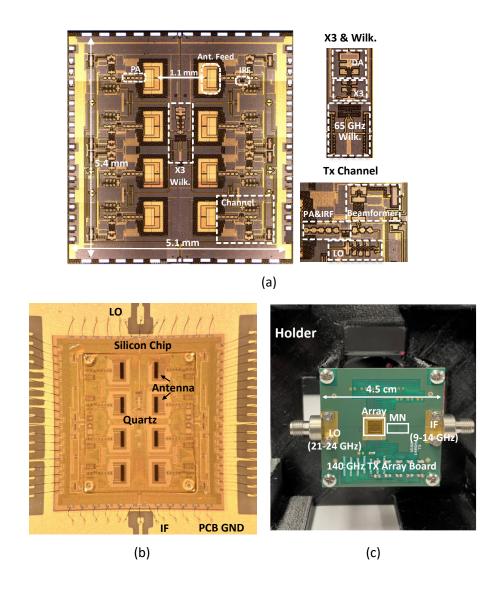

| Figure 3.1:                | Block diagram of 8-element wafer-scale IF beamforming phased array trans-                                                                                                                                                                                                                                                                                                                        |                |

| 0                          | mitter chip at 140 GHz                                                                                                                                                                                                                                                                                                                                                                           | 48             |

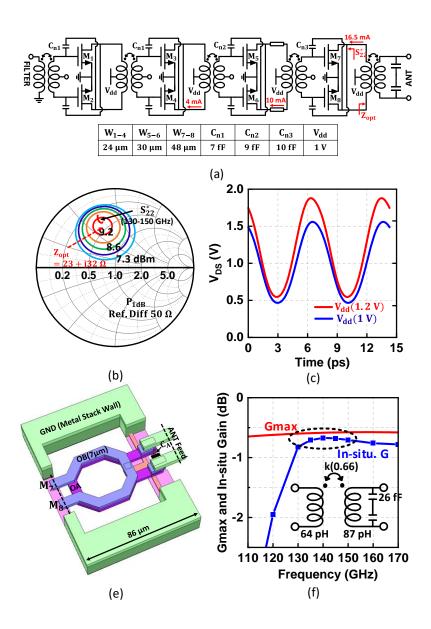

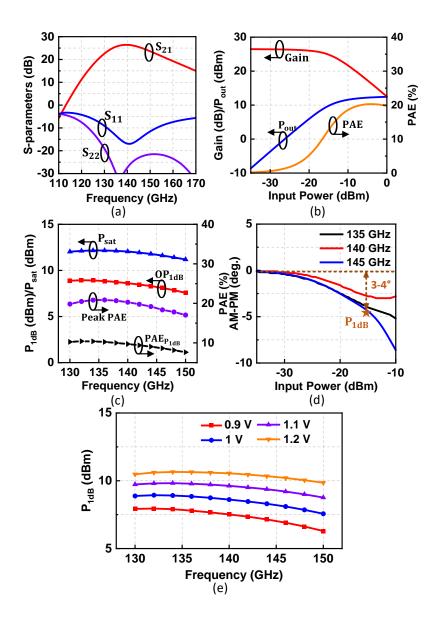

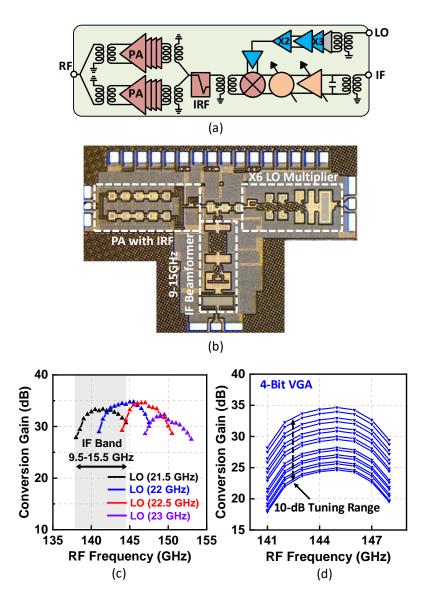

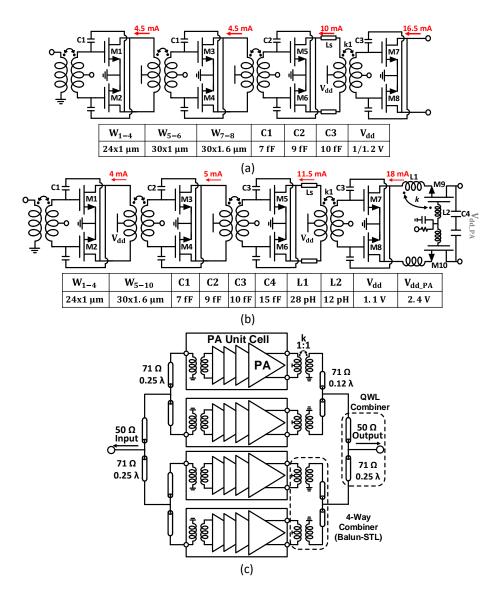

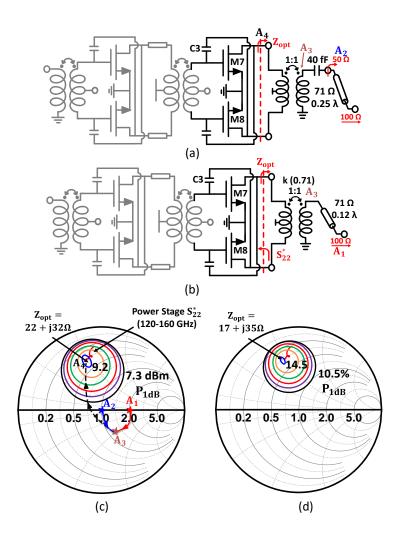

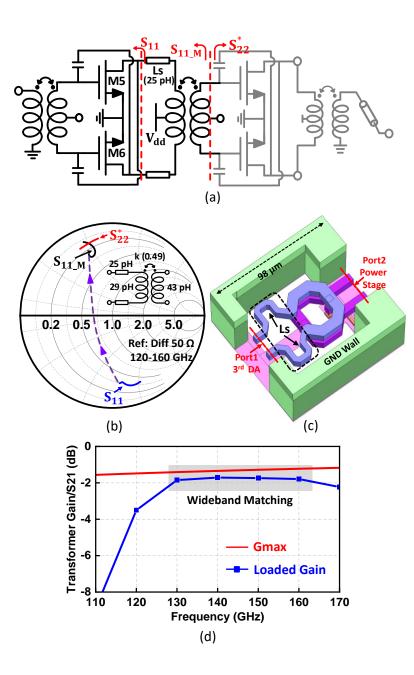

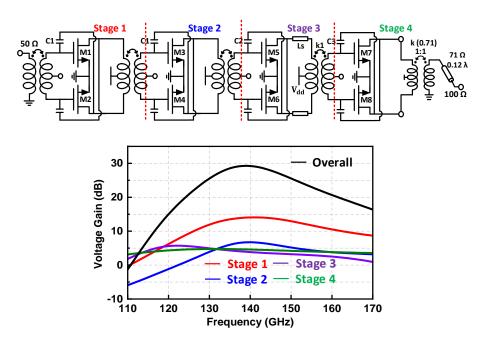

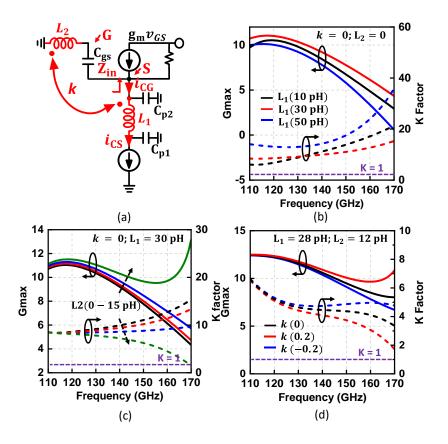

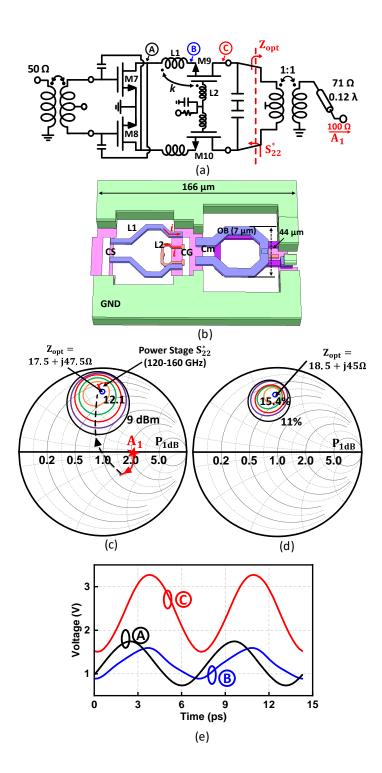

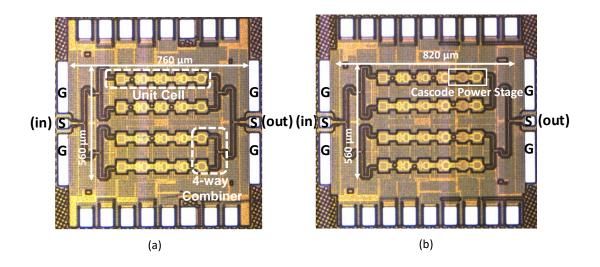

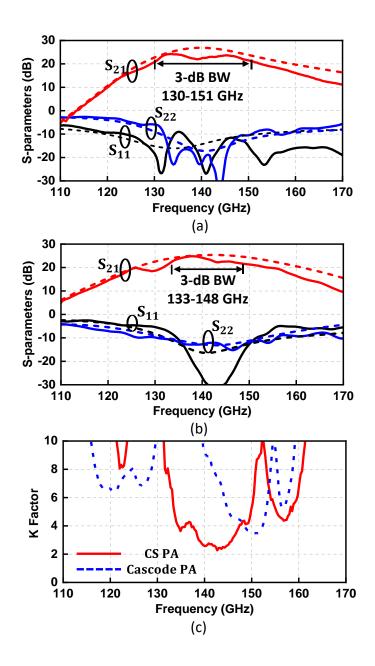

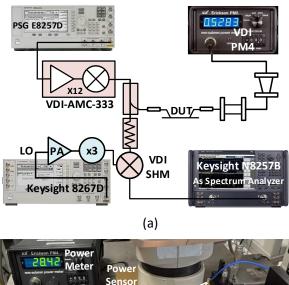

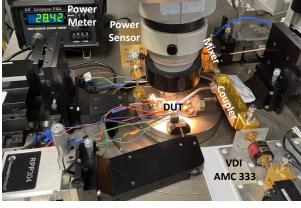

| Figure 3.2:<br>Figure 3.3: | TX phased-array PA power stage model and analysis                                                                                                                                                                                                                                                                                                                                                | 51             |

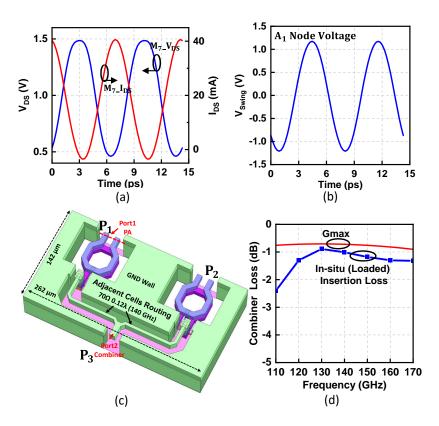

| Figure 3.4:                | and (f) simulated Gmax and in-situ (loaded) gain                                                                                                                                                                                                                                                                                                                                                 | 53             |

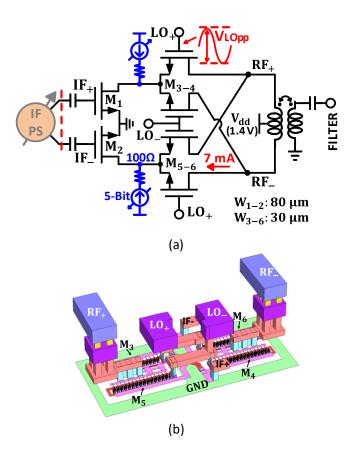

| Figure 2 5.                | voltages                                                                                                                                                                                                                                                                                                                                                                                         | 54<br>56       |

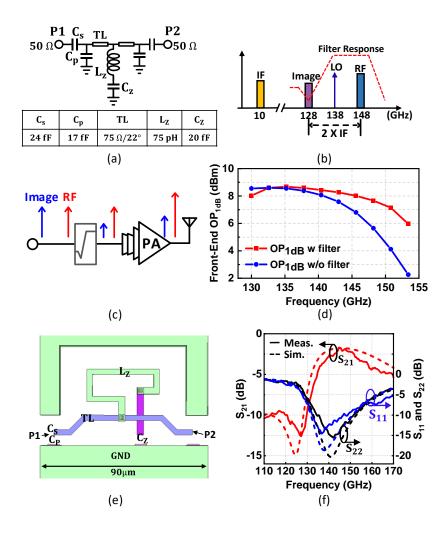

| Figure 3.5:<br>Figure 3.6: | <ul> <li>(a) Active mixer schematic. (b) 3-D layout of the mixer switching quad.</li> <li>(a) Image rejection filter (IRF) schematic. (b) Frequency spectrum of the IF, RF, LO and image signals. (c) Filtering PA schematic. (d) Simulated front-end OP<sub>1dB</sub> with and without filter versus frequency. IRF (e) layout 3-D view and (f) simulated and measured S-parameters.</li> </ul> | 56<br>57       |