#### **UC** Irvine

#### **UC Irvine Electronic Theses and Dissertations**

#### **Title**

Hardware/Software Co-design Methodologies for Efficient AI Systems and Applications

#### **Permalink**

https://escholarship.org/uc/item/5qh4b7q3

#### **Author**

Odema, Mohanad

#### **Publication Date**

2024

#### **Copyright Information**

This work is made available under the terms of a Creative Commons Attribution License, available at <a href="https://creativecommons.org/licenses/by/4.0/">https://creativecommons.org/licenses/by/4.0/</a>

Peer reviewed|Thesis/dissertation

# $\begin{array}{c} {\rm UNIVERSITY\ OF\ CALIFORNIA,} \\ {\rm IRVINE} \end{array}$

# Hardware/Software Co-design Methodologies for Efficient AI Systems and Applications DISSERTATION

submitted in partial satisfaction of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

in Electrical and Computer Engineering

by

Mohanad Mohamed Abdelmagid Abdelkhalek Odema

Dissertation Committee: Professor Mohammad Abdullah Al Faruque, Chair Professor Marco Levorato Professor Hyoukjun Kwon

Chapter 2 © 2023 IEEE.

Chapter 4 is adopted from an ArXiv version of a paper submitted to an IEEE/ACM conference

Chapter 5 © 2022 IEEE.

Appendix A © 2023 IEEE.

Appendix B © 2023 IEEE.

All other materials © 2024 Mohanad Mohamed Abdelmagid Abdelkhalek Odema

# **DEDICATION**

To my Mum and Brother

# TABLE OF CONTENTS

|              |                           | Pa                                                                         | age                              |

|--------------|---------------------------|----------------------------------------------------------------------------|----------------------------------|

| LI           | IST (                     | F FIGURES                                                                  | vii                              |

| LI           | IST (                     | F TABLES                                                                   | xi                               |

| LI           | IST (                     | F ALGORITHMS                                                               | xii                              |

| $\mathbf{A}$ | CKN                       | OWLEDGMENTS                                                                | xiii                             |

| $\mathbf{V}$ | ITA                       | 2                                                                          | xiv                              |

| $\mathbf{A}$ | BSTI                      | RACT OF THE DISSERTATION x                                                 | vii                              |

| 1            | Intr<br>1.1<br>1.2<br>1.3 | Action Research Scope                                                      | 1<br>2<br>4<br>6                 |

| 2            | _                         | mizing Dynamic Neural Networks Design and Deployment onto Heteneous MPSoCs | 7                                |

|              | 2.1                       | Introduction                                                               | 7<br>9                           |

|              | 2.2 2.3                   | Related Works                                                              | 10<br>11<br>11<br>12<br>18<br>18 |

|              | 2.4                       | 2.3.4 Evaluation and Results                                               | 23<br>23<br>26<br>28<br>29<br>31 |

|              | 2.5                       | Concluding Remarks                                                         | $\frac{31}{34}$                  |

| 3 | $\mathbf{A} \mathbf{N}$ | Mapping-Aware Graph Neural Architecture Search Framework for Het-                                                                                                                                |

|---|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | erog                    | geneous MPSoC Deployment 35                                                                                                                                                                      |

|   | 3.1                     | Introduction                                                                                                                                                                                     |

|   |                         | 3.1.1 Motivational Example                                                                                                                                                                       |

|   |                         | 3.1.2 Novel Contributions                                                                                                                                                                        |

|   | 3.2                     | Preliminaries and Related Works                                                                                                                                                                  |

|   |                         | 3.2.1 A Primer on Vision Graph Neural Networks                                                                                                                                                   |

|   |                         | 3.2.2 Related Works                                                                                                                                                                              |

|   | 3.3                     | System Model and Problem Formulation                                                                                                                                                             |

|   |                         | 3.3.1 System Model for mapping GNNs onto Heterogeneous SoCs 43                                                                                                                                   |

|   |                         | 3.3.2 Nested Search Formulation                                                                                                                                                                  |

|   | 3.4                     | MaGNAS Framework                                                                                                                                                                                 |

|   |                         | 3.4.1 Supernet Construction and Training                                                                                                                                                         |

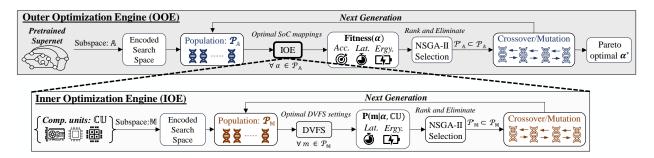

|   |                         | 3.4.2 Nested Evolutionary Search: Outer Optimization Engine 48                                                                                                                                   |

|   |                         | 3.4.3 Nested Evolutionary Search: Inner Optimization Engine 50                                                                                                                                   |

|   | 3.5                     | Experiments                                                                                                                                                                                      |

|   |                         | 3.5.1 Experimental Setup                                                                                                                                                                         |

|   |                         | 3.5.2 OOE Results: GNN Architecture Optimization                                                                                                                                                 |

|   |                         | 3.5.3 IOE Results: Hardware Mapping Optimization                                                                                                                                                 |

|   |                         | 3.5.4 Analysis of Pareto Search and Models                                                                                                                                                       |

|   |                         | 3.5.5 Generality and Scalability                                                                                                                                                                 |

|   | 3.6                     | Summary and Concluding Remarks                                                                                                                                                                   |

|   | 0.0                     |                                                                                                                                                                                                  |

| 4 | $\operatorname{Sch}$    | eduling Multi-Model Workloads on 2.5D Chiplet-based Architectures 64                                                                                                                             |

|   | 4.1                     | Introduction                                                                                                                                                                                     |

|   | 4.2                     | Background and Preliminaries 6                                                                                                                                                                   |

|   |                         | 4.2.1 Multi-model AI Workloads 6'                                                                                                                                                                |

|   |                         | 4.2.2 MCM AI Accelerators                                                                                                                                                                        |

|   |                         | 4.2.3 Scheduling space                                                                                                                                                                           |

|   | 4.3                     | System Modeling and Problem Formulation                                                                                                                                                          |

|   |                         | 4.3.1 Base Formulation                                                                                                                                                                           |

|   |                         | 4.3.2 Workload Partitioning Space                                                                                                                                                                |

|   |                         | 4.3.3 Scheduling Space                                                                                                                                                                           |

|   |                         | 4.3.4 Scheduling Problem                                                                                                                                                                         |

|   |                         | 4.3.5 Latency Modeling                                                                                                                                                                           |

|   |                         | 4.3.6 Energy Modeling                                                                                                                                                                            |

|   | 4 4                     |                                                                                                                                                                                                  |

|   | 4.4                     | Scheduling Framework                                                                                                                                                                             |

|   | 4.4                     | · ·                                                                                                                                                                                              |

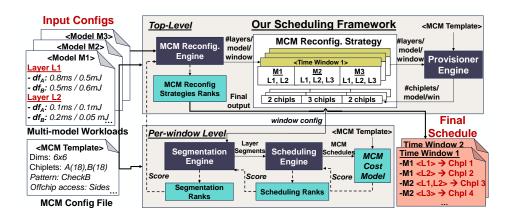

|   | 4.4                     | 4.4.1 MCM Reconfiguration Engine (MCM-Reconfig)                                                                                                                                                  |

|   | 4.4                     | 4.4.1 MCM Reconfiguration Engine (MCM-Reconfig)                                                                                                                                                  |

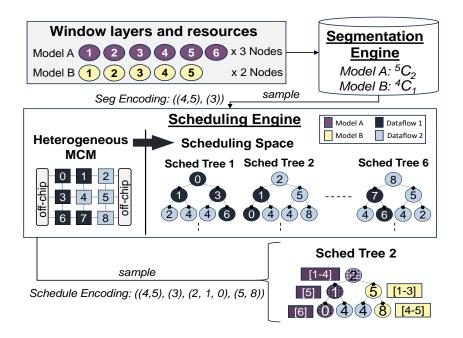

|   | 4.4                     | 4.4.1MCM Reconfiguration Engine $(MCM\text{-}Reconfig)$ 754.4.2Provisioner Engine $(PROV)$ 804.4.3Segmentation Engine $(SEG)$ 85                                                                 |

|   | 4.4                     | 4.4.1MCM Reconfiguration Engine $(MCM\text{-}Reconfig)$ 794.4.2Provisioner Engine $(PROV)$ 804.4.3Segmentation Engine $(SEG)$ 824.4.4Scheduling Engine $(SCHED)$ 83                              |

|   | 4.4                     | 4.4.1MCM Reconfiguration Engine $(MCM\text{-}Reconfig)$ 754.4.2Provisioner Engine $(PROV)$ 804.4.3Segmentation Engine $(SEG)$ 854.4.4Scheduling Engine $(SCHED)$ 854.4.5Cost Model and Scoring86 |

|   |                         | 4.4.1MCM Reconfiguration Engine $(MCM\text{-}Reconfig)$ 794.4.2Provisioner Engine $(PROV)$ 804.4.3Segmentation Engine $(SEG)$ 824.4.4Scheduling Engine $(SCHED)$ 83                              |

|   |      | 4.5.3 Top Performing Schedules Comparison                                                                              |                       | 91                                     |

|---|------|------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------|

|   |      | 4.5.4 Ablation on Windowing and Chiplets Scaling                                                                       |                       | 94                                     |

|   | 4.6  | Related Works                                                                                                          |                       | 95                                     |

|   | 4.7  | Summary                                                                                                                |                       | 97                                     |

| 5 | Effi | icient Split Computing for Edge-AI Autonomous System                                                                   | ns applications       | 98                                     |

|   | 5.1  | Introduction                                                                                                           |                       | 98                                     |

|   |      | 5.1.1 Current Limitations of Split Computing                                                                           | · · · · · · · · · ·   | 100                                    |

|   |      | 5.1.2 Novel Contributions                                                                                              |                       | 101                                    |

|   | 5.2  | Related Works                                                                                                          | · · · · · · · · · · · | 101                                    |

|   | 5.3  | Design of Split Computing Models                                                                                       | · · · · · · · · · · · | 102                                    |

|   |      | 5.3.1 Bottleneck Design                                                                                                | · · · · · · · · · · · | 103                                    |

|   |      | 5.3.2 NAS for Distributed Multi-Branch Model Architecture                                                              |                       | 104                                    |

|   | 5.4  | Context Aware Runtime Controller Design                                                                                | · · · · · · · · · · · | 108                                    |

|   |      | 5.4.1 Agent Design                                                                                                     | · · · · · · · · · · · | 108                                    |

|   |      | 5.4.2 DRL Environment                                                                                                  |                       | 110                                    |

|   | 5.5  | Evaluation                                                                                                             | · · · · · · · · · · · | 114                                    |

|   |      | 5.5.1 Experimental Setup                                                                                               | · · · · · · · · · · · | 114                                    |

|   |      | 5.5.2 Bottleneck Evaluation in Multi-sensor ADS                                                                        | · · · · · · · · · · · | 115                                    |

|   |      | 5.5.3 DRL Efficiency and Robustness Evaluation                                                                         | · · · · · · · · · · · | 116                                    |

|   | 5.6  | Concluding Remarks and Future Directions                                                                               |                       | 121                                    |

| 6 | Pro  | ovably-Safe Offloading for Edge Neural Network Control                                                                 | llers 1               | <b>2</b>                               |

|   | 6.1  | Introduction                                                                                                           |                       | 122                                    |

|   |      | 6.1.1 Related Work                                                                                                     | · · · · · · · · · ·   | 125                                    |

|   | 6.2  | Preliminaries                                                                                                          |                       | 125                                    |

|   |      | 6.2.1 Notation                                                                                                         | · · · · · · · · · ·   | 125                                    |

|   |      | 6.2.2 Kinematic Bicycle Model                                                                                          |                       | 126                                    |

|   |      | 6.2.3 Barrier Functions and Shielding                                                                                  |                       | 127                                    |

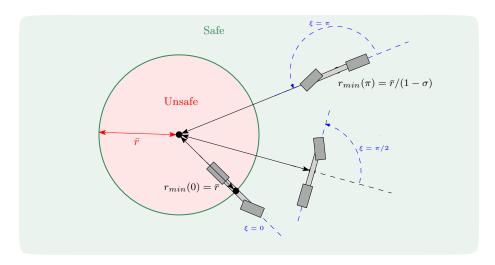

|   |      | 6.2.4 A Controller Shield for the KBM                                                                                  |                       | 129                                    |

|   | 6.3  | Framework                                                                                                              |                       | 131                                    |

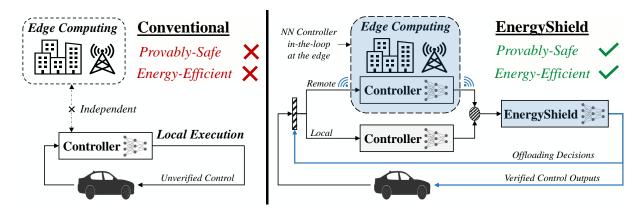

|   |      | 6.3.1 EnergyShield Motivation and Context                                                                              |                       | 131                                    |

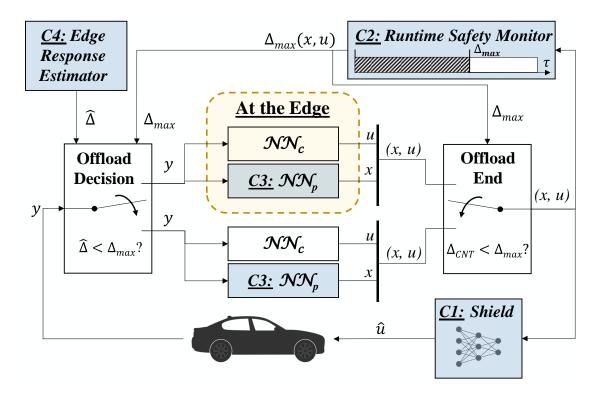

|   |      | 6.3.2 EnergyShield Structure                                                                                           |                       | 100                                    |

|   |      | 0.9.2 Energy Smela Stracture                                                                                           | · · · · · · · · · ·   | 132                                    |

|   |      | 6.3.3 Semantics of an EnergyShield Offloading Decision                                                                 |                       | 132 $135$                              |

|   | 6.4  | 9.v                                                                                                                    |                       |                                        |

|   | 6.4  | 6.3.3 Semantics of an EnergyShield Offloading Decision                                                                 |                       | 135                                    |

|   | 6.4  | 6.3.3 Semantics of an EnergyShield Offloading Decision EnergyShield: Provably Safe Offloading                          |                       | 135<br>136                             |

|   | 6.4  | 6.3.3 Semantics of an EnergyShield Offloading Decision EnergyShield: Provably Safe Offloading                          |                       | 135<br>136<br>136                      |

|   | 6.4  | 6.3.3 Semantics of an EnergyShield Offloading Decision EnergyShield: Provably Safe Offloading                          |                       | 135<br>136<br>136<br>139               |

|   |      | 6.3.3 Semantics of an EnergyShield Offloading Decision EnergyShield: Provably Safe Offloading                          |                       | 135<br>136<br>136<br>139               |

|   |      | 6.3.3 Semantics of an EnergyShield Offloading Decision EnergyShield: Provably Safe Offloading 6.4.1 Main Formal Result |                       | 135<br>136<br>136<br>139<br>140        |

|   |      | 6.3.3 Semantics of an EnergyShield Offloading Decision . EnergyShield: Provably Safe Offloading                        |                       | 135<br>136<br>136<br>139<br>140<br>142 |

| 7                | Con   | clusion and Future Directions                                      | 150  |

|------------------|-------|--------------------------------------------------------------------|------|

|                  | 7.1   | Overall Findings and insights.                                     | 150  |

|                  | 7.2   | Study Limitations and Future Directions                            | 153  |

| Bi               | bliog | graphy                                                             | 156  |

| $\mathbf{A}_{]}$ | ppen  | dix A Privacy-aware Neural Architecture Search for Split Computing | g175 |

| $\mathbf{A}_{]}$ | ppen  | dix B HW/SW Co-design for Digital Mobile Health Applications       | 198  |

# LIST OF FIGURES

|         |                                                                                                                                                                                                                                     | Page     |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

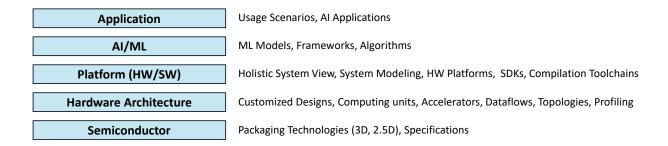

| 1.1     | Abstract model of the HW/SW research vertical in this dissertation                                                                                                                                                                  | 3        |

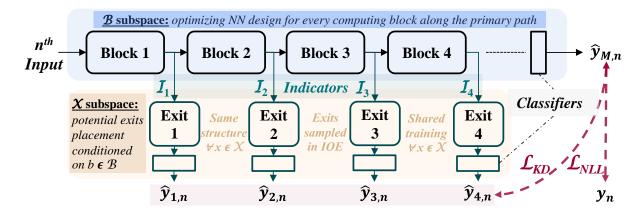

| 2.1 2.2 | HADAS co-optimization framework                                                                                                                                                                                                     | 13<br>16 |

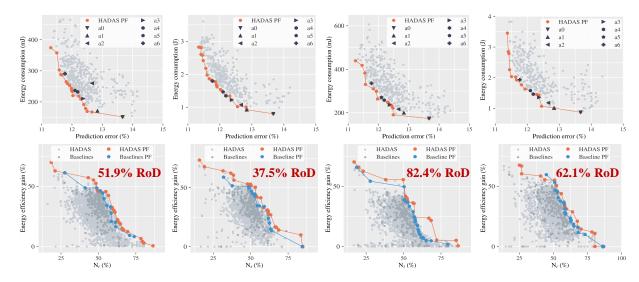

| 2.3     | The top row gives the results of the outer optimization on 4 hardware settings of (from left to right): a) AGX Volta GPU, b) Carmel ARM v8.2 CPU, c) TX2 Pascal GPU, and d) NVIDIA Denver CPU. The bottom row shows the             |          |

|         | results of the inner optimization engine, with the same hardware settings. The points in the top row depict the static performance of the explored backbone pound networks in (R) by the OOE without early evit or DVES. The points |          |

|         | neural networks in $(\mathcal{B})$ by the OOE, without early-exit or DVFS. The points in the bottom row represent the performance of the explored combinations of                                                                   |          |

|         | backbones, early-exits, and DVFS in $(\mathcal{B}, \mathcal{X}, \mathcal{F})$ by the IOE                                                                                                                                            | 20       |

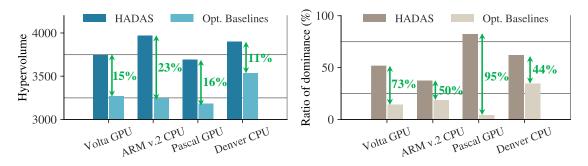

| 2.4     | Comparing search efficacy for HADAS and the optimized baselines with re-                                                                                                                                                            | 20       |

|         | gards to: a) hypervolume ( $left$ ) and b) ratio of dominance ( $right$ )                                                                                                                                                           | 21       |

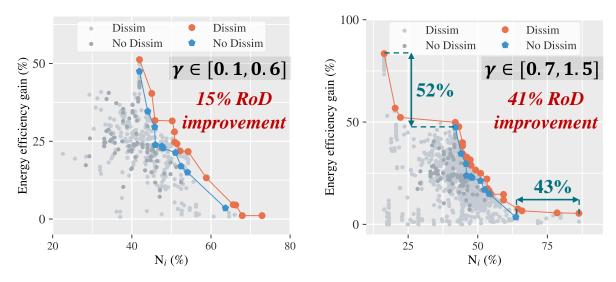

| 2.5     | Inner optimization improvement by regularizing the exits scores with the dis-                                                                                                                                                       |          |

|         | similarity function $(dissim)^{\gamma}$ over two ranges of $\gamma$ values                                                                                                                                                          | 22       |

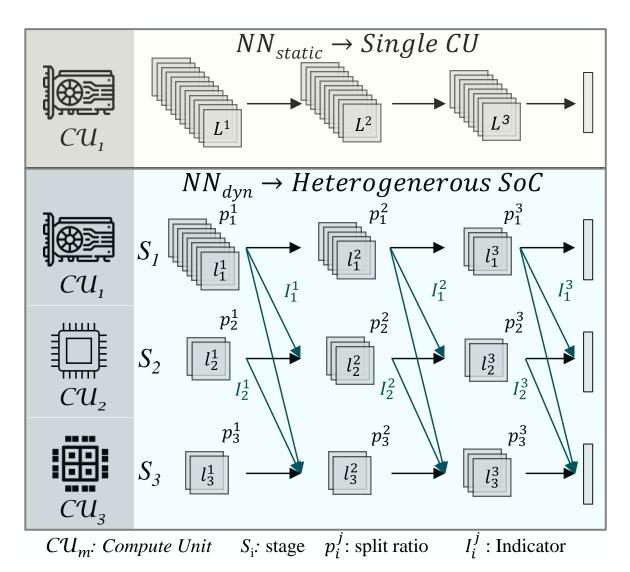

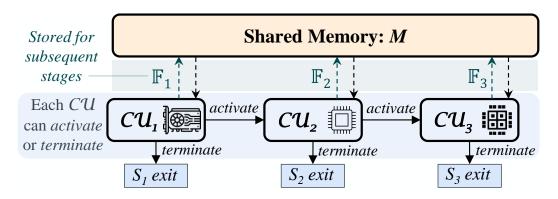

| 2.6     | Transformation of $NN_{static}$ into $NN_{dyn}$ and mapping $NN_{dyn}$ onto multiple $CU$                                                                                                                                           | s 25     |

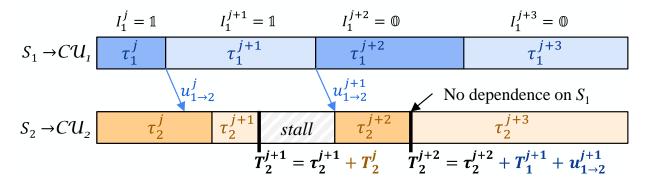

| 2.7     | Concurrent execution of $S_2$ and $S_1$ considering timing dependencies                                                                                                                                                             | 26       |

| 2.8     | Illustration of data movement and feature storage on the MPSoC                                                                                                                                                                      | 28       |

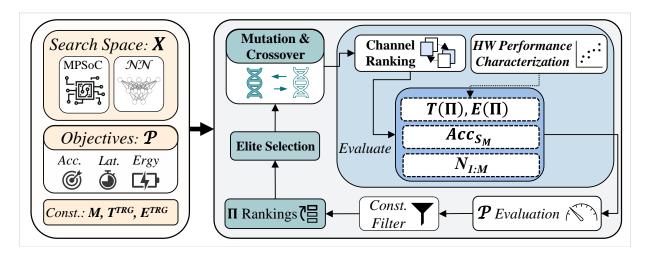

| 2.9     | Overview of our proposed optimization framework                                                                                                                                                                                     | 29       |

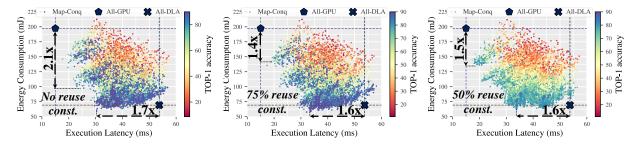

| 2.10    | Results of three different search strategies: Left) No constraint is set on the                                                                                                                                                     |          |

|         | Fmap Reuse. Middle) Under a constraint of reusing only less than 75%                                                                                                                                                                |          |

|         | of feature maps. Right) Under a constraint of reusing only less than 50%                                                                                                                                                            |          |

|         | of feature maps. All the results are reported for Visformer on the AGX                                                                                                                                                              |          |

|         | Xavier MPSoC. In the three plots, we highlight the configurations that exhibit                                                                                                                                                      |          |

|         | the highest latency-energy tradeoff while preserving less than $0.5\%$ drop in                                                                                                                                                      |          |

|         | accuracy                                                                                                                                                                                                                            | 32       |

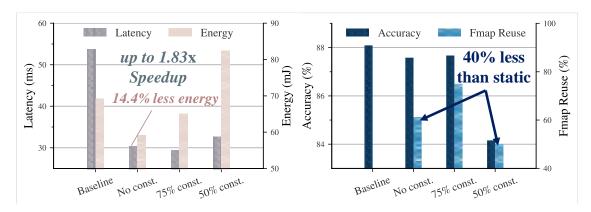

| 2.11    | Comparison between the most energy-oriented models selected from the ob-                                                                                                                                                            |          |

|         | tained Pareto sets by each search strategy and the baseline on DLA                                                                                                                                                                  | 33       |

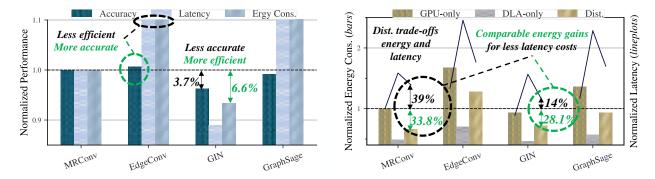

| 3.1        | Comparing ViG model variants [68] with different graph learning operators when trained on the Oxford-Flowers dataset and deployed onto the NVIDIA                                                                         |    |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | Jetson AGX Xavier SoC. All values are normalized by the baseline performance evaluations incurred by the original ViG with MRConv layers when                                                                             |    |

|            | fully deployed onto the GPU only. The <i>left</i> figure shows how performance                                                                                                                                            |    |

|            | characteristics differ from one variant to the other regarding accuracy, latency,                                                                                                                                         |    |

|            | and energy consumption. The right figure illustrates how distributed map-                                                                                                                                                 |    |

|            | ping strategies across the GPU and DLA can yield different latency-energy                                                                                                                                                 |    |

|            | trade-offs                                                                                                                                                                                                                | 37 |

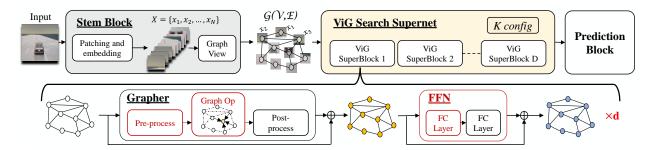

| 3.2        | The ViG supernet implementation for MaGNAS co-search framework. The supernet comprises $D$ ViG search super blocks, each of which constitutes a sequence of $d_i$ Grapher and FFN computing modules. Architectural search |    |

|            | parameters characterizing $\mathbb{A}$ subspace are highlighted in $red$ and detailed in                                                                                                                                  |    |

|            | the text                                                                                                                                                                                                                  | 46 |

| 3.3        | MaGNAS two-tier evolutionary search framework                                                                                                                                                                             | 49 |

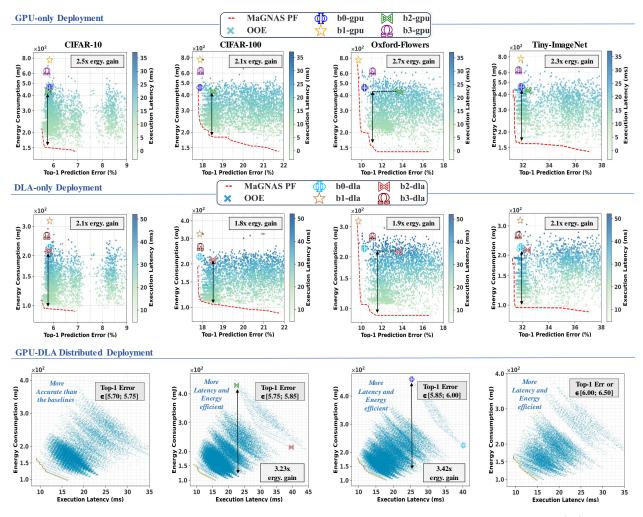

| 3.4        | The first two rows show the performance of the explored GNNs in $(A)$ by the OOE on four datasets (from left to right: a) CIFAR-10, b) CIFAR-100, c)                                                                      |    |

|            | Oxford-Flowers, and d) Tiny-ImageNet. The Hardware metrics (i.e., latency                                                                                                                                                 |    |

|            | and energy) are shown for $GPU$ -only deployment in the first row and for $DLA$ -                                                                                                                                         |    |

|            | only deployment in the second row. The third row shows the IOE results on                                                                                                                                                 |    |

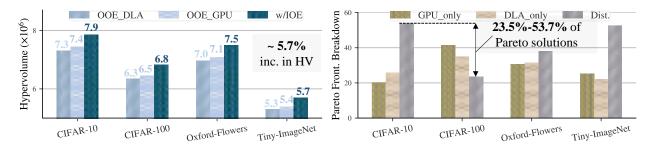

| 3.5        | CIFAR-10 grouped by prediction error intervals                                                                                                                                                                            | 55 |

| 5.5        | standalone OOE for the DLA and GPU. Right: Breakdown of the combined                                                                                                                                                      |    |

|            | Pareto Fronts constituents on the basis of mapping options                                                                                                                                                                | 58 |

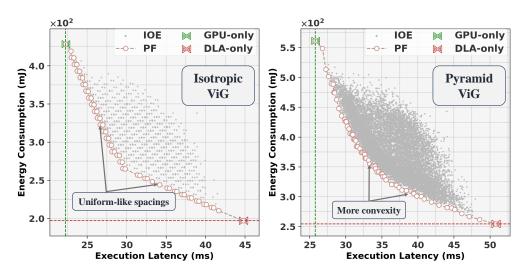

| 3.6        | The results of the IOE EA optimization on the Isotropic Vision GNN ( <i>left</i> ) and Pyramid Vision GNN ( <i>right</i> )                                                                                                | 61 |

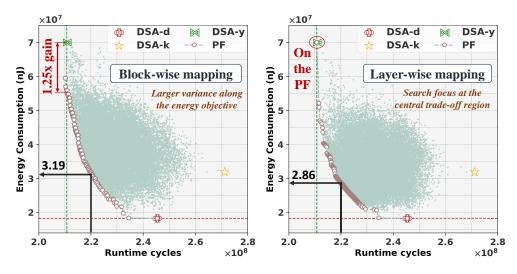

| 3.7        | The results of the IOE optimization on MAESTRO [99] with: i) Block-wise                                                                                                                                                   | 01 |

|            | mapping granularity (left) and ii) Layer-wise mapping granularity (right)                                                                                                                                                 | 62 |

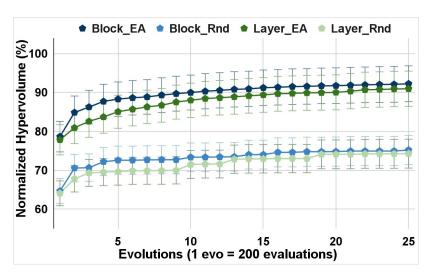

| 3.8        | Evolutionary Vs. Random Search                                                                                                                                                                                            | 63 |

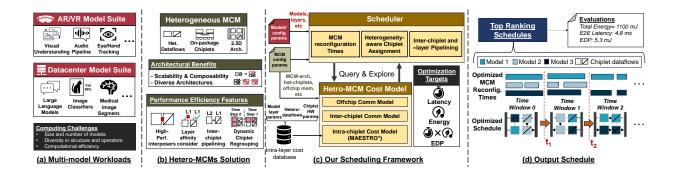

| 4.1        | Proposed scheduling framework for multi-model workloads on 2.5D MCMs.                                                                                                                                                     | 66 |

| 4.2        | An overview of our scheduling algorithm.                                                                                                                                                                                  | 78 |

| 4.3        | Our proposed multi-model scheduling framework on heterog. MCM                                                                                                                                                             | 78 |

| 4.4        | Schedules creation through the SEG and SCHED engines                                                                                                                                                                      | 84 |

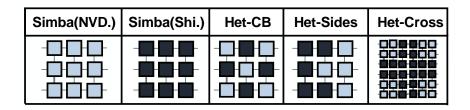

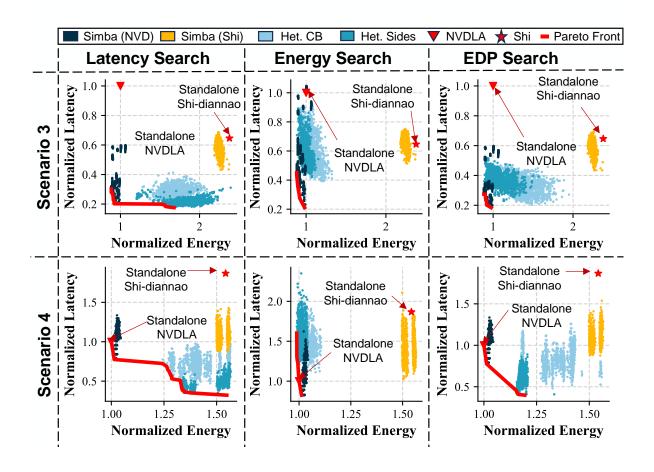

| 4.5<br>4.6 | The evaluated MCM chiplet organizations                                                                                                                                                                                   | 89 |

| 4.0        | MCM configurations for various search targets for scenarios 4 and 5 from                                                                                                                                                  |    |

|            | Table 4.2. standalone Shi-diannao and standalone NVDLA indicate cases                                                                                                                                                     |    |

|            | where execution is performed on a single chiplet supporting said dataflow                                                                                                                                                 | 90 |

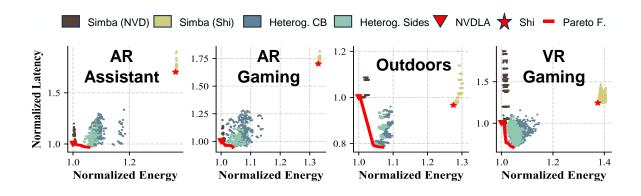

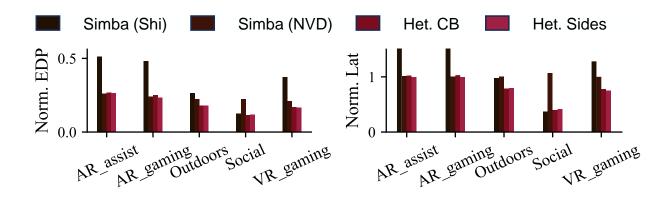

| 4.7        | Pareto optimal results on the EDP search experiments for the labeled XR-                                                                                                                                                  |    |

|            | Bench usage scenarios. Results normalized by standalone NVDLA                                                                                                                                                             | 90 |

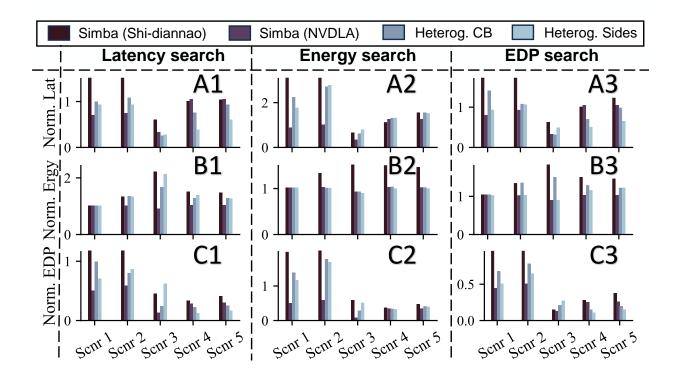

| 4.8        | Comparing latency, energy, and EDP evaluations for the top-scoring candi-                                                                                                                                                 |    |

|            | dates from every search experiment with different optimization criteria across                                                                                                                                            | 00 |

|            | every scenario in Table 4.2. Values normalized by NVDLA standalone                                                                                                                                                        | 92 |

| 4.9        | Each window showcases the top-performing schedule within, and the mapping                                                                                                                     | 92                                |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 1 11       | of models onto chiplets. Time boundaries between successive windows are computed over 500 MHz                                                                                                 | 94<br>95                          |

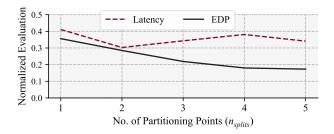

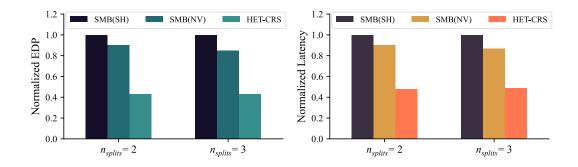

|            | Comparing EDP and Latency at $n_{splits} \in \{2,3\}$ for the $6 \times 6$ MCM for target EDP optimizaiton and an evolutionary search algorithm.                                              | 96                                |

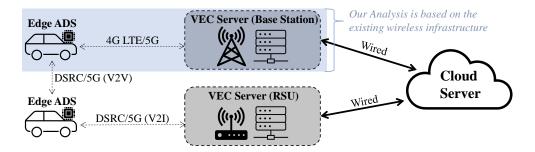

| 5.1        | A Practical Example of the Edge Computing Paradigm for Vehicular Applications                                                                                                                 | 100                               |

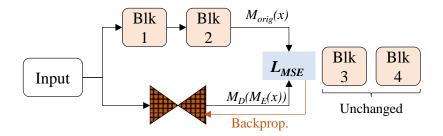

| 5.2        | Our ResNet-18 feature extractors undergo Knowledge Distillation to train $\mathcal{M}_E \cdot \mathcal{M}_D$ using the first 2 blocks                                                         | 104                               |

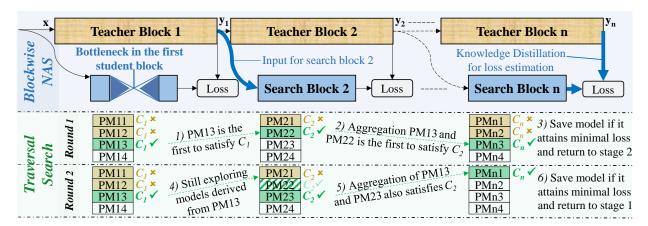

| 5.3        | Blockwise NAS for edge computing $(top)$ and a walk-through example for the traversal search $(bottom)$ . PM is for partial model and its indices are for the                                 | 40*                               |

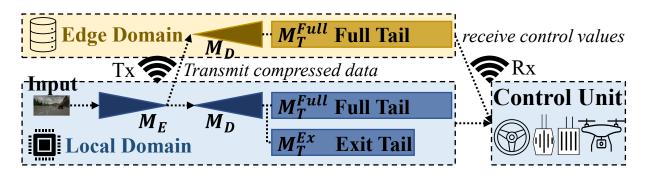

| 5.4        | stage and the PM's ranking based on the loss defined in (5.5) An example end-to-end distributed multi-branch DNN architecture for reliable and efficient edge computing in autonomous systems | 105<br>107                        |

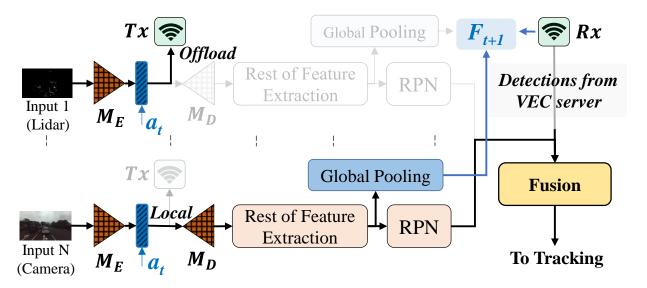

| 5.5        | Illustration of multi-sensor object detection with late fusion and offloading support. Blue blocks/variables are passed to/from the DRL. Transparent                                          |                                   |

| F 6        | blocks are inactive                                                                                                                                                                           | 108                               |

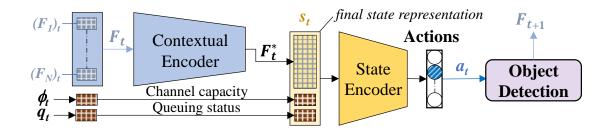

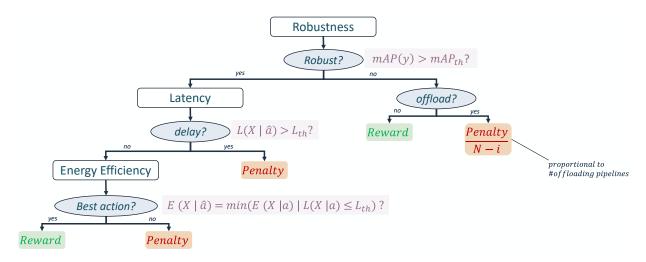

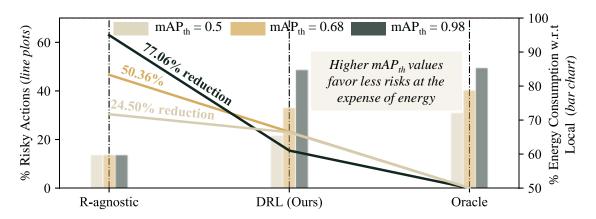

| 5.6<br>5.7 | Our hierarchical agent for runtime mode selection                                                                                                                                             | 109                               |

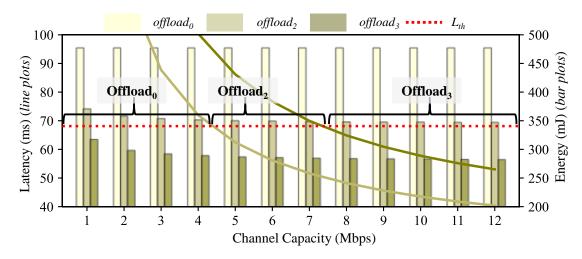

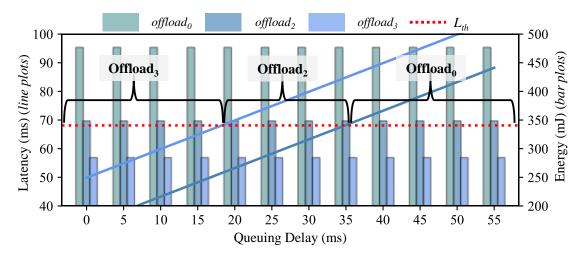

| 5.8        | Variation of Latency and Energy Analysis w.r.t. Channel Capacity. Energy                                                                                                                      | 112                               |

| 5.9        | as bar charts, Latency as plot lines                                                                                                                                                          | <ul><li>117</li><li>118</li></ul> |

| 5.10       | bar charts, Latency as plot lines                                                                                                                                                             | 110                               |

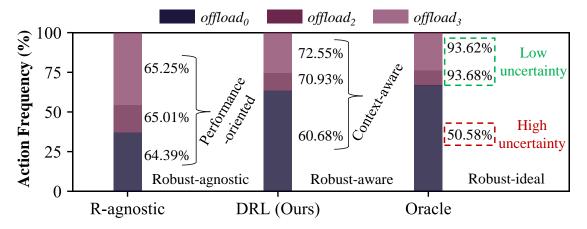

| 5.11       | action                                                                                                                                                                                        | 121                               |

| 6.1        | Illustration of Provably-Safe Offloading of Edge Neural Network Controllers.                                                                                                                  | 123                               |

| 6.2        | Obstacle specification and minimum barrier distance as a function of relative                                                                                                                 | 100                               |

| 6.3        | vehicle orientation, $\xi$                                                                                                                                                                    | 126 $135$                         |

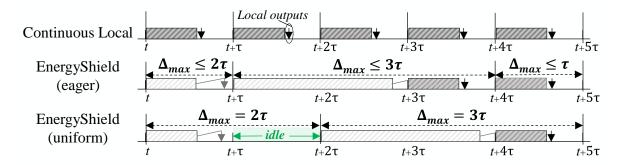

| 6.4        | Timeline for an offloading period experienced through EnergyShield                                                                                                                            | 136                               |

| 6.5        | The operational policies in our experiments given base time window $\tau$ . Darker instances imply local execution.                                                                           | 143                               |

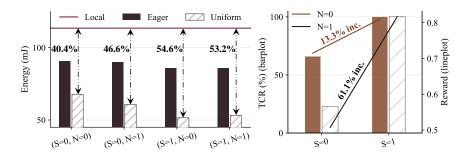

| 6.6        | EnergyShield's energy efficiency gains with respect to continuous local execution ( $left$ ) and safety analysis in terms of the $\mathcal{R}$ evaluation and $\%$ TCR                        |                                   |

|            | (right)                                                                                                                                                                                       | 145                               |

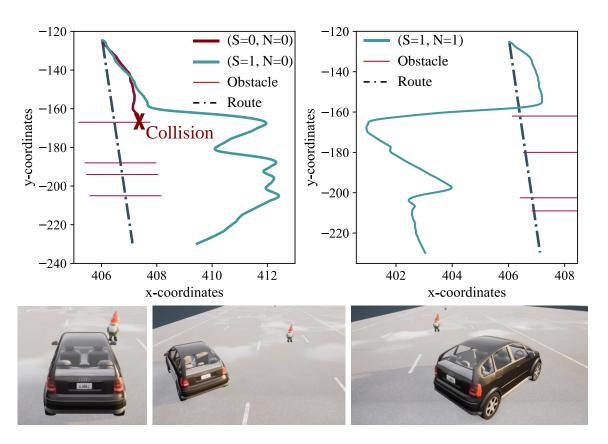

| 6.7  | Top: Example trajectories followed by the ego vehicle with the start point at |     |

|------|-------------------------------------------------------------------------------|-----|

|      | the top. Bottom: illustration of how the ego vehicle under the aforementioned |     |

|      | operational modes behaved in reaction to the first encountered obstacle       | 146 |

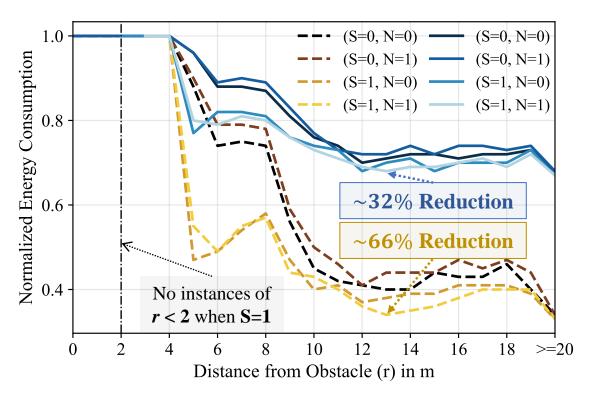

| 6.8  | Normalized Energy Gains for the eager (solid) and uniform (dashed) Ener-      |     |

|      | gyShield modes with respect to the distance from obstacle $(r)$ in m          | 148 |

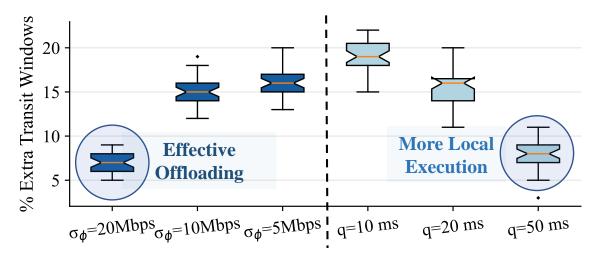

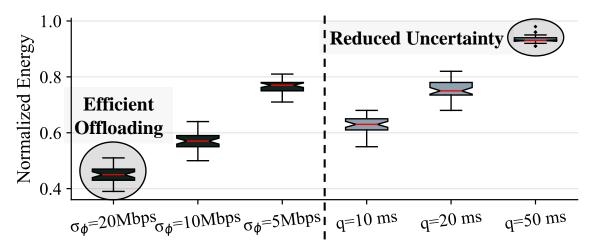

| 6.9  | Analyzing the $\%$ extra transit windows over 35 episodes of uniform Ener-    |     |

|      | gyShield given various $\sigma_{\phi}$ and $q$                                | 149 |

| 6.10 | Analyzing the Normalized Energy cons. over 35 episodes of uniform Ener-       |     |

|      | gyShield given various $\sigma_{\phi}$ and $q$                                | 149 |

### LIST OF TABLES

|                                               |                                                                                                                                         | Page              |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 2.1<br>2.2<br>2.3                             | Details on HADAS joint search spaces in our experiments                                                                                 | 19<br>21<br>34    |

| 3.1<br>3.2<br>3.3                             | Comparison between related Graph Neural Architecture Search works and our Search space parameters for GNN architectures                 | s. 42<br>53       |

| 3.4                                           | and DLA, respectively                                                                                                                   | 57<br>60          |

| 4.1                                           | MCM microarchitecture parameters from [143, 167]. All numbers are scaled to 28 nm process node technology                               | 86                |

| 4.3                                           | sequence length                                                                                                                         | 87<br>94          |

| 4.4                                           | Comparison against prior related scheduling works                                                                                       | 97                |

| <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Loss and mAP (%) before (orig) and after (dist) integrating $\mathcal{M}_E \cdot \mathcal{M}_D$ across various late fusion combinations | 116<br>116<br>118 |

| 5.4                                           | Action frequency analysis at mAP <sub>th</sub> = $0.68 \dots \dots \dots \dots \dots$                                                   | 120               |

| 5.5                                           | Energy analysis relative to local at $mAP_{th} = 0.98$                                                                                  | 120               |

# LIST OF ALGORITHMS

|   |                                |  |  |  |  |  |  |  |  |  |  | ŀ | ag | ge |

|---|--------------------------------|--|--|--|--|--|--|--|--|--|--|---|----|----|

| 1 | Greedy Layer Packing Algorithm |  |  |  |  |  |  |  |  |  |  |   | 8  | 31 |

#### ACKNOWLEDGMENTS

I thank my advisor and committee chair, Professor Mohammad Abdullah Al Faruque, for his mentorship, guidance, and support throughout my doctoral studies. I would also like to express my gratitude to my committee members, Professor Marco Levorato and Professor Hyoukjun Kwon, for serving on my doctoral committee and for all our research collaborations.

I collaborated with several colleagues during my graduate studies on various research projects. Specifically, I would like to thank Luke Chen, Halima Bouzidi, Nafiul Rashid, Arnav Malawade, and Berken Utku Demirel for their contributions to the projects presented in this dissertation. Additionally, I thank my external collaborators, James Ferlez, Yasser Shoukry, Smail Niar, and Hamza Ouarnoughi for our collaborations on several projects presented in this dissertation. I also want to thank my past and present colleagues at the AICPS lab: Trier Mortlock, Yonatan Giazchew, Kohei Tsujio, Junyao Wang, Mohammed Habib Fakih, Yasamin Moghaddas, Tyler Zhang, Rozhin Yasaei, and Shih-Yuan Yu. I enjoyed sharing this journey with them immensely.

I would like to thank UCI's Department of Electrical Engineering and Computer Science for their support during my PhD. I also thank the National Science Foundation for their funding assistance via awards CCF-2140154 and CMMI-1739503. Any opinions, findings, conclusions, or recommendations expressed in this paper are those of the authors and do not necessarily reflect the views of the funding agencies. I thank IEEE, ACM, and original authors for granting permission to include the content for my dissertation based on content originally published in their IEEE and ACM transactions and conference papers.

#### VITA

#### Mohanad Mohamed Abdelmagid Abdelkhalek Odema

#### **EDUCATION**

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Irvine

Master of Science in Computer Engineering

Ain Shams University

Cairo, Egypt

Bachelor of Science in Electrical Engineering

Ain Shams University

Cairo, Egypt

#### RESEARCH EXPERIENCE

Graduate Research Assistant2019-2024University of California, IrvineIrvine, CaliforniaAI Architecture and Algorithm Intern2023-2023MediaTekSan Jose, CaliforniaResearch Assistant2015-2018Ain Shams UniversityCairo, Egypt

#### TEACHING EXPERIENCE

Teaching Assistant2022-2024University of California, IrvineIrvine, CaliforniaTeaching Assistant2015-2019Ain Shams UniversityCairo, Egypt

#### REFEREED JOURNAL PUBLICATIONS

| EPIC: Efficient Autonomous Driving Perception via Integrated Accelerator Chiplets (Under Review)  IEEE Transactions on Computer-Aided Design of Integrated Circuits and Syste (TCAD) | <b>2024</b><br>ms |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| MaGNAS: A Mapping-Aware Graph Neural Architecture Search Framework for Heterogeneous MPSoC Deployment ACM Transactions on Embedded Computing Systems (TECS)                          | 2023              |

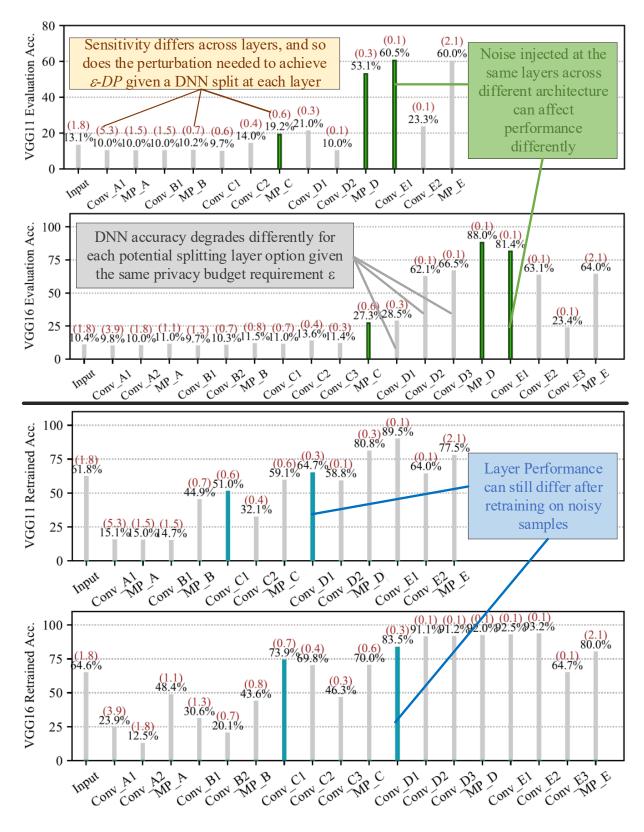

| PrivyNAS: Privacy-Aware Neural Architecture Search for Split Computing in Edge-Cloud Systems IEEE Internet of Things Journal (IoTJ)                                                  | 2023              |

| Testudo: Collaborative Intelligence for Latency-Critical<br>Autonomous Systems<br>IEEE Transactions on Computer-Aided Design of Integrated Circuits and Syste<br>(TCAD)              | <b>2022</b><br>ms |

| SAGE: A Split-Architecture Methodology for Efficient<br>End-to-End Autonomous Vehicle Control<br>ACM Transactions on Embedded Computing Systems (TECS)                               | 2021              |

| REFEREED CONFERENCE PUBLICATIONS                                                                                                                                                     |                   |

| SCAR: Scheduling Multi-Model AI Workloads on Heterogeneous Multi-Chiplet Module Accelerators (Accepted) IEEE/ACM International Symposium on Microarchitecture (MICRO)                | 2024              |

| SEO: Safety-Aware Energy Optimization Framework<br>for Multi-Sensor Neural Controllers at the Edge<br>ACM/IEEE Design Automation Conference (DAC)                                    | 2023              |

| Map-and-Conquer: Energy-Efficient Mapping of Dynamic Neural Nets onto Heterogeneous MPSoCs<br>ACM/IEEE Design Automation Conference (DAC)                                            | 2023              |

| EnergyShield: Provably-Safe Offloading of Neural Network Controllers for Energy Efficiency ACM/IEEE 14th International Conference on Cyber-Physical Systems (ICCPS)                  | 2023              |

| HADAS: Hardware-Aware Dynamic Neural Architecture Search for Edge Performance Scaling Design, Automation & Test in Europe Conference & Exhibition (DATE)                                            | 2023              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Romanus: Robust Task Offloading in Modular Multi-<br>Sensor Autonomous Driving Systems<br>IEEE/ACM International Conference on Computer-Aided Design (ICCAD)                                        | 2022              |

| Template Matching Based Early Exit CNN for Energy- efficient Myocardial Infarction Detection on Low-power Wearable Devices ACM on Interactive, Mobile, Wearable and Ubiquitous Technologies (IMWUT) | 2022              |

| LENS: Layer Distribution Enabled Neural Architecture Search in Edge-Cloud Hierarchies ACM/IEEE Design Automation Conference (DAC)                                                                   | 2021              |

| EExNAS: Early-Exit Neural Architecture Search Solutions for Low-Power Wearable Devices IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPE)                                 | <b>2021</b><br>D) |

| Energy-Aware Design Methodology for Myocardial Infarction Detection on Low-Power Wearable Devices Asia and South Pacific Design Automation Conference (ASP-DAC)                                     | 2021              |

#### SOFTWARE

EnergyShield https://github.com/MohanadOdema/EnergyShield Oepn Source Code for EnergyShield provably-safe optimizations in CARLA Simulator

#### ABSTRACT OF THE DISSERTATION

Hardware/Software Co-design Methodologies for Efficient AI Systems and Applications

By

Mohanad Mohamed Abdelmagid Abdelkhalek Odema

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Irvine, 2024

Professor Mohammad Abdullah Al Faruque, Chair

The landscape of AI research is dominated by the search for powerful deep learning models and architectures that enable fascinating applications from the edge to the cloud. Indeed, we have witnessed the emergence of efficient, on-device deep learning models that facilitate smart edge applications (autonomous vehicles, AR/VR systems), and the emergence of billion parameter foundation/LLM models that excel at tasks thought achievable only through human-level understanding. On the other hand, the calls for more advanced hardware and systems continue to grow considering the scale at which deep learning model workloads evolve, and to facilitate sustainable, efficient model operation across the various application contexts.

This suggests a natural way to design deep learning models and their systems: viz, through hardware/software co-design methodologies, capturing the interplay and mutual dependencies across various HW/SW layers of the computing stack to guide different design choices. From the algorithmic side, an awareness of the target platform's compute capabilities and resources guides the deep learning model architectural and optimization choices (e.g., compression) towards maximizing performance efficiency on the target hardware at deployment time. From the hardware side, understanding the deep learning workloads and computing kernels can shape future architectures of AI hardware that improves on efficiency from the

lower levels (as seen through customized accelerators). Even more so, frameworks like TVM and ONNX Runtime have also emerged to standardize model deployment on various target hardware systems, offering unified interfaces to enact necessary compiler optimizations.

As hardware and software continue to undergo continuous innovation, this dissertation aims to investigate relevant emergent technologies and challenges at this unified research frontier to guide the design of future AI systems and models. The dissertation focuses on characterizing nascent design spaces, exploring various optimization opportunities, and developing new methodologies to maximize the impact of such innovations. In brief, this dissertation goes over the following topics:

- Understanding the benefits of dynamic neural networks for efficient inference, and how to optimize their design for target platform deployment

- Studying emergent models (like Graph Neural Networks) with irregular computational flows and how their design can be optimized for deployment on heterogeneous SoCs

- Understanding how multi-model workloads can be scheduled and co-located on multichip AI Accelerator modules based on 2.5D chiplets technology while accounting for workloads' diversity, affinities, and memory access patterns

- Exploring new methodologies to maximize the impact of split computing inference in edge-cloud architectures, and elevate resource efficiency of edge devices

- Studying the impact emergent schemes like split computing could have on the broader cyber-physical system and application with regards to safety and privacy, and proposing methods to counteract potential disruptions and maintain desired formal guarantees

# Chapter 1

## Introduction

The AI ecosystem is going through seismic transformations driven by recent innovations in the field. Though the release of ChatGPT is widely regarded as the watershed moment for the AI field, its success can be attributed to decades of technological advancements across multiple sectors leading up to that moment. To put it succinctly, the brilliance and promise of AI technology rests on the strong, mature foundation of enabling industries of semiconductor, hardware manufacturing, and software development. And today, AI is becoming a vortex around which these industries - and more - are oriented. In fact, the nature of AI's relationship with these industries is shifting from reliance towards co-dependence. For instance, AI advancements and application use cases are fueling innovation and shaping the vision of semiconductor and hardware manufacturing industries, while at the same time they remain dependent on breakthroughs in the very same fields to realize their full potential.

This mutual co-dependence underpins an intuitive philosophy: Hardware/software co-design is pivotal to bringing the best out of AI applications by enhancing their performance efficiency on target systems. From an algorithmic perspective, optimizing the design and deployment of underlying machine learning models is to be performed in a hardware-aware manner. This

is driven by how underlying resource constraints and hardware capabilities could influence decisions pertaining to the extent of a model's representational capacity through architecture parameter choices, compression techniques, scheduling options, and so on. As for the hardware, understanding the emerging trends in AI model workloads guides the design of the next generations of AI hardware, as we see today through the progression of computing capabilities in GPUs, domain specific accelerators, and heterogeneous SoCs.

While standard tools such as ONNX Runtime and TVM have emerged to optimize model deployment on target hardware platforms, the rapid evolution of AI usage scenarios, model architectures, semiconductor technologies has outpaced current optimization practices. That is, despite the effectiveness of standard model optimization techniques like quantization, AutoML, operator fusion, new challenges have emerged from the trends of multi-model workloads in AR/VR systems and data center multi-tenancy, as well as from recent innovations in dynamic and graph neural networks. Similarly, advancements in semiconductor technologies, such as chiplet-based 2.5D multi-chip module AI accelerators, have expanded the HW/SW optimization space beyond the capabilities of existing practices.

In this dissertation, our aim is to study and understand these nascent frontiers, exploring the optimization opportunities they present from a hardware/software co-design perspective. As detailed in the following chapters, our research consistently guides us towards characterizing novel design spaces, for which we propose methodologies to maximize the performance of AI applications and systems in these evolving settings.

#### 1.1 Research Scope

Figure 1.1 illustrates our abstract hardware/software research vertical that is traversed throughout this dissertation. This characterization serves to organize the the various con-

Figure 1.1: Abstract model of the HW/SW research vertical in this dissertation.

cepts, technologies, and innovations pertaining to different layers of abstraction from the broader hardware/software stack. That way, not only do we analyze and innovate methods/techniques in isolation, but also understand cross-layer impacts, and how to improve the overall AI system utility and efficiency. For instance, advancements in 2.5D packaging technology in the 'Semiconductor' layer enable new customized designs in the 'Hardware Architecture' layer, improving the efficiency of AI/ML workload processing, and providing better application usage experiences at the higher levels of the stack.

In this dissertation, we study the hardware-software co-design challenges for AI algorithms and systems from a variety of perspectives, and propose novel methodologies to enhance the efficiency of AI on respective target hardware systems. Our studies are motivated by and shaped through real-world, practical applications, use cases, and emerging trends of AI models and systems from the edge to the cloud. In particular, emphasis is drawn from:

(i) The Edge-AI application domain, which entails machine learning models deployed on constrained edge computing devices in the wild (e.g., autonomous driving systems). (ii) The multi-model AI workload trend, which entails a diverse set of large, complex models running simultaneously on a target system to meet application demands (e.g., multi-tenancy and AR/VR). From here, our studies take us to understand the underlying model architectures and classes (transformers, CNNs, GNNs), computational workflow (static, dynamic), and constituent compute kernels (GEMMs, Non-GEMMs), enabling us to shape the design space of algorithmic optimizations.

As for the hardware, we focus our analysis on two classes of systems corresponding to the above areas. (i) Heterogeneous SoCs, which service numerous Edge-AI applications (e.g., Tesla FSD for autonomous driving), and constitute a diverse set of computing units, such as CPUs, GPUs, and DSPs, all integrated onto the same die. (ii) Chiplet-based 2.5D multi-chip modules, which - owing to the mix-and-match characteristic of chiplets - enable integration of heterogeneous accelerator chips on the package level to efficiently service multi-model workloads. Through both, we are able to characterize hardware design spaces that cover different dimensions of hardware optimization options, including scheduling, pipelining, hardware reconfigurability, and accelerator hardware parameter choices.

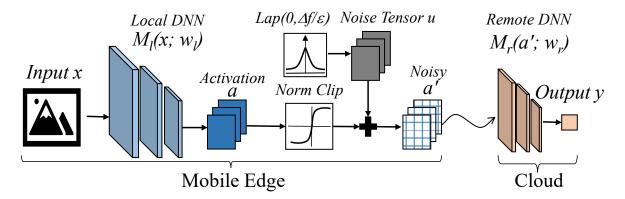

Furthermore, we study the emerging paradigm of split-computing and how its effectiveness can be maximized through co-optimization approaches. As inferred from the name, split-computing partitions a machine learning model between a constrained user edge device and a compute capable edge server, offering a viable alternative for enabling powerful, on-device machine learning without compromising on the model's representational capacity. We also engage specific challenges of split-computing including context-aware runtime adaptation and maintaining formal safety guarantees when applied to mission-critical systems.

#### 1.2 Primer: Neural Architecture Search

A recurring theme throughout this dissertation is Neural Architecture Search (NAS), which is an automated design space exploration technique to optimize the design of neural architectures for target machine learning tasks. NAS can provide DNN architectures that are on-par or outperform their manually-crafted counterparts [22, 25, 26, 232]. In a nutshell, the purpose of NAS is to effectively navigate an enormous design space of neural architectural parameters to identify optimal candidate model architecture designs suited for the target objectives. Primarily, there are three foundational pillars to any NAS framework:

**Search Space.** Through the coalescence of various combinations of architectural design parameters, a pool of candidate designs can be constructed for the NAS engine to access. Thus, DNN architectural parameter choices such as the #layers, # channels, type of layer operation, etc can all be encoded into a single unified search string.

Search Controller. Due to the colossal size of typical DNN architectural search spaces, NAS frameworks employ search controllers adopting sophisticate search strategies to effectively balance the exploration/exploitation of the search space. In particular, search controllers learn to identify promising design subspaces from which they can sample superior population of architectural candidates, reducing the likelihood of considering sub-optimal designs in the interim. These controllers are typically adopt strategies that follow a learning-based approach (e.g., reinforcement learning based [26, 232]) or a metaheuristic approach (e.g., evolutionary algorithm [22]).

**Performance Evaluation.** In order to guide the search controller on promising architectural design sub-spaces, performance evaluations of the candidate model design on the target objectives (e.g., accuracy and execution latency) are fed back to the search controller for it to exploit optimizations around the top-performing candidates in a progressive manner.

Traditionally, classical NAS frameworks [142, 232] relied on training candidate models from scratch to determine the accuracy scores needed for comparison. However, to circumvent the inefficiency of training each candidate model to convergence before throwing away all its parameters, recent NAS approaches [22, 25, 26] proposed a one-shot approach in which all candidate models are trained simultaneously through the concepts of supernet and shared weights. Briefly, the idea relies on specifying the search space as a single, multi-path overparameterized network model (i.e., a supernet) that encapsulates all candidate architectural designs within (i.e., subnets). In this case, the sampling of a candidate model from the supernet is achieved through selecting for each potential layer position a particular path reflecting a specific architecture choice, as in choosing a path representing a 3×3 convolution.

Then, the weights associated with the  $3 \times 3$  convolution are loaded within the supernet, used for the candidate model evaluation, and are updated in the next update step.

#### 1.3 Organization

The rest of the disseration is organized as follows. Chapter 2 discusses how to co-optimize dynamic neural networks design and deployment onto heterogeneous MPSoCs. Chapter 3 introduces our novel mapping-aware graph neural architecture search for heterogenous MPSoC deployment. Chapter 4 addresses the challenges of scheduling multi-model workloads on emerging 2.5D architectures, and presents a novel framework to effectively enact such scheduling. Chapter 5 moves on to discuss efficient split-computing approaches for Edge-AI autonomous system applications, and chapter 6 engages the offloading challenges with regards to maintaining guarantees on safety in the cases of autonomous driving. Chapter 7 presents our overall findings and insights from our studies, lays out our study limitations, and provides directions for future research.

# Chapter 2

# Optimizing Dynamic Neural Networks Design and Deployment onto Heterogeneous MPSoCs

#### 2.1 Introduction

The hardware era has witnessed the emergence of various computing devices, from powerful GPUs to tiny Micro-controllers. To meet the requirements of compute-intensive applications, such as Deep Learning workloads, MPSoCs are designed to incorporate heterogeneous computing units (CU) within the same die, typically sharing the same system memory (DRAM). This hardware architecture paradigm enables the collaborative usage of multiple CUs to accelerate different operations of the same application, hence providing energy savings and performance benefits. However, the causality between the hardware heterogeneity of MP-SoC and the obtained performance for similar and different operations remains an open research question. Indeed, some CUs (e.g., GPUs) can offer high execution speedup at the

cost of being energy-hungry, while others, such as NPUs, are power-friendly at the cost of being slow. Conventional deployment schemes lack a holistic overview of how heterogeneous CUs may behave regarding various computing workloads. In addition, the systematic approach of considering a single CU to deploy an entire application is suboptimal since it overlooks opportunities for further performance gains through maximizing the utilization of the MPSoC's hardware resources.

Recent works have shed light on the *computation mapping* problem for MPSoC by providing comprehensive modeling methodologies in [40,132,173,212] to characterize computing workloads performances. The resulting models are typically used to map computations onto CUs in a sequential pipeline fashion. However, for workloads exhibiting a high degree of parallelism, such as Neural Networks ( $\mathcal{N}\mathcal{N}$ ), there's still room for improvement by refashioning the execution pipeline into parallel stages running concurrently on different CUs, especially considering the inherent capacity for concurrency within  $\mathcal{N}\mathcal{N}$  layers such as convolutional and multi-head self-attention layers [66].

On the other hand, recent research works have introduced Dynamic Neural Networks (DyNNs) [69] which contrary to conventional *static* neural network models with fixed computational graphs, offer to adapt their model structure or parameters to suit the runtime context, offering resource efficiency at the edge while maintaining the models' utility. The motivation behind DyNNs being the in-the-wild deployment of machine learning models at the edge which makes them susceptible to considerable runtime variations. One prominent DyNN technique is early exiting which facilitates concluding the processing of the "easier" input samples at earlier layers of a model for resource efficiency. This feature is often realized through a multi-exit architecture that integrates intermediate classifiers onto a shared backbone model [140, 144, 186].

Typically, the design workflow of dynamic networks like multi-exit models initially assumes that a backbone architecture has been *optimally* designed to maximize performance on a

target task. Evidently, backbones in related works were either based on renowned state-of-the-art NN architectures, e.g., ResNets in [186], or models rendered through the design automation frameworks of Neural Architecture Search (NAS) [194]. This means that backbones were originally designed to serve as *standalone* static models. Thus, a subject of debate is whether such design optimality of these models would hold when auxiliary tasks are added – as in to serve as the backbone of a dynamic model.

Given this pretext, we identify several limitations of current practice for designing and deploying DyNNs onto heterogeneous MPSoCs:

- The backbone model architectures of DyNNs are not optimized for dynamic inference

- State-of-the-art NN design frameworks (e.g., NAS) do not characterize the runtime aspects of dynamic inference, potentially leading to suboptimal DyNN design

- The co-optimization synergy between DyNNs design, underlying heterogeneity of hardware, and DVFS configuration settings remain under-exploited.

#### 2.1.1 Novel Contributions

Addressing these limitations, we present the following contributions in this Chapter:

- We present HADAS [21], a novel hardware-aware Dynamic Neural Architecture Search

Framework for joint optimization of multi-exit DyNNs design and DVFS settings for

efficient edge operation. HADAS can be integrated on top of modern pretrained supernets of existing state-of-the-art NAS frameworks.

- We present Map-and-Conquer [23], a framework for transforming static neural networks to DyNNs with multiple inference stages leveraging heterogeneous pipelining parallelism across the model width dimension.

#### 2.2 Related Works

Dynamic Neural Networks. Dynamic Neural Networks serve as attractive solutions to scale computation according to the input complexity, providing latency speedup and energy gains. Incorporating dynamicity into NN inference has been widely studied for CNN architectures through early-exiting along the architecture's depth [144, 186] or width [225]. Early-exiting has also been successfully applied for emerging classes of models like Vision Transformers (ViT) [155, 224]. In the above works, the multi-exit networks have been manually designed based on heuristic choices of exits' positions, structure, and count conditioned on their respective backbone architecture [103]. Recent works [140, 225] have investigated the applicability of NAS techniques to automate the design of multi-exit networks, where the backbone and exits' design spaces can be jointly explored to reach superior DyNN architectures. However, a scalable, more generic solutions for designing DyNNs remaind lacking.

Computation mapping on MPSoCs. Recent MPSoCs contain diverse heterogeneous CUs that usually share system memory, making them more flexible for collaborative execution. Recent works have explored this specificity of MPSoC to optimize the execution of  $\mathcal{NN}$ . AxoNN and MEPHESTO [40, 132, 212] propose modeling strategies to characterize execution latency and energy consumption for computation mapping on the AGX Xavier MPSoC. Jedi [82] provides a framework built upon TensorRT to accelerate  $\mathcal{NN}$  via model parallelism to maximize throughput for batched inference. [87, 90] proposes evolutionary-based scheduling for NN layers on heterogeneous MPSoCs with DVFS by exploiting both data and model parallelism to optimize the throughput. DistrEdge [76] provides a detailed analysis of different model parallelism schemes for distributed computing over edge devices. However, none of the prior works have considered the design of dynamic NN in the computation mapping problem for collaborative execution on MPSoCs.

Dynamic hardware reconfiguration: Dynamically scaling NNs results in different com-

putational and energy footprints that require adapting the hardware configuration accordingly. In [52, 149], the hardware has been co-designed with the multi-exit networks using FPGAs, showcasing how further energy efficiency gains can be achieved through having specialized hardware for exits. Nevertheless, the considerable switching overheads of hardware configurations in FPGAs are not typically acceptable for runtime applications. A viable alternative came in the form of hardware reconfiguration through supported DVFS features, where the operational frequency can be scaled after exiting to preserve energy resources [108, 182].

# 2.3 HADAS: Hardware-Aware Dynamic Neural Architecture Search

We formulate the dynamic neural architecture search formulation, present the HADAS framework, and provide evaluation results on its efficacy compared to conventional approaches.

#### 2.3.1 Problem Formulation

As the combined design space size for the DyNNs and hardware configurations can be enormous, we characterize three separate subspaces to manage the joint optimization of their parameters as follows: (i) **The backbones** ( $\mathcal{B}$ ); which are models originally designed in a monolithic fashion for *static* inference with no adaptive behavior, (ii) **The exits** ( $\mathcal{X}$ ); which are the dynamic components to be integrated onto a backbone, and (iii) **The DVFS settings** ( $\mathcal{F}$ ); constituting the space of operational frequencies for the underlying hardware components. For the DyNNs, our reasons for designating  $\mathcal{B}$  and  $\mathcal{X}$  as separate subspaces are twofold: (a) To maintain the generality of the approach by having the  $\mathcal{X}$  subspace indifferent to the "type" of candidate backbones in  $\mathcal{B}$ , and (b) To leverage the existing infrastructure

of pretrained supernets from established NAS frameworks (as in [25,194]) so as to provide high-caliber backbone models for the  $\mathcal{B}$  subspace.

In order to rank candidate dynamic architectural designs, we denote  $\mathcal{S}$  and  $\mathcal{D}$  as generic performance objectives under *static* and *dynamic* deployments, respectively. Mainly,  $\mathcal{S}$  represents the backbone evaluations when designated as a fixed standalone model (e.g., baseline energy), whereas  $\mathcal{D}$  is for the evaluations of its dynamic variant after integrating the exits (e.g., average energy when effective mapping of inputs to exits). Hence, this implies a bi-level optimization problem with the  $\mathcal{B}$  as the outer-level subspace and  $(\mathcal{X}, \mathcal{F})$  as the inner-level:

$$b^* = \underset{b \in \mathcal{B}}{\operatorname{arg max}} \ \psi[\mathcal{S}(b), \mathcal{D}(x^*, f^* \mid b)]$$

(2.1)

$$s.t. \ x^*, f^* = \underset{x \in \mathcal{X}, f \in \mathcal{F}}{\operatorname{arg \, max}} \ \mathcal{D}(x, f \mid b)$$

(2.2)

where the global optimization objective to identify the ideal parameter combination  $(b^*, x^*, f^*)$  that maximizes a global function  $\psi$  combining the performance objectives of  $\mathcal{S}$  and  $\mathcal{D}$ . In practice, the underlying optimization objectives are conflicting by nature – e.g., the larger, expensive models enjoy higher accuracy scores and vice versa. Thus, the problem can be approached as a multi-objective optimization searching for Pareto optimal solutions.

#### 2.3.2 HADAS Framework

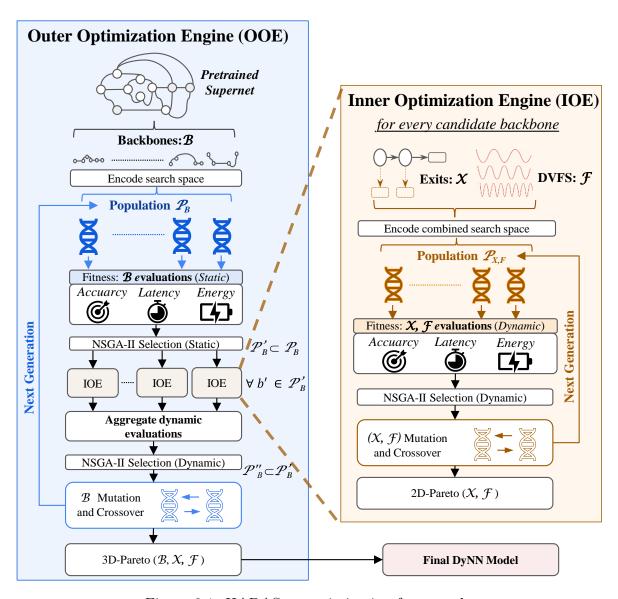

HADAS solves the bi-level optimization via a nested metaheuristic framework in Figure 2.1.

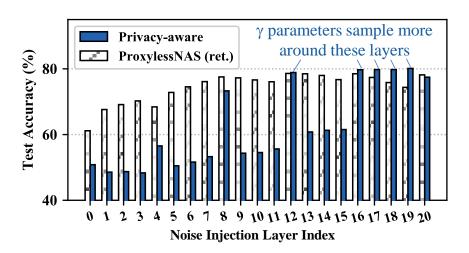

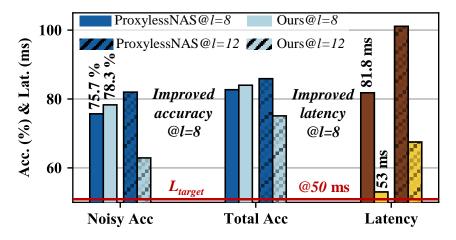

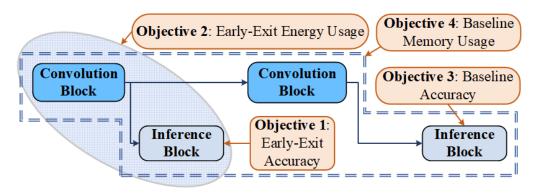

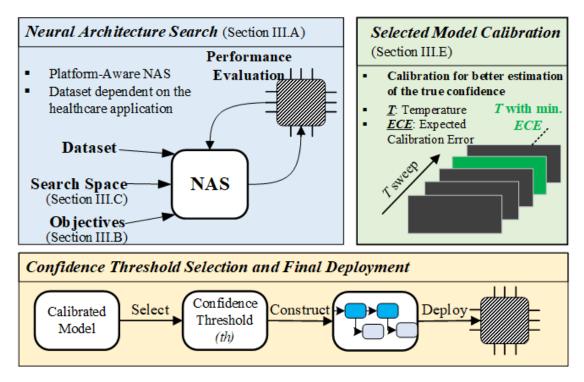

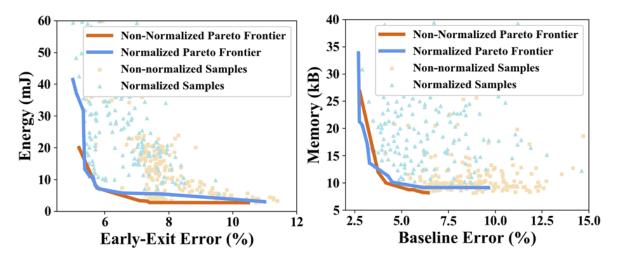

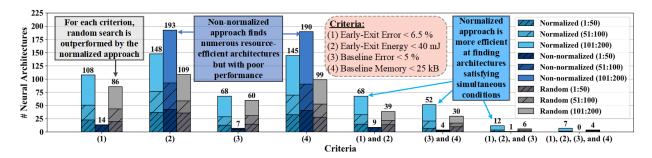

#### Outer Optimization Engine (OOE)