# UC Santa Barbara

**UC Santa Barbara Electronic Theses and Dissertations**

### Title

mmWave Massive MIMO for Multiuser Communication: From System Design to Hardware Demonstration

**Permalink** https://escholarship.org/uc/item/5s04h861

**Author** Farid, Ali Ahmed

Publication Date

2021

Peer reviewed|Thesis/dissertation

University of California Santa Barbara

# mmWave Massive MIMO for Multiuser Communication: From System Design to Hardware Demonstration

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Electrical and Computer Engineering

by

### Ali Ahmed Farid

Committee in charge:

Professor Mark Rodwell, Chair Professor Upamanyu Madhow Professor James Buckwalter Professor Umesh Mishra Professor Ali Niknejad

September 2021

The Dissertation of Ali Ahmed Farid is approved.

Professor Upamanyu Madhow

Professor James Buckwalter

Professor Umesh Mishra

Professor Ali Niknejad

Professor Mark Rodwell, Committee Chair

July 2021

# mmWave Massive MIMO for Multiuser Communication: From System Design to Hardware Demonstration

Copyright  $\bigodot$  2021

by

Ali Ahmed Farid

#### Acknowledgements

First and foremost, I would like to thank the almighty God (Allah) for his countless blessing and his great mercy supporting me till the end. If it were not for his help, I would not have reached this point.

With a deep sense of gratitude, I would like to thank my advisor, Professor Mark Rodwell, for his mentorship, guidance, and supervising my Ph.D. thesis. Prof. Rodwell was an advocate for my ambitious systems and demo scale projects. He supported and guided me to take my project from system-level design and modeling to circuit and chip design, then to packaging and building arrays; I am so indebted for all his support.

I would like to thank my Ph.D. committee members: Professor Upamanyu Madhow, Professor James Buckwalter, and Professor Umesh Mishra for overseeing my research, providing constructive feedback on points that needed improvements, and for all their support. I am so grateful for our weekly meetings with Prof. Madhow's and Prof. Buckwalter's teams. The collaboration we had was very productive and instructive.

I want to thank all the past and present Rodwell group members; Ahmed Ahmed, Arda Simsek, Utku Soylu, Seong-Kyun Kim, Prof. Munkyo Seo and Rob Maurer. They all played a role in my research, and I learned a lot by interacting with every one of them. Arda was instrumental in the IC design efforts and laid much of the groundwork upon which I built my transceivers. Ahmed's assistance in the packaging efforts made this project a reality.

It was my pleasure working with Madhow's students, Mohammed Abdelghany and Dr. Maryam Rasekh. Their help, guidance, and assistance were instrumental, and I am so grateful for all that they taught me. None of the system-level work in this thesis would have been done without Mohammed's and Maryam's assistance and guidance.

I wouldn't have done any of the MIMO demos without Aditya Dhananjay's help and efforts. Aditya is a very experienced system architect with broad knowledge in signal processing and FPGA coding. He never saved time or effort helping me doing my link measurements, and I will always be grateful for his support and dedication.

It was a blessing being part of ComSenTer and the SRC community; we got the opportunity to interact and work with the world's best researchers across different universities. I am very grateful for our collaboration and interaction with Professor Ali Niknejad's UC Berkeley group (Anita Flynn, Lorenzo Iotti, James Dunn, Nima Baniasadi). I am also so grateful for Prof. Gabriel Rebeiz and all his valuable comments and bits of advice on the packaging and assembly efforts. Finally, it was a pleasure interacting with our industry liaisons and SRC industry members; I am incredibly grateful for all the interaction and collaboration we had with the Samsung Research America team (Gary Xu, Daquan Huang, Navneet Sharma, Shadi Abu-Surra, Hamidreza Memar, Wunsok Choi).

Finally, I would like to thanks my family for their unconditional love and support. Thanks for always being there for me.

### Curriculum Vitæ Ali Ahmed Farid

### Education

| 2021 | Ph.D. in Electrical and Computer Engineering (Expected), University of California, Santa Barbara. |

|------|---------------------------------------------------------------------------------------------------|

| 2016 | M.Sc in Electronics and Electrical Communications Engineering,<br>Cairo University, Cairo, Egypt. |

| 2012 | B.S. in Electronics and Electrical Communications Engineering,<br>Cairo University, Cairo, Egypt. |

### **Professional Experience**

| 9/2016 -8/2021  | Research Assistant at the High-Speed Electronics Group at University of California, Santa Barbara, USA. |

|-----------------|---------------------------------------------------------------------------------------------------------|

| 6/2019 -12/2019 | Summer Internship at Samsung Research America, Dallas, Texas, USA.                                      |

| 6/2017 - 9/2017 | Summer Internship at Goodix Inc, Irvine, CA, USA.                                                       |

| 9/2012 - 8/2016 | Analog/RF IC Design Engineer, Atmel Corp., Cairo, Egypt.                                                |

### Publications

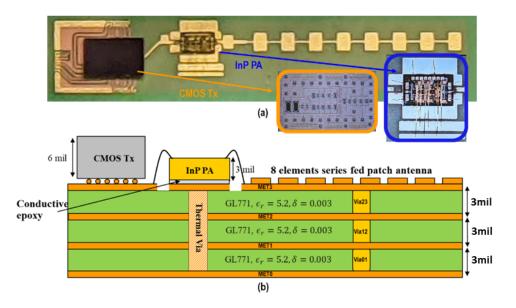

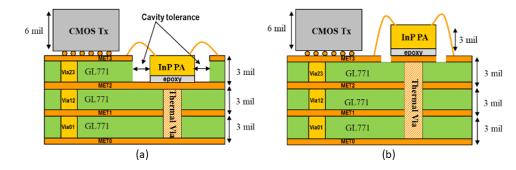

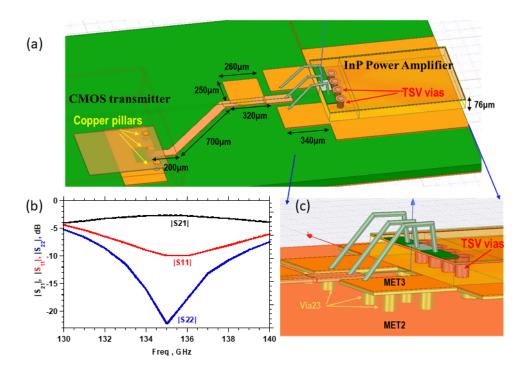

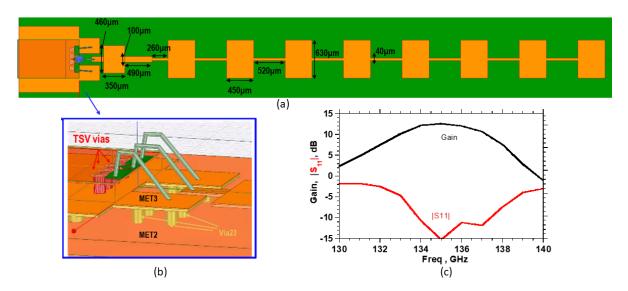

- 1. A. A. Farid, et al., "A 27.5dBm EIRP D-Band Transmitter Module on a Ceramic Interposer" 2021 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Atlanta, GA, USA, 2021

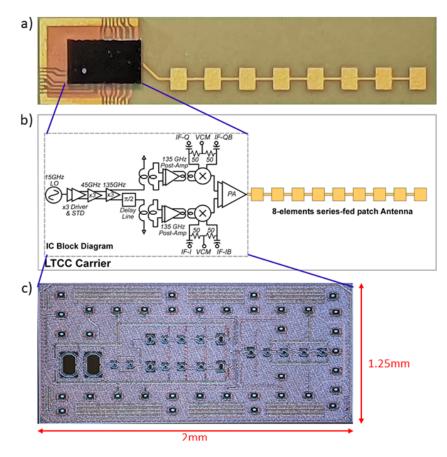

- 2. A. A. Farid, et al., "A Packaged 135GHz 22nm FD-SOI CMOS Transmitter on an LTCC Carrier" 2021 IEEE International Microwave Symposium (IMS), Atlanta, GA, USA, 2021

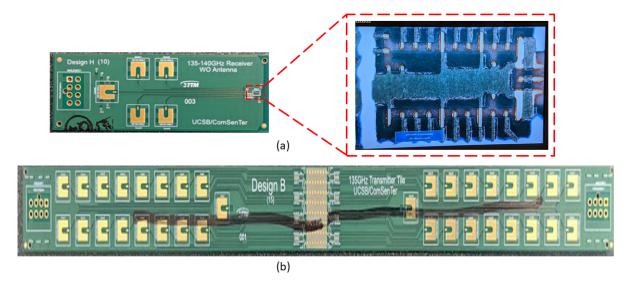

- 3. A. A. Farid, et al., "An 8-Channel 135GHz CMOS/InP/LTCC MIMO Transmitter Array Tile Module with 38.5dBm EIRP" 2021 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), 2021

- 4. A. A. Farid, et al., "135GHz CMOS / LTCC MIMO Receiver Array Tile Modules" 2021 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), 2021

- 5. M. Rodwell, A. A. Farid, et al., "100-300GHz Wireless: ICs, Arrays, and Systems," 2021 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), 2021

- A. A. Farid, et al., "Dynamic Range Requirements of Digital vs. RF and Tiled Beamforming in mm-Wave Massive MIMO" 2021 IEEE Radio and Wireless Symposium (RWS), 2021, pp. 46-48

- et al A. A. Farid., "End-to-end 140 GHz Wireless Link Demonstration with Fully-Digital Beamformed System," 2021 IEEE International Conference on Communications Workshops (ICC Workshops), 2021, pp. 1-6

- 8. M. Abdelghany, A. A. Farid, et al., "A design framework for all-digital mmWave massive MIMO with per-antenna nonlinearities," 2021 IEEE Transactions on Wireless Communications.

- A. S. H. Ahmed, M. Seo, A. A. Farid, et al., "A 200mW D-band Power Amplifier with 17.8% PAE in 250-nm InP HBT Technology," 2020 15th European Microwave Integrated Circuits Conference (EuMIC), 2021, pp. 1-4

- A. S. H. Ahmed, M. Seo, A. A. Farid, et al. "A 140GHz power amplifier with 20.5dBm output power and 20.8% PAE in 250-nm InP HBT technology," 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 2020, pp. 492-495.

- A. Simsek, A. S. H. Ahmed, A. A. Farid, et al., "A 140GHz Two-Channel CMOS Transmitter Using Low-Cost Packaging Technologies," 2020 IEEE Wireless Communications and Networking Conference Workshops (WCNCW), Seoul, Korea (South), 2020, pp. 1-3,

- A. A. Farid, et al., "A Broadband Direct Conversion Transmitter/Receiver at D-band Using CMOS 22nm FDSOI," IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2019

- M. Abdelghany, A. A. Farid, et al., "Towards All-digital mmWave Massive MIMO: Designing around Nonlinearities," 2018 52nd Asilomar Conference on Signals, Systems, and Computers, Pacific Grove, CA, USA, 2018

- 14. A. S. H. Ahmed, A. Simsek, A. A. Farid, et al., "A W-Band transmitter channel with 16dBm output power and a receiver channel with 58.6mW DC power consumption using heterogeneously integrated InP HBT and Si CMOS technologies," 2019 (IMS), Boston, MA, USA, 2019.

- A. S. H. Ahmed, A. A. Farid, M. Urteaga and M. J. W. Rodwell, "204GHz Stacked-Power Amplifiers Designed by a Novel Two-Port Technique," 2018 13th European Microwave Integrated Circuits Conference (EuMIC), Madrid, 2018, pp. 29-32.

#### Patents

1. Ali Farid, et al., "Successive Approximation Register (SAR) Analog to Digital Converter (ADC) with Switchable Reference Voltage," US Patent. 10461767

- 2. Ali Farid, et al., "Successive approximation register (SAR) analog to digital converter (ADC) dynamic range extension," US Patent. 10491232

- 3. Ali Farid, et al., "Data Converters Systematic Error Calibration using on chip precise reference," US Patent. 10630305.

- 4. M.Aboudina, Ali Farid, et al., "Efficient successive approximation register analog to digital converter," US Patent. 10735017 .

#### Abstract

## mmWave Massive MIMO for Multiuser Communication: From System Design to Hardware Demonstration

by

#### Ali Ahmed Farid

Future trends in wireless communication systems show rapid growth in mobile data traffic. The number of subscribed users per mobile base station grows linearly with time. Emerging immersive media formats and applications (i.e., HD/UHD, 360 videos, AR/VR) requires a higher data rate and larger channel bandwidth. Millimeter-Wave massive multiuser multiple-input multiple-output (MU-MIMO) is a potential candidate for high-capacity, high data rate wireless base stations. The available mm-wave spectrum between 100GHz to 300GHz is large. The small carrier wavelength ( $\lambda$ ) permits compact arrays with many antennas; hence spatial multiplexing can be utilized to increase the system capacity.

This thesis explores system architectures, transceiver circuit design, and high-performance packaging technologies suitable for mm-wave and sub-THz multiuser massive MIMO arrays. First, we present a comprehensive study between potential mm-wave MU-MIMO architectures (all-digital, hybrid, and fully-RF) in terms of system dynamic range requirement. We draw guidelines on the required system front-end 1-dB compression point and the required analog-to-digital converter resolution for each architecture. We also illustrate the impact of system power control and antenna load factor on relaxing the dynamic range requirements. Next, we present the core elements for our massive MIMO arrays. We designed and tested a single-channel direct conversion transmitter (Tx) and a single-channel direct conversion receiver (RX) using Global-Foundries 22FD-SOI technology, with a record measured 3-dB modulation bandwidth of 20GHz. The Rx has 27dB conversion gain and -30dBm P-1dB. The Tx has a saturated output power (Psat) of 3dBm. Then, we used those transmitter and receiver chips and demonstrated two different packaging technologies in building our mm-wave MU-MIMO arrays. We designed, fabricated, and tested tiles of 8-elements transmitters/receivers, integrated with an on-package series fed patch antennas, assembled on high-performance laminate material and on Kyocera low permittivity ceramic interposer. We illustrate the pros and cons of each packaging technology and show the superiority of the ceramic interposers for mm-wave applications and highly dense arrays.

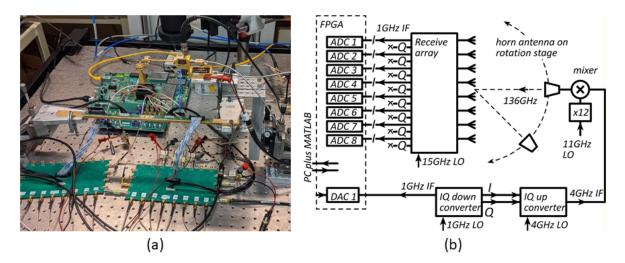

Finally, we integrated our MU-MIMO transmitter/receiver tiles with Xilinx ZCU111 FPGA and demonstrated the world's first mm-wave MU-MIMO arrays at 135GHz. Our transmitter MU-MIMO array has a record transmitter effective isotropic radiated power of 39dBm, a field of view of +/-15 degree. It can support a wide range of modulation schemes (i.e., QPSK, 16QAM). The integrated transmitter and receiver MU-MIMO arrays can be used for a broad range of applications, including single beam and multibeam phased arrays, wireless backhaul, imaging, and radar applications.

# Contents

| Cı | irrici                           | ulum Vitae                                                                                                                                       | vi                                                                 |

|----|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Ał | ostra                            | $\operatorname{ct}$                                                                                                                              | ix                                                                 |

| Li | st of                            | Figures                                                                                                                                          | xiv                                                                |

| Li | st of                            | Tables                                                                                                                                           | xxi                                                                |

| 1  | <b>Intr</b><br>1.1<br>1.2<br>1.3 | oduction         Millimeter Wave Wireless Communication         Dissertation Contributions and Organization         Permissions and Attributions | <b>1</b><br>1<br>4<br>7                                            |

| 2  |                                  | Imeter-Wave Multiuser Massive MIMO Architecture Choice: Dig-Hybrid or RF?Introduction                                                            | 8<br>8<br>10<br>11<br>11<br>14<br>15<br>15<br>15<br>20<br>23<br>24 |

| 3  |                                  | adband transceiver design at D-band using GF 22nm FDSOI CMOSanologyIntroductionTechnology Characterization3.2.1Transistor Footprint              | <b>25</b><br>25<br>26<br>26                                        |

|          |      | 3.2.2 Transistor Characteristics                                                                                             |            |

|----------|------|------------------------------------------------------------------------------------------------------------------------------|------------|

|          | 3.3  | 0                                                                                                                            | 28         |

|          |      |                                                                                                                              | 29         |

|          |      |                                                                                                                              | 31         |

|          |      |                                                                                                                              | 35         |

|          | 3.4  | 8                                                                                                                            | 87         |

|          |      |                                                                                                                              | 88         |

|          | 3.5  |                                                                                                                              | <b>9</b>   |

|          |      | 3.5.1 Receiver Measurements                                                                                                  | <b>8</b> 9 |

|          |      | 3.5.2 Transmitter Measurements                                                                                               | 1          |

|          | 3.6  | Conclusion                                                                                                                   | 13         |

| 4        | Pac  | kaging Technologies for mm-wave Massive MIMO Arrays 4                                                                        |            |

|          | 4.1  |                                                                                                                              | 15         |

|          |      | 0 0 0                                                                                                                        | 8          |

|          | 4.2  | 0                                                                                                                            | 9          |

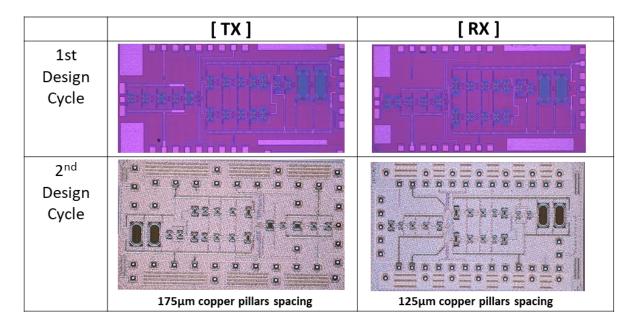

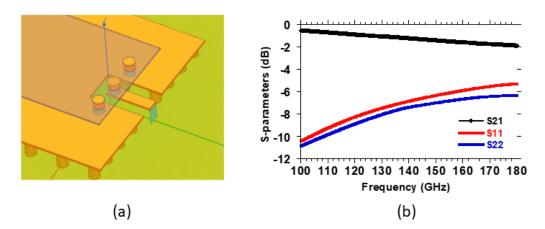

|          |      | 4.2.1 D-band Transmitter and Receiver Chips with GF Copper Pillars . 5                                                       | 52         |

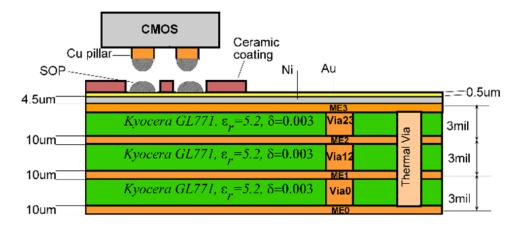

|          | 4.3  | Packaging Material and Technology                                                                                            | 66         |

|          | 4.4  | A Fully Packaged D-Band MIMO Array on a High-Performance Laminate                                                            |            |

|          |      | $Material \dots \dots$ | 57         |

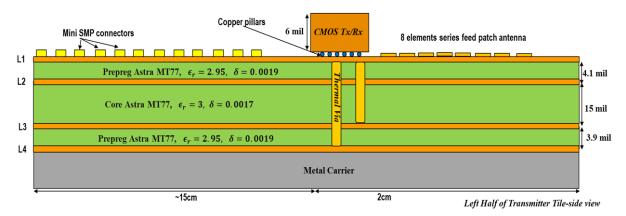

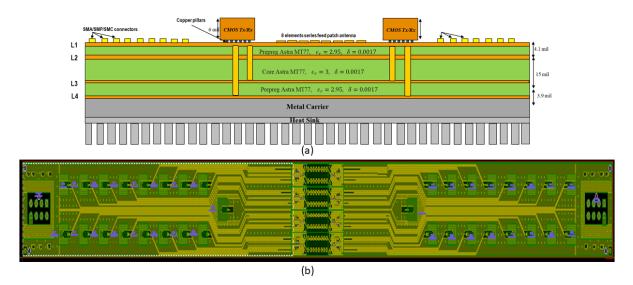

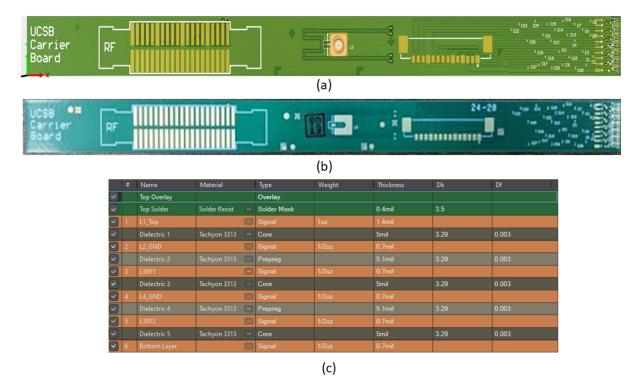

|          |      | 4.4.1 PCB Stack Build-up                                                                                                     | 68         |

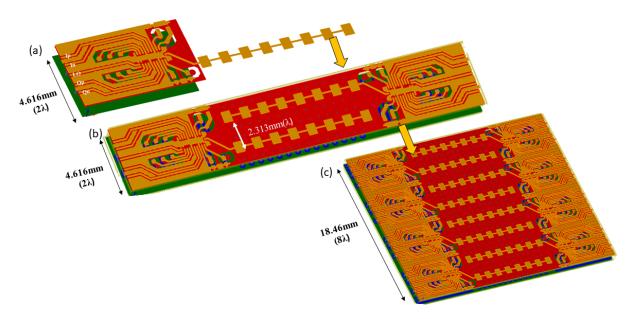

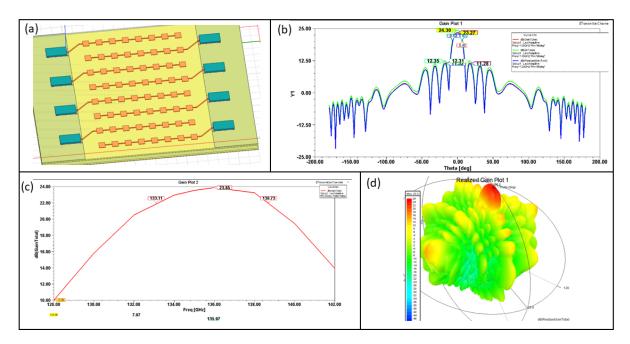

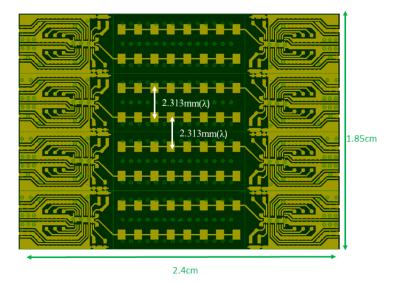

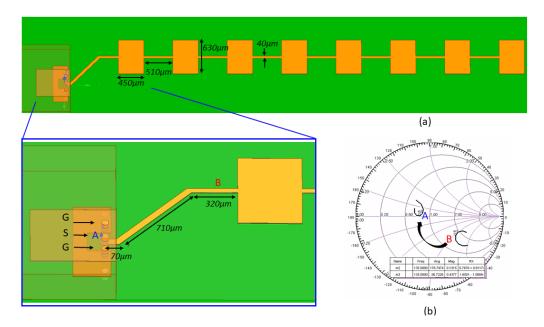

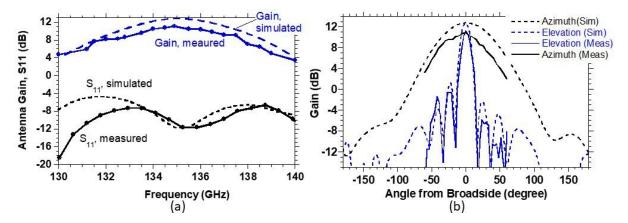

|          |      | 4.4.2 8-Elements Series-Fed Patch Antenna                                                                                    | 59         |

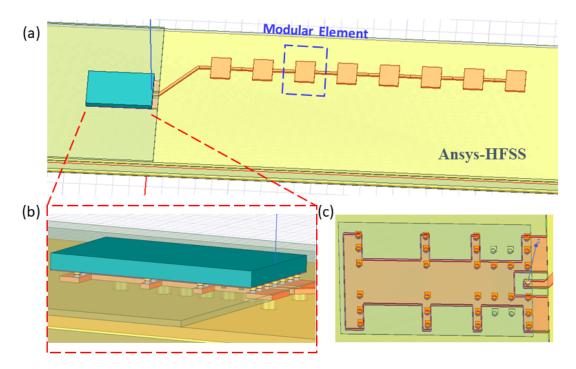

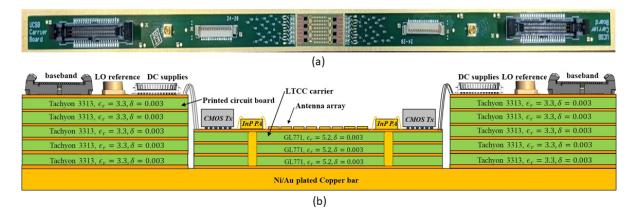

|          |      | 4.4.3 MIMO 1-D Tile Frontend Development                                                                                     | 51         |

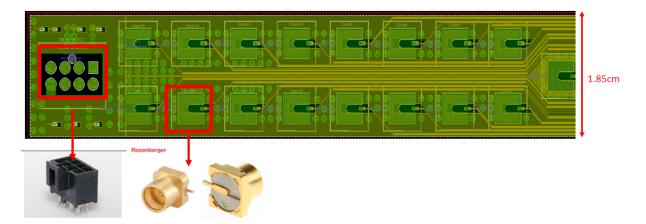

|          |      | 4.4.4 MIMO 1-D Tile Backend Development                                                                                      | 52         |

|          |      | 4.4.5 Integrated 1-D MIMO Tile on Astra MT77 High-performance Lam-                                                           |            |

|          |      |                                                                                                                              | 64         |

|          |      | 4.4.6 Assembly challenges with the MIMO tile on High-Performance PCB 6                                                       | 5          |

|          | 4.5  | Conclusion                                                                                                                   | 66         |

| <b>5</b> | Full | y Packaged D-Band Tx/Rx Multiuser MIMO Tiles using LTCC                                                                      |            |

| -        |      | riers 6                                                                                                                      | 8          |

|          | 5.1  | Introduction                                                                                                                 | 58         |

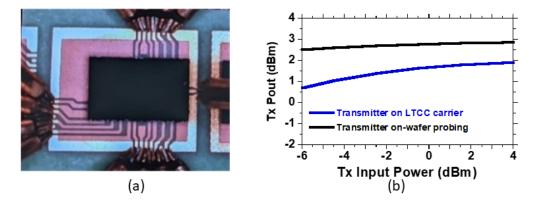

|          | 5.2  | Low Power Single Channel D-band Transmitter on LTCC Carrier 6                                                                | 59         |

|          |      | 5.2.1 Ceramic Carrier Design                                                                                                 | 0          |

|          |      | ÷                                                                                                                            | 0          |

|          |      |                                                                                                                              | 2          |

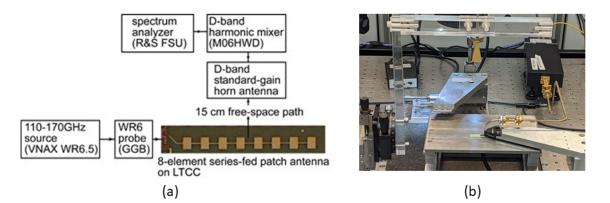

|          |      |                                                                                                                              | '4         |

|          | 5.3  |                                                                                                                              | 7          |

|          |      |                                                                                                                              | 8          |

|          |      | 0                                                                                                                            | <b>'</b> 9 |

|          |      |                                                                                                                              | 30         |

|          |      | 0                                                                                                                            | 30         |

|    | 5.4            | High-Power 8-channels 135GHz MIMO Hub Transmitter Tile Module | 87  |

|----|----------------|---------------------------------------------------------------|-----|

|    |                | 5.4.1 MIMO Hub Transmitter Core                               | 87  |

|    |                | 5.4.2 MIMO Hub Transmitter Backend                            | 88  |

|    |                | 5.4.3 MIMO Hub Transmitter Module Integration                 | 89  |

|    | 5.5            | Low-Power 8-channels 135GHz MIMO Hub Transmitter Tile Module  | 91  |

|    | 5.6            | Eight-channels 135GHz MIMO Hub Receiver Tile Module           | 92  |

|    | 5.7            | conclusion                                                    | 94  |

| 6  | MI             | O Demonstration                                               | 96  |

|    | 6.1            | Introduction                                                  | 96  |

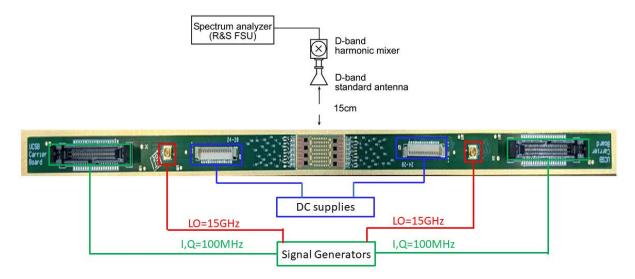

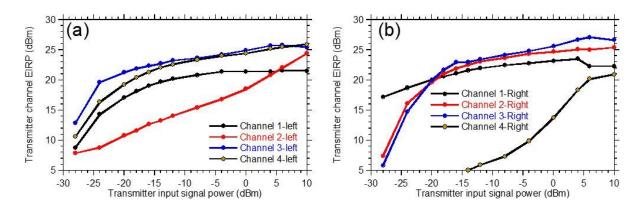

|    | 6.2            | Transmitter Array/Tile Demonstration                          | 97  |

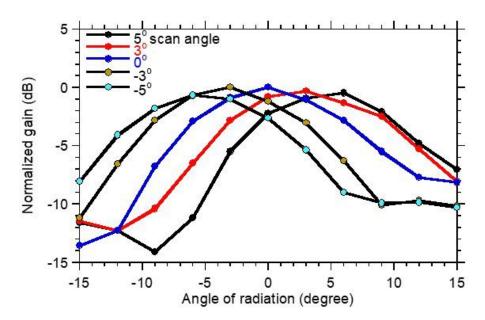

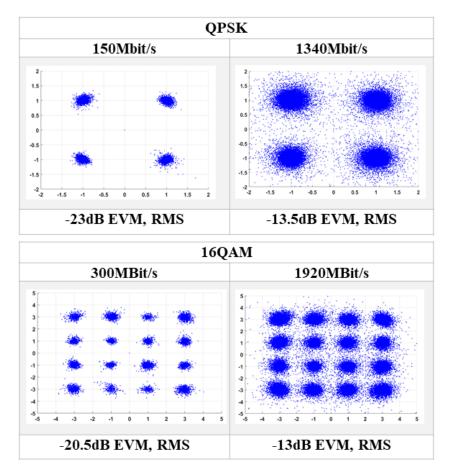

|    |                |                                                               | 99  |

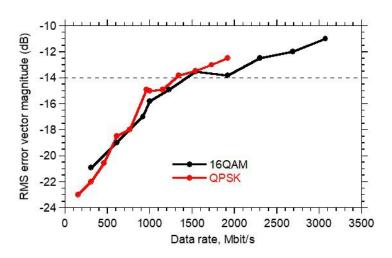

|    |                |                                                               | .00 |

|    |                | 6.2.3 Multi-Beam Experiment                                   | 02  |

|    |                | 6.2.4 Transmitter Array Summary                               | .03 |

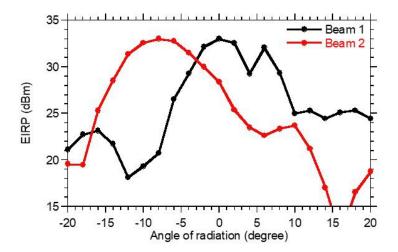

|    | 6.3            | Receiver Array/Tile Demonstration                             | .04 |

|    |                | 6.3.1 Receiver Array Radiation pattern                        | .05 |

|    |                | 6.3.2 Receiver Array Wireless Link                            | .07 |

|    |                | 6.3.3 Receiver Array Summary                                  | .08 |

| 7  | Con            | elusions and Future Work 1                                    | 10  |

| Bi | Bibliography 1 |                                                               |     |

end

# List of Figures

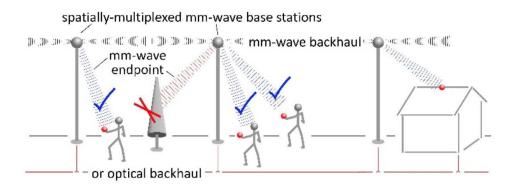

| 1.1 | Spatially multiplexed networks for multi-Gigabit mobile and residential/office communication [1].                                                  | 2  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

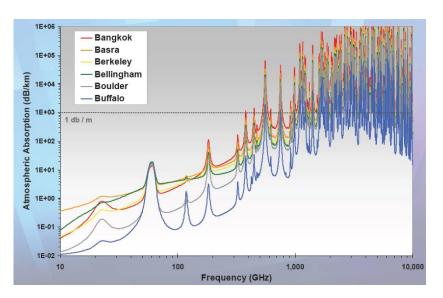

| 1.2 | Approximate sketch of atmospheric attenuation vs. frequency for different                                                                          | 2  |

|     | cities $[2]$                                                                                                                                       | 3  |

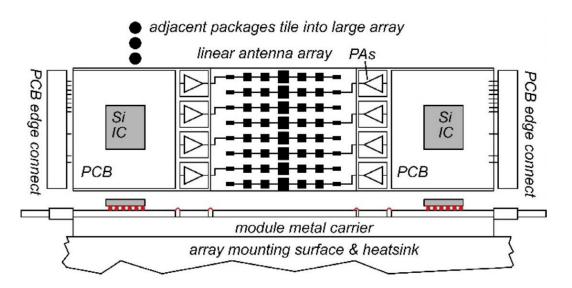

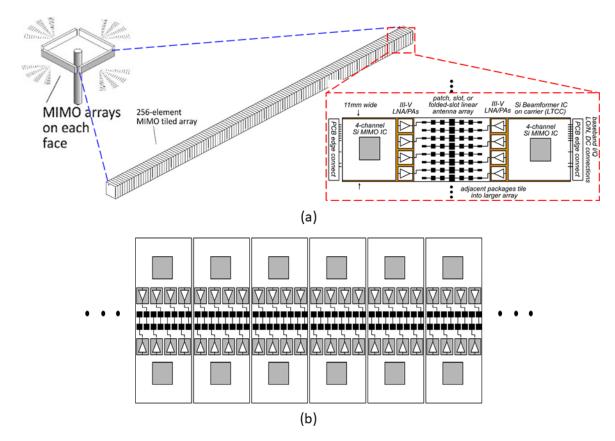

| 1.3 | Array tile design for linear arrays providing beam steering in azimuth but                                                                         |    |

|     | not elevation [1]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                | 4  |

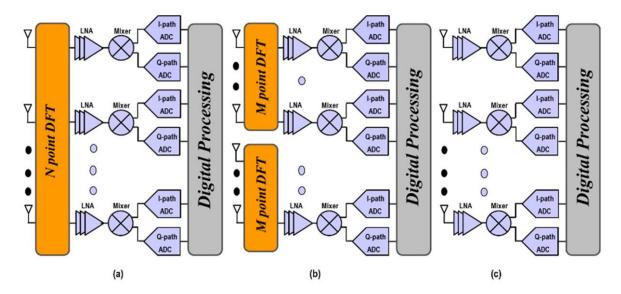

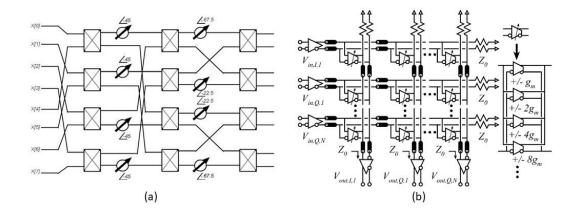

| 2.1 | Multiuser massive MIMO beamforming architectures: (a) RF-beamforming                                                                               |    |

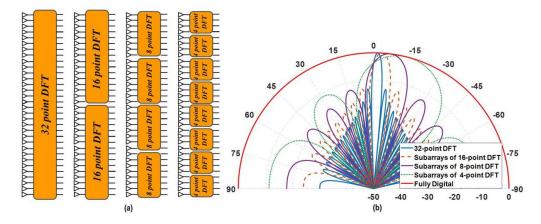

| 0.0 | (b) Array of subarrays (c) All-digital beamforming [11]                                                                                            | 9  |

| 2.2 | (a) RF beamforming architectures (b) and corresponding radiation pat-<br>terns, at the DFT outputs for a 32-point DFT (the fully RF architecture), |    |

|     | for 2 parallel subarrays having 16-point DFTs, for 4 parallel subarrays                                                                            |    |

|     | having 8-point DFTs, and for 8 parallel subarrays having 4-point DFTs.                                                                             |    |

|     | [11]                                                                                                                                               | 11 |

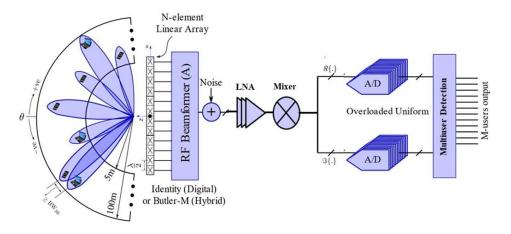

| 2.3 | mmWave multiuser massive MIMO system model with a fixed frontend matrix, this matrix deploys N-point DFT for fully-RF, or N/M M-point              |    |

|     | DFT for hybrid or identity matrix for all-digital solution. [11]                                                                                   | 12 |

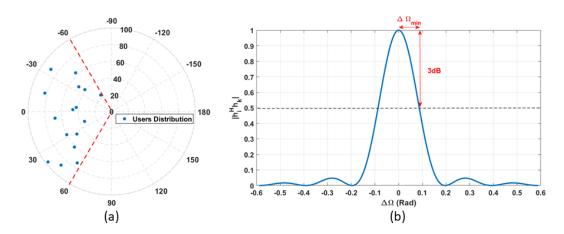

| 2.4 | (a) Users distribution around base station (b) Normalized correlation be-                                                                          |    |

|     | tween two users with spatial frequency difference of $\Delta\Omega$ . Note that the                                                                |    |

|     | closest users, depicted by red arrow, are separated by larger or equal to                                                                          | 10 |

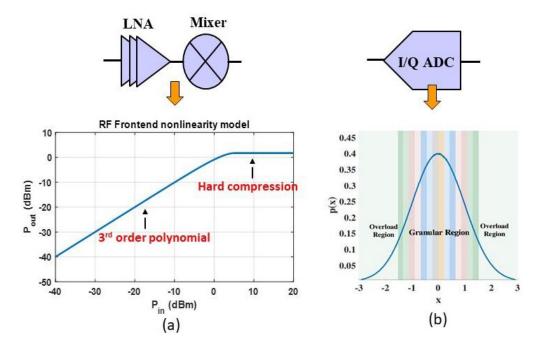

| 2.5 | half the 3 dB beamwidth.)                                                                                                                          | 13 |

| 2.0 | compression (b) Histogram of I and Q baseband components along with                                                                                |    |

|     | ADC quantization bins. [16]                                                                                                                        | 14 |

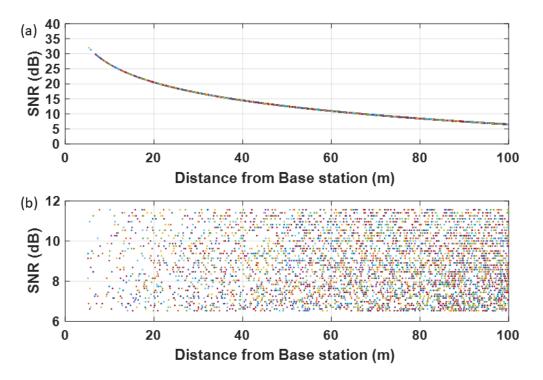

| 2.6 | SNR at the array for each user(a)without power control (b) with 5-dB                                                                               |    |

| ~ - | power control                                                                                                                                      | 16 |

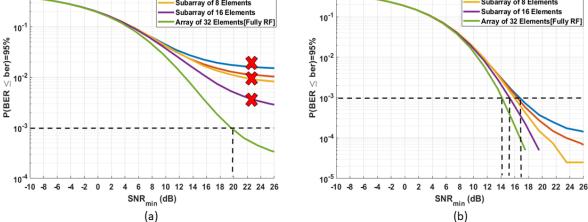

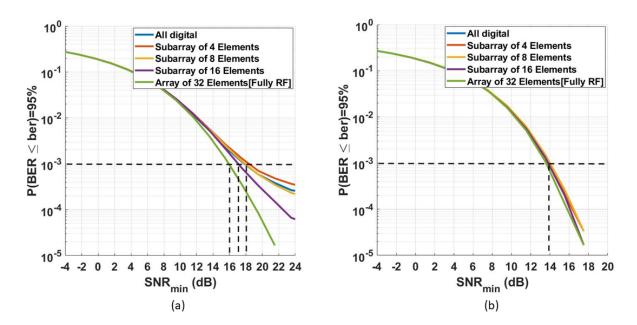

| 2.7 | BER that 95% of users achieve vs SNR at 100m $(SNR_{min})$ for $\beta = 1/2$<br>(a) using 3-bits ADC (b) using 4-bits ADC. (W/O power control)     | 17 |

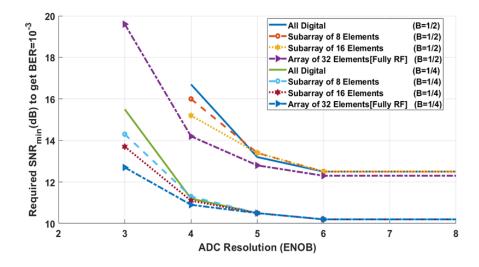

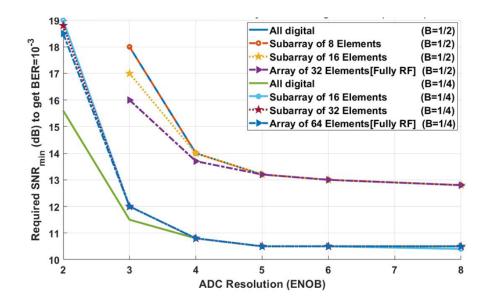

| 2.8 | ADC performance summary for different architecture and different load                                                                              | 11 |

|     | factors (W/O power control)                                                                                                                        | 17 |

|     |                                                                                                                                                    |    |

| 2.9            | BER that 95% of users achieve vs SNR at 100m $(SNR_{min})$ for $\beta = 1/2$<br>(a) using 3-bits ADC (b) using 4-bits ADC. (With 5-dB power control) .                                                                          | 18       |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.10           | ADC performance summary for different architecture and different load factors (With 5-dB power control)                                                                                                                         | 19       |

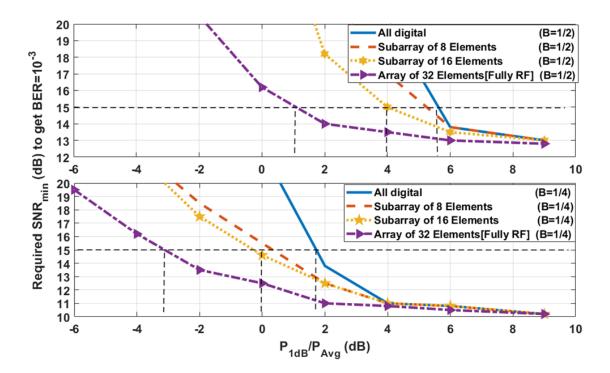

| 2.11           | P1dB specification for different architectures and different load factors (W/O power control).                                                                                                                                  | 21       |

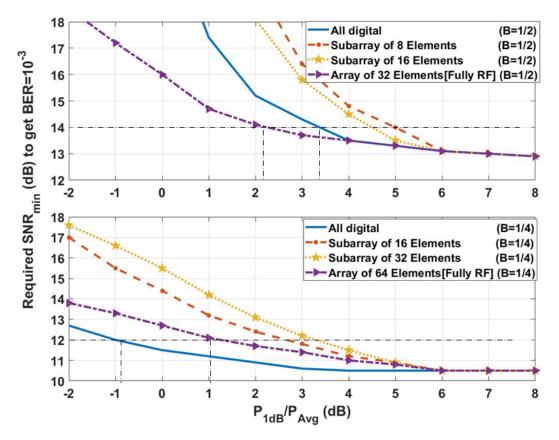

| 2.12           | P1dB specification for different architectures and different load factors<br>(With 5-dB power control).                                                                                                                         | 22       |

| 2.13           | (a) 8x8 Butler Matrix (b) 4x4 Analog Beamforming Matrix                                                                                                                                                                         | 23       |

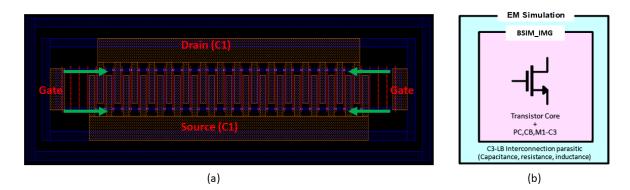

| 3.1            | SLVT Transistor footprint: (a) layout with gate relaxation. (b) parasitic extraction model                                                                                                                                      | 26       |

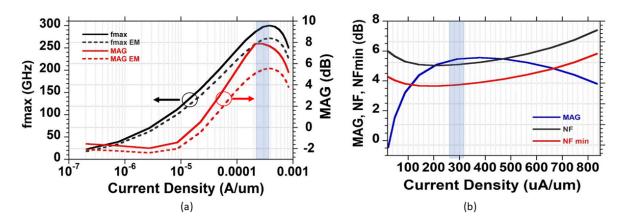

| 3.2            | Transistor characteristics (a) Transistor $f_{max}$ and $MAG$ referenced to bot-<br>tom Metal layer (M1) and to the top Metal layer (AL) (b) Transistors noise<br>figure (NF) and $NF_{min}$                                    | 27       |

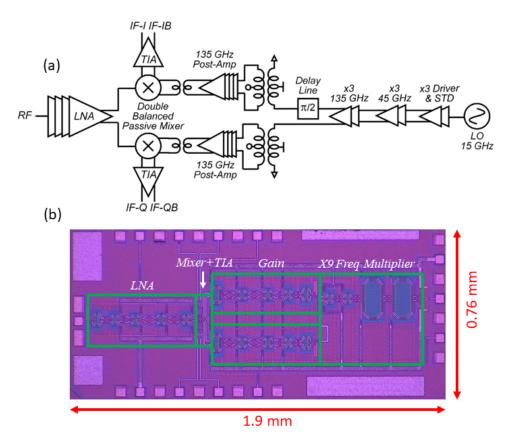

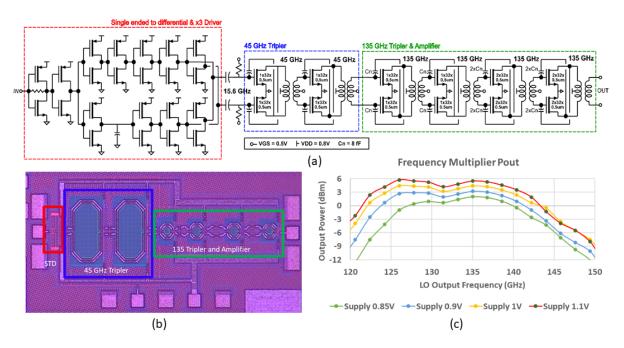

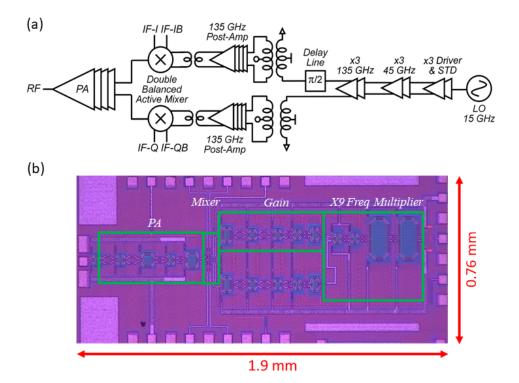

| 3.3            | D-band single-channel direct conversion receiver (a) circuit block diagram<br>and (b) chip micrograph. The die area is 1.9mm x 0.76mm including pads.                                                                           | 28       |

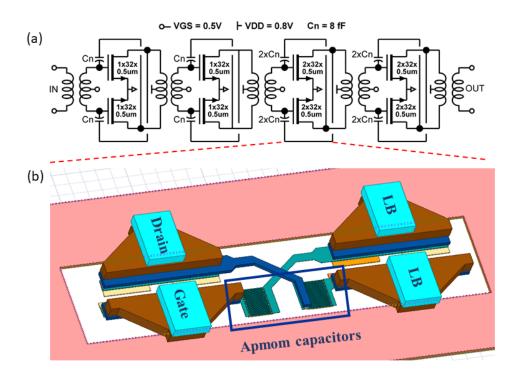

| 3.4            | (a) Circuit diagram of a 4-stage broadband LNA/PA using staggered tun-<br>ing (b) EM modeling of the cross coupled pair                                                                                                         | 20<br>29 |

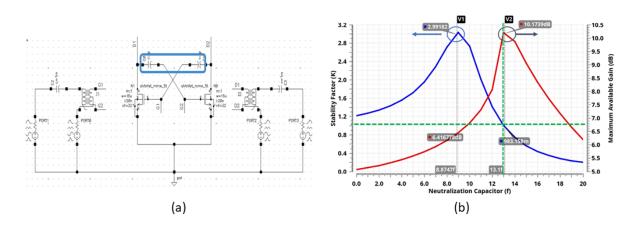

| 3.5            | Single differential pair gain stage (a) test bench to select the neutralization                                                                                                                                                 | 20<br>30 |

| 3.6            | Single differential pair gain stage (a) test bench to select the neutralization capacitance value, (b)simulated K-factor & MAG Vs neutralization cap value                                                                      | 30       |

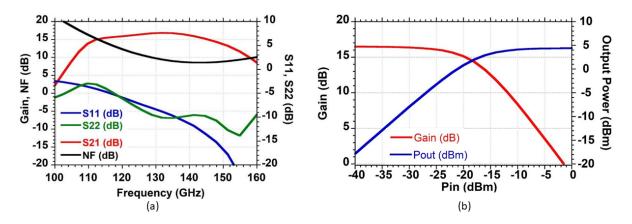

| 3.7            | LNA/PA simulated (a) S-parameters and Noise Figure, (b)large signal gain and $P_{sat}$                                                                                                                                          | 31       |

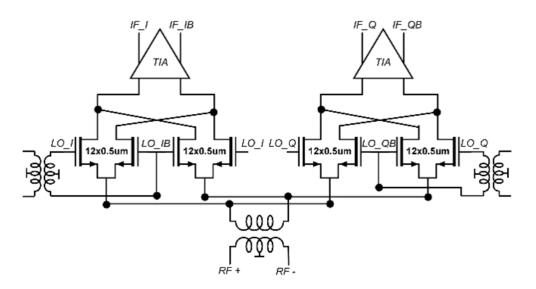

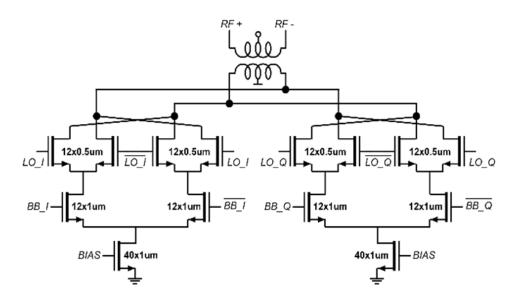

| 3.8            | Circuit diagram of the $(I/Q)$ down conversion mixer, followed by TIA .                                                                                                                                                         | 32       |

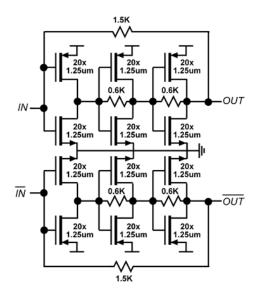

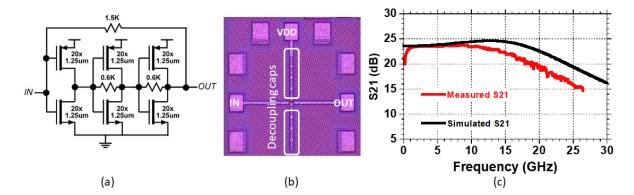

| 3.9            | circuit diagram of pseudo-differential TIA                                                                                                                                                                                      | 33       |

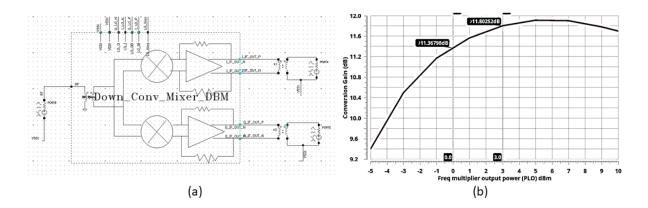

| $3.10 \\ 3.11$ | Integrated Mixer and TIA (a) schematic (b) conversion gain Vs LO power<br>TIA test structure (a) schematic for the single ended test structure (b) chip<br>micrograph of the TIA (c)simulation vs. measurement for single ended | 34       |

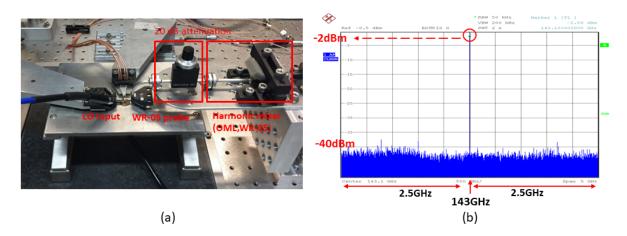

| 3.12           | TIA test structure                                                                                                                                                                                                              | 34       |

| 3.13           | (a) Test bench used to test multiplier output spectrum (b) multiplier out-                                                                                                                                                      | 35       |

| 3.14           | put spectrum at 143GHz with 5GHz span<br>D-band single channel direct conversion transmitter (a) circuit block di-<br>agram (b) chip micrograph, including pads. The die area is 1.9mm x                                        | 36       |

| 3.15           | 0.76mm                                                                                                                                                                                                                          | 37       |

|                | coupled                                                                                                                                                                                                                         | 38       |

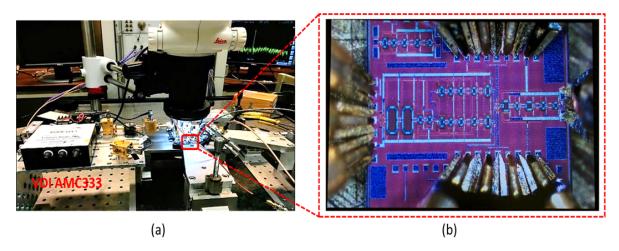

| 3.16 | Receiver on wafer testing setup (a) Conversion gain and linearity measurement setup, (b) IQ, RF, and LO signal feed with GGB probes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

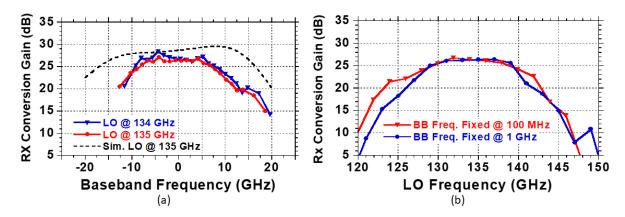

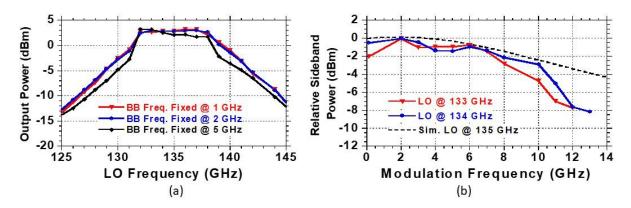

| 3.17 | a) Receiver conversion gain vs. baseband frequency with a fixed LO frequency (b) Receiver conversion gain vs. LO frequency with fixed baseband                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

|      | frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40       |

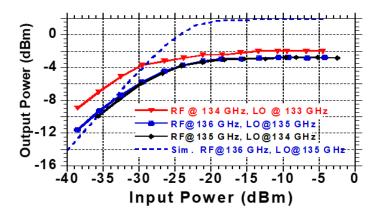

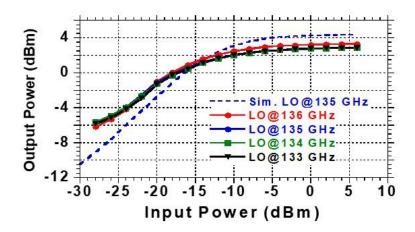

| 3.18 | Receiver normalized output power vs. input power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40       |

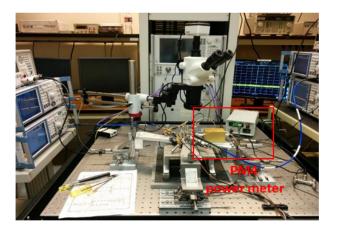

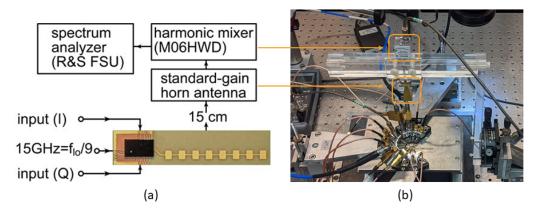

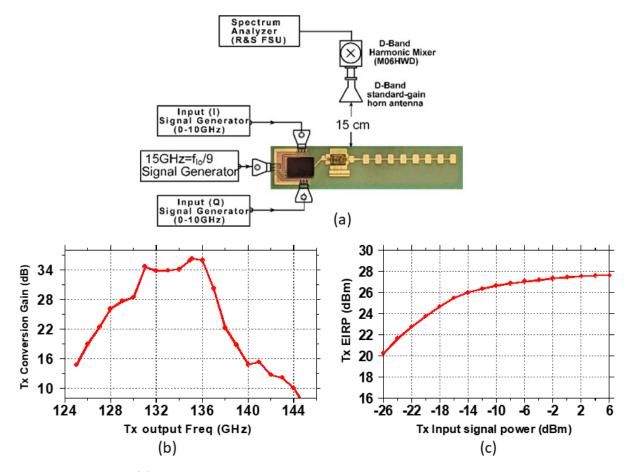

| 3.19 | Transmitter measurement setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41       |

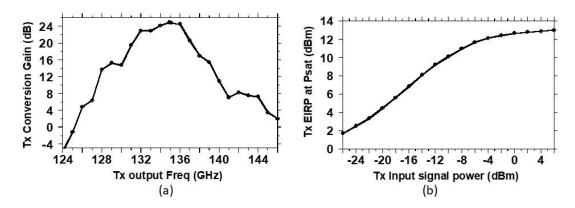

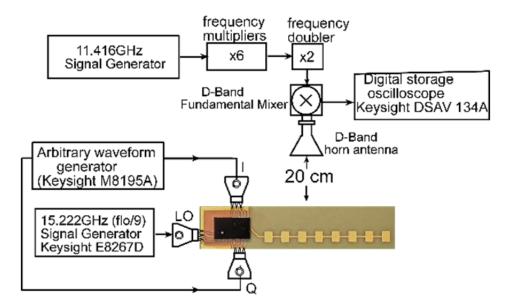

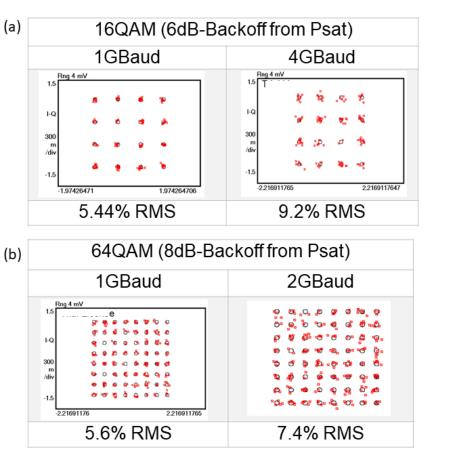

| 3.20 | Transmitter characteristics. (a) Saturated output power as a function of carrier frequency, with a -3 dBm baseband input signal, this showing an 8 GHz RF tuning range. (b) Modulation sideband power as a function of modulation frequency, this showing a 8GHz (SSB) modulation bandwidth.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42       |

| 3.21 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|      | 18dB gain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42       |

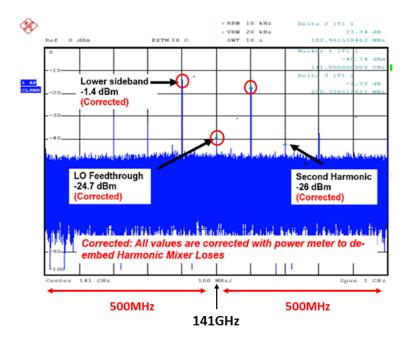

| 3.22 | Transmitter output spectrum with center frequency 141GHz and 100MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|      | input signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43       |

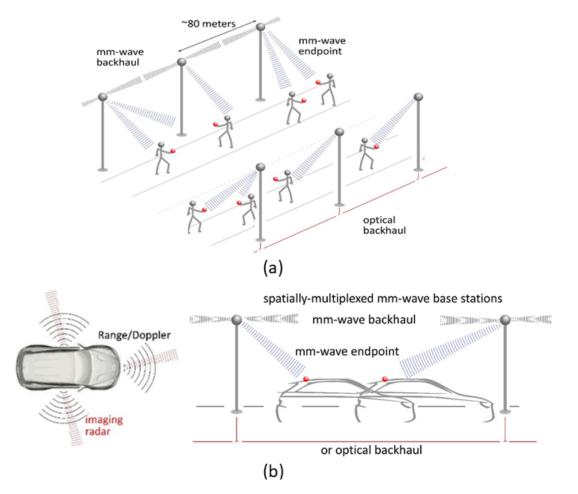

| 4.1  | mm-wave/THz applications: (a) spatially multiplexed networks for multi-<br>Gigabit mobile and residential/office communication and (b) THz radar<br>and imaging systems supporting autonomous cars and driving in foul<br>weather, with wideband links between cars and highway infrastructure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| 4.2  | to coordinate traffic. [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46       |

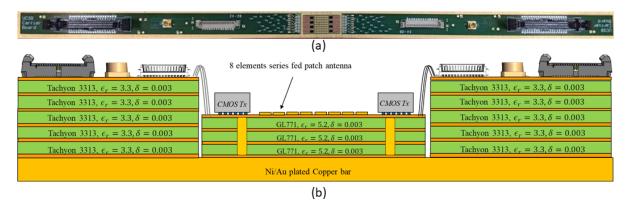

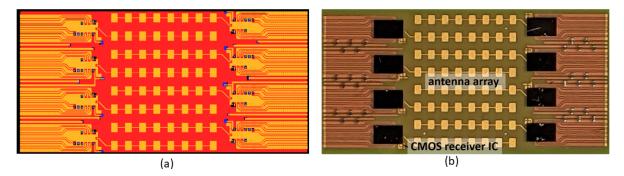

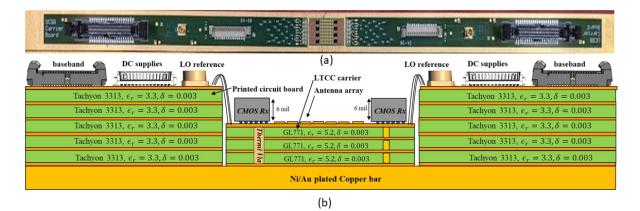

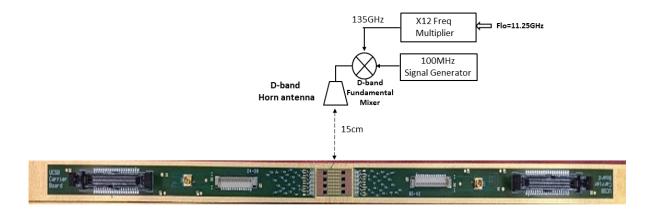

|      | 8 tiles of 8-elements . [1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47       |

| 4.3  | Comparison between IC-Package transition technologies for mm-wave applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51       |

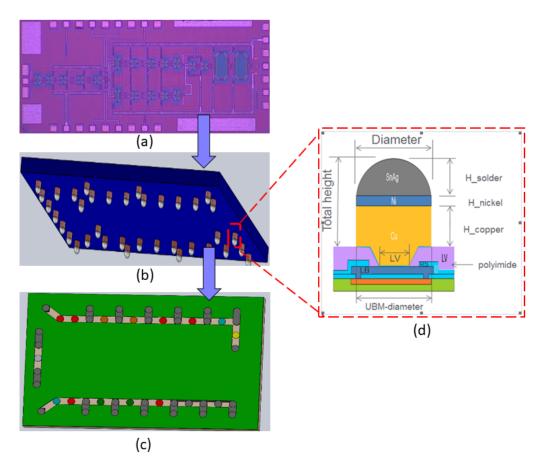

| 4.4  | Illustrative drawing showing the procedures going the first design cycle to<br>the second design cycle (a) chip with pads for on wafer testing (b) cartoon<br>drawing for transmitter chips with GF copper pillars (c) PCB/ceramic<br>carrier with solder mask opening at copper pillar locations (d) copper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| 4 5  | pillar structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52       |

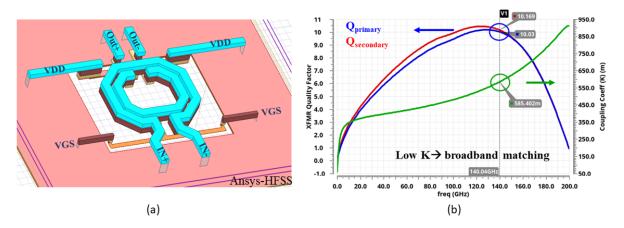

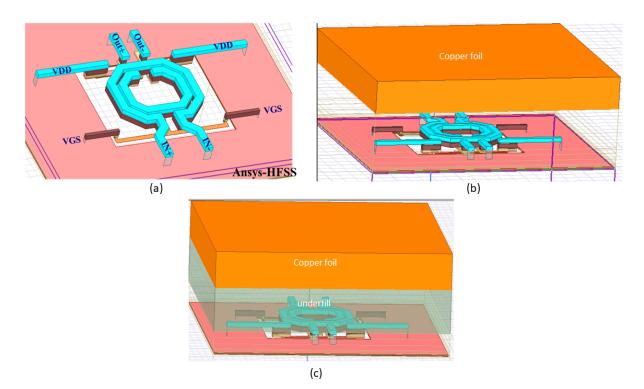

| 4.5  | EM simulation using Ansys HFSS for a 135GHz transformer (a) while $1 + 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 = 1 + 2 $ |          |

|      | being open up to the air, (2) with a copper foil at $30\mu$ m distance, and (3) with copper foil at $20\mu$ m distance and with under fill metazial in between                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

|      | with copper foil at $30\mu$ m distance and with under-fill material in-between<br>the transformer and the performer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ະາ       |

| 16   | the transformer and the package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53       |

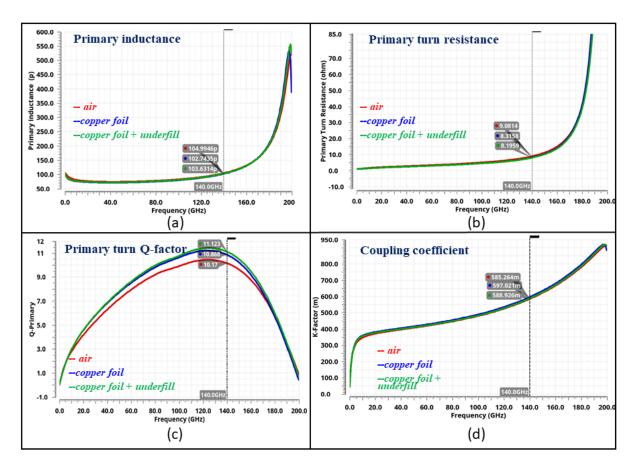

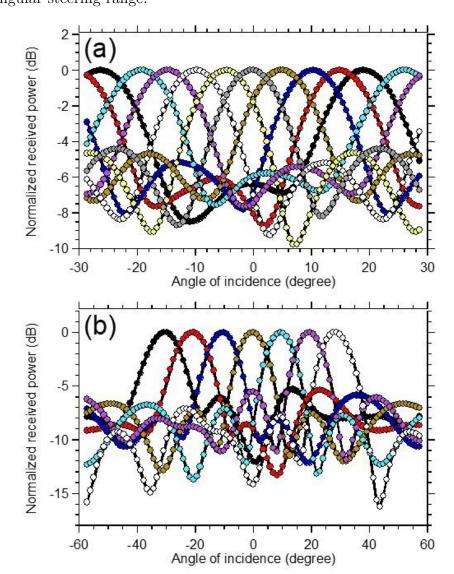

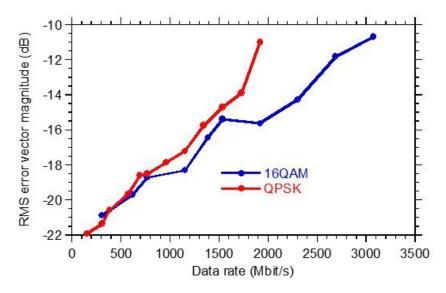

| 4.6  | EM simulation results for a 135GHz inter-stage matching transformer (a) transformer's primary inductance (b) Primary turn resistance (c) primary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |