## **UC Santa Barbara**

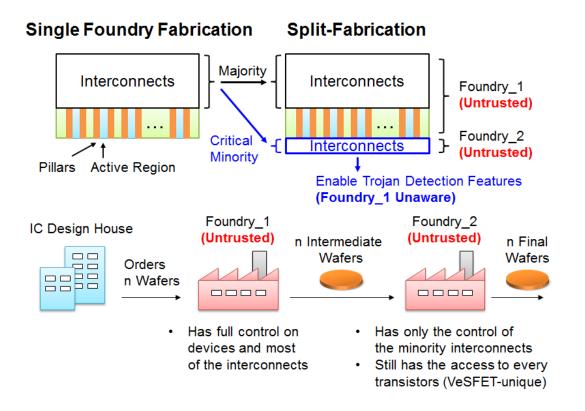

### **UC Santa Barbara Electronic Theses and Dissertations**

### **Title**

Assessing VeSFET Monolithic 3D Technology in Physical Design, Dynamic Reconfigurable Computing, and Hardware Security

### **Permalink**

https://escholarship.org/uc/item/5s9833kz

#### **Author**

Yang, Ping-Lin

### **Publication Date**

2017

Peer reviewed|Thesis/dissertation

### UNIVERSITY OF CALIFORNIA

### Santa Barbara

Assessing VeSFET Monolithic 3D Technology in Physical Design,

Dynamic Reconfigurable Computing, and Hardware Security

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Ping-Lin Yang

Committee in charge:

Professor Malgorzata Marek-Sadowska, Chair

Professor Kwang-Ting Tim Cheng

Professor Wojciech P. Maly

Professor Li-C. Wang

January 2018

# The dissertation of Ping-Lin Yang is approved.

| Wojciech P. Maly |

|------------------|

|                  |

|                  |

|                  |

| Li-C. Wang       |

|                  |

|                  |

|                  |

December 2017

Assessing VeSFET Monolithic 3D Technology in Physical Design,

Dynamic Reconfigurable Computing, and Hardware Security

Copyright © 2017

by

Ping-Lin Yang

#### **ACKNOWLEDGEMENTS**

This dissertation and all the research works I have finished during my Ph.D. journey would not have been possible without my advisor and mentor Professor Malgorzata Marek-Sadowska. I would like to express my deepest gratitude to her. Over hundreds of discussions, she guided me, enlightened me, inspired me, was always open-minded, and gave me precise and constructive suggestions at all times. Her wisdom, knowledge, philosophy, diligence, patience, and attitudes toward work and life have greatly influenced me. I feel very lucky and thankful to have such the great advisor and mentor in one of the most important chapter of my life.

I deeply appreciate Professor Wojciech P. Maly, the inventor of VeSFET, and as my coadvisor and another mentor. He always provided me valuable comments, critiques, and outof-the-box ideas with his deep insights of VeSFET. I admire his passion of researches and his determination of driving new technology for the human society, which inspired me every time we talked or met.

I want to express my gratitude to Professor Kwang-Ting Tim Cheng and Professor Li-C. Wang. Their valuable and constructive comments and suggestions helped me to shape my researches and this dissertation better.

This work is a fruit of collective efforts. I am grateful to Dr. Xiang Qiu and Dr. Vivek S. Nandakumar, for sharing their knowledge and past works on VeSFET research. I really appreciate my mentors in IBM Research, Dr. Terence B. Hook, Dr. Philip J. Oldiges, and Dr. Bruce B. Doris, for their guidance and knowledge on device level researches, which gave me deeper understanding on VeSFET behavior in advanced technology nodes. I thank Professor

Dominik Kasprowicz and Professor Andrzej Pfitzner, for improving the VeSFET transistor models, which made the experiments possible. I want to express my appreciation to all former or current colleagues and friends in the lab: Dr. Miguel Lastras, Ali Abbasinasab, Dr. Zhong Guan, Shabnam Larimian, Dr. Chun-Kai Hsu, Dr. Fan Lin, Dr. Amirali Ghofrani, Dr. Rui Wu, Dr. Nicole Fern, Yuyang Wang, and Leilai Shao. The conversations with you were always helpful and joyful, which enriched my research and life.

I would like to express my deepest gratitude to my dearest family: my parents, my wife Chin-Mao, and my younger sister Hui-Chen, and my dear friends living nearby on the same Ph.D. journey. They are my strongest supports and always there for sharing my happiness, pressure, or even depression. Especially for my wife Chin-Mao, she is always understanding and supportive, taken care of our daily life and our little daughter, which allowed me to stride ahead.

At the end, I deeply appreciate the support of National Science Foundation (NSF) under Grant CCF-1320401. In addition, I want to express my gratitude to the computing resource support from the Center for Scientific Computing from the California NanoSystems Institute (CNSI) and Materials Research Laboratory (MRL) at the University of California, Santa Barbara, supported by NSF MRSEC (DMR-1121053) and NSF (CNS-0960316). Furthermore, I would like to thank the Department of Electrical and Computer Engineering at the University of California, Santa Barbara, for all the help of administrative works and IT infrastructure.

### VITA OF PING-LIN YANG

#### December 2017

#### **EDUCATION**

**Doctor of Philosophy** in *Electrical and Computer Engineering* University of California, Santa Barbara, December 2017 (expected) Advisor: Professor Malgorzata Marek-Sadowska

**Master of Science** in *Electrical Engineering*National Tsing Hua University, Hsinchu, Taiwan, July 2007

Advisors: Professor Yarsun Hsu, Professor Ching-Te Chiu, and Professor Shuo-Hung Hsu

**Bachelor of Science** in *Electrical Engineering*National Tsing Hua University, Hsinchu, Taiwan, June 2005

### PROFESSIONAL EMPLOYMENT

09/2013 – 12/2017: **Graduate Student Researcher**, VLSI CAD Lab, Department of Electrical and Computer Engineering, University of California, Santa Barbara

06/2015 – 09/2015: **Research Intern**, IBM, Albany, NY

10/2007 – 09/2013: **R&D Principal Engineer**, TSMC, Hsinchu, Taiwan

07/2005 – 07/2007: **Research Assistant**, High Performance Computer & Communication Lab, Department of Electrical Engineering, National Tsing Hua University, Hsinchu, Taiwan

09/2006 – 01/2007: **Teaching Assistant**, Department of Electrical Engineering, National Tsing Hua University, Hsinchu, Taiwan

09/2002 – 10/2006: **Web and Database Programmer**, Computer and Communication Center, National Tsing Hua University, Hsinchu, Taiwan

#### **PUBLICATIONS**

[1] **P.-L. Yang**, X Qiu, and M. Marek-Sadowska, "VeSFET monolithic 3D technology physical design assessment," *IEEE Transactions on Very Large Scale Integration Systems (T-VLSI)*, 2017 (Submitted and under review process)

- [2] **P. -L. Yang** and M. Marek-Sadowska, "High performance architecture using fast dynamic reconfigurable accelerators," *IEEE Transactions on Very Large Scale Integration Systems (T-VLSI)*, 2017 (Reviewed, minor revision, and under further review process)

- [3] **P.-L. Yang** and M. Marek-Sadowska, "Making split-fabrication more secure," in *Proc.* of the 35<sup>th</sup> IEEE/ACM International Conference on Computer-Aided Design (ICCAD'16), Nov. 2016, pp. 1-8

- [4] **P.-L. Yang** and M. Marek-Sadowska, "A fast, fully verifiable, and hardware predictable ASIC design methodology," in *Proc. of the 34<sup>th</sup> IEEE International Conference on Computer Design (ICCD'16)*, Oct. 2016, pp. 364-367

- [5] **P.-L. Yang**, T. B. Hook, P. J. Oldiges, and B. B. Doris, "Vertical slit FET at 7-nm node and beyond," *IEEE Transactions on Electron Devices (T-ED)*, vol. 63, no. 8, Aug. 2016, pp. 3327-3334

- [6] H. Hsieh, S. H. Dhong, C. -C. Lin, M. -Z. Kuo, K. -F. Tseng, P. -L. Yang, K. Huang, M. -J. Wang, and W. Hwang, "Custom 6-R, 2- or 4-W multi-port register files in an ASIC SOC with a DVFS window of 0.5 V, 130 MHz to 0.96 V, 3.2 GHz in a 28-nm HKMG CMOS technology," in *Proc. of the IEEE Custom Integrated Circuits Conference (CICC'15)*, Sep. 2015, pp. 1-3

- [7] **P.-L. Yang**, M. Marek-Sadowska, and W. Maly, "Performance assessment of VeSFET-based SRAM," in *Proc. of the* 11<sup>th</sup> *IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC'15)*, Jun. 2015, pp. 79-82

- [8] M. -Z. Kuo, H. Hsieh, S. Dhong, **P. -L. Yang**, C. -C. Lin, R. Tseng, K. Huang, M. -J. Wang, and W. Hwang, "A 16 kB tile-able SRAM macro prototype of an operating window of 4.8GHz at 1.12V VDD to 10 MHz at 0.5V in a 28-nm HKMG CMOS," in *Proc. of the IEEE Custom Integrated Circuits Conference (CICC'14)*, Sep. 2014, pp. 1-4

- [9] S. Dhong, R. Guo, M. -Z. Kuo, **P. -L. Yang**, C. -C. Lin, K. Huang, M. -J. Wang, and W. Hwang, "A 0.42V Vccmin ASIC-compatible pulse-latch solution as a replacement for a traditional master-slave flip-flop in a digital SOC," in *Proc. of the IEEE Custom Integrated Circuits Conference (CICC'14)*, Sep. 2014, pp. 1-4

- [10] **P.-L. Yang**, C.-C. Lin, M.-Z. Kuo, S.-H. Dhong, C.-M. Lin, K. Huang, C.-N. Peng, and M.-J. Wang, "A 4-GHz universal high-frequency on-chip testing platform for IP validation," in *Proc. of the 32<sup>nd</sup> IEEE VLSI Test Symposium (VTS'14)*, Apr. 2014, pp. 1-6

- [11] M. -Z. Kuo, O. Takahashi, **P. -L. Yang**, C. -C. Lin, M. -J. Wang, P. -W. Wang, and S. -H. Dhong, "A HKMG 28nm 1GHz fully-pipelined tile-able 1MB embedded SRAM IP with 1.39mm<sup>2</sup> per MB," in *Proc. of the IEEE Custom Integrated Circuits Conference (CICC'13)*, Sep. 2013, pp. 1-4

- [12] C. -T Chiu, Y. -H. Hsu, J. -M Wu, S. -H. Hsu, M. -S. Kao, H. -C. Tzeng, M. -C. Du, **P. -L. Yang**, M. -H. Lu, F. Chen, H. -Y. Lin, and Y. -S. Hsu, "An 8 × 8 20 Gbps reconfigurable load balanced TDM switch IC for high-speed networking," *Journal of Signal Processing Systems*, vol. 66, no. 1, Jan. 2012 pp. 57-73

- [13] Y.-H. Hsu, M.-H. Lu, **P.-L. Yang**, F.-T. Chen, Y.-H. Li, M.-S. Kao, C.-H. Lin, J.-M. Wu, S.-H. Hsu, Y. S. Hsu, and C.-T. Chiu, "A quarter-rate 2.56/3.2Gbps 16/20:1 SERDES interface in 0.18µm CMOS technology," *International Journal of Electrical Engineering (IJEE)*, vol. 16, no. 1, Feb. 2009, pp. 39-49

- [14] Y.-H. Hsu, M.-H. Lu, **P.-L. Yang**, F.-T. Chen, Y.-H. Li, M.-S. Kao, C.-H. Lin, C.-T. Chiu, J.-M. Wu, S.-H. Hsu, and Y.-S. Hsu, "A 28Gbps 4×4 switch with low jitter SerDes using area-saving RF model in 0.13μm CMOS technology," in *Proc. of the IEEE International Symposium on Circuits and Systems (ISCAS'08)*, May. 2008, pp. 3086-3089

- [15] C. -T. Chiu, J. -M. Wu, S. -H. Hsu, Y. Hsu, M. -H. Lu, **P. -L. Yang**, F. -T. Chen, Y. -H. Li, Y. -H. Hsu, and M. -S. Kao, "A quarter-rate 2.56/3.2Gbps 16/20:1 SERDES interface in 0.18μm CMOS technology," in *Proc. of the 18<sup>th</sup> VLSI Design/CAD Symposium*, Aug. 2007, pp. 634-637

- [16] C. -T. Chiu, Y. -H. Hsu, M. -S. Kao, H. -C. Tzeng, M. -C. Tu, **P. -L. Yang**, M. -H. Lu, F. Chen, H. -Y. Lin, J. -M. Wu, S. -H. Hsu, and Y. -S. Hsu, "A scalable load balanced Birkhoff-von Neumann symmetric TDM switch IC for high-speed networking applications," in *Proc. of the IEEE International Symposium on Circuits and Systems (ISCAS'07)*, May. 2007, pp. 2754-2757

- [17] C. -H. Hsiao, M. -S. Kao, C. -H. Jen, Y. -H. Hsu, **P. -L. Yang**, C. -T. Chiu, J. -M. Wu, S. -H. Hsu, and Y. -S. Hsu, "A 3.2 Gbit/s CML transmitter with 20:1 multiplexer in 0.18 CMOS technology," in *Proc. of the 13<sup>th</sup> International Conference Mixed Design of Integrated Circuits and Systems (MIXDES'06)*, Jun. 2006, pp. 179-183

### **PATENTS**

- [1] "Contactless communications using ferromagnetic material," U.S. Patent 9,412,721, Aug. 9, 2016

- [2] "Electron beam lithography methods including time division multiplex loading," U.S. Patent 9,378,926, Jun. 28, 2016

- [3] "Clock regenerator," U.S. Patent 9,362,899, Jun. 7, 2016

- [4] "Charged particle lithography system with a long shape illumination beam," U.S. Patent 9,202,662, Dec. 1, 2015

- [5] "Electron beam lithography systems and methods including time division multiplex loading," Korea Patent 10-1563055-0000, Oct. 19, 2015

- [6] "Electron beam lithography systems and methods including time division multiplex loading," U.S. Patent 8,941,085, Jan. 27, 2015

- [7] "3D IC configuration with contactless communication," U.S. Patent 8,921,160, Dec. 30, 2014

- [8] "Contactless communications using ferromagnetic material," U.S. Patent 8,760,255, Jun. 24, 2014

- [9] "Conditional cell placement," U.S. Patent 8,560,997, Oct. 15, 2013

- [10] "3D IC configuration with contactless communication," U.S. Patent 8,513,795, Aug. 20, 2013

- [11] "Power-down circuit with self-biased compensation circuit," U.S. Patent 7,760,009, Jul. 20, 2010

- [12] "Power-down circuit with self-biased compensation circuit," China Patent CN101753126A, Jun. 23, 2010

#### **ABSTRACT**

Assessing VeSFET Monolithic 3D Technology in Physical Design,

Dynamic Reconfigurable Computing, and Hardware Security

by

### Ping-Lin Yang

With the continuous demands on integrating more functions and devices on a single chip, the technology has been evolving along the scaling path for decades. The transistor feature size has been scaled down from µm order toward 7nm, 5nm, and even below. Conventional MOSFET / FinFET devices are approaching physical limitations. It is extremely difficult to integrate more devices solely by further transistor scaling. Besides scaling, 3D integration technologies offer attractive features. By stacking devices, it increases device density and reduces wire length, which implies better PPA (performance, power consumption, and area). However, the increased power density and the extra overhead of inter-tier connections are significant concerns for deploying 3D integration technologies. For sustaining future technology growth, it is expected that fundamental changes of device structure are required.

Vertical Slit Field Effect Transistor (VeSFET) is a novel transistor with unique structure and characteristics. It is two-side accessible and low power consuming, which is 3D integration friendly. This dissertation investigates VeSFET technology and proposes unique and powerful applications, which are not feasible using MOSFET technologies. The scope of

our studies includes SRAM, monolithic 3D physical design assessment, 3D FPGA, fast and hardware predictable ASIC design methodology, high performance reconfigurable architecture with dynamic reconfigurable accelerators, and hardware security.

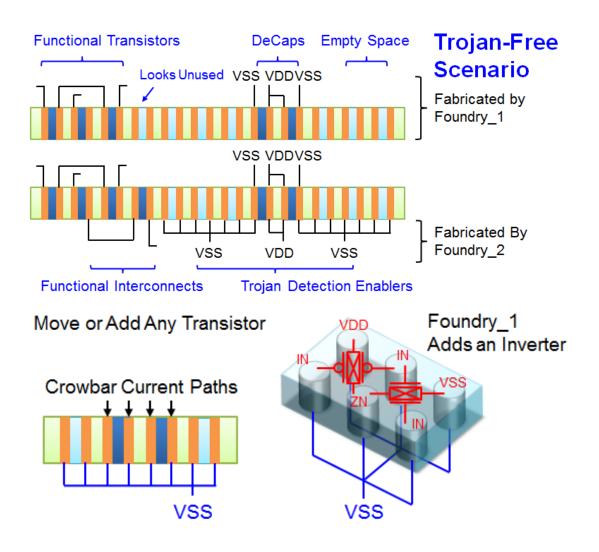

In this dissertation, SRAM performance assessment shows that VeSFET SRAM is speed competitive to CMOS SRAM and consumes much less power. The monolithic 3D physical design assessment compares MOSFET and VeSFET monolithic 3D integrated circuits. In particular, the IR-drop on power delivery network (PDN) and clock distribution network (CDN) characteristics are assessed. Due to VeSFET's lower power consumption, 3D VeSFET ICs have lower IR-Drop and CDN power consumption. A fast, fully verifiable, and hardware predictable ASIC design methodology using VeSFET 3D FPGA is presented. The performance comparison of VeSFET 2D and 3D FPGA shows that the 3D FPGA is faster, smaller, and consumes less power. A high performance reconfigurable architecture is proposed using VeSFET fast reconfigurable 3D FPGA-based accelerators with novel bitstream replacement method. The system level performance evaluation shows significant improvement over the system with no accelerator or with conventional FPGA-based accelerator. Toward trustworthy hardware designs, a secure split-fabrication method using VeSFET is proposed for addressing hardware security concerns, such as piracy prevention, hardware Trojan prevention and detection. Any Trojan insertion or design tampering can be easily detected.

### TABLE OF CONTENTS

| Chapter 1 Introduction                                   | 1  |

|----------------------------------------------------------|----|

| 1.1 Challenges of Future ICs                             | 1  |

| 1.2 3D Integration Technologies                          | 3  |

| 1.3 VeSFET (Vertical Slit FET)                           | 4  |

| 1.4 Dissertation Organization                            | 5  |

| Chapter 2 VeSFET Technology                              | 6  |

| 2.1 Device Structure                                     | 6  |

| 2.2 Circuits and Layouts                                 | 10 |

| 2.3 SRAMs                                                | 11 |

| 2.3.1 6T Bit Cell                                        | 12 |

| 2.3.2 SRAM Array Performance                             | 16 |

| 2.4 Two-side Accessibility and Monolithic 3D Integration | 22 |

| Chapter 3 Physical Design Assessment                     | 27 |

| 3.1 Introduction                                         | 27 |

| 3.2 Assessment Methodology                               | 28 |

| 3.2.1 Technology Assumptions                             | 29 |

| 3.2.2 2D Implementations                                 | 34 |

| 3.2.3 3D Partition Methods                               | 36 |

| 3.3 Power Delivery Network Assessments                   | 41 |

| 3.3.1 Inter-tier Connection Technical Assumptions        | 42 |

| 3.3.2 Current Sink Modeling                              | 44 |

|           | 3.3.3 Inter-tier Connection Modeling                                    | 45   |

|-----------|-------------------------------------------------------------------------|------|

|           | 3.3.4 Experimental Results                                              | 48   |

|           | 3.4 Clock Distribution Network Assessments                              | 54   |

|           | 3.4.1 Clock Distribution Network Structure                              | 54   |

|           | 3.4.2 Experimental Results                                              | 55   |

|           | 3.5 Summary                                                             | 60   |

| Chapter 4 | A Fast, Fully Verifiable, and Hardware Predictable ASIC Design Methodol | logy |

|           | using 3D FPGAs                                                          | 62   |

|           | 4.1 Introduction                                                        | 62   |

|           | 4.2 The Design Methodology                                              | 66   |

|           | 4.3 VeSFET Monolithic 3D FPGA                                           | 70   |

|           | 4.4 3D FPGA to 2D ASIC Migration and the Costs                          | 74   |

|           | 4.5 Performance Evaluation                                              | 77   |

|           | 4.6 Summary                                                             | 81   |

| Chapter 5 | High Performance Dynamic Reconfigurable Computing with Accelerators     | 83   |

|           | 5.1 Introduction                                                        | 83   |

|           | 5.2 Prior Works on Reconfigurable Systems                               | 86   |

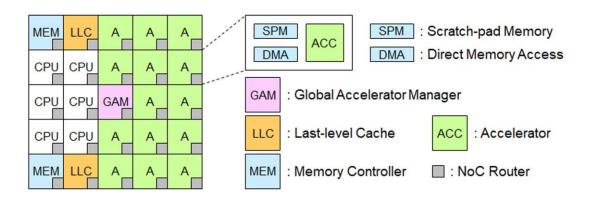

|           | 5.3 The Proposed Architecture                                           | 88   |

|           | 5.3.1 Overview                                                          | 89   |

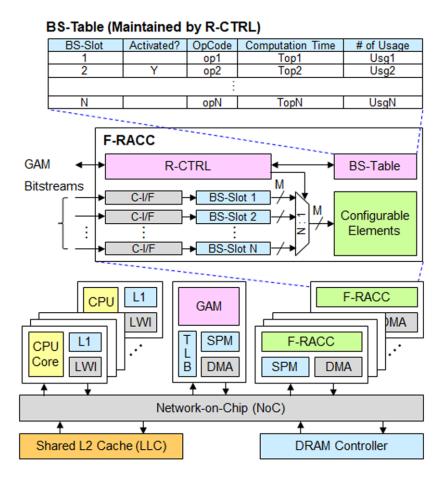

|           | 5.3.2 Fast Dynamic Reconfigurable Accelerators                          | 92   |

|           | 5.3.3 Fast Dynamic Reconfiguration                                      | 97   |

|           | 5.3.4 Performance Improvement Assessment                                | 101  |

|           | 5.4 Experimental Results                                                | 108  |

| 5.4.1 Power and Area Overhead, and Switch      | ing Time Assessment111 |

|------------------------------------------------|------------------------|

| 5.4.2 Performance Assessment                   | 115                    |

| 5.5 Summary                                    | 120                    |

| Chapter 6 Making Split-Fabrication More Secure | 122                    |

| 6.1 Introduction                               | 123                    |

| 6.2 Security Threats                           | 126                    |

| 6.3 The Proposed Methodology                   | 128                    |

| 6.3.1 Methodology for 2D Designs               | 128                    |

| 6.3.2 Methodology for 3D Designs               | 131                    |

| 6.4 Implementation Details                     | 137                    |

| 6.4.1 Net Partition                            | 137                    |

| 6.4.2 Transistor Hiding and Pin Shaking        | 139                    |

| 6.4.3 Trojan Detection Scan Path               | 140                    |

| 6.5 Security Evaluation                        | 143                    |

| 6.6 Summary                                    | 147                    |

| Chapter 7 Conclusion and Future Opportunities  | 148                    |

| 7.1 Conclusions                                | 148                    |

| 7.2 Future Work and Opportunities              | 151                    |

| 7.2.1 Device and Process Tuning                | 151                    |

| 7.2.2 Utilizing Independent Gate Configurat    | ion (IGC)152           |

| 7.2.3 Heterogeneous Monolithic 3D Integrat     | ion153                 |

| 7.2.4 Low Power Applications                   | 153                    |

| 7.2.5 Neural Networks and Machine Learnin      | ıg154                  |

| 7.2.6 More Security F  | eatures     | 154 |

|------------------------|-------------|-----|

| 7.2.7 Testing, Repairi | ng, and ECO | 155 |

| 7.2.8 Image Sensing    |             | 155 |

| 7.2.9 Microchip Impla  | ants        | 156 |

| References             |             | 157 |

### LIST OF FIGURES

| Figure 2.1. VeSFET; (a) 3D view of a single VeSFET; (b) 3D view of a VeSFET-based                        |

|----------------------------------------------------------------------------------------------------------|

| chip; (c) top view of a single VeSFET; (d) top view of a VeSFET-based chip.                              |

| VeSFETs are placed as an array formed by metal pillars7                                                  |

| Figure 2.2. Independent gate configuration (IGC) VeSFETs and the circuits9                               |

| Figure 2.3. Three VeSFET circuit layout styles and the corresponding 1P1N inverter                       |

| standard cell implementations                                                                            |

| Figure 2.4. VeSFET cell layout $v0$ , cell size = $24r \times 16r = 384r^2$                              |

| Figure 2.5. VeSFET cell v0 3D diagram (Courtesy of Professor Wojciech P. Maly,                           |

| Department of Electrical and Computer Engineering, Carnegie Mellon                                       |

| University)                                                                                              |

| Figure 2.6. VeSFET cell layout $vI$ , cell size = $12r \times 28r = 336r^2$                              |

| Figure 2.7. VeSFET cell layout $v2$ , cell size = $20r \times 16r = 320r^2$                              |

| Figure 2.8. Default <i>CACTI</i> CMOS cell footprint [43] with area = $1.46F^2$ ( <i>F</i> is transistor |

| feature size) and aspect ratio 1.46                                                                      |

| Figure 2.9. Tool validation: CACTI and Hspice delay and energy simulation results                        |

| comparison of a WLD + WL. Based on OR-type TGC VeSFETs                                                   |

| Figure 2.10. Different 3D IC technologies. Two-side accessible transistor monolithic 3D                  |

| offers shortest cross-tier interconnects                                                                 |

| Figure 2.11. A Tied-Gate-Controlled (TGC) 1P1N inverter. (a) Layout; (b) Conventional                    |

| structure one-side routed; (c) Two-side routed implementation23                                          |

| Figure 2.12. VeSFET-based monolithic 3D integration flow. In Step 8, the bumps can be                   |

|---------------------------------------------------------------------------------------------------------|

| made on the <i>n-th</i> tier directly or on the first tier with a flip24                                |

| Figure 2.13. VeSFET-based monolithic 3D IC (a) cross-sectional view; (b) monolithic 3D                  |

| IC structure                                                                                            |

| Figure 2.14. The size comparison among different 3D inter-tier interconnects technologies.              |

| The area of 14nm MIV [8] is the baseline set to 1X26                                                    |

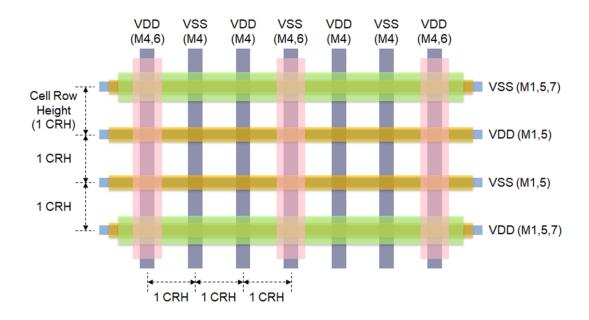

| Figure 3.1. Power delivery network (PDN) mesh structure                                                 |

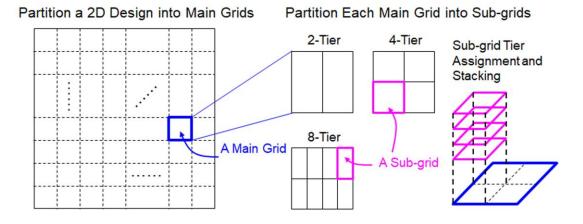

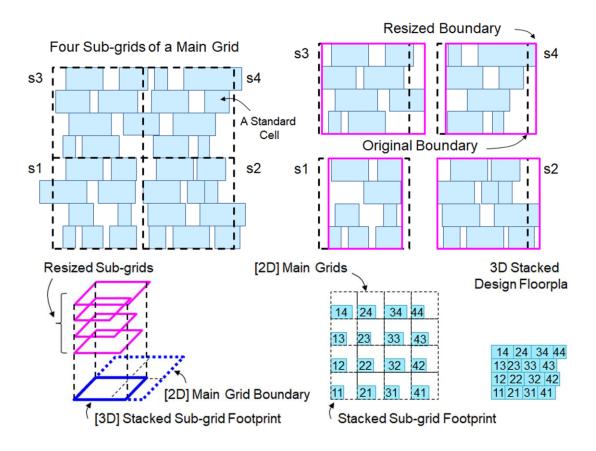

| Figure 3.2. 3D partition method, a 2D design is divided into main grids and sub-grids. Each             |

| sub-grid is assigned to a tier according to different partition methods. Stack                          |

| sub-grids to construct the partitioned 3D design                                                        |

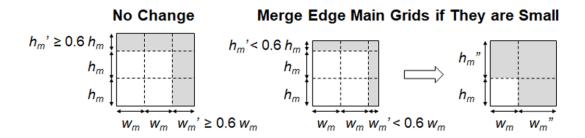

| Figure 3.3. Edge <i>main grid</i> resizing. Each <i>main grid</i> is with the same size except the edge |

| grids. Merge edge grids if they are small                                                               |

| Figure 3.4. Sub-grid resizing and 3D stacking. The sub-grid width is resized according to the           |

| range of the standard cells in this <i>sub-grid</i>                                                     |

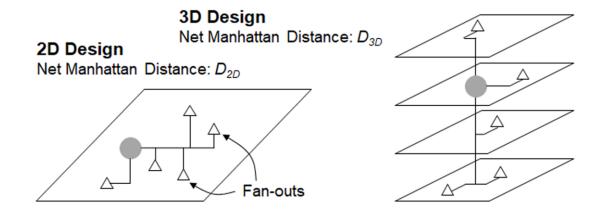

| Figure 3.5. Net Manhattan distance in 2D and 3D designs                                                 |

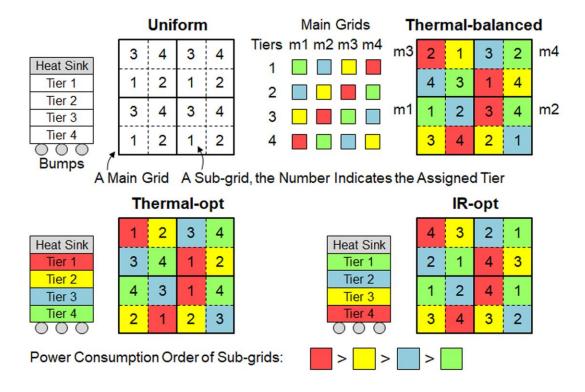

| Figure 3.6. Four different 3D partition methods                                                         |

| Figure 3.7. Inter-tier connection schemes assumed for IR-drop assessments                               |

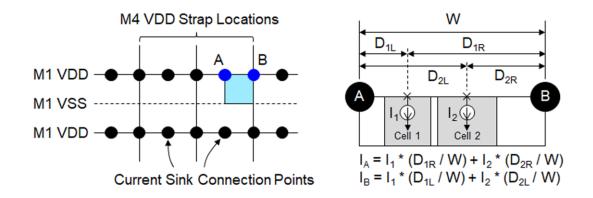

| Figure 3.8. Current sink modeling. The current consumed by each cell is modeled and                     |

| placed on specific connection points for reducing the data size of current sink                         |

| models                                                                                                  |

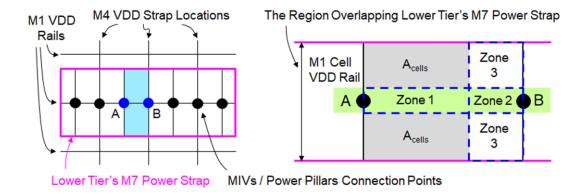

| Figure 3.9. Inter-tier VDD connection modeling. CMOS's VDD MIVs can be placed on                        |

| Zones 2 and 3; VeSFET's VDD pillars can be placed on Zones 1, 2, and 346                                |

| Figure 3.10. The pitches of CMOS MIVs and VeSEET pillars.  46                                           |

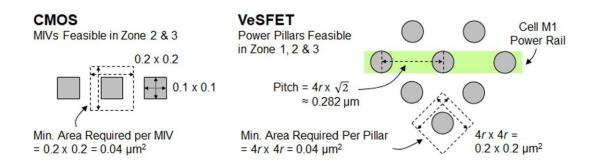

| Figure 3.11. Max. static VDD IR-Drop, <i>PDN-10-20</i> , partitioned into 2 and 8 Tiers with four       |

|---------------------------------------------------------------------------------------------------------|

| different partition methods. On average among all circuits in 2-Tier and 8-Tier,                        |

| VeSFET to CMOS ratios are 44.3%, 44.5%, 46.0%, and 42.7% (Uni, T-bal, T-                                |

| opt, and IR-opt)53                                                                                      |

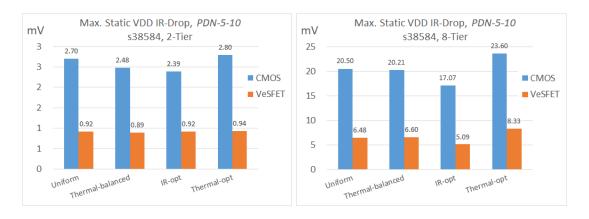

| Figure 3.12. Max. static VDD IR-Drop, <i>PDN-5-10</i> , <i>s38584</i> , partitioned into 2 and 8 Tiers  |

| with four different partition methods53                                                                 |

| Figure 3.13. Max. static VDD IR-Drop, <i>PDN-5-10</i> , <i>fft_256</i> , partitioned into 2 and 8 Tiers |

| with four different partition methods54                                                                 |

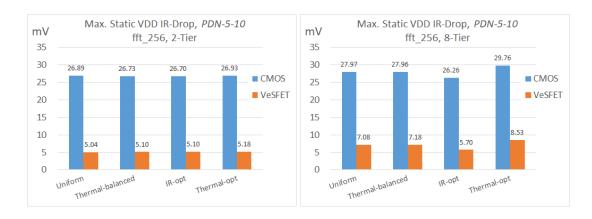

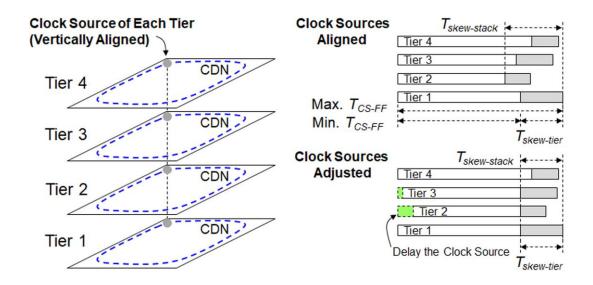

| Figure 3.14. Clock distribution scheme assumption                                                       |

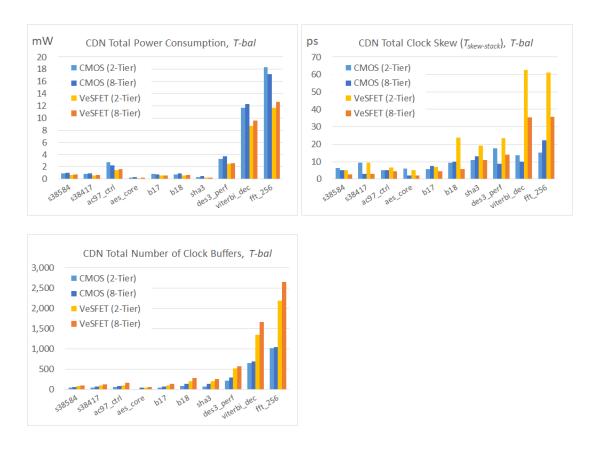

| Figure 3.15. CDN characteristics of all circuits partitioned into 2 and 8 Tiers with <i>Thermal</i> -   |

| balanced (T-bal) method. On average of all circuits in 2-Tier and 8-Tier with T                         |

| bal method, VeSFET to CMOS ratios are 71.9%, 157.6%, and 213.6% (Total                                  |

| power consumption, clock skew, and number of clock buffers)60                                           |

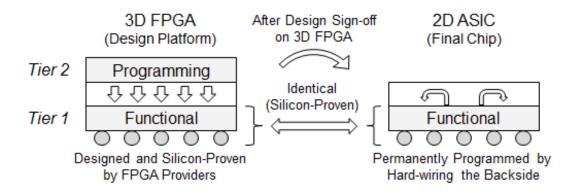

| Figure 4.1. The key idea of the proposed ASIC design methodology                                        |

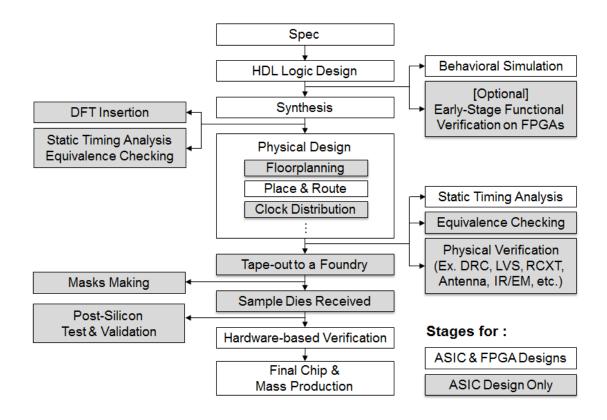

| Figure 4.2. ASIC and FPGA design flows                                                                  |

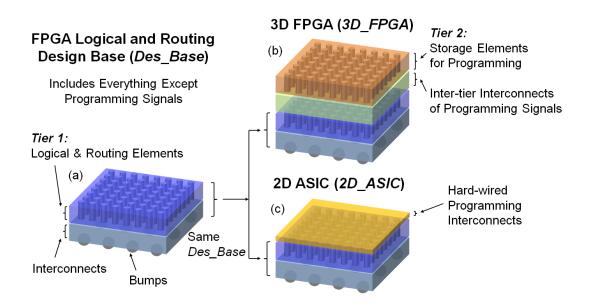

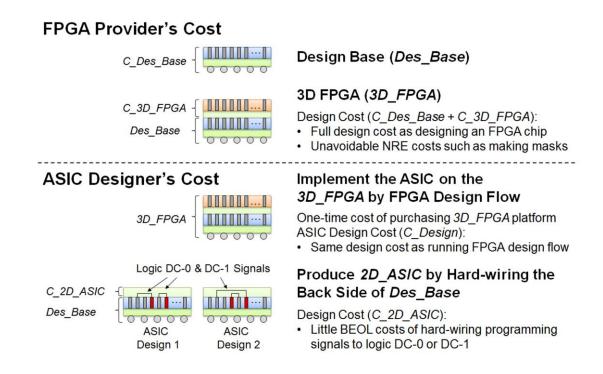

| Figure 4.3. The chip structures of the proposed methodology. (a) The design base, which                 |

| includes all the logical and routing elements of an FPGA (Des_Base); (b) 3D                             |

| FPGA for design implementation (3D_FPGA); (c) The final 2D ASIC                                         |

| (2D_ASIC)67                                                                                             |

| Figure 4.4. The design flow and the design costs of this methodology, for FPGA provider                 |

| and ASIC designers68                                                                                    |

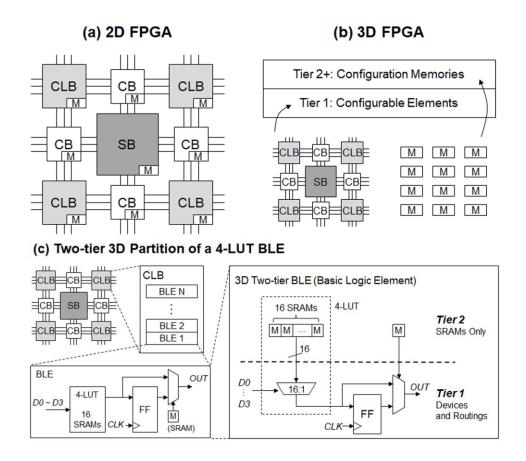

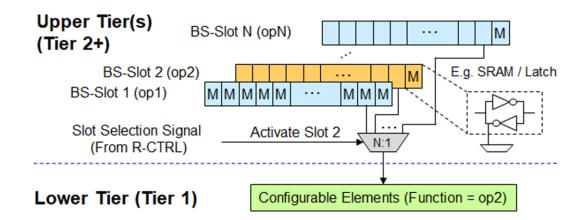

| Figure 4.5. 2D to 3D FPGA migration. (a) a 2D conventional island style FPGA; <i>M</i> is               |

| configuration memory; (b) a 3D FPGA, all the configuration memories are                                 |

| placed on independent tier(s) ( <i>Tier 2+</i> ), the configurable elements are placed                  |

|---------------------------------------------------------------------------------------------------------|

| on Tier 1; (c) a two-tier implemented 3D 4-LUT basic logic element (BLE)70                              |

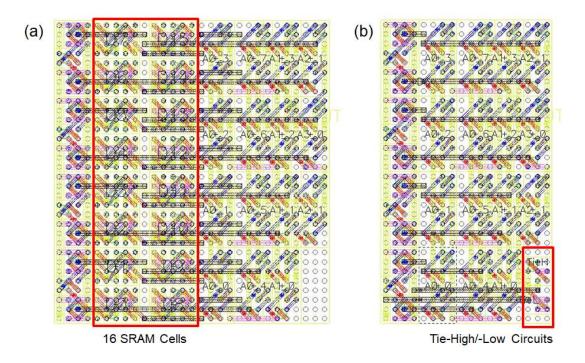

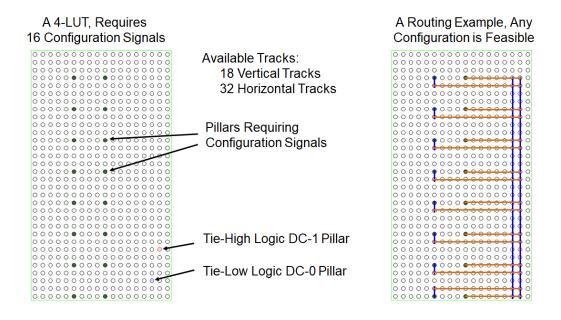

| Figure 4.6. 4-LUT layouts. (a) 2D (116r x 128r, 100%); (b) 3D Tier 1 (72r x 128r, 62%) .72              |

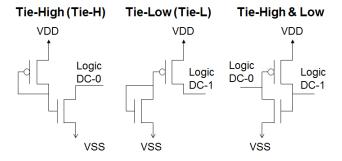

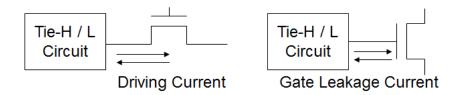

| Figure 4.7. Conventional Tie-High, Tie-Low, and Tie-High & Low circuits73                               |

| Figure 4.8. Two-layer backside routing of a 4-LUT in 2D_ASIC76                                          |

| Figure 4.9. Tie-H / L circuit connection scenarios. Left: to drain or source; Right: to gate .77        |

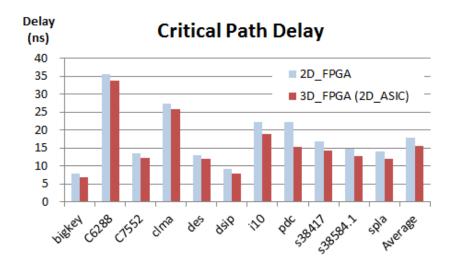

| Figure 4.10. Critical path delay of 2D_FPGA and 3D_FPGA (2D_ASIC). On average,                          |

| 2D_FPGA is 17.9 ns, 3D_FPGA (2D_ASIC) is 15.7 ns79                                                      |

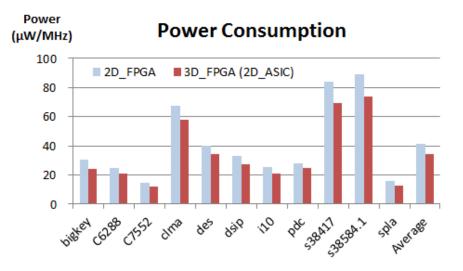

| Figure 4.11. Power consumption comparison of 2D_FPGA and 3D_FPGA (2D_ASIC). On                          |

| average, $2D\_FPGA$ is 41.1 $\mu$ W/MHz, $3D\_FPGA$ ( $2D\_ASIC$ ) is 34.3 $\mu$ W/MHz                  |

| 79                                                                                                      |

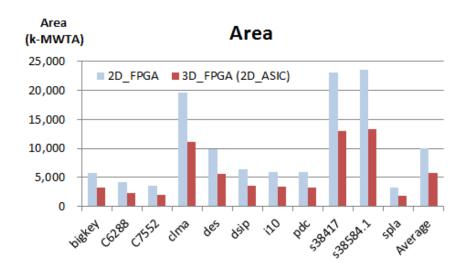

| Figure 4.12. Area comparison of 2D_FPGA and 3D_FPGA (2D_ASIC), in Kilo Minimum                          |

| Width Transistor Area (k-MWTA), for VeSFET with $r = 50$ nm, MWTA =                                     |

| 0.04μm <sup>2</sup> . On average, 2 <i>D_FPGA</i> is 10067.2 k-MWTA, 3 <i>D_FPGA</i> (2 <i>D_ASIC</i> ) |

| is 5693.3 k-MWTA80                                                                                      |

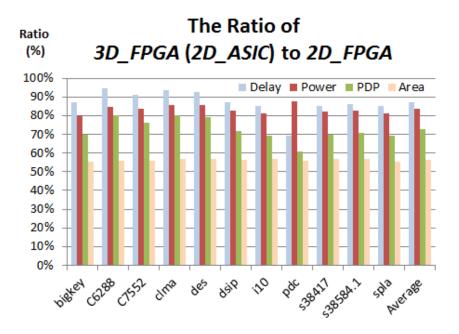

| Figure 4.13. The delay, power consumption, power-delay product (PDP), and area ratios of                |

| 3D_FPGA (2D_ASIC) to 2D_FPGA. On average, 3D_FPGA (2D_ASIC) is                                          |

| 87%, 83%, 72.6%, and 56% to 2D_FPGA in delay, power consumption, PDP,                                   |

| and area, respectively80                                                                                |

| Figure 5.1. Accelerator-rich architecture in [18-20] and [63]                                           |

| Figure 5.2. The proposed high performance reconfigurable architecture using fast dynamic                |

| reconfigurable accelerators (F-RACCs). 92                                                               |

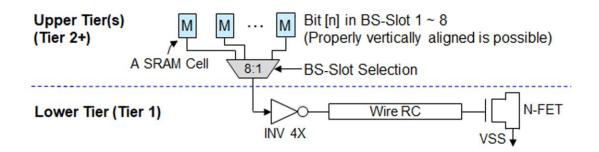

| Figure 5.3. The configuration structure. R-CTRL selects bitstream slot 2 (BS-Slot 2) for                             |

|----------------------------------------------------------------------------------------------------------------------|

| activation. The configurable elements are programmed to function op294                                               |

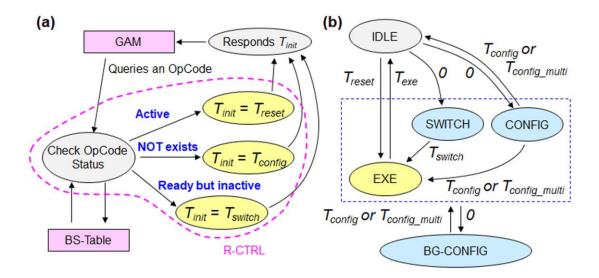

| Figure 5.4. F-RACC dynamic reconfiguration states. (a) When GAM queries a function                                   |

| (OpCode), R-CTRL responds with the initialization time required according to                                         |

| the status of the BS-Slots. (b) The state diagram of an F-RACC, arcs are                                             |

| annotated with times taken to change the state98                                                                     |

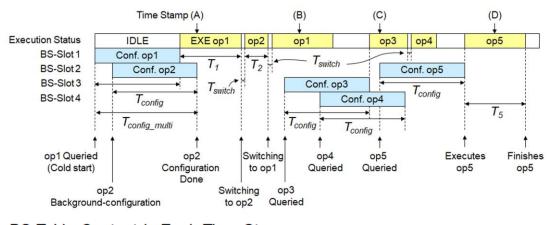

| Figure 5.5. The timeline and the BS-Table contents of a 4-BS-Slot F-RACC execution                                   |

| example. Tables (A) – (D) show the BS-Table contents in each time stamp                                              |

| marked on the timeline                                                                                               |

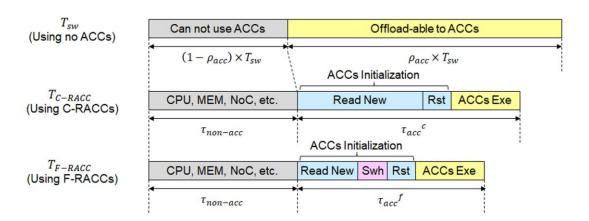

| Figure 5.6. System performance breakdown for 1) no accelerators (ACCs), pure CPU                                     |

| software path, 2) using C-RACCs, and 3) using F-RACCs. The accelerator                                               |

| initialization portion can be in one of three states: reading a new bitstream;                                       |

| switching to another BS-Slot; and just resetting the accelerator for next coming                                     |

| usage, as described in Section 5.3.3, Figure 5.4 and Figure 5.5103                                                   |

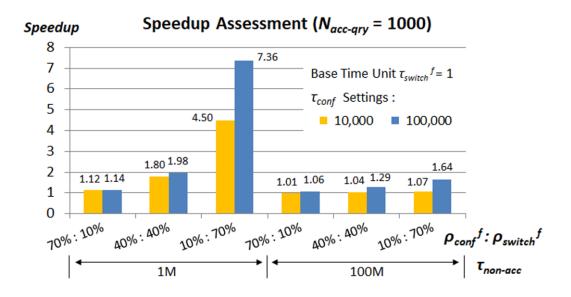

| Figure 5.7. Speedup assessment of using F-RACCs over using C-RACC, based on 1000                                     |

| accelerator queries ( $N_{acc-qry}$ ). Setting the switch time $\tau_{switch}^f = 1$ as the base time                |

| unit, for: a) $\tau_{conf} = 10,000$ and $100,000$ , b) $\tau_{non-acc} = 1$ M and $100$ M, c) $\rho_{conf}{}^{f}$ : |

| $\rho_{switch}^{f} = 70\%:10\%, 40\%:40\%, 10\%:70\%$ , while $\rho_{reset}$ is kept 20% and $\tau_{reset} = 0$ .    |

|                                                                                                                      |

| Figure 5.8. The circuit for delay and energy consumption simulations                                                 |

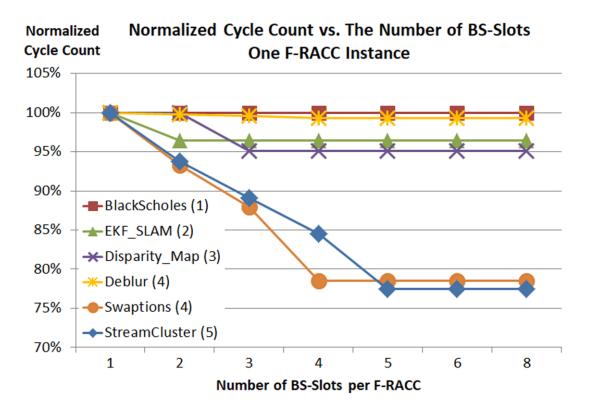

| Figure 5.9. Cycle count reduction by providing more BS-Slots in an F-RACC. In "()" we                                |

| show the number of different accelerated functions required for that benchmark                                       |

| application. The reduction saturates when the number of BS-Slots is sufficient                           |

|----------------------------------------------------------------------------------------------------------|

| for supporting the number of different accelerated functions required116                                 |

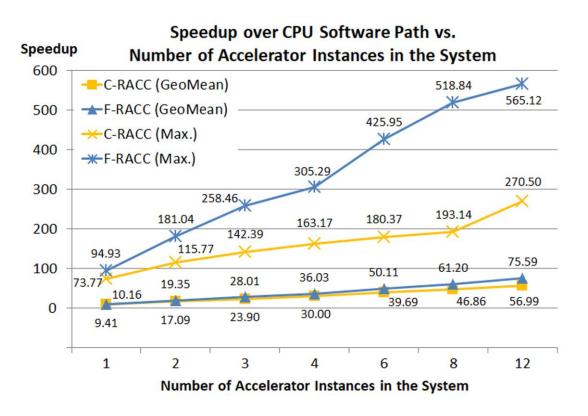

| Figure 5.10. The geometric mean and maximum of system speedup over CPU software path                     |

| among 11 benchmark applications with different number of accelerator                                     |

| instances. There are 8 BS-Slots per F-RACC119                                                            |

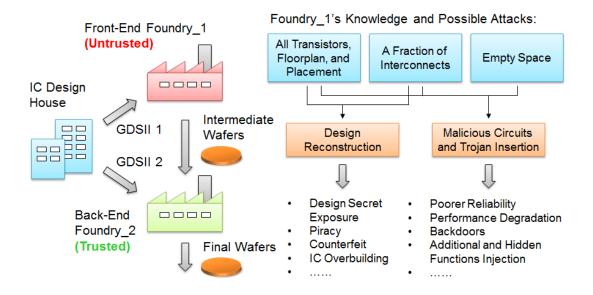

| Figure 6.1. Security threats in a conventional split-fabrication method127                               |

| Figure 6.2. The overview of VeSFET-based split-fabrication method of a 2D design 129                     |

| Figure 6.3. Trojan detection in a 2D chip                                                                |

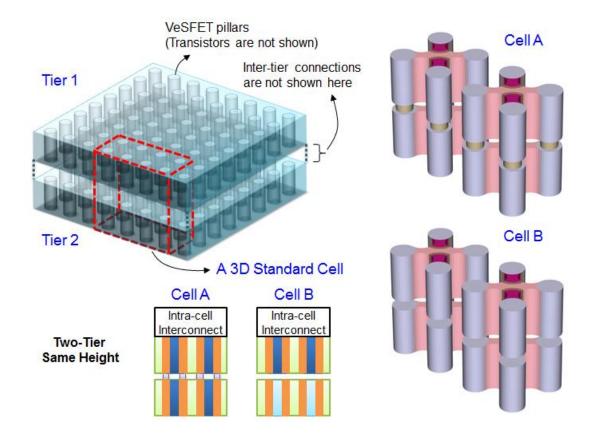

| Figure 6.4. VeSFET-based 3D standard cells, design feasible with conventional 2D EDA                     |

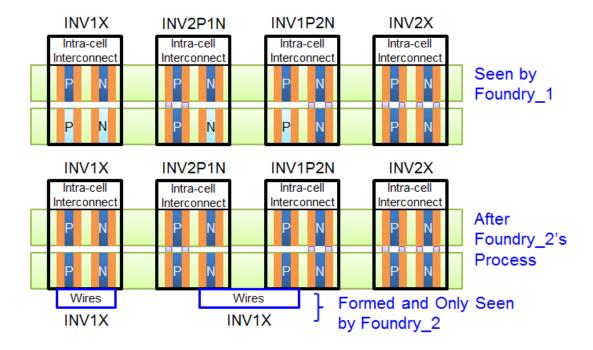

| tools                                                                                                    |

| Figure 6.5. Extra available circuits constructed by <i>foundry_2</i> , invisible to <i>foundry_1</i> 133 |

| Figure 6.6. VeSFET-based 3D chip split-fabrication                                                       |

| Figure 6.7. Trojan detection in a 3D chip                                                                |

| Figure 6.8. A simple logical encryption implementation                                                   |

| Figure 6.9. The difficulties of guessing missing nets                                                    |

| Figure 6.10. Selecting candidate nets to be partitioned                                                  |

| Figure 6.11. Transistor hiding and pin shaking                                                           |

| Figure 6.12. 3D Trojan detection scan chain (TD_Scan). (a) 3D structure; (b) four transistors            |

| share a pillar; (c) Trojan-free and attack scenarios; (d) DeCap cells142                                 |

| Figure 6.13. Trojan detection by <i>TD_Scan</i> path143                                                  |

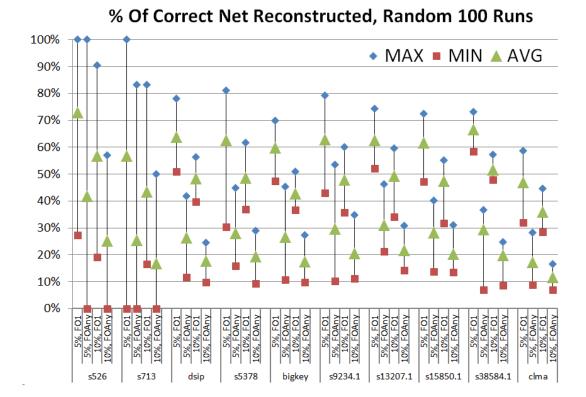

| Figure 6.14. Proximity attack results, randomly select nets to be partitioned in four cases: (1          |

| 5% FOL (2) 5% FOAmy (3) 10% FOL and (4) 10% FOAmy 145                                                    |

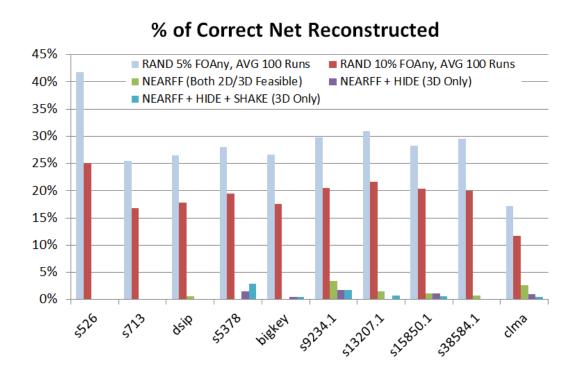

| Figure 6.15. Proximity attack results for the designs implemented with the proposed |     |

|-------------------------------------------------------------------------------------|-----|

| methodology                                                                         | 146 |

### LIST OF TABLES

| Table 2.1. AND- and OR-type VeSFETs with TGC and IGC Configurations              | 9  |

|----------------------------------------------------------------------------------|----|

| Table 2.2. VeSFET 6T SRAM Bit Cell Performance, VDD = 0.8V                       | 13 |

| Table 2.3. SRAM Cells in the Simulation                                          | 18 |

| Table 2.4. SRAM Array Configurations in the Simulation                           | 18 |

| Table 2.5. SRAM Array Access Time Comparison (ns)                                | 20 |

| Table 2.6. SRAM Array Dynamic Read Energy per Access (pJ)                        | 20 |

| Table 2.7. SRAM Array Leakage Power                                              | 21 |

| Table 2.8. SRAM Array Total Power @ 100MHz                                       | 21 |

| Table 3.1. The Benchmark Circuits from [46][47]                                  | 29 |

| Table 3.2. Summary of CMOS and VeSFET Technologies                               | 30 |

| Table 3.3. The BEOL Metal and VIA Characteristics                                | 31 |

| Table 3.4. Metal Characteristics of Each Layer                                   | 31 |

| Table 3.5. PDN Mesh Density for 2D Implementations                               | 33 |

| Table 3.6. The Synthesis Results                                                 | 35 |

| Table 3.7. 2D Implementation Results                                             | 36 |

| Table 3.8. fft_256 4-tier Partition, Power Consumption of Each Tier              | 42 |

| Table 3.9. The Inter-tier Connection Parameters                                  | 44 |

| Table 3.10 (a). CMOS and VeSFET Maximum Static IR-Drop Results, 2-Tier Partition |    |

| (CMOS / VeSFET, mV)                                                              | 50 |

| Table 3.10 (b). CMOS and VeSFET Maximum Static IR-Drop Results, 4-Tier Partition |    |

| (CMOS / VeSFET. mV)                                                              | 51 |

| Table 3.10 (c). CMOS and VeSFET Maximum Static IR-Drop Results, 8-Tier Partition              |

|-----------------------------------------------------------------------------------------------|

| (CMOS / VeSFET, mV)                                                                           |

| Table 3.11 (a). CMOS and VeSFET Clock Distribution Network (CDN) Characteristics, 2-          |

| Tier Partition (CMOS / VeSFET)57                                                              |

| Table 3.11 (b). CMOS and VeSFET Clock Distribution Network (CDN) Characteristics, 4-          |

| Tier Partition (CMOS / VeSFET)58                                                              |

| Table 3.11 (c). CMOS and VeSFET Clock Distribution Network (CDN) Characteristics, 8-          |

| Tier Partition (CMOS / VeSFET)59                                                              |

| Table 4.1. 4-LUT performance comparison in $2D\_FPGA$ and $3D\_FPGA$ , (Pillar radius $r =$   |

| 50nm, $h = 200$ nm, VDD = 0.8V)74                                                             |

| Table 4.2. Benchmerk Circuits <i>ABC</i> Synthesis and <i>VPR</i> Place & Route Information78 |

| Table 5.1. Symbols for F-RACC's Reconfiguration Status                                        |

| Table 5.2. Symbols for Performance Assessment                                                 |

| Table 5.3. The Simulated x86 System                                                           |

| Table 5.4. The Simulated Benchmarks                                                           |

| Table 5.5. Conditions Corresponding to Accelerators                                           |

| Table 5.6. Delay and Energy Consumption of Switching 1 bit in 8 BS-Slots114                   |

| Table 5.7. F-RACC Over C-RACC Speedup                                                         |

| Table 5.8. Speedup over CPU Software Path                                                     |

| Table 6.1. Possible Attacks and the Corresponding Situations Seen by the Two Untrusted        |

| Foundries                                                                                     |

# Chapter 1

## **INTRODUCTION**

## 1.1 Challenges of Future ICs

With the continuous demands on integrating more functions and devices on a single chip, the technology has been evolving along the scaling path for decades. However, recent and coming technologies such as 10nm, 7nm, 5nm, and below are approaching physical limitations. It is extremely difficult to integrate more devices solely by further transistor scaling. Although a chip can have more devices and functions by growing its size on 2D *X*-and *Y*-directions, there are limitations. Larger chips are more likely of having defects, which reduces yield. The longer signal wire lengths degrade the chip performance. Furthermore, drastic increase of power consumption and heat generation per unit chip area are unaccompanied by improvements in heat dissipation efficiency. These phenomena result in dark silicon effect when only a fraction of devices present on a chip can be operated at the same time. Dark silicon effect gradually limits the growth of future ICs. According to the results in [1-2], over 50% of the chip will not be utilized at 8nm.

However, the need of higher computing power is endless. Abundant applications in our daily life require faster computer chips. Such performance demand can be satisfied by integrating more devices together, better physical implementation method, or using more efficient computing architectures. In physical design's aspect, instead of growing chip size

along 2D directions, devices can be stacked vertically in 3D Z-direction allowing for integrating more devices within the same footprint. 3D integrated circuits (3D ICs) have been a focus of attention for years. They offer higher device density, smaller chip footprint, and shorter interconnect lengths. 3D ICs with better PPA (performance, power consumption, and area) over conventional 2D ICs have been reported in [3-16]; however, there are tradeoffs [9].

In computing architecture's aspect, power and utilization walls hinder further increase of general processors' computing capability achievable through scaling, which had been the main driver of the electronic industry for decades. To address this bottleneck, the ideas of moving specific tasks from general-purpose cores to specially designed computing units have been proposed. Conservation cores architectures [17] delegate jobs to specialized processors to save energy. Accelerator-rich architecture [18-20] includes a sea of heterogeneous dedicated hardware accelerators implementing different functions that may be invoked by applications running on the system. The performance, either speed or power, of specific applications can benefit from these specialized computing units. However, a system may need to handle wide spectrum of applications. Data centers or cloud computing systems need to respond to all kinds of requests; their workloads demand flexible and efficient computing platforms. In such cases, it is impractical to provide all kinds of specialized accelerators in accelerator-rich architectures. To address the demands of flexibility and performance, reconfigurable computing architectures provide attractive characteristics for this kind of systems [21-22]. The key idea is to offload system tasks to reconfigurable processing units, such as accelerators implemented by FPGAs. Thus, the functions of processing units can be reconfigured according to the workloads demand. However, the reconfiguration time is one of the concerns toward fast dynamic reconfigurable systems.

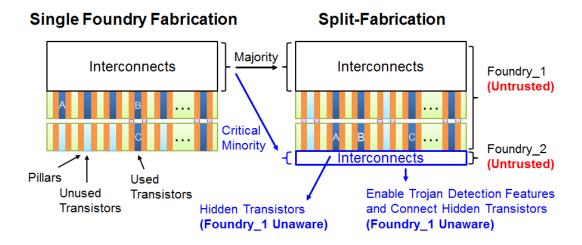

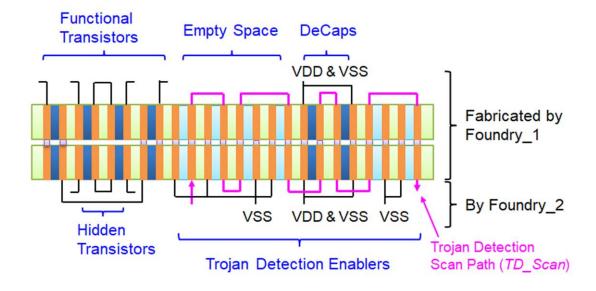

Besides the chip performance considerations, making trustworthy hardware has attracted designers' attentions especially for those sensitive applications. Today many design houses must outsource their design fabrication to a third party which is often an overseas foundry. Split-fabrication is proposed for combining the FEOL capabilities of an advanced but untrusted foundry with the BEOL capabilities of a trusted foundry [23-25]. Hardware security in this business model relates directly to the front-end foundry's ability to interpret the partial circuit design it receives in order to reverse engineer or insert malicious circuits. The published experimental results indicate that a relatively large percentage of the split nets can be correctly guessed [26] and there is no easy way of detecting the possibly inserted Trojans.

## 1.2 3D Integration Technologies

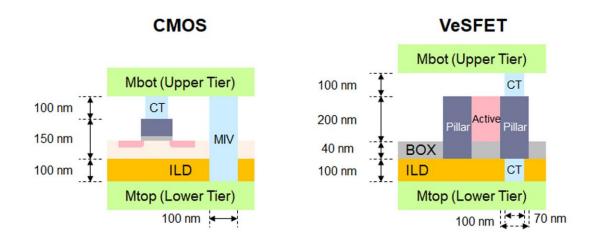

Although 3D ICs offer attractive features, there are tradeoffs [9] for integrating circuits vertically, such as higher power density and extra vertical inter-tier connections passing through device layers. Those inter-tier connection channels may occupy parts of the chip resulting in reduced area and placement freedom for transistors and other devices. The increased power density causes more problems with IR-drop and heat dissipation. In the era of aggressively scaled transistors and low VDD power supply, the acceptable maximum IR-drop is tightly constrained. Also, the increased heat dissipation may cause various temperature dependent problems, such as reliability, shorter product life, as well as unmodeled device and performance behaviors. Even worse, it may lead to dark silicon effect [8] [9] when devices on a chip cannot be fully operated due to the limited power and thermal budgets. The increasing power consumption is one of the key issues that hinder the growth of 3D integration; it can even be a showstopper. There are several 3D integration technologies; the best known uses

Through-Silicon VIAs (TSVs). TSVs connect two or more independent dies vertically with µ-bumps and costs extra area overhead, which is not ignorable. Newer technology called monolithic 3D (3Dm) integration integrates transistors and interconnects tier-by-tier on the same wafer. The inter-tier interconnects are implemented as small monolithic inter-tier VIAs (MIVs), whose sizes are like the usual metal VIAs [8]. Thus, abundant vertical inter-tier channels are feasible with these small MIVs. Although MIVs' area overhead is much less than TSVs', a portion of the die size needs to be reserved for MIVs. The area overhead is not zero.

### 1.3 VeSFET (Vertical Slit FET)

MOSFET technology has dominated the IC industry for decades and is approaching the physical limitation. Engineers and scientists have been working hard for a good substitution, which can continue the future growth. To keep technology rolling, it is expected that fundamental changes will be required.

Vertical Slit Field Effect Transistor (VeSFET) is a novel transistor with attractive characteristics, such as two-side accessibility, lower power consumption, high regularity, circle-based patterning, and good thermal properties [27-40]. The device's two-side accessible pillars are two-side routable, which mitigates routing congestion issues [35] in 2D designs and make the device 3D-integration friendly without extra area overhead for inter-tier connections. Reference [36] describes a three-tier 3D VeSFET SRAM cell. Furthermore, VeSFET has good thermal properties [37-38], which is another key advantage for 3D ICs. It has a special structure that is very different than those of the existing MOSFETs or FinFETs. The prototypes in 65nm-equivalent technology have been successfully fabricated [28] [29]. A device level study for 7nm equivalent technology shows that VeSFET's characteristics are

competitive to FinFET with comparable dimensions [31]. These characteristics make it a potentially good technology for future 2D/3D ICs.

## 1.4 Dissertation Organization

This dissertation investigates VeSFET monolithic 3D integration technology in system and physical levels. The domains include SRAM, physical design, design methodology, FPGA, dynamic reconfigurable architecture, and hardware security. Unique application and architectures are proposed, which are not feasible using MOSFET technologies. Chapter 2 introduces the fundaments of VeSFET technology including device, circuit, layout, SRAM, and monolithic 3D integration. SRAM performance is assessed and presented in Section 2.3. A physical design assessment of VeSFET monolithic 3D integration is provided in Chapter 3; which includes power delivery network (PDN)'s IR-drop analysis and clock distribution network (CDN)'s characteristics. Chapter 4 proposes a fast, fully verifiable, and hardware predictable ASIC design methodology using 3D FPGAs. The performance of VeSFET 3D FPGA is assessed. In Chapter 5, a high performance dynamic reconfigurable architecture using fast dynamic reconfigurable accelerators is proposed and assessed. In Chapter 6, a secure split-fabrication method is proposed for trustworthy hardware. Chapter 7 concludes this dissertation and discusses future opportunities.

# Chapter 2

## **VESFET TECHNOLOGY**

Emerging technologies provide opportunities for more efficient implementations of many applications. Vertical Slit Field Effect Transistor (VeSFET) is one of such emerging transistors with unique characteristics, which offer advantages over MOSFET technology.

### 2.1 Device Structure

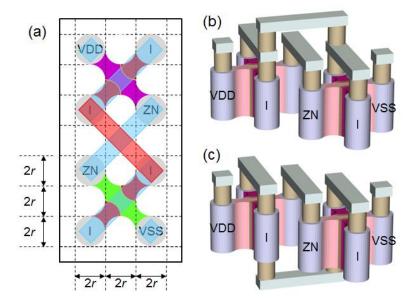

VeSFET is a highly regular twin-gate device with four vertical cylinder metal pillars and a horizontal channel. VeSFET's highly regular structure is intended for mitigating the fabrication difficulties while the device size is aggressively scaled. Figure 2.1 shows VeSFET structure and illustrates how transistors are integrated on a chip. The four metal pillars implement four vertical transistor terminals: two gates (G1 & G2), a drain (D), and a source (S). Such pillar structure naturally acts as vertical routing and heat dissipation channel, which is very friendly for 3D integration. The two gates offer better channel and leakage current control. Pillar radius (r) defines the technology feature size. VeSFET can be patterned with 2r diameter circles as shown in Figure 2.1 (c). This circle-based patterning offers the potential of optical proximity correction (OPC) free fabrication [28]. This characteristic simplifies OPC process, which is one of the major fabrication concerns while the transistor feature size is aggressively shrunk. The footprint of a single transistor bounded by the centers of four pillars is  $4r \times 4r = 16r^2$ . VeSFET pillar height (h) determines the driving strength of a single

transistor. *h* is conceptually equivalent to CMOS channel width. Since VeSFET is a twin-gate device, the equivalent transistor width is 2*h*. A VeSFET-based chip is composed of a regular array of metal pillars as shown in Figure 2.1 (b) and (d), each square bounded by four adjacent pillars is a feasible VeSFET location.

Figure 2.1. VeSFET; (a) 3D view of a single VeSFET; (b) 3D view of a VeSFET-based chip; (c) top view of a single VeSFET; (d) top view of a VeSFET-based chip. VeSFETs are placed as an array formed by metal pillars.

Another unique and useful feature of VeSFET is the possibility of controlling its behavior by properly adjusting signals applied to each of its gates. VeSFET can be implemented as tied gate configuration (TGC) or independent gate configuration (IGC). In a TGC VeSFET, two

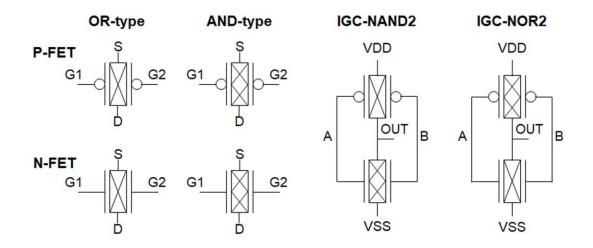

gates are hard-wired together and the transistor works as a normal MOSFET with a single gate. IGC VeSFET offers area and circuit design advantages; each of the two gates is controlled by an independent signal. An IGC VeSFET can be realized as an AND- or OR-type transistor by adjusting fabrication parameters [32] [33]. For an AND-type IGC VeSFET, the channel is turned on only when both gates are asserted; for an OR-type IGC VeSFET, it requires only one asserted gate to turn the channel on. Thus, an AND or an OR function can be realized by a single transistor. Table 2.1 summarizes the transistor operation modes of different VeSFET types. Figure 2.2 shows the IGC transistor representation and the circuit implementations of NAND2 and NOR2 functions. Only two IGC-VeSFETs are required for such functions, in contrast to the conventional CMOS implementations that require four transistors. IGC VeSFET also offers an attractive capability for transistor level circuit designs. The designer can treat one of the two gate terminals as a transistor gate and the other as a transistor profile adjuster. Each transistor's profile, such as I-V curve, threshold voltage, etc., can be adjusted by properly controlling one of the two gate terminals.

Table 2.1. AND- and OR-type VeSFETs with TGC and IGC Configurations

| Gate Configuration |        | AND-type |       | OR-type |       |       |

|--------------------|--------|----------|-------|---------|-------|-------|

| Configuration      | Gate 1 | Gate 2   | P-FET | N-FET   | P-FET | N-FET |

| TGC / IGC          | 0      | 0        | On    | Off     | On    | Off   |

|                    | 1      | 1        | Off   | On      | Off   | On    |

| IGC                | 0      | 1        | Off   | Off     | On    | On    |

|                    | 1      | 0        | Off   | Off     | On    | On    |

VeSFET in 65nm-equivalent technology has been fabricated [28] [29]. Its chip-level performance is studied in [34] using standard cell design methodology in 65nm-equivalent technology with pillar radius r = 50nm and heights h = 200nm and 400nm. The results show the power delay product is 35% of comparable 65nm CMOS. Reference [31] reports the

device-level comparison of VeSFETs with pillar radius r = 10nm and FinFET in 7nm technology using TCAD simulations. The results indicate high  $I_{\text{eff}}$  to  $I_{\text{off}}$  ratio, low gate capacitance, and competitive drivability with respect to a comparable FinFET.

Figure 2.2. Independent gate configuration (IGC) VeSFETs and the circuits.

## 2.2 Circuits and Layouts

In a VeSFET 2D chip, the devices are placed as a highly regular transistor array called *canvas*. Horizontal, vertical, and diagonal metal directions are feasible [28] [34]. To achieve better design manufacturability, design rules of metal layers are strictly defined using pillar radius *r* [28]. All wires within a metal layer are parallel, and their locations are aligned with pillars. VeSFET-based 2D design methodology and the performance comparisons to CMOS designs are developed and reported in [34]. It reports that VeSFET designs consume only 35% dynamic power and 2.6% leakage power of the comparable CMOS-based designs.

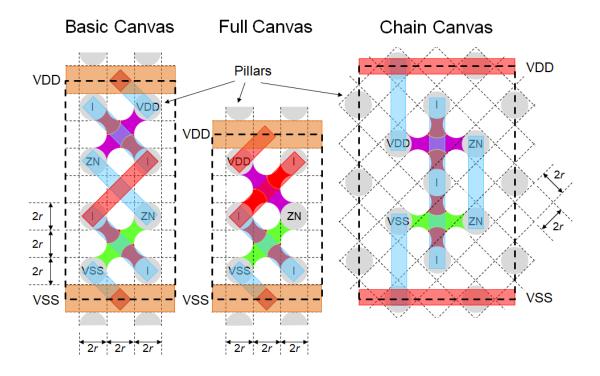

In the literature, circuits implemented in *basic canvas* and *chain canvas* were studied [34]. Besides them, there is a third implementation called *full canvas*. Figure 2.3 shows 1*P*1*N* inverter layouts implemented using each of them. In the *basic canvas*, the transistor array

consists of devices that do not share pillars. The maximum transistor utilization (i.e. the ratio of the number of used transistors to the maximum number of possible transistors) of *basic canvas* is 25%. In the *full canvas*, two transistors may share two pillars and every minimum size square bounded by four pillars may contain a transistor. Layouts of certain circuit structures may ideally achieve 100% transistor utilization. In the *chain canvas*, two transistors may share one pillar and the maximum transistor utilization is 50%. Reference [34] compared the 2D circuits implemented using *basic* and *chain canvases*. *Chain canvas* yields better results than *basic canvas* because of its denser footprint. Denser layouts using *full canvas* and diagonal metal are possible. The *chain canvas* layout shown in Figure 2.3 has the pillar array 45-degree rotated, which fits well into standard cell layout style using vertical and horizontal metal wires only.

Figure 2.3. Three VeSFET circuit layout styles and the corresponding 1P1N inverter standard cell implementations.

Since VeSFET's driving current is determined by pillar height, larger and different driving strengths can be achieved with the same footprint. However, the pillar heights of VeSFETs on the same 2D design plane should be the same for process considerations. A quantization effect as in the case of FinFETs is expected; shorter pillars provide better granularity but require larger area for the desired driving strength; higher pillars contribute larger driving current per unit area, but the granularity is poorer.

### **2.3 SRAMs**

SRAMs are fundamental blocks of VLSI systems, which are usually used for technology evaluation. This section provides a VeSFET SRAM performance assessment modeled by *CACTI 6.5* [41], a cache modeling tool. The results show that VeSFET SRAM design is speed competitive to CMOS SRAM with about 40% of dynamic read energy consumption and 35% of total power consumption for read access rate 100MHz.

#### 2.3.1 6T Bit Cell

In planar CMOS SRAM cell designs, the width of pull-up (PU), pull-down (PD) and passgate (PG) transistors are well tuned to achieve the best performance for the target specific application domain. These transistors' lengths are also specially designed to achieve high yield and density. In VeSFET SRAM cell design, all transistor widths are equal to the predefined VeSFET height, the characteristics of SRAM bit cell can be determined by the type of transistor used. Table 2.2 shows the VeSFET 6T SRAM bit cell pre-layout Hspice simulation results with VDD = 0.8V. All transistors are in TGC configuration with radius r = 50nm and height h = 200nm. The VeSFET transistor models are based on TCAD simulation

results [39-40]. The static noise margin (SNM) is measured in the closed word-line (WL) scenario.

Table 2.2. VeSFET 6T SRAM Bit Cell Performance, VDD = 0.8V

| VeSF | ET Type, | TGC | r = 50nm, $h = 200$ nm, by $Hspice$ |                  |                 |                    |  |  |

|------|----------|-----|-------------------------------------|------------------|-----------------|--------------------|--|--|

| PU   | PD       | PG  | SNM                                 | Write<br>Voltage | Read<br>Current | Leakage<br>Current |  |  |

| OR   | OR       | OR  | 299mV                               | 217mV            | 10.44uA         | 93.81pA            |  |  |

| AND  | OR       | OR  | 238mV                               | 346mV            | 10.44uA         | 10.85pA            |  |  |

| AND  | AND      | OR  | 346mV                               | 356mV            | 3.58uA          | 0.036pA            |  |  |

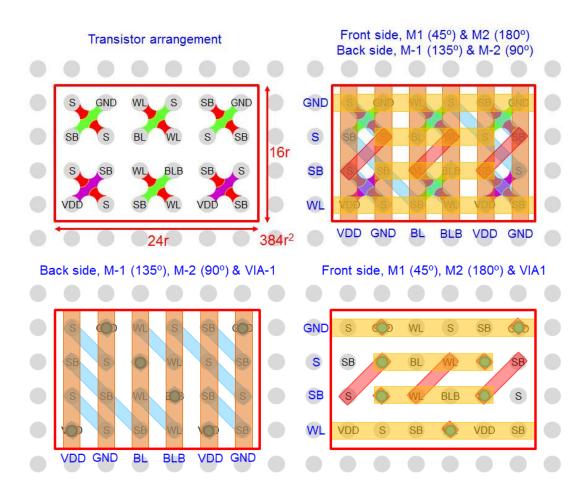

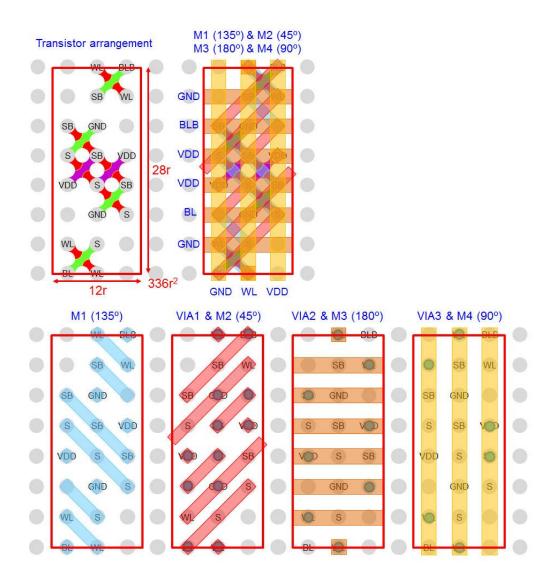

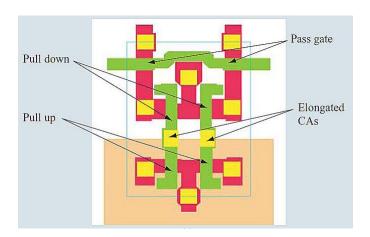

Figure 2.4. VeSFET cell layout  $v\theta$ , cell size =  $24r \times 16r = 384r^2$

In VeSFET designs, metal pillars can be shared, which reduces the area and parasitic capacitance. For the worst-case scenario without any pillar sharing, the area of a 6T SRAM cell is  $24r \times 16r = 384r^2$ . Figure 2.4 shows the transistor arrangement and the layout of such a worst area SRAM bit cell v0 with wire connections on both front and backside. A 3D diagram of cell v0 is shown in Figure 2.5. M-1 and M-2 are two metal layers on the backside; M1 and M2 are on the front side. The metal wires in the same layer are all aligned in a unified direction and all metal segments start and end at pillars. These properties increase the regularity of layout patterns and reduce the manufacturing process complexity.

Figure 2.5. VeSFET cell v0 3D diagram (Courtesy of Professor Wojciech P. Maly, Department of Electrical and Computer Engineering, Carnegie Mellon University)

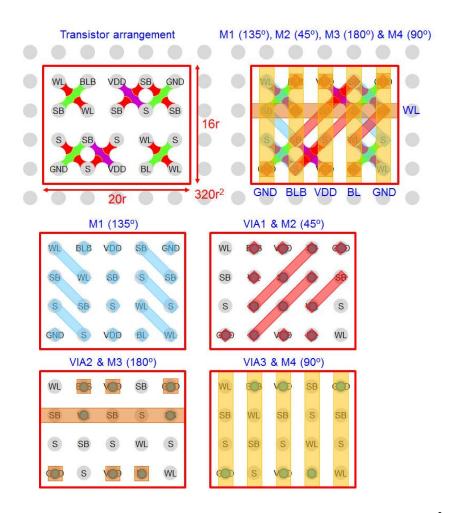

Two other one-side routed VeSFET layouts vI and v2 are shown in Figure 2.6 and 2.7, respectively. Cell vI is optimized for power and speed, where BL and WL lengths within the cell are 12r and 28r; the cell area is  $336r^2$ . Cell v2 is optimized for area, where BL and WL

lengths within the cell are 16r and 20r and the cell area is  $320r^2$ . If r = 50nm, the area of cell v1 is  $0.6 \mu m \times 1.4 \mu m = 0.84 \mu m^2$ , and of cell v2 is  $1 \mu m \times 0.8 \mu m = 0.8 \mu m^2$ . In these two layouts, all the transistors are TGC configured. Metal 1 (M1) is  $135^{\circ}$  oriented; metal 2, 3 and 4 (M2, M3, and M4) are  $45^{\circ}$ ,  $180^{\circ}$  and  $90^{\circ}$  oriented respectively. The transistors and wires are well

Figure 2.6. VeSFET cell layout vI, cell size =  $12r \times 28r = 336r^2$

arranged, which allows for the cell abutment to form a sub-array, the VDD and GND power straps are all aligned with *BL* and *BLB* shielded to enhance power network robustness and to reduce *BL* coupling noise. In a traditional read scheme, *BL*s are pre-charged to VDD and 1)

keep floating if the read data is 1; 2) pulled down by a cell if the read data is 0. The voltage level on a floating *BL* could degrade due to the coupling effect from adjacent *BL*s pulling down. This degraded voltage level could cause read errors.

Figure 2.7. VeSFET cell layout v2, cell size =  $20r \times 16r = 320r^2$

### 2.3.2 SRAM Array Performance

To evaluate VeSFET SRAM performance and to compare with CMOS designs, a CMOS cache modeling tool *CACTI 6.5* [41] is used and modified to support VeSFET technology. *CACTI*'s modeling engine is not touched to guarantee that: 1) CMOS SRAM results are not changed by the tool modifications, and 2) the modeling methods are the same. VeSFET

technology parameters required for *CACTI*'s computation are extracted by *Hspice* simulation based on the VeSFET transistor model with radius r = 50nm. There are three ITRS-based CMOS models originally embedded in *CACTI*: High Performance (*HP*), Low Operating Power (*LOP*), and Low Standby Power (*LSTP*). For our comparisons we assumed the default *CACTI* CMOS SRAM cell of area  $146F^2$  (*F* is the feature size) and aspect ratio 1.46 [42]. Figure 2.8 shows the cell footprint from [43] which is referenced in [42] as the default cell model in *CACTI*. For 65nm technology, the cell size is  $0.65\mu$ m x  $0.949\mu$ m =  $0.61685\mu$ m<sup>2</sup>. Tables 2.3 and 2.4 summarize four simulated SRAM cells and six array configurations.

Figure 2.8. Default *CACTI* CMOS cell footprint [43] with area =  $1.46F^2$  (*F* is transistor feature size) and aspect ratio 1.46

Table 2.3. SRAM Cells in the Simulation

| Cells                          | WL Length (µm) | BL Length<br>(µm) | Area<br>(μm²) |

|--------------------------------|----------------|-------------------|---------------|

| CACTI Default 65nm CMOS        | 0.65           | 0.949             | 0.61685       |

| VeSFET cell $v0$ , $r = 50$ nm | 1.2            | 0.8               | 0.96          |

| VeSFET cell $vI$ , $r = 50$ nm | 1.4            | 0.6               | 0.84          |

| VeSFET cell $v2$ , $r = 50$ nm | 1.0            | 0.8               | 0.80          |

**Table 2.4. SRAM Array Configurations in the Simulation**

| Size (kByte) | Cells / WL | Cells / BL |

|--------------|------------|------------|

| 0.5          | 32         | 32         |

| 2            | 64         | 64         |

| 4            | 128        | 64         |

| 8            | 128        | 128        |

| 16           | 256        | 128        |

| 32           | 256        | 256        |

In this simulation, OR-type Tied-Gate-Controlled (TGC) VeSFET SRAM with radius r = 50nm is compared to the *CACTI*'s default ITRS-based 65nm CMOS technology. We note here that it is not straightforward to decide which CMOS technology node is equivalent to VeSFET technology with r = 50nm. Here we assume equivalence based on metal layout design rules. If device layer rules were adopted, CMOS 65nm node would be equivalent to VeSFET with r much less than 50nm. The VeSFET height h is set to 200nm. The VDD of VeSFET is 0.8V, and the default 65nm CMOS VDDs in *CACTI* are 1.1V (HP), 0.8V (LOP) and 1.2V (LSTP).

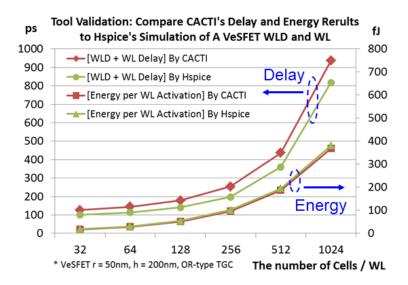

We validate the speed and energy consumption of CACTI's VeSFET simulation results. Circuits composed of a single word-line driver (WLD) and a word-line (WL) with different bit-cell loadings were simulated by Hspice and compared to the results extracted from CACTI simulation. Figure 2.9 shows the results. In Hspice simulation, the WL is modeled by RC  $\pi$ -models including SRAM's pass-gate (PG) gate loadings. The measured delay includes WLD delay and the WL RC delay from the output of WLD to the end of WL. It can be observed that the delay number reported by CACTI is greater than the delay measured by Hspice; this provides additional delay margin of performance modeling. The energy measured is the energy consumed per WL activation of a WLD driving a WL with SRAM gate loadings.

Figure 2.9. Tool validation: CACTI and Hspice delay and energy simulation results comparison of a WLD + WL. Based on OR-type TGC VeSFETs.

Tables 2.5 to 2.8 show the speed and power comparison for 65nm CMOS technologies and OR-type TGC VeSFET with height h=200nm and radius r=50nm. The speed of VeSFET SRAM is comparable to 65nm CMOS High Performance (HP) with about 40% of dynamic read energy consumption. Compared with 65nm CMOS Low Operating Power (LOP), the dynamic read energy is about 60%. VeSFETs consume about 2% of 65nm CMOS LOP leakage power. Although VeSFET's leakage power is greater than 65nm CMOS Low Standby Power (LSTP), VeSFET is much faster with about 35% total power including active and standby parts. VeSFET's twin-gate junctionless structure provides a better channel controllability and smaller parasitic capacitance, which are critical characteristics for low power designs.

**Table 2.5. SRAM Array Access Time Comparison (ns)**

| Size | 65nm CMOS |           |      | VeSI    | VeSFET Cell v0 |     |                | ET C     | ell <i>v1</i> | VeSFET Cell v2 |      |     |

|------|-----------|-----------|------|---------|----------------|-----|----------------|----------|---------------|----------------|------|-----|

| kB   | HP        | TP HP LOP | ns   | % to HP | % to LOP       | ns  | % to <i>HP</i> | % to LOP |               |                |      |     |

| 0.5  | 0.81      | 1.31      | 1.95 | 0.63    | 77%            | 48% | 0.59           | 73%      | 45%           | 0.62           | 76%  | 47% |

| 2    | 0.86      | 1.40      | 2.05 | 0.70    | 82%            | 50% | 0.66           | 77%      | 47%           | 0.70           | 81%  | 50% |

| 4    | 0.87      | 1.42      | 2.10 | 0.74    | 85%            | 52% | 0.70           | 81%      | 49%           | 0.73           | 84%  | 51% |

| 8    | 1.00      | 1.68      | 2.43 | 0.94    | 95%            | 56% | 0.87           | 87%      | 52%           | 0.93           | 94%  | 56% |

| 16   | 1.02      | 1.72      | 2.49 | 1.03    | 101%           | 60% | 0.97           | 95%      | 57%           | 1.01           | 99%  | 59% |

| 32   | 1.21      | 2.09      | 2.97 | 1.38    | 114%           | 66% | 1.24           | 102%     | 59%           | 1.36           | 112% | 65% |

Table 2.6. SRAM Array Dynamic Read Energy per Access (pJ)

| Size | 65nm CMOS |      |          | VeSI  | VeSFET Cell v0 |          |       | VeSFET Cell v1 |                 |       | VeSFET Cell v2 |          |  |

|------|-----------|------|----------|-------|----------------|----------|-------|----------------|-----------------|-------|----------------|----------|--|

| kB   | HP        | LOP  | LS<br>TP | рJ    | % to <i>HP</i> | % to LOP | рJ    | % to HP        | % to <i>LOP</i> | рJ    | % to <i>HP</i> | % to LOP |  |

| 0.5  | 2.6       | 1.7  | 3.2      | 1.04  | 40%            | 61%      | 0.99  | 39%            | 58%             | 1.02  | 40%            | 60%      |  |

| 2    | 5.9       | 3.9  | 7.1      | 2.42  | 41%            | 61%      | 2.25  | 38%            | 57%             | 2.39  | 41%            | 61%      |  |

| 4    | 11.2      | 7.6  | 13.6     | 4.72  | 42%            | 62%      | 4.39  | 39%            | 58%             | 4.67  | 42%            | 62%      |  |

| 8    | 14.8      | 10.2 | 17.7     | 6.26  | 42%            | 62%      | 5.58  | 38%            | 55%             | 6.22  | 42%            | 61%      |  |

| 16   | 29.0      | 19.9 | 34.6     | 12.37 | 43%            | 62%      | 11.02 | 38%            | 55%             | 12.28 | 42%            | 62%      |  |

| 32   | 41.3      | 28.8 | 49.4     | 17.81 | 43%            | 62%      | 15.56 | 38%            | 54%             | 17.72 | 43%            | 61%      |  |

**Table 2.7. SRAM Array Leakage Power**

|      | Leakage Power (mW & μW) |             |              |                 |                 |                 |  |  |  |  |  |  |

|------|-------------------------|-------------|--------------|-----------------|-----------------|-----------------|--|--|--|--|--|--|

| Size | 6                       | 5nm CMOS    | S            |                 | VeSFET          |                 |  |  |  |  |  |  |

| (kB) | HP (mW)                 | LOP<br>(mW) | LSTP<br>(µW) | Cell νθ<br>(μW) | Cell v1<br>(µW) | Cell v2<br>(µW) |  |  |  |  |  |  |

| 0.5  | 0.4                     | 0.01        | 0.02         | 0.18            | 0.18            | 0.18            |  |  |  |  |  |  |

| 2    | 1.6                     | 0.03        | 0.08         | 0.59            | 0.58            | 0.59            |  |  |  |  |  |  |

| 4    | 2.9                     | 0.05        | 0.14         | 1.05            | 1.04            | 1.05            |  |  |  |  |  |  |

| 8    | 5.7                     | 0.10        | 0.28         | 2.06            | 2.05            | 2.06            |  |  |  |  |  |  |

| 16   | 10.7                    | 0.19        | 0.54         | 3.87            | 3.84            | 3.87            |  |  |  |  |  |  |

| 32   | 21.2                    | 0.38        | 1.06         | 7.62            | 7.61            | 7.62            |  |  |  |  |  |  |

Table 2.8. SRAM Array Total Power @ 100MHz

|      | To         | Total Power (mW) @ Read Access Rate 100MHz |              |                     |                     |                    |  |  |  |  |  |  |

|------|------------|--------------------------------------------|--------------|---------------------|---------------------|--------------------|--|--|--|--|--|--|

| Size | 6          | 5nm CMOS                                   | S            |                     | VeSFET              |                    |  |  |  |  |  |  |

| (kB) | HP<br>(mW) | LOP<br>(mW)                                | LSTP<br>(mW) | Cell <i>v0</i> (mW) | Cell <i>v1</i> (mW) | Cell<br>v2<br>(mW) |  |  |  |  |  |  |

| 0.5  | 0.6        | 0.18                                       | 0.32         | 0.10                | 0.10                | 0.10               |  |  |  |  |  |  |

| 2    | 2.1        | 0.42                                       | 0.71         | 0.24                | 0.23                | 0.24               |  |  |  |  |  |  |

| 4    | 4.0        | 0.81                                       | 1.36         | 0.47                | 0.44                | 0.47               |  |  |  |  |  |  |

| 8    | 7.2        | 1.12                                       | 1.77         | 0.63                | 0.56                | 0.62               |  |  |  |  |  |  |

| 16   | 13.6       | 2.19                                       | 3.46         | 1.24                | 1.11                | 1.23               |  |  |  |  |  |  |

| 32   | 25.3       | 3.26                                       | 4.94         | 1.79                | 1.56                | 1.78               |  |  |  |  |  |  |

These preliminary results are very promising. Although VeSFETs are novel devices and were not well tuned for SRAM performance, VeSFET SRAM is speed competitive with much less power consumption than CMOS bulk. We believe that better VeSFET cell layouts and better device profiles are also possible. VeSFET technology could offer an attractive solution for future VLSI technology.

## 2.4 Two-side Accessibility and Monolithic 3D Integration

3D stacked transistor layers increase transistor density, support more functions, and the reduced chip size provides higher speed and consumes less power. A 3D IC stack can be implemented using different methods as shown in Figure 2.10. Through-silicon VIAs (TSVs) were developed to vertically connect two or more independent dies with μ-bumps. TSVs pass through the entire die thickness, their cross-sectional area cannot be too small for reliability and process reasons and the available channel count of vertical interconnects is limited. TSVs induce area overhead; other devices cannot use the regions occupied by TSVs.

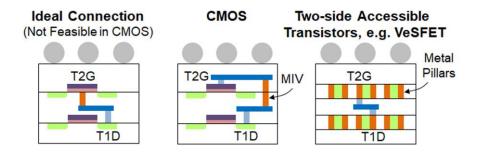

Figure 2.10. Different 3D IC technologies. Two-side accessible transistor monolithic 3D offers shortest cross-tier interconnects.

Monolithic 3D (3Dm) IC technology [3-5] [7-8] [10-16] was proposed to increase vertical channel counts, to reduce the length of vertical interconnect, and to eliminate  $\mu$ -bump bonding. In MOSFET 3Dm technology, transistor tiers are fabricated on the same wafer and are vertically connected by monolithic inter-tier VIAs (MIVs). Although those MIVs are much smaller than TSVs, they have similar structure.

In MOSFET 3D designs, either with planar FETs, FinFETs, or tri-gate FETs, TSVs and MIVs are implemented on empty space and introduce area overhead. TSV is big and tall, it goes through the whole thickness of a die and connects the adjacent lower die via μ-bumps [5] [8-9]. It has large footprint and keep-out zone for process considerations. Dummy TSVs are often inserted, which costs more area, to guarantee the successful inter-tier connections and for thermal dissipation purposes. TSVs' locations are usually reserved prior to placing active elements. MIVs are very small, and they are usually inserted in empty space after other elements have been placed. The available locations for MIVs are constrained, which implies that their numbers may be limited, especially for designs reaching higher utilization, the location of a MIV may not be optimized, and extra interconnects are required to connect MIVs to their corresponding devices.

Figure 2.11. A Tied-Gate-Controlled (TGC) 1P1N inverter. (a) Layout; (b) Conventional structure one-side routed; (c) Two-side routed implementation.

Two-side accessible transistors such as VeSFET are very well suited to implement monolithic 3D integrated circuits. This is a unique characteristic that is not feasible in conventional transistors such as MOSFET, FinFET, SOI, etc. Vertical inter-tier connections can be implemented using front and back sides of a transistor layer. As illustrated in Figure 2.10, the best way to connect transistor 1's drain (T1D) and transistor 2's gate (T2G) is through T2G's bottom; however, this is not feasible in the current MOSFET technology. But in VeSFET technology, every transistor terminal (pillars) on a tier is freely accessible by its adjacent tiers. It offers the capability of creating ideally positioned, short, and less complicated inter-tier interconnects for 3D ICs. Beside 3D ICs, the two-side accessible pillars also benefit 2D ICs. This feature doubles routing resources since the chip can be routed on both the front and back sides [35]. Figure 2.11 (a-b) shows a VeSFET TGC 1P1N inverter layout routed on one side and Figure 2.11 (c) shows a VeSFET-unique two-sided implementation.

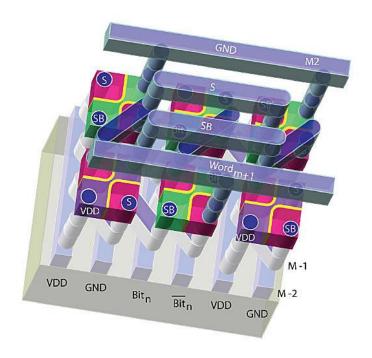

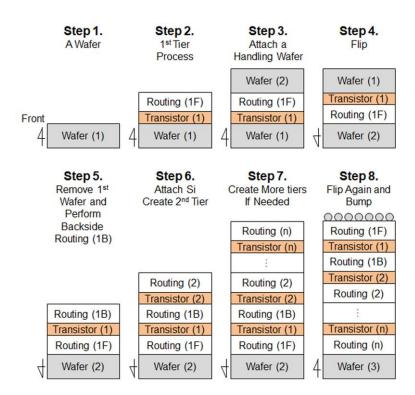

Figure 2.12. VeSFET-based monolithic 3D integration flow. In Step 8, the bumps can be made on the *n-th* tier directly or on the first tier with a flip.

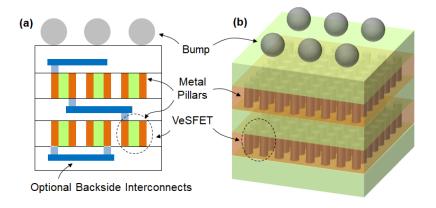

Figure 2.12 illustrates the integration flow of a VeSFET monolithic 3D circuit. The first two steps are the same as in 2D circuits. Then, in the steps 3 to 5, the backside routing is created. The backside routing shares the same BEOL process flow as the front-side routing. This unique capability is achieved by VeSFET's two-side accessible metal pillars. After step 5, a two-side routed 2D chip is formed and is ready to be bumped as a regular 2D chip. Steps 6 and 7 create more tiers and form a monolithic 3D stack. At the end, the designer can decide to do bumping upon the routing on the *n-th* tier directly, or flip again to bump on the first tier. Figure 2.13 shows a cross-sectional view and the 3D structure of a two-tier VeSFET monolithic 3D IC stack.

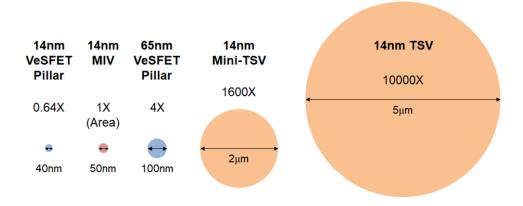

Reference [8] illustrates the diameter comparison of MIVs (50nm), aggressively sized TSVs (5μm), and mini-TSVs (2μm) in 14nm technology, where the keep-out zones are not

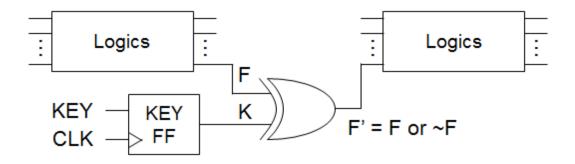

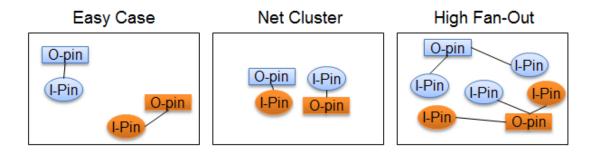

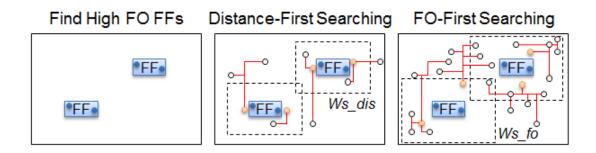

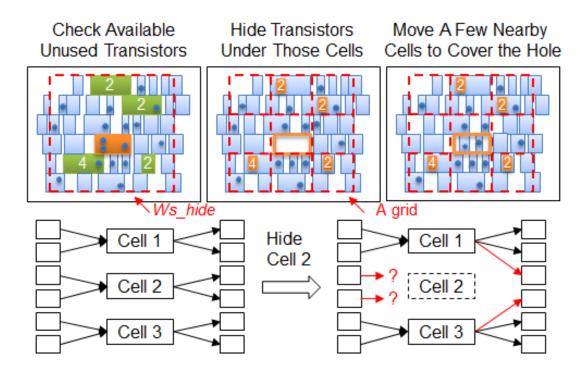

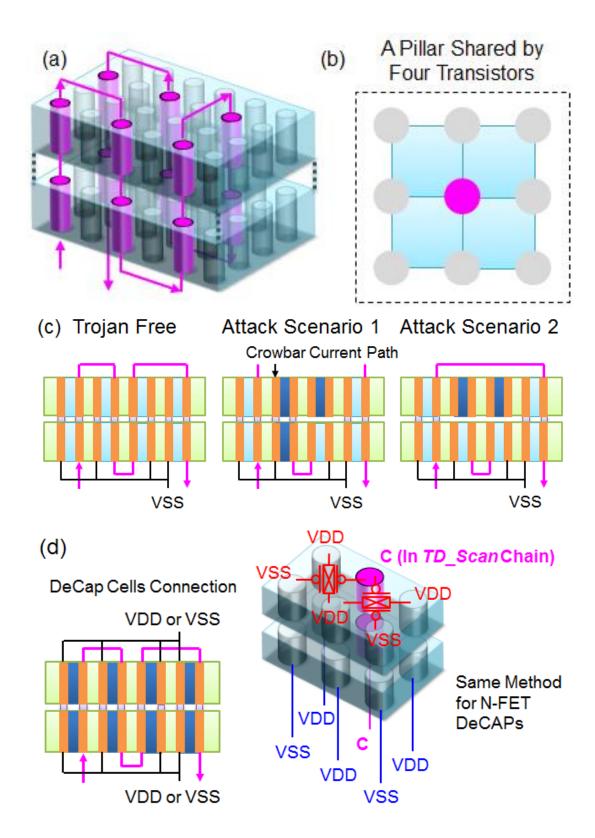

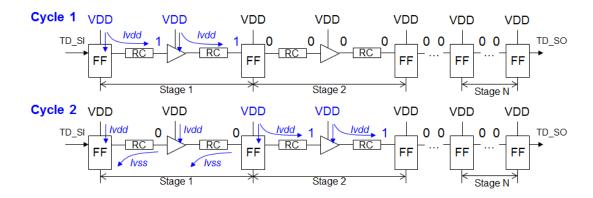

Figure 2.13. VeSFET-based monolithic 3D IC (a) cross-sectional view; (b) monolithic 3D IC structure.