## UC San Diego UC San Diego Electronic Theses and Dissertations

### Title

Robust Physical Design and Design Technology Co-Optimization Methodologies at Advanced VLSI Technology

**Permalink** https://escholarship.org/uc/item/5wb14729

**Author** Kim, Minsoo

**Publication Date**

2023

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA SAN DIEGO

#### Robust Physical Design and Design Technology Co-Optimization Methodologies at Advanced VLSI Technology

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Computer Engineering)

by

Minsoo Kim

Committee in charge:

Professor Andrew B. Kahng, Chair Professor Chung-Kuan Cheng Professor Sujit Dey Professor Farinaz Koushanfar

Copyright

Minsoo Kim, 2023

All rights reserved.

The dissertation of Minsoo Kim is approved, and it is acceptable in quality and form for publication on microfilm and electronically.

University of California San Diego

2023

### DEDICATION

To my family.

| Dissertation App                          | proval Page                                                                                                                                                                                                                  | iii                              |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Dedication                                |                                                                                                                                                                                                                              | iv                               |

| Table of Content                          | ts                                                                                                                                                                                                                           | v                                |

| List of Figures .                         |                                                                                                                                                                                                                              | vii                              |

| List of Tables                            |                                                                                                                                                                                                                              | xiv                              |

| Acknowledgmen                             | nts                                                                                                                                                                                                                          | xviii                            |

| Vita                                      |                                                                                                                                                                                                                              | xxi                              |

| Abstract of the I                         | Dissertation                                                                                                                                                                                                                 | xxiv                             |

| 1.1 New C<br>1.1.1<br>1.1.2<br>1.1.3      | troduction                                                                                                                                                                                                                   | 1<br>1<br>3<br>4<br>5            |

| -                                         | eneral Physical Design Methodology<br>I Bounded-Skew Steiner Trees to Minimize Maximum <i>k</i> -Active Dynamic                                                                                                              | 10                               |

| 2.1.1<br>2.1.2<br>2.1.3<br>2.1.4          | Related Work         Problem Formulation         Experimental Setup and Results         Conclusion         ECO: Concurrent Refinement of Detailed Place-and-Route for an Efficient                                           | 10<br>15<br>17<br>27<br>34       |

| ECO A<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4 | Leo. concurrent Remember of Detailed Flace-and-Route for an Efficient         utomation         CoRe-ECO Framework         Switchbox Generation         Experimental Setup and Results         Conclusion         wledgments | 35<br>37<br>41<br>49<br>58<br>58 |

| -                                         | chnology-Aware Physical Design Methodology                                                                                                                                                                                   | 59                               |

|                                           | on Break-Aware Leakage Power Optimization and Detailed Placement in         nm VLSI         Related Work         2 <sup>nd</sup> DB-Aware Leakage Optimization and Placement                                                 | 60<br>64<br>65                   |

#### TABLE OF CONTENTS

|          | 3.1.3          | Experimental Setup and Results                                        | 72  |

|----------|----------------|-----------------------------------------------------------------------|-----|

|          | 3.1.4          | Conclusion                                                            | 76  |

| 3.2      | Detaile        | ed Placement for IR Drop Mitigation by Power Staple Insertion in Sub- |     |

|          |                | VLSI                                                                  | 77  |

|          | 3.2.1          | Related Work                                                          | 79  |

|          | 3.2.2          | Our Approach                                                          | 81  |

|          | 3.2.3          | Experimental Setup and Results                                        | 86  |

|          | 3.2.4          | Conclusion                                                            | 95  |

| 3.3      | Acknow         | wledgments                                                            | 96  |

| Chapter  | 4 D            | esign-Technology Co-Optimization                                      | 97  |

| 4.1      | PROBI          | E2.0: A Systematic Framework for Routability Assessment from Technol- |     |

|          | ogy to         | Design in Advanced Nodes                                              | 98  |

|          | 4.1.1          | Related Work                                                          | 101 |

|          | 4.1.2          | The PROBE2.0 Framework                                                | 105 |

|          | 4.1.3          | Routability Assessment and Learning-Based $K_{th}$ Prediction         | 115 |

|          | 4.1.4          | Experimental Setup and Results                                        | 122 |

|          | 4.1.5          | Conclusion                                                            | 133 |

| 4.2      | A Nov          | el Framework for DTCO: Fast and Automatic Routability Assessment      |     |

|          |                | Cachine Learning for Sub-3nm Technology Options                       | 136 |

|          | 4.2.1          | DTCO Framework and Configuration for Sub-3nm Nodes                    | 137 |

|          | 4.2.2          | Routability Assessment and Block-Level Area Case Study                | 139 |

|          | 4.2.3          | Machine Learning (ML)-Assisted Routability Assessment                 | 143 |

|          | 4.2.4          | Conclusion                                                            | 144 |

| 4.3      | PROBI          | E3.0: A Systematic Framework for Design-Technology Pathfinding with   |     |

|          | Improv         | ved Design Enablement                                                 | 144 |

|          | 4.3.1          | Related Work                                                          | 146 |

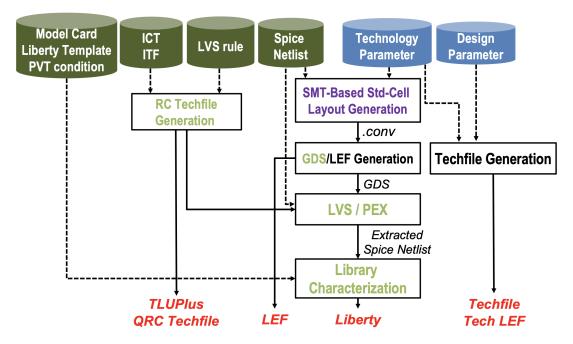

|          | 4.3.2          | Standard-Cell Library and PDK Generation                              | 148 |

|          | 4.3.3          | Power Delivery Network                                                | 154 |

|          | 4.3.4          | Enhanced Artificial Designs for PPAC Exploration                      | 159 |

|          | 4.3.5          | Cell Width-Regularized Placements for More Realistic Routability As-  | 165 |

|          | 126            |                                                                       |     |

|          | 4.3.6<br>4.3.7 | Experimental Setup and Results                                        | 172 |

| 1 1      |                | Conclusion                                                            | 182 |

| 4.4      | ACKNO          | wledgments                                                            | 184 |

| Chapter  | 5 C            | onclusion                                                             | 185 |

| Bibliogr | aphy           |                                                                       | 188 |

#### LIST OF FIGURES

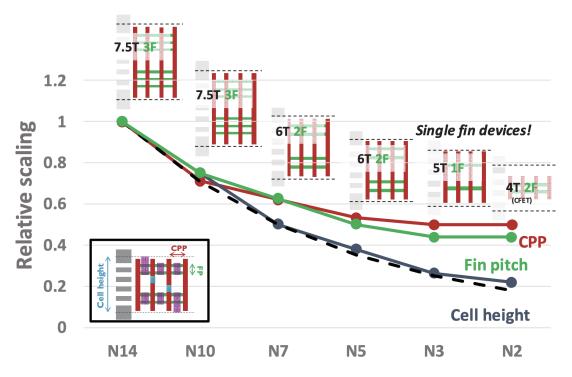

| Figure 1.1. | The scaling rates of fin pitch, contacted poly pitch (CPP) and standard-<br>cell height have slowed down over time, and device architectures have<br>also evolved from fin field-effect transistor (FinFET) to complementary<br>field-effect transistor (CFET) [104].                                                                                                                   | 2  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

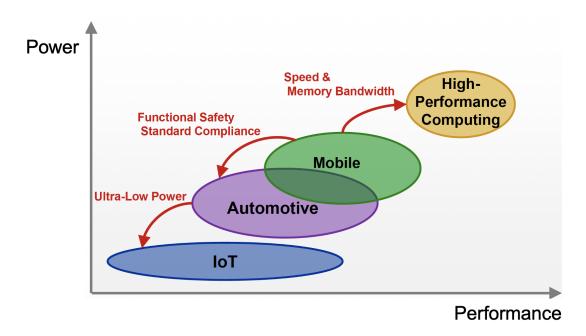

| Figure 1.2. | Power and performance requirements for applications [89]                                                                                                                                                                                                                                                                                                                                | 3  |

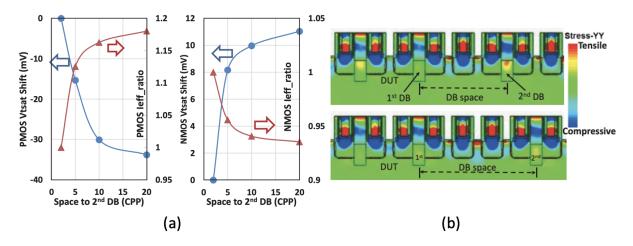

| Figure 1.3. | Local layout effect [128]. (a) Saturation voltage and effective current shifts caused by the second diffusion break effect. (b) Interlayer dielectric (ILD) stress in a TCAD simulation, which is a function of the spacing between the first and the second diffusion breaks                                                                                                           | 4  |

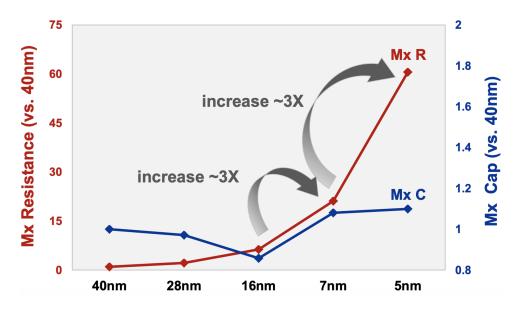

| Figure 1.4. | Resistance of BEOL metal layers ( <i>Mx</i> ) increases exponentially as technology advances [89].                                                                                                                                                                                                                                                                                      | 5  |

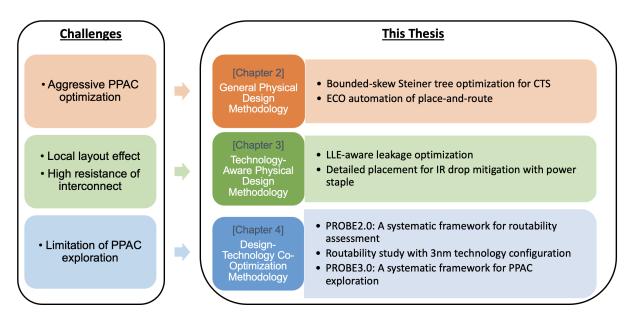

| Figure 1.5. | Overview of this thesis                                                                                                                                                                                                                                                                                                                                                                 | 6  |

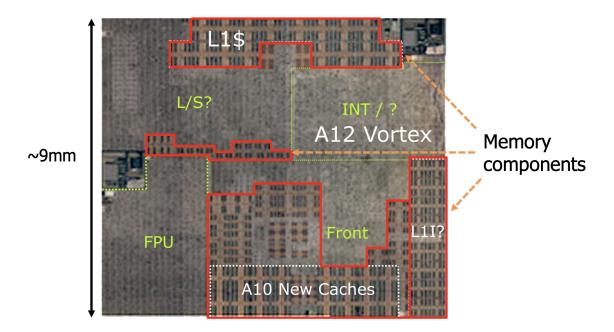

| Figure 2.1. | An example floorplan view of a memory-dominant chip [175]. The red boxes indicate memory components in the chip                                                                                                                                                                                                                                                                         | 11 |

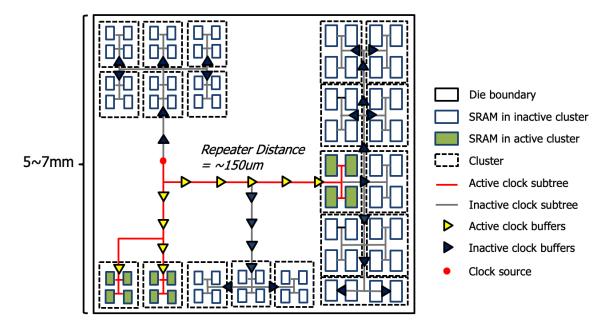

| Figure 2.2. | "Cartoon" of floorplan and clock tree structures for a memory-dominant SOC design, which motivates our <i>k</i> -active dynamic power minimization formulation.                                                                                                                                                                                                                         | 12 |

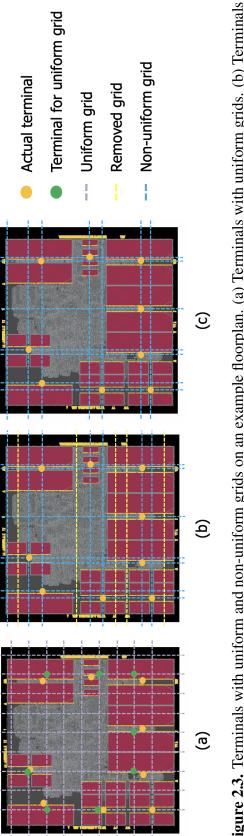

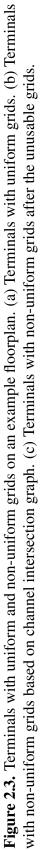

| Figure 2.3. | Terminals with uniform and non-uniform grids on an example floorplan.<br>(a) Terminals with uniform grids. (b) Terminals with non-uniform grids<br>based on channel intersection graph. (c) Terminals with non-uniform grids<br>after the unusable grids.                                                                                                                               | 23 |

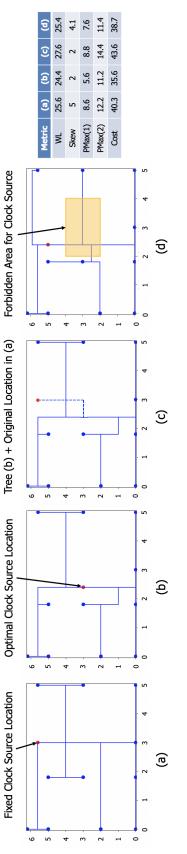

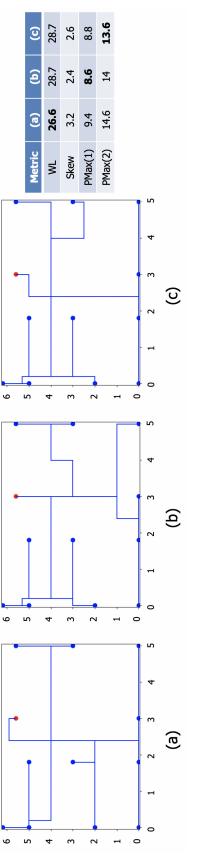

| Figure 2.4. | Example trees for flexible clock sources. (a) A tree with a fixed clock source. (b) A tree with a movable clock source, with optimal source location. (c) A tree with the tree from (b) and the original source location from (a). (d) A tree with a movable clock source that has a forbidden area.                                                                                    | 25 |

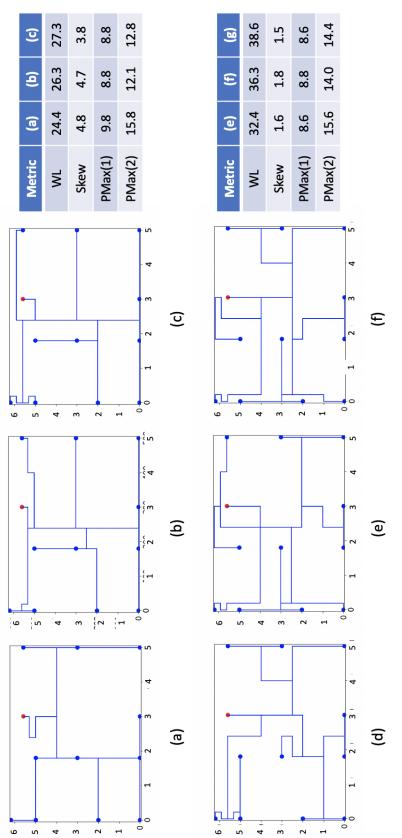

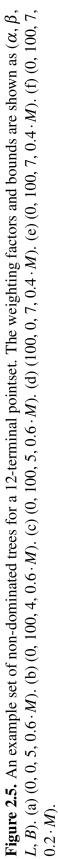

| Figure 2.5. | An example set of non-dominated trees for a 12-terminal pointset. The weighting factors and bounds are shown as $(\alpha, \beta, L, B)$ . (a) (0, 0, 5, 0.6 $\cdot$ <i>M</i> ). (b) (0, 100, 4, 0.6 $\cdot$ <i>M</i> ). (c) (0, 100, 5, 0.6 $\cdot$ <i>M</i> ). (d) (100, 0, 7, 0.4 $\cdot$ <i>M</i> ). (e) (0, 100, 7, 0.4 $\cdot$ <i>M</i> ). (f) (0, 100, 7, 0.2 $\cdot$ <i>M</i> ). | 28 |

| Figure 2.6. | Example trees with various weighting factors in our objective function. (a) A tree solution to minimize the total wirelength. (b) A tree solution to minimize $PMax(1)$ . (c) A tree solution to minimize $PMax(2)$                                                                                                                                                                     | 29 |

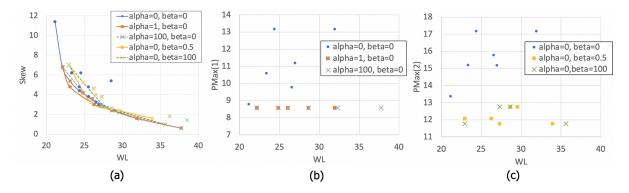

| Figure 2.7.  | Scatter plots for (a) skew-wirelength, (b) $PMax(1)$ -wirelength and (c) $PMax(2)$ -wirelength for the 12-terminal pointset with various weighting factors $\alpha$ and $\beta$ . Additional points that do not correspond to the figure legend are obtainable with other values of $\alpha$ , $\beta$ , $L$ and $B$ | 30 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

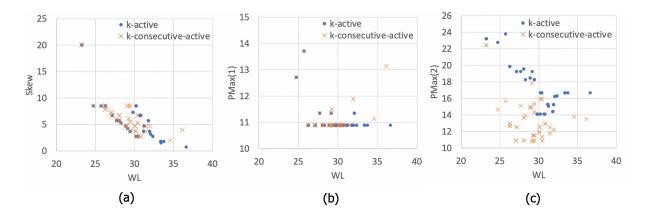

| Figure 2.8.  | Scatter plots for (a) skew-wirelength, (b) $PMax(1)$ -wirelength and (c) $PMax(2)$ -wirelength for <i>k</i> -active sinks and <i>k</i> -consecutive-active sinks                                                                                                                                                     | 32 |

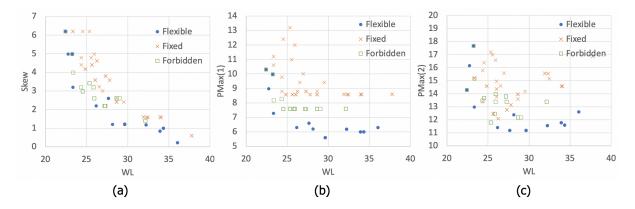

| Figure 2.9.  | Scatter plots for (a) skew-wirelength, (b) $PMax(1)$ -wirelength and (c) $PMax(2)$ -wirelength for <i>fixed</i> and <i>flexible</i> clock source locations, as well as flexible clock source locations with a <i>forbidden</i> $2 \le x \le 4, 2 \le y \le 4$ area.                                                  | 32 |

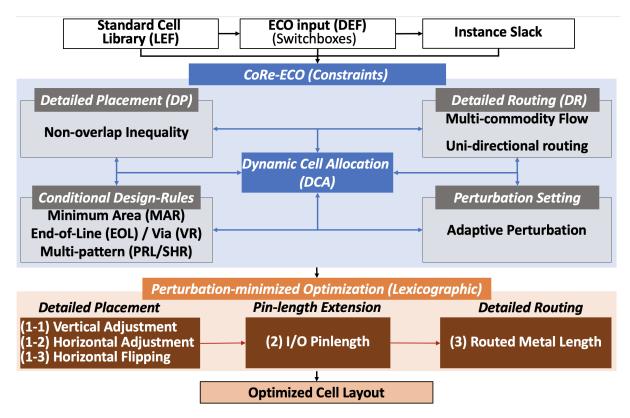

| Figure 2.10. | Framework overview.                                                                                                                                                                                                                                                                                                  | 36 |

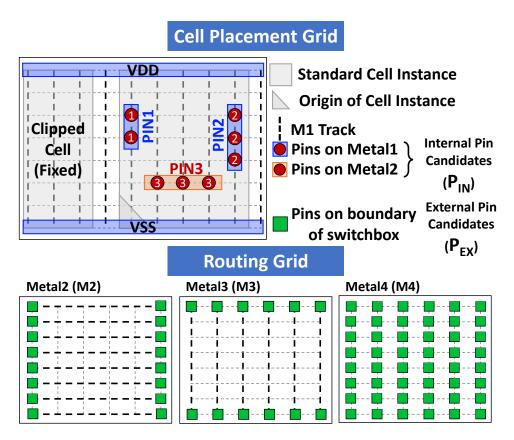

| Figure 2.11. | Grid-based place-and-route architecture.                                                                                                                                                                                                                                                                             | 39 |

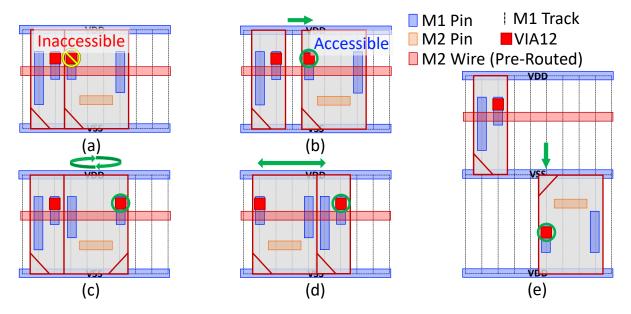

| Figure 2.12. | Placement adjustments. (a) Initial placement. (b) Horizontal shifting. (c)<br>Horizontal flipping. (d) Cell swapping. (e) Vertical shifting                                                                                                                                                                          | 40 |

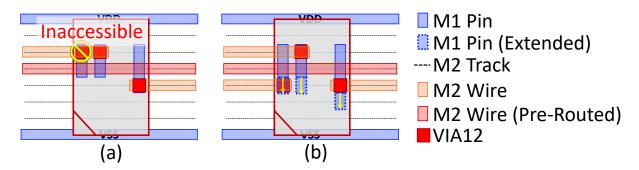

| Figure 2.13. | Pinlength extension. (a) Initial placement. (b) Pinlength extension                                                                                                                                                                                                                                                  | 41 |

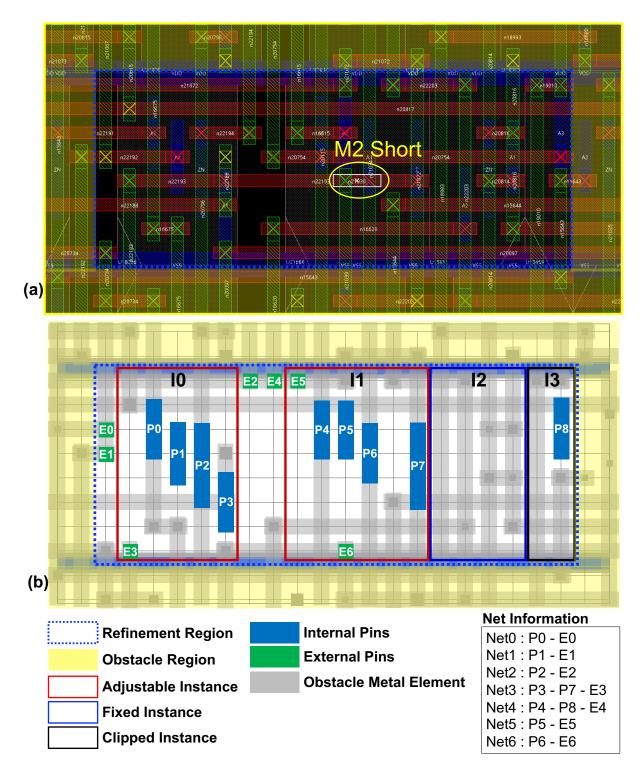

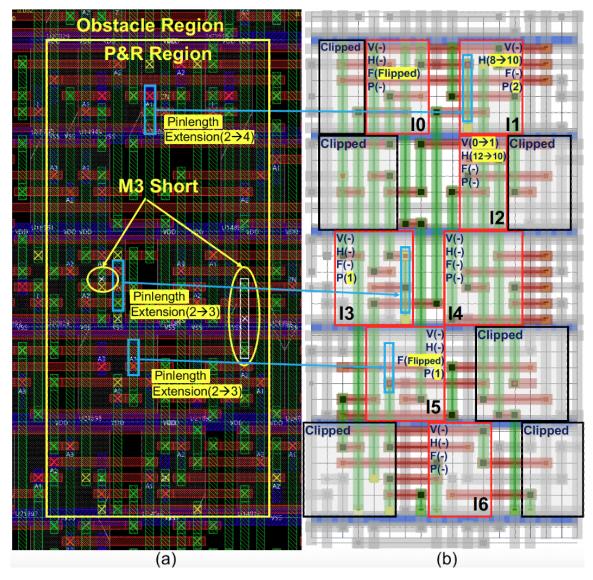

| Figure 2.14. | Switchbox generation. (a) Local window with one DRC, displayed by the commercial tool [144]. (b) Visualization of the generated switchbox                                                                                                                                                                            | 42 |

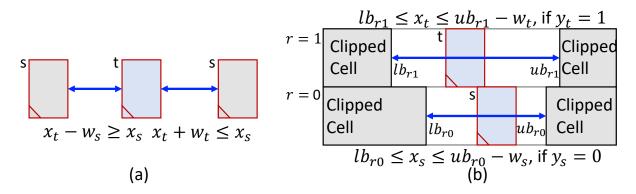

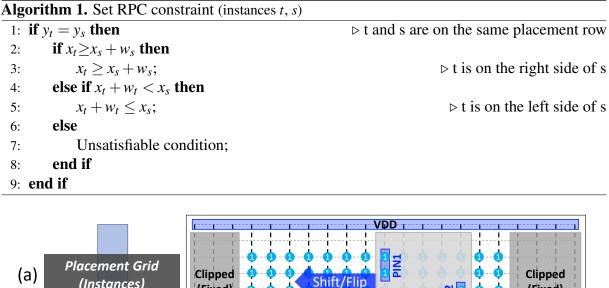

| Figure 2.15. | Placement constraints. (a) Relative positions between two instances in the same placement row. (b) Boundary condition of each placement row                                                                                                                                                                          | 45 |

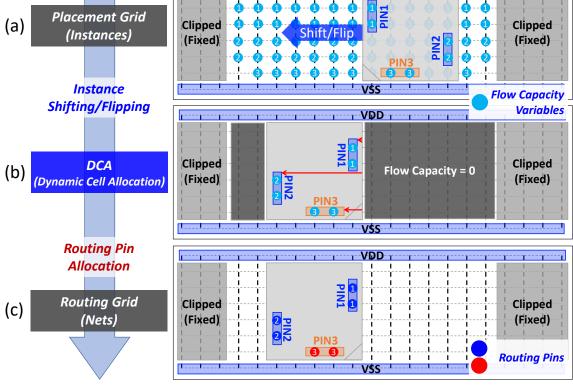

| Figure 2.16. | Dynamic cell allocation (DCA)                                                                                                                                                                                                                                                                                        | 46 |

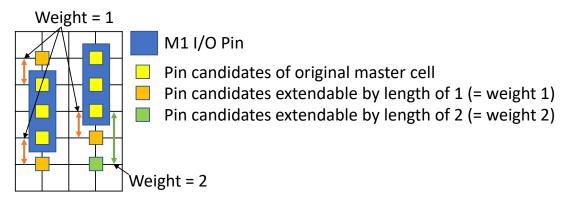

| Figure 2.17. | Weighted extendable pin candidates.                                                                                                                                                                                                                                                                                  | 48 |

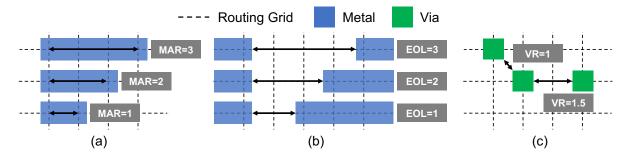

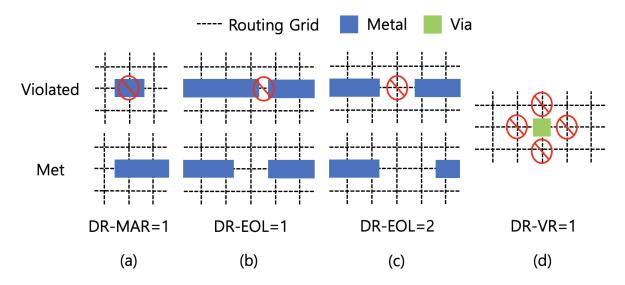

| Figure 2.18. | Grid-based conditional design rules: (a) MAR, (b) EOL and (c) VR                                                                                                                                                                                                                                                     | 48 |

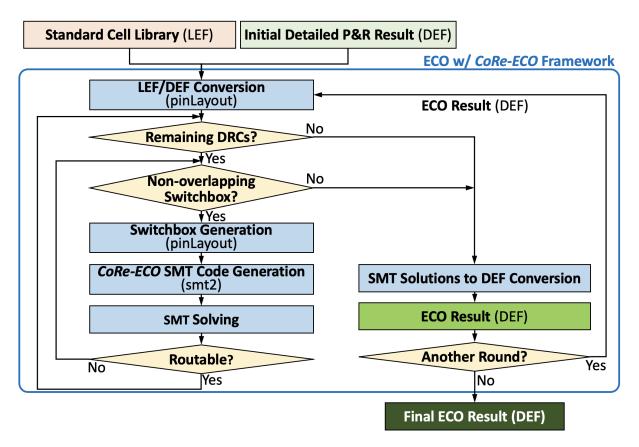

| Figure 2.19. | Overall ECO flow using <i>CoRe-ECO</i> framework                                                                                                                                                                                                                                                                     | 51 |

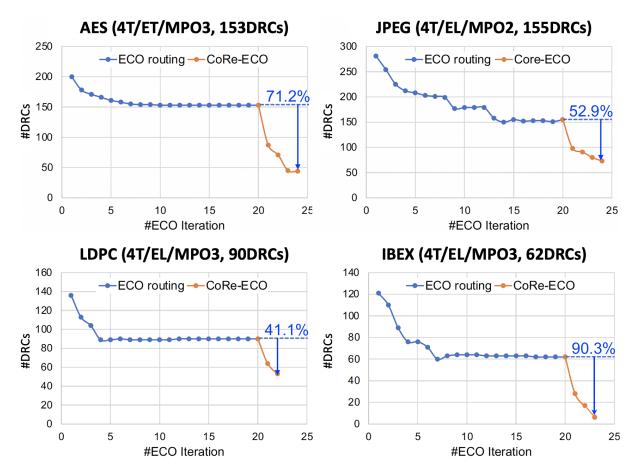

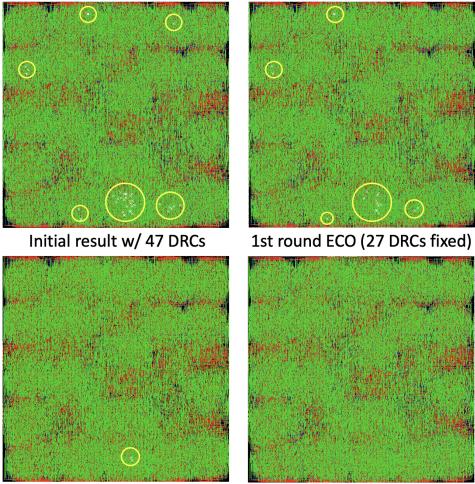

| Figure 2.20. | Example trends of the number of DRCs by the ECO routing and the proposed <i>CoRe-ECO</i> iterations                                                                                                                                                                                                                  | 52 |

| Figure 2.21. | DRC reductions by <i>CoRe-ECO</i> rounds for AES (4T/ET/MPO2)                                                                                                                                                                                                                                                        | 56 |

| Figure 2.22. | Example of refinement operations in the proposed ECO flow (Index 38 case in Table 2.7). (a) Switchbox with three DRCs. (b) Routable solution with placement adjustments and pinlength extensions                                                                                                                     | 57 |

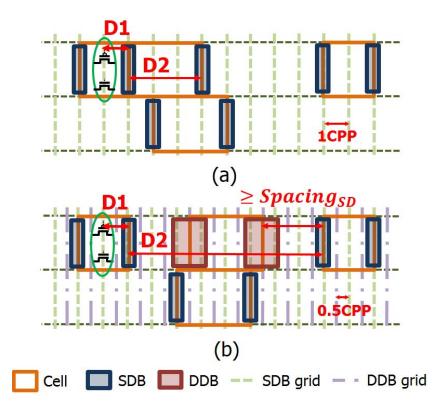

| Figure 3.1.  | Examples illustrating DB types and placement constraints. (a) Layout with four SDB cells ( <i>Type-I</i> ). (b) <i>Mixed-DB</i> layout with three SDB cells plus one DDB cell ( <i>Type-II</i> )                                                                                                                                   | 61 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

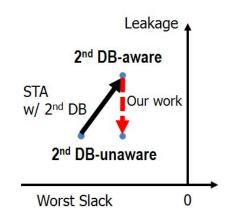

| Figure 3.2.  | Target of our work. We seek to minimize <i>actual</i> , $2^{nd}$ DB-aware leakage power with no timing degradation.                                                                                                                                                                                                                | 63 |

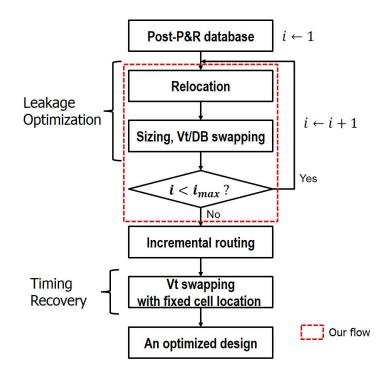

| Figure 3.3.  | Overview of our overall optimization flow. The red box indicates steps that we implement. A commercial P&R tool is used for all other steps in the flow.                                                                                                                                                                           | 65 |

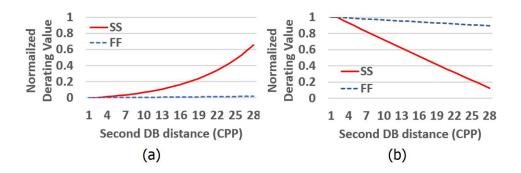

| Figure 3.4.  | Normalized derating values for (a) leakage power and (b) cell delay according to the $2^{nd}$ DB distance.                                                                                                                                                                                                                         | 66 |

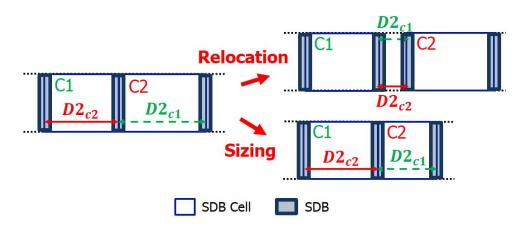

| Figure 3.5.  | Examples of $2^{nd}$ DB distance change due to cell relocation and sizing. The red color of $D2_{C2}$ indicates the $2^{nd}$ DB distance of C2 and the green color of $D2_{C1}$ indicates the $2^{nd}$ DB distance of C1                                                                                                           | 67 |

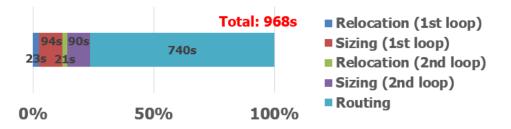

| Figure 3.6.  | Runtime analysis for AES design. We use Type-II, 60% initial utilization and 0.5ns clock period. $1^{st}$ <i>loop</i> denotes the first iteration of our optimization and $2^{nd}$ <i>loop</i> denotes the second iteration. Sizing includes sensitivity calculations and cell moves for gate sizing, Vt swapping and DB swapping. | 74 |

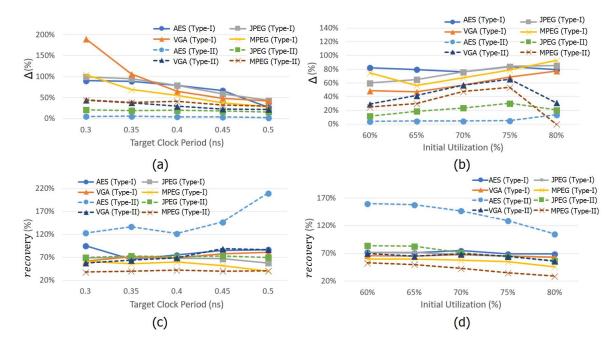

| Figure 3.7.  | Studies of leakage power with varying target clock period and initial utilization. Leakage increment from the $2^{nd}$ DB effect vs. (a) target clock period and (b) initial utilization. Leakage recovery by our optimization vs. (c) target clock period and (d) initial utilization.                                            | 76 |

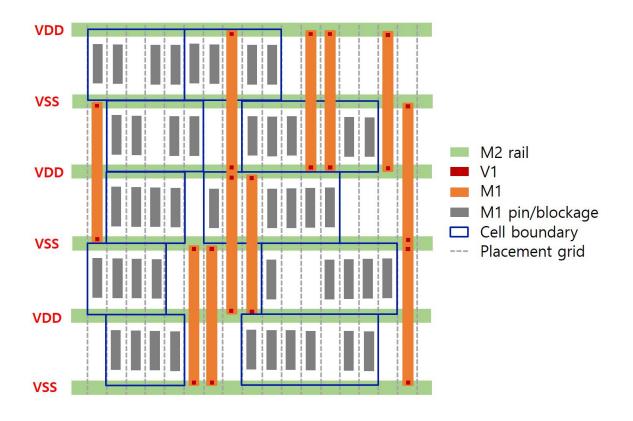

| Figure 3.8.  | Illustration of power staple insertions                                                                                                                                                                                                                                                                                            | 78 |

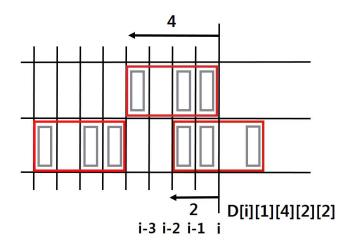

| Figure 3.9.  | The case represented by D[i][1][4][2][2].                                                                                                                                                                                                                                                                                          | 86 |

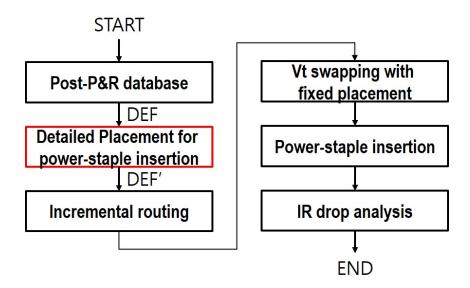

| Figure 3.10. | Overall flow of our work. The red box indicates steps that we implement.<br>Commercial tools [144] [148] are used for all other steps                                                                                                                                                                                              | 87 |

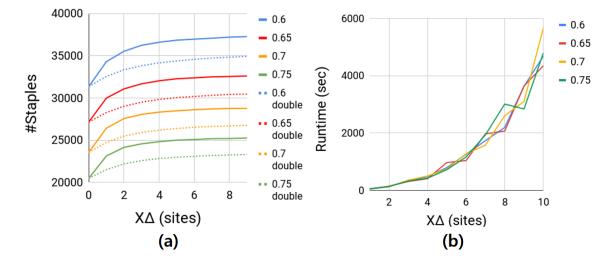

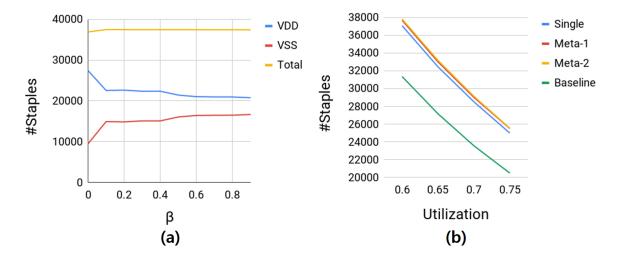

| Figure 3.11. | (a) Sensitivity of #staples to displacement range $x_{\Delta}$ and (b) sensitivity of runtime to displacement range $(x_{\Delta})$ .                                                                                                                                                                                               | 88 |

| Figure 3.12. | Sensitivities of (a) #staples and (b) total cell displacement, to the displacement factor ( $\alpha$ ).                                                                                                                                                                                                                            | 90 |

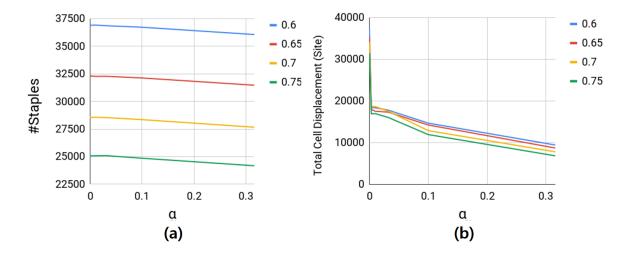

| Figure 3.13. | Design examples with different lengths of power staples. (a) Power staple length = 2 row heights. (b) Power staple length = 10 row heights                                                                                                                                                                                         | 91 |

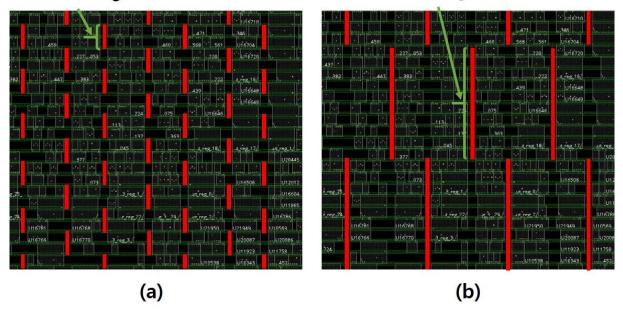

| Figure 3.14. | (a) Number of staples (total, VDD and VSS) that can be placed, versus balance factor ( $\beta$ ) (AES with utilization 0.60) and (b) number of staples that can be placed, versus utilization by different strategies (AES with utilization between 0.60 and 0.75).                           | 94  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

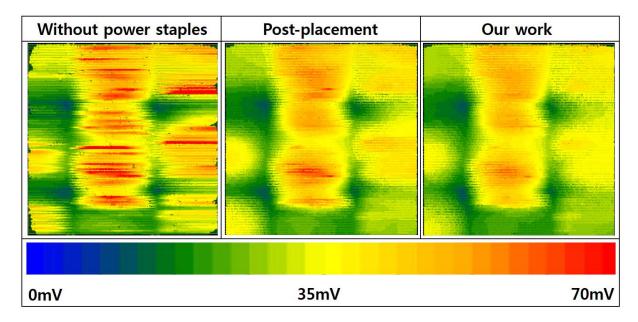

| Figure 3.15. | Heatmaps of vectorless dynamic IR drop for AES.                                                                                                                                                                                                                                               | 95  |

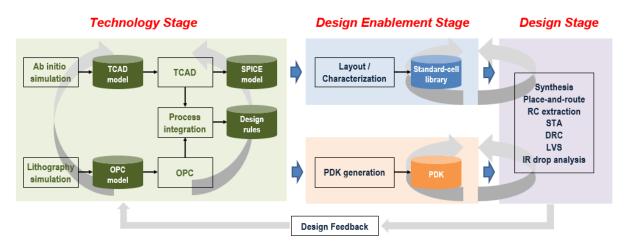

| Figure 4.1.  | The DTCO process consists of three main stages: <i>Technology</i> , <i>Design Enablement</i> , and <i>Design</i> . Figure is redrawn from [174]                                                                                                                                               | 99  |

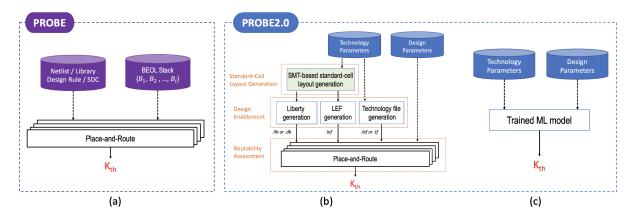

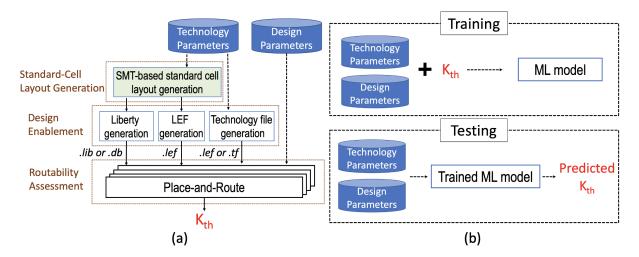

| Figure 4.2.  | Overall flows for PROBE [64] and PROBE2.0. (a) PROBE only evaluates BEOL stack options. (b) The PROBE2.0 flow includes standard-cell layout generation [26] [82], design enablement and routability assessment. (c) The PROBE2.0 flow uses a trained learning-based model to predict $K_{th}$ | 105 |

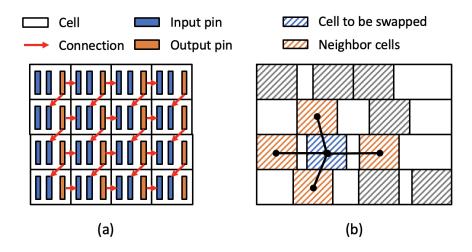

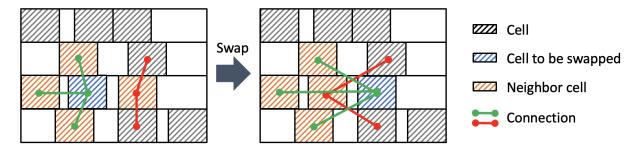

| Figure 4.3.  | Placements for PROBE [64]. (a) A mesh-like placement based on a 2-input cell. (b) A cell width-regularized placement. The orange-striped cells are considered to be neighbors of the blue-striped cell. The blue-striped cell is swapped with a randomly-selected neighbor.                   | 106 |

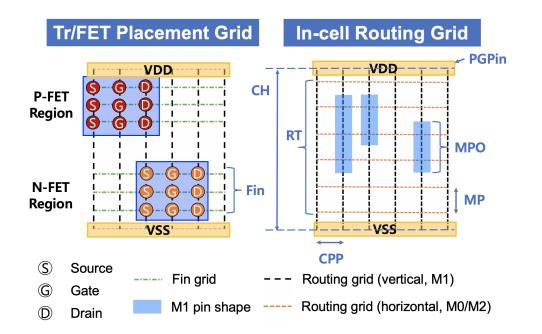

| Figure 4.4.  | A grid-based standard-cell architecture and technology parameters for standard cells                                                                                                                                                                                                          | 107 |

| Figure 4.5.  | DR-MAR, DR-EOL and DR-VR design rules                                                                                                                                                                                                                                                         | 109 |

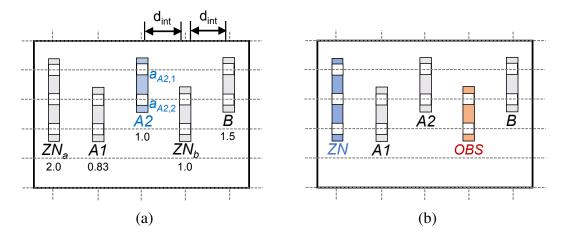

| Figure 4.6.  | Example of pin shape selection in a standard cell (2Fin, 5RT, 2MPO and EUV-Loose). (a) Initial layout of OAI21_X1 from SMT-based layout generation. (b) The OAI21_X1 layout after RPA-based pin shape selection.                                                                              | 114 |

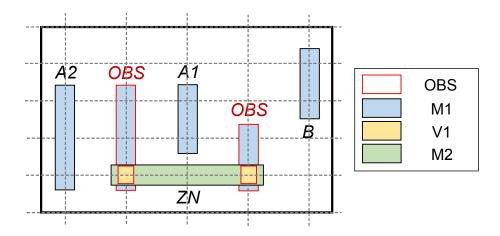

| Figure 4.7.  | Example of standard-cell layout with top-metal-only pin shape selection. We show an initial layout of AOI21_X1 (2Fin, 5RT, 2MPO and EUV-Loose). In this case, the <i>ZN</i> pin has only the M2 pin shape, and the M1 and V1 shapes become OBS.                                               | 114 |

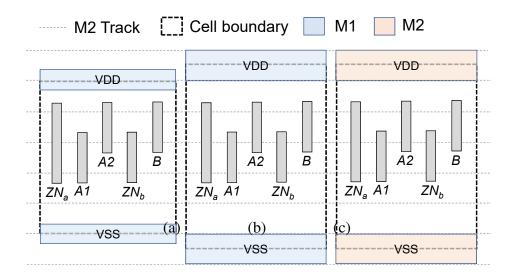

| Figure 4.8.  | Power and ground pin (PGpin) examples: (a) BPR, (b) M1 and (c) M1+M2.<br>The signal pin shapes (gray) are the same regardless of PGpin                                                                                                                                                        | 115 |

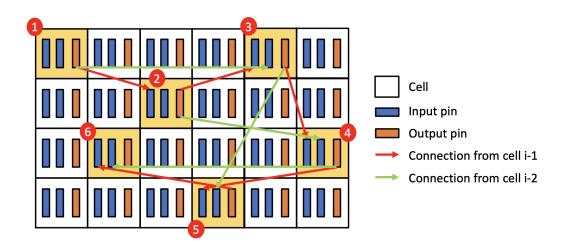

| Figure 4.9.  | Example of knight's tour-based connections in a placement of 2-input cells.<br>Numbers in red circles indicate the knight's tour ordering                                                                                                                                                     | 117 |

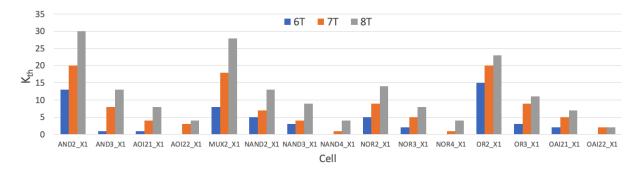

| Figure 4.10. | $K_{th}$ results from knight's tour-based cell-level routability assessments across various track heights and cell masters. 15 cell masters from 6T, 7T and 8T standard-cell libraries are used in this experiment.                                                                           | 124 |

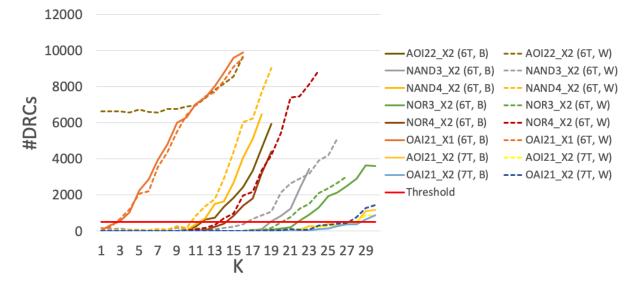

| Figure 4.11. | Cell-level routability assessments showing #DRCs versus <i>K</i> with different pin shape selection methods. RPA-Best ( <i>B</i> ) and RPA-Worst ( <i>W</i> ) pin shape selection methods are shown. Solid lines are for cells with RPA-Best, and dashed lines are for cells with RPA-Worst                              | 125 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

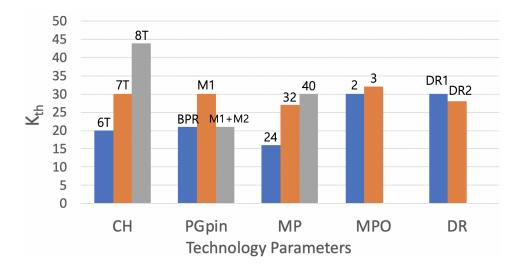

| Figure 4.12. | Design-level assessments with various technology parameters                                                                                                                                                                                                                                                              | 127 |

| Figure 4.13. | <i>K<sub>th</sub></i> results of design-level routability assessments with various design parameters.                                                                                                                                                                                                                    | 129 |

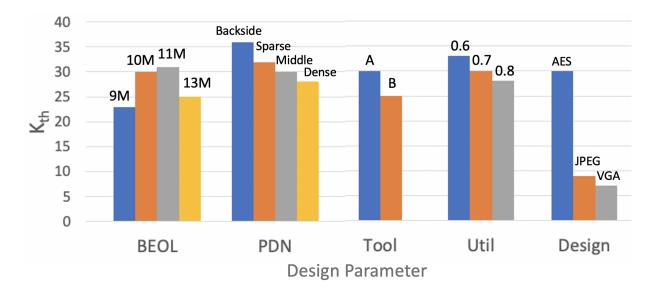

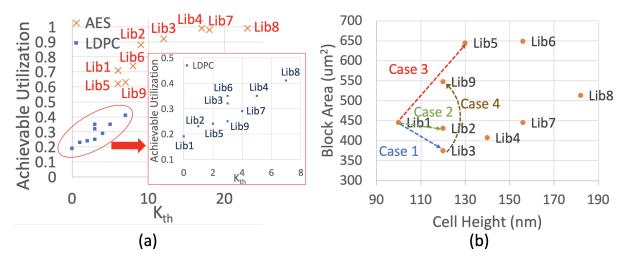

| Figure 4.14. | Comparison between $K_{th}$ and <i>achievable utilization</i> for the AES and LDPC designs.                                                                                                                                                                                                                              | 130 |

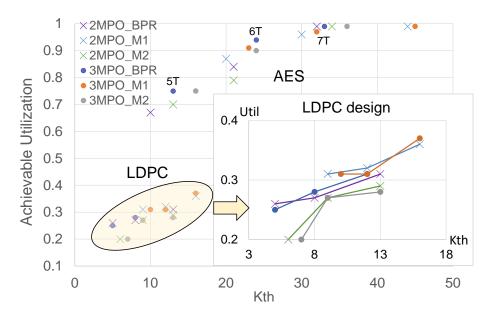

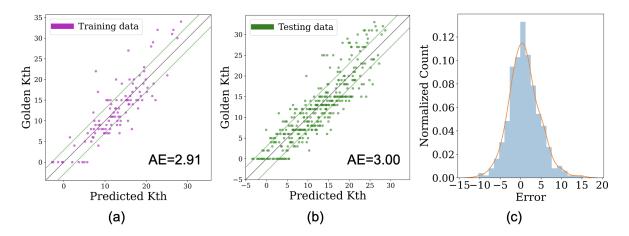

| Figure 4.15. | Comparison between golden $K_{th}$ and predicted $K_{th}$ and extracted feature importance; (a) training data, (b) testing data, (c) error distribution on testing data with kernel density estimation (KDE) plot and (d) extracted feature importance.                                                                  | 134 |

| Figure 4.16. | (a) Overall flow of PROBE2.0 [24] and (b) machine learning-based $K_{th}$ prediction.                                                                                                                                                                                                                                    | 137 |

| Figure 4.17. | An example of neighbor-swap operation. The blue-colored cell is swapped with one of the red-colored neighboring cells.                                                                                                                                                                                                   | 138 |

| Figure 4.18. | Standard-cell layout of the nine libraries in Table 4.16. OAI21_X1 of Lib1 to Lib9 are illustrated in (a) to (i), respectively. We show a LEF view (cell boundary and pin) of layout of OAI21_X1 per library                                                                                                             | 139 |

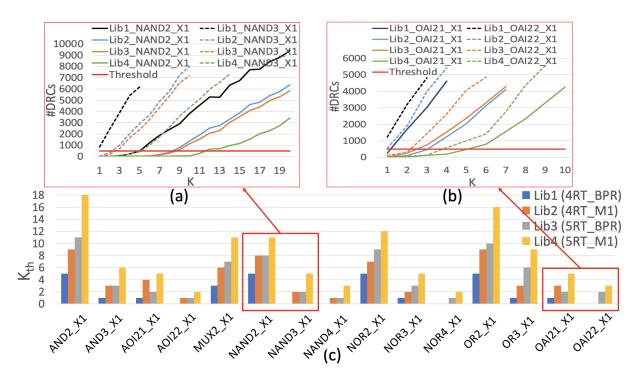

| Figure 4.19. | Results for cell-level routability assessments. (a) #DRC vs. $K_{th}$ plot for NAND2_X1 and NAND3_X1. (b) #DRC vs. $K_{th}$ plot for OAI21_X1 and OAI22_X1. (c) $K_{th}$ values for 15 cell types per four standard-cell libraries.                                                                                      | 140 |

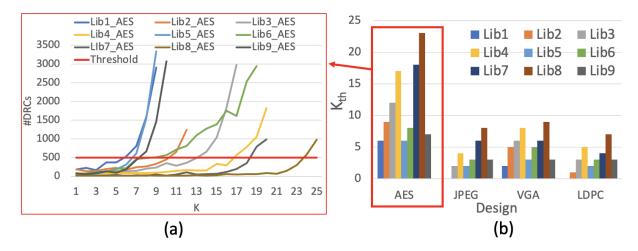

| Figure 4.20. | Design-level routability assessment for the nine standard-cell libraries. (a) #DRC vs. $K_{th}$ plot for AES design. (b) $K_{th}$ values for AES, JPEG and VGA designs. We use 0.6 Util for AES, JPEG and VGA and 0.15 Util for LDPC design.                                                                             | 141 |

| Figure 4.21. | Achievable density and block-area case study. (a) Plot for $K_{th}$ vs. achiev-<br>able utilization for AES and LDPC designs. (b) Achievable block-area<br>study with the nine libraries and AES design. The arrows show block-level<br>area and cell height differences in the case study, as also shown in Table 4.17. | 141 |

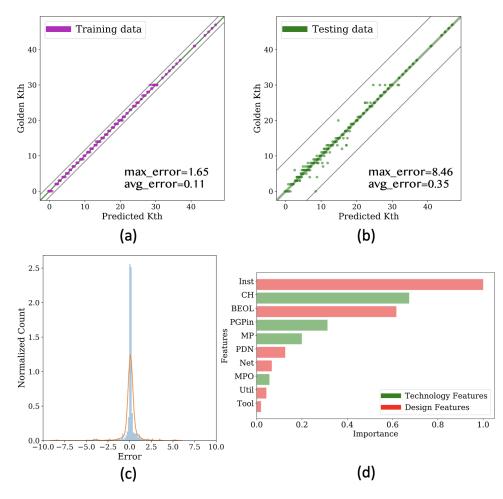

| Figure 4.22. | Comparison between golden $K_{th}$ and predicted $K_{th}$ . (a) Results for 128 training data sampled by LHS. (b) Results for 320 testing data. (c) Error distribution on the testing dataset with kernel density estimation (KDE) plot.                                                                                 | 143 |

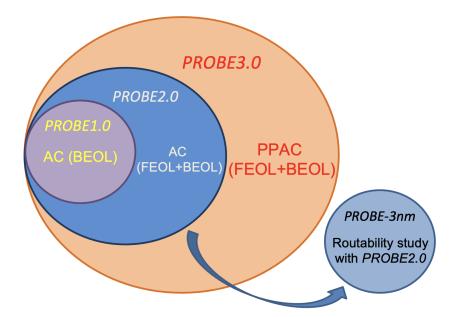

| Figure 4.23. | Scope of PROBE. <i>PROBE1.0</i> [64] and <i>PROBE2.0</i> [24] (Section 4.1 of this thesis) address AC given BEOL and FEOL/BEOL, respectively. <i>PROBE-3nm</i> [27] (Section 4.2 of this thesis) studies routability with sub-3nm configurations. PROBE3.0 provides true full-stack PPAC pathfinding         | 146 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.24. | Automatic standard-cell library and PDK generation ( <i>Design Enablement</i> ) in the PROBE3.0 framework. In addition to technology and design parameters in the PROBE3.0 framework, other technology-related inputs are required.                                                                          | 149 |

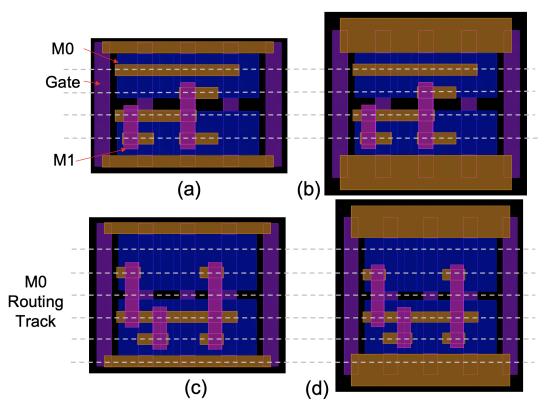

| Figure 4.25. | Example standard cells (AND2_X1). The cells are generated by our standard-cell layout generation with the following parameters (Fin, RT, PGpin, CH): (a) <i>Lib1</i> (2Fin, 4RT, BPR, 5T), (b) <i>Lib2</i> (2Fin, 4RT, M0, 6T), (c) <i>Lib3</i> (3Fin, 5RT, BPR, 6T) and (d) <i>Lib4</i> (3Fin, 5RT, M0, 7T) | 153 |

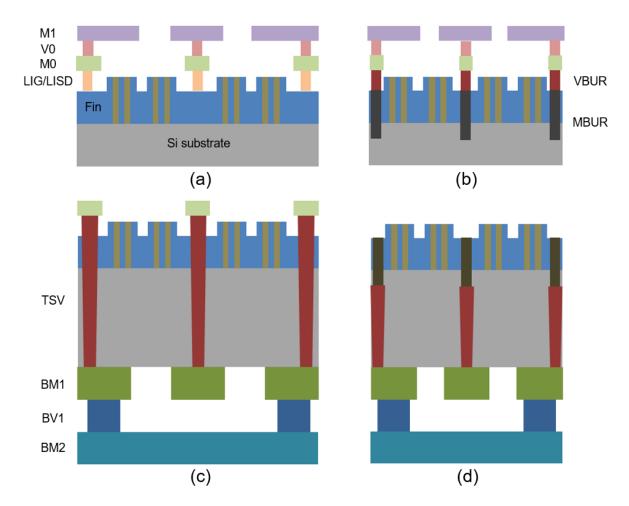

| Figure 4.26. | Cross-section view of four PDN options in the PROBE3.0 framework: (a) Frontside PDN ( $P_{FS}$ ), (b) Frontside PDN with BPR ( $P_{FB}$ ), (c) Backside PDN ( $P_{BS}$ ) and (d) Backside PDN with BPR ( $P_{BB}$ )                                                                                          | 155 |

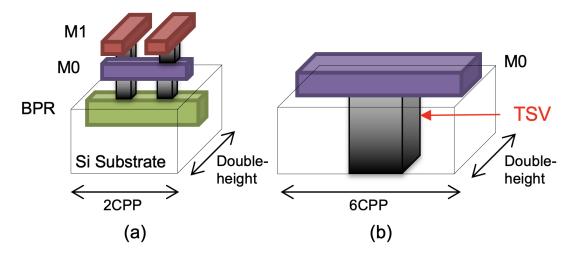

| Figure 4.27. | Power tap cells for (a) $P_{FB}$ and (b) $P_{BS}$                                                                                                                                                                                                                                                            | 157 |

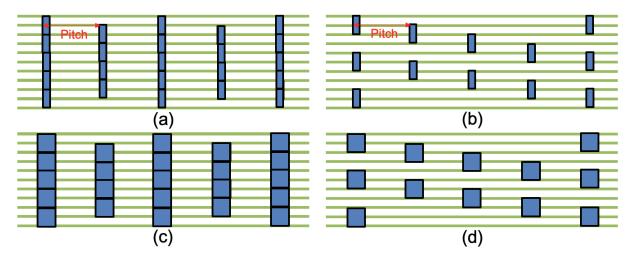

| Figure 4.28. | Four power tap cell insertion results: (a) Power tap cells for $P_{FB}$ (2CPP width) with <i>Column</i> ; (b) power tap cells for $P_{FB}$ with <i>Staggered</i> ; (c) power tap cells for $P_{BS}$ (6CPP width) with <i>Column</i> ; and (d) power tap cells for $P_{BS}$ with <i>Staggered</i> .           | 158 |

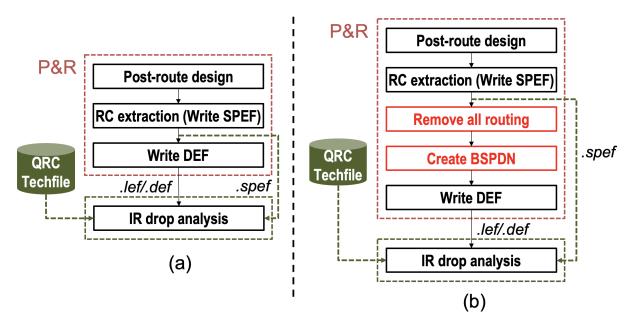

| Figure 4.29. | IR drop analysis flow for (a) FSPDN and (b) BSPDN. For the IR drop flow for BSPDN, we delete all the signal and clock routing after P&R and build power stripes for BSPDN.                                                                                                                                   | 159 |

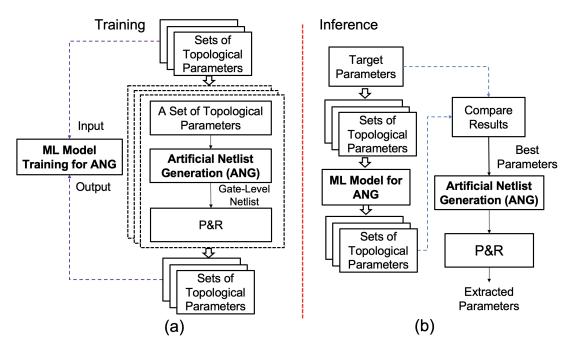

| Figure 4.30. | ML-based parameter tuning for ANG.                                                                                                                                                                                                                                                                           | 165 |

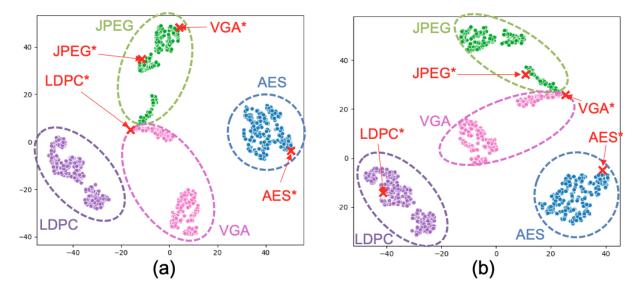

| Figure 4.31. | Comparison between real and artificial designs by t-SNE [91]. (a) t-SNE visualization for real and artificial (ANG, design names followed by *) designs <b>without</b> our parameter tuning flow. (b) Real and artificial (ANG) designs <b>with</b> our ML-based parameter tuning flow.                      | 166 |

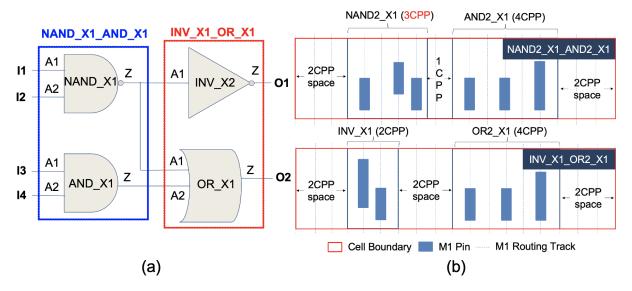

| Figure 4.32. | Two example clustered cells NAND_X1_AND_X1 and INV_X1_OR_X1, in clustering-based cell width-regularization. (a) Schematic view, and (b) physical layout view assuming <i>Lib2</i> . Here, the maximum clustered cell width $w_{max}$ is 12CPP.                                                               | 167 |

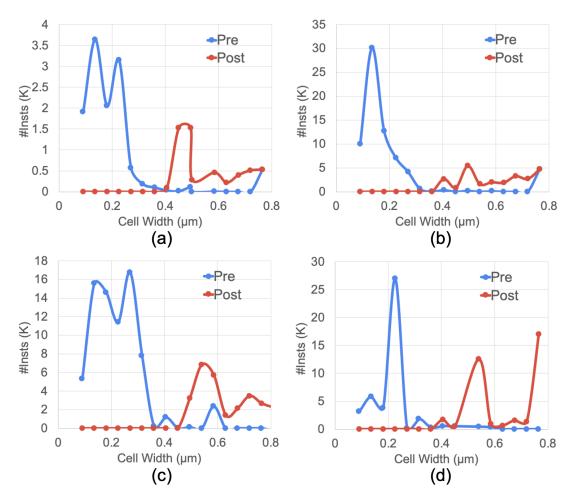

| Figure 4.33. | Cell width distributions pre-clustering (i.e., original netlist) and post-<br>clustering (i.e., by <i>CWR-FC</i> ) for (a) AES, (b) JPEG, (c) LDPC and (d) VGA.                                                                                                                                              | 170 |

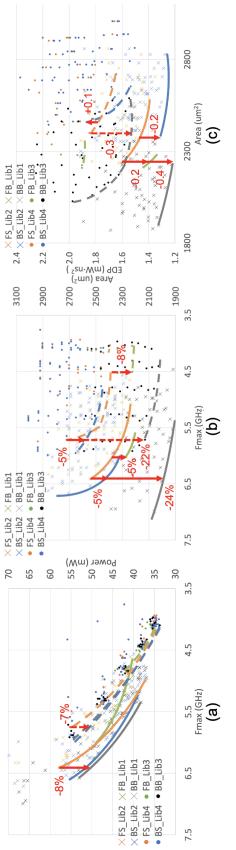

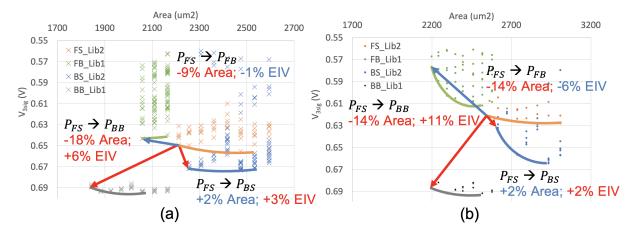

| Figure 4.34. | PPAC tradeoffs for JPEG with four standard-cell libraries ( <i>Lib1-4</i> ) and four<br>PDN structures. We measure improvements relative to traditional PDN<br>( $P_{FS}$ ), to show the benefits of BSPDN and BPR: (a) <i>Performance-Power</i> ,<br>(b) <i>Performance-Area</i> and (c) <i>Energy-Delay Product-Area</i> | 177 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

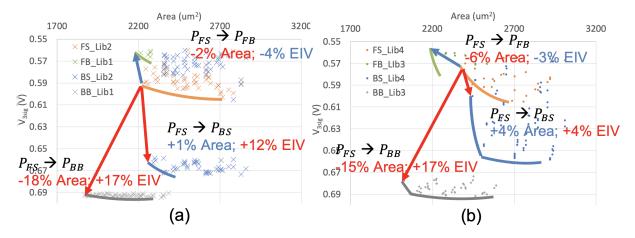

| Figure 4.35. | <i>IR drop-Area</i> plots for JPEG with four standard-cell libraries ( <i>Lib1</i> , <i>Lib2</i> , <i>Lib3</i> and <i>Lib4</i> ). (a) JPEG with 4RT ( <i>Lib1/2</i> ). (b) JPEG with 5RT ( <i>Lib3/4</i> ).                                                                                                                | 178 |

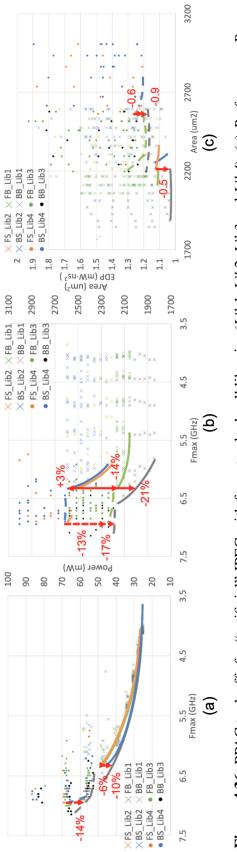

| Figure 4.36. | PPAC tradeoffs for "artificial" JPEG with four standard-cell libraries ( <i>Lib1</i> , <i>Lib2</i> , <i>Lib3</i> and <i>Lib4</i> ). (a) <i>Performance-Power</i> . (b) <i>Performance-Area</i> . (c) <i>Energy-Delay Product-Area</i> .                                                                                    | 180 |

| Figure 4.37. | <i>IR drop-Area</i> plots for "artificial" JPEG with four standard-cell libraries ( <i>Lib1</i> , <i>Lib2</i> , <i>Lib3</i> and <i>Lib4</i> ). (a) JPEG with 4RT ( <i>Lib1/2</i> ). (b) JPEG with 5RT ( <i>Lib3/4</i> ).                                                                                                   | 181 |

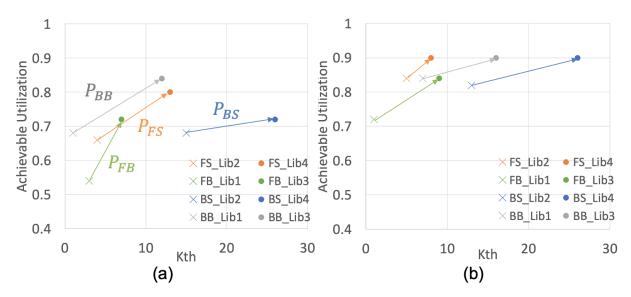

| Figure 4.38. | $K_{th}$ and achievable utilization for (a) AES and (b) JPEG, with various libraries and power delivery methodologies                                                                                                                                                                                                      | 182 |

#### LIST OF TABLES

| Table 2.1. | Notations                                                                                                                                                                                                                                                                                    | 16 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.2. | Average ILP runtime when $\alpha = 1, \beta = 0.5, L = M - B$ . <i>M</i> denotes the maximum distance between source and sink                                                                                                                                                                | 33 |

| Table 2.3. | ILP runtime for fixed and flexible clock source locations in Figure 2.4 and non-uniform grids. We set variables $\alpha = 1, \beta = 0.5, L = M - B$ . <i>M</i> denotes the maximum distance between source and sink                                                                         | 34 |

| Table 2.4. | Notations for the proposed <i>CoRe-ECO</i> framework                                                                                                                                                                                                                                         | 38 |

| Table 2.5. | Standard-cell architectures                                                                                                                                                                                                                                                                  | 49 |

| Table 2.6. | Experimental statistics. RT = the number of routing tracks, DRSet = Design rule set, Impr./Incr. = Improvement/Increment ratio over ECO routing, #V/#H/#F/#P = the number of refined instances by vertical shift-ing/horizontal shifting/horizontal flipping/pinlength extension             | 50 |

| Table 2.7. | Detailed experimental results of the proposed ECO flow (AES, 4T, ET, MPO2, 74 DRCs).                                                                                                                                                                                                         | 54 |

| Table 3.1. | Preliminary study of the 2 <sup>nd</sup> DB effect. Design nomenclature specifies design name (AES or VGA), filler insertion strategy (Small ( <i>sm</i> ) or Standard ( <i>std</i> )), and design type ( <i>Type-I</i> or <i>Type-II</i> ). WS denotes the worst slack of a design.         | 63 |

| Table 3.2. | Notations                                                                                                                                                                                                                                                                                    | 68 |

| Table 3.3. | Experimental results for all the design blocks.                                                                                                                                                                                                                                              | 71 |

| Table 3.4. | Experimental results for design space exploration. We use AES Type-II design with 60% initial utilization and 0.5ns target clock period                                                                                                                                                      | 75 |

| Table 3.5. | Experimental results for sensitivity to the tolerance. The $2^{nd}$ DB-aware leak-<br>age power of the design is 0.190mW. Reloc., $1^{st}$ loop and $2^{nd}$ loop denote<br>runtime of the relocation step, and of the first and the second iterations of<br>the optimization, respectively. | 77 |

| Table 3.6. | Notations                                                                                                                                                                                                                                                                                    | 80 |

| Table 3.7. | Design information                                                                                                                                                                                                                                                                           | 88 |

| Table 3.8.  | Total #staples placed when we apply two rounds of optimization with total displacement range $(x_{\Delta}) = 6$ . Each row represents design AES with utilization between 0.60 and 0.75.                                                                                                                                     | 90  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.9.  | IR drop vs. staple length.                                                                                                                                                                                                                                                                                                   | 91  |

| 14010 3.9.  |                                                                                                                                                                                                                                                                                                                              | 91  |

| Table 3.10. | Experimental results using double-row optimization.                                                                                                                                                                                                                                                                          | 93  |

| Table 4.1.  | Standard-cell architectures in our experiments.                                                                                                                                                                                                                                                                              | 109 |

| Table 4.2.  | Four BEOL stack options. <i>R</i> denotes <i>routing resource</i>                                                                                                                                                                                                                                                            | 111 |

| Table 4.3.  | Details of PDN options. All numbers are pitches in units of $\mu m$ for each layer. " <i>P</i> " indicates that we use a given layer only for PDN at maximum area density, and do not allow the layer to be used for signal routing. The width of M5 stripes is $0.96\mu m$ and the width of M6/M8 stripes is $1.296\mu m$ . | 111 |

| Table 4.4.  | Technology and design parameters in our experiments.                                                                                                                                                                                                                                                                         | 112 |

| Table 4.5.  | Placed design information for AES, mesh-like placements and knight's tour based topologies. Mesh-like placements and knight's tours have $115 \times 115$ placed instances. Area denotes total instance area in the designs. Area is in units of $\mu m^2$ and wirelength (WL) is in units of $\mu m$ .                      | 118 |

| Table 4.6.  | Rent parameters for mesh-like and knight's tour-based placed netlists. We use <i>rectangle sampling-based methods I and II</i> for the evaluation method, <i>Types I and II</i> for the pin counting method, and <i>geometric mean</i> for the averaging method in [165]                                                     | 119 |

| Table 4.7.  | Input features of the $K_{th}$ prediction                                                                                                                                                                                                                                                                                    | 121 |

| Table 4.8.  | Default parameters in our experiments                                                                                                                                                                                                                                                                                        | 122 |

| Table 4.9.  | List of 39 standard cells per generated library                                                                                                                                                                                                                                                                              | 123 |

| Table 4.10. | $K_{th}$ results with RPA-Best and RPA-Worst pin shape selection methods. This table shows the $K_{th}$ values corresponding to the data shown in Figure 4.11.                                                                                                                                                               | 126 |

| Table 4.11. | $K_{th}$ results with various Fin, MP, RT, PGpin and MPO                                                                                                                                                                                                                                                                     | 128 |

| Table 4.12. | Results on training data of Top-5 ML models by using AutoML. The three <i>GBM</i> models ( <i>GBM_1</i> , <i>GBM_2</i> and <i>GBM_3</i> ) have different configurations for hyperparameters. The training runtime is limited to one hour with 80 CPU threads.                                                                | 132 |

| Table 4.13. | Results of DL modeling with AutoML. $DL_1h$ (resp. $DL_24h$ ) denotes a DL model with a 1-hour (resp. 24-hour) runtime limit for training                                                                                                                                                                                                       | 132 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 4.14. | Model accuracy results with different amounts of training data ( <i>TD</i> ), i.e., 20, 40, 60 and 80% of the total data (2460 $K_{th}$ values), with a one-hour limit and 80 threads. Testing data are fixed for an apples-to-apples comparison. <i>ME</i> and <i>AE</i> respectively denote maximum and average error of $K_{th}$ prediction. | 132 |

| Table 4.15. | Technology and design parameters in this work. We use all the parameter types defined in [24]                                                                                                                                                                                                                                                   | 138 |

| Table 4.16. | Technology parameters for the nine standard-cell libraries which we study in this work.                                                                                                                                                                                                                                                         | 139 |

| Table 4.17. | Results for achievable block-level area case study, expressed as overhead of <i>Lib B</i> relative to <i>Lib A</i> , i.e., $(Area_B - Area_A)/Area_A \times 100\%$                                                                                                                                                                              | 142 |

| Table 4.18. | Layer definition in the PROBE3.0 technology.                                                                                                                                                                                                                                                                                                    | 150 |

| Table 4.19. | Key features of the PROBE3.0 technology.                                                                                                                                                                                                                                                                                                        | 151 |

| Table 4.20. | List of 41 standard cells per generated library                                                                                                                                                                                                                                                                                                 | 152 |

| Table 4.21. | PDN configurations for FSPDN and BSPDN. A pair of power (VDD) and ground (VSS) stripes are placed every pitch, while maintaining the spacing between VDD and VSS. <i>Density</i> denotes the percentage of routing tracks occupied by PDN.                                                                                                      | 156 |

| Table 4.22. | Definition of topological parameters in ANG [78] [140]                                                                                                                                                                                                                                                                                          | 160 |

| Table 4.23. | Topological parameters for real netlists from OpenCores [161] and artificial netlists generated by [78]. Design names followed by * indicate ANG-generated artificial netlists.                                                                                                                                                                 | 161 |

| Table 4.24. | Parameter sets for training and testing. We train our ML model with ANG input parameters and post-P&R output parameters. The total number of datapoints is $4 \times 6 \times 6 \times 5 \times 5 \times 6 = 21600$ . Testing is performed in the ranges around given target parameters, according to the step sizes                            | 163 |

| Table 4.25. | Topological parameters for target, input and output netlists. The design<br>names followed by ** indicate ANG-generated artificial netlists with ML-<br>based ANG parameter tuning.                                                                                                                                                             | 164 |

| Table 4.26. | Comparison of the width-regularized clustered netlist produced by <i>CWR-FC</i> ([C]) with the original flat netlist ([A]) and a width-regularized clustered netlist induced from a placement of the flat netlist ([B]).                                                                                                                        | 172 |

| Table 4.27. | Technology and design parameters in our experiments                                                                                                                                                                                       | 174 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 4.28. | Tools and versions in our experiments.                                                                                                                                                                                                    | 175 |

| Table 4.29. | <i>K<sub>th</sub></i> comparison for the JPEG design with <i>cell width-regularized placements</i> ([A]) and <i>clustering-based cell width-regularized placements</i> ([C]). Util denotes real utilization with 0.6 initial utilization. | 183 |

#### ACKNOWLEDGMENTS

I would like to express my gratitude to my advisor, Professor Andrew B. Kahng, for serving as the chair of my committee and providing invaluable guidance throughout my Ph.D. journey.

I also want to thank my fellow labmates at the UCSD VLSI CAD Laboratory, including Nikhil Dakwala, Sayak Kundu, Jiantao Liu, Bodhisatta Pramanik, Ravi Varadarajan, Zhiang Wang, Mingyu Woo, Chien-Yi Yang and Dooseok Yoon, as well as former lab members, including Payal Agarwal, Dr. Wei-Ting (Jonas) Chan, Dr. Ahmed Taha Elthakeb, Dr. Kwangsoo Han, Dr. Chia-Tung (Mark) Ho, Dr. Seungwon Kim, Dr. Hyein Lee, Hsin-Yu (Desmond) Liu, Dr. Uday Mallappa, Tushar Shah, Siddharth Singh, Dr. Vaishnav Srinivas, Sriram Venkatesh, Dr. Lutong Wang and Dr. Bangqi Xu, for their assistance and thought-provoking discussions. Special thanks go to Dr. Tuck-Boon Chan, Dr. Ilgweon Kang, Dr. Daeyeal Lee, Dr. Jiajia Li and Dr. Dongwon Park for their guidance during my Ph.D. studies.

I am also grateful to my thesis committee members, Professor Chung-Kuan Cheng, Professor Sujit Dey and Professor Farinaz Koushanfar, for their time, encouragement and insightful comments.

I would like to acknowledge the invaluable feedback and support of my industrial collaborators, including Suhyeong Choi, Dr. Hamed Fatemi, Dr. Jose Pineda de Gyvez, Sunik Heo, Dr. Jinwook Jung, Chunghee Kim, Hayoung Kim, Dr. Jaehwan Kim, Dr. Gi-Joon Nam and Dr. S. C. Song.

I extend my gratitude to my old fellows from South Korea, Jinhwan Choi, Sangha Chung, Sangyeop Kim, Youngmin Kim, Seungheon Lee and Byeong-Geun Sun, as well as my beloved companions, Hyunwoo Baek, Woojae Park, Eunjae Shin and Sooyoung Son.

Finally, I would like to express my heartfelt appreciation to my parents, Hongjin Kim and Jungsuk Kang, my mother-in-law, Nankyung Kim, and the rest of my family for their endless love and encouragement. I owe a special debt of gratitude to my wife, Youri Jeong, whose unwavering love and support enabled me to complete this journey, and my lovely daughters, Joy and Skylar, who gave me the strength I needed every day with their love. This thesis is dedicated to my family.

The material in this thesis is based on the following publications.

Chapter 2 contains a reprint of Hamed Fatemi, Andrew B. Kahng, Minsoo Kim and Jose Pineda de Gyvez, "Optimal Bounded-Skew Steiner Trees to Minimize Maximum k-Active Dynamic Power", *Proc. International Workshop on System-Level Interconnect Problems and Pathfinding*, 2020; and Chung-Kuan Cheng, Andrew B. Kahng, Ilgweon Kang, Minsoo Kim, Daeyeal Lee, Bill Lin, Dongwon Park and Mingyu Woo, "CoRe-ECO: Concurrent Refinement of Detailed Place-and-Route for an Efficient ECO Automation", *Proc. IEEE International Conference on Computer Design*, 2021. The dissertation author is a main contributor to, and a primary author of, each of these papers.

Chapter 3 contains a reprint of Sunik Heo, Andrew B. Kahng, Minsoo Kim and Lutong Wang, "Diffusion Break-Aware Leakage Power Optimization and Detailed Placement in Sub-10nm VLSI", *Proc. Asia and South Pacific Design Automation Conference*, 2019; and Sunik Heo, Andrew B. Kahng, Minsoo Kim and Lutong Wang and Chutong Yang, "Detailed Placement for IR Drop Mitigation by Power Staple Insertion in Sub-10nm VLSI", *Proc. Design, Automation and Test in Europe*, 2019. The dissertation author is a main contributor to, and a primary author of, each of these papers.

Chapter 4 contains a reprint of Chung-Kuan Cheng, Andrew B. Kahng, Hayoung Kim, Minsoo Kim, Daeyeal Lee, Dongwon Park and Mingyu Woo, "PROBE2.0: A Systematic Framework for Routability Assessment from Technology to Design in Advanced Nodes", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and System* 41(5), 2022; Chidi Chidambaram, Andrew B. Kahng, Minsoo Kim, Giri Nallapati, S. C. Song and Mingyu Woo, "A Novel Framework for DTCO: Fast and Automatic Routability Assessment with Machine Learning for Sub-3nm Technology Options", Proc. IEEE Symposium on VLSI Technology, 2021; and Suhyeong Choi, Jinwook Jung, Andrew B. Kahng, Minsoo Kim, Chul-Hong Park, Bodhisatta Pramanik and Dooseok Yoon, "PROBE3.0: A Systematic Framework for DesignTechnology Pathfinding with Improved Design Enablement", in submission to *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 2023. The dissertation author is a main contributor to, and a primary author of, each of these papers.

All co-authors, listed in alphabetical order, including Professor Chung-Kuan Cheng, Dr. Chidi Chidambaram, Suhyeong Choi, Dr. Hamed Fatemi, Sunik Heo, Dr. Jinwook Jung, Professor Andrew B. Kahng, Dr. Ilgweon Kang, Hayoung Kim, Dr. Daeyeal Lee, Professor Bill Lin, Dr. Giri Nallapati, Dr. Chul-Hong Park, Dr. Dongwon Park, Dr. Jose Pineda de Gyvez, Bodhisatta Pramanik, Dr. S. C. Song, Dr. Lutong Wang, Mingyu Woo, Chutong Yang and Dooseok Yoon, have kindly approved the inclusion of the aforementioned publications in my thesis.

#### VITA

| 2011      | B. S., Electrical Engineering,<br>Yonsei University, Seoul, South Korea                                    |

|-----------|------------------------------------------------------------------------------------------------------------|

| 2013      | M. S., Electrical Engineering,<br>Korea Advanced Institute of Science and Technology, Daejeon, South Korea |

| 2013-2017 | Engineer, Samsung Electronics, Gyeonggi-do, South Korea                                                    |

| 2021      | C. Phil., Electrical Engineering (Computer Engineering),<br>University of California San Diego             |

| 2023      | Ph. D., Electrical Engineering (Computer Engineering),<br>University of California San Diego               |

All papers coauthored with my advisor Professor Andrew B. Kahng have authors listed in alphabetical order.

#### PUBLICATIONS

Suhyeong Choi, Jinwook Jung, Andrew B. Kahng, **Minsoo Kim**, Chul-Hong Park, Bodhisatta Pramanik and Dooseok Yoon, "PROBE3.0: A Systematic Framework for Design-Technology Pathfinding with Improved Design Enablement", in submission to *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*.

Chia-Tung Ho, Alvin Ho, Matthew Fojtik, **Minsoo Kim**, Shang Wei, Yaguang Li, Brucek Khailany and Haoxing Ren, "NVCell 2: Routability-Driven Standard Cell Layout in Advanced Nodes with Lattice Graph Routability Model", *Proc. International Symposium on Physical Design*, 2023, pp. 44-52.

Chung-Kuan Cheng, Andrew B. Kahng, Ilgweon Kang, **Minsoo Kim**, Daeyeal Lee, Bill Lin, Dongwon Park and Mingyu Woo, "PROBE2.0: A Systematic Framework for Routability Assessment from Technology to Design in Advanced Nodes", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and System* 41(5) (2022), pp. 1495-1508.

Andrew B. Kahng, **Minsoo Kim**, Seungwon Kim and Mingyu Woo, "RosettaStone: Connecting the Past, Present and Future of Physical Design Research", *IEEE Design & Test* 39(5) (2022), pp. 70-78.

Chung-Kuan Cheng, Andrew B. Kahng, Ilgweon Kang, **Minsoo Kim**, Daeyeal Lee, Bill Lin, Dongwon Park and Mingyu Woo, "CoRe-ECO: Concurrent Refinement of Detailed Place-and-Route for an Efficient ECO Automation", *Proc. IEEE International Conference on Computer Design*, 2021, pp. 366-373.

Chidi Chidambaram, Andrew B. Kahng, **Minsoo Kim**, Giri Nallapati, S. C. Song and Mingyu Woo, "A Novel Framework for DTCO: Fast and Automatic Routability Assessment with Machine Learning for Sub-3nm Technology Options", *Proc. IEEE Symposium on VLSI Technology*, 2021, pp. 1-2.

Hamed Fatemi, Andrew B. Kahng, **Minsoo Kim** and Jose Pineda de Gyvez, "Optimal Bounded-Skew Steiner Trees to Minimize Maximum k-Active Dynamic Power", *Proc. ACM/IEEE International Workshop on System-Level Interconnect Problems and Pathfinding*, 2020, pp. 1-8.

Austin Rovinski, Tutu Ajayi, **Minsoo Kim**, Guanru Wang and Mehdi Saligane, "Bridging Academic Open-Source EDA to Real World Usability", *Proc. IEEE/ACM International Conference on Computer-Aided Design*, 2020, pp. 1-7.

Vidya A. Chhabria, Andrew B. Kahng, **Minsoo Kim**, Uday Mallappa, Sachin S. Sapatnekar and Bangqi Xu, "Template-based PDN Synthesis in Floorplan and Placement Using Classifier and CNN Techniques", *Proc. Asia and South Pacific Design Automation Conference*, 2020, pp. 44-49.

Tutu Ajayi, Vidya A. Chhabria, Mateus Fogaça, Soheil Hashemi, Abdelrahman Hosny, Andrew B. Kahng, **Minsoo Kim**, Jeongsup Lee, Uday Mallappa, Marina Neseem, Geraldo Pradipta, Sherief Reda, Mehdi Saligane, Sachin S. Sapatnekar, Carl Sechen, Mohamed Shalan, William Swartz, Lutong Wang, Zhehong Wang, Mingyu Woo and Bangqi Xu, "Toward an Open-Source Digital Flow: First Learnings from the OpenROAD Project", *Proc. ACM/IEEE Design Automation Conference*, 2019, pp. 76:1-76:4.

Tutu Ajayi, David Blaauw, Tuck-Boon Chan, Chung-Kuan Cheng, Vidya A. Chhabria, David K. Choo, Matteo Coltella, Sorin Dobre, Ronald Dreslinski, Mateus Fogaça, Soheil Hashemi, Abdelrahman Hosny, Andrew B. Kahng, **Minsoo Kim**, Jiajia Li, Zhaoxin Liang, Uday Mallappa, Paul Penzes, Geraldo Pradipta, Sherief Reda, Austin Rovinski, Kambiz Samadi, Sachin S. Sapatnekar, Lawrence Saul, Carl Sechen, Vaishnav Srinivas, William Swartz, Dennis Sylvester, David Urquhart, Lutong Wang, Mingyu Woo and Bangqi Xu, "OpenROAD: Toward a Self- Driving, Open-Source Digital Layout Implementation Tool Chain", *Proc. Government Microcircuit Applications and Critical Technology Conference*, 2019, pp. 1105-1110.

Sunik Heo, Andrew B. Kahng, **Minsoo Kim**, Lutong Wang and Chutong Yang, "Detailed Placement for IR Drop Mitigation by Power Staple Insertion in Sub-10nm VLSI", *Proc. Design, Automation & Test in Europe Conference & Exhibition*, 2019, pp. 824-829.

Sunik Heo, Andrew B. Kahng, **Minsoo Kim** and Lutong Wang, "Diffusion Break-Aware Leakage Power Optimization and Detailed Placement in Sub-10nm VLSI", *Proc. Asia and South Pacific Design Automation Conference*, 2019, pp. 550-556.

**Minsoo Kim**, Chong-Min Kyung and Kang Yi, "An Energy Management Scheme for Solar-Powered Wireless Visual Sensor Networks Toward Uninterrupted Operations", *Proc. IEEE International SoC Design Conference*, 2013, pp. 23-26.

#### ABSTRACT OF THE DISSERTATION

#### Robust Physical Design and Design Technology Co-Optimization Methodologies at Advanced VLSI Technology

by

#### Minsoo Kim

Doctor of Philosophy in Electrical Engineering (Computer Engineering)

University of California San Diego, 2023

Professor Andrew B. Kahng, Chair

The semiconductor industry has achieved remarkable progress by adhering to Moore's Law in the past few decades. As a result, technology has continuously scaled down and advanced to the 2nm and 3nm nodes by 2023. The consistent scaling of advanced technologies has made it possible to utilize them in various applications of modern IC designs, such as mobile, data center, automotive, graphics, the Internet of Things (IoT) and artificial intelligence (AI), which may demand high performance and/or ultra-low power consumption. However, the recent slowdown in the traditional Moore's Law scaling rate has presented significant challenges. Therefore, considerable efforts have been devoted to physical design and design-technology co-optimization

to optimize the advantages of advanced technology nodes for different applications.

This thesis presents robust physical design and design-technology co-optimization methodologies that aim to maximize the benefits of advanced technologies and optimize power, performance, area and cost in modern IC design. The proposed methodologies are categorized into three main directions: (i) general physical design methodologies, (ii) technology-aware physical design methodologies and (iii) design-technology co-optimization methodologies.

To address challenges in modern IC design, this thesis presents two works: (i) boundedskew Steiner tree optimization for clock tree synthesis to minimize active power and (ii) concurrent refinement of detailed place-and-route (P&R) for efficient engineering change order (ECO) automation.

To address challenges specific to advanced technology nodes, this thesis presents two works: (i) leakage power optimization with the awareness of local layout effects and (ii) detailed placement for IR drop mitigation by power staple insertions.

Finally, to address challenges in design-technology co-optimization at advanced technology nodes, this thesis presents three works: (i) PROBE2.0: A systematic framework for routability assessments, (ii) a routability study using the PROBE2.0 framework with 3nm technology configurations and (iii) PROBE3.0: A systematic framework for power, performance, area and cost explorations, with improved design enablement.

# Chapter 1 Introduction

In the last several decades, the semiconductor industry has successfully followed Moore's Law as a guide for the long-term planning of advanced technology development. As a result, semiconductor technologies have consistently scaled down to the 2nm and 3nm nodes, with the number of transistors in a single chip now exceeding tens of billions due to aggressive transistor density scaling. These advanced technologies bring various capabilities to applications, including mobile, data center, automotive, graphics, the Internet of Things (IoT) and artificial intelligence, with significantly improved performance and/or reduced power consumption.

## **1.1 New Challenges**

Despite the semiconductor industry's past success, the trend of Moore's Law scaling has recently slowed down. Figure 1.1 illustrates this slowdown, where the fin pitch, contacted poly pitch (CPP) and standard-cell height scaling rates have flattened over time. Consequently, the slowdown has presented numerous challenges across many applications, and both the semiconductor industry and academia have made significant efforts to mitigate the slowdown and address the challenges posed by various applications and advanced technology nodes.

#### 1.1.1 Challenges for Modern IC Design

In modern Integrated Circuit (IC) designs, various applications target different power and performance levels. Figure 1.2 illustrates the major applications in modern IC design and

**Figure 1.1.** The scaling rates of fin pitch, contacted poly pitch (CPP) and standard-cell height have slowed down over time, and device architectures have also evolved from fin field-effect transistor (FinFET) to complementary field-effect transistor (CFET) [104].

their general power and performance requirements. High-performance computing demands high performance with high power consumption, while IoT aims to achieve long operational lifetimes with ultra-low power consumption. Across these applications, the ultimate goal of modern IC design is to optimize power, performance, area and cost (PPAC) within a reasonable turnaround time. However, as the target PPAC is dependent on the application and design, optimizing for various applications can be challenging in modern IC design.

Aggressive PPAC optimizations introduce further challenges in modern IC design. One such challenge is the demand for aggressive power reduction. Although low power methodologies have enabled significant power reductions while maintaining or even improving performance, the recent demand for ultra-low power consumption in automotive, mobile and IoT applications comes with strict power constraints. Another challenge is the routability problem and complex design rule check violations (DRC) caused by aggressive area reduction in physical design.

Figure 1.2. Power and performance requirements for applications [89].

The complexity of design rules and constraints in advanced nodes exacerbates this problem, necessitating additional human engineering resources to address the problem.

#### 1.1.2 Challenges for Advanced Technology Nodes

As technology advances, aggressive scaling of critical dimensions and pitches poses new challenges in placement, clock tree synthesis, routing and timing analysis. One of these challenges arises due to the increasing impact of layout-dependent device parameter shifts. This local layout effect (LLE) becomes more significant at advanced nodes due to aggressive scaling. LLE can cause power and performance variations in devices, resulting from standard-cell architectures and/or placement in physical design. For example, in standard cells, diffusion breaks isolate two neighboring devices. In advanced nodes, these breaks can have a stress effect on timing and leakage power. Figure 1.3(a) illustrates the saturation voltage and effective current shifts caused by LLE from the second diffusion break. Figure 1.3(b) shows the interlayer dielectric (ILD) stress in a TCAD simulation, which depends on the spacing between the first and second diffusion breaks.

**Figure 1.3.** Local layout effect [128]. (a) Saturation voltage and effective current shifts caused by the second diffusion break effect. (b) Interlayer dielectric (ILD) stress in a TCAD simulation, which is a function of the spacing between the first and the second diffusion breaks.

Another challenge is the high resistance of interconnects due to aggressive BEOL metal pitch scaling. Figure 1.4 illustrates the unit resistance of interconnects for recent technologies, where the 5nm technology has a 9X larger unit resistance for the lowest BEOL metal layers (Mx) compared to the 16nm technology. This leads to severe timing degradation from interconnects and voltage (IR) drop problems.

#### **1.1.3** Challenges for Design-Technology Co-Optimization

*Design-Technology Co-Optimization* (DTCO) is an optimization process that aims to maximize the benefits of advanced technology nodes by exploring most beneficial design and technology configurations. Fast and accurate PPAC explorations are key players in this process as they help to explore new transistor architectures, materials, standard-cell architectures and design knobs. In addition, *scaling boosters* are introduced at advanced technology nodes to maintain the traditional Moore's Law density scaling rate. These scaling boosters provide more design and technology configurations and broader solution spaces for the PPAC explorations. However, the exploration of these new technology options is becoming increasingly difficult and complicated, and requires thorough evaluations.

Today's DTCO methodologies face several limitations in advanced nodes. One of the

Figure 1.4. Resistance of BEOL metal layers (Mx) increases exponentially as technology advances [89].

major challenges is the limited exploration of the entire solution space due to a lack of human engineering resources. The process is not fully automated and requires significant manual efforts from human engineers, such as creating standard-cell layouts and process design kits (PDK). Another challenge is that the current ring oscillator-based PPAC explorations do not always match the results of real chips as they do not address all aspects of design, such as routability. Moreover, PPAC is design-dependent, and the results from ring oscillators cannot be applied to all types of designs. Finally, due to the competitive nature of the semiconductor industry, critical information related to advanced technologies remains under the proprietary domain of semiconductor companies, making it inaccessible to academia. As a result, academic researchers are unlikely to make significant innovations in DTCO research as they cannot conduct experiments with real values corresponding to modern IC technologies.

## **1.2** This Thesis

This thesis presents robust physical design and DTCO methodologies to tackle challenges posed by advanced technology nodes. The methodologies proposed in this thesis can be classified

Figure 1.5. Overview of this thesis.

into three main categories, as illustrated in Figure 1.5.

- General physical design methodologies.

- Technology-aware physical design methodologies.

- Design-technology co-optimization (DTCO) methodologies.

First, to address the challenges for modern IC design, the *general physical design methodologies* chapter of this thesis presents approaches to optimize bounded-skew Steiner trees for clock tree synthesis to minimize active power, and to concurrently refine detailed placement and routing for efficient engineering change orders (ECO) automation.

Second, to address the challenges for advanced technology nodes, the *technology-aware physical design methodologies* chapter of this thesis presents approaches to optimize leakage power with the awareness of local layout effects, and to mitigate IR drop by detailed placement that enables more power staples to be inserted.

Last, to address challenges for DTCO, the *design-technology co-optimization* chapter of this thesis presents a systematic framework for routability assessments, a routability study by

using the PROBE2.0 framework with 3nm technology configurations and a systematic framework for PPAC explorations with improved design enablements.

The reminder of this thesis is organized as follows.