# **UC Santa Barbara**

# **UC Santa Barbara Electronic Theses and Dissertations**

### **Title**

Efficient In-DRAM Near-Bank Processing for Emerging Parallel Computing Workloads

### **Permalink**

https://escholarship.org/uc/item/5xt5818s

### **Author**

Xie, Xinfeng

# **Publication Date**

2022

Peer reviewed|Thesis/dissertation

### University of California Santa Barbara

# Efficient In-DRAM Near-Bank Processing for Emerging Parallel Computing Workloads

A dissertation submitted in partial satisfaction of the requirements for the degree

$\begin{array}{c} {\rm Doctor~of~Philosophy} \\ {\rm in} \\ {\rm Electrical~and~Computer~Engineering} \end{array}$

by

Xinfeng Xie

### Committee in charge:

Professor Yuan Xie, Chair Professor Dmitri Strukov Professor Tim Sherwood Professor Yufei Ding

| The Dissertation of Xinfeng Xie is approved. |

|----------------------------------------------|

|                                              |

|                                              |

|                                              |

| Professor Dmitri Strukov                     |

|                                              |

|                                              |

| Professor Tim Sherwood                       |

|                                              |

|                                              |

| D . ( V ( : D:                               |

| Professor Yufei Ding                         |

|                                              |

|                                              |

| Professor Yuan Xie, Committee Chair          |

March 2022

Efficient In-DRAM Near-Bank Processing for Emerging Parallel Computing Workloads

Copyright © 2022

by

Xinfeng Xie

I am dedicating this dissertation to my parents, Jieli Fang and Boxuan Xie, for bringing me to this world and giving me their unconditional support and love throughout my life.

## Acknowledgements

I have received help from many people along my Ph.D. program. I would like to express my deepest gratitude to these kind people and their nice help. Without their generous help, it would be impossible for me to complete this dissertation.

First of all, I would like to thank my advisor, Prof. Yuan Xie. As my advisor, Prof. Yuan Xie is very supportive of my research and professional skill development. He leaves me the highest degree of freedom to select research topics and schedule project agendas, and he always encourages me to explore topics I am most interested in. Moreover, when I was frustrated with obstacles and difficulties, he always encourages me to insist on my research direction. In addition to my research projects, he also supports all of my decisions about industrial internships. These internship experiences deeply shape my research tastes and motivate me to focus more on real-world problems.

Second, I would like to thank all members of my Ph.D. committee, Prof. Dimitri Strukov, Prof. Tim Sherwood, and Prof. Yufei Ding, for their professional services. Especially, I would like to thank Prof. Yufei Ding for her suggestions and help to improve my research work in this dissertation.

Third, I would like to thank all of my labmates and collaborators, including but not limited to Dr. Lei Deng, Dr. Fengbin Tu, Dr. Jiayi Huang, Dr. Maohua Zhu, Dr. Abanti Basak, Alvin Glova, Liu Liu, Wenqin Huangfu, Nan Wu, Tianqi Tang, Gushu Li, Ling Liang, Bangyan Wang, Jilan Lin, Zheng Qu, Zhaodong Chen, Guyue Huang, and Anbang Wu. Working in a research lab of so many great researchers with diverse research directions, I learned a lot from them in a wide spectrum of research fields. Among all labmates and collaborators, I would like to especially thank Dr. Xing Hu and Dr. Peng Gu for their help to both my research projects and my personal life. Dr. Xing Hu is the senior researcher who helped me build fundamental skills in the early stage of my Ph.D.

program. She also helped me a lot when I was settling down in Santa Barbara. Dr. Peng Gu is my most important collaborator, who is the co-primary contributor to two projects in this dissertation. He taught me a lot about memory technology and hardware knowledge. Also, his hard-working and enthusiasm for research always motivate me to push myself forward in my research projects.

In addition to the help I received in my academic research projects, I also received a lot of help from industrial mentors in internships during my Ph.D. program. I would like to thank Dr. Andrea Di Blas, Dr. Qiuling Zhu, Dr. Yuchen Hao, Dr. Jianyu Huang, Dr. Peter Ma, and Dr. Yanqi Zhou for their great mentorship during my stays in Google and Facebook. I sincerely appreciate their efforts to help me build professional skills and help me set up a good starting point in my career path.

Last but not least, I am thankful to my friends and my family members for their continuous support and encouragement not only in this Ph.D. program but also in my whole life. Especially, I thank my parents, Jieli Fang and Boxuan Xie, for bringing me to this world and encouraging me to explore the beauty, art, and adventure of this journey.

# Curriculum Vitæ Xinfeng Xie

#### Education

| 2022 | Ph.D. in Electrical and Computer Engineering (Expected), University of California, Santa Barbara, United States. |

|------|------------------------------------------------------------------------------------------------------------------|

| 2020 | M.S. in Electrical and Computer Engineering, University of California, Santa Barbara, United States.             |

| 2017 | B.S. in Microelectronics Science and Engineering, Peking University, Beijing, China.                             |

#### **Publications**

- [C1] Pengfei Zuo, Yu Hua, Ling Liang, Xinfeng Xie, Xing Hu, Yuan Xie. "SEALing Neural Network Models in Encrypted Deep Learning Accelerators." 2021 58th ACM/IEEE Design Automation Conference (DAC). IEEE, 2021.

- [C2] Xinfeng Xie, Zheng Liang, Peng Gu, Abanti Basak, Lei Deng, Ling Liang, Xing Hu, Yuan Xie. "SpaceA: Sparse Matrix Vector Multiplication on Processing-in-Memory Accelerator." 2021 IEEE International Symposium on High-Performance Computer Architecture (HPCA). IEEE, 2021.

- [C3] Abanti Basak, Jilan Lin, Ryan Lorica, Xinfeng Xie, Zeshan Chishti, Alaa Alameldeen, Yuan Xie. "Saga-bench: Software and hardware characterization of streaming graph analytics workloads." 2020 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS). IEEE, 2020.

- [C4] Peng Gu, Xinfeng Xie (co-primary author), Yufei Ding, Guoyang Chen, Weifeng Zhang, Dimin Niu, Yuan Xie. "iPIM: Programmable in-memory image processing accelerator using near-bank architecture." 2020 ACM/IEEE 47th Annual International Symposium on Computer Architecture (ISCA). IEEE, 2020.

- [C5] Xing Hu, Ling Liang, Shuangchen Li, Lei Deng, Pengfei Zuo, Yu Ji, Xinfeng Xie, Yufei Ding, Chang Liu, Timothy Sherwood, Yuan Xie. "Deepsniffer: A dnn model extraction framework based on learning architectural hints." Proceedings of the Twenty-Fifth International Conference on Architectural Support for Programming Languages and Operating Systems. 2020.

- [C6] Kun Wu, Guohao Dai, Xing Hu, Shuangchen Li, Xinfeng Xie, Yu Wang, Yuan Xie. "Memory-bound proof-of-work acceleration for blockchain applications." Proceedings of the 56th Annual Design Automation Conference 2019. 2019.

- [C7] Yu Ji, Youyang Zhang, Xinfeng Xie, Shuangchen Li, Peiqi Wang, Xing Hu, Youhui Zhang, Yuan Xie. "Fpsa: A full system stack solution for reconfigurable reram-based nn accelerator architecture." Proceedings of the Twenty-Fourth International Conference on Architectural Support for Programming Languages and Operating Systems. 2019.

- [C8] Abanti Basak, Shuangchen Li, Xing Hu, Sang Min Oh, <u>Xinfeng Xie</u>, Li Zhao, Xiaowei Jiang, Yuan Xie. "Analysis and optimization of the memory hierarchy for graph processing workloads." 2019 IEEE International Symposium on High Performance Computer Architecture (HPCA). IEEE, 2019.

- [C9] Peiqi Wang, <u>Xinfeng Xie</u>, Lei Deng, Guoqi Li, Dongsheng Wang, Yuan Xie. "Hitnet: Hybrid ternary recurrent neural network." Proceedings of the 32nd International Conference on Neural Information Processing Systems. 2018.

- [C10] Jie Wang, <u>Xinfeng Xie</u>, Jason Cong. "Communication optimization on GPU: A case study of sequence alignment algorithms." 2017 IEEE International Parallel and Distributed Processing Symposium (IPDPS). IEEE, 2017.

- [J1] <u>Xinfeng Xie</u>, Peng Gu, Jiayi Huang, Yufei Ding, Yuan Xie. "MPU-Sim: A Simulator for In-DRAM Near-Bank Processing Architectures." IEEE Computer Architecture Letters, vol. 21, no. 1, pp. 1-4, 1 Jan.-June 2022, doi: 10.1109/LCA.2021.3135557.

- [J2] Xinfeng Xie, Prakash Prabhu, Ulysse Beaugnon, Mangpo Phitchaya Phothilimthana, Sudip Roy, Azalia Mirhoseini, Eugene Brevdo, James Laudon, Yanqi Zhou. "A Transferable Approach for Partitioning Machine Learning Models on Multi-Chip-Modules." arXiv preprint arXiv:2112.04041 (2021).

- [J3] Xiaobing Chen, Yuke Wang, <u>Xinfeng Xie</u>, Xing Hu, Abanti Basak, Ling Liang, Mingyu Yan, Lei Deng, Yufei Ding, Zidong Du, Yuan Xie. "Rubik: A Hierarchical Architecture for Efficient Graph Neural Network Training." IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (2021).

- [J4] Xinfeng Xie, Peng Gu, Yufei Ding, Dimin Niu, Hongzhong Zheng, Yuan Xie. "MPU: Towards Bandwidth-abundant SIMT Processor via Near-bank Computing." arXiv preprint arXiv:2103.06653 (2021).

- [J5] <u>Xinfeng Xie</u>, Xing Hu, Peng Gu, Shuangchen Li, Yu Ji, Yuan Xie. "NNBench-X: A Benchmarking Methodology for Neural Network Accelerator Designs." ACM Transactions on Architecture and Code Optimization (TACO) 17.4 (2020): 1-25.

- [J6] Peng Gu, Xinfeng Xie, Shuangchen Li, Dimin Niu, Hongzhong Zheng, Krishna T Malladi, Yuan Xie. "Dlux: a lut-based near-bank accelerator for data center deep learning training workloads." IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (2020).

- [J7] Peiqi Wang, Dongsheng Wang, Yu Ji, <u>Xinfeng Xie</u>, Haoxuan Song, XuXin Liu, Yongqiang Lyu, Yuan Xie. "QGAN: Quantized generative adversarial networks." arXiv preprint arXiv:1901.08263 (2019).

- [J8] Xinfeng Xie, Xing Hu, Peng Gu, Shuangchen Li, Yu Ji, Yuan Xie. "Nnbench-x: Benchmarking and understanding neural network workloads for accelerator designs." IEEE Computer Architecture Letters 18.1 (2019): 38-42.

- [J9] Xinfeng Xie, Dayou Du, Qian Li, Yun Liang, Wai Teng Tang, Zhong Liang Ong, Mian Lu, Huynh Phung Huynh, Rick Siow Mong Goh. "Exploiting sparsity to accelerate

fully connected layers of cnn-based applications on mobile socs." ACM Transactions on Embedded Computing Systems (TECS) 17.2 (2017): 1-25.

#### Abstract

Efficient In-DRAM Near-Bank Processing for Emerging Parallel Computing Workloads

by

### Xinfeng Xie

Despite the success of parallel architectures and domain-specific accelerators in boosting the performance of emerging parallel workloads, contemporary computer organizations still face the bottleneck of data movement between processors and the main memory. Processing-in-memory (PIM) architectures, especially those designs integrating compute logics near DRAM memory banks, are promising to address this bottleneck. However, such an in-DRAM near-bank integration faces hardware and software design challenges in performance, area overheads, architecture complexity, and programmability.

To address these challenges, this dissertation focuses on developing efficient hardware and software solutions for in-DRAM near-bank computing. First, this dissertation investigates the memory bandwidth bottleneck of contemporary hardware platforms through in-depth workload characterization, which motivates in-DRAM near-bank processing solutions. Second, this dissertation proposes multiple full-stack in-DRAM near-bank processing solutions targeting different application scopes that vary from application-specific to general-purpose computing. These solutions reveal a wide spectrum of trade-off points among hardware efficiency, architecture flexibility, and software complexity. On top of these solutions, this dissertation introduces an open-source simulation framework that supports the architectural and software optimization studies of in-DRAM near-bank processing. Finally, this dissertation develops novel machine learning-based compiler optimizations for partitioning workloads on a chiplet hardware platform that has a distributed compute-memory abstraction similar to in-DRAM near-bank architectures.

# Contents

| $\mathbf{C}_{1}$ | Curriculum Vitae                                                                                     | vii                                    |

|------------------|------------------------------------------------------------------------------------------------------|----------------------------------------|

| $\mathbf{A}$     | Abstract                                                                                             | x                                      |

| 1                | Introduction                                                                                         | 1                                      |

| 2                | NNBench-X: A Benchmarking Methodology for Neural Network A celerator Designs  2.1 Motivation         | 6<br>8<br>13<br>24<br>35               |

| 3                | SpaceA: Sparse Matrix Vector Multiplication on Processing-in-Memora Accelerator  3.1 Motivation      | 39<br>41<br>44<br>49<br>53<br>66<br>68 |

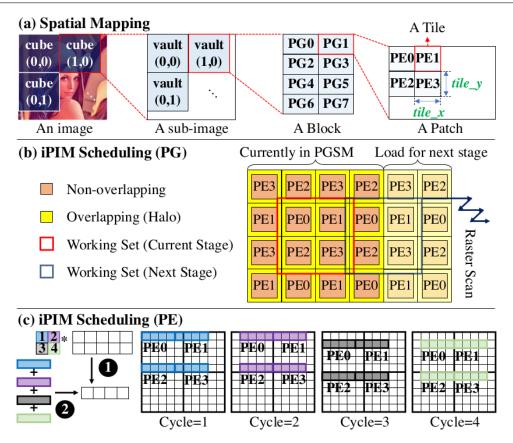

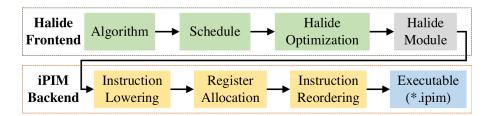

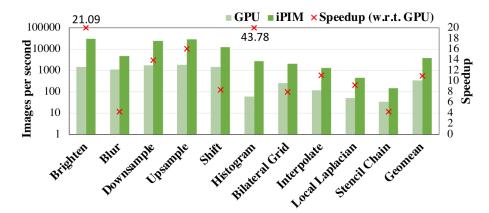

| 4                | iPIM: Programmable In-Memory Image Processing Accelerator Usin Near-Bank Architecture 4.1 Motivation | 70<br>73<br>76<br>78<br>85             |

| 5  | MP    | U: Memory-Centric SIMT Processor via In-DRAM Near-Bank Con        | m-  |

|----|-------|-------------------------------------------------------------------|-----|

|    | put   | ing                                                               | 98  |

|    | 5.1   | Motivation                                                        | 101 |

|    | 5.2   | MPU Architecture                                                  | 103 |

|    | 5.3   | Compiler Support                                                  | 108 |

|    | 5.4   | Evaluation                                                        | 111 |

|    | 5.5   | Related Work                                                      | 122 |

|    | 5.6   | Conclusion                                                        | 124 |

| 6  | MP    | U-Sim: A Simulator for In-DRAM Near-Bank Processing Architecture  | c-  |

|    | ture  | es                                                                | 125 |

|    | 6.1   | MPU Simulator                                                     | 127 |

|    | 6.2   | Calibration Studies                                               | 133 |

|    | 6.3   | Case Studies                                                      | 135 |

|    | 6.4   | Related Work                                                      | 138 |

|    | 6.5   | Conclusion                                                        |     |

| 7  | АТ    | Transferable Approach for Partitioning Machine Learning Models of | n   |

|    |       | lti-Chip-Modules                                                  | 140 |

|    | 7.1   | Motivation                                                        | 142 |

|    | 7.2   | Related Work                                                      | 146 |

|    | 7.3   | Hardware Architecture and Problem Formulation                     | 148 |

|    | 7.4   | Reinforcement Learning with a Constraint Solver                   | 151 |

|    | 7.5   | Experiments                                                       |     |

|    | 7.6   | Conclusion                                                        |     |

| 8  | Sun   | nmary                                                             | 166 |

| Ri | hliog | graphy                                                            | 170 |

# Chapter 1

# Introduction

The slowdown of technology node scaling urges hardware architecture innovations to sustain the performance improvements of modern computing platforms. Over the last several decades, parallel computing architectures, including multi-core CPUs and many-cores GPUs, have achieved great success in accelerating many data-intensive parallel computing workloads. Additionally, domain-specific hardware designs further boost the performance improvements in many important application domains, such as TPU [1] for machine learning applications. Despite these successful architecture innovations, the advances in computation capability significantly outpace the improvements of memory technology. Compared with the growth of computation capability on modern computing platforms, the increase of memory bandwidth is much slower. This comes from the difficulties in increasing the number of off-chip I/O pins and the frequency of memory bus under stringent area, thermal, and signal integrity constraints. As a result, the memory bandwidth wall emerges as a new bottleneck where data movements between processors and memory units can hardly catch up with the computation throughput.

The 3D-stacking near-data-processing (3D-NDP) architecture [2] emerges as a promising approach to alleviate this memory bandwidth bottleneck. Currently, high-end GPUs

are equipped with high-bandwidth memory (HBM) stacks, where off-chip data transfers need to go through the low performance I/Os on the silicon interposer. The principal idea of 3D-NDP is to closely integrate affordable logic components adjacent to the memory stack. A large number of pioneering studies have adopted the processing-on-base-logic-die (PonB) architecture, where general purpose cores (e.g., SIMT cores [3–10]) are placed on the base logic die of the 3D stack to benefit from the intra-stack bandwidth enhancement (around 2× w.r.t. HBM [10]). This solution provides a mediocre bandwidth improvement because intra-stack memory accesses are still bounded by the limited number of through-silicon-vias (TSVs) between memory dies and the base logic die. To overcome this bandwidth bottleneck of TSVs, recent near-bank accelerators [11–13] further move simple arithmetic units closer to the DRAM banks to harvest the abundant bank-internal bandwidth (around 10× w.r.t. process-on-logic-die solution). These near-bank accelerators have demonstrated significant speedups (around  $2 \times -14 \times$  w.r.t. GPU). Moreover, recent industrial near-bank prototypes from UPMEM [14] and Samsung [15] have demonstrated that it is feasible to place compute-logic on DRAM dies. Thus near-bank processing is promising to tackle the memory bandwidth issue.

Despite the promising future of near-bank processing, there are still hardware and software challenges for efficient near-bank processing that need innovative solutions and comprehensive studies. In terms of hardware designs, we need to not only innovate area-efficient near-bank processing architectures but also investigate the trade-off between hardware programmability and efficiency. Although prior work demonstrates several near-bank processing designs through domain customization [11,12,15], the solutions for efficient programmable in-DRAM compute-logics are still missing. Moreover, the fabrication of such compute-memory hybrid chips is expensive so that the trade-offs among application scopes, hardware costs, and performance are important. In terms of software support, the unique hardware features of near-bank processing architectures together with

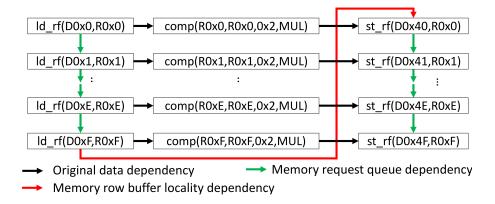

a wide spectrum of hardware designs open a new space for studying efficient programming language and system supports. Because of domain specialization, prior studies usually only narrow this large space to their applications. In particular, near-bank processing architectures have unique hardware features different from traditional processors that are not taken into consideration in modern compilers and system software. For example, different access patterns to the same memory bank could result in significant bandwidth differences because DRAM row buffer locality affects DRAM timing. These unique hardware features make the optimizations of not only data locality but also memory access order important and challenging. Finally, an open-source simulator for studying the hardware and software challenges of near-bank processing is missing. Even though there are some existing simulators for PIM architectures, they can hardly support the unique architecture features and the best fit programming model of near-bank processing. This missing piece significantly impedes the research and development of efficient in-DRAM near-bank processing solutions.

To address the aforementioned challenges for efficient in-DRAM near-bank processing, we make the following contributions in this dissertation:

Architecture Designs: In this dissertation, we develop three near-bank processing architectures targeting different application scopes. These architectures include application-specific, domain-specific, and general-purpose computing designs. In particular, we develop SpaceA for sparse matrix-vector multiplication, iPIM for image processing applications, and MPU for data-intensive parallel computing workloads Our architectural innovations include lightweight hardware components through customization and decoupled control-execution to minimize in-DRAM overheads. Through our evaluations of performance, power, and area overheads among these three architectures, this dissertation provides a comprehensive view of trade-offs between application scopes and these design metrics. In particular, application-specific designs provide the most significant

performance and energy efficiency improvements with the smallest area overhead while general-purpose design can also achieve considerable performance benefits with affordable overheads.

<u>Software Support:</u> To address the challenges of unique memory abstraction and fully exploit the hardware potentials of near-bank processing platforms, we develop several optimizations in this dissertation. These optimizations include data locality exploration in SpaceA by clustering matrix rows with similar column indices to the same memory bank, memory order enforcement in iPIM, and register location analysis in MPU. In addition to these architecture-dependent optimizations, we also study the workload partitioning problem on multi-chip-modules (MCMs) that have a similar memory space abstraction as near-bank processing architectures. We develop a novel constrained reinforcement learning method to partition machine learning workloads on an MCM-based ML accelerator, and our real hardware evaluation demonstrates its significant improvements over existing search methods in not only the final achieved speedups but also the compilation time.

<u>Simulation Infrastructure:</u> Through our research projects for near-bank processing architectures, we build and release an open-source simulator, MPU-Sim, for studying hardware and software challenges. In particular, MPU-Sim supports unique architecture features that are important to near-bank processing, such as individual memory bank control, shared bus arbitration, and decoupled execution pipelines. Moreover, MPU-Sim supports the single instruction multiple threads (SIMT) programming model that is the best fit to control a massive number of parallel memory banks. These unique hardware and software features are missing from existing PIM simulators. We conduct calibration and case studies to validate MPU-Sim and demonstrate its potential usage for the future research of near-bank processing solutions.

The remainder of this dissertation is organized as follows: Chapter 2 presents a holistic benchmarking methodology for neural network accelerator designs, which moti-

vates near-bank computing architectures to overcome the memory bandwidth bottleneck. Chapter 3, Chapter 4, and Chapter 5 present near-bank processing architectures for application-specific accelerator, domain-specific accelerator, and general-purpose computing respectively. In particular, Chapter 3 presents SpaceA for sparse matrix vector multiplication, Chapter 4 presents iPIM for image processing applications, and Chapter 5 presents MPU for data-intensive parallel computing workloads. We also develop and detail our open-source simulator, MPU-Sim, in Chapter 6 that is an important tool in studying hardware and software challenges for efficient near-bank processing. In addition to simulation tools, we also optimize the workload partitioning problem on real hardware in Chapter 7 that has a similar memory space abstraction as near-bank processing architectures. Finally, Chapter 8 summarizes the research projects and contributions of this dissertation for efficient in-DRAM near-bank computing solutions.

# Chapter 2

# NNBench-X: A Benchmarking

# Methodology for Neural Network

# Accelerator Designs

In this chapter, we introduce NNBench-X which is a benchmarking methodology for neural network accelerator designs. This project conducts workload characterization and hardware evaluation for neural network (NN) applications, which derives insights about both workload characteristics and future hardware design guidelines. One of the most important observations in this project is the memory bandwidth bottleneck in many NN models despite the wide usage of compute-intensive tensor operations. Our hardware evaluation reveals that these applications urge the memory bandwidth of future hardware designs.

Neural network (NN) algorithms have demonstrated better accuracy than traditional machine learning algorithms in a wide range of application domains, such as computer vision (CV) [16–19] and natural language processing (NLP) [20–22]. These breakthroughs indicate a promising future for their real-world deployment. Deploying these applications,

especially for the inference stage, requires high performance under stringent power budgets, which boosts the emergence of accelerator designs for these applications. However, designing such an NN accelerator using application-specific integrated circuits (ASICs) is challenging because NN applications are changing rapidly to support new functionalities and improve accuracies, while ASIC design requires a long design and manufacturing period. The accelerator design could be prone to becoming obsolete if the design fails to capture key characteristics of emerging models. Therefore, a benchmark to capture these workload characteristics is crucial to guiding NN accelerator design.

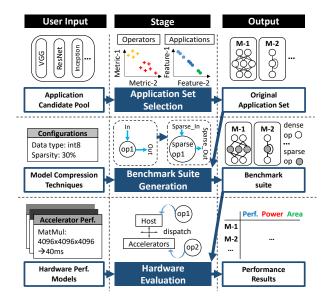

In this work, we propose an end-to-end benchmarking approach for software-hardware co-design to quantitatively select applications and benchmark software-hardware co-design by decoupling our approach into three stages, workload characterizations, software-level model compression strategies, and hardware-level accelerator evaluations. In the first stage, application set selection, we characterize NN applications of interest without considering any software optimization techniques. After gathering their performance features, we select representative applications for the original application set. In the second stage, benchmark suite generation, users can refine the selected applications to generate the final benchmark suite according to their model compression strategies. New NN models for each application in the original benchmark suite will be generated according to software-level optimizations, such as quantizing and pruning techniques. In the last stage, hardware evaluation, users can provide the performance models of their accelerator designs together with the assumptions of interconnection and host. Accelerators are evaluated with the benchmark suite generated from the second stage. Power, performance, and area results are derived according to input performance models.

To demonstrate the functionality of our benchmark, we conduct a case study on designing NN accelerators for general NN applications. First, we comprehensively analyze 57 models with 224,563 operators from the TensorFlow (TF) Model Zoo [23]. Second, we

generate benchmark suites by using several state-of-the-art software-level optimizations including quantizing and pruning NN models. Finally, we evaluate several representative accelerators including general-purpose processors (CPU and GPU), accelerator architecture (DianNao [24]), near-data-processing architecture (Neurocube [25]), and sparse-aware architecture (Cambricon-X [26]).

Our contributions can be summarized as follows:

- We propose a novel benchmarking method, which selects the benchmark by analyzing a user-input candidate application pool and covers software-hardware co-design configurations with high flexibility. Therefore, our benchmark method is able to provide guidelines for architecture design to trade-off application compatibility, algorithm accuracy, and hardware performance.

- We conduct a case study of generating a general-purpose NN benchmark suite from the TF Model Zoo while applying state-of-the-art NN model compression techniques and evaluate it on representative architectures to demonstrate the functionality of our benchmark method. Our case study reveals that CV and NLP applications show very different performance characteristics and favor different compression techniques and hardware architectures.

# 2.1 Motivation

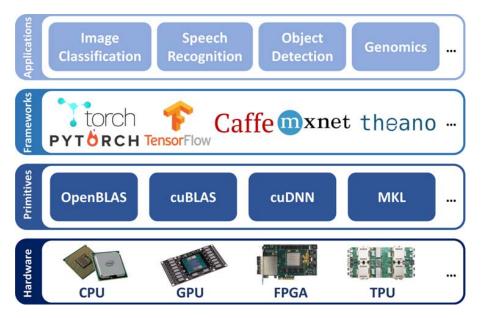

# 2.1.1 System Stack and Neural Network Models

Modern NN development and deployment system stacks are decoupled into several levels. As shown in Figure 2.1, the whole system stack includes application, framework, primitive, and hardware levels. From top to bottom, the application level focuses on developing high accuracy algorithms, and sometimes makes trade-offs between accuracy

Figure 2.1: System stack for the development and deployment of NN applications including (1) application layer, (2) framework layer, (3) primitive layer, and (4) hardware layer.

and performance when exploring different NN structures. The framework level focuses on transforming high level abstractions into hardware primitives by providing a flexible programming model and efficient runtime environment. Meanwhile, the primitive level provides simple and well-optimized primitives for the hardware. For example, cuDNN [27] provides well-optimized library for executing convolution on GPUs. At the bottom of the whole development and deployment stack, the hardware level provides efficient hardware platforms for executing NN applications.

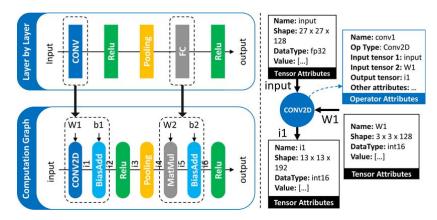

Across these system stack levels, each NN model is represented by a computation graph, which abstracts tensor operators as vertexes and tensor operands as edges to present an NN model. The topology of computation graphs indicate the data dependency among tensor operators. Figure 2.2 provides an example NN represented by these two abstractions to demonstrate their differences. The computation graph abstraction brings a more flexible representation of NN models and modern frameworks, such as TensorFlow [28] and PvTorch [29], adopt computation graph as the programming model.

Figure 2.2: An NN example represented by the layer-by-layer abstraction and the computation graph with the detailed components of a Conv2D operator to explain what are included in an operator.

Thus, the computation graph representation is general across different NN frameworks. Moreover, because the computation graph does not have any constraint on the graph topology, it is fully compatible with all widely used NN models including RNN models even though it could introduce loops in the computation graph. All models from Tensor-Flow Model Zoo [23] are represented by TensorFlow graphs, which is an implementation of the computation graph concept. In the rest of this paper, we adopt this abstraction taking an NN model as a computation graph.

### 2.1.2 Neural Network Benchmarks

Although many NN benchmark suites have recently been proposed, through analyzing available suites we see that many demands are not met. We first narrow down the analysis of existing suites by categorizing all previous benchmarks in terms of benchmark-suite and benchmark-object. Then, we highlight the novelty of this work by comparing it to BenchIP [30] and Fathom [31] in four detailed aspects.

All previous NN benchmarks can be categorized according to the benchmark-suite and benchmark-object. A benchmark-suite consists of a set of representative workloads

Table 2.1: Classifying NN benchmarks w.r.t. benchmark-suite and benchmark-object. (★: benchmark-suite, □: benchmark-object)

|             | BenchNN | BenchDL | DeepBench | Fathom | BenchIP | Our Work |

|-------------|---------|---------|-----------|--------|---------|----------|

|             | [32]    | [33]    | [34]      | [31]   | [30]    |          |

| Application | *       | *       |           | *      | *       | ★ □      |

| Framework   |         |         |           |        |         |          |

| Primitive   |         |         | *         |        | *       |          |

| Hardware    |         |         |           |        |         |          |

Table 2.2: The uniqueness of our benchmarking methodology. (X means the corresponding feature is not supported, and  $\checkmark$  means the corresponding feature is supported)

|                                | Fathom | BenchIP | Ours     |

|--------------------------------|--------|---------|----------|

| Analysis based App. Selection  | Х      | Х       | ✓        |

| Flexible with Update/Customize | Х      | Х       | ✓        |

| SW/HW Co-design                | Х      | fixed   | general  |

| Evaluation on Accelerators     | Х      | ASIC    | ASIC/NDP |

to be evaluated on different benchmark-objects. We classify the benchmark-suite and benchmark-object into different levels in the system stack, as shown in Table 2.1. Although BenchNN [32] is one of earliest efforts in building an NN benchmark, the benchmark-suite is a bit out of date without updates. Prior study [33] (denoted as BenchDL) proposes a benchmark suite for evaluating different deep learning software tools, i.e., frameworks in our system stack of NN applications. DeepBench [34] is a benchmark suite comparing the performance of different primitives on different platforms. However, benchmarking NN applications from the primitive layer loses the whole picture. Fathom [31] and BenchIP [30] serve a similar purpose as our work. However, they do not take software-hardware co-design as the benchmark object. Different from all of them, our benchmarking methodology targets at capturing end-to-end application-to-hardware characteristics to guide architecture design for state-of-the-art NN workloads. Since both Fathom and BenchIP serve a similar purpose of benchmarking NN accelerator designs, we further detail our comparison with Fathom and BenchIP in four aspects, as summarized

in Table 2.2.

Quantitative analysis based benchmark selection: Accelerator designers usually know the application domain they are interested in, which could include a large number of NN applications. Thus, it is important to select representative NN applications to guide hardware architecture design. Fathom and BenchIP pick their applications with some empirical guidelines but not by any quantitative analysis. Even though they show the effectiveness of their selected suits afterward, there is no guarantee that their selections are the most representative. On the contrary, our approach selects benchmarks according to the results of extensive profiling and analyzing. Our method characterizes NN applications through application features that are key to the performance, from the perspective of architecture designs. At the end of Section 2.3.1, we show how our method captures additional features that other benchmarks fail to cover.

Flexible with updates and customizations: We propose a benchmarking methodology, not simply a benchmark suite. By doing this, we are subject to updates due to the rapid developing NN algorithms. Statistics [30] have shown that within one year, the NN models proposed in top tier conferences double. For a fixed benchmark suite, it is difficult to know whether to extend the suite and whether a new accelerator is needed when a new model appears. Although evaluating a new model on existing accelerators can help us understand its characteristics to some extent, the demand for updating the benchmark suite and designing a new accelerator would be challenging without an in-depth workload characterization. In addition, most of the accelerators target a certain application scenario (e.g., autonomous cars), instead of a general NN processor. A single one-for-all benchmark suite does not adequately address these needs. Instead, we generate different suites according to the user-customized candidate application pool.

SW/HW co-design: Recent NN accelerator designs usually include both software optimizations, such as model pruning and quantization, and hardware optimizations.

Our benchmark method is the first for accelerators with a comprehensive awareness of software-hardware co-design. Although BenchIP [30] includes sparse models, such as Sparse VGG, into their application set as representative workloads, these considerations are insufficient due to two reasons. First, pruned models are very similar to their original models in their work. For example, Sparse VGG performs very similar to VGG in terms of extracted performance features, making it redundant. Second, their sparsity benchmark cannot consider all model compression techniques. For example, structural sparsity [35] is not covered.

Diversity of evaluation platforms: Because of the growing heterogeneity of hardware platforms, targeting only ASIC designs is not sufficient. We evaluate our benchmarks not only on CPU/GPU and ASICs but also on other innovative architectures such as NDP architectures. In addition, our evaluation method is not limited to any NN framework. Instead, we use the computation graph as a programming model with a general abstraction for the execution of NN applications across different platforms.

# 2.2 Benchmarking Methodology

An overview of our benchmarking method is shown in Figure 2.3. Our benchmarking method includes three stages. The first stage is application set selection, with an application candidate pool as its user input and original application set as its output [36]. The second stage is benchmark suite generation, with the model compression technique as the user input and the previous generated original application set as another input. The last stage is the hardware evaluation, which takes the generated benchmark suite and the hardware performance models as its inputs, and then outputs the performance results. The rest of this section will introduce these three stages in detail.

Figure 2.3: Benchmark method overview with three main stages and their corresponding inputs and outputs.

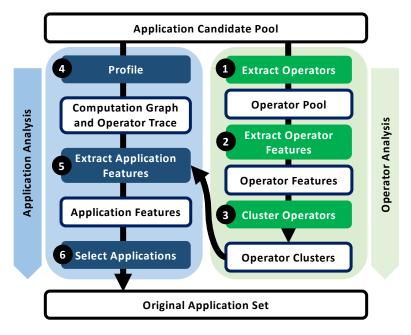

# 2.2.1 Application Set Selection

In the first stage, application set selection, we select diverse and representative NN applications from the application candidate pool which includes the applications of the user's interests.

The proposed application set selection consists of two phases, operator-level and application-level analysis, as shown in Figure 2.4. Since tensor operators are the primitives of NN applications, operator-level analysis is conducted first, before application-level analysis. In the operator-level analysis, we extract all operators from the application candidate pool, and use two important metrics, locality and parallelism, as the performance feature to represent an operator. Then, all the operators are clustered into several groups according to the extracted operator features. This process of getting operator clusters is detailed as Algorithm 1. After the operator-level clustering, application-level analysis is performed as the second phase. Applications are first profiled on baseline architectures before they are quantified by time breakdown on the different operator clusters. The

Figure 2.4: Application set selection process with two phases: operator-level analysis phase and application-level analysis phase.

process of getting application features is detailed as Algorithm 2. After obtaining these application features, we conduct a similarity analysis for all applications. Finally, an application set composed of diverse and representative workloads can be selected out of the application candidate pool. Instead of clustering operators according to their functionalities, as in prior work [31], our work is fundamentally different because it clusters tensor operators according to their architectural features, i.e. locality and parallelism. We observe that functionality-based classification is not sufficient and can cause incorrect bottleneck characterization, as validated by the experiments at the end of Section 2.3.1.

### Operator-level Analysis

As shown in Figure 2.4, we perform operator-level analysis in the first phase to extract operator features and cluster operators based on these operator features. Our operator-level analysis first extracts all operators from the applications in the application candidate pool. Then, we analyze operator features from the perspective of architecture designs.

Finally, we cluster these operators.

To improve the generality of the generated benchmark suite, we use platform-independent metrics as the operator feature. Specifically, we define two platform-independent metrics, Locality and Parallelism, for the operator-level analysis to reflect general architecture considerations when designing accelerators for tensor operators. A common practice in accelerator design is to consider customized data-path designs, such as the different dataflow structures in Eyeriss [37], that can leverage both the locality of these operators and can utilize multiple processing elements (PEs) to exploit the available parallelism. Thus, these two platform-independent metrics can be useful to help understand operators from the viewpoint of architectural designs for overall demands. The definition of these two metrics used to represent the architectural feature of an operator is detailed as follows.

**Locality.** This metric is defined as the amount of data needed by an operator divided by the number of scalar arithmetic computations it needs. The amount of data needed by an operator is equal to the sum of the input tensor size and the output tensor size. Input tensors include all input data needed by this operator, such as model weights. Our locality metric reflects the overall locality of an operator because it indicates the average times of a byte used in the scalar arithmetic computations. Moreover, the average times of a byte used in the computation indicates the locality in an ideal memory system where a cache hit happens if the same location was accessed before. For example, when the locality metric of an operator equals to 0.1, it means that this operator performs an arithmetic scalar computation on 0.1 byte of data on average. In other words, each byte is used for  $10 = \frac{1}{0.1}$  scalar computations on average. In an ideal memory system, this byte is accessed 10 times (1 access per arithmetic computations), and the miss rate is 10% because only the first access of these ten accesses will result in a cache miss. Another example is that when the locality metric of an operator equals to 12, it means that this

operator performs an arithmetic scalar computation on 12 bytes of data on average. In this case, each data is accessed only once for the computation, and the miss rate in an ideal memory system is 100% because there is no data-reuse. In summary, the cache miss rate of an operator in an ideal memory system is  $min\{Locality, 100\%\}$  when the cache line size is 1 byte. Thus lower values of this metric indicate better locality for the operator.

Parallelism. This metric is defined as the ratio of scalar arithmetic operations which can be executed in parallel, assuming sufficient hardware resources. Thus the quantitative value of this metric falls into the range between 0 and 1. Higher values of this metric express greater available parallelism for the operator. This metric reflects the parallelism of computations in terms of data dependency. For example, a tensor Add operator which adds two tensors with N elements in an element-wise manner has N scalar-add operations. All of these scalar-add operations can be executed in parallel without any true dependency. Therefore, the parallelism for this tensor Add operator is 100%. Take a tensor Max operator as another example. The functionality of a tensor Max operator is to find the maximum value in the input tensor with N elements. A tree-based reduction can explore the parallelism with logN sequential steps that must be executed in a sequential manner. In each step of this tree-based reduction, all of the N scalar-max operations can be executed in parallel given sufficient hardware resources. As a result, the parallelism for a tensor Max operator is  $\frac{1}{logN}$ .

After obtaining operator features in the aforementioned metrics, we can group operators into several clusters according to these operator features.

#### Application-level Analysis

As shown in Figure 2.4, we perform application-level analysis in the second phase to extract application features and select applications based on these application features. We define the performance feature of an application as the time breakdown on the different operator clusters obtained from the operator-level analysis. We denote the number of operator clusters as n. Specifically, the performance feature is denoted as  $\vec{f} = (R_1, R_2, ..., R_n)$  where  $R_i$  represents the percentage of the elapsed time spent in the i-th class operators. We profile each application from the application candidate pool on the baseline hardware, usually a CPU or a GPU, to obtain its time spent in each operator cluster. By analyzing applications in terms of time breakdown, benchmark users can have a better understanding of which operator class acts as a bottleneck on the baseline hardware. Because operators are grouped by their architecture features of both locality and parallelism, it provides clearer guidelines to design specialized hardware to accelerate the bottleneck operator cluster.

We rely on the application-level analysis phase to understand the application characteristics on baseline platforms. Thus there are several major design decisions when we are building application features. First, we use profiling information on existing baseline platforms for a more accurate analysis. Although baseline platforms are usually general-purpose processors, such as CPU or GPU, they can be changed to other hardware devices depending on design goals. For example, if NNBench-X is used to develop the second generation of TPU, the first version of TPU could be the baseline device [1]. Second, because this phase in the application set selection stage, this phase needs to be independent from software-hardware co-design solutions to be evaluated by NNBench-X. Specifically, this phase does not take any software-hardware co-design solutions as inputs and extracts application features based on performance models of these co-designs, such as the roofline model [38]. Third, we do not consider inter-operator parallelism as a part of application features because software frameworks usually take operators as the granularity of scheduling. These frameworks will offload operators to hardware instead of the whole computation graph and they are responsible to exploit inter-operator parallelism.

### Algorithm 1 Operator-level analysis to get operator clusters.

```

Input: A list of models (M) and the number of operator clusters (N)

Output: Operator cluster centers

Init All_Op_Features = []

for m in M do

for op in m.operator_list() do

op_features = ExtractOperatorFeatures(op)

All_Op_Features.append(op_features)

end for

end for

cluster_centers = kMeans(All_Op_Feastures, num_clusters=N)

Return cluster_centers

```

### **Algorithm 2** Application-level analysis to get application features.

```

Input: A list of models (M) and the centers of operator clusters (cluster_centers)

Output: The application features for each model (All_App_Features)

Init All_App_Features = []

for m in M do

Init app_feature = [0.0] * len(cluster_centers)

Init total_time = 0.0

for op in m.operator_list() do

op\_features = ExtractOperatorFeatures(op)

cluster_id = GetNearestClusterCenterID(op_features, cluster_centers)

app_feature[cluster_id] += op.elapsed_time

total_time += op.elapsed_time

end for

app_feature = app_feature / total_time

All_App_Features.append(app_features)

end for

Return All_App_Features

```

However, when designing an accelerator taking the whole computation graph as inputs, this metric can be added into application features as discussed in Section 2.4.

After this two-level analysis, we select representative applications out of the application candidate pool to build the original application set.

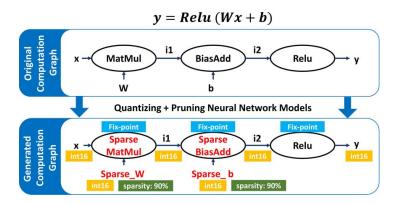

Figure 2.5: An example for benchmark suite generation to generate a new computation graph according to user-provided quantizing (int16) and pruning strategies (sparse weights).

### 2.2.2 Benchmark Suite Generation

In the second stage, benchmark suite generation, we provide interfaces for users to customize their NN compression techniques to generate the final benchmark suite.

This stage is motivated by the success of model compression techniques, either quantizing or pruning, and the fact that state-of-the-art accelerator designs leverage these techniques for better computation and memory access efficiency by designing specialized hardware, either fixed-point ALU or sparse tensor computation engines. Although we obtain a diverse and representative application set after the first stage, we cannot benchmark different accelerators using only one set of applications because of the diversity of NN model compression techniques.

Each application from the original application set is a computation graph. To customize different NN model compression techniques, we provide interfaces for the users to specify the data type of tensors in this computation graph. For tensors storing the pretrained weights, users can overwrite these weights by using pruned weights so that these tensors become sparse. Sparsity information can also be included as an additional attribute in the tensors storing weights. The sparsity of the tensors produced by activation functions, such as ReLU, can be computed in runtime. Figure 2.5 illustrates a case for

these interfaces. Suppose we quantize the original application from the single-precision floating-point into 16-bit fixed-point, and prune weights by 90%, the structure of the computation graph remains the same but the operators and tensors are changed accordingly, as shown in Figure 2.5. Users can define and import model compression methods, and change the information of operators and tensors to generate the final benchmark suite according to their software-level studies in the training stage. Compression techniques resulting in intolerable accuracy degradations should not be imported into this stage. At the end of this stage, NNbench-X produces the final test set of applications composed of quantized and pruned NN models for evaluations.

Because our benchmark methodology provides interfaces for the users to specify their own compression methods instead of defining several patterns, NNBench-X is able to support a wide range of compression methods. For example, when NNBench-X is used to evaluate software-hardware co-designs exploiting the structural sparsity [39,40], NNBench-X passes model weights to compression methods provided by the users to generate weights in structural sparse patterns. In this case, the pruned models with weights in structural sparse patterns will be in the generated benchmark suite at the end of this stage.

### 2.2.3 Hardware Evaluation

In the final stage, the hardware evaluation, we evaluate the generated benchmark suite on accelerator designs.

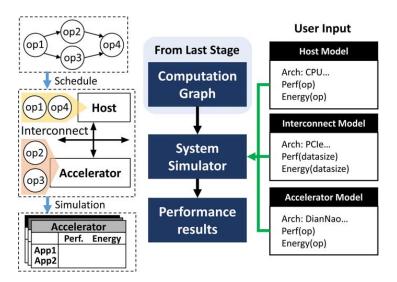

Although this stage can be completed by users with detailed simulation results of accelerators, we build a system-level simulator for fast performance estimation in the initial architecture design stages to provide high-level guidelines for accelerator designs. Our system-level simulator evaluates accelerators on the generated benchmark suite by using

Figure 2.6: The workflow of hardware evaluation with the user-inputs for hardware modeling including models for host, interconnect, and accelerators.

the performance models of the accelerator, the host, and the interconnection between the accelerator and the host. These performance models are provided by users so that they can be as simple as a roofline model or as complicated as a cycle-accurate simulator depending on the demands of hardware evaluation. For example, early design stages could use the roofline model to decide the balance between computation and memory resources while later design stages could need cycle-accurate simulators to model more hardware details. The inputs and outputs of our system-level simulator are shown in Figure 2.6. For each application in the generated benchmark suite, our simulator schedules operators into either the accelerator or the host by a first-come-first-serve scheduling algorithm. When an operator is not supported by the accelerator, it will be launched into the host with subsequent data transfer between the accelerator and the host. The performance results of running supported operators on accelerators and overheads of data transfer between the host and accelerators are provided by input hardware models which are a part of inputs to our system-level simulator. To demonstrate the usage of our system-level simulator, we use a simple but effective analytical model, the roofline model, in

Section 2.3.2 to evaluate various architectures including DianNao [24], Neurocube [25], and Cambricon-X [26].

Our system-level simulator plays a role similar to that of frameworks. Our straightforward scheduling policy may not consistently achieve optimal performance, but integrating accelerators into the whole system with developed primitives is time-consuming and impractical in the initial design space exploration stage for architectures. As the case study shown in Section 2.3.2, the performance speedups of different architectures could vary in orders of magnitudes. Therefore, our coarse but fast estimations can still provide insightful guidelines in architectural designs. Furthermore, the accuracy of estimation in this stage depends on the accuracy of performance models provided by users. Although we use a simple analytical model, roofline model, in Section 2.3.2 as a demo case, users can provide models capturing more hardware details to fit their demands exploiting various hardware designs. For example, when it is decided to use dataflow architectures in NN accelerators and our benchmark methodology is used to evaluate and compare different dataflow designs, the MAESTRO [41] framework can be used to provide the performance results of different architectures for supported operators. Another example is that when the users want to evaluate software-hardware co-designs exploiting structural sparsity, the user-provided performance models of hardware designs need to take the sparsity into account [39,40]. In both examples, our system-level simulator is responsible to provide operator information, such as input tensor shapes and operator weights, while users need to implement their own performance models as the backend to return the performance results of running the operator on their accelerators. For accelerator designs in Section 2.3.2, we implement a roofline model as the backend for various accelerator designs which returns the performance by using the roofline model according to operator information and hardware specifications. For the performance of operators on real devices, such as CPU and GPU, we implement the backend performance model by running the operator on the real device and returning the measured time.

## 2.3 Workload Characterization

We conduct a case study of benchmarking NN inference accelerators to demonstrate the usage of our benchmark approach. To this end, we set the TensorFlow (TF) Model Zoo [23] (with 57 NN models and 224,563 operators) as the application candidate pool, and our software-hardware co-design evaluation includes several state-of-the-art model compression techniques and hardware designs. The version of the TF Model Zoo we used in this case study contains 57 NN models from 24 different applications. These NN models have very diverse structures including convolutional neural networks (CNNs) and recurrent neural networks (RNNs). From the perspective of learning algorithms, these models are from different learning methods, including supervised learning, unsupervised learning, and reinforcement learning. Thus our application pool has very good coverage on existing NN applications from different application domains, with different model structures, and trained by different learning algorithms. This section follows the three-step process introduced in Section 2.2. First, Section 2.3.1 studies our application set selection process to select representative applications from TF Model Zoo. By comparing to the application set of prior benchmarks, we also demonstrate the advantages by the end of Section 2.3.1. Then, Section 2.3.2 evaluates several software-hardware codesigns on these selected applications. In the process of both application set selection and evaluating software-hardware co-designs, we conclude several observations on application characteristics and architecture design guidelines from these studies.

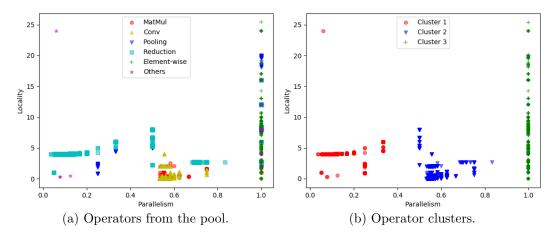

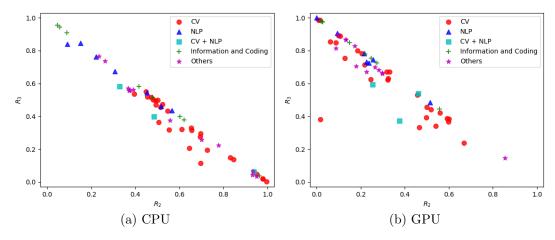

#### 2.3.1 Application Selection from TensorFlow Model Zoo

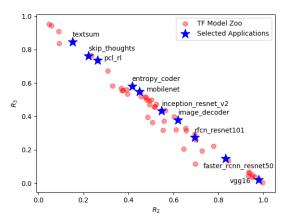

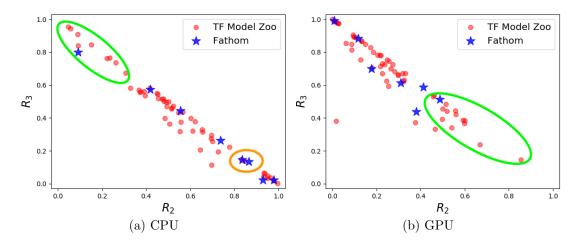

As the first step of our analysis flow, we apply the operator-level analysis to most of the applications from the TensorFlow Model Zoo [23]. We first perform extract operators Figure 2.4-1) to all 224,563 operators from the application candidate pool. We then extract operator features (Figure 2.4-2) and measure both the locality and the parallelism of the operators as defined in Section 2.2.1. The resulting distribution of operator features is shown in Figure 2.7a. It labels different operator functionalities including matrix multiplication (MatMul), convolution (Conv), pooling, reduction, element-wise, and other irregular operators (Others) where computations and memory accesses are dependent on input tensor values. Based on the performance feature distribution, we conduct cluster operations step (Figure 2.4-3), which groups these operators into three clusters. We apply the k-means algorithm and obtain the cluster results shown as Figure 2.7b. After this, we conduct an application-level analysis. Because most accelerator designs compare their performance to two kinds of general-purpose processors, CPU and GPU, we profile (Figure 2.4-4) all applications from the application candidate pool on Intel Xeon E5-2680 CPU and NVIDIA Titan Xp GPU. To extract application features (Figure 2.4-5), we use the three operator classes from previous operator analysis. The application performance feature in this case study is denoted as  $\vec{f} = (R_1, R_2, R_3)$ , where  $R_1$ ,  $R_2$ , and  $R_3$  represent the time breakdown of an application into three operator clusters. The performance feature distributions measured on CPU and GPU are shown as Figure 2.8a and Figure 2.8b. Since  $R_1 + R_2 + R_3 = 1$ , we plot two dimensional scatter figures where x-axis stands for the  $R_2$ , y-axis stands for the  $R_3$ , and  $R_1$  can be derived by  $1 - R_2 - R_3$ . Finally, we select applications (Figure 2.4-6). Based on the distribution of the application features on CPU, we select ten diverse and representative applications as the original application set by evenly sampling the application candidate pool. The

Figure 2.7: The distribution of operator features for all operators from the application candidate pool (TF Model Zoo) and the clustering results by running k-means.

Figure 2.8: The distribution of application features using CPU and GPU as baseline devices.

distribution of these ten applications is shown in Figure 2.9. Brief descriptions for these ten applications can be found in Table 2.3.

Observations on the operator-level analysis. We classify operators into several categories to obtain observations on their architectural characteristics. The operator categories are designed to reflect operator functionalities or data access patterns. Among these operator categories, matrix multiplication (MatMul), convolution (Conv), and pooling attract intensive attention in many accelerator designs because of their importance in early NN models, such as VGG models [16]. The activation functions are also very

Table 2.3: Brief descriptions for ten applications selected into the original application set.

| Application                    | Description                | Application Domain          |

|--------------------------------|----------------------------|-----------------------------|

| textsum [21]                   | Text summarization         | Natural Language Processing |

| $skip\_thoughts$ [22]          | Sentence-to-vector encoder | Natural Language Processing |

| pcl_rl [42]                    | Reinforcement learning     | Others                      |

| entropy_coder [43]             | Image file compression     | Information and Coding      |

| mobilenet [19]                 | Image classification       | Computer Vision             |

| inception_resnet_v2 $[17, 18]$ | Image classification       | Computer Vision             |

| image_decoder [44]             | Image file decompression   | Information and Coding      |

| $rfcn_resnet 101 [45]$         | Object detection           | Computer Vision             |

| faster_rcnn_resnet50 [46]      | Object detection           | Computer Vision             |

| vgg16 [16]                     | Image classification       | Computer Vision             |

common in NN models, such as ReLU operation in convolutional neural networks [16–18], and all of them are vector-like element-wise operations. Thus we create a category as Element-wise in Figure 2.7a for all operators performing vector-like operations. We also create a separate category named as reduction for operators with reduction patterns, such as the *Softmax* and *Argmax* operations. Although these five categories cover most of the operators, we put the rest of operators into the last category as others.

We make several observations from the results of operator clustering (Figure 2.7a-2.7b). First, convolution and matrix multiplication operators are similar to each other, and most of them have good locality. Because of existing reduction patterns along some tensor dimensions, such as input channels in convolution operators, these two kinds of operators possess moderate parallelism. Second, all element-wise operators have identical parallelism while the computation intensity on each tensor element can vary significantly. Because of fully parallel scalar operations for all elements in element-wise operators, element-wise operators have the largest degree of parallelism (100%). Third, operators with the same or similar functions can have very different performance features, such as reduction and pooling operators. Clustering these operators by functions and designing hardware accordingly would result in bottleneck mis-prediction.

Figure 2.9: The distribution of application features for selected applications out of the application candidate pool (TF Model Zoo).

Architecture implications of operator clusters. The application feature in our work is directly associated with the breakdown of execution time spent on different operator clusters. Since we cluster operators according to their architecture features, i.e. locality and parallelism, operators in the same cluster could favor similar architecture designs. Specifically, operators in the first cluster have limited parallelism and moderate locality, whose execution time contributes to  $R_1$ . These operators could benefit from the locality optimizations while they can hardly benefit from more parallel processing elements (PEs). Operators from the second cluster have both moderate parallelism and locality, such as matrix multiplication and convolution, whose execution time contributes to  $R_2$ . These operators could benefit from parallel PE design, more computation resources, and optimizations on locality, such as the careful design of data-flow to exploit data reuse. Finally, operators from the third cluster can be fully parallelized whose execution time contributes to  $R_3$ . Increasing the number of PEs is helpful to exploit the parallelism while these operators will become bounded by memory bandwidth when the number of PEs is sufficient.

From the perspective of applications, application features indicate the distribution of execution time on these operator clusters. Thus these application features help iden-

tify the application bottleneck from the perspective of operator clusters, which further provides architecture design guidelines. For example, an application with a large  $R_2$  indicates that its bottleneck comes from operators in the second cluster, which could prefer architecture designs with more computation resources or larger on-chip memory. Similarly, an application with a large  $R_3$  could prefer memory-centric architectures for higher effective memory bandwidth because it is bounded by operators in the third cluster.

Observations on the application-level analysis. For the application-level analysis in Figure 2.8a-2.8b, we summarize the following observations. First, Conv., MatMul, and Element-wise operators take up a majority of the application time in most of the applications, since most of the applications distribute near the line  $R_2 + R_3 = 1$ . Second, in contrast to CPU, GPU is more likely to be bounded by  $R_1$ , due to its more powerful computing resource and higher memory bandwidth. In addition,  $R_3$  takes a larger percentage on GPU, indicating there are opportunities for GPU memory system optimization. Third, the consideration of application scenarios reveals additional trends. Both of Figure 2.8a and Figure 2.8b label different application domains including computer vision (CV), natural language processing (NLP), hybrid CV and NLP (CV+NLP), information and coding, and others. We classify applications into application domains according to the task of applications. Applications for traditional CV or NLP tasks are labeled as CV or NLP respectively. The task of some applications is mixed by traditional CV or NLP tasks. For example, image captioning requires image understanding and caption generation where image feature extraction is a CV task while the caption generation involving text summary is an NLP task. The application domain of these mixed tasks is denoted as CV+NLP. In addition to these traditional CV or NLP tasks, some tasks focus on the coding of information, such as file compression, decompression, and encryption. The application domain of these tasks related to information and coding is labeled as Information and Coding although they could need domain knowledge related to CV or

Figure 2.10: The application feature distribution of applications from our application candidate pool (TF Model Zoo) compared to the distribution of applications in Fathom.

NLP when handling corresponding information, such as image compression. The domain labeled as Others includes the rest of the applications, most of the applications in this category belong to applications using reinforcement learning, such as robotics applications.  $\underline{Most\ CV\ applications\ are\ bounded\ by\ operations\ from\ R_2\ (mostly\ Conv\ and\ MatMul).}$  On the contrary, most  $NLP\ applications\ are\ bounded\ by\ operations\ from\ the\ R_3\ (mostly\ element-wise\ operators)$ . This indicates that memory-centric computing architectures can be helpful for these NLP applications.

The advantage of our methodology. We first demonstrate the advantage of the operator-level analysis by showing how misleading bottleneck diagnosis would occur if the aforementioned analysis is neglected. Without operator-level clustering, one has to extract the application feature with function-based operator clustering. For example, as described by Fathom, Add operators are clustered as the category Elementwise Arithmetic, but transpose operators are clustered as another category Data Movement. However, when using our operator-level analysis, these two clusters should be in the same category  $(R_3$  in our notation), since they have very similar architecture features in terms of locality and parallelism. There would be an issue in the case where  $R_3$  is

the application's bottleneck, but as part of  $R_3$ , neither Elementwise Arithmetic nor Data Movement individually shows as a bottleneck. The bottleneck is then misunderstood. The described problem happens for 15 out of 57 models in the TF Model Zoo. Taking application video\_prediction\_stp [47] for example, according to the performance feature defined in Fathom, it will show Conv2D as the bottleneck (taking 38% of total time). However, the elapsed time of operators from the  $R_3$  cluster takes 52% of total time, making  $R_3$ -like operators (memory-intensive highly parallel operators) the actual bottleneck, not Conv2D. Instead of accelerating Conv2D, which would result in more computation resources or larger on-chip memory, our analysis recommends that the architecture should be designed with higher effective memory bandwidth, such as processing-in-memory architectures [25,48–50], for  $R_3$ -like operators because they take the majority of the elapsed time.

Second, our benchmark process selects more diverse and representative applications. Compared to Fathom, our method selects applications from a large application candidate pool based on extracted application features. Therefore, our analysis-based selection guarantees the diversity and representativeness of selected applications from the viewpoint of performance features. To understand the representativeness of Fathom applications on the TF Model Zoo, we go through the same application analysis process for applications (8 applications in total) from Fathom. The results measured on the CPU and the GPU are shown as Figure 2.10a and 2.10b. Through comparisons, we can conclude that the application selection in Fathom is fairly good due to its similar distribution as TF Model Zoo. However, compared with Fathom, our benchmark selection in Figure 2.9 is more evenly distributed, making it more representative as a general benchmark. For example, the two selected benchmark applications in the orange circle in Figure 2.10a are too close to each other, making one of them redundant. In addition, some applications are underrepresented, such as applications in green circles in Figure 2.10a and 2.10b. The

Table 2.4: The description of hardware platforms.

| Platform                | GPU    | Nuerocube | DianNao     | Cambricon-X |

|-------------------------|--------|-----------|-------------|-------------|

| Peak Comp (GOPs)        | 12,100 | 132.4     | 482         | 528         |

| Peak Mem (GB/s)         | 547.7  | 320       | 250         | 250         |

| TDP(W)                  | 250    | 21.5      | $0.485^{1}$ | $0.954^{1}$ |

| Area (mm <sup>2</sup> ) | 471    | 68        | $3.02^{1}$  | $6.38^{1}$  |

| Tech Node (nm)          | 16     | 15        | 65          | 65          |

<sup>&</sup>lt;sup>1</sup>These power and area data are from their original papers without considering the power consumption and area cost of DRAM dies.

applications from Fathom in these green circles are not sufficiently representative of the other applications with similar characteristics.

#### 2.3.2 Hardware Evaluation

We need the benchmark generation step (Section 2.2.2) after application selection, to plug-in the NN compression setup. This step is user-customized. According to our evaluation target, we generate our benchmark suite with three config:nnbench-x:urations: no compression (for GPU), quantized 16-bit fixed-point (for DianNao), and 16-bit fixed-point quantized and 90%/95% pruned (for Cambricon-X).

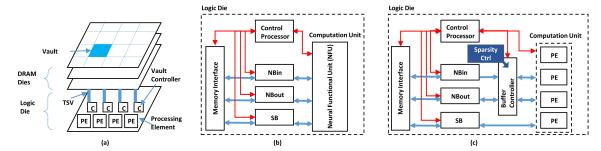

Finally, we conduct studies on evaluating several state-of-the-art software-hardware solutions in this section. In particular, we evaluate GPU (Titan Xp), Neurocube [25], DianNao [24], and Cambricon-X [26] with different model compression techniques. Among these hardware platforms we evaluated, GPU is a representative many-core processor exploiting the massive parallelism in tensor operators. Neurocube is an NDP design that exploits an internal memory bandwidth of memory cubes to accelerate memory-bound operators while DianNao is a compute-centric accelerator design with on-chip computation and data movements tailored for NN applications. Both of these two platforms are designed for computing fixed-point arithmetic, which needs the help of NN model quantization from the software-level. Cambricon-X has a similar design as DianNao except that

its design is intensively customized to exploit the sparsity of NN models, which needs the help of NN model pruning. For the purpose of architecture comparison, Figure 2.11 shows the architecture of Neurocube, DianNao, and Cambricon-X.

Table 2.4 includes comparisons among these platforms in terms of power, performance, and area. These numbers are collected from official product specifications or their original papers. Due to the lack of detailed power models and area models on these platforms, such as the off-chip DRAM power and area data of DianNao and Cambricon-X, we only estimate the performance in our case studies. We use our system-level simulator to estimate the performance of these platforms compared to the CPU baseline implementation. According to the performance results presented in the original papers, we derive an analytical model based on the roofline model [38] to estimate the performance of each supported tensor operators on accelerators. Results on the GPU are profiled and measured from the execution on a real machine. We assume that these heterogeneous platforms are connected to a host CPU, Intel Xeon E5-2680 CPU, through PCIe and any unsupported operator will be offloaded into the CPU for computation. The time of execution on the host CPU and data transfers triggered by offloading unsupported operators will be counted in the final elapsed time. However, we exclude the time used for transferring input data and model weights into these platforms because transferring different batches of input data can overlap in real-world inference stage, and loading trained weights into these platforms is a one-time overhead.

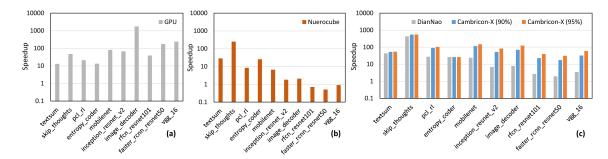

Our simulation results are shown in Figure 2.12. The original application set is evaluated on the GPU, and results are shown in Figure 2.12a. Figure 2.12b presents the performance results on Neurocube for applications quantized into 16-bit fixed-point data-type. Figure 2.12c presents the performance results for DianNao and Cambricon-X. Applications executed on DianNao are also quantized into 16-bit fixed-point. We evaluate two pruning strategies for applications executed on Cambricon-X which prunes

Figure 2.11: The architecture overview of (a) Neurocube, (b) DianNao, and (c) Cambricon-X to distinguish key architecture differences among them: (a) an NDP design, (b) a compute-centric design, and (c) a compute-centric design with the support for sparsity.

Figure 2.12: The speedups over CPU baseline of applications on (a) GPU without any model compression (b) Neurocube with models quantized into 16-bit fixed-point (c) DianNao with models quantized into 16-bit fixed-point, Cambricon-X (90%) with models further pruned 90% weights, and Cambricon-X (95%) with models further pruned 95% weights.

90% and 95% weights of models, denoted as Cambricon-X (90%) and Cambricon-X (95%), respectively.

Insights from the result. By evaluating three representative accelerator designs with various compression config:nnbench-x:uration, we make the following observations from Figure 2.12. First, GPU can benefit these applications with a higher  $R_2$  ratio in their performance features. These applications are usually computation bound. Since applications on the x-axis are ordered by the increasing order of  $R_2$ , applications closer to the right direction along the x-axis spend more time in the second cluster operators, of which most are convolution and matrix multiplication operations. As shown in Figure 2.12a, GPU obtains higher speedups on applications on the right side of the x-axis. Second,

near-data computing architectures favor applications (mostly NLP related) with a higher  $R_3$  ratio. Figure 2.12b shows that Neurocube achieves higher speedups on applications on the left side of the x-axis. Finally, we found that weight pruning is less attractive for NLP applications than it is for CV applications. Figure 2.12c shows the comparison of DianNao and Cambricon-X in terms of performance benefits from pruning NN model weights, which reduces the computation and memory workloads of matrix multiplication and convolution operations. Comparing Cambricon-X (90%) to DianNao, Cambricon-X can achieve higher speedups than DianNao, which mainly benefits from the reduction of computation and memory workloads due to pruned models. Such speedups are more significant for computation-bound applications as opposed to memory-bound applications. The results of models with different sparsities, Cambricon-X (90%) and Cambricon-X (95%), indicate that pruning more weights can have slight benefits on memory-bound applications while significant benefits on computation bound applications.

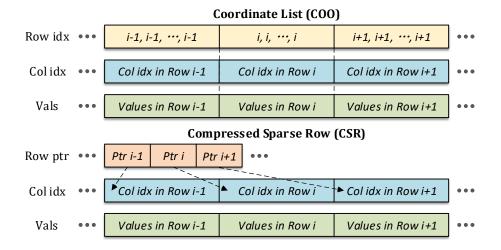

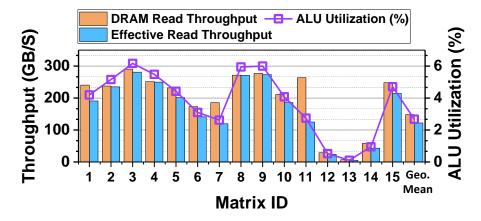

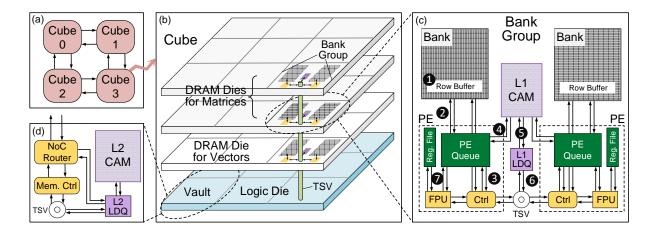

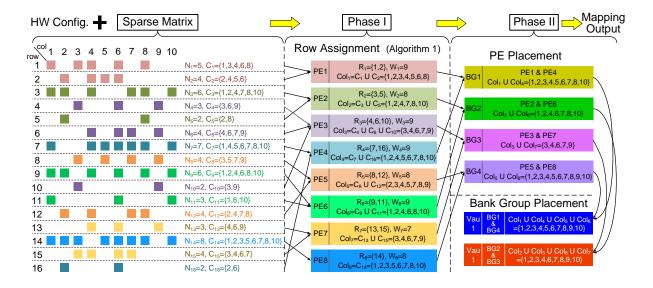

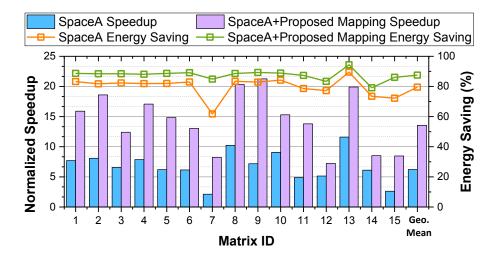

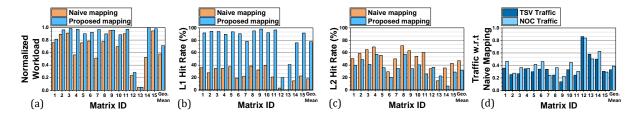

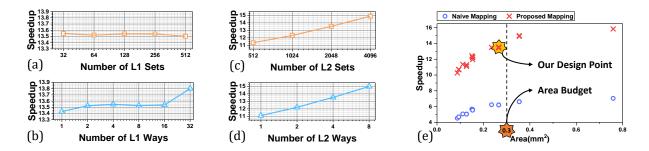

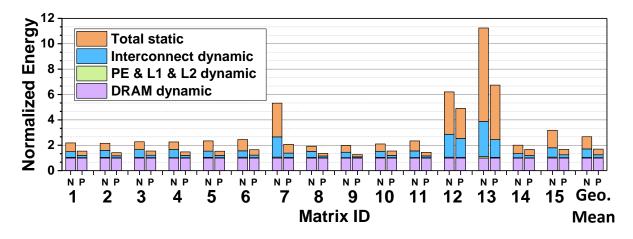

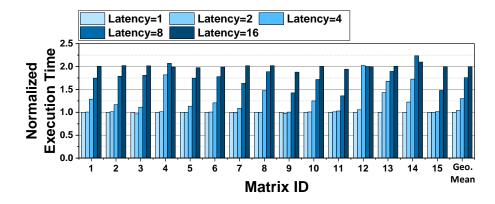

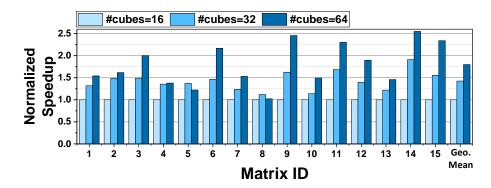

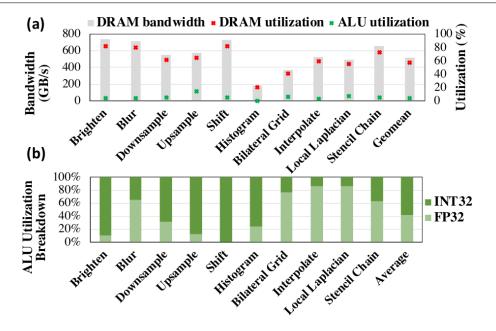

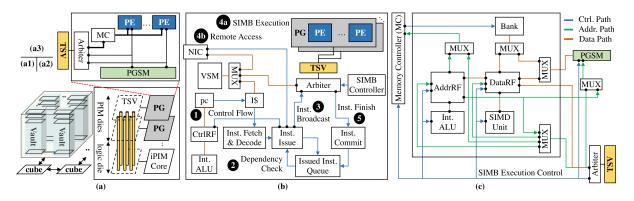

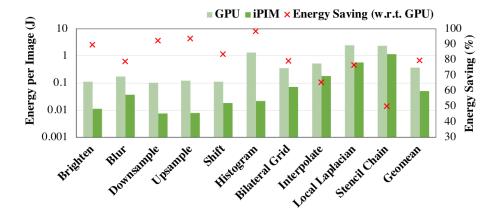

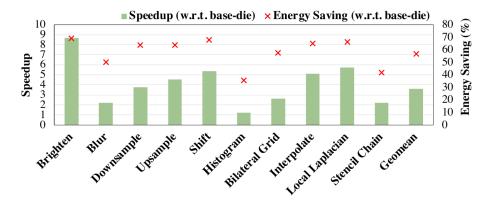

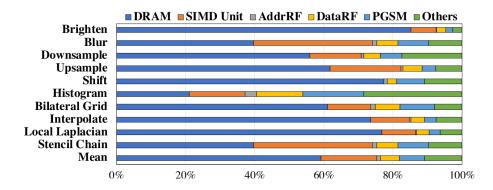

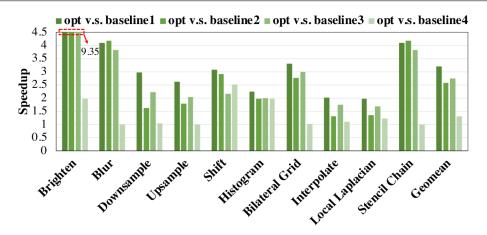

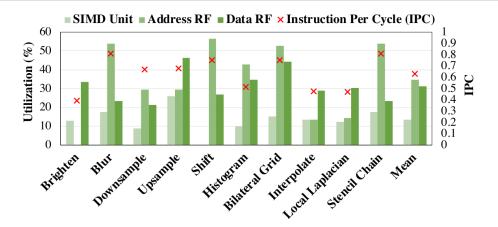

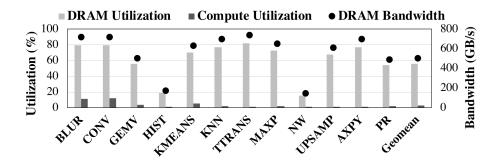

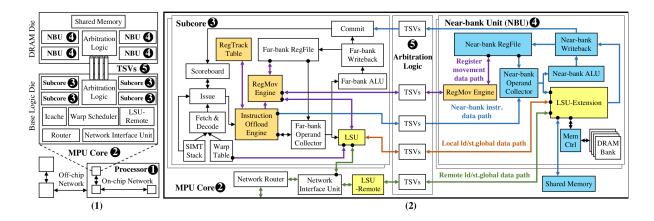

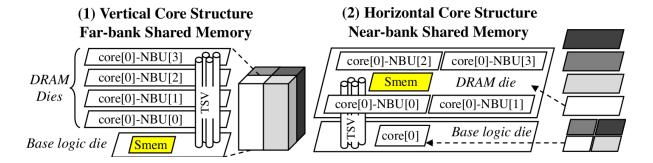

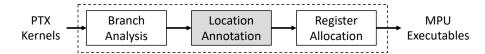

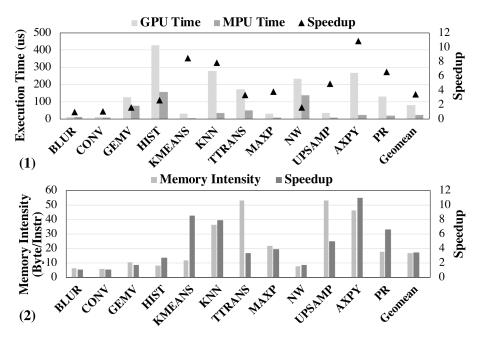

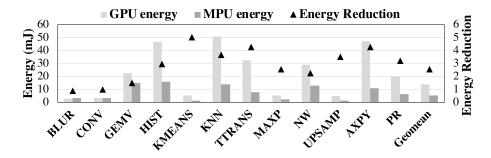

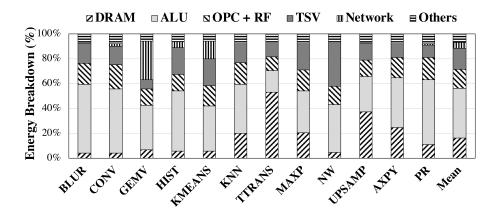

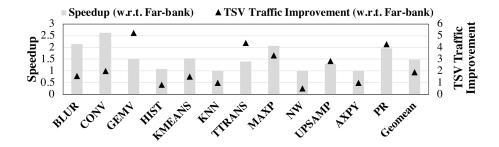

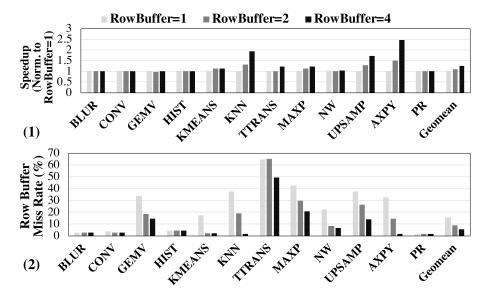

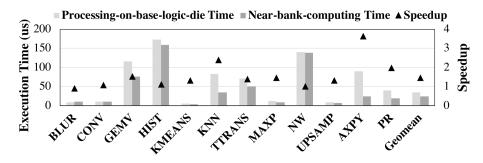

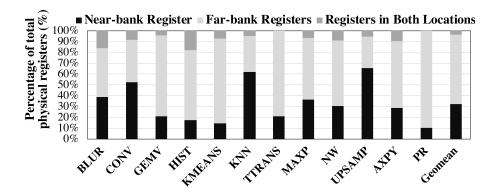

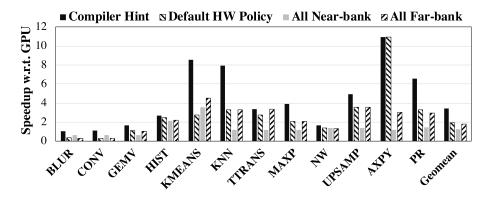

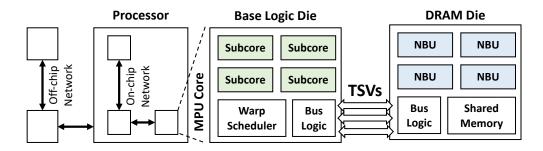

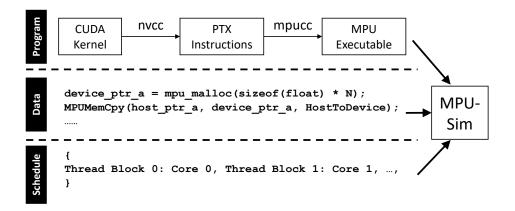

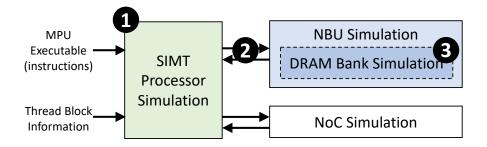

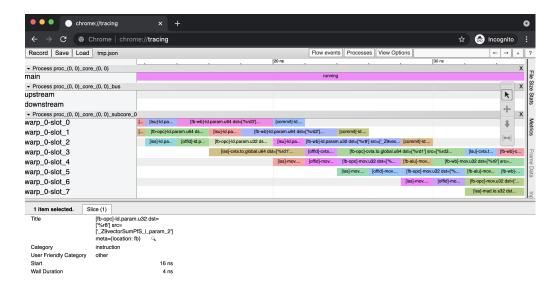

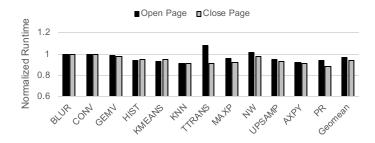

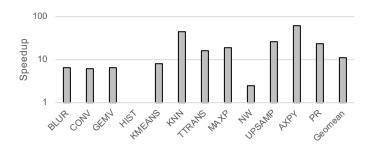

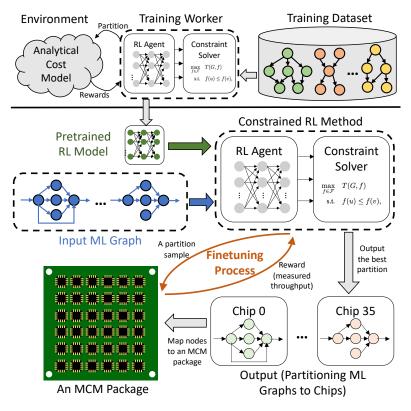

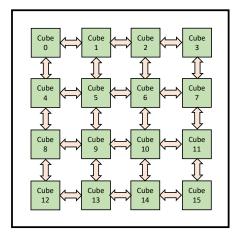

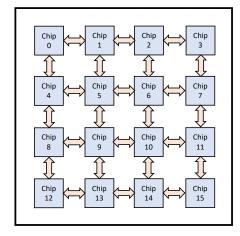

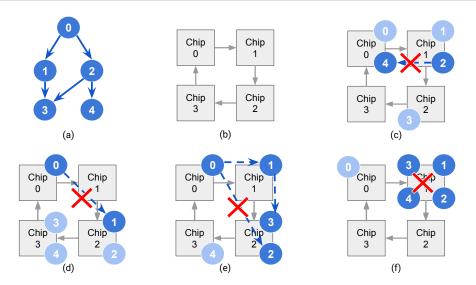

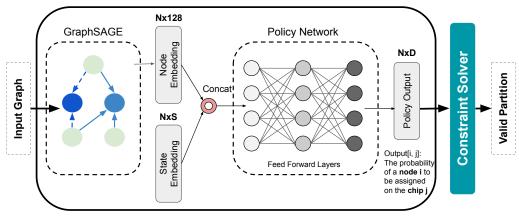

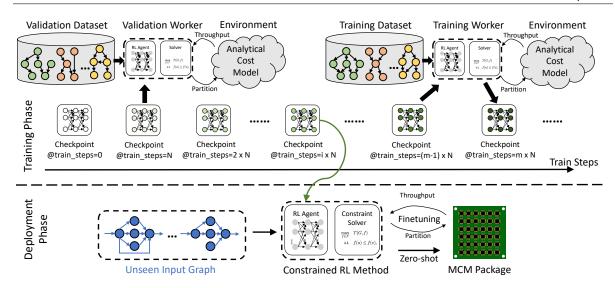

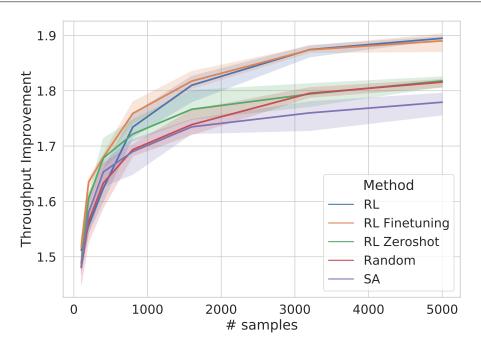

## 2.4 Discussion