# UCLA UCLA Electronic Theses and Dissertations

# Title

Integration of active GaAs based optoelectronics onto Si substrates

Permalink https://escholarship.org/uc/item/5z47h066

**Author** Chu, Chia-Pu

Publication Date 2014

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA

Los Angeles

Integration of Active GaAs Based Optoelectronics onto Si Substrates

A dissertation submitted in partial satisfaction

of the requirements for the degree Doctor of Philosophy

in Electrical Engineering

by

Chia-Pu Chu

2014

© Copyright by

Chia-Pu Chu

2014

#### ABSTRACT OF THE DISSERTATION

#### Integration of Active GaAs Based Optoelectronics onto Si Substrates

by

### Chia-Pu Chu

Doctor of Philosophy in Electrical Engineering University of California, Los Angeles, 2014 Professor Kang Lung Wang, Chair

Controlled heteroepitaxy and integration of arsenide based III-V compounds onto Si surfaces have been an important enabling technology for high efficiency solar cells and light emitters in satellite and optical interconnect applications. However, obtaining high crystal quality III-V compounds on Si, such as GaAs on Si is still challenging: (1) anti-phase domain (APD) boundary formation as the result of the polar GaAs growth on non-polar Si system, (2) a high density of threading dislocations generated by 4.1% lattice constant mismatch, and (3) the 62% thermal expansion coefficient mismatch leading to cracks during the cooling process.

The objective of this research is to obtain arsenide based III-V compounds monolithically integrated onto Si surfaces being APD-free with chemically abrupt GaAs/Si interfaces and possessing excellent optoelectronic properties. Patterned growth scheme by molecular beam epitaxy (MBE) is the approach I undertook to integrate GaAs based III-V compounds onto exactly oriented Si substrates. And the research consists of the following three stages to fulfill the objective.

(1) Precise positioning and low defect density selective area epitaxy for selfassembled/catalyst-free GaAs nanodisks on SiO<sub>2</sub> masked exactly oriented Si(100) substrates:

Pure zincblende GaAs nanodisks with precise positioning and low defect density are demonstrated by selective area epitaxy. Defects in the epilayers are reduced by strain relaxation through facets formation and by a lateral overgrowth scheme atop the SiO2 mask.

# (2) High-quality and defect-free GaAs thin film on SiO<sub>2</sub> masked exactly oriented Si(111) substrates by a two-step growth technique:

Taking advantages of low energy for both Si(111) surface and GaAs/Si(111) interface, the two-step grown GaAs of total ~175 nm atop patterned Si(111) substrates exhibits atomically smooth surface morphology, single crystallinity and a remarkably low defect density.

# (3) Successful integration of InGaAs/GaAs double heterostrucure onto SiO<sub>2</sub> masked exactly oriented Si(111) substrates with remarkably reduced thermal stress:

The atomically smooth and high crystalline quality InGaAs/GaAs DH is realized. The confined misfit dislocations at the nucleation layer and nearly threading dislocation-free buffer layer contribute to the atomically sharp GaAs/Si interface. The remarkable reduction in the thermally induced stress corroborates the effectiveness of the square shape pattern design. Optical properties and carrier dynamics are characterized by micro-photoluminescence ( $\mu$ -PL) and time-resolved PL.

The dissertation of Chia-Pu Chu is approved.

Mark S. Goorsky

Jia Ming Liu

Oscar M. Stafsudd

Kang Lung Wang, Committee Chair

University of California, Los Angeles

2014

# Table of Contents

# Chapter 1: Background and Introduction

| 1.1 Background                                                        | 1  |

|-----------------------------------------------------------------------|----|

| 1.2 The role of MBE in III-V technology                               | 2  |

| 1.3 An overview of activities in electrical vs. optical interconnects | 5  |

| 1.4 Heteroepitaxial Growth of III-V compound semiconductors on Si     | 9  |

| 1.5 Challenges of Heteroepitaxial Growth of GaAs on Si                | 17 |

| 1.6 Dissertation Outline                                              | 20 |

# Chapter 2: Experimental Techniques

| 2.1 molecular beam epitaxy (MBE)                                            | 21 |

|-----------------------------------------------------------------------------|----|

| 2.2 scanning electron microscope (SEM) and energy dispersive spectrum (EDS) | 25 |

| 2.3 atomic force microscopy (AFM)                                           | 26 |

| 2.4 transmission electron microscopy (TEM)                                  | 27 |

| 2.5 X-ray diffractometry (XRD)                                              | 28 |

| 2.6 photoluminescence (PL) and time-resolved photoluminescence (TRPL)       | 30 |

# Chapter 3: Experimental Results

| 3.1 Precise positioning and low defect density selective area epitaxy for self-assembled/catal | lyst- |

|------------------------------------------------------------------------------------------------|-------|

| free GaAs nanodisks on SiO2 masked exactly oriented Si substrates                              | 32    |

| 3.1.1 INTRODUCTION                                                                             | 32    |

| 3.1.2 EXPERIMENTAL DETAILS                                                                     | 35    |

| 3.1.3 RESULTS AND DISCUSSION  | 36 |

|-------------------------------|----|

| 3.1.4 SUMMARY AND CONCLUSIONS | 48 |

| 3.2 High-quality and defect-free GaAs on SiO2 masked exactly oriented Si(111) substrates b | эу а |

|--------------------------------------------------------------------------------------------|------|

| two-step growth technique and its photovoltaic applications                                | 49   |

| 3.2.1 INTRODUCTION                                                                         | 49   |

| 3.2.2 EXPERIMENTAL DETAILS                                                                 | 52   |

| 3.2.3 RESULTS AND DISCUSSION                                                               | 53   |

| 3.2.4 SUMMARY AND CONCLUSIONS                                                              | 63   |

| 3.3 Integration of InGaAs/GaAs double heterostrucure (DH) onto SiO2 masked exactly orier | nted |

|------------------------------------------------------------------------------------------|------|

| Si(111) substrates and its optical property characterizations                            | 64   |

| 3.3.1 INTRODUCTION                                                                       | 64   |

| 3.3.2 EXPERIMENTAL DETAILS                                                               | 66   |

| 3.3.3 RESULTS AND DISCUSSION                                                             | 69   |

| 3.3.4 SUMMARY AND CONCLUSIONS                                                            | 84   |

|                                                                                          |      |

| Chapter 4: Future Work 8 | 85 |

|--------------------------|----|

|--------------------------|----|

| Reference | 88 |

|-----------|----|

| Reference | 00 |

| Acknowledgement 90 |

|--------------------|

|--------------------|

## Figures and Tables

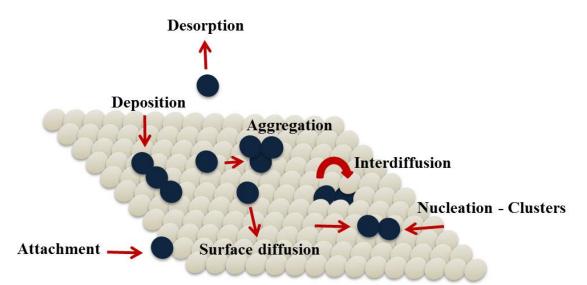

| Figure 1.1: A schematic of basic possible processes during epitaxial growth 11                                             |

|----------------------------------------------------------------------------------------------------------------------------|

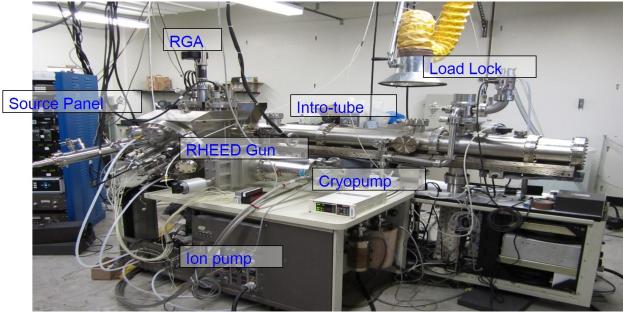

| Figure 2.1.1: The picture of Perkin-Elmer MBE 430 system 21                                                                |

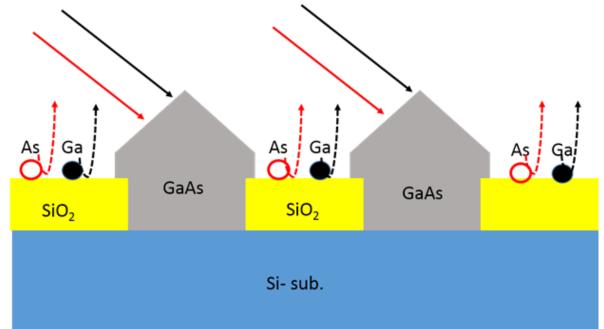

| Figure 3.1.1: The schematic of growth mechanism for selective area epitaxy (SAE) 38                                        |

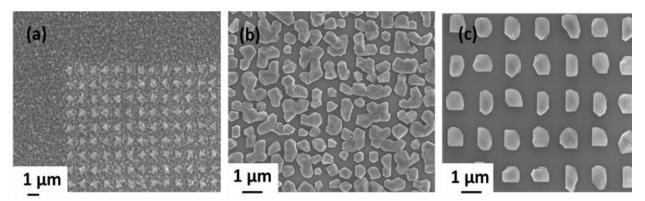

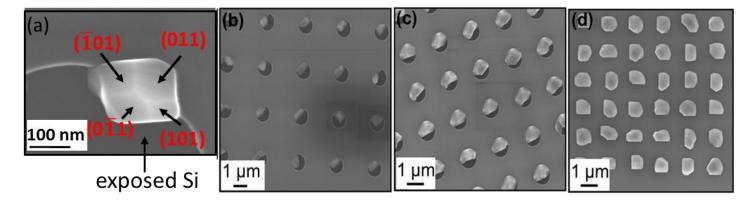

| Figure 3.1.2: SEM images of growth temperature dependent study for SAE 41                                                  |

| Figure 3.1.3: SEM images of time evolution study for SAE grown GaAs nanodisks 42                                           |

| Figure 3.1.4: The SEM images of two adjacent GaAs nanodisks grown at 630 °C 43                                             |

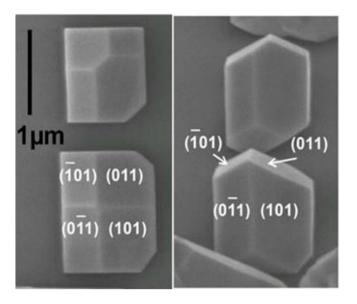

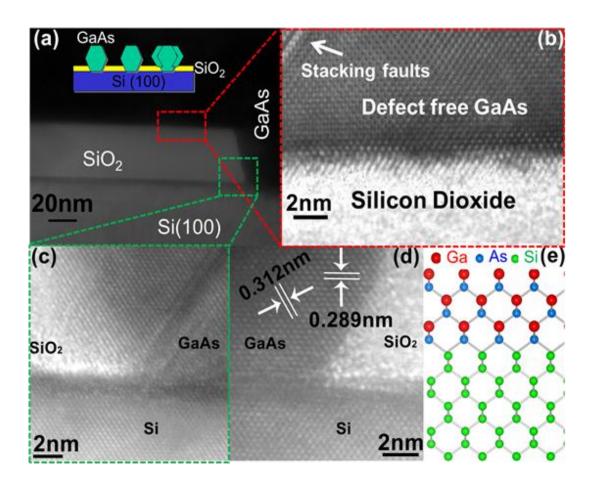

| Figure 3.1.5: The XTEM images of (a) GaAs/Si interface; (b) GaAs laterally overgrown on top of                             |

| SiO <sub>2</sub> showing very few stacking faults (c) left edge, (d) right edge of GaAs/SiO <sub>2</sub> interface showing |

| defect free nature beyond the edge, and (e) GaAs-Si covalent bond diagram 44                                               |

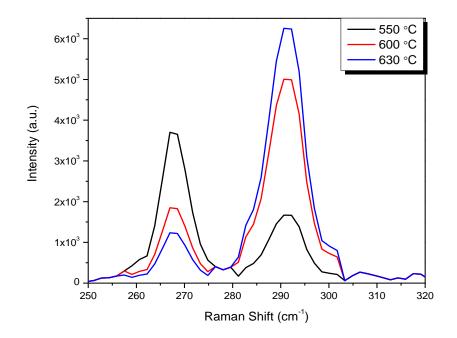

| Figure 3.1.6: The micro-Raman spectra for GaAs nanodisks grown at different growth                                         |

| temperatures 46                                                                                                            |

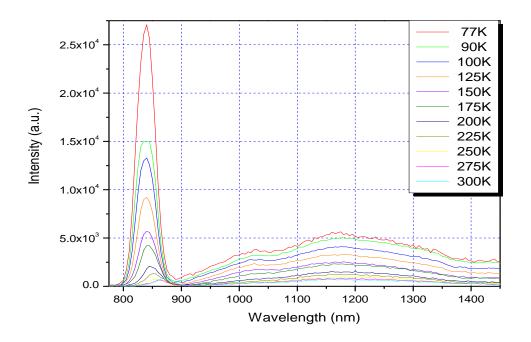

| Figure 3.1.7: The temperature dependent $\mu$ -PL spectra in the temperature range from 77 K to 300                        |

| K 47                                                                                                                       |

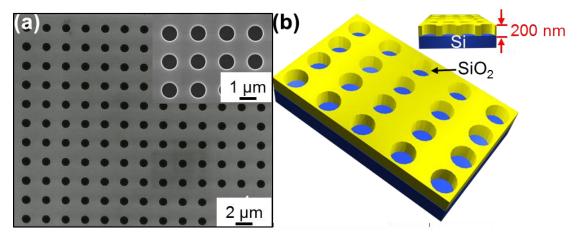

| Figure 3.2.1: (a) SEM images for arrays of patterned holes with 1 µm diameter formed by stepper                            |

| lithography, where the dark circular holes are exposed Si surface. (b) Schematics of tilted and                            |

| cross-section views for patterned Si substrates with a 200-nm-thick SiO <sub>2</sub> mask 53                               |

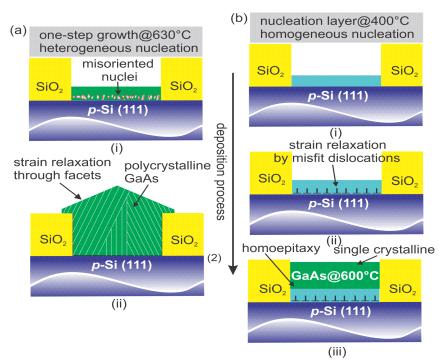

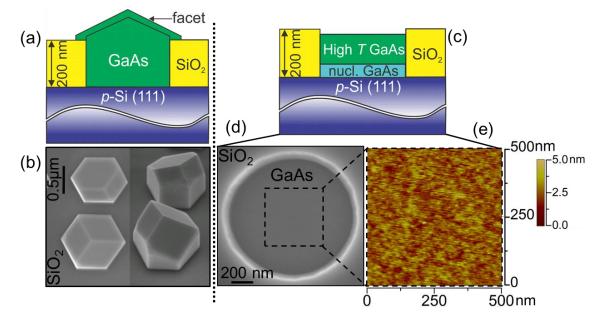

Figure 3.2.2: Schematic illustrations of two different growth schemes at different stages (a) onestep growth model: (i) growth initialization at 630°C through the formation of misoriented nuclei without misfit dislocations, (ii) polycrystallinity of GaAs and the facet formation as the growth continues, (b) two-step growth model: (i) deposition of nucleation layer at 400°C, (ii) introduction of misfit stress and its relaxation through misfit dislocation, (iii) deposition of high quality GaAs Figure 3.2.3: Schematic cross-sectional views of GaAs via (a) one-step and (c) two-step growth scheme. (b) SEM plan-view and 45° tilt-view images for self-assembled GaAs crystals. (d) SEM plan-view image of GaAs within the patterned circular hole. (e) Corresponding 0.5  $\mu$ m × 0.5  $\mu$ m AFM image for the selected region in (d) showing the ultra-smooth surface morphology of GaAs

\_\_\_\_\_

56

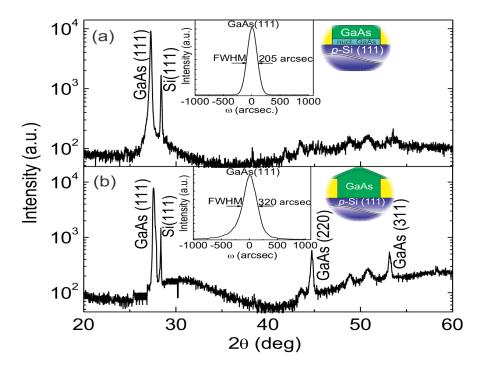

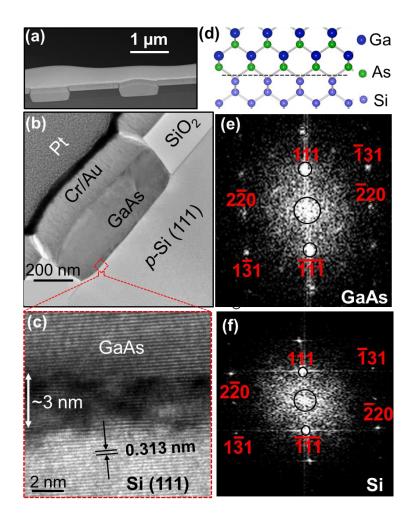

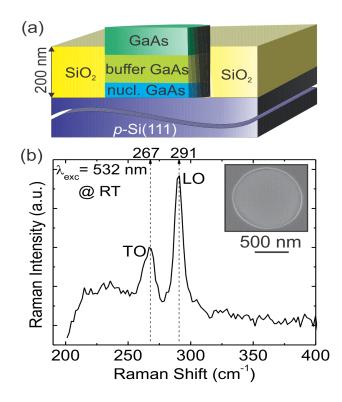

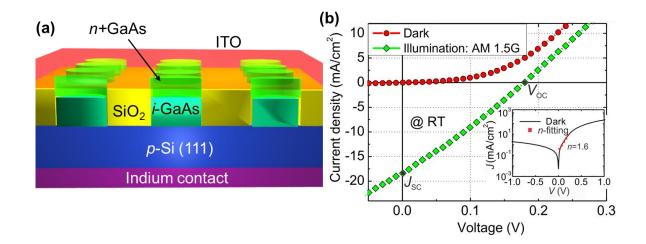

Figure 3.2.4: (a) The XRD omega-2 theta scan for structures grown by (a) two-step growth scheme showing nearly single-crystallinity and (b) one-step (self-assembled) growth scheme showing poly-crystallinity with the presence of GaAs(220) and (311). Two insets show their corresponding rocking curves of GaAs(111) peaks------ 58 Figure 3.2.5: (a) HAADF XTEM image of GaAs/Si(111) grown by the two-step growth scheme. (b) close-up view of BF XTEM image of GaAs/Si(111), demonstrating the confinement of the defects at the GaAs/Si interface and threading-dislocation-free GaAs beyond the interfacing layer. (c) HRTEM image of GaAs/Si(111), indicating that the misfit dislocations are confined within a few nm region near the GaAs/Si interface. (d) GaAs/Si covalent bond diagram. (e) and (f) SAED patterns taken for GaAs epilayer and Si, respectively, indicating the GaAs layers were epitaxially grown on Si(111) substrates following the same single-crystalline orientation----- 59 Figure 3.2.6 (a) Schematic cross-sectional view for a structure consisting of a 150-nm GaAs on top of a high quality GaAs buffer layer. (b) Micro-Raman spectrum for the as-grown structure at RT. The inset shows an SEM image of the as-grown structure----- 60 Figure 3.2.7 (a) Schematic cross-sectional view of the fabricated p-i-n solar cell (b) J-Vcharacteristics of the device under dark and illumination of one sun AM1.5G; the semilogarithmic plot of dark *J*-*V* is shown as inset----- 62

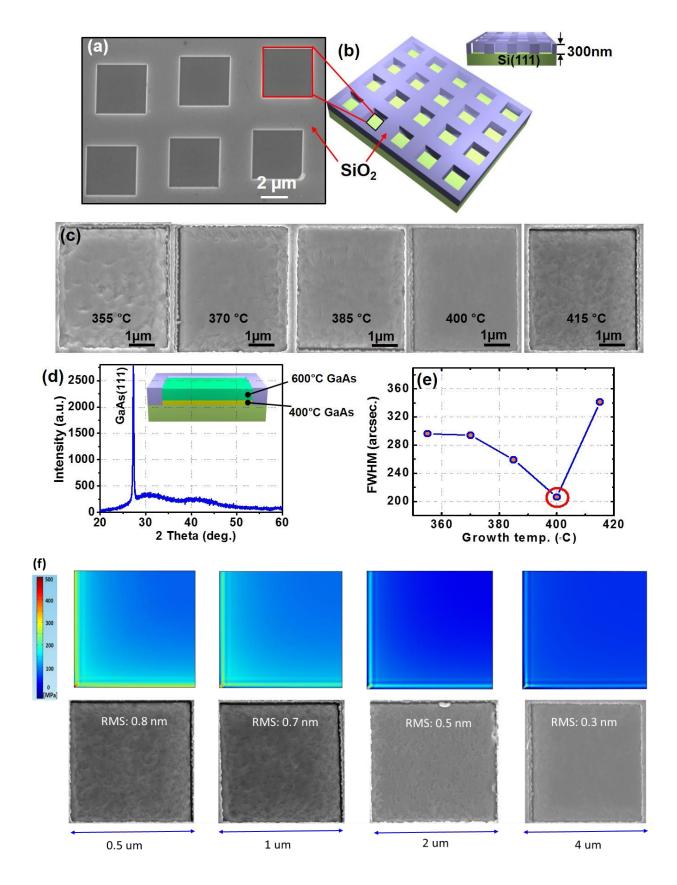

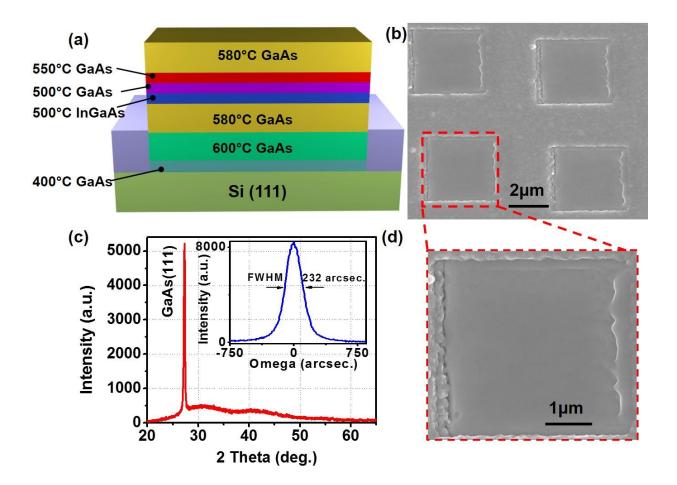

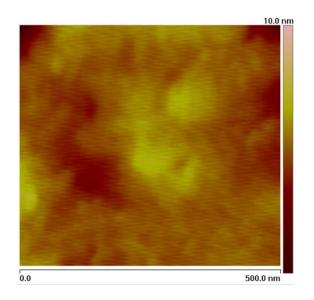

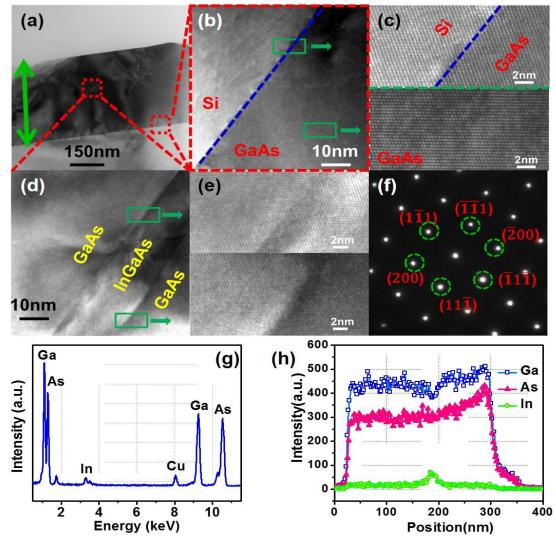

Figure 3.3.1: (a) A plan-view SEM image of  $SiO_2$  masked Si(111) patterned substrate and (b) its schematic. (c) SEM images for the growth temperature dependent GaAs nucleation layer (d) XRD  $\omega$  - 2 $\theta$  scan for the structure in the inset based on the 400 °C grown nucleation layer. (e) FWHM for XRD  $\omega$  –scan on the samples with various growth temperature nucleation layers----- 68 Figure 3.3.2: (a) The schematic cross-section view of the InGaAs/GaAs DH grown based on a Si(111) patterned substrate. (b) A plan-view SEM image of the as-grown InGaAs/GaAs DH. (c) The XRD  $\omega$ -2 $\theta$  scan for the as-grown InGaAs/GaAs DH exhibits the single crystalline nature, and the corresponding  $\omega$ -scan at the GaAs(111) peak is shown in the inset. (d) The close-up view for a single InGaAs/GaAs DH at a patterned window----- 71 Figure 3.3.3: The AFM image of scanned 0.5  $\mu$ m × 0.5  $\mu$ m area from a single patterned window showing the ultra-smooth surface morphology with a RMS roughness of 0.25 nm for as-grown InGaAs/GaAs DH surface----- 74 Figure 3.3.4: (a) The cross-sectional TEM (XTEM) image of the InGaAs/GaAs DH grown on patterned Si(111). The green arrows indicates the vertical range of the whole structure. (b) The XTEM image at GaAs/Si heterointerface showing nonobservable threading dislocations. (c) The high resolution TEM (HRTEM) images shows the abrupt and defect-free GaAs/Si interface (Top), and stacking fault free GaAs epilayer right above the Si (Bottom). (d) Magnified TEM image of the InGaAs/GaAs DH. Although the defects are visible at the GaAs/InGaAs interface, while no threading-dislocation are observed beyond the DH. (The lefthand side of the image is toward the Si surface) (e) The XTEM image for the interface between GaAs barrier layers and the InGaAs layer: Bottom GaAs barrier layer /InGaAs interface (Top), and top GaAs barrier layer/InGaAs interface (Bottom). (The green arrows also indicate the relative locations.)(f) Selective Area Electron Diffraction (SAED) patterns taken for GaAs epilayer, indicating the GaAs layers were

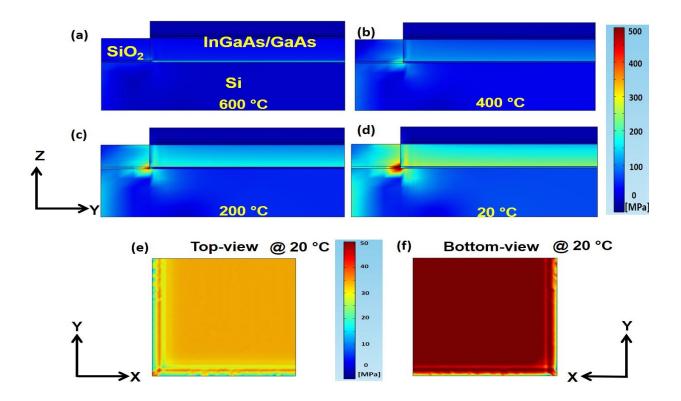

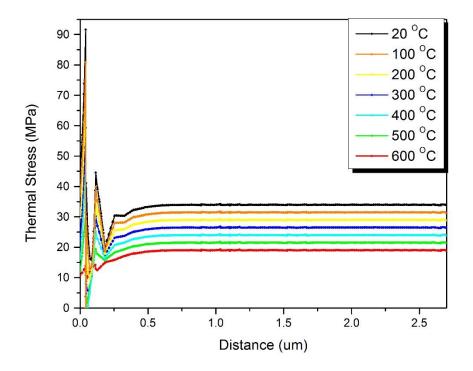

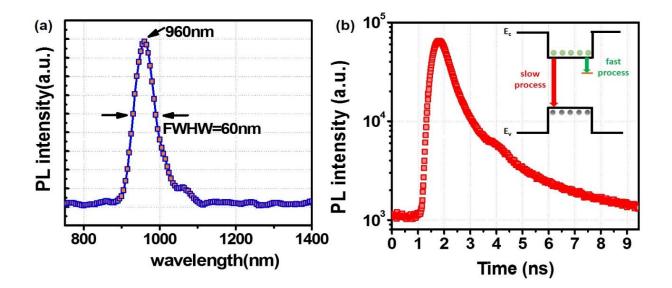

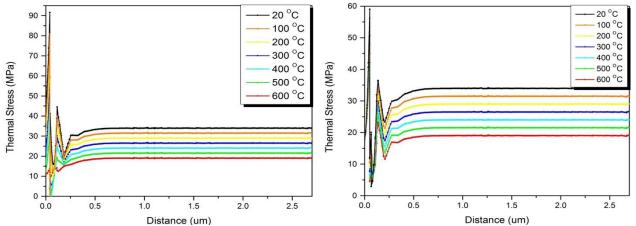

epitaxially grown on Si(111) following the exactly single-crystalline orientation. (g) The energy dispersive spectrscopy (EDS) of the whole InGaAs/GaAs DH. (h) The position dependent EDS line-scan for the whole DH. (The plot starts from the GaAs/Si interface)----- 76 Figure 3.3.5: (a) to (d) The thermally induced stress profile was simulated in COMSOL to display the stress build-up profile during the cooling process (from 700 °C to 20 °C) after the post growth in-situ annealing was finished. The DH simulated in COMSOL was built in the geometrically quarter-symmetric manner for the InGaAs/GaAs DH at a single 4  $\mu$ m  $\times$  4  $\mu$ m patterned window. (e) The thermally induced stress profile for the InGaAs layer (seen from the top). (f) The thermally induced stress profile for the InGaAs layer (seen from the bottom)------ 78 Figure 3.3.6: Thermally induced stress line-scan profile in the diagonal direction (from edge to the center) on the InGaAs layer for all the temperature steps during the cooling process------ 81 Figure 3.3.7: (a) Low temperature (77 K) µ-PL spectrum from InGaAs/GaAs DH n a patterned Si substrate, and (b) The semilogarithmic plot of the TRPL intensity for the ground state emission. Inset: schematic illustration of the carrier dynamics in the DH (the brown horizontal line indicates any types of trap center in the forbidden gap)----- 82

Table 4.1: Material stiffness and thermal properties concerned in the patterned growth scheme

85

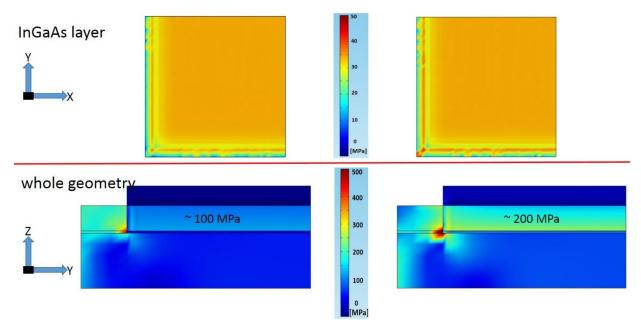

Figure 4.2: Thermal stress distribution in the InGaAs layer (top row) for the Al2O3 masked template (Left column), SiO2 masked template (Right column); and the cross-section views of whole quarter geometry (bottom row) for the Al2O3 masked template (Left column), SiO2 masked template (Right column). The thermal stress distribution displays the Al2O3 masked template is a promising choice to further relax the thermal stress by confining the stress at the corner and dielectric-----86

Figure 4.3: Thermal stress magnitude line-scan from the edge to the center (diagonal direction) in

the 4 um windows for the SiO2 masked template (Left), Al2O3 masked template (Right)----- 86

## **Chapter 1**

## **Background and Introduction**

### **1.1 Background**

Controlled heteroepitaxy and integration of arsenide based III-V compounds onto Si surfaces has been an important enabling technology for high efficiency solar cells and light emitters in satellite and optical interconnect applications. Since the 1980s, III-V compounds epitaxially grown on Si substrates have attracted a great deal of interest due to the monolithic integration of optoelectronic devices with Si-based microelectronics<sup>1-3</sup>. In fact, successful heteroepitaxial growth will not only provide high carrier mobility and direct bandgap III-V materials, but also maintain the advantages of lightweight and low-cost Si substrates with high mechanical strength and excellent thermal management. Clearly, a number of advantages have been claimed for GaAs/Si technology. However, the drawback of the technology is that the GaAs layers monolithically grown on Si are much more defective than those on GaAs wafers, with the dislocation density of  $10^7$  cm<sup>-2</sup> on Si wafers versus  $10^3 \sim 10^4$  cm<sup>-2</sup> typical for GaAs wafers. In addition, Si doesn't provide the semi-insulating property as GaAs does, which will make high speed device fabrication more difficult. Nevertheless, solar cells for satellites or light sources for optical interconnects would be durable applications because the lightweight, robust, higher thermally conductive are the driving forces.

On the other hand, the potential advantage is the capability to use the well-developed Si fabrication technology for high integration level, and to use GaAs based materials in local areas providing special functions. If the GaAs/Si layers can be seamlessly integrated with the Si devices, the combination would remarkably offer unique advantages. Optical interconnect technology would be the best example, and GaAs/Si technology could be used for optical interconnections

between silicon VLSI circuits. Current issues with optical interconnects are hybrid packaging, crosstalk, speed, and power consumption while signals traveling off chips<sup>4</sup>. An additional problem with optical interconnects is the loss associated with inefficiencies in converting the optical power to electrical power<sup>5</sup>. However, the direct combination of monolithically grown GaAs onto Si would solve these problems. To date, researchers have extensively focused on the growth of high quality III-V compounds on Si and accomplished the so-called bottom-up integration. However, obtaining high crystal quality III-V compounds, such as GaAs on Si is still challenging due to anti-phase domain (APD) boundary formation as the result of the polar GaAs growth on non-polar Si system; a high density of threading dislocations generated by 4.1% lattice mismatch along with 62% thermal expansion coefficient mismatch.

The objective of this dissertation is to obtain arsenide based III-V compounds monolithically integrated onto Si surfaces which are APD-free with chemically abrupt GaAs/Si interfaces and possess excellent optoelectronic properties. Because of the ultra-high vacuum nature of molecular beam epitaxy (MBE), we are capable of controlling the initial surface exposure, and apply in-situ high energy electron beam characterization technique to monitor the nucleation and growth process under various experimental conditions.

#### 1.2 The role of MBE in III-V technology

Two epitaxial methods being successfully applied to the growth of high quality III-V compound semiconductors are MBE and metal organic chemical vapor deposition (MOCVD) as well as their variations. MBE and MOCVD are two fundamentally different crystal growth methods: MBE is primarily a non-equilibrium process while MOCVD is a quasi-equilibrium process. In comparison to MOCVD, MBE offers a superior capability in rendering highly complex compositional and

doping profiles required for high performance devices. This strength is the result of the conceptual simplicity of the MBE growth process, where doped layers are grown by depositing the constituent elements and dopants atom by atom. MBE growth can be understood without using either thermodynamics or crystalline physics. The composition of a layer and its doping level only rely on the arrival rate of their sources. The rate of production of the sources can be very easily and accurately controlled by effusion cell temperatures.

An MOCVD, however, is complicated by the need for chemical decomposition of the starting materials at elevated temperatures which introduces more remarkable diffusion and autodoping problems. Furthermore, fine control of atomic abruptness in MOCVD is severely affected by finite gas flow velocities and boundary layer effects. Ideally, MBE is a much simpler process for crystal growth compared to MOCVD, and all of the record-making microwave and optoelectronic devices are grown by MBE. Furthermore, since the performance is of paramount importance, MBE has an edge; there are several devices could only be successfully fulfilled from MBE growth procedures. One example related to the work here is the low-threshold continuouswave (CW) GaAs-on-Si quantum well lasers. Additionally, MBE is a relatively low temperature, non-equilibrium growth process. The defects due to the lattice and thermal mismatch are more likely to be localized and usually will not affect the device operation a few hundreds nm away from the GaAs/Si heterointerface. Until MOCVD can really rival its performance, MBE along with its improved versions is here to stay although its role has been mostly continue to be restricted to research laboratories. For example, Chemical Beam Epitaxy (CBE) and Gas-Source MBE (GSMBE) combining the advantages of MBE and MOCVD can provide a long-term supply of source materials without breaking the vacuum which is very desirable in mass production<sup>6-7</sup>, and they offer easy control of V/III ratio in growing quaternary materials like InGaAsP, which cannot

be easily done in conventional solid-source MBE. The only drawback has been the concerns over the use of highly toxic gases.

On the other hand, the combination of ion beam etching techniques and molecular beams in an MBE system offers an opportunity to complete the material growth, masking, etching, and metallization in a single MBE system without breaking the vacuum. With the help of such a technology is potentially more reliable and cost-effective. In the field of GaAs-on-Si, there have been numerous opportunities and challenges. Presently, almost all high-end microwave and optoelectronic devices have already been dominated by MBE, despite of the difficulty of GaAson-Si growth. The main problems within this field which remain are high defect density at the GaAs/Si interface, the control of interface defects and strain, the improvement of device performance. However, the development of the applications in GaAs-on-Si has been promising. The capability to produce device-quality heteroepitaxial growth for specific device purpose is a non-trivial challenge, and beginning with an issue of lattice constant mismatch, then thermal mismatch and bandgap alignment. The amount of lattice mismatch has the direct relevance to the success in epitaxial growth. Whereas, the mismatch in coefficient of thermal expansion can lead to severe growth/fabrication issues for the defect propagation into the active region of the devices. Last, the bandgap alignment evaluations determines suitability of the materials to fulfill a specific function within the devices. The monolithic integration of the III-V on Si holds a great promise for the future demonstration of the practical integrated III-V optoelectronics on a Si complementary metal oxide semiconductor (CMOS) platform such as the optical connects. Moreover, if successful, it will smoothly shift the optoelectronic market from using relatively expensive intrinsic substrates like GaAs or InP to Si substrates.

#### 1.3 An overview of activities in electrical vs. optical interconnects

As aforementioned applications of III-V on Si integration indicate, optical interconnects could be the technology with the impactful importance. Future ultra-speed computers will process tremendous amount of data to meet the ever growing demand in science and technology. The throughput of a computer has to be increased dramatically from the current level. The researchers have predicted that the chip-to-chip bandwidth demand is likely to jump to 100 Gb/s or more in the near future<sup>8</sup>, which could create enormous difficulties even for the latest VLSI microelectronic technology<sup>9-10</sup>. The parasitic impedance of copper interconnects is starting to place restrictions on scaling for higher throughputs. Therefore, electrical interconnects and switching speed have been identified as the two major bottlenecks to throughput of computing systems. We cannot take full advantage of the development of high-speed Si and GaAs switching and parallel architecture, unless we can solve the interconnect problem. However, using photons rather than electrons to communicate between chips has the potential advantages of large bandwidth, low crosstalk, and low power consumption<sup>5</sup>.

A modern computing system functions by bringing a large number of separate elements to bear on a common problem. Coordinated operations of the elements requires a large amount of communication among them through many long wires. Variability in manufacturing and fluctuation in a system causes the elements of a system to differ from one another in their response to signals. Therefore, signals must be large enough to be interpretable by any element of the system. This means high-power dissipation over a finite length of interconnections. Thus, fitting a complex interconnection pattern into a small space become the most limiting factor in a computer system and the other being the switching speed of an element. Currently, the study of communication and information is aimed at providing the largest bandwidth and lowest power dissipation in a system. In general, we have been faced with a few fundamental limits unique to a computing system. First, the nature of a computing system which requires more than two streams of information to interact indicate that the times of arrival of information at a device are extremely important. Second, the coding of data streams that allows efficient use of a communication channel capacity cannot be applied to a computer because the methods of information processing through the interaction of two or more streams of coded data are not known yet. Experimentally, the packaging of microelectronics presents an enormous problem for a system designers.

However, deciding between electrical and optical interconnects is a complex task. Although fiber optic transmission techniques have some intrinsic merits, the existing computer architectures are based on electrical interconnects and can seriously limit the application of optical interconnects. In general, insertion of optical interconnects as a direct one-to-one replacement of point-to point electrical interconnects doesn't offer remarkable advantages for current computer systems. This is because: (1) overall system reliability would decrease because of the use of hybrid optical components, (2) overall system power consumption can increase because of the inefficiency of the optical-to-electrical conversion, and (3) increased costs due to the increase in packaging complexity. The cost factor can be offset by higher performance; the high-power consumption can be reduced with sub-milliampere threshold lasers and high quality photodetectors, but the system reliability issue cannot be solved easily. It's therefore desirable to use as few optical interconnects as possible, in the most necessary and effective places. One area where optical interconnects can improve system performance is where large signal fan-outs are required over long distance and at high speeds. High electrical fan-outs are common at the intra-chip and interboard level, including data bus, control lines, and clock lines. If the distance between two elements on a transmission line is much less than the wavelength of the signal, the entire fan-out

system can be viewed as a single transmission line with a load increasing with distance. The impedance of a transmission line is

$$Z = \sqrt{\frac{L}{C}}$$

Where L and C are the inductance and capacitance per unit length. Without fan-out, the unloaded line has an impedance of

$$Z_0 = \sqrt{\frac{L_0}{C_0}}$$

With loading, the capacitance per unit length is changed to

$$C = \frac{C_0 C_l}{C_0 + C_l}$$

Where  $C_0$  and  $C_l$  are unloaded and distributed loading capacitance due to fan-outs. And we can get the impedance on the line a distance d away from the starting point

$$Z(d) = \frac{Z_0}{\sqrt{1 + C_{load}/C_0 d}}$$

Where  $C_{load}$  is the total load capacitance, d is the transmission line length,  $C_0$  is the intrinsic line capacitance. As a result, the driving power has to be increased to maintain a constant signal level. Another effect due to increased fan-out is the propagation delay. Since the velocity of propagation is given by

$$v = \frac{1}{\sqrt{LC}}$$

We have

$$t(d) = t_0 \sqrt{1 + \frac{C_{load}}{C_0 d}}$$

The increase in propagation delay is due to the charging-up of capacitive element at each fan-out. While the increase in driving power is not fundamentally limiting since the driver lines can be designed to carry enough power, the propagation delay decreases the critical line length  $l_c$  which is the distance that an electrical signal can travel without causing any signal skew<sup>5,8</sup>.

The fundamental difference between electrical and optical fan-outs is that in the case of electrical fan-outs, the signal travels in the media surrounding the transmission line usually made of the ceramic or polyimide circuit board. Whereas, for optical fan-outs, the signal travels in a guided media, the optical fiber or silica waveguide. In an optical fiber, the effect of capacitive loading doesn't exist since no conductor is used. The number of fan-outs for optical interconnects is limited by the available power to the detectors. The amount of power available to the detectors is determined from the source power and the distributed losses throughout the system. Optical fan-out is achieved by power splitting of a channel. The power should be split equally among n detectors. In addition to the distributed loss, there is an excess loss due to the imperfect coupling. Let the sensitivity of detectors used in the system be  $P_{min}$ , source power be  $P_{source}$ , the total power loss be; then the maximum number of optical fan-outs can be calculated from

$$P_{source} + \alpha = P_{min}$$

Accordingly, the optical fan-outs can offer a higher fan-out speed since there is no additional propagation delay, and they don't require increased driving power. However, unterminated electrical transmission lines are limited by the critical line length (given the total  $C_{load}$  for the entire system, the line length dominates), while terminated transmission lines are limited by the density of fan-out (given the total line length, the per unit length capacitance dominates) along the line. Hence, it's clear from the analysis above that optical interconnects should be used to implement data buses and distribution structures within computing systems

which are currently limited by electrical interconnects.

#### 1.4 Heteroepitaxial Growth of III-V compound semiconductors on Si

In order to realize the monolithic integration of III-V material on silicon substrate, highquality III-V compound buffer layers must be grown on a Si substrate. However, heteroepitaxy between III-V thin films and silicon substrates induces a large strain energy in the thin films. Due to the large lattice and thermal mismatches, this large strain is released by the formation of structural defects and dislocations in the III-V material. Therefore, the density of structural dislocations should be reduced to an acceptable level or even defect-free structures as an ideal goal, since the performance of light emitting devices is deteriorated and is degraded due to the irradiative recombination processes occurring at defect centers. However, structural-defect-free III-V compounds have not been grown on Si substrates by lattice-mismatched heteroepitaxy regardless of a great deal of research.

The key challenges in the heteroepitaxy of semiconductors, relative to the development of useful optoelectronic devices, are the control of the growth morphology, stress and strain introduced by mismatched system and crystal defects. The purpose of this chapter is to review the properties and challenges of the epitaxial integration of III-V semiconductors on silicon substrates that bear on these aspects of heteroepitaxy, including crystallographic properties, elastic properties, surface properties as well as the different types of structural defects.

The term "epitaxial" is applied to a thin film grown atop the crystalline substrate in ordered fashion that atomic arrangement of the thin film accepts crystallographic structure of the substrate. Epitaxial growth is one of the most important techniques to fabricate various "state of the art" optoelectronic devices. Modern devices require very sophisticated structures, which are composed

of thin layers with various compositions. Quality, performance and lifetime of these devices are determined by the purity, structural perfection and homogeneity of the epitaxial layers<sup>11</sup>. Epitaxial crystal growth resulting in epitaxial layer perfection, surface flatness and interface abruptness depend on a number of factors like: the epitaxial layer growth method, the interfacial energy between substrate and epitaxial thin film, as well as the growth parameters - thermodynamic driving force, substrate and layer misfit, substrate misorientation, growth temperature, etc.

Regardless of the growth technique, atoms and molecules are delivered to the substrate surface, and a large fraction of these species adsorb on the surface. Once adsorbed, there are three things that can happen to an adatom. It can either form a strong chemical bond to the surface where it is trapped, diffuse onto the surface to find an energetically preferred location prior to strong chemical bonding or desorb. Once adsorbed chemically, the adatoms can diffuse on the surface and this diffusion can be highly anisotropic, depending on the symmetry and nature of the surface<sup>12</sup>. These adatoms diffuse on the surface till they either desorb from the surface, find another adatom or nucleate to an island, attach or aggregate to an existing island or step, diffuse onto the surface or react at a defect site. Diffusion onto the surface, or interdiffusion can be significant under certain growth conditions<sup>12</sup>. The main surface process that occur during epitaxy are schematically shown in Fig 1.1 with different atomistic processes. The extent of interdiffusion can be thought as solubility of one material into other and clearly has strong dependence on the material system. On the other hand, the reactions at defect site are often important. For example, reactions at step edges (a defect with respect to perfect surface) are the foundation of step-flow growth<sup>11</sup>.

The formation of islands and the attachment of atoms to existing structures and clusters are important in the formation of self-assembled islands. When diffusing adatoms impinge on each other, they will nucleate and form an island. Adatoms that directly impinge to on an island can either incorporate into the island or lead to the next layer growth, depending on the surface potential and energy. As the island continues to grow further and possibly migrate, they can find other islands and coalesce into larger islands<sup>12-13</sup>.

Understanding kinetics, thermodynamics and how they interact and compete with each other would enables us to know how to control the growth of thin films. However, in MBE growth, the molecular beams from different sources intersect each other at the substrate surface, where the crystallization processes take place. A series of surface processes take place during MBE growth which are schematically summarized in figure 1.1. The surface processes occurring during MBE growth are characterized by a set of relevant kinetic parameters that describe them quantitatively.

Figure 1.1: A schematic of basic possible processes during epitaxial growth.

The arrival rate is described by the flux of the arriving species and gives the number of atoms impinging on the unit area of the surface per second. Impinging atoms with temperature  $T_i$  onto substrate surface, which has temperature  $T_s$ , usually lower than  $T_i$  at different positions are with different kinetics energies. Depending on the atom energy and the position at which it hits the substrate surface, the impinging atom could re-evaporate immediately, carrying with it an energy corresponding to temperature  $T_e$  (exchange energy) with atoms of the substrate at  $T_s$ . A

description of this process is possible by defining the thermal accommodation coefficient ( $\alpha$ ) as<sup>14</sup>:

$$\alpha = \frac{T_i - T_e}{T_i - T_s}$$

When  $T_e$  equals  $T_s$ , the accommodation coefficient is unity. Thus, it is a measure of the extent to which whether the adatoms reach the thermal equilibrium with the substrate. Furthermore, the sticking coefficient ( $S_c$ ) is defined as the ratio of the number of atoms which adsorb ( $N_{ads}$ ) or stick to the substrate surface, to the total number of atoms (( $N_{tot}$ ) that impinge upon substrate surface during the same period of time, and expressed as below<sup>14</sup>:

$$S_c = \frac{N_{ads}}{N_{tot}}$$

In many cases  $S_c$  is less than unity and it may be a small fraction in cases when the adsorption energy of atoms on the substrate is low, or the substrate temperature is high. Assuming  $\alpha$  is unity, all the impinging atoms are accommodated on the substrate surface and achieve thermodynamic equilibrium. However, this doesn't mean they will stay on the adsorbed sites permanently. The adatoms still have a finite probability related to the substrate temperature of acquiring sufficient energy to overcome the adhesive forces and leave the substrate<sup>14-15</sup>. If aggregation of adatoms doesn't occur, all the adatoms will eventually be re-evaporated. Thus, the  $S_c$  could almost be zero even when  $\alpha$  is unity. There are two main types of adsorption that can occur during MBE. The first is physical adsorption referring to the case where there is no electron transfer between adsorbate and adsorbent by forming a van der Waal's bond with a surface atom. This type is so-called "physisorption". The second type resulted from forming a covalent or ionic bond with a surface atom, referring to the case with electron transfer, i.e., chemical reaction, taking place between adsorbate and adsorbent. And this is so-called "chemisorption"<sup>13-15</sup>.

In addition, the rate at which adatoms are adsorbed to the surface can be described by an

exponential law<sup>15</sup>:

$$R_{ads} \propto v_a e^{-E_{ads}/_{kT}}$$

Where  $v_a$  is the adsorption,  $E_{ads}$  describes the necessary energy to overcome the electrostatics potential, k is Boltzmann constant and T is the substrate temperature<sup>14-15</sup>. However, most substrates have complicated reconstructions and the bonding is highly directional. Therefore, the probability of adsorption to some sites is higher than other. Assuming defect-free surfaces, a number of theoretical and experimental works has been carried out to find the most stable adsorption sites. Adsorbed atoms may diffuse from one site to another via thermally activated hopping, the diffusion rate which can also be expressed by:

$$D \propto a^2 K_s \propto a^2 e^{-E_d/_{kT}}$$

Where  $K_s$  is the site-to-site hoping rate,  $K_s$  is the effective hopping distance between sites,  $E_d$  is the diffusion energy, and T is the substrate temperature<sup>13, 15-16</sup>. Because of the complicated nature of the most surfaces, diffusion is a complicated process. It should be pointed out that diffusion is the process responsible for the degree of smoothness of the grown film at a fixed growth rate. Furthermore, atoms meet and bond with each other after diffusion forming various size clusters are dependent on the deposition/growth rate.

Another crucial factor is the temperature of the substrate T. Increasing the temperature beyond the certain limits leads to desorption of the molecules back into the chamber vacuum. In thermodynamics, the desorption rate increases exponentially and the actual growth rate decreases accordingly.

$$R_{des} \propto f(\theta) e^{-E_{des}/_{kT}}$$

The desorption rate  $R_{des}$  is dependent on the degree of coverage  $f(\theta)$  and the desorption energy  $E_{des}$ <sup>15</sup>. However, the slow growth rates allow the adsorbed molecules to migrate on the substrate to a proper nucleation site for the growth. Notably, nucleation on smooth surfaces is not energetically favored. The most energetically favorable sites are those on terraces and step edges on the growing surface as more chemical bonds tend to bond to neighboring sites at these locations.

Growth parameters like substrate temperature T, growth rate, and the V/III ratio have to be chosen appropriately for the desired application. The V/III ratio has a similar impact on the layer growth as the substrate temperature does. High values shorten the migration length of the group III species because they can more easily find a nucleation sites and then incorporate into the crystals. However, this can also deteriorate the thin film quality due to the tendency of islands formation. On the other hand, the desorption of group III species is counteracted by the higher V/III ratio due to the lower sticking coefficient under the high V/III ratio. Low values, otherwise increase the migration length, but also enhance the probability of desorption. The growth rates are thereby determined by the group III fluxes and the desorption. In the MBE growth, the substrate surfaces are held in UHV chambers while being exposed to molecular beams of the growing material. Meanwhile, the thermodynamics and kinetic factors determine the growth mechanisms. The classical thermodynamic approach to epitaxial thin film growth leads to the definition of the so-called growth modes. This thermodynamics approach is used to determine growth modes of thin films close to equilibrium. The growth mode describes the nucleation and growth processes. Moreover, there is a direct correspondence between the growth mode and the film morphology, which gives the structural properties such as perfection, flatness and interface abruptness of the layers. The kinetic description of growth in which the film morphology is the result of the microscopic path taken by the system during growth. This path is determined by the displacement

rates of the single atom, cluster, or molecule as compared to the deposition, desorption, and dissociation rates. It is determined by the kinetics of the transport and diffusion processes on the surface<sup>13, 16-17</sup>.

The competition between the film and substrate surface energies resulting from the growth dynamics and growth conditions determines the growth mode of the epitaxial growth process close to equilibrium. However, the MBE growth process is a kinetically dominated process and thermal equilibrium conditions are only partially fulfilled. Thin films grown by MBE technique are usually not in thermodynamic equilibrium, but kinetically. This is due to the limited surface diffusion, the deposited material cannot completely rearrange itself to minimize the surface energy. The supersaturation of the deposited species leads to a large nucleation rate, and kinetics will lead to the occurrence of different growth modes<sup>15, 17</sup>. Therefore, the behavior of deposited species will be determined by a number of kinetic parameters. Among them, the diffusion coefficient ( $D_S$ ) is probably the most important parameters. It determines the average distance an atom can travel on flat surface before being trapped. This distance is the surface diffusion length ( $l_D$ ) and can be defined by

$$l_D = \sqrt{D_S \tau}$$

Where  $\tau$  is the dwelling time before re-evaporation. And the surface diffusion coefficient is generally expressed as<sup>16</sup>:

$$D_S = va^2 e^{-E_A/_{kT}}$$

Where  $E_A$  is the activation energy for diffusion, v is the frequency of diffusion, and a is the characteristic diffusing distance. From the equation above, it is clear that deposition temperature is important because it controls the diffusivity of the adatoms. Therefore, the growth modes in real systems far from equilibrium will be controlled mostly by these kinetic factors and partially by the

thermodynamic factors.

Experimentally, the distinction between three classical growth modes is well known and classified into three growth regimes: Frank-van der Merwe (FM) (layers growth mode), Volmer-Weber (VW) (islands growth mode) and Stranski-Krastonov (SK) (mixed growth mode for layers and islands). The study of the thin film growth typically involves the deposition of a controlled amount of atoms onto a well characterized crystalline substrate at a prescribed set of growth conditions. In the case of Frank-van der Merwe (FM) (layer by layer growth mode): Layer growth is observed when the sum of the binding energy (as known as, the surface energy) for the deposited film/substrate interface and substrate itself is larger than that of the deposited film particles. In this sense, a uniform monolayer of deposited material can form a planar 2D sheet as long as the thin film surface energy is decreased toward the bulk crystal value. Then the layer growth is sustained. However, during FM growth mode, a new layer is nucleated only after the completion of the layer below.

On other hand, while there is no strong bonding between film and substrate, 3D-islands are being formed. The film dose not wet the substrate because this will lead to an increase in the total surface energy. This growth mode is referred to as Volmer-Weber (VW) growth mode. It occurs when the binding force between the particles of the deposited material stronger than the forces between the material and the substrate. In the heteroepitaxial growth, the so-called Stranski-Krastanov (SK) growth mode can also occur. SK mode is considered as the combination between the FM and VW growth modes, and the former growth modes are merged in this case. The layerto-island growth more results from significant misfit dislocations between the thin film and the substrate. the growth mode changes from layer by layer to island growth. During heteroepitaxial growth, the lattice mismatch between the substrate and the deposited film gives rise to biaxial strain, resulting in an elastic energy that grows with the increasing layer thickness. Misfit dislocations at or near the film/substrate interface will be formed if the layer thickness exceeds a critical thickness. At this thickness, it is thermodynamically favorable to introduce dislocations because the elastic energy released by the dislocations becomes comparable to the increase in the interfacial energy. In other words, misfit dislocations are necessarily to be introduced to release the strain through defects formation<sup>17</sup>.

The concept of monolithically epitaxial integration of III-V compound semiconductors onto Si substrates is not straightforward but very challenging due to the significant differences in basic material and crystal properties that exist between elemental silicon and III-V compounds. Heteroepitaxy differs from homoepitaxy in that it requires the nucleation of a new phase on a foreign substrate. Because of this, the surface chemistry and physics play important roles in determining the properties of heteroepitaxial deposits, including structural and electrical characteristics, defect densities and structure, and the layer morphology<sup>11,15</sup>. However, the heteroepitaxy is classified for three main types based on the lattice constants of the two crystalline materials, lattice-matched heteroepitaxy for the same lattice constants and lattice-mismatched heteroepitaxy but elastically strained like InGaAs on GaAs for different lattice constants, and partially relaxed as in the case of the growth of GaAs on silicon with high misfit dislocation density. The heteroepitaxy process is widely used, not only for research but also for manufacturing semiconductor devices such as lasers, light emitting diodes (LEDs) and transistors.

#### 1.5 Challenges of Heteroepitaxial Growth of GaAs on Si

Growing GaAs on Si presents a notable materials problem. There are essentially three difficulties for growing high quality bulk GaAs/Si films. First the 4% lattice mismatch between

GaAs and Si leads to a high dislocation density. While theoretically these dislocations could all be confined at the GaAs/Si interface, in actuality,  $10^7 - 10^8$  cm<sup>-2</sup> dislocations would propagate to the GaAs surface. These dislocations can be modeled as lines of point defects (threading dislocations), and will thus lead to higher number of deep level traps, reduced carrier lifetime, and reduced carrier mobility. Various techniques have been examined to attempt to improve the quality of the GaAs/Si interface, each usually claiming to cause an order of magnitude reduction in dislocation density. These two techniques are universally accepted as useful. The first is increasing the thickness of the buffer layer deposited below the actual device layers. As the buffer GaAs/Si thickness is increased up to several um thick<sup>18-21</sup>, more defects have the chance to annihilate each other, leading to higher quality material and thus higher device performance. The second, and more successful technique to improve the GaAs layer is thermal annealing<sup>22-24</sup>. In-situ and ex-situ techniques have been demonstrated to be effective by a number of groups. The results demonstrated by the groups suggested that thermal cycling combined with in-situ annealing with AlGaAs caps are most effective in removing the dislocations<sup>25-26</sup>. While the literature is unanimous on the improvements produced in GaAs/Si by using thermal cyclic annealing, there is confusion regarding the effects of strained layer superlattices (SLS). SLS are designed to bend dislocations, either to leave the crystal or to react with nearby dislocations. And they are supposed to work better in cooperation with thermal cycling. However, these techniques are not cost-effective and would even complicate the growth procedures.

The second problem is the growth of polar GaAs on the non-polar Si substrates. This can potentially lead to growth of antiphase domain disorders (APDs). At the single-atom steps of the Si surface, antiphase domain boundaries consisting of As-As and Ga-Ga bonds are easily formed. However, misorienting the substrate from (001) axis by a few degrees (typically  $2 - 4^{\circ}$ ) will eliminate the antiphase domains from thick films. The standard model explain the elimination of these domains is the presence of the double-atom steps. However, it is clear from a number of reports<sup>27-28</sup> that the standard cleaning process may actually lead to man-atom supersteps rather than a uniform distribution of double-atom steps. Since GaAs/Si is grown free from antiphase domains using these techniques, it's probable that another mechanism is responsible for the reduction of antiphase domains. self-annihilation is one proposed model<sup>29</sup>. Although the antiphase domain problem has been solved through the use of off-axis substrates, the requirement of using these vicinal substrates may cause problems in the Si devices.

The final problem is the 62% thermal expansion coefficient mismatch between GaAs and Si. This limits the thickness for GaAs/Si lasers and durable LEDs. Since the quality of the GaAs/Si layers improves monotonically as thicker layers are grown, this limit is of more than research importance. It may be that InP and InGaAs layers, despite an even larger lattice mismatch than GaAs, are better suited to heteroepitaxial growth since their thermal expansion coefficients are better matched to Si's. Sapphire substrate on the other hand, are well matched in thermal expansion to GaAs, although GaAs/Si/sapphire material is of poorer quality than GaAs/Si because of the poorer Si on top of the sapphire. The other alternative would be the wafer bonding technique, however, this technique will lead to some mechanical defects at the interface and low-yield in productivity.

Recently, the patterned growth scheme has been demonstrated as an excellent alternative to obtain high quality GaAs and other materials on silicon dioxide (SiO<sub>2</sub>) patterned Si substrates<sup>30-<sup>33</sup>. Most importantly, this growth scheme can effectively mitigate these three major mismatch problems<sup>34-36</sup>. Instead of misoriented (vicinal) Si substrates, this patterned growth approach using exactly Si substrates could also effectively reduce the probability of forming high-density APD</sup> boundaries. Based on the finite size growth nature in the patterned growth scheme, the strain induced by the mismatches in lattice constants and coefficient of thermal expansion will be mitigated remarkably. Hence, the exactly oriented Si substrates was chosen as the starting material in my work to carry out the patterned growth scheme for the III-V to Si integration in the MBE chamber.

#### **1.6 Dissertation outline**

This dissertation will describe my work based on the patterned growth scheme by MBE to fulfill:

(1) Precise positioning and low defect density selective area epitaxy for self-assembled/catalystfree GaAs nanodisks on SiO<sub>2</sub> masked exactly oriented Si substrates.

(2) High-quality and defect-free GaAs on  $SiO_2$  masked exactly oriented Si(111) substrates by a two-step growth technique and its photovoltaic applications.

(3) Integration of InGaAs/GaAs double heterostrucure onto SiO<sub>2</sub> masked exactly oriented Si(111) substrates and its optical property characterizations.

# **Chapter 2**

# **Experimental Techniques**

## Introduction

This chapter discusses the major experimental techniques used in this study. They are molecular beam epitaxy (MBE), scanning electron microscopy (SEM) and energy dispersive spectrum (EDS), atomic force microscopy (AFM), transmission electron microscopy (TEM), X-ray diffractometry (XRD), photoluminescence (PL) and time-resolved photoluminescence (TRPL).

### 2.1 molecular beam epitaxy (MBE)

The critical experimental apparatus used in this study is the Perkin-Elmer MBE 430 system, as shown in figure 2.1.1. In addition to the main growth chamber with three ultra-high

Figure 2.1.1: The picture of Perkin-Elmer MBE 430 system.

vacuum (UHV) pumps – ion pump, titanium sublimation pump and cryo-pump, the key system components include substrate manipulator holding the samples, and the source flange containing

various solid source elemental effusion cells (As, Ga, In, Al, Si and Be as n- and p-type dopants respectively).

The vacuum system consists in a stainless-steel growth chamber, UHV-connected to an intro-tube chamber as shown in the figure 2.1.1, where substrates are degassed prior to growth, and a load-lock chamber for transfer to and from air. All the components of the growth chamber must be able to resist bake-out temperatures of up to 200 °C for extended periods of time, which are necessary to minimize outgassing from the internal walls. The pumping system must be able to efficiently reduce residual impurities to a minimum. Typical MBE growth rates for III-V type semiconductors are of the order of 1ML/sec, obtained for group III partial pressures of  $\sim 10^{-6}$  torr. With atomic densities in the crystal of about  $10^{22}$  cm<sup>-3</sup> meaning that to reduce the impurity concentrations below  $10^{15}$  cm<sup>-3</sup>, the impurity partial pressures must be reduced below ~ $10^{-13}$  torr, assuming a unity sticking coefficient. In practice, base pressure is reduced to the  $10^{-11} \sim 10^{-12}$  torr range, with the residual gas being essentially H<sub>2</sub>. The pumping system usually consists of ion pumps, with auxiliary Ti-sublimation and cryogenic pumps, for the pumping of specific gas species. On the other hand, liquid N<sub>2</sub> cryoshroud surround internally both the main chamber wall and the source flange. Since MBE is a cold wall technique, cryoshroud prevent re-evaporation from parts other than the hot cells. Besides, they provide thermal isolation among the different cells, as well as additional pumping for the residual gas.

Effusion cells are the key components of an MBE system, because they must provide excellent flux stability and uniformity, and material purity. Furthermore, being the parts that must withstand the highest temperatures (up to 1400 °C) for the longest periods, they are often responsible for machine downtime. Therefore a careful choice of elements, materials and geometry must be taken. The cells are placed on a source flange, and are co-focused on the substrate heater,

to optimize flux uniformity. There are four major parts of a cell: (1) The crucible is usually made of pyrolitic boron nitride, which can stand temperatures of up to ~1300°C without appreciable degassing. Its shape can be cylindrical or conical with different tapering angles, depending on the material to be evaporated. Its size depends on the material to be evaporated as well, and has to be big enough to provide several months of operation before the depletion of the material. (2) Ta filament is in charge of heating, while (3) multiple Ta foils provide heat shielding. (4) A thermocouple is located in an appropriate position in order to measure the material temperature; temperature regulation is provided by high-precision PID regulators. A mechanical or pneumatic shutter, usually made of Ta or Mo, is placed in front of the cell to trigger the flux. The shutters must be operated much faster than the growth rate, and should be computer-controlled to provide reproducible growth cycles, especially for superlattices. Besides, they must be designed not to outgas when heated from the cells, and not to constitute an appreciable heat shield, giving rise to flux transients after opening. An important source type for evaporation of group-V elements is the so-called cracking cell. In this cell, the material is first thermally evaporated (in the form of tetramers) from a large-capacity reservoir; afterwards it passes through a hotter cracking zone in a tube, where molecules are dimerized (As<sub>4</sub>  $\rightarrow$  As<sub>2</sub>).

Speaking of the growth of GaAs, the growth must be performed within a range of substrate temperatures and beam fluxes such that the surface chemistry favors stoichiometric growth. Fortunately, such conditions are well established. For a broad temperature band ranging from below 500 °C up to ~ 680 °C, the Ga atoms sticking coefficient onto GaAs is unity, that is, all the Ga atoms impinging upon the GaAs surface will stick). Whereas at these substrate temperatures, the As-As bond is unstable so that As will only bond to Ga. If the beam flux ratio is excessive such that As flux is much greater than Ga flux, stoichiometric GaAs is achieved, since the As flux in

excess of Ga flux will not stick. The growing crystal arranges itself into its lowest energy state which is the desired stoichiometric GaAs zincblende crystal structure. In practice, a flux ratio ~10:1 (As : Ga) is usually used for MBE growth. Much higher ratios lead to higher defect density, whereas lower flux ratios may lead to a Ga-rich film. As far as substrate temperature goes, the highest temperature feasible (limited by Ga desorption) is usually the best, as this limits the incorporation of impurity atoms into the film. The exception to these rules is in the case of heavy doping Be doping, where a lower temperature and higher As flux is usually used to combat the tendency of Be to diffuse rapidly in GaAs. Furthermore, since Ga atom has unity sticking coefficient, the growth rate can be directly calculated from the Ga flux and is directly proportional to the Ga flux.

MBE is as much a surface science technique as it is a growth technique. The UHV nature of MBE provides extremely clean, atomically abrupt surfaces which can be probed by a variety of electron beam techniques. Chief among these is reflection high energy electron diffraction (RHEED). RHEED is a glancing angle electron diffraction technique whose diffraction patterns reflect primarily the surface periodicity due to the shallow beam angle. If electrons interact only with the first atomic layer of a perfectly flat and ordered surface, the three-dimensional reciprocal lattice points degenerate into parallel infinite rods. In the resulting Ewald construction the intersection of the Ewald sphere (with a radius much larger than the inter-rod spacing for typical RHEED energies) consists therefore of a series of points placed on a half circle. In reality, thermal vibrations and lattice imperfections cause the reciprocal lattice rods to have a finite thickness, while the Ewald sphere itself has some finite thickness, due to divergence and dispersion of the electron beam. Therefore, even diffraction from a perfectly flat surface results in a diffraction pattern consisting in a series of streaks with modulated intensity, rather than points. If the surface is not flat, many electrons will be transmitted through surface asperities and scattered in different directions, resulting in a RHEED pattern constituted by many spotty features. Therefore, a first important information provided by RHEED regards the flatness of a surface. Furthermore, it is evident that diffraction from an amorphous surface (such as an oxide on top of a semiconductor) gives no diffraction pattern at all, and only a diffuse background will result. This is important, for example, for evaluating oxide desorption when a new substrate is initially heated up prior to growth in the MBE chamber, exposing the underlying, crystalline semiconductor surface.

#### 2.2 scanning electron microscope (SEM) and energy dispersive spectrum (EDS)

SEM is basically a mechanism for a scanning electron beam across a sample in a controlled manner (area, beam diameter, resolution). An electron beam incident on the sample produces an image while in the field emission microscope the specimen itself is the source of electrons. The interaction of an electron beam with a solid can lead to the ejection of loosely bound electrons from the conduction band. These are the secondary electrons with energies below around 50 eV. The standard SEM mode is imaging the secondary electron signal, since the secondary electron are largely emitted from a region relatively near the surface. An SEM consists of an electron gun, a lens system, scanning coils, and an electron collector. The electron energy is typically about 10-30 keV for most samples, but for insulating samples the energy can be as low as several hundred eV. The use of electrons has two advantages over optical microscopes: much larger magnifications are possible since electron wavelengths are much smaller than photon wavelengths and the depth of field is much higher.

Characteristic X-rays result from electron transitions between inner orbits, which are normally full. An electron must first be removed in order to create a vacancy into which another can 'fall' from an orbit further out. In electron probe analysis vacancies are produced by electron bombardment, which also applies to X-ray analysis in the TEM. EDS makes use of the X-ray spectrum emitted by a solid sample bombarded with a focused beam of electrons to obtain a localized chemical analysis. All elements from atomic number 4 (Be) to 92 (U) can be detected in principle, though not all instruments are equipped for 'light' elements (Z < 10). Qualitative analysis involves the identification of the lines in the spectrum and is fairly straightforward owing to the simplicity of X-ray spectra. Quantitative analysis (determination of the concentrations of the elements present) entails measuring line intensities for each element in the sample and for the same elements in calibration Standards of known composition. By scanning the beam in a television-like raster and displaying the intensity of a selected X-ray line, element distribution images or 'maps' can be produced. Also, images produced by electrons collected from the sample reveal surface topography or mean atomic number differences according to the mode selected. The SEM which is closely related to the electron probe, is designed primarily for producing electron images, but can also be used for element mapping, and even point analysis, if an X-ray spectrometer is added. There is thus a considerable overlap in the functions of these instruments.

#### 2.3 atomic force microscopy (AFM)

AFM is essentially ultra-sensitive surface profilometer. Using piezoelectric positioning gears and near-atomically sharp tips, AFM can provide vertical resolution of a few tens of angstroms and lateral resolution of fractions of micron. AFM has been used to identify characteristic surface morphology features as well as yielding root-mean-square (RMS) roughness values. With respect to RMS roughness, it should be noted that this value is somewhat area dependent (averaging over larger areas usually slightly increases the RMS roughness). Also, RMS roughness can be misleading if the surface contains, for example, a limited distribution of narrow

but deep pits. Nonetheless, RMS roughness provides a measure of the surface smoothness or roughness which allows sample-to-sample comparison. In these studies, AFM was also used to characterize antiphase domains and threading dislocations, both of which produce identifiable surface features.

#### 2.4 transmission electron microscopy (TEM)

TEM is the electron beam analogous to optical microscopy of thin, transparent samples. Imaging may be done in either cross-section or plan-view modes, dependent on sample preparation. The electron beam transparency requirement demands sample thickness of order 200 nm or les, requiring a complex sample preparation process involving polishing, grinding, and ultimately ion milling to produce the final thinned sample. Cross-sectional TEM further requires gluing together a stack of wafers with the desired interface at the center, which is then processed similarly to planview samples. For cross-sectional samples it is essential to ion mill (mostly by focused ion beam) centered on the target interface in order to image it.

The tediousness of TEM sample preparation is offset by the wealth of information which can be obtained. TEM can image dislocations, antiphase domains, stacking faults, interface roughness, and other crystallographic defects, and provide extensive information about each, including dislocation burgers vectors, domain orientations, etc. TEM can provide statistically accurate threading dislocation densities for values above about 10<sup>7</sup> cm<sup>-2</sup>, where etch pit density measurements become inaccurate. Below this level, however, TEM becomes inaccurate due to the excessive number of imaging areas required to assess these low densities, for which typically less than one dislocation per field of view is observed. TEM can also distinguish individual layers in a multi-layer structure if there is sufficient electron scattering contrast. Practically, this usually

means that compositional differences are observable, but not doping differences. Noticeably both plan-view and cross-sectional imaging is necessary in order to unambiguously identify all defects. In particular, the misfit dislocations are only imaged in plan-view since they do not extend far beyond the interface between the epi-layers and the substrates.

#### 2.5 X-ray diffractometry (XRD)

X-rays primarily interact with electrons in atoms. When x-ray photons collide with electrons, some photons from the incident beam will be deflected away from the direction where they original travel, much like billiard balls bouncing off one another. If the wavelength of these scattered x-rays did not change (meaning that x-ray photons did not lose any energy), the process is called elastic scattering (Thompson Scattering) in that only momentum has been transferred in the scattering process. These are the x-rays that we measure in diffraction experiments, as the scattered x-rays carry information about the electron distribution in materials. On the other hand, In the inelastic scattering process (Compton Scattering), x-rays transfer some of their energy to the electrons and the scattered x-rays will have different wavelength than the incident x-rays.

Diffracted waves from different atoms can interfere with each other and the resultant intensity distribution is strongly modulated by this interaction. If the atoms are arranged in a periodic fashion, as in crystals, the diffracted waves will consist of sharp interference maxima (peaks) with the same symmetry as in the distribution of atoms. Measuring the diffraction pattern therefore allows us to deduce the distribution of atoms in a material.

The peaks in a x-ray diffraction pattern are directly related to the atomic distances. Let us consider an incident x-ray beam interacting with the atoms arranged in a periodic manner as shown in 2 dimensions in the following illustrations. The atoms, represented as green spheres in the graph,

can be viewed as forming different sets of planes in the crystal. For a given set of lattice plane with an inter-plane distance of d, the condition for a diffraction (peak) to occur can be simply written as

$$2d\sin\theta = n\lambda$$

which is known as the Bragg's law, after W.L. Bragg, who first proposed it. In the equation,  $\lambda$  is the wavelength of the x-ray,  $\theta$  is the scattering angle, and n is an integer representing the order of the diffraction peak. The Bragg's Law is one of most important laws used for interpreting x-ray diffraction data. It is important to point out that although we have used atoms as scattering points in this example, Bragg's Law applies to scattering centers consisting of any periodic distribution of electron density.

Powder XRDis perhaps the most widely used x-ray diffraction technique for characterizing materials. As the name suggests, the sample is usually in a powdery form, consisting of fine grains of single crystalline material to be studied. The technique is used also widely for studying particles in liquid suspensions or polycrystalline solids (bulk or thin film materials). The term powder really means that the crytalline domains are randomly oriented in the sample. Therefore when the 2-D diffraction pattern is recorded, it shows concentric rings of scattering peaks corresponding to the various d spacings in the crystal lattice. The positions and the intensities of the peaks are used for identifying the underlying structure (or phase) of the material. Generally speaking thin film diffraction refers not to a specific technique but rather a collection of XRD techniques used to characterize thin film samples grown on substrates. These materials have important technological applications in microelectronic and optoelectronic devices, where high quality epitaxial films are critical for device performance. Thin film diffraction methods are used as important process development and control tools, as hard x-rays can penetrate through the epitaxial layers and

measure the properties of both the film and the substrate.

Basic XRD measurements made on thin film samples include:

• Precise lattice constants measurements derived from  $\omega$ -2 $\theta$  scans, which provide information about lattice mismatch between the film and the substrate and therefore is indicative of strain & stress

• Rocking curve measurements made by doing a  $\omega$  scan at a fixed 2 $\theta$  angle, the width of which is inversely proportionally to the dislocation density in the film and is therefore used as a gauge of the quality of the film.

• Superlattice measurements in multilayered heteroepitaxial structures, which manifest as satellite peaks surrounding the main diffraction peak from the film. Film thickness and quality can be deduced from the data.

• Glancing incidence x-ray reflectivity measurements, which can determine the thickness, roughness, and density of the film. This technique does not require crystalline film and works even with amorphous materials.

#### 2.6 photoluminescence (PL) and time-resolved photoluminescence (TRPL)

The phenomena which involve absorption of energy and subsequent emission of light are classified generically under the term luminescence. Phosphors are luminescent materials that emit light when excited by radiation, and are usually microcrystalline powders or thin-films designed to provide visible color emission. Excitation by absorbance of a photon leads to a major class of technically important luminescent species which fluoresce or phosphoresce. In general, fluorescence is "fast" (ns time scale) while phosphorescence is "slow" (longer time scale, up to hours or even days). The absorption of energy, which is used to excite the luminescence, takes place by either the host lattice or by intentionally doped impurities. In most cases, the emission takes place on the impurity ions, which, when they also generate the desired emission, are called activator ions. When the activator ions show too weak an absorption, a second kind of impurities can be added (sensitizers), which absorb the energy and subsequently transfer the energy to the activators. This process involves transport of energy through the luminescent materials. Quite frequently, the emission color can be adjusted by choosing the proper impurity ion, without changing the host lattice in which the impurity ions are incorporated. On the other hand, quite a few activator ions show emission spectra with emission at spectral positions which are hardly influenced by their chemical environment. This is especially true for many of the rare-earth ions. Generally, luminescence of phosphors involves two processes: excitation and emission. Many types of energy can excite the phosphors. Excitation by means of energetic electrons is cathodoluminescence (CL). PL occurs when excited by photons, electroluminescence (EL) is excited by an electric voltage, chemiluminescence is excited by the energy of a chemical reaction, and so on. The process of emission is a release of energy in the form of photon. In the host lattice with activator, the activator is directly excited by incoming energy; the electron on it absorbs energy and is raised to an excited state. The excited state returns to the ground state by emission of radiation.

PL is a basically a measurement in which electron-hole pairs are photogenerated, typically by a laser beam whose photo energy is well above bandgap, and the resultant luminescence produced by radiative decay is measured spectrographically. TRPL is a variant whereby only a single luminescence wavelength is temporally monitored after the photoexcitation source is abruptly cut off. The decay transient as the original equilibrium illuminated minority carrier concentration decays through recombination is measured. The TRPL transient thus will be a measure of those material or heterostructure parameters which control the rate of recombination. For a very thick film under low-level injection where photogeneration is deep (i.e. far from the surface or epi-layer/substrate interface) the TRPL decay will simply reflect the bulk lifetime. Such measurement is often impractical, however, since the above-bandgap excitation will be absorbed near the sample surface, so that the decay rate will be dominated by recombination at the typically very high density of surface states. TRPL dacay lifetime can be related to the bulk minority carrier lifetime as<sup>37</sup>:

$$\frac{1}{\tau_{TRPL}} = \frac{1}{\tau_P} + \frac{2S}{d}$$

Where  $\tau_{TRPL}$  is the TRPL decay lifetime,  $\tau_P$  is the bulk minority lifetime, *S* is the interface recombination velocity, and *d* is the epi-layer thickness. TRPL provides a simple, non-destructive means of evaluating the minority carrier recombination velocity and the interface recombination velocity, both of which are critical parameters for designing lasers, LEDs, and solar cells such minority carrier devices.

## **Chapter 3**

# **Experimental Results**

# **3.1** Precise positioning and low defect density selective area epitaxy for selfassembled/catalyst-free GaAs nanodisks on SiO<sub>2</sub> masked exactly oriented Si substrates.

This section is focused on the structural and optical characterizations of selfassembled/catalyst-free GaAs nanodisks on SiO<sub>2</sub> masked Si(100) patterned substrates by molecular beam epitaxial growth. Pure zincblende GaAs nanodisks with precise positioning and low defect density are demonstrated by selective area epitaxy. The influence of the growth temperature and deposition duration is investigated. Excellent morphological and structural properties are characterized by scanning electron microscopy and cross-sectional transmission electron microscopy. Defects in the epilayers are reduced by strain relaxation through facets formation and by a lateral overgrowth scheme atop the SiO<sub>2</sub> mask which is corroborated by micro-Raman spectroscopy. In particular, I show how the material quality contributes to excellent optical properties observed by micro-photoluminescence spectroscopy from 77 K to room temperature.

#### **3.1.1 INTRODUCTION**