## UC Berkeley UC Berkeley Electronic Theses and Dissertations

### Title

Rapid ASIC Design for Digital Signal Processors

### Permalink

https://escholarship.org/uc/item/5z64j8br

### **Author** Bailey, Steven

# Publication Date 2018

Peer reviewed|Thesis/dissertation

#### Rapid ASIC Design for Digital Signal Processors

by

Steven Bailey

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolić, Chair Professor Elad Alon Professor Aaron Parsons

Fall 2018

## Rapid ASIC Design for Digital Signal Processors

Copyright 2018 by Steven Bailey

#### Abstract

#### Rapid ASIC Design for Digital Signal Processors

by

Steven Bailey

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Chair

Application-specific integrated circuit (ASIC) signal processors are necessary to achieve the high performance and low power requirements of modern applications, but long development times are one hurdle contributing to their declining adoption. A significant percentage of their development time goes into the design and verification of the architecture, with the remainder consumed by back-end ASIC flow work and chip testing. Agile hardware principles, borrowed from a similar successful software approach and previously applied to general-purpose processors, offer a promising solution to continuing the development of signal processing systems on a chip (SoCs).

This work presents a digital signal processing SoC design framework that, when coupled with agile design principles, supports rapid prototyping and designing of ASICs for signal processing applications. First, applications and existing ASIC solutions are explored and analyzed in Chapter 2 to glean useful properties and trends. From this, Chapter 3 proposes a model for a generic signal processing SoC is developed. Next, a new Chisel generator design framework is presented in Chapter 4. Chisel is a hardware construction language written as a DSL in Scala, allowing for high-level and functional programming use when designing hardware. This framework couples a general-purpose processor with a signal processing accelerator, and much of the library code for connectivity, memory mapping, and programming is made available. This framework, when coupled with an agile design process, supports rapid development of ASICs. The accelerator performs streaming signal processing to offload high-throughput computational kernels from the CPU. As processing elements for the desired application are produced, processing moves from the CPU to the accelerator. Low-rate processing tasks are computed on the CPU, meaning tape-out occurs on time and produces a working chip able to perform the entire application.

The methodology and proposed agile design process were validated on two separate chips in Chapters 5 and 6, spanning two applications and two process nodes. The ASIC spectrometer (Splash2), for which the RTL was designed in eight weeks by one person, demonstrates the power of Chisel to rapidly construct processing element generators. These generators were then improved and the parameters adjusted as physical design and timeline constraints imposed new restrictions. The radar receive processor design fleshed out the generator framework details. A significantly larger design, this chip required about 300 engineering-weeks of work over 9 months, equivalent to a team of 8 engineers working full time. About 30% of that time was spent designing the framework and reusable processing elements. This represents a 56% reduction in development time compared to the estimated 14.4 months from standard practices (excluding time for framework design, fabrication, and testing). Both efforts produced working chips competitive against state-of-the-art custom ASICs in terms of performance, power, and capabilities.

## Contents

| Co       | onten | $\mathbf{ts}$ |                                                                                             |       |     | i    |

|----------|-------|---------------|---------------------------------------------------------------------------------------------|-------|-----|------|

| Lis      | st of | Figures       |                                                                                             |       |     | iv   |

| Lis      | st of | Tables        |                                                                                             |       |     | viii |

| 1        | Intr  | oduction      |                                                                                             |       |     | 1    |

|          | 1.1   | Motivation    |                                                                                             |       |     | 1    |

|          | 1.2   | Background    | d                                                                                           |       |     | 6    |

|          |       | 1.2.1 Sign    | nal Processing Models                                                                       |       |     | 8    |

|          |       | 1.2.2 RT      | L Design Frameworks                                                                         |       |     | 15   |

|          |       | •             | tem Design $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |       |     | 16   |

|          | 1.3   | Thesis Out    | line                                                                                        | <br>• |     | 17   |

| <b>2</b> | Sign  | al Process    | sing Applications and Models                                                                |       |     | 19   |

|          | 2.1   | Astronomio    | cal and Atmospheric Spectroscopy                                                            |       |     | 19   |

|          |       |               | orithms and Instruments                                                                     |       |     | 19   |

|          | 2.2   | Radio Base    | eband Processing                                                                            |       |     | 22   |

|          |       | 2.2.1 An      | OFDM Modem                                                                                  |       |     | 23   |

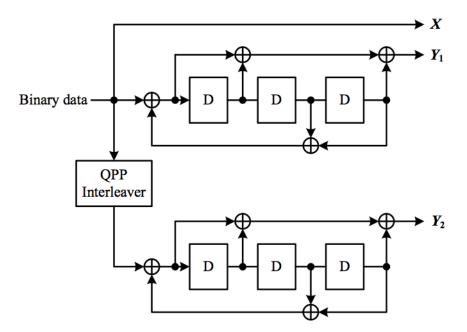

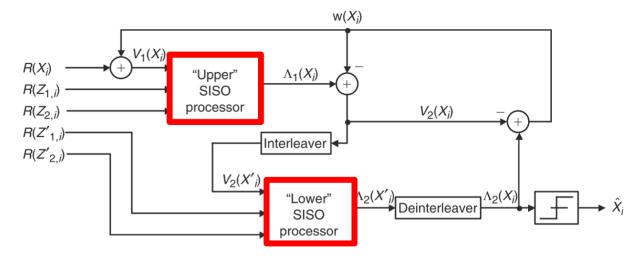

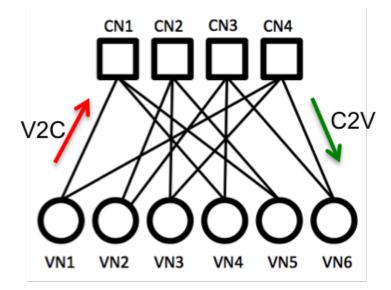

|          |       | 2.2.2 For     | ward Error Correction                                                                       |       |     | 23   |

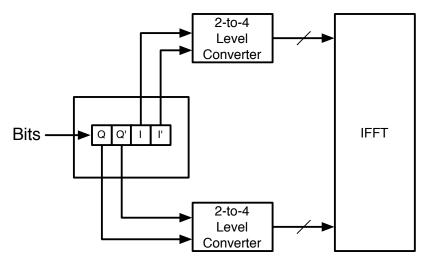

|          |       | 2.2.3 Dig     | ital Modulation                                                                             |       |     | 26   |

|          |       | 2.2.4 Oth     | er Processing Blocks                                                                        |       |     | 28   |

|          | 2.3   | Radar Tran    | nsceivers                                                                                   |       |     | 28   |

|          | 2.4   | A Common      | n Signal Processing Algorithm Model                                                         | <br>• | • • | 30   |

| 3        | Digi  | tal Signal    | Processing SoC Model                                                                        |       |     | 32   |

|          | 3.1   | 0             | odels                                                                                       |       |     | 32   |

|          |       | -             | tralized Digital Signal Processors                                                          |       |     | 32   |

|          |       | 3.1.2 Dist    | tributed Digital Signal Processors                                                          |       |     | 34   |

|          |       |               | dened Digital Signal Processors                                                             |       |     | 35   |

|          |       |               | nmary and Trends                                                                            |       |     | 36   |

|          | 3.2   | System Ov     | erview                                                                                      |       |     | 37   |

|          | 3.3            | General-Purpose Processor                                                                                                         |

|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------|

|          | 3.4            | Signal Processing Accelerator                                                                                                     |

|          | 3.5            | Debug and Test                                                                                                                    |

| 4        | ΛГ             | OSP SoC Generator 42                                                                                                              |

| 4        | <b>A L</b> 4.1 | Generator Overview                                                                                                                |

|          | 4.2            | General-Purpose Processor Generator   43                                                                                          |

|          |                | 1                                                                                                                                 |

|          | 4.3            | 8 0                                                                                                                               |

|          | 4.4            | Verifying the Generators                                                                                                          |

| <b>5</b> | ΑD             | Digital Spectrometer Design 50                                                                                                    |

|          | 5.1            | Introduction                                                                                                                      |

|          | 5.2            | Spectrometer Generator                                                                                                            |

|          |                | 5.2.1 Polyphase Filter                                                                                                            |

|          |                | 5.2.2 Fast Fourier Transform                                                                                                      |

|          |                | 5.2.3 Sideband Separation, Power, and Accumulation                                                                                |

|          |                | 5.2.4 ASIC Design and Verification                                                                                                |

|          | 5.3            | ASIC Implementation                                                                                                               |

|          | 0.0            | 5.3.1 Serial Links                                                                                                                |

|          |                | 5.3.2 Digital Instance                                                                                                            |

|          |                | 5.3.3 Clocking                                                                                                                    |

|          | 5.4            |                                                                                                                                   |

|          | -              | 1 0                                                                                                                               |

|          | 5.5<br>5.c     | Agile Principles Applied    70      Combust    70                                                                                 |

|          | 5.6            | $Conclusion \dots \dots$    |

| 6        | Exa            | mple: A Signal Analysis SoC 72                                                                                                    |

|          | 6.1            | Introduction $\ldots \ldots 72$ |

|          | 6.2            | SoC Architecture                                                                                                                  |

|          | 0              | 6.2.1 General-Purpose Processor                                                                                                   |

|          |                | 6.2.2 Digital Signal Processing Accelerator                                                                                       |

|          |                | 6.2.3   Processing Elements   74                                                                                                  |

|          |                | 6.2.4   Bit Manipulator   75                                                                                                      |

|          |                | $6.2.5$ Tuner $\ldots$ $\ldots$ $76$                                                                                              |

|          |                | 6.2.6 Decimating Filter                                                                                                           |

|          |                | 0                                                                                                                                 |

|          |                | J 1                                                                                                                               |

|          | <i>c</i> 9     |                                                                                                                                   |

|          | 6.3            | IP Integration                                                                                                                    |

|          |                | 6.3.1 ADC and Calibration                                                                                                         |

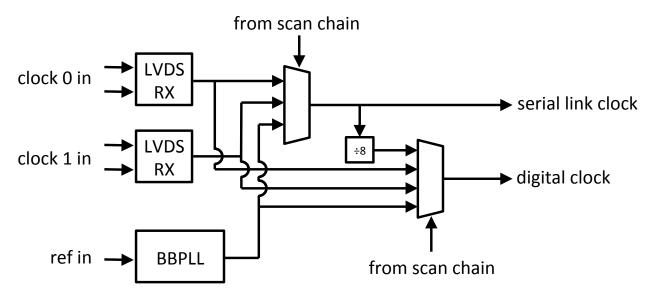

|          |                | 6.3.2 Clock Receiver                                                                                                              |

|          |                | 6.3.3 UART                                                                                                                        |

|          |                | 6.3.4 Memories and IO                                                                                                             |

|          | 6.4            | Verification and Design-For-Test                                                                                                  |

|    |       | 6.4.1 Unit Tests                                                                              | 86  |

|----|-------|-----------------------------------------------------------------------------------------------|-----|

|    |       | 6.4.2 System Tests                                                                            | 90  |

|    |       | 6.4.3 DfT Considerations                                                                      | 92  |

|    | 6.5   | Testing Results and Measurements                                                              | 93  |

|    | 6.6   | Signal Analysis Applications                                                                  | 94  |

|    |       | $6.6.1  \text{Spectrometry}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 95  |

|    |       | 6.6.2 Radar                                                                                   | 97  |

|    | 6.7   | Agile Design Process                                                                          | 99  |

|    | 6.8   | Conclusion                                                                                    | 102 |

| 7  | Con   | nclusion                                                                                      | 104 |

|    | 7.1   | Summary of Contributions                                                                      | 104 |

|    | 7.2   | Future Work                                                                                   | 105 |

| Bi | bliog | graphy                                                                                        | 106 |

## Bibliography

# List of Figures

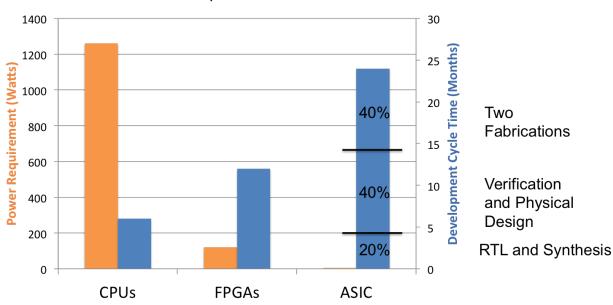

| 1.1          | ASICs are much lower power than CPUs but require significantly more develop-<br>ment time for a particular application [1].                                                                                                                                                                                                                    | 2        |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

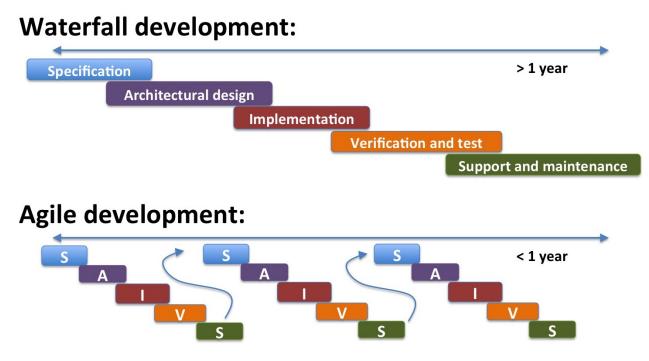

| 1.2          | A comparison of waterfall and agile software development paradigms shows the differences in development cycles and project completion timeframes. Waterfall development uses a top-down approach and frequently takes over a year. Agile development uses a smaller, iterative approach with sufficient results completed in less than a year. | 2        |

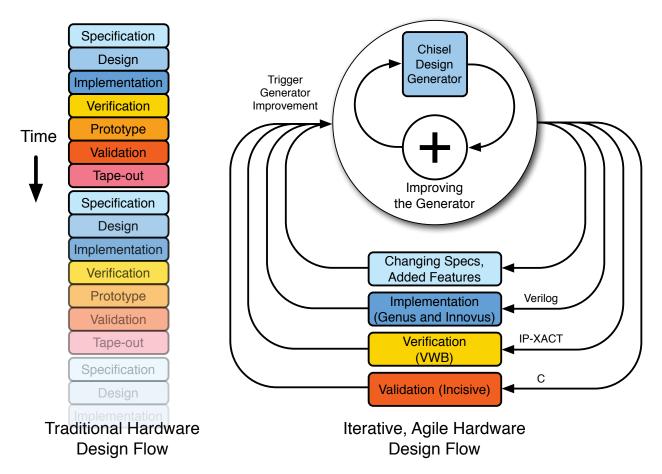

| 1.3          | A comparison of traditional, open-loop design flow with our agile, iterative de-<br>sign flow. Changing specifications and issues during the process trigger generator<br>improvement work. Design generators are also portable across designs, so these<br>iterative enhancements persist.                                                    | 5        |

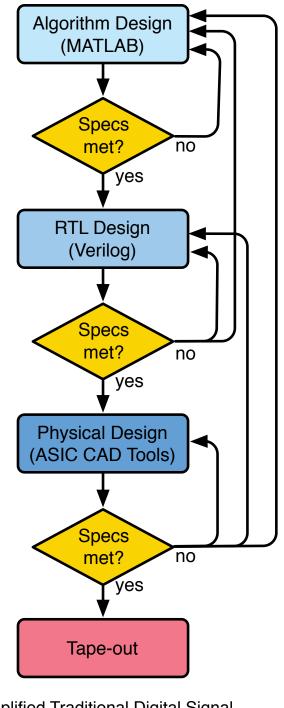

| 1.4          | Traditional DSP hardware design produces an instance tailored to the specific application and technology. It is not easily reusable across applications and technologies [2].                                                                                                                                                                  | 7        |

| 1.5          | Simple synchronous data flow model showing actors as nodes connected through FIFOs as edges. Production and consumption rates are fixed and shown on the figure. Fixed rates support static scheduling.                                                                                                                                        | 9        |

| 1.6          | Flynn's taxonomy of computer architectures                                                                                                                                                                                                                                                                                                     | 10       |

| 1.7          | Stanford's Imagine stream processor. Bandwidths assume a core clock of 180 MHz<br>[3]                                                                                                                                                                                                                                                          | 12<br>13 |

| 1.8          | VLSI circuit design flow [4]                                                                                                                                                                                                                                                                                                                   | 15       |

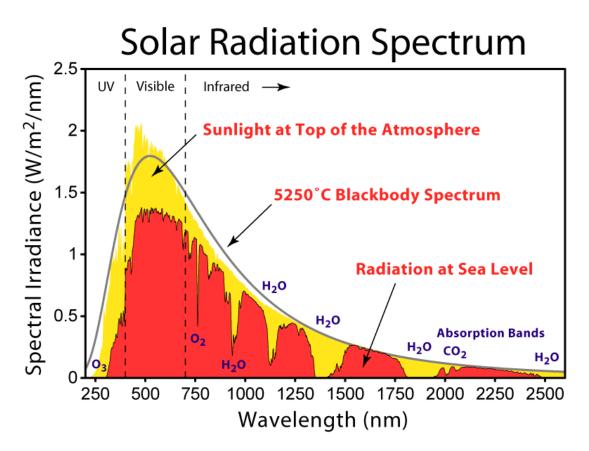

| 2.1          | The Sun emits blackbody radiation, which is intermittently absorbed by particles in the corona and in Earth's atmosphere [5].                                                                                                                                                                                                                  | 20       |

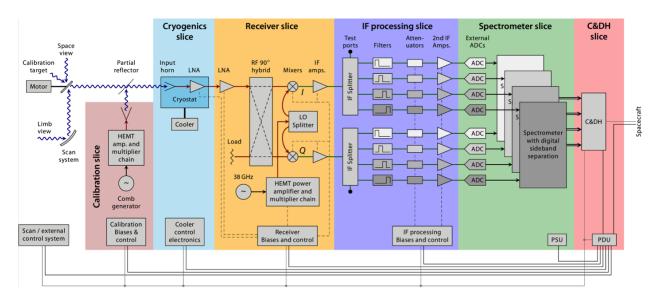

| 2.2          | A full satellite terahertz receiver design for the compact adaptable microwave limb sounder (CAMLS) project [6]                                                                                                                                                                                                                                | 21       |

| 2.3          | The receiver block diagram for the CAMLS instrument, a modification of a pre-<br>vious design [7]. Analog and digital blocks amenable to ASIC implementation are                                                                                                                                                                               |          |

| 2.4          | in the dotted box                                                                                                                                                                                                                                                                                                                              | 21       |

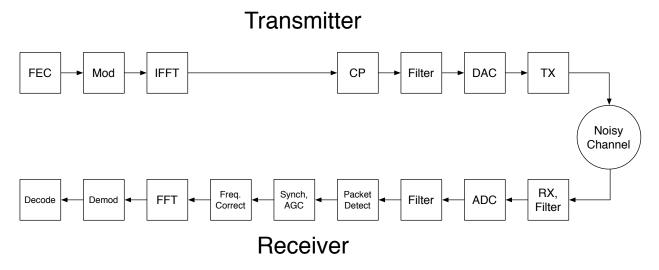

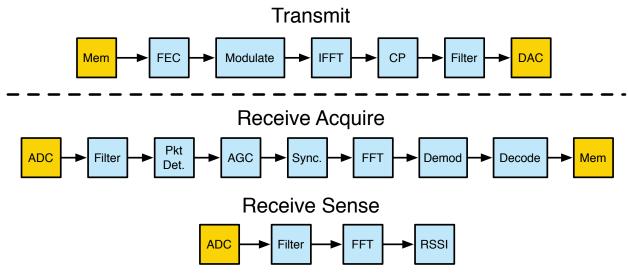

| 2.4          | A simplified block diagram of a typical OFDM modem                                                                                                                                                                                                                                                                                             | 23       |

| $2.5 \\ 2.6$ | LTE turbo encoding and decoding block diagrams                                                                                                                                                                                                                                                                                                 | 24<br>25 |

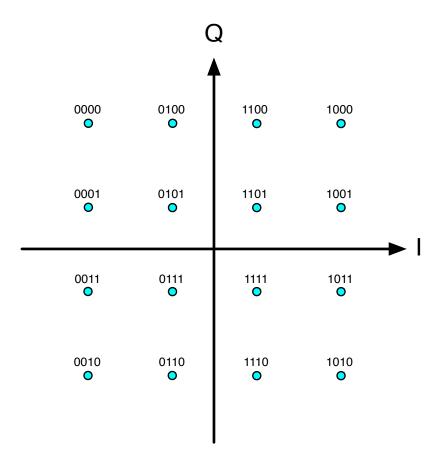

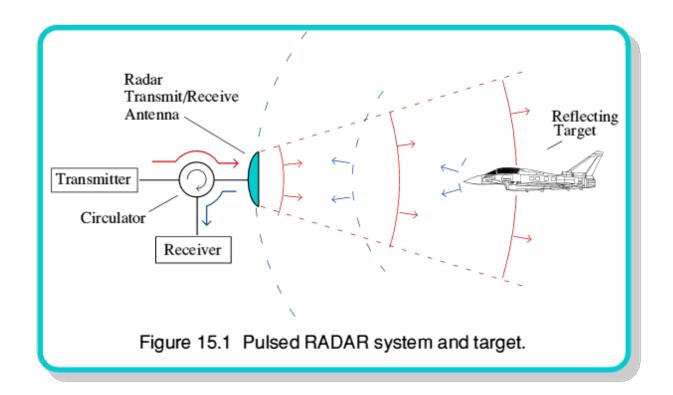

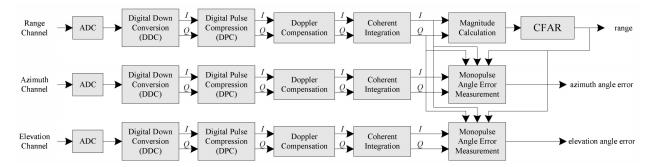

| 2.7<br>2.8   | LTE turbo encoding and decoding block diagrams                                                                                                                                                          | 27<br>29 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.9          | Typical radar receiver block diagram, here showing multiple receive channels with<br>each one processed similarly [9]. Computation after coherent integration is slow<br>enough to be done in software. | 29       |

| 2.10         |                                                                                                                                                                                                         | 31       |

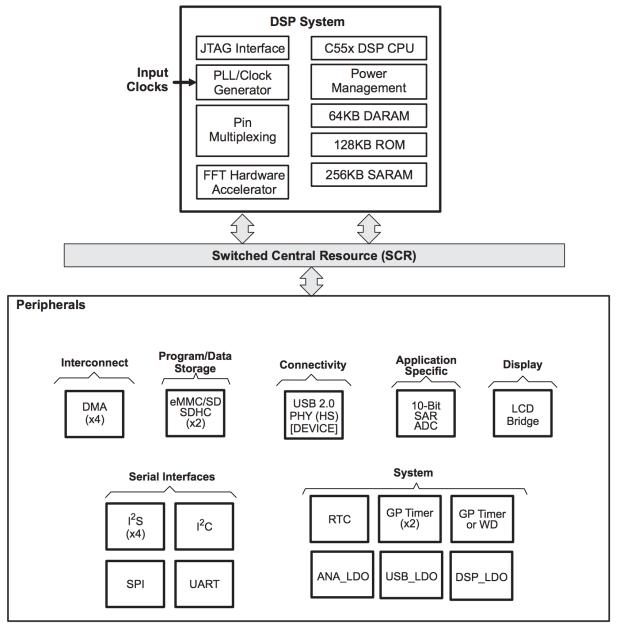

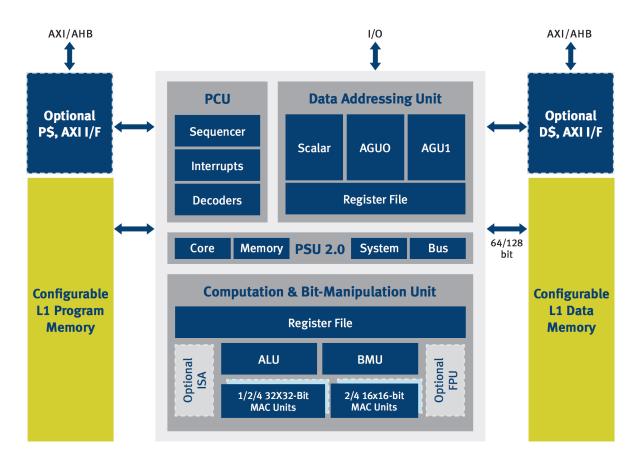

| $3.1 \\ 3.2$ | The Texas Instruments TMS320C5545 DSP SoC block diagram [10]<br>The Ceva Teaklite-4 architecture, showing the physically separate program and<br>data memories (Harvard architecture) [11]              | 33<br>34 |

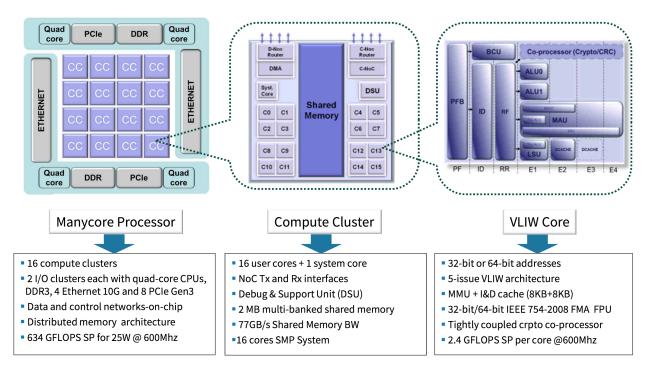

| 3.3          | The Kalray MPPA-256 Bostan Processor Architecture, showing hierarchical many-<br>core clustering [12]                                                                                                   | 35       |

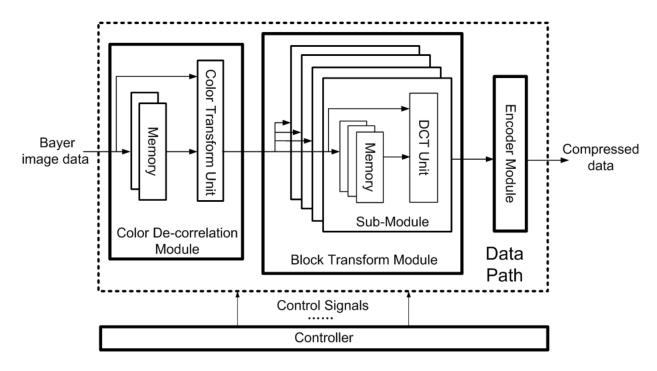

| 3.4          | Image compression architectural datapath block diagram for a capsule endocscopy<br>ASIC [13]                                                                                                            | 36       |

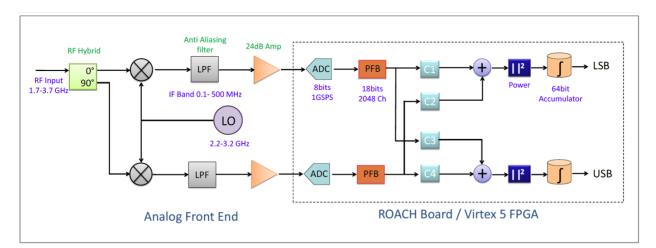

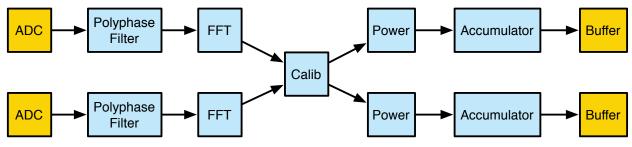

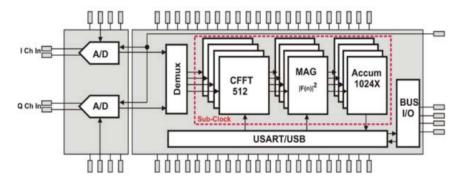

| 3.5          | Spectrometer architectural block diagram, showing the digital processing path after the ADC inputs [14]                                                                                                 | 37       |

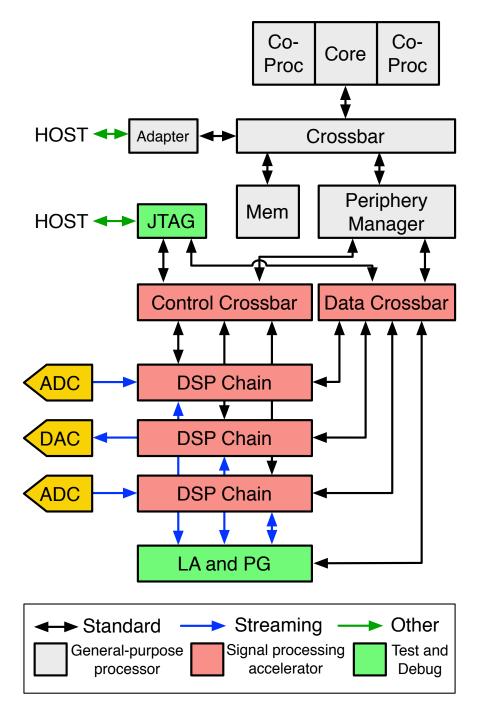

| 3.6          | A digital signal SoC model. The general-purpose processor and local co-processors talk to the digital signal processing accelerator through a periphery manager and                                     |          |

| 0 7          | memory-mapped IO.                                                                                                                                                                                       | 38       |

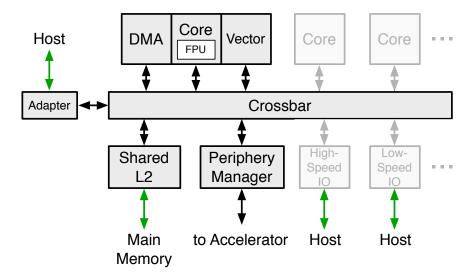

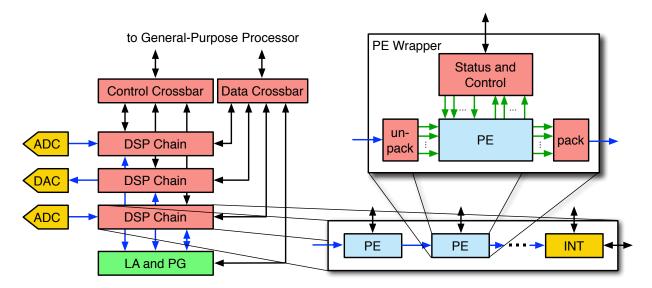

| $3.7 \\ 3.8$ | General-purpose processor architecture. Grayed out boxes show possible extensions.<br>Signal processing accelerator architecture.                                                                       | 39<br>41 |

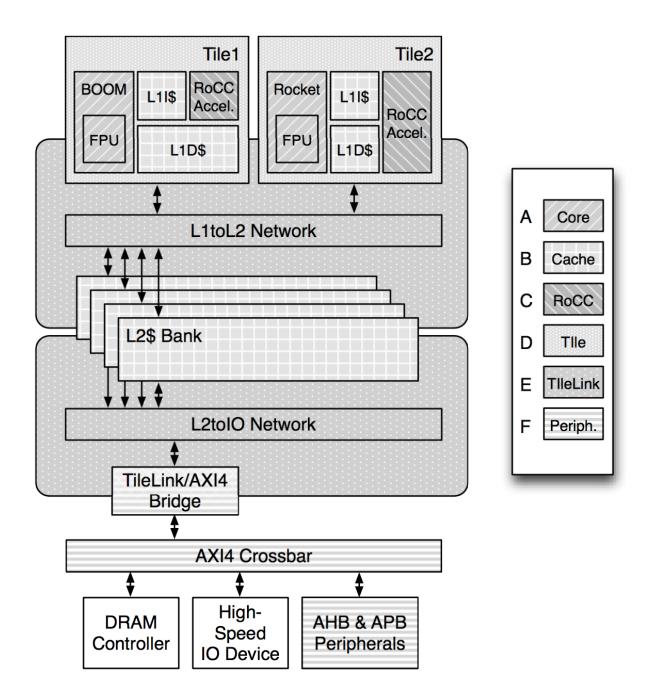

| 4.1          | The rocket-chip generator can produce various topologies using hierarchical gen-<br>erators [15]                                                                                                        | 44       |

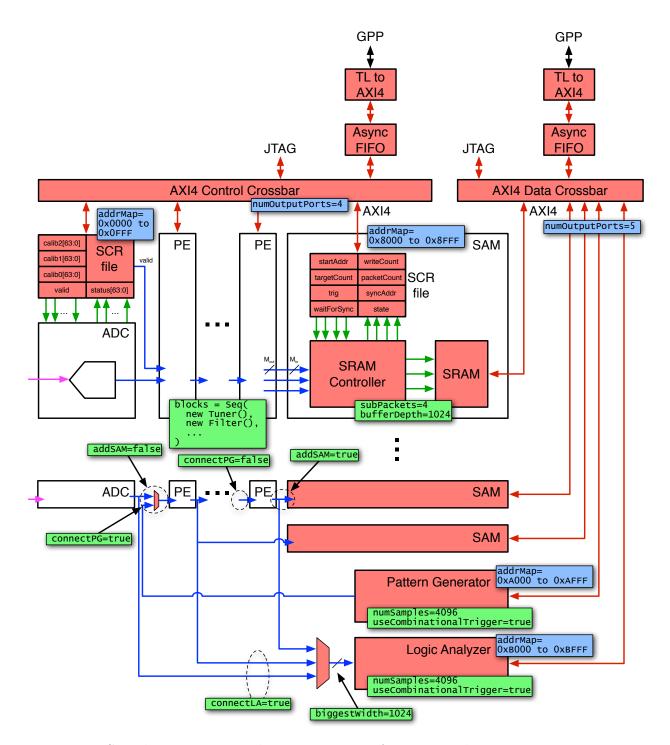

| 4.2          | Signal processing accelerator generator features, with user input parameters in green, generated parameters and automated checks in blue, and auto-generated                                            | 10       |

| 4.3          | designs in red                                                                                                                                                                                          | 46       |

|              | Builders, and a handful of other parameters.                                                                                                                                                            | 47       |

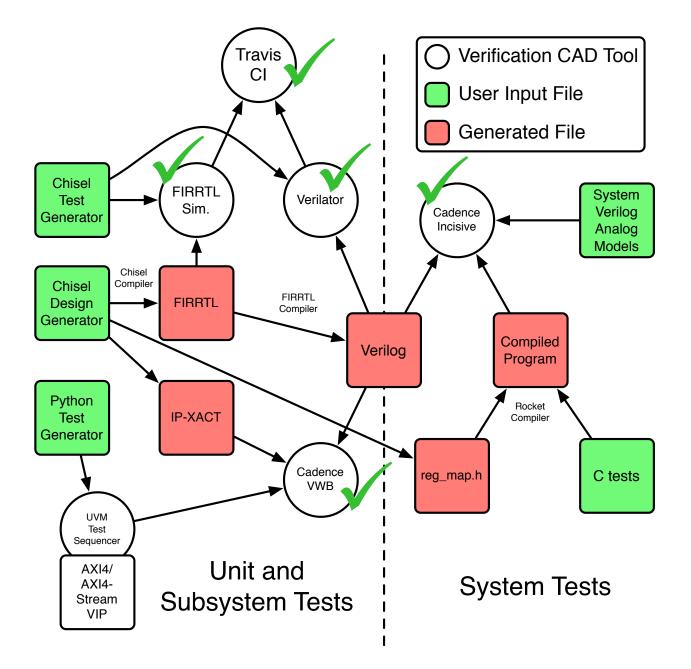

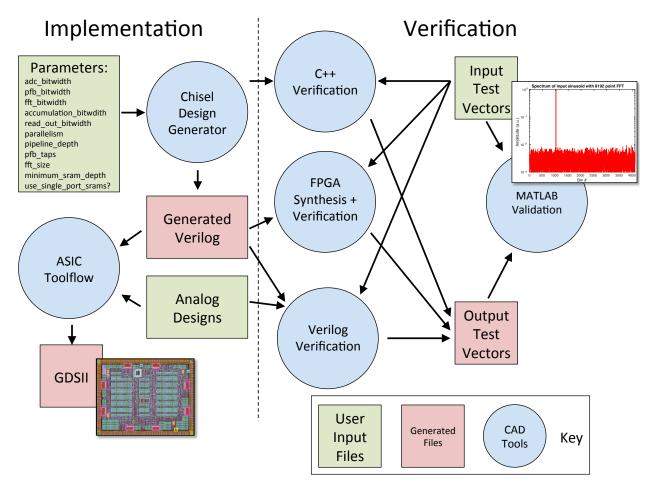

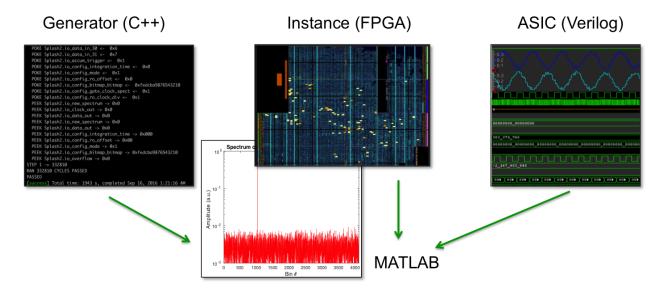

| 4.4          | Verification framework.                                                                                                                                                                                 | 49       |

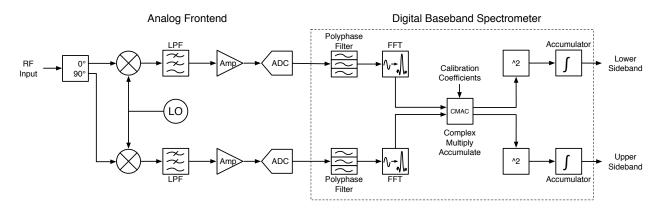

| 5.1          | Generic spectrometer receiver. The analog front-end performs RF to baseband conversion, optional sideband (IQ) separation, filtering, and amplification. The                                            |          |

|              | digital baseband backend performs additionally filtering, transformation to the                                                                                                                         | 51       |

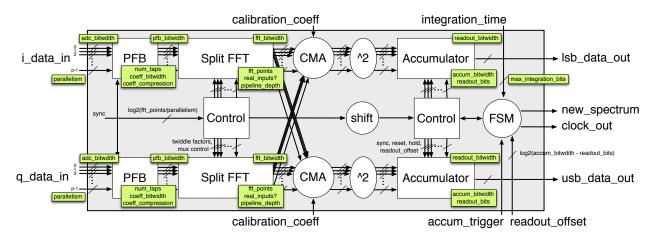

| 5.2          | frequency domain, calibration, magnitude calculation, and accumulation. $\dots$ Spectrometer generator. Parameters are shown in green. Separate $I$ and $Q$ inputs                                      | 51       |

| 5.3          | arrive from two ADCs                                                                                                                                                                                    | 52       |

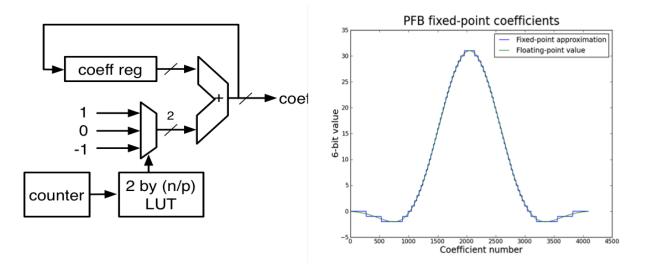

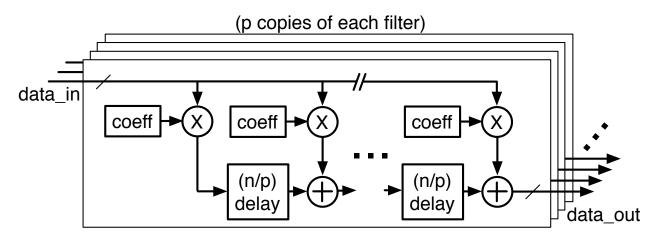

|              | parameter values, such as the bitwidths, number of taps, and number of channels.                                                                                                                        | 53       |

| 5.4   | Parameterized polyphase filter. Coefficient values are addressed by the global synchronization signal. Delays are mapped to SRAMs when long. These delays                      |          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|       | · · · · · · · ·                                                                                                                                                                | 53       |

| 5.5   | The FFT generator.                                                                                                                                                             | 55       |

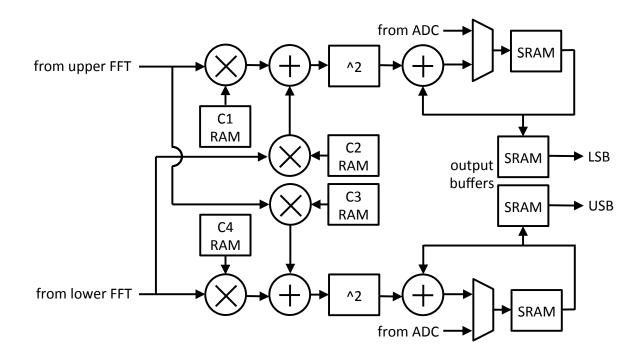

| 5.6   | Calibration, power, and accumulation signal path block diagram. Calibration fixes mismatch between front-end receivers and ADCs                                                | 57       |

| 5.7   | Generator flow diagram, showing verification paths on the right and the imple-                                                                                                 | 58       |

| 5.8   | 1                                                                                                                                                                              | 59       |

| 5.9   |                                                                                                                                                                                | 59       |

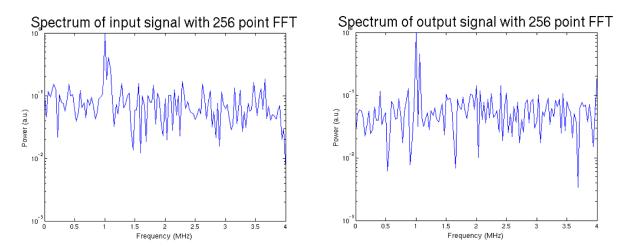

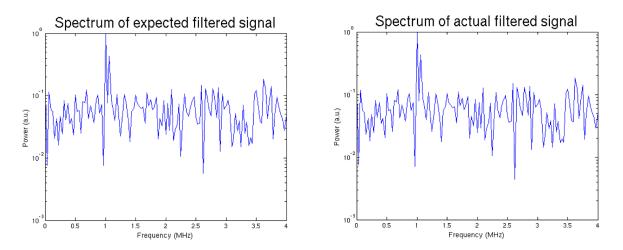

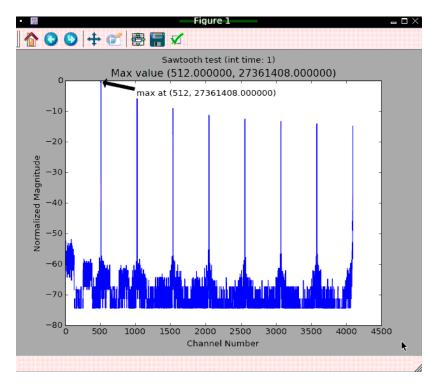

| 5.10  | PFB and FFT verification. Quantized coefficients were applied to the MATLAB                                                                                                    | ,0       |

| 0.10  | PFB, and the input signal was quantized, but all other operations were floating                                                                                                | 30       |

| 5 11  | FPGA verification allowed for full design simulation. This figure shows the spec-                                                                                              | ,0       |

| 0.11  | <u> </u>                                                                                                                                                                       | 50       |

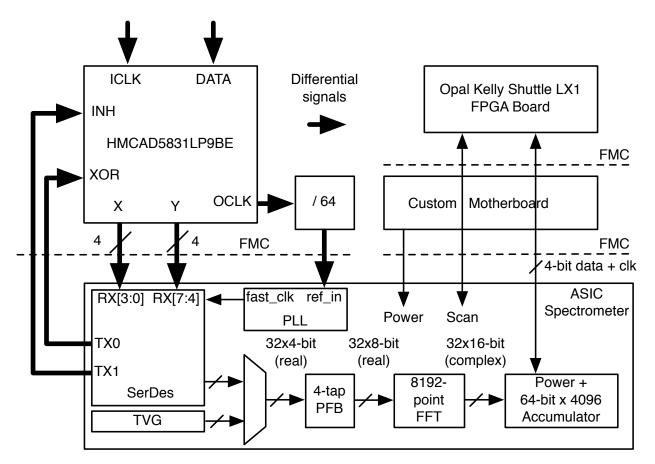

| 5.12  | · ·                                                                                                                                                                            | 51       |

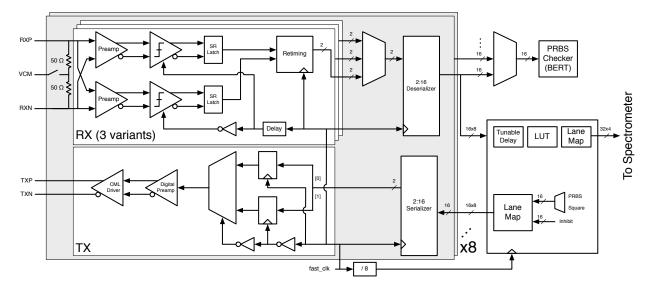

|       | SerDes block diagram, including digital back-ends for monitoring and spectrom-                                                                                                 |          |

|       |                                                                                                                                                                                | 52       |

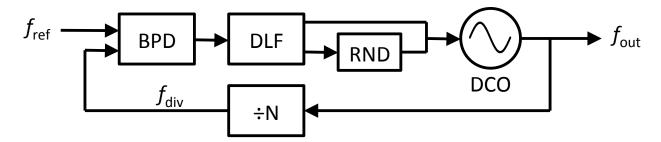

| 5.14  |                                                                                                                                                                                | -<br>54  |

|       | · · ·                                                                                                                                                                          | 34       |

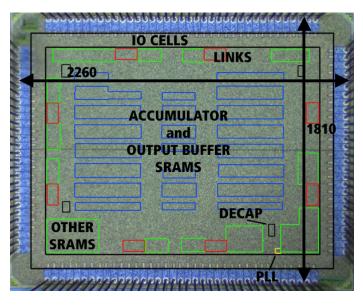

|       | Chip die photo, with large components annotated. Note the distributed serial links and memory-dominated floorplan. The size was 4.2 mm <sup>2</sup> . Annotated dimensions     |          |

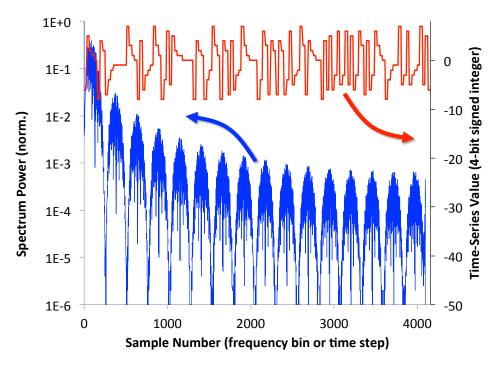

| 5.17  | Time-series snapshot and spectrum power from the PRBS TVG. Both match                                                                                                          | 35<br>36 |

| 5 1 9 |                                                                                                                                                                                | 50<br>57 |

| 5.19  | Example full system measured spectra at 1 GHz sampling frequency. Signal and                                                                                                   |          |

| 5.20  | Measured spectra at 1 Gs/s with a 166 MHz input signal, accumulated over 16384                                                                                                 | 58<br>59 |

| 0.1   |                                                                                                                                                                                | 70       |

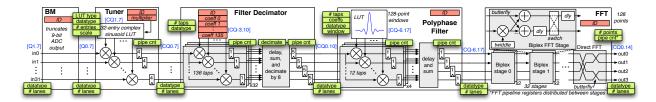

| 6.1   |                                                                                                                                                                                | 73       |

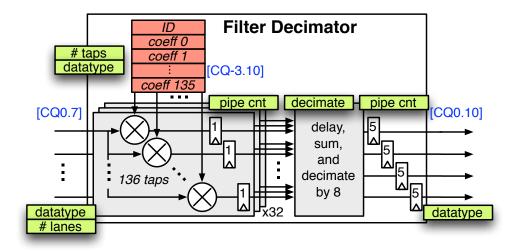

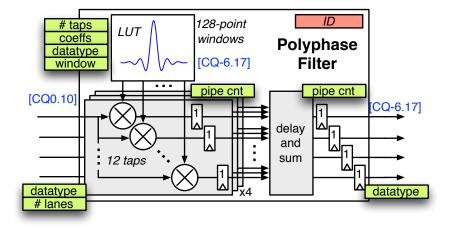

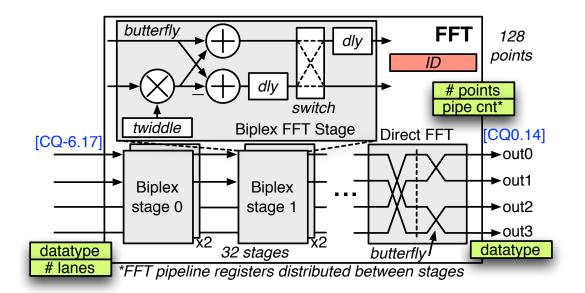

| 6.2   | Detailed diagram of the processing elements in the DSP accelerator. Red boxes                                                                                                  |          |

|       | indicate memory-mapped IO SCRs. Green overlays show generator parameters.                                                                                                      |          |

|       | Blue text gives fixed-point data type parameters chosen. $CQ = complex$ fixed-                                                                                                 | 75       |

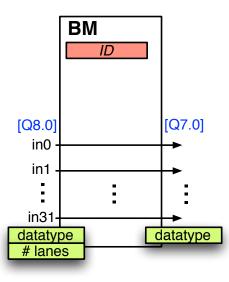

| 6.3   | Bit manipulator, showing how the output is directly connected to the input, but                                                                                                | 75       |

| C A   |                                                                                                                                                                                | 76       |

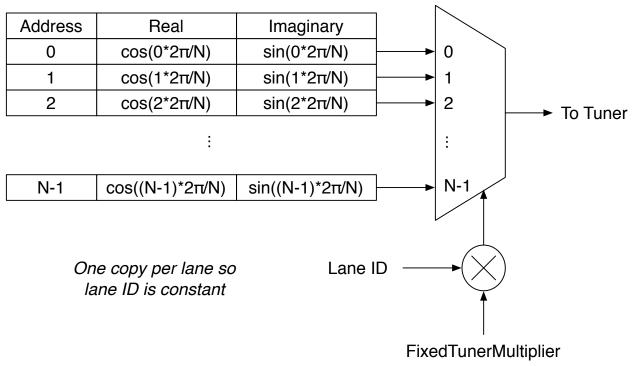

| 6.4   | Tuner coefficient LUT diagram for the <i>Fixed</i> configuration. This architecture sim-<br>plifies the hardware by hard coding coefficients and requiring a single multiplier |          |

|       | plifies the hardware by hard-coding coefficients and requiring a single multiplier                                                                                             | 77       |

|       | input                                                                                                                                                                          | 77       |

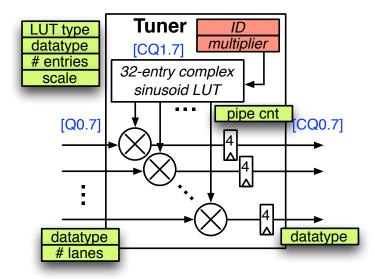

| 6.5  | Example tuner block diagram. Note the implicit conversion from real to complex.                                    |     |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

|      | Pipeline registers are all placed at the output. Direct synthesis tools to retime as                               | 70  |

| C C  | needed for improved performance.                                                                                   | 78  |

| 6.6  | Simplified decimating filter block diagram, with delay and summation logic ob-                                     | 70  |

| 67   | fuscated                                                                                                           | 79  |

| 6.7  | The polyphase filter looks almost identical to the decimating filter, but the                                      |     |

|      | polyphase filter lanes are kept distinct, while the decimating filter treats all lanes<br>as one continuous input. | 80  |

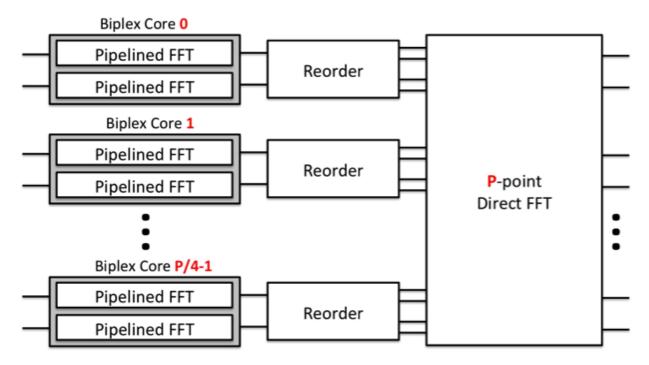

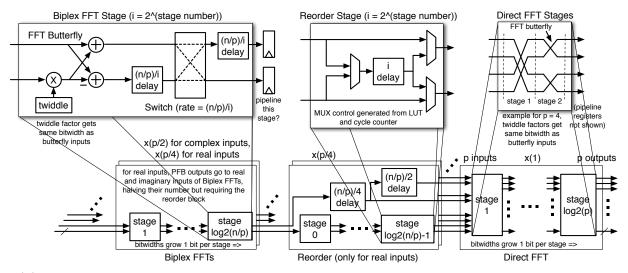

| 6.8  | Fast Fourier transform block diagram. The ratio of biplex to direct FFT butter-                                    | 00  |

| 0.0  | flies scales automatically with the specified number of points and lanes. Twiddle                                  |     |

|      | factors and intermediate bitwidths are calculated automatically for any design size.                               | 81  |

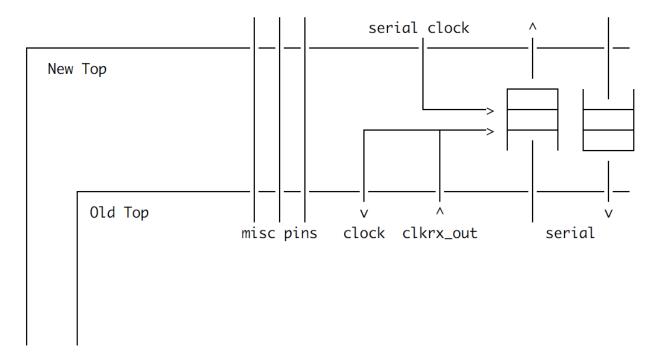

| 6.9  | Clock looping to override default clock connections. The asynchronous FIFOs                                        | 01  |

| 0.9  | convert between the slow external clock domain and the fast on-chip clock domain.                                  | 85  |

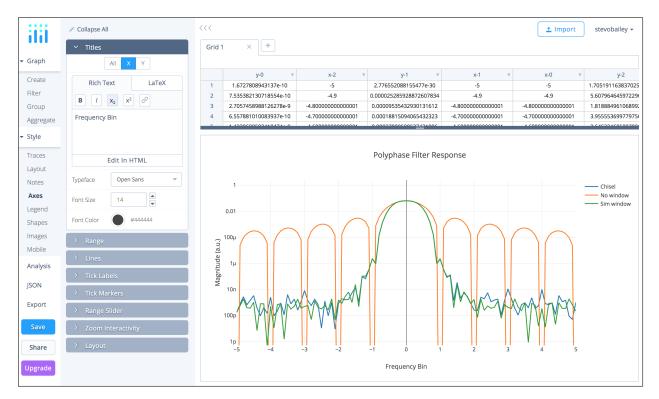

| 6 10 | Visualizing the PFB filter response in Plot.ly.                                                                    | 90  |

|      | System simulations included a noisy sine wave input to the ADC to check for                                        | 50  |

| 0.11 | end-to-end functionality.                                                                                          | 92  |

| 6.12 | Chip layout, die photo, and summary.                                                                               | 93  |

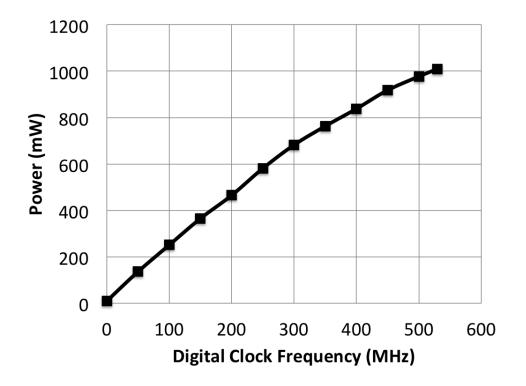

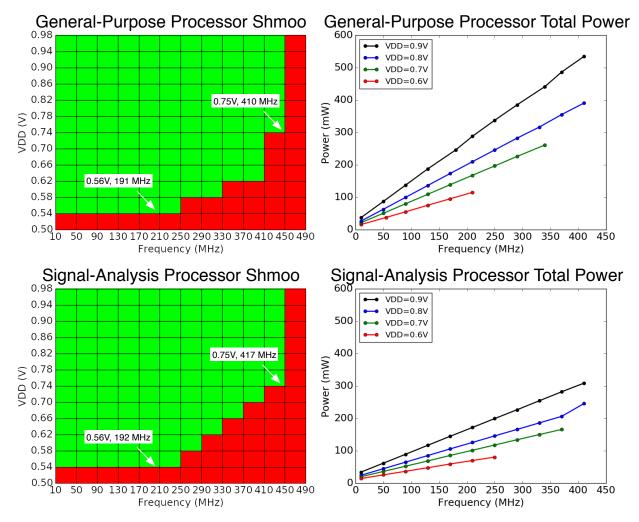

|      | Both processors function under similar operating condition ranges. The general-                                    | 00  |

|      | purpose processor consumes more power because of the 8 MB main memory                                              | 95  |

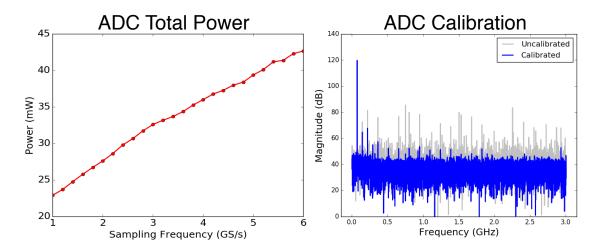

| 6.14 | Typical ADC power consumption is less than 50 mW at 0.9V. Calibration of the                                       |     |

|      | ADC reduces noise and spurs.                                                                                       | 96  |

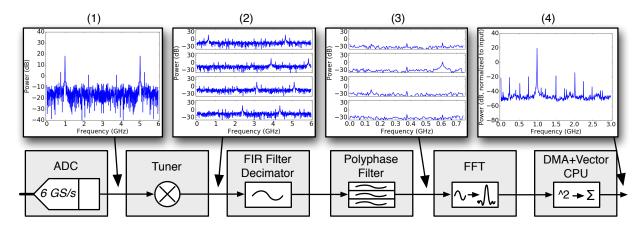

| 6.15 | Spectrometer signal processing example. Snapshots captured in the SAMs. (1) A                                      |     |

|      | real-valued signal is sampled through the calibrated ADC, producing a symmetric                                    |     |

|      | spectrum. (2) Four tuner LO frequencies are mixed with the input, producing                                        |     |

|      | four frequency-shifted spectra. (3) These spectra are low-pass filtered and down-                                  |     |

|      | converted by 8, resulting in four separate frequency bands. (4) The bands are                                      |     |

|      | Fourier transformed, accumulated, and combined on the CPU. This figure shows                                       |     |

|      | 100 accumulated spectra                                                                                            | 96  |

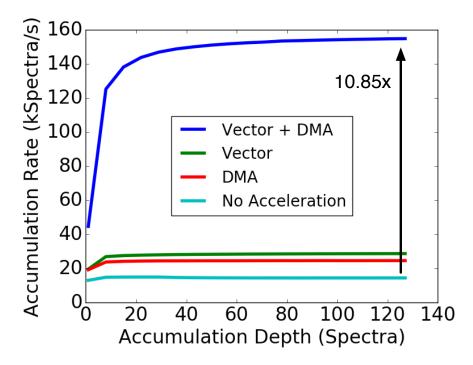

| 6.16 |                                                                                                                    |     |

|      | 10x. This plot includes the overhead of sweeping the tuner frequency to monitor                                    |     |

|      | four frequency bands, so each spectrum is 512 channels                                                             | 97  |

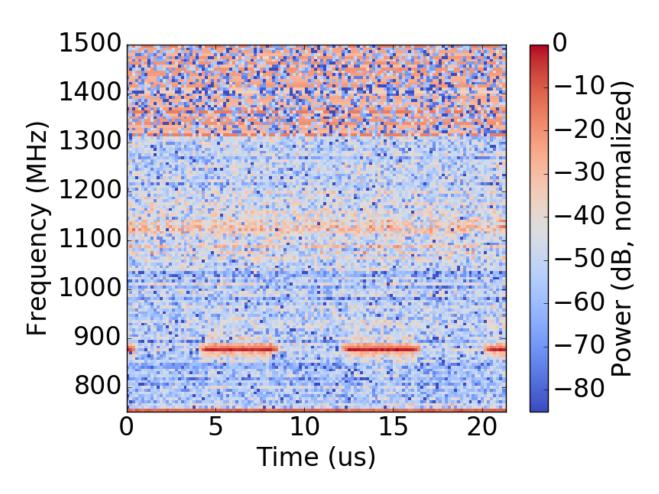

|      | Measured spectrogram of a 4 us pulse at 876 MHz                                                                    | 98  |

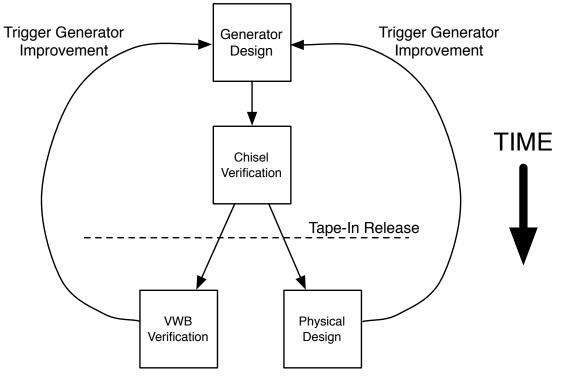

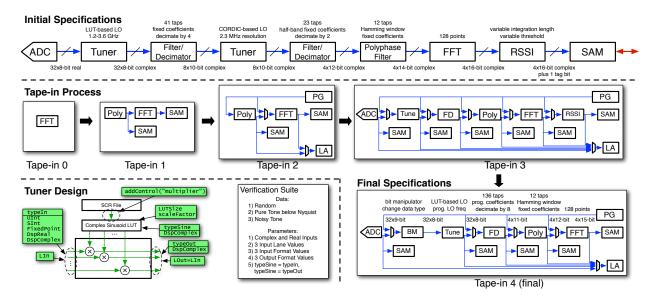

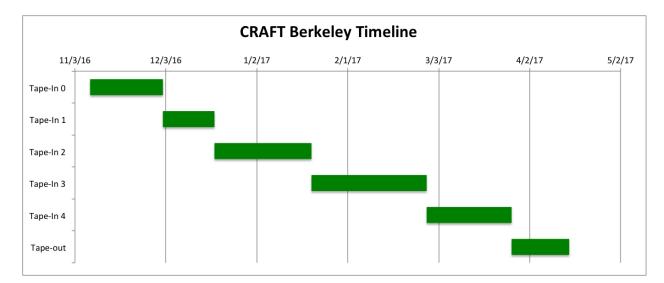

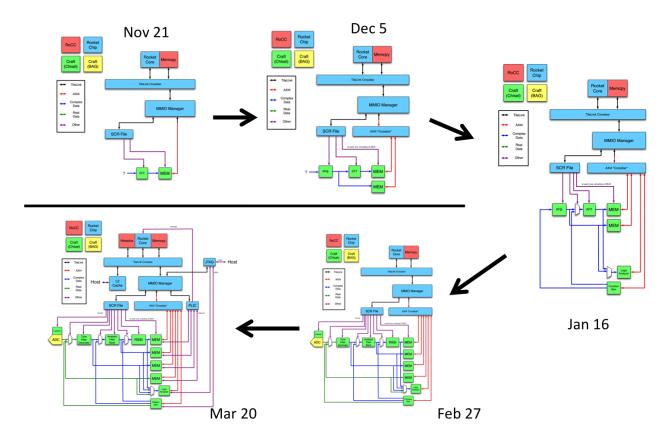

|      | 1                                                                                                                  | 100 |

| 6.19 | Radar processor design flow. Top: Initial customer specifications. Middle: Agile                                   |     |

|      | design evolution, Bottom-Left: Example tuner design showing parameterization                                       | 101 |

| 0.00 | 0                                                                                                                  | 101 |

|      |                                                                                                                    | 102 |

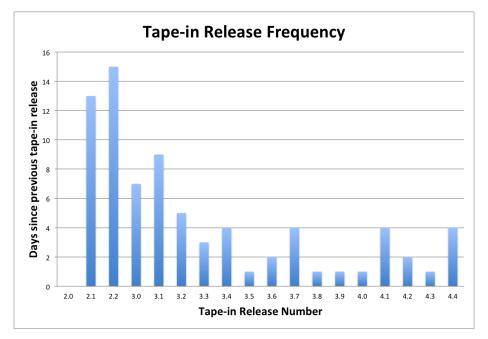

| 0.21 | The incremental addition of features in the framework and design defined a tape-                                   | 100 |

|      | in schedule, which quickly broke down.                                                                             | 103 |

## List of Tables

| 1.1 | Agile software development led to more projects finishing on time, where "finishing" means delivering a product that satisfies the customer [16]                                                                                                                                                                                              | 3  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | A comparison of properties in the 802.11ac WiFi and LTE standards                                                                                                                                                                                                                                                                             | 22 |

| 5.1 | Properties of recently published digital spectrometer backends suggest a single parameterized generator covering the gamut of possible design choices would avoid repeated design efforts.                                                                                                                                                    | 50 |

| 5.2 | PFB Parameterization                                                                                                                                                                                                                                                                                                                          | 54 |

| 5.3 | FFT Parameterization                                                                                                                                                                                                                                                                                                                          | 56 |

| 5.4 | Comparison of state-of-the-art ASIC spectrometers                                                                                                                                                                                                                                                                                             | 70 |

| 6.1 | Breakdown of operations in the signal-analysis processor. Each operation is per-<br>formed once per cycle. C represents a complex number, R represents a real num-<br>ber, and square braces show the number of bits for that operand. I assume $C \times R$<br>is 2 multiplies, $C \times C$ is 3 multiplies and 5 adds, and $C+C$ is 2 adds | 94 |

| 6.2 | Comparison of state-of-the-art ASIC spectrometers                                                                                                                                                                                                                                                                                             | 97 |

|     | 1 1                                                                                                                                                                                                                                                                                                                                           |    |

#### Acknowledgments

The PhD journey is not a solitary sojourn; rather, it requires one person to work with countless others, both past and present, to push the bubble of knowledge outward one iota in one direction. I would like to acknowledge the shoulders on which I stood and the arms that held mine during this adventure. Thanks to those mentioned here, and thanks to those not mentioned who also participated in my efforts. I could not have it done it without y'all.

Thanks to my undergraduate advisor, Professor Mircea Stan, and UVA Professor Ben Calhoun, for pressuring me to apply for PhD programs. And thanks to fellow UVA student Kevin Linger; our competitive views on exams and thorough exploration of SRAMs in our class project forced me to expand my knowledge. Kyle Powers, I hope when you took over my resilient adder project that you learned from my mistakes and improved upon the simple ideas of that project.

My first few years of graduate school were replete with classmates who all formed a tightknit group of dedicated learners. Garen Der-Khachadourian, thanks for being my project partner and friend, helping me to feel comfortable in a new state and new school. Ben Keller, you still astound me with your efficiency; I learned a lot from you while we shared classes and projects. Pi-Feng Chiu, thanks for pushing me to attend core blast, and for sharing the learning of CAD tools during the Raven projects with me. Rachel Hochman, you helped me keep my interest in space alive, and I enjoyed our pre-radio lab Chipotle runs. Angie Wang, in you I finally found a more perfect perfectionist than myself. Nathan Narevsky, you're doing great. And thanks to all the other students in my year, including Jackie Leverett, Yongjun Li, Amanda Pratt, Bonjern Yang, Ozzy LaCaille, and any others I've forgotten.

Most of my learning came from mentoring by students and postdocs above my year. Brian Zimmer, you embody the ideal that all students hope to achieve. Thanks for your patience, teachings, and exemplary attitude. Yunsup Lee, hopefully one day I can keep up with your typing speed. Jaehwa Kwak, thanks for being the lighthearted one who taught me that work is not without play. Ruzica Jevtic and Miki Blagojevic, how you both put up with my inexperience I'll never know. Martin Cochet, you were the nicest project partner ever. And to my other instructors, Michael Zimmer, Yue Lu, Lingkai Kong, and those I have forgotten, it is because of you I've learned so much.

Other project and tape-out partners where invaluable in completing my program in a timely manner. These include John Wright, Jaeduk Han, Amy Whitcombe, Eric Chang, Zhonkgai Wang, Nandish Mehta, Colin Schmidt, Adam Izraelevitz, Edward Wang, Chick Markley, Keertana Settaluri, Woorham Bae, Albert Magyar, Alon Amid, Richard Lin, Howie Mao, and Paul Rigge.

The Berkeley Wireless Research Center provided the tools and support I needed to get through this program. So thanks to the students, staff, and faculty of the BWRC, especially James Dunn and Brian Richards. And thanks to various BWRC collaborators, both inside and outside Berkeley, including Calvin Cheng, Aaron Parsons, Hong Chen, Rick Raffanti, Robert Jarnot, Paul Stek, JPL, STMicroelectronics, Cadence Design Systems, and Northrop Grumman Corporation. My projects were funded in part by the DARPA PER-FECT project (HR00111320007) and Berkeley's ASPIRE program, NASA's Earth Science Technology Office's Instrument Incubator Program as part of the *Compact, Adaptable Microwave Limb Sounder* project, grant number NNX12AK39G; the DARPA CRAFT program (HR001116C0052); and the Intel iSTC on Agile Design (ADEPT).

Finally, thanks to my parents, Sandy and Tim, who continue to support me in all I choose to do.

## Chapter 1

## Introduction

### 1.1 Motivation

Signal processing system designers trade off algorithmic hardware design metrics like performance, area, and power for development time. The first choice is between off-the-shelf (CPUs or DSP-based processors), reconfigurable (FPGAs), or custom (ASICs) hardware [17]. Writing software for existing CPUs saves time and money, but such applications will never approach the low power, high performance, and small volume of specialized hardware often needed for embedded signal processing applications. And though FPGAs provide a convenient middle ground, high-end signal processing applications require high-end, applicationspecific integrated circuits (ASICs) to meet cutting edge specifications. However, designing custom chips imposes a burden on both the budget and the timeline of a project. Typically quoted non-recurring engineering (NRE) costs are in the tens of millions of dollars stemming from the complexity of design, verification, validation, and programming that takes many engineer-years and prototypes before calling the design finished. Figure 1.1 shows the tradeoff between development time and power consumed by a particular design from DARPA [1].

Figure 1.1 also shows a rough breakdown of where the development time goes and why it takes so long to produce custom hardware. First, the design itself consumes development time. There is no standard design framework above Verilog RTL that is universally accepted, so academic researchers and commercial design teams often develop their own in Python [18], Perl [19], SystemVerilog [20], C++ [21], and Simulink [22]. at different abstraction levels (RTL, HLS). And though attempts have been made, few frameworks outside of hardened IP couple RTL design with physical design, so even RTL reuse requires new physical design development. This is somewhat evident by Intel's tick-tock methodology [23], whereby moving to a new technology is equated in time with redesigning and optimizing the architecture. Second, verification suffers a similar lack of consistency, and it arguably consumes more work hours, sometimes as high as 70% [24]. In signal processing, a typical flow connects Verilog designs to MATLAB (or sometimes Python) golden models using SystemVerilog direct programming interface (DPI) function calls to a C program, which runs

Power and Development Time trade-off

Example data from representative DoD design, 2015

Figure 1.1: ASICs are much lower power than CPUs but require significantly more development time for a particular application [1].

MATLAB library routines [25]. However, this translation complicates the process and can lead to errors. Third, physical design flows take significant time to both set up and run. Even minimal design changes necessitate rerunning a full synthesis and place-and-route run, so much of CAD tool runtime is spent redoing the same optimizations [26]. Finally, fabrication and testing present time costs that, as bugs are found, require repeated fabrication and testing. Including sufficient design-for-test (DfT) structures and backup measures can reduce the time to find bugs and yield issues introduced by physical design and fabrication [27]. Entire tools exist solely to estimate the effort, cost, time-to-market, etc. of custom hardware projects [28].

One effort to tackle the latency of hardware design focuses on agile development, a phrase borrowed from software. The original agile manifesto came out in 2001 [29]. It promoted four values, which are copied below:

Figure 1.2: A comparison of waterfall and agile software development paradigms shows the differences in development cycles and project completion timeframes. Waterfall development uses a top-down approach and frequently takes over a year. Agile development uses a smaller, iterative approach with sufficient results completed in less than a year.

Table 1.1: Agile software development led to more projects finishing on time, where "finishing" means delivering a product that satisfies the customer [16].

| Approach  | On Time | Late | Canceled |

|-----------|---------|------|----------|

| Waterfall | 10%     | 52%  | 38%      |

| Agile     | 76%     | 20%  | 4%       |

- 1. Individuals and interactions over processes and tools.

- 2. Working software over comprehensive documentation.

- 3. Customer collaboration over contract negotiation.

- 4. Responding to change over following a plan.

These principles were in contrast to the traditional software development model, termed waterfall development. Waterfall development took a top-down approach, nearly completing each step in the flow before moving on to the next. This caused long project cycles, delays in product release, and sometimes even project cancellations. Agile development recognized the need for communication and adaptation, and projects following agile principles tended to finish on time much more frequently than those following the traditional waterfall style [16]. Figure 1.2 compares waterfall and agile software development styles, and Table 1.1 compares project success rates for each. It's important to emphasize that not all project completions are equal. Just because a project is declared finished and on time does not mean it meets all project goals, perform all the initially desired features, or contain complete documentation. Rather, features were incrementally added over time, adjusting to changing customer specifications. When the project deadline hit, a sufficient version was declared complete. But the agile argument declares this superior to a significantly delayed or canceled product, as, indeed, delay is expensive [30].

A form of agile development has been deployed in processor system design efforts. Companies have more recently used agile hardware development to varying degrees of success [31, 32]. This success hinges on adoption and agreement by the design team members on the details of agile development and how it applies to their work. Software and hardware are inherently different, as hardware product timeframes are heavily quantized on the order of about a year, and quick updates are all but impossible. So agile hardware design must still avoid show-stopping bugs and ensure sufficient verification coverage the first time around. Academics have attempted to solidify a modified form of the software manifesto into a set of principles more relevant to hardware development. These agile hardware development principles include (from [33]):

- 1. Functional (albeit incomplete) prototypes over fully featured models.

- 2. Collaborative, flexible teams over rigid silos.

- 3. Improving tools and generators over improving the instance.

- 4. **Responding to change** over following a plan.

Successful use of these principles has yielded complex SoC systems built within a limited timeframe by small teams of designers [33]. These 11 chips built over 5 years by a total of about 20 students and staff tested a new dynamic voltage and frequency scaling paradigm and CMOS silicon photonics designs in multiple technology nodes using and reusing a RISC-V

Figure 1.3: A comparison of traditional, open-loop design flow with our agile, iterative design flow. Changing specifications and issues during the process trigger generator improvement work. Design generators are also portable across designs, so these iterative enhancements persist.

central processor. Some of these team members have since gone on to apply their rapid design skills to the corporate world [34]. Figure 1.3 shows the traditional waterfall development style compared to an iterative, agile hardware design process used by the students. It's clear that such a flow responds to change more easily, and that solved issues become embedded in the design generator and propagate to future designs. Moving forward, agile hardware design, when applied correctly, is an effective tool for rapidly producing RISC-V processor chips.

Agile hardware development was previously applied to general purpose ASICs, but to date no efforts are known that successfully apply these principles to signal processing ASIC development. Though tools exist that support rapid development of signal processing ASICs. For example, Xilinx's System Generator for DSP [35] offers a graphical design interface, but it targets FPGA platforms, so results are often optimized for FPGA resources and not immediately suitable for ASIC implementation. MathWorks offers HDL Coder, which generates RTL from MATLAB and/or Simulink models [36]. But without easy access to gatelevel manipulations of algorithms, a user can easily write suboptimal designs that explode in size or suffer in hardware performance. Previous work has attempted to map designs from FPGA design environments to IC-suitable Verilog, which speeds up the design and verification process at the algorithmic level, but not at the ASIC level [37, 38]. It's common practice instead to design for ASICs and map to FPGAs for verification, as this ensures the hardware is optimized for custom circuits and not targeted to fit in the LUTs and BRAMs efficient for an FPGA. The DSP designs are typically accelerators tightly coupled with general-purpose processors [39] or dataflow models mapped directly into hardware [40]. Accelerators are more flexible but less performant and require more programming overhead.

In summary, ASIC signal processors are necessary to achieve the high performance and low power requirements of modern applications, but their long development time hinders their progress and ubiquity. A significant percentage of their development time goes into the design and verification of the architecture, with the remainder consumed by back-end ASIC flow work. Agile hardware principles, borrowed from a similar successful software approach and previously applied to general-purpose processors, offer a promising solution to signal processing SoCs. But such a solution has yet to be viably demonstrated on real systems running real applications.

### **1.2** Background

Traditional signal processing ASIC design, shown in Figure 1.4, follows a waterfall development model: the algorithm is designed, then this algorithm is mapped to an RTL implementation, and finally the RTL is synthesized and placed-and-routed to create a chip [2]. MATLAB or Python numerical libraries are used to explore algorithmic considerations, typically in floating-point precision. The translation to fixed-point introduces quantization errors, so the algorithm is adjusted to accommodate the added noise. Once a suitable fixed-point RTL implementation is ready, physical design begins. Issues with constraints like timing, area, and congestion further necessitate algorithm and RTL modifications. And eventually, once the chip is ready, the final product looks quite different from the initial concept. Also, the finished design works well for this application and technology, but porting the design to a new process or application generally requires starting the process over.

The rest of this section explores these pieces and previous attempts at improving productivity in the design of digital signal processing hardware.

Simplified Traditional Digital Signal Processing Hardware Design Flow

Figure 1.4: Traditional DSP hardware design produces an instance tailored to the specific application and technology. It is not easily reusable across applications and technologies [2].

#### **1.2.1** Signal Processing Models

Specific applications are discussed in Chapter 2, but this section provides an overview of generic signal processing models. Algorithms are often designed in MATLAB or Python (especially with the NumPy and SciPy libraries) since they provide both a simple programming interface and pre-designed library components for signal processing. An algorithm defines which computational kernels are performed on which data, e.g. performing digital down conversion (DDC) requires mixing a signal with an LO to down convert it, then applying a low-pass filter to remove aliases. One algorithmic modeling technique represents these kernels as nodes in a flow graph, with edges representing data moving between kernels. Software models consider how the computation moves through the data, or how the data move through the computations. For example, DDC could be executed sequentially, with mixing and filtering performed one after another on each datum, or in parallel, with mixing and filtering performed simultaneously on a parallel set of data. The software model should be influenced by the hardware model. A general-purpose processor can handle either sequential or stream processing, though it will not take advantage of the data locality and consistent kernel sequencing of stream processing. Other hardware models specialize in stream processing, and will perform a DDC much more efficiently. Algorithms are often used as golden models for correctness verification, software models should efficiently "glue" algorithms and hardware, and hardware models should take advantage of commonly occurring algorithmic paradigms to optimally process signals. This section explores computational, software, and hardware models.

#### **Computational Models**

Signal processing computes on large, or sometimes infinite, data sets. However, the control flow for signal processing is often simple. These realizations permit a modeling approach that is focused on how data moves through computational kernels, rather than one that determines which computations to perform on the data. Kahn process networks do this by representing streams of data as edges in a directed graph, and computation as nodes. The most common subsets of these data flow graphs are synchronous data flow (SDF) and asynchronous data flow (ADF) [41].

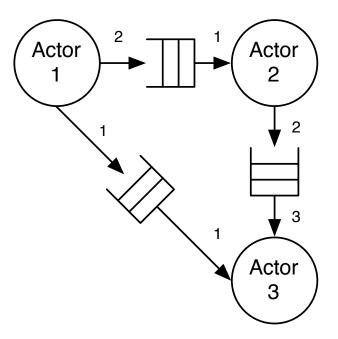

Figure 1.5 shows an example of a simple SDF system. In synchronous data flow, nodes, sometimes called actors, transform input data tokens in some way to produce output tokens. Tokens are typically sets of data. To account for rate mismatches between consumption and production, FIFO buffers are often employed between actors. The data flow graph is synchronous because each actor consumes a fixed number of tokens and produces a fixed number of tokens each time it fires. This feature allows for static scheduling, so compilers can ensure FIFO depths are minimal and throughput is guaranteed without concerns for excessive backpressure. In asynchronous data flow, rates of production and consumption are not fixed, meaning they vary with data or time. Static scheduling is no longer possible, so runtime scheduling is required. This leads to much more complex control flows.

Figure 1.5: Simple synchronous data flow model showing actors as nodes connected through FIFOs as edges. Production and consumption rates are fixed and shown on the figure. Fixed rates support static scheduling.

More formally, a Kahn process network (KPN) is an example of a distributed or concurrent computational model. Operations happen in parallel as data moves through them. But a KPN cannot express complex control flow succinctly. Sequential models are one alternative, though they are less suited for signal processing. In sequential models, operations typically move through the data, where data-dependent control flow is easier to handle. One operation happens at a time, and data may or may not be accessed randomly. Examples of sequential models include finite state machines and Turing machines. Computational models are useful for describing algorithms in meaningful ways, but translating these models into something capable of being computed by a modern computer is nontrivial.

#### Hardware Models

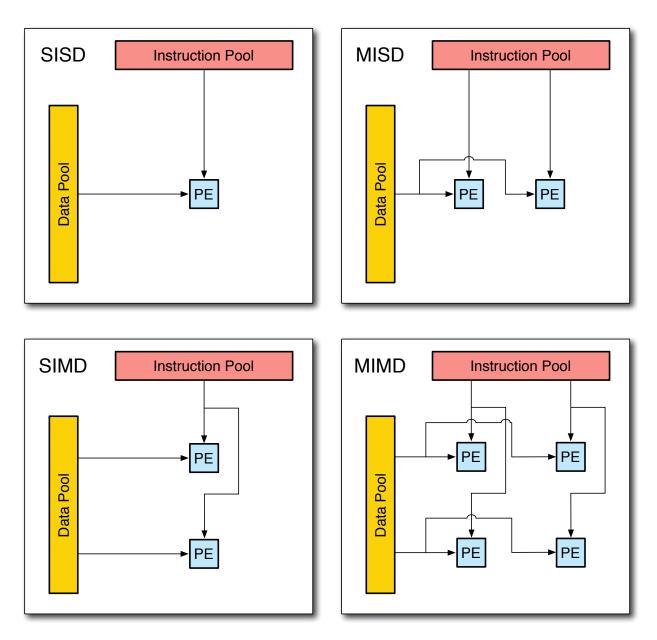

The choice of hardware influences which software model is needed, thus we begin by exploring how to map from computational models to gates. A custom hardware mapping requires an extensive, low-level design effort but limits the amount of software needed. Reusing an existing, flexible hardware solution is also possible but requires a more complex software layer. Flynn's taxonomy condenses hardware models into dimensions of instruction concurrency and data concurrency. Extra dimensions, such as the memory architecture (centralized or distributed) and thread support add richness to the original taxonomy, allowing it to usefully model a wider array of architectures. Figure 1.6 shows the set of architectures in Flynn's taxonomy. Single instruction single data (SISD) performs a single instruction on a single piece

Figure 1.6: Flynn's taxonomy of computer architectures.

of data in every time step. Typical minimal processor cores are SISD architectures. Multiple instruction single data (MISD) performs a multiple instructions on a single piece of data in every time step. While rarely used, MISD supports applications requiring fault tolerance. Single instruction multiple data (SIMD) performs a single instructions on multiple data pieces in every time step. Examples of SIMD processors are vector machines and GPUs. Multiple instruction multiple data (MIMD) performs a different instruction on each data piece for each processing element (PE) in every time step. MIMD processors offer the most performance for targeted applications (modern supercomputers use MIMD architectures).

Centralized memory-based hardware operates on data stored in random access memory. Sequential computational models and sequential or vector software models map closely to memory-based hardware. Data are often stored in various locations in memory, so random access is needed to gather data before performing an operation on it. Thus data movement and indexing become significant computational overheads in memory-based hardware designs. However, complex control flow is feasible, so algorithms with heavy data dependence require memory-based hardware to execute. Signal processing in memory-based hardware is done either through ALUs performing multiply accumulate (MAC) operations, LUT-based arithmetic, or any other processing element [42].

Some general-purpose processors offload specific computational kernels to accelerators designed to quickly compute those kernels. A SIMD or vector co-processor is an example of an accelerator. Previous work showed that accelerating thirteen *motifs* would sufficiently cover the space of computational needs [39]. This approach is much more flexible, allowing a processor to compute a wider array of applications efficiently. In reality, the only accelerators modern processors contain are some kind of parallel computational accelerator (such as a GPGPU) and/or very specialized accelerators (such as an LDPC decoder or MPEG decoder). This is done because programming applications to target generalized accelerators requires expert knowledge, and tuning that application for a specific accelerator instance is difficult to automate [43]. Also, many applications are memory or IO bound instead of compute bound, so building memory access accelerators instead of compute accelerators may be more productive [39].

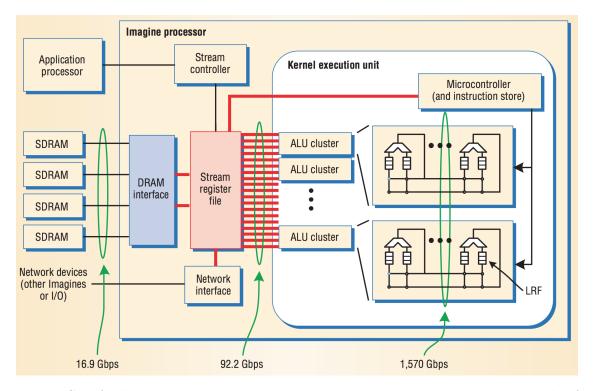

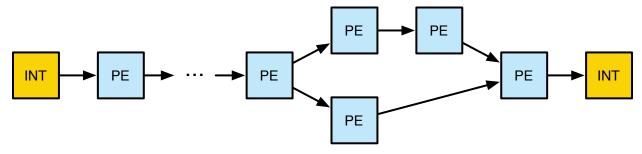

Data-heavy workloads and high-throughput requirements push architectures further toward specialization. Stream processors provide flexible signal processing kernel capabilities while optimizing memory for streaming data [3], as seen in Figure 1.7. At a high level, stream processors place ALU clusters or vector operation accelerations in series (a type of MIMD architecture), allowing data to flow from one to the next without the overhead of memory reads and writes in between. Such an architecture performs signal processing algorithms efficiently, but maximizing throughput and minimizing power requires a custom ASIC. Many application-specific processors exist to support common applications, but they lack flexibility.

Signal flow graphs (SFGs) are useful representations for how data moves through computational kernels. While these graphs map more directly to custom hardware, they can also be translated to SIMD or accelerator-based architectures. In this case, the same kernel (node on the graph) is computed in parallel on different data sets. Languages like Cuda and OpenCL

Figure 1.7: Stanford's Imagine stream processor. Bandwidths assume a core clock of 180 MHz [3].

support mapping of C code to SIMD architectures. But performance becomes limited when control flows diverge, such as when half the parallel graphs do not need to compute the current kernel. Whole Function Vectorization (WFV) is one automated approach to solving this through an automated compiler [44].

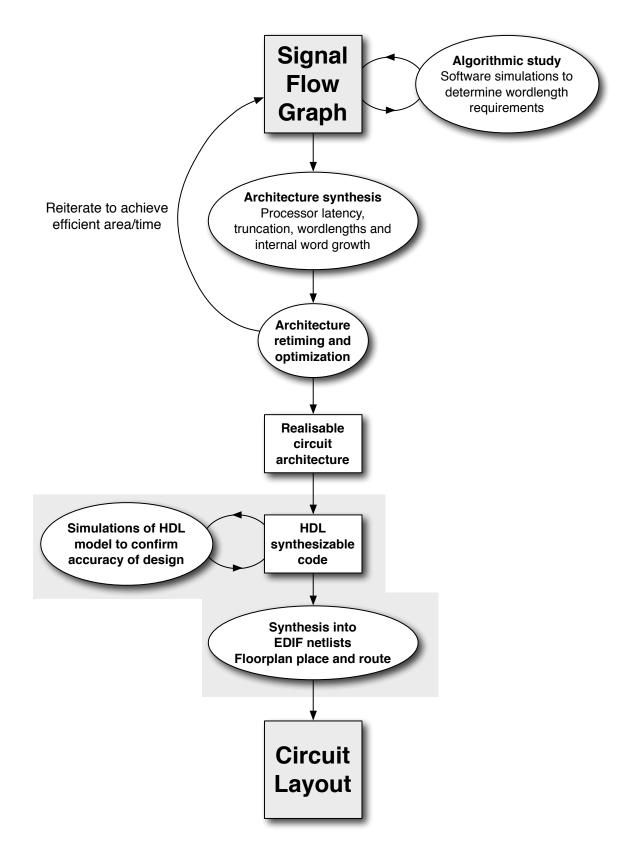

Mapping from a signal flow graph computational model to custom hardware is a multistep process with iterative development and feedback, as illustrated in Figure 1.8. General purpose processors already contain reasonable hardware architectures, so this mapping assumes custom hardware is desired. Also, SFGs typically assume distributed memory and embed concurrency into the graph structure, so optimizing the hardware may require adjusting the SFG. First, the precision requirements of an SFG must be explored to determine appropriate data types and word lengths. Next, the SFG is mapped to a hardware architecture, ideally with reusable blocks. This step involves converting graph nodes into HDL models and graph edges into HDL interconnect. It requires verification that the hardware matches the algorithm. It also requires the exploration of timing, with concurrency within a node affecting algorithmic latency and throughput. Finally, the hardware model is ready for further mapping to an FPGA or ASIC. The rest of this section explores alternate hardware implementations which require a software layer to convert between the computational model SFG to the hardware model.

Figure 1.8: VLSI circuit design flow [4].

#### Software Models

Software models for signal processing algorithms typically fall into a few modes of concurrency, namely sequential execution, vector processing, and stream processing. Sequential execution performs one computation at a time, stepping through data and kernels one after another. Listing 1.1 shows pseudocode for sequential execution of an operation that adds two 100-element arrays, then squares the result. Ordering the operations as data-first or kernel-first takes the same amount of time because each operation is performed sequentially. However, the order may affect the maximum memory requirement.

Listing 1.1: Sequential software model

```

for (int i = 0; i < 100; i++)

sum[i] = a[i] + b[i]

sqr[i] = sum[i] * sum[i]</pre>

```

Parallel processing is usually a single-instruction multiple-data (SIMD) paradigm which performs the same operation in parallel on multiple data. A SIMD version of the previous code might look like Listing 1.2, where a 25-element vector operation is assumed available. Typical SIMD architectures fix the vector length and require vector-scalar operations to be expanded into vector-vector operations. Typical vector architectures provide variable vector lengths per iteration and support both vector-vector and vector-scalar operations [45].

Listing 1.2: Vectorized software model

```

for (int i = 0; i < 4; i++)

start = i*25

end = (i+1)*25

vector_add(sum[start:end], a[start:end], b[start:end])

vector_mul(sqr[start:end], sum[start:end], sum[start:end])</pre>

```

Finally, stream processing streams data through kernels, where allocation, synchronization, and communication between processing units is not handled by a CPU explicitly. This is equivalent to having multiple accelerators that support chaining. Processing units are initialized and data are gathered in the first step. Execution involves invoking kernels onto data sets. And at the end, results are returned, typically by "scattering" back to memory locations. Listing 1.3 shows pseudocode for a stream processing algorithm.

Listing 1.3: Streaming software model

```

kernel0 = kernel.init(add)

kernel1 = kernel.init(mul)

stream0 = gather(a)

stream1 = gather(b)

sum = kernel0.invoke(stream0, stream1)

sqr = kernel1.invoke(sum, sum)

```

#### **1.2.2** RTL Design Frameworks

Translating algorithms and hardware models into synthesizable designs requires choosing an implementation language and paradigm. This section discusses the large number of programming and modeling languages available, and it explores the pros and cons of each. The discussed projects and languages accelerate the writing of synthesizable hardware by mapping higher-level constructs into lower-level RTL. Some of the ideas compiled here were first presented in [46].

High-level synthesis tools abstract away low-level implementation details from the algorithm to hardware translation process. HLS code is written in extensions to C, MATLAB, and SystemVerilog (see SystemC, ANSI-C/C++, Bluespec SystemVerilog [20]). For example, Xilinx Vivado allows designers to use C, C++, or SystemC to describe algorithms that are then compiled into RTL [47]. Bluespec uses guarded atomic actions, where actors fire atomically once some guard condition is met, which may or may not be the same as the SDF guard (input tokens are ready and output space is available). HLS is especially useful for designing blocks that require complex memory access scheduling, deep pipelining, and more generally, sequential logic. However, many DSP datapaths exhibit high degrees of parallelism that are best described structurally, necessitating that the SystemC code be carefully structured. Functionally correct algorithms often produce inefficient or even unsynthesizable code. Finally, hardware generation from recursive functions is generally not allowed, except through template metaprogramming.

MathWorks Simulink can save about 30% in design time [48] when systems are built from pre-existing IP by allowing users to pass intent to early stages of design and verification in a model-based design framework. It supports systems validation/verification with floatingpoint simulations and uses application-representative test vectors to optimize fixed-point bitwidths. The Simulink environment supports the "Chip-in-a-Day" methodology [49] but only accelerates a single instance's design for a single hardware platform, rather than accelerating *generator* design targeting *multiple* platforms. It lacks transparent, programmatic and easily extensible abstractions, requiring significant manual work to support multiple targets (FPGA/ASIC) and multiple data types. Unlike Simulink, HDL coder is platform-agnostic, meaning pre-existing IP and library designs map to a variety of FPGAs and custom ASIC designs. However, without difficult low-level manipulations, signal processing RTL is often insufficiently optimized [46].

High-level models and abstractions of data processing can simplify ASIC design efforts, but they present a large disconnect between the design and implementation of an algorithm. Generators support reuse of ideas and designer methodologies rather than IP instances, which often fail to meet the specific requirements of a new system. They also bridge the gap between algorithm design and RTL implementation better. Generator-based methodologies include simple constructs like **genvar** and parameters in Verilog, though this is insufficient to capture high-level designer intent. Perl and python scripts wrapped around Verilog (or even inside SystemVerilog, such as Stanford's Genesis2 [19]) are a cumbersome albeit common approach to extending parameterization and generation of RTL. Because Genesis2 relies on two decoupled languages, there is a higher likelihood of generating difficult-to-debug syntax errors. Spiral is a generator specifically targeting DSP hardware [50]. Although powerful, Spiral is designed for static function generation and is not well suited for dynamic or reconfigurable architectures. New domain-specific languages (DSLs), such as Berkeley's Chisel [51] and Stanford's Magma [52], enable powerful processor generators but come with a steep learning curve [15]. But even IP generators are only as (re)useful as their interoperability. Efforts to standardize interfaces and IP metadata have produced AMBA protocols like AXI, APB, and AHB, and design XML files like IP-XACT [53, 54]. Existing commercial tools support automated verification of designs using these standards through the universal verification methodology (UVM).

Hardware construction/generation languages like Bluespec (closed-source) and Chisel (open-source) enable systems modeling, generator construction, and test environment creation all within a single, but powerful, underlying language with both functional programming and object-oriented constructs [20, 51]. They support (1) custom-defined types for high-level number abstractions, (2) stronger type-checking to catch errors at compile-time, (3) type polymorphism and operator overloading for hardware template parameterization, (4) recursive functions for hardware generation, and (5) functional constructs like map and reduce that help to concisely express highly structured data paths (more so than SystemC). Bluespec and Chisel are both architecturally transparent, exposing fine-grain implementation details for optimization that are typically hidden by HLS tools and allowing for more optimization opportunities.

#### 1.2.3 System Design

Any digital design must interface with the real world eventually. These interfaces are typically analog designs, with common examples being PLLs for clock generation; high-speed serial links for communication; analog-to-digital converters (ADCs) and digital-to-analog converters (DACs) for data domain conversion; low-dropout (LDO), switched capacitor, and boost/buck regulators for power supply generation; and antennas, amplifiers, and mixers for radio signal processing. Most analog designs are hand created and customized heavily for each application, but recent work in producing analog generators shows that alternative, automated design approaches are possible [55]. The digital generators presented in this thesis should be considered in a system context which includes analog generators, as exemplified in some later chapters.

Building and verifying digital integrated circuits is a difficult task, but no design is complete without test structures to prove functionality post fabrication. Good DfT requires

- 1. large coverage as quickly as possible

- 2. limited intrusion into the design

- 3. limited area, power, and performance overhead

#### 4. useful feedback when tests fail

Typical test methods are *structural*, meaning they only care about the logic gates implemented and not the function of the circuit. The most common approach is through scan chains, which combine all or a subset of registers in the design into long chains when scan is enabled. Data may be shifted in and out, or propagated through combinational logic through toggling of the scan clock, resulting in extensive controllability and observability with limited overhead. Automatic test pattern generation (ATPG) seeks to create good input and output test vectors, where *good* may mean high coverage, fast runtime, localized error isolation, or a combination of these. This largely solves verification of the instance, where the fabricated design is tested for equivalence to the placed-and-routed model (which, hopefully, was verified to match the RTL logic).

Validation is the process of proving that the design meets the needs of the customer. Functional tests should be solved through validation routines, which depend on the design's intent. Providing functional test points in the system is one solution. These may be pattern generators to drive known data into the logic, or logic analyzers to monitor and snapshot data at key design boundaries. Having direct outside access to these test points is ideal, as any intervening logic could also be a source of error. Thus many designs implement debug modes and ports. On-chip validation support is necessary because involved validation routines often take too long to simulate.

### **1.3** Thesis Outline

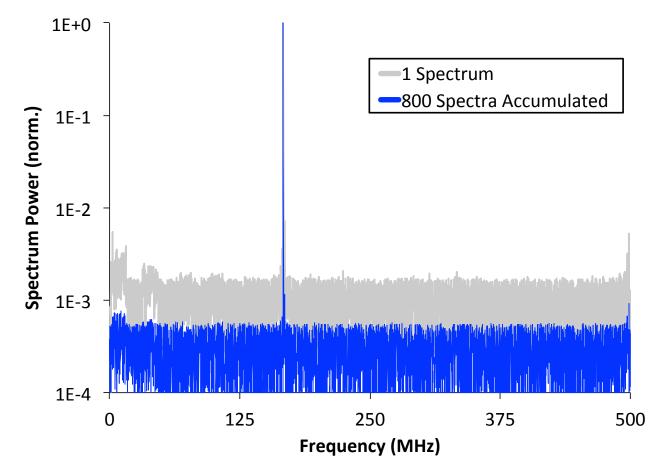

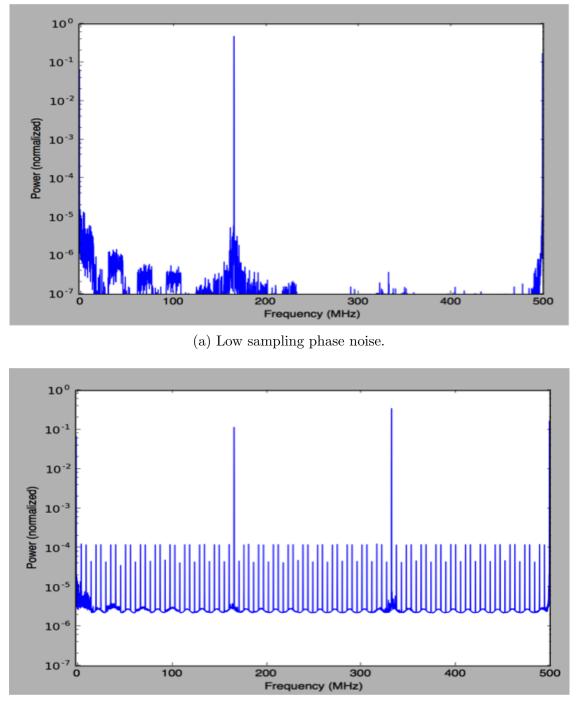

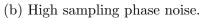

This thesis solves the issue of slow signal processing ASIC design by creating a set of tools and methodologies that support agile development principles. It then applies those tools in the creation of several signal processing ASICs.