Precise Pulse Discrimination for Space-Based Timing Front Ends

By

Lydia Lee

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Kristofer S.J. Pister, Chair Professor Vladimir Stojanovic Professor Wenbin Lu

Summer 2023

Precise Pulse Discrimination for Space-Based Timing Front Ends

Copyright 2023 by Lydia Lee

#### Abstract

#### Precise Pulse Discrimination for Space-Based Timing Front Ends

by

Lydia Lee

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Kristofer S.J. Pister, Chair

The conversion of trigger events to their digital equivalent is a central component of any timing-based front end, with applications found in mass spectrometry, single channel analyzers, and a huge variety of 3D mapping and ranging systems. At the same time, evertightening size, weight, and power budgets for space launches with a skyrocketing (no pun intended) number of launches in the last decade have made application-specific integrated circuit solutions increasingly appealing. However, conventional analog methods of pulse discrimination introduce timing walk or are limited to a narrow range of pulse shapes, while early-stage digitization requires impractically high sample rates for the events in question.

This work presents the analysis, design, and measurement of an integrated constant fraction discriminator with theoretically zero timing walk and a programmable, constant trigger fraction which does not depend on input pulse shape. The specific silicon presented here was designed for the Solar Probe Analyzer for Ions as part of its time-of-flight mass spectrometer to determine the ion composition of space plasmas. This dissertation discusses the front end requirements for a radiation hardened pulse discriminator in the context of SPAN-Ion. We then address the architectural modifications used to achieve a pulse shape-independent constant trigger fraction, as well as the analog and digital hardening techniques required to detect, correct, and/or mitigate radiation-induced effects. Finally, this work presents the first attempt at an integrated pulse-shaping front end for SPAN-Ion, concluding with simulation results from a more recent chip and a discussion of future work both for SPAN-Ion and for further code base development. To my family and friends (pets included).

# Contents

| Co            | onten | ts                                   | ii           |

|---------------|-------|--------------------------------------|--------------|

| $\mathbf{Li}$ | st of | Figures                              | $\mathbf{v}$ |

| Li            | st of | Tables x                             | ii           |

| 1             |       | oduction                             | 1            |

|               | 1.1   | The Solar Probe Analyzer for Ions    | 1            |

|               | 1.2   | Radiation and Integrated Circuits    | 5            |

|               |       | 1.2.1 Effects                        | 5            |

|               |       | 0                                    | 14           |

|               | 1.0   | 0                                    | 19           |

|               | 1.3   |                                      | 23           |

|               | 1.4   | Acronyms                             | 25           |

| <b>2</b>      | Puls  | e Discrimination 2                   | 26           |

|               | 2.1   | Topology Overview                    | 26           |

|               | 2.2   | Timing Walk                          | 29           |

|               | 2.3   | Afterpulse Rejection                 | 31           |

|               | 2.4   | Constant Fraction Discrimination     | 32           |

|               | 2.5   | SEE Watchdog                         | 37           |

| 3             | Chi   | $\mathbf{V}\mathbf{V}1$              | <b>3</b> 9   |

|               | 3.1   |                                      | 39           |

|               | 3.2   |                                      | 41           |

|               |       | 3.2.1 Power and Reference Generation | 41           |

|               |       | 3.2.2 No-Shape/Small Signal Chain    | 44           |

|               |       |                                      | 55           |

| 4             | Chi   | $\sim V2$                            | 64           |

| -             | 4.1   |                                      | 54           |

|               | 4.2   |                                      | 35           |

|               |       | ·                                    | 35           |

|              |            | 4.2.2   | Full/Main Signa                | l Chain |        |     |     | ••• |     |     |     |     |   |     |     |   | • | 67           |

|--------------|------------|---------|--------------------------------|---------|--------|-----|-----|-----|-----|-----|-----|-----|---|-----|-----|---|---|--------------|

| 5            | Con        | clusior | s and Future V                 | Nork    |        |     |     |     |     |     |     |     |   |     |     |   |   | 72           |

| 0            | 5.1        |         | -Press Design wi               |         | r      |     |     |     |     |     |     |     |   |     |     |   |   | 73           |

| Bi           | bliog      | graphy  |                                |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 75           |

| Δ            | SCN        | Л3x     |                                |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 83           |

| <b>1 L</b>   |            | -       | LDO                            |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 83           |

|              |            |         | - PGA Sensor In                |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 85           |

|              |            | 112 0   | 1 011 2011001 111              |         |        |     |     |     |     |     |     |     |   | • • |     |   | • | 00           |

| В            |            |         | igital Flow Doo                |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 90           |

|              | B.1        | Code I  | Base                           |         |        |     |     | ••• |     |     |     |     | • |     | • • |   |   | 90           |

|              | B.2        |         | $tion \ldots \ldots \ldots$    |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 91           |

|              | B.3        | -       |                                |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 94           |

|              | B.4        |         | ng the Flow                    |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 99           |

|              | B.5        |         | Idiosyncrasies .               |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 111          |

|              | B.6        | Signoff | •••••                          |         |        |     | • • | ••• |     |     |     |     | • |     | •   |   | • | 112          |

| С            | Ont        | ical Re | coivor                         |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 115          |

| U            | -          |         | ound                           |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 115<br>115   |

|              | C.1<br>C.2 | 0       | ummary                         |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 115          |

|              | 0.2        | -       | I/O                            |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 110          |

|              |            |         | Scan                           |         |        |     |     |     |     |     |     |     |   |     |     |   |   | $110 \\ 120$ |

|              | C.3        |         | Front End                      |         |        |     |     |     |     |     |     |     |   |     |     |   |   | $120 \\ 120$ |

|              | C.3<br>C.4 | 0       | Scheme                         |         |        |     |     |     |     |     |     |     |   |     |     |   |   | $120 \\ 127$ |

|              | C.4<br>C.5 |         | Test Structure .               |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 127          |

|              | C.6        |         | Base and Cadence               |         |        |     |     |     |     |     |     |     |   |     |     |   |   | $120 \\ 130$ |

|              | 0.0        |         |                                | LOCau   | 0115 . |     | ••• | ••• | ••• | • • | ••• | • • | • | ••• | • • | • | • | 100          |

| D            | BA         | G 2.0 S | $\mathbf{cripts}$              |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 131          |

|              | D.1        | Genera  | l Utilities                    |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 131          |

|              | D.2        | Scripts |                                |         |        |     |     | ••• |     |     |     |     |   |     | •   |   |   | 131          |

| $\mathbf{E}$ | Chi        | р V1 Г  | ocumentation                   |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 135          |

|              | E.1        | -       | ructure                        |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 135          |

|              | E.2        |         |                                |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 136          |

|              | E.3        |         | its                            |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 138          |

|              | E.4        |         | $etup \dots \dots \dots \dots$ |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 139          |

|              | E.5        |         | ce Locations                   |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 143          |

|              | E.6        |         | Idiosyncrasies .               |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 144          |

|              |            |         |                                |         | -      | ••• | -   |     |     |     |     |     | · | -   |     | - |   | -            |

| $\mathbf{F}$ | -          | -       | ocumentation                   |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 145          |

|              | F.1        | Infrast | ructure                        |         |        |     |     |     |     |     |     |     |   |     |     |   |   | 145          |

iii

| F.2 | ΙΟ                   | 146 |

|-----|----------------------|-----|

| F.3 | Scan Bits            | 148 |

| F.4 | Test Setup           | 148 |

| F.5 | Cadence Locations    | 150 |

| F.6 | Known Idiosyncrasies | 150 |

|     |                      |     |

### G Miscellaneous

152

# List of Figures

| 1.1  | [44] Block diagram of the SPAN-I sensor, including ESA, TOF, and individual                         |    |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | components of the electronics box.                                                                  | 2  |

| 1.2  | Operation of SPAN-I's time-of-flight mass spectrometer. (a) The ion is accel-                       |    |

|      | erated with a known potential to a speed defined by Equation 1.1. (b) Upon                          |    |

|      | impact, the START carbon foil releases secondary electrons which are amplified                      |    |

|      | then picked up by the START anode as a current pulse. (c) The ion travels                           |    |

|      | through the START foil to the STOP foil, which is a fixed distance $L$ away. This                   |    |

|      | produces a STOP pulse by the same mechanism as the START pulse                                      | 3  |

| 1.3  | Time of flight calibration data versus theoretical time of flight with and without                  |    |

|      | a $1.0\mu g/cm^2$ carbon foil. Each data point corresponds to the time of flight mode               |    |

|      | bin with 100ps resolution. Calibration data courtesy of SSL                                         | 4  |

| 1.4  | [49] An energy band diagram of a MOS structure for positive gate bias, indicating                   |    |

|      | major physical processes underlying radiation response                                              | 6  |

| 1.5  | [21] Threshold voltage shift in commercial 130nm CMOS as a function of TID                          |    |

|      | for different (a) NMOS and (b) PMOS transistor sizes, up to 136Mrads. PMOS                          |    |

|      | threshold shift is absolute value. The last point refers to full annealing at 100°C.                | 7  |

| 1.6  | (a) [63] Ratio between the value of $1/f$ noise parameter $K_f$ at 10Mrad absorbed                  |    |

|      | dose of ${}^{60}$ Co $\gamma$ -rays and the value before irradiation as a function of drain current |    |

|      | $I_D$ for NMOS and PMOS devices in the 0.13µm process. (b) [51] $1/f$ noise spectra                 | ~  |

| 1 8  | $S_v$ as a function of total dose. The device was under +6V bias during irradiation.                | 8  |

| 1.7  | [35] $I_{DS}$ - $V_{GS}$ characteristics before and after TID irradiation for a core NMOS           | 0  |

| 1 0  |                                                                                                     | 9  |

| 1.8  | [76] Threshold voltage mismatch between identically designed pairs of a regular                     | 10 |

| 1.0  | and b enclosed transistors before and after $\gamma$ irradiation up to 100kGy                       | 10 |

| 1.9  | [76] Standard deviation of the current factor mismatch between identically de-                      |    |

|      | signed pairs of a regular and b enclosed transistors before and after $\gamma$ irradiation          | 10 |

| 1.10 | up to 100kGy                                                                                        | 10 |

| 1.10 | resultant current pulse caused by the passage of a high-energy ion                                  | 11 |

|      | resultant current pulse caused by the passage of a high-energy lon                                  | ΤT |

| 1.11  | [46] (a) ITRS scaling of first-level metal half pitch and progression into ultra-<br>thin fully depleted silicon-on-insulator and multiple gate technologies, compared |                 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|       | with a representative diameter of the ionized free charge distribution in silicon in                                                                                   |                 |

|       | the wake of a light ion interaction. Node indicators are approximate. (b) ITRS                                                                                         |                 |

|       | scaling of gate charge for a nominal $3X/6X$ NMOS/PMOS inverter                                                                                                        | 13              |

| 1 1 2 | Layers of radiation hardening                                                                                                                                          | 14              |

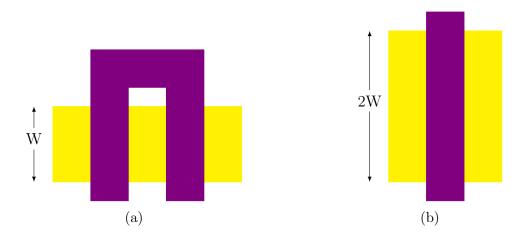

|       | Two variants of a MOSFET with $W_{\text{eff}} = 2W$ . Purple is the gate with oxide—                                                                                   | 14              |

| 1.10  | either for the channel or for isolation—underneath it, yellow is the source and                                                                                        |                 |

|       | drain of the device. The device with two fingers (a) has a greater total gate area                                                                                     |                 |

|       | with isolation oxide placed underneath it, due to the additional gate material                                                                                         |                 |

|       | required to electrically connect the two fingers                                                                                                                       | 15              |

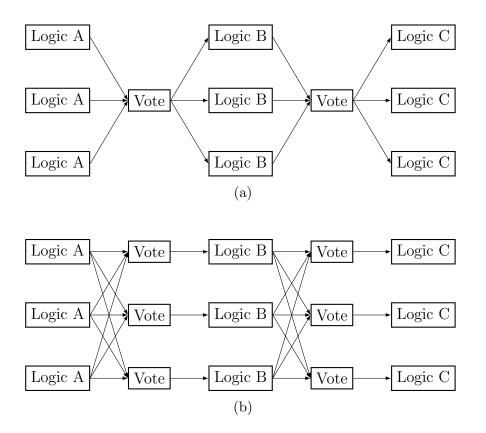

| 1 1/  | (a) 3-to-1 majority voting and (b) 3-to-3 voting. 3-to-3 voting ensures the input                                                                                      | 10              |

| 1.14  | of all Logic blocks B and C are correct in the event of one SET (assuming good                                                                                         |                 |

|       | layout practice)                                                                                                                                                       | 17              |

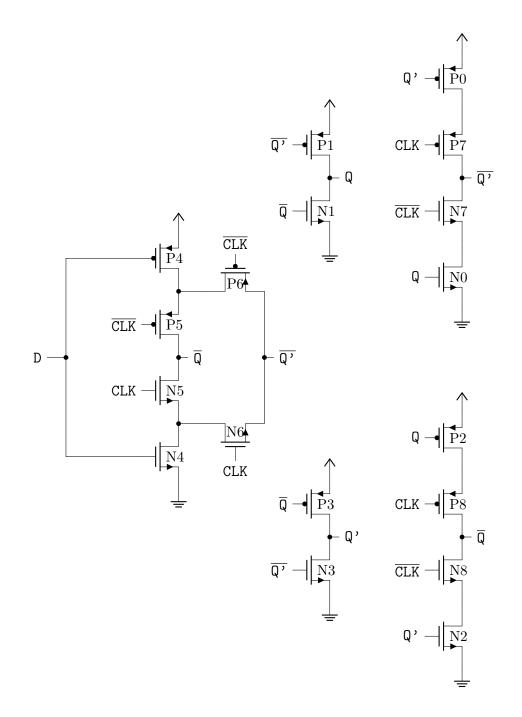

| 1 15  | The DICE memory cell, adapted from [13]                                                                                                                                | 18              |

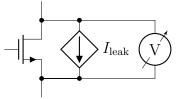

|       | Leaky MOSFET used to emulate radiation-exacerbated leakage. The sign and                                                                                               | 10              |

| 1.10  | to an extent the magnitude of $I_{\text{leak}}$ depends on the voltage measured by the                                                                                 |                 |

|       | voltmeter, clipped at a fixed value. The leakage also scales with device aspect ratio.                                                                                 | 20              |

| 1.17  | Estimated charge collected per micron of collection depth for an SET produced                                                                                          | 20              |

| 1.11  | by the ions available in the cocktails at Lawrence Berkeley National Laboratory                                                                                        |                 |

|       | [41]                                                                                                                                                                   | 21              |

| 1.18  | SET emulator circuit. $\tau_r = R_r C_r$ and $\tau_f = R_f C_f$ for Equation 1.6. The input                                                                            |                 |

| 1.10  | voltage source on the left provides a step function                                                                                                                    | 22              |

| 1.19  | TID test flow. Adapted from [55]                                                                                                                                       | 23              |

|       | The BAG design flow for a block.                                                                                                                                       | $\frac{-0}{24}$ |

| -     |                                                                                                                                                                        |                 |

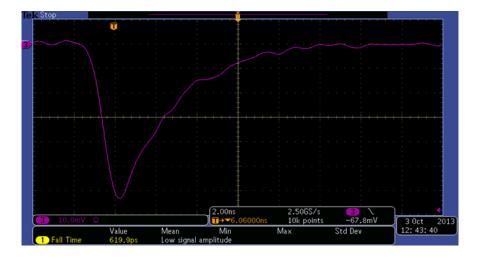

| 2.1   | MCP output, converted to a voltage and averaged over a periodic event trigger.                                                                                         | 27              |

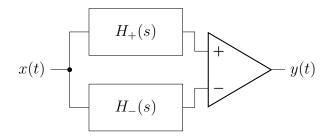

| 2.2   | Block diagram of a common generalized CFD, implemented with two LTI oper-                                                                                              |                 |

|       | ations $H_+(s)$ and $H(s)$ along with an ideal comparator.                                                                                                             | 28              |

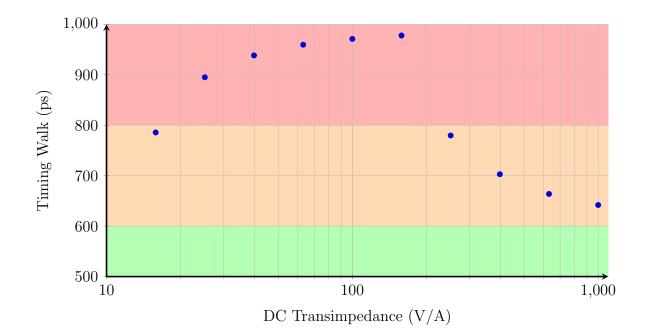

| 2.3   | Plot of timing walk given 2-20Me <sup>-</sup> pulses with $\tau_r = 500$ ps, $\tau_f = 1$ ns to roughly                                                                |                 |

|       | match Figure 2.1, with a threshold set at $2 \times 3.3 \text{V}/2^9 \approx 12.9 \text{mV}$ for a tran-                                                               |                 |

|       | simpedance amplifier with a fixed gain-bandwidth product of $30 \mathrm{GHzV/A}$ . In-                                                                                 |                 |

|       | creasing the transimpedance sees the timing walk asymptotically approach 611ps.                                                                                        |                 |

|       | This is the bleeding edge of what the process node can achieve under nominal                                                                                           |                 |

|       | operating conditions; decreasing the gain-bandwidth product to $10 \text{GHz V/A}$ to                                                                                  |                 |

|       | account for variation in process, supply, and temperature makes it so even 1LSB                                                                                        |                 |

|       | of the 9-bit DAC is insufficient to meet walk requirements.                                                                                                            | 30              |

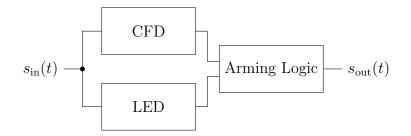

| 2.4   | High level concept of CFD usage in parallel with an LED. Here, the LED deter-                                                                                          | - ·             |

|       | mines if there is a pulse, and the CFD provides the timing of the pulse                                                                                                | 31              |

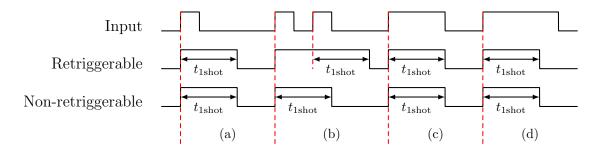

| 2.5          | The response of a retriggerable one shot and a non-retriggerable one shot to (a) a single pulse with duration shorter than $t_{1\text{shot}}$ (b) two pulses whose rising edges occur within $t_{1\text{shot}}$ of each other (c) a pulse with duration equal to $t_{1\text{shot}}$ (d) a pulse with duration longer than $t_{1\text{shot}}$ . Each one shot produces HIGH pulses in |          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|              | response to rising edges.                                                                                                                                                                                                                                                                                                                                                            | 32       |

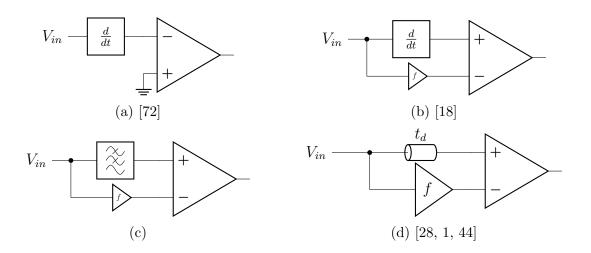

| 2.6          | The core methods behind prior implementations of constant fraction discriminators.                                                                                                                                                                                                                                                                                                   | 33       |

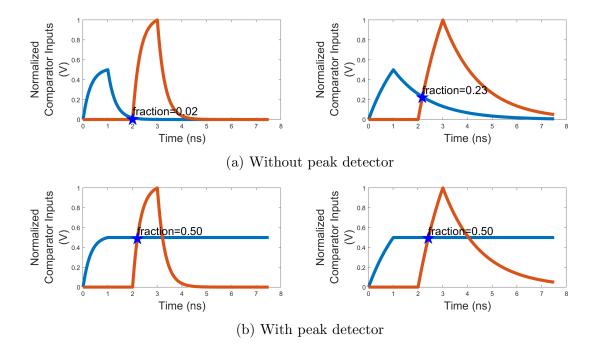

| 2.7          | Example inputs to the CFD comparator, with (b) and without (a) the peak detector inserted in the shaping chain. The orange line is the delayed input                                                                                                                                                                                                                                 |          |

|              | pulse, the blue line is the input pulse, attenuated by a factor $f = 0.5$ .                                                                                                                                                                                                                                                                                                          | 34       |

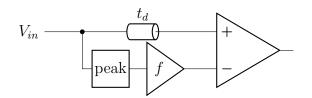

| 2.8          | The modified CFD with the peak detector added before the attenuator                                                                                                                                                                                                                                                                                                                  | 34       |

| 2.9          | Block diagram of the front end and its operation with the CFD branch outlined<br>in blue and the LED branch outlined in yellow. The one shot output is used to                                                                                                                                                                                                                       |          |

|              | reset the peak detector                                                                                                                                                                                                                                                                                                                                                              | 36       |

| 2.10         | Diagram with one possible scenario for SEE-induced lockout. In general, lockout                                                                                                                                                                                                                                                                                                      | 50       |

|              | can occur if an SET on the peak detector raises the output of the attenuator to<br>a level that real pulses can never reach. The CFD output remains low, and the                                                                                                                                                                                                                     |          |

|              | system never resets the peak detector until the chip is reconfigured.                                                                                                                                                                                                                                                                                                                | 37       |

| 2.11         |                                                                                                                                                                                                                                                                                                                                                                                      | 37       |

|              |                                                                                                                                                                                                                                                                                                                                                                                      | 01       |

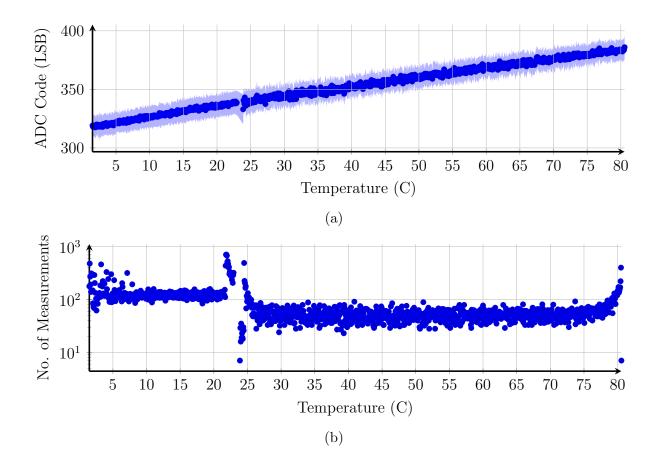

| $3.1 \\ 3.2$ | Chip die photo with main structures annotated. Photo courtesy of Hani Gomez.<br>Bandgap voltage versus temperature with the envelope of the standard deviation.                                                                                                                                                                                                                      | 40       |

|              | Spikes at low temperatures were from condensation within the chamber                                                                                                                                                                                                                                                                                                                 | 42       |

| 3.3          | The reference routing network for power distribution. There are three LDOs on                                                                                                                                                                                                                                                                                                        |          |

|              | the chip, all implemented in a similar fashion.                                                                                                                                                                                                                                                                                                                                      | 43       |

| 3.4          | The low dropout regulator used within the chip. The enable device (green) is not included in the always-on regulator, and the reference voltage $V_{\text{REF}}$ is produced                                                                                                                                                                                                         |          |

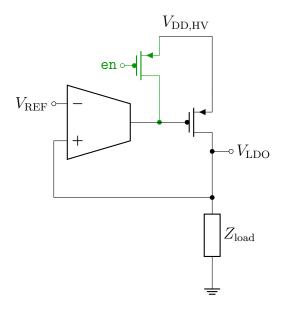

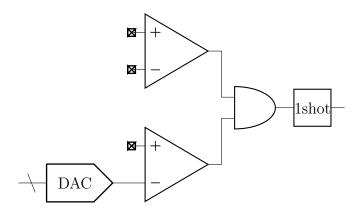

| 3.5          | using an on-chip bandgap reference circuit                                                                                                                                                                                                                                                                                                                                           | 44<br>44 |

|              |                                                                                                                                                                                                                                                                                                                                                                                      |          |

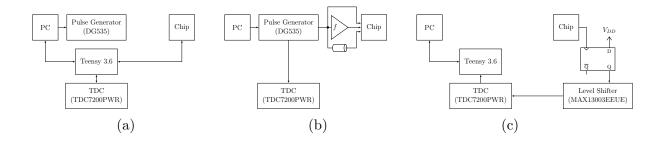

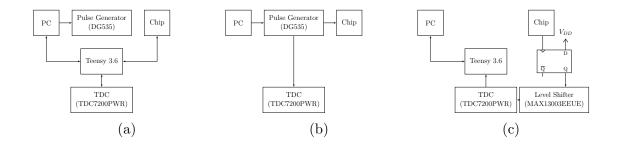

| 3.6  | Measurement setup and procedure for gathering timing statistics for the small         |    |

|------|---------------------------------------------------------------------------------------|----|

|      | signal chain. (a) Configure the DG535, TDC, and chip scan chain. (b) Trigger          |    |

|      | the DG535. The DG535's triggered output is then used as the START event to the        |    |

|      | TDC. A subsequent pulse nominally 1µs wide with an amplitude anywhere from            |    |

|      | 50mV to 600mV is routed down three paths: an attenuator (Kay Elemetrics 839);         |    |

|      | a coaxial cable roughly 60cm longer than that of the attenuator for an additional     |    |

|      | $\approx$ 2ns delay; and directly to the positive input of the LED comparator. Each   |    |

|      | pulse amplitude test is performed 500 times with at least 100ns between pulses.       |    |

|      | (c) The chip output is latched and level shifted from the 1.8V core voltage to        |    |

|      | 3.3V to be fed into the TDC as a STOP event.                                          | 45 |

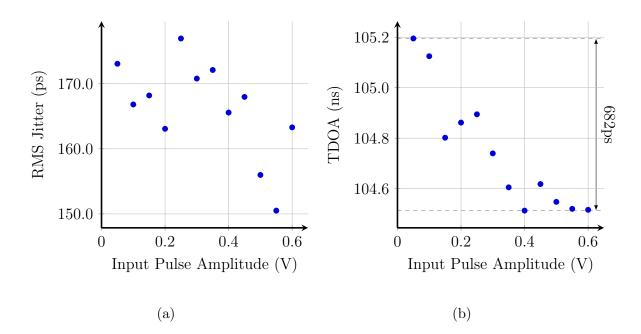

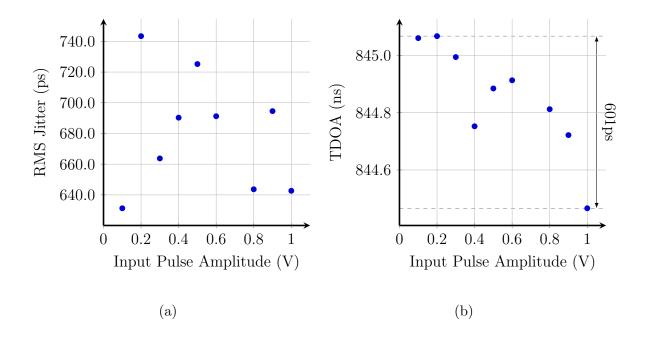

| 3.7  | (a) Jitter and (b) time difference of arrival of the measured pulses. Worst case      |    |

|      | jitter was measured at $176.9 ps_{rms}$ , and timing walk at $682 ps.$                | 46 |

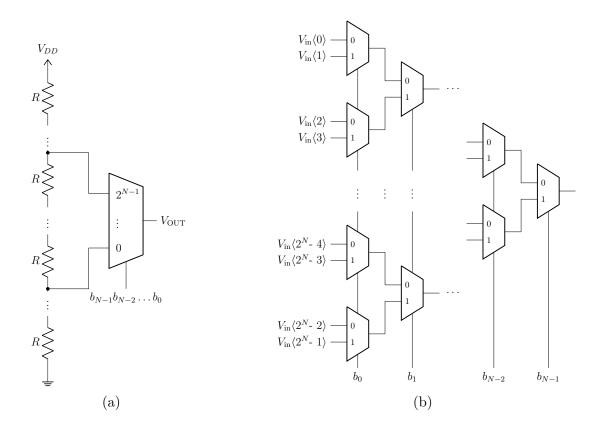

| 3.8  | (a) The resistive ladder DAC was chosen for its simplicity and guaranteed mono-       |    |

|      | tonicity. (b) The analog mux with N bits was constructed with $2^N - 1$ two-to-one    |    |

|      | muxes to enable direct feed of binary selection bits with no additional encoding.     | 47 |

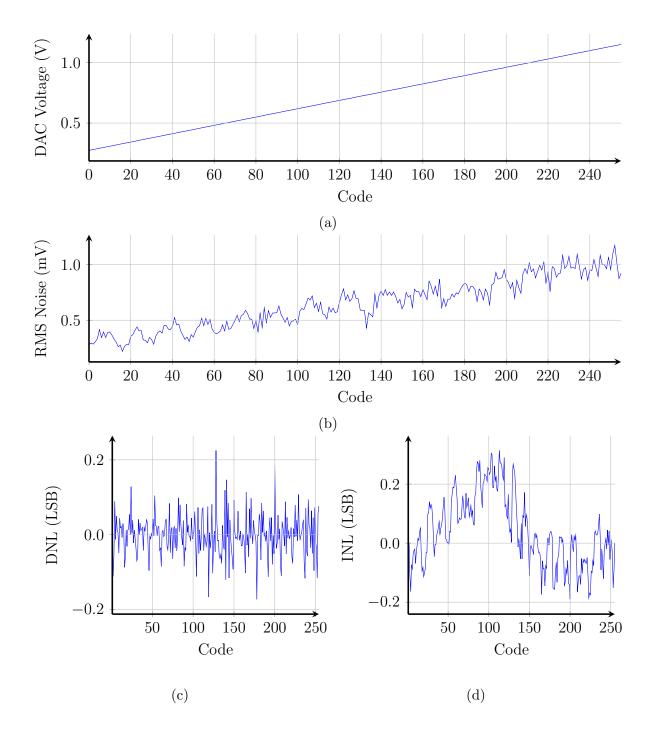

| 3.9  | (a) Voltage DAC transfer function with the supply voltage set to its lowest value.    |    |

|      | Each data point is the average of 100 measurements. The gain is $3.44 \text{mV/LSB}$  |    |

|      | for a full scale range of 877.22mV. (b) The DAC's RMS noise $\leq 1.17$ mV, or 2.9    |    |

|      | LSB. Measured with nominally 10nF of decoupling capacitance on the output of          |    |

|      | the DAC. (c) DNL min/max -0.17/0.23 LSB. (d) INL min/max -0.19/0.31 LSB.              | 48 |

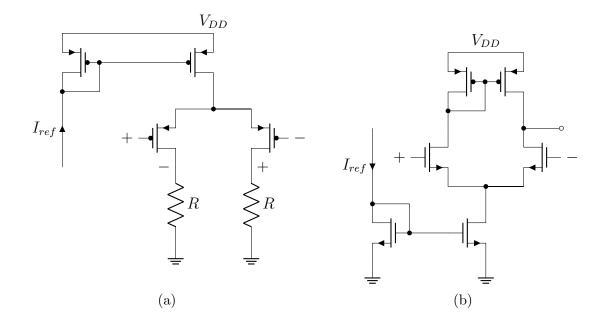

| 3.10 | The core of every comparator consisted of several cascaded fully differential stages  |    |

|      | (a) and one final stage for a single-ended conversion (b)                             | 49 |

| 3.11 | High level diagram of the autozeroed comparator. Because there is no clock,           |    |

|      | the sampling phase $\phi_1$ occurs when the chip is reconfigured, i.e. the scan chain |    |

|      | is LOADed into the rest of the chip. In our use, the nulling amplifier and the        |    |

|      | nulling pins are differential; we show the single ended variant here for clarity      | 50 |

| 3.12 | The core fully differential amplifier in grey, with its offset control in black and   |    |

|      | boxed on the left. The choice to burn additional current by adding $R_{\rm OS}$ was   |    |

|      | to more consistently define the gain of the offset control across corners; biasing    |    |

|      | resistors largely guaranteed the current source for $I_{\rm OS}$ behaved as such      | 51 |

| 3.13 | A standard scan chain circuit (a) and its operation (b). Buffers and the like have    |    |

|      | been removed for clarity.                                                             | 52 |

| 3.14 | A triple modular redundant scan cell as it was used in the chip. As a defense         |    |

|      | against timing violations, the clock was routed in reverse order relative to the      |    |

|      | input data signal.                                                                    | 53 |

| 3.15 | The one shot pulse generator, with triplicated components outlined. Each out-         |    |

|      | lined section was followed by a 3-to-3 majority vote on its output(s). The reset      |    |

|      | switch is necessary to ensure consistent output pulse widths when input events        |    |

|      | are closely spaced in time relative to the RC time constant                           | 53 |

| 3.16           | Normal one shot operation without the reset $\phi_{\rm rst}$ in the presence of a single short<br>pulse from the fully settled stable state. The grey line is the inverter switching<br>point. Note that the the RC node takes finite time to settle to $\approx 0$ V even after                                                                                                                                                                                                                                                                                                                                                                                       |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|                | the output pulse has terminated. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54         |

| 3.17           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54         |

| 3.18           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 94         |

|                | width without the reset switch was 15.4ns and 16.8ns with the reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55         |

| 3.19           | Measurement setup for gathering timing statistics for the small signal chain. (a)<br>Configure the DG535, TDC, and chip scan chain. (b) Trigger the DG535. The<br>DG535's triggered output is then used as the START event to the TDC. A sub-<br>sequent pulse nominally 2ns wide with an amplitude ranging from 0.1V to 1V<br>is connected with a 50 $\Omega$ termination to the PCB and AC coupled with a 2pF<br>capacitor for current pulses of 1.2mA to 12mA into the preamplifier. Each pulse<br>amplitude test is performed 500 times with at least 100ns between pulses. (c)<br>The chip output is latched and level shifted from the 1.8V core voltage to 3.3V |            |

|                | to be fed into the TDC as a STOP event.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56         |

| 3.20           | (a) Jitter and (b) time difference of arrival of the measured pulses for the main                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |

|                | signal chain. Worst case jitter was measured at $743 \mathrm{ps_{rms}},$ and timing walk at 601ps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56         |

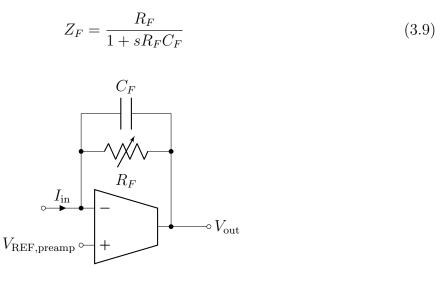

| 3.21           | The preamplifier. The referencing used for biasing is generated by a resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

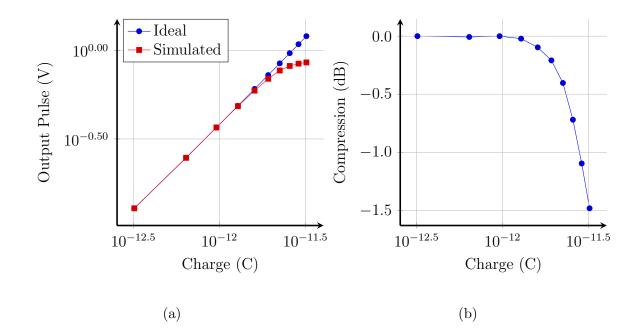

| 3.22           | the input pulse increases. The ideal values are calculated by linearly fitting the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57         |

|                | simulated data. The charge corresponds to 2Me <sup>-</sup> to 20Me <sup>-</sup> . (b) The compression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>F</b> 0 |

| 3 93           | of the peak as the size of the pulse increases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 58<br>58   |

|                | The peak detector. The switch (grey) was not included in this version of the thip.<br>The positive and negative inputs to the LED and CFD comparators, without a<br>reset on the output of the preamplifier. If $t_{1\text{shot}}$ is short relative to the settling<br>time of the preamplifier, the peak detector output (red) will rise past the LED                                                                                                                                                                                                                                                                                                                | 90         |

| 3.25           | threshold and trigger the output once more, causing the appearance of afterpulsing.<br>(a) Static error of the peak detector. (b) The percent error of the measured<br>output voltage relative to its target value. (c) The standard deviation of the                                                                                                                                                                                                                                                                                                                                                                                                                  | 59         |

|                | measured output voltage. The error and statistics show noticeable spikes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 60         |

| 3.26           | Tracking the spikes in voltage for (a) the largest and (b) second largest spikes in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| a a <b>-</b>   | measurement variance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61         |

| $3.27 \\ 3.28$ | Sallen-Key topology associated with the transfer function in Equation 3.11<br>The resistive divider attenuator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 61<br>62   |

| 4.1            | Chip die photo with main structures annotated. Photo courtesy of Alexander Alvara.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 65         |

| 4.2                                                     | Time difference of arrival of the simulated pulses with an emulated benchtop setup and microchannel plate.                                                                                                                                                                       | 66                       |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| $\begin{array}{c} 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \end{array}$ | Trimmed comparator stage                                                                                                                                                                                                                                                         | 67<br>68<br>68<br>69     |

| 4.7                                                     | Two Sallen-Key filters to give the fourth order transfer function in Equation 4.2.                                                                                                                                                                                               | 70                       |

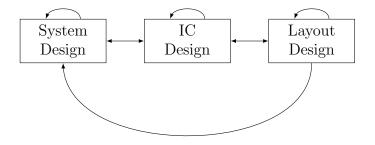

| 5.1                                                     | A typical design flow                                                                                                                                                                                                                                                            | 73                       |

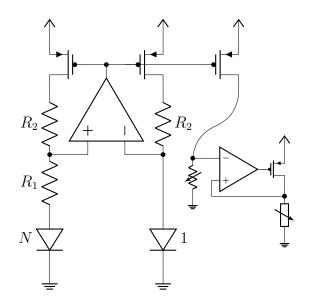

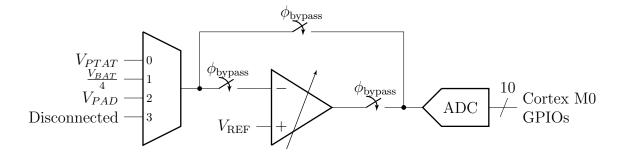

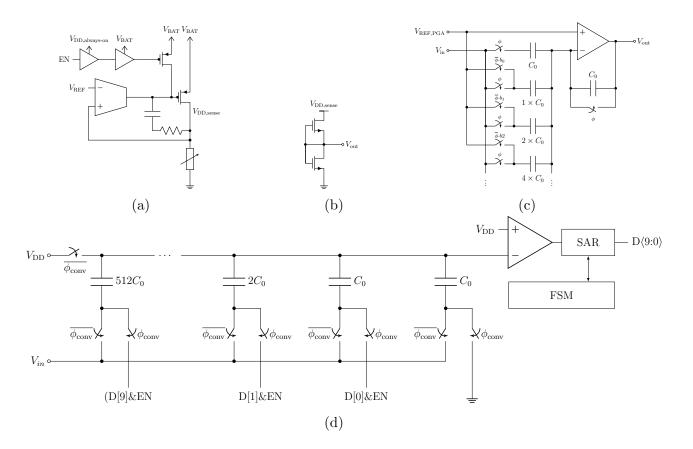

| A.1<br>A.2<br>A.3                                       | Annotated schematic of the digital LDO                                                                                                                                                                                                                                           | 84<br>86                 |

| A.4                                                     | Temperature precision was 0.01°C                                                                                                                                                                                                                                                 | 87                       |

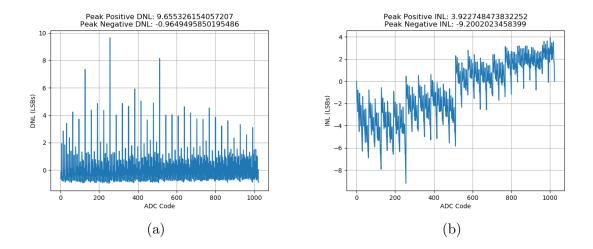

| A.5                                                     | register analog to digital converter                                                                                                                                                                                                                                             | 88                       |

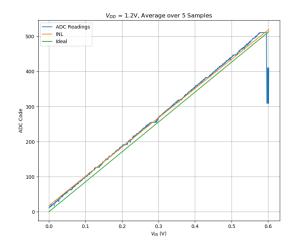

| A.6                                                     | consistent with binary DACs, with some nonmonotonicity with the DAC The ADC output code versus input voltage. The nominal FSR is $V_{\text{DD,sensor}} = 1.2$ V, and each data point is the result of 5 averaged samples. Unfortunately the raw data for this plot has been lost | 89<br>89                 |

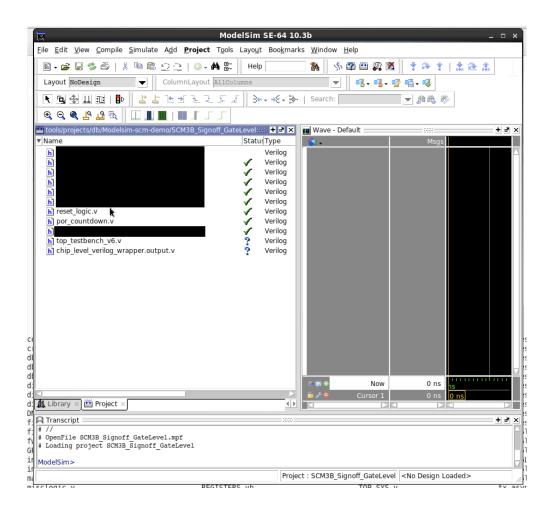

| B.1<br>B.2<br>B.3                                       | ModelSim window after launch, showing Library and Project tabs on the left and<br>Wave tab on the right                                                                                                                                                                          | 92<br>93<br>94           |

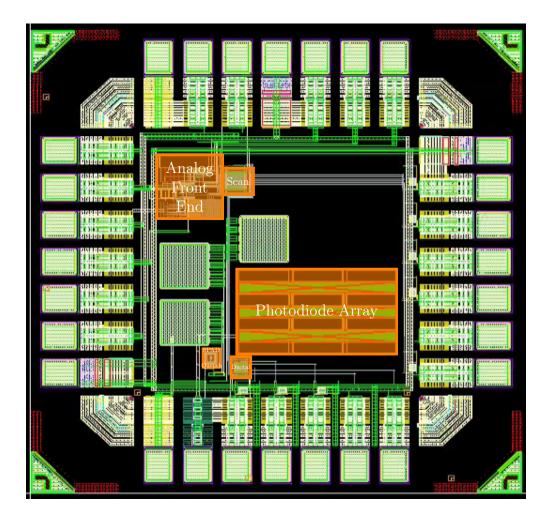

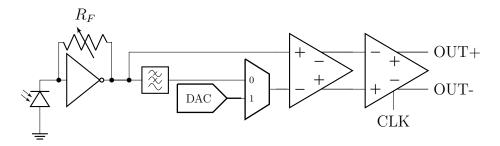

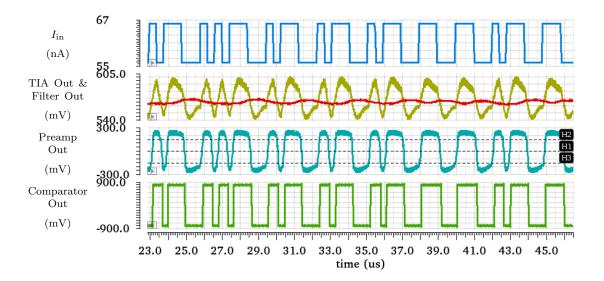

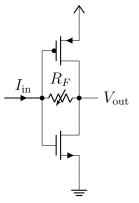

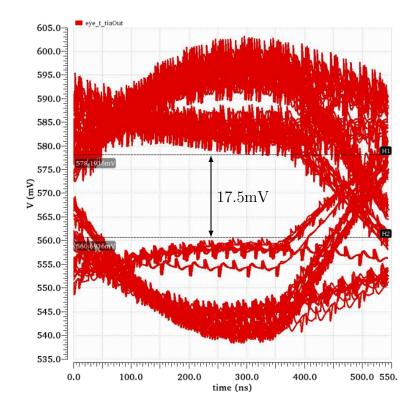

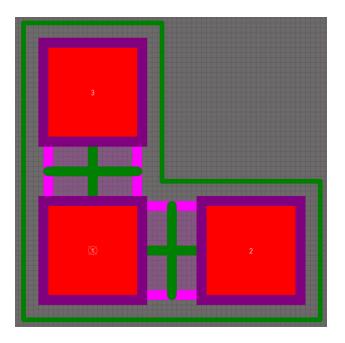

| C.1<br>C.2<br>C.3<br>C.4<br>C.5                         | Chip layout screenshot. The analog front end fits in 130µm×130µm A block diagram of the analog front end of the optical receiver                                                                                                                                                 | 117<br>121<br>121<br>122 |

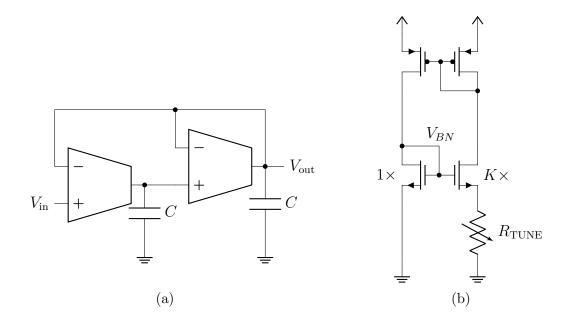

| C.6                                                     | to program SCM with a 10nA signal. The eye opening is roughly 17.5mV (a) The second order low pass filter with a corner frequency of $\omega_0 = \frac{G_m}{C}$ . The $G_m$ of each operational transconductance amplifier is controlled with the tunable                        | 123                      |

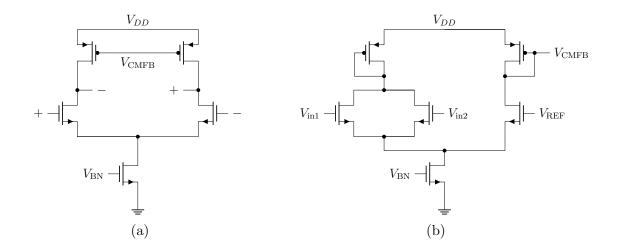

| C.7                                                     | constant- $g_m$ circuit shown in (b), used for adjusting the tail current of each OTA.<br>(a) The main amplifier for the preamp. (b) The common mode feedback amplifier                                                                                                          | 124                      |

|                                                         | used in the preamp to maintain biasing                                                                                                                                                                                                                                           | 125                      |

х

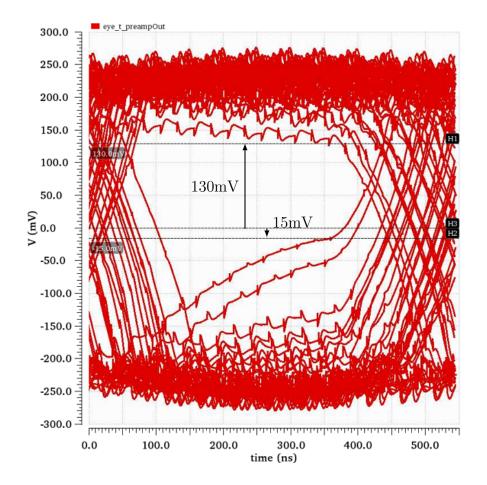

| C.8  | An eye diagram of the output of the preamp when the TIA is fed a 1.84Mbps        |     |

|------|----------------------------------------------------------------------------------|-----|

|      | OOK signal to program SCM with a 10nA signal. The eye opening spans from         |     |

|      | 130 mV to $-15 mV$ because of DC imbalance, suggesting 4b5b is necessary for any |     |

|      | ООК                                                                              | 126 |

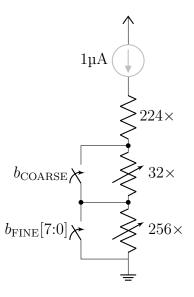

| C.9  | The resistive ladder intended for a 1 $\mu$ A bias current                       | 126 |

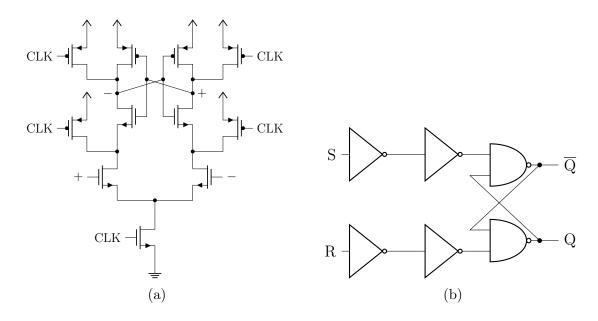

| C.10 | (a) The strongarm latch and (b) subsequent SR latch used in the clocked com-     |     |

|      | parator                                                                          | 127 |

| F.1  | The L-resistor footprint. Only one direction (N/S or E/W) is populated           | 149 |

# List of Tables

| 1.1<br>1.2<br>1.3                             | Location and scale parameters of the Moyal distributions used to fit TOF data.<br>Some useful definitions for discussing radiation in electronics                                                                                                                                                              | 5<br>6<br>12                                  |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.1                                           | Measured parameters for SPAN-I's previous chip designed by Johns Hopkins APL, and the target specification for the iteration of SPAN-I discussed in this dissertation. Area limits were set by available area on the BSAC shuttle. The 180nm process was chosen because BSAC does not need to pay for the area | 27                                            |

| 3.1                                           | Chip V1 versus the target specifications                                                                                                                                                                                                                                                                       | 41                                            |

| $4.1 \\ 4.2$                                  | Chip V2 simulated performance versus the target specifications                                                                                                                                                                                                                                                 | 66<br>70                                      |

| A.1<br>A.2<br>A.3                             | Simulated performance of the digital LDO                                                                                                                                                                                                                                                                       | 84<br>85<br>86                                |

| C.1<br>C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.7 | Optical receiver target specifications.                                                                                                                                                                                                                                                                        | 116<br>116<br>118<br>119<br>120<br>129<br>130 |

| D.1<br>D.2<br>D.3                             | SPAN-Ion specific schematic generators                                                                                                                                                                                                                                                                         | 132<br>133<br>134                             |

| E.1                                           | Chip V1 I/O and associated pad locations. Unconnected pads are marked as x.                                                                                                                                                                                                                                    | 136                                           |

|     | Chip V1 I/O descriptions                                                     |     |

|-----|------------------------------------------------------------------------------|-----|

| E.4 | Top-level Cadence libraries for Chip V1                                      | 143 |

| F.1 | Chip V2 I/O and associated pad locations. Unconnected pads are not included. | 146 |

| F.2 | Chip V2 I/O descriptions.                                                    | 147 |

| F.3 | Chip V2 scan bits.                                                           | 148 |

| F.4 | Top-level Cadence libraries for Chip V2.                                     | 150 |

| G.1 | Locations of useful tribal knowledge.                                        | 152 |

#### Acknowledgments

As with any PhD, it would not have been possible without a veritable village of people. To my advisor, Kris Pister: without your encouragement, I wouldn't have even applied to a PhD program. Your endless supply of enthusiasm, patience, and Hawaiian shirts has made for both a fun and educational grad school experience.

To my collaborators at SSL—Robert, Roberto, Ken, Davin—and the rest of the wonderful people there: Thanks for putting up with all my derpy questions, and for sharing your experience and insight over the last few years. Your breadth and depth of expertise and knowledge have been an inspiration for an engineer who occasionally felt like things had gone stale.

I'd also like to thank Carl Grace and Professors Stojanovic and Pilawa-Podgurski for their encouragement and enthusiasm as members of my qualifying exam committee; and Professor Lu for agreeing on extremely short notice to be a part of my dissertation committee.

Throughout grad school I've also had the privilege of being in the same group as some of the best people I know, and been lucky enough to call several of them my friends. Alex, your humor, warmth, resilience, and snappy wardrobe have kept me sane through the crazy-train of grad school more than you probably know. Mauricio, thank you for simultaneously being a great researcher, incredibly humble, and one of the most genuinely caring people I've had the pleasure of calling a friend. Daniel (Teal), you are the human embodiment of sunshine, if sunshine wore exclusively black; your technical acumen and unflappable optimism inspire the people around you to be better engineers, researchers, and people. Hani, thank you for showing me that there's more to happiness than productivity, and for teaching me how to be both a better communicator and researcher. Alexander, you're always there to root for people and help them out, and being your friend and colleague has taught me to be a better advocate for myself and for others. Nate, thanks for being a great desk buddy and giving me perspective for life beyond school—who'd have thought that we'd end up publishing together? Many thanks to the old(er) guard SCµM crew of Fil, DB, Brad, and Osama for your mentorship and guidance in getting me started with grad school. Bhuvan, you've been the best undergrad a grad student could hope to work with, and there is zero doubt in anyone's mind that you're going to do amazing things. To the youngins of the Pister group—Yu-Chi, Yichen, Titan, Daniel (Lovell), Daniel (Finell), and generations to come—I look forward to the cool things y'all will accomplish in the coming years.

Beyond the Pister group, other members of the EECS department—Kevin (Zheng), Dalene, Shirley, Pat, Glenna, Finsen, Yifan, Shm, and countless more—have been invaluable for their insight, assistance, and endless generosity with time and energy throughout my studies at Berkeley.

Outside of grad student life, Berkeley has introduced me to Katherine, Raymond, Saavan, Divya, Jayss, Zeke, and many more people for whom I'd happily trade all my material possessions if it meant I could bring them with me. You all bring such joy and light into the world, and it makes leaving that much harder.

Finally, I'd like to thank my family. Lyndon, you've always been a better person than I, and you always know how to cheer me up no matter the circumstances. Mom and Dad, this would not have been possible without your unwavering support, advice, and recognition that "When are you going to graduate?" is a bad question to ask a PhD student.

Thank you all for believing in me, being there, and making this possible.

# Chapter 1 Introduction

The utility of a circuit cannot be defined in a vacuum; it must be contextualized by the circuit's application. This chapter will describe the Solar Probe Analyzer for Ions as the specific target use case of this dissertation's hardware, with the understanding that the methods and analysis here can be broadly applied to similar systems. It will provide background on ionizing radiation in the context of integrated circuit design, as well as a discussion of the Berkeley Analog Generator as it was used for this dissertation.

### 1.1 The Solar Probe Analyzer for Ions

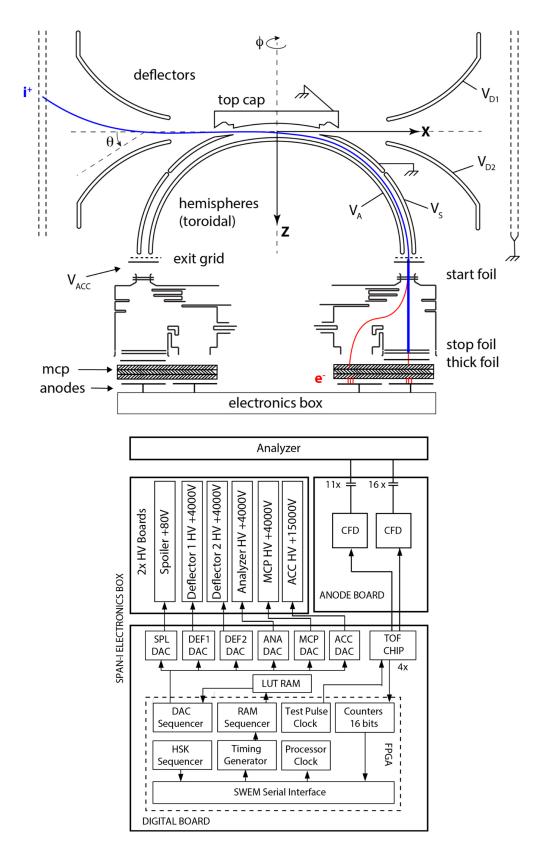

The Solar Probe Analyzer for Ions (SPAN-Ion) is an electrostatic analyzer (ESA) designed by the Berkeley Space Sciences Lab to measure the ion composition and 3D distribution function of the thermal corona and solar wind plasma [44]. It derives much of its design from the Mars MAVEN electrostatic analyzer, has a legacy which includes the Parker Solar Probe and the Lunar Gateway, and is slated for use in the Mars EscaPADE mission in mid-2024. Figure 1.1 shows a cross section of the instrument with the top hat ESA and time-of-flight (TOF) apparatus, as well as a block diagram of components of the electronics box below.

Figure 1.1: [44] Block diagram of the SPAN-I sensor, including ESA, TOF, and individual components of the electronics box.

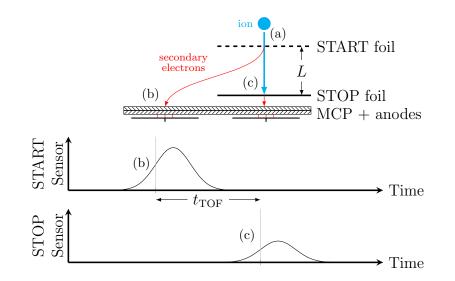

At the highest level, its purpose is to advance our understanding of space weather to improve our nowcasting and forecasting capabilities. SPAN-Ion uses a time-of-flight mass spectrometer to determine the mass/charge ratios of the ions selected by the electrostatic analyzer (Figure 1.2).

Figure 1.2: Operation of SPAN-I's time-of-flight mass spectrometer. (a) The ion is accelerated with a known potential to a speed defined by Equation 1.1. (b) Upon impact, the START carbon foil releases secondary electrons which are amplified then picked up by the START anode as a current pulse. (c) The ion travels through the START foil to the STOP foil, which is a fixed distance L away. This produces a STOP pulse by the same mechanism as the START pulse.

The mass spectrometer operates by accelerating the selected ion with a potential U = -15keV. Assuming the ion has negligible initial kinetic energy, the ion reaches a speed determined by its mass/charge ratio, described in Equation 1.1.

$$qU \approx \frac{1}{2}m\dot{x}^2 \tag{1.1}$$

The ion strikes a START carbon foil, triggering the release of secondary electrons which are then directed to a microchannel plate (MCP) to produce a START pulse. The ion continues through the START foil and travels L = 2cm to the thicker STOP foil, and upon impact again produces secondary electrons which are amplified by the MCP to produce a STOP pulse. Assuming no energy is lost upon collision with the START foil, the time the ion takes to traverse the distance L is defined by Equation 1.2.

$$t_{\text{TOF,lossless}} = \frac{L}{\dot{x}} \approx \frac{L}{\sqrt{2U}} \sqrt{\frac{m}{q}} \propto \sqrt{\frac{m}{q}}$$

(1.2)

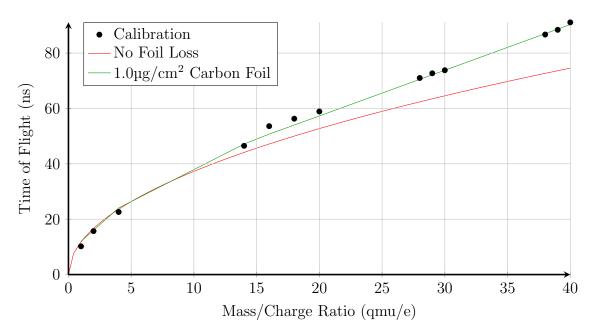

SSL provided calibration data, fitted to Moyal distributions, for the TOF of different ion species in Figure 1.3.

Figure 1.3: Time of flight calibration data versus theoretical time of flight with and without a  $1.0\mu g/cm^2$  carbon foil. Each data point corresponds to the time of flight mode bin with 100ps resolution. Calibration data courtesy of SSL.

Comparing the ground calibration data and idealized expression for time of flight in Equation 1.2, we see in Figure 1.3 that there is non-negligible energy loss from the collision with the START carbon foil. Using TRIM [88], we estimate a carbon foil thickness of  $\approx 1.0 \mu g/cm^2$ . More importantly for this dissertation, the timing accuracy and precision required to distinguish between the target mass/charge ratios is half the minimum difference between any two mass/charge ratios, or 600-800 ps.

Both variation in energy loss from the carbon foil collision and initial kinetic energy cause spread within the TOF distribution—a phenomenon broadly categorized as straggling. The flexibility of the target timing precision is due to significant straggling within each TOF distribution, especially at higher mass/charge ratios. From Table 1.1, the Moyal scale parameters for TOF distributions for ions with mass/charge ratios of 29 and 30 are 5.6ns and 6.0ns—more than  $4 \times$  the difference in times of flight used to distinguish the two mass/charge ratios.

| MQ Ratio | TOF Moyal $\sigma$ (ns) | TOF Mode (ns) |

|----------|-------------------------|---------------|

| 1        | 0.3                     | 10.2          |

| 2        | 0.4                     | 15.7          |

| 4        | 0.3                     | 22.6          |

| 14       | 1.9                     | 46.5          |

| 16       | 2.8                     | 53.6          |

| 18       | 3.9                     | 56.3          |

| 20       | 3.2                     | 58.9          |

| 28       | 6.4                     | 71.0          |

| 29       | 5.6                     | 72.7          |

| 30       | 6.0                     | 73.8          |

| 38       | 8.8                     | 86.7          |

| 39       | 8.6                     | 88.4          |

| 40       | 9.7                     | 91.1          |

Table 1.1: Location and scale parameters of the Moyal distributions used to fit TOF data.

### **1.2** Radiation and Integrated Circuits

Ionizing radiation refers to particles and photons with sufficient energy to detach electrons from atoms or molecules. This section will discuss its effects on integrated circuits, hardening techniques against it, and methods for validation in representative environments. We assume a basic understanding of energy bands and band diagrams.

#### 1.2.1 Effects

Ionizing radiation can cause cumulative effects over periods of prolonged exposure, as well as more transient single event effects (SEEs). The former refers to changes in device characteristics due to total ionizing dose (TID), though it can also cause non-ionizing damage in the form of displacement damage (DD). The latter encompasses a host of phenomena which all result from the relatively short-lived injection and redistribution of charge as the ionizing radiation interacts with electronics.

Before continuing, a note about units: astronomers and astrophysicists often use CGS units over SI. One reason I've heard for this is so the energy density of an electromagnetic field can be written without needing the permittivity  $\epsilon_0$  and magnetic permeability  $\mu_0$  of free space (Equation 1.3).

$$U_{\rm CGS} = \frac{1}{8\pi} \left( \mathcal{E}^2 + B^2 \right)$$

(1.3a)

$$U_{\rm MKS} = \frac{\epsilon_0}{2} \mathcal{E}^2 + \frac{1}{2\mu_0} B^2$$

(1.3b)

#### CHAPTER 1. INTRODUCTION

| Term                         | Definition                                                                                                                                                   | Common Units                                      |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Linear Energy Transfer (LET) | $\frac{dE}{dt} \frac{1}{\rho_{\rm medium}}$                                                                                                                  | $\frac{\text{MeV} \times \text{cm}^2}{\text{mg}}$ |

| flux                         | $\frac{dx \ \rho_{\text{medium}}}{\text{\# particles}}$ area × time                                                                                          | $\frac{1}{\mathrm{cm}^2 \times \mathrm{s}}$       |

| fluence                      | $\int (\text{flux}) dt = \frac{\# \text{ particles}}{\text{area}}$<br>LET × fluence × 1.6(10 <sup>-7 Gy)×mg</sup> / <sub>MeV</sub> = $\frac{E}{\text{mass}}$ | $\frac{1}{\mathrm{cm}^2}$                         |

| dose                         | LET × fluence × $1.6(10^{-7} \frac{\text{Gy}) \times \text{mg}}{\text{MeV}} = \frac{E}{\text{mass}}$                                                         | 1 Gy = 100 rad                                    |

| SEE Cross-Section            | $\frac{\# \text{ of errors}}{\text{fluence}}$                                                                                                                | $\mathrm{m}^2$                                    |

The units in Table 1.2 are CGS for the most part only to give a sense of normalization quantities (e.g. per area, volume, etc.). This dissertation will always specify units.

Table 1.2: Some useful definitions for discussing radiation in electronics.

#### 1.2.1.1 Total Ionizing Dose

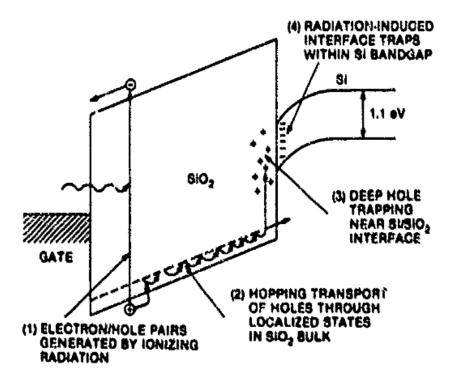

Total ionizing dose (TID) is used when describing the long-term degradation of electronics due to ionizing radiation. Figure 1.4 [49] shows how ionizing radiation causes this long-term damage.

Figure 1.4: [49] An energy band diagram of a MOS structure for positive gate bias, indicating major physical processes underlying radiation response.

#### CHAPTER 1. INTRODUCTION

First, the ionizing radiation generates electron hole pairs (EHPs). The quantity of EHPs depends on a number of variables including the bandgap of the medium and its density—the energy to generate an EHP in crystalline silicon is 3.6eV, while the energy required to generate an EHP in silicon dioxide is 17eV [70]. Second, some of the pairs recombine, but those which don't (usually holes due to lower mobility [6]) polaron hop via shallow traps into the dielectric. Finally, the unrecombined holes end up in oxide traps, often near the surface interface, though they can also appear in the bulk and at the interface [24].

Process improvements have generally worked in favor of robustness against total ionizing dose; thinner oxides and improved interface engineering allow for fewer defects and traps. However, dielectrics such as the buried oxide in silicon-on-insulator processes and field oxides used in trench isolation still experience the effects of total ionizing dose.

For MOS devices, holes trapped at interfaces do not anneal out like those in the dielectric can, resulting in a shift in threshold voltage defined by Equation 1.4 where  $C_{\text{ox}}$  is oxide capacitance,  $t_{\text{ox}}$  is oxide thickness, and  $\rho_{\text{ox}}$  is trap density.

$$\Delta V_t = -\frac{Q_{\text{interface}}}{C_{\text{ox}}} = -\frac{1}{\varepsilon_{\text{ox}}} \int_0^{t_{\text{ox}}} x \rho_{\text{ox}}(x) dx \tag{1.4}$$

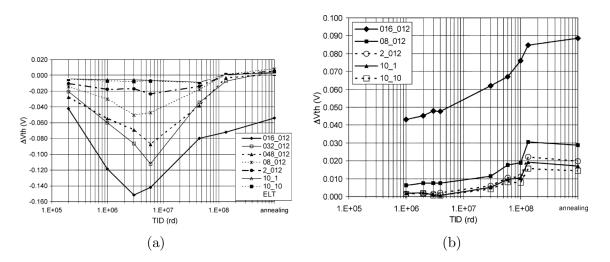

Note that this is an absolute threshold voltage shift, meaning NMOS devices will become faster and PMOS devices will become slower, e.g. [21] (Figure 1.5).

Figure 1.5: [21] Threshold voltage shift in commercial 130nm CMOS as a function of TID for different (a) NMOS and (b) PMOS transistor sizes, up to 136Mrads. PMOS threshold shift is absolute value. The last point refers to full annealing at 100°C.

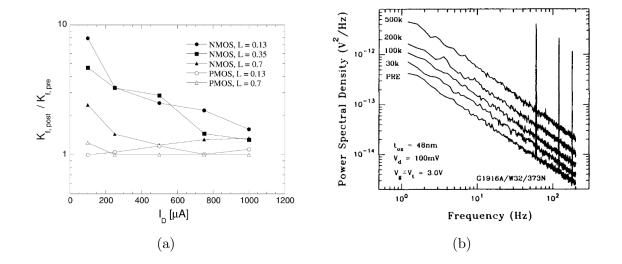

Flicker or 1/f noise in MOS devices also degrades with total ionizing dose. One oftencited contributor to flicker noise in MOS devices [50] is carrier trap and release at or near the silicon-oxide interface. There is contention [34] surrounding the McWhorter model and the source of electronic flicker noise, but physical origins of flicker aside, [51] measured the 1/f noise in MOS devices through irradiation and annealing, noting a strong correlation between flicker noise and oxide trapped charge, and no correlation between flicker noise and interface trap charge (up to 10kHz). [63] ran extensive device characterizations on 0.13µm CMOS devices and showed increases in the flicker noise coefficient  $K_f$  for n-channel devices, particularly at low drain currents, with significantly less of an increase for p-channel devices (Figure 1.6).

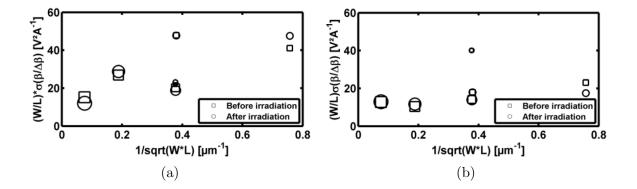

Figure 1.6: (a) [63] Ratio between the value of 1/f noise parameter  $K_f$  at 10Mrad absorbed dose of <sup>60</sup>Co  $\gamma$ -rays and the value before irradiation as a function of drain current  $I_D$  for NMOS and PMOS devices in the 0.13µm process. (b) [51] 1/f noise spectra  $S_v$  as a function of total dose. The device was under +6V bias during irradiation.

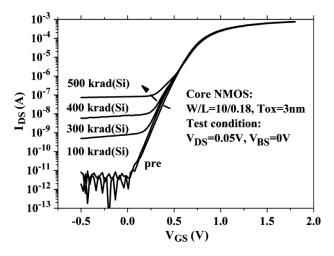

For MOS device leakage, [35] showed significant increases in off-state leakage current for HV, I/O, and core devices, particularly under subthreshold bias conditions (Figure 1.7). They also observed a "hump" in the  $I_D$ - $V_{GS}$  curves for several devices, attributable to oxide trapped charge trapping in the corners of devices' shallow trench isolation (STI).

Figure 1.7: [35]  $I_{DS}$ - $V_{GS}$  characteristics before and after TID irradiation for a core NMOS device.

Trapped charge in isolation oxide can also form a parasitic transistor, exacerbating drain induced barrier lowering (DIBL) by providing a charge path through what should have been isolation oxide on the sides of the transistor [86]

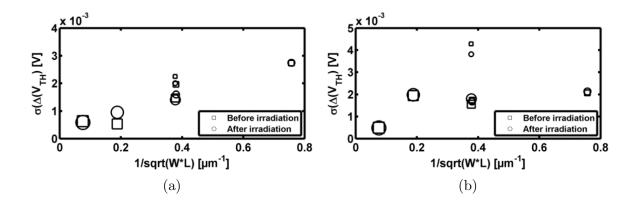

Ionizing radiation also tends to exacerbate mismatch by degrading devices more quickly, but at different rates. [76] measured variation in the mismatch parameters  $\Delta V_t$  and  $\frac{\Delta\beta}{\beta}$  based on Equation 1.5.

$$\frac{\Delta I_D}{I_D} = \frac{\Delta \beta}{\beta} + \Delta V_t \left(\frac{g_m}{I_D}\right) \tag{1.5}$$

Examining threshold voltage and current factor mismatch before and after irradiation, they found marginal increases in the mismatch parameters for standard MOSFETs in their given process, and smaller increases in these parameters for dedicated enclosed layout devices (Figures 1.8 and 1.9).

Figure 1.8: [76] Threshold voltage mismatch between identically designed pairs of a regular and b enclosed transistors before and after  $\gamma$  irradiation up to 100kGy.

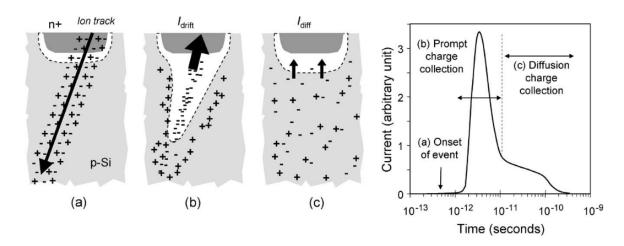

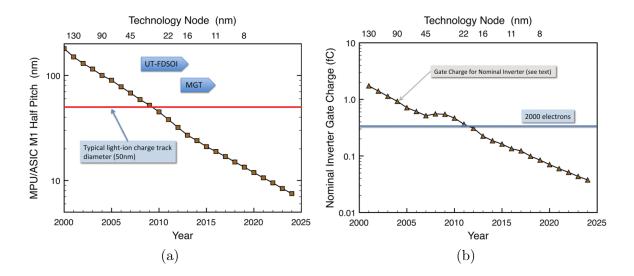

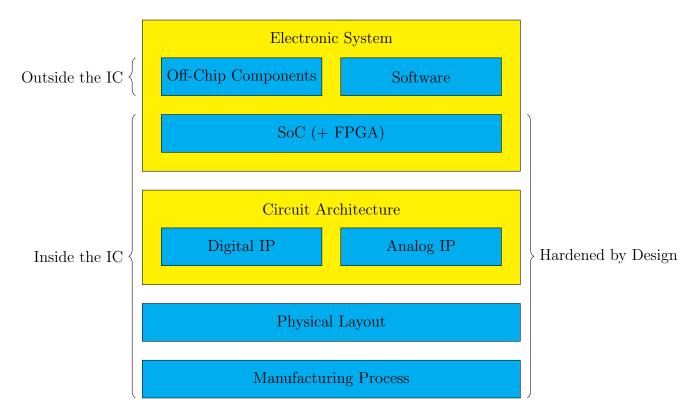

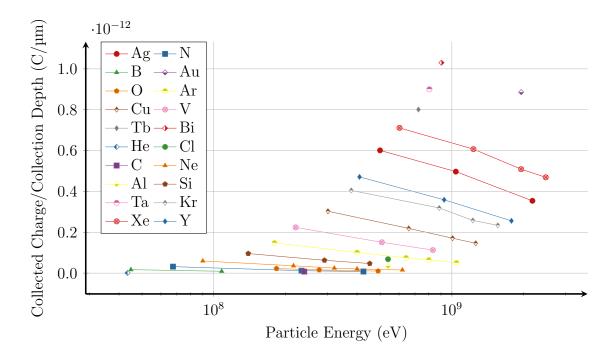

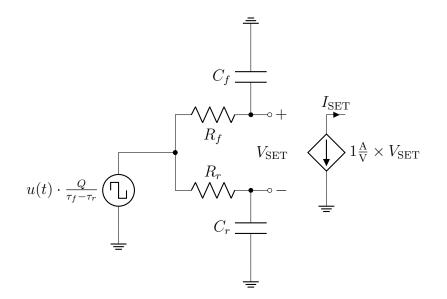

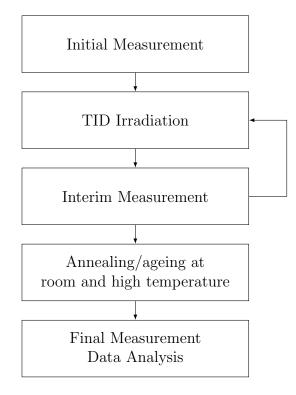

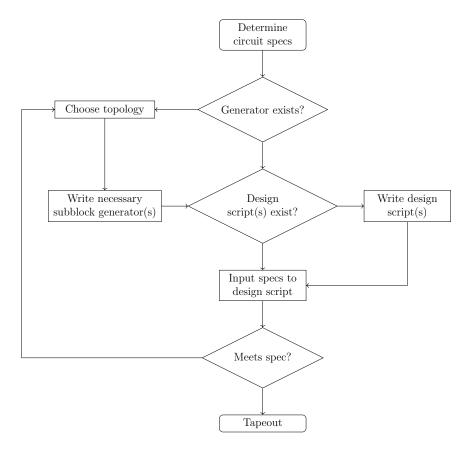

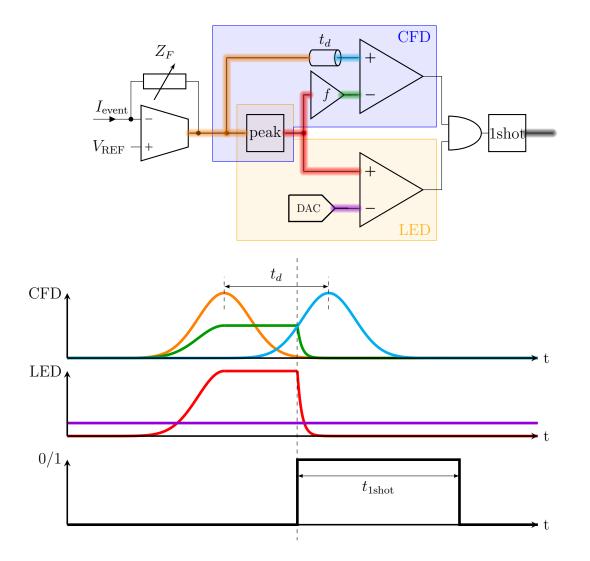

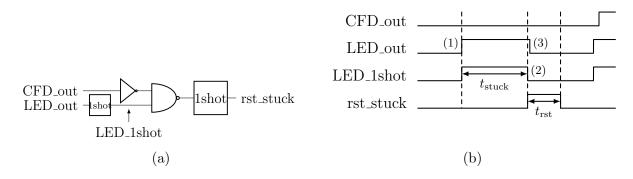

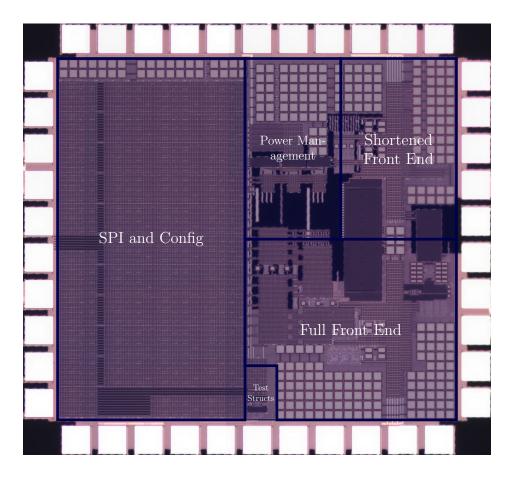

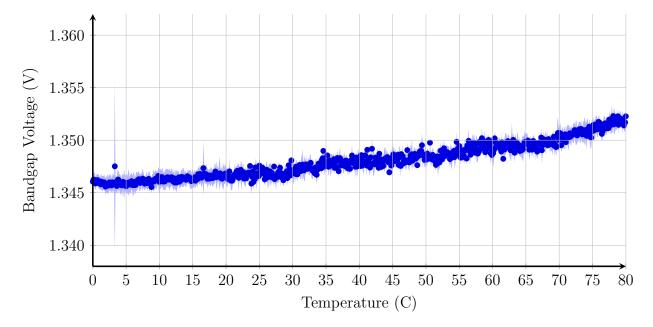

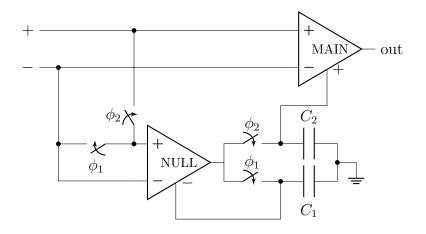

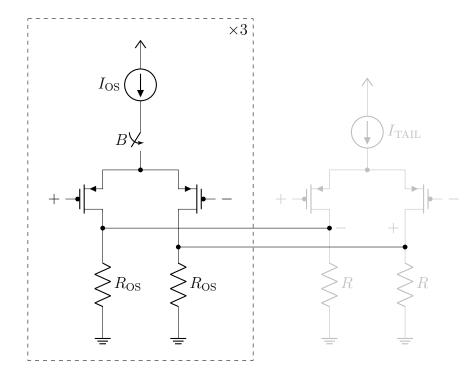

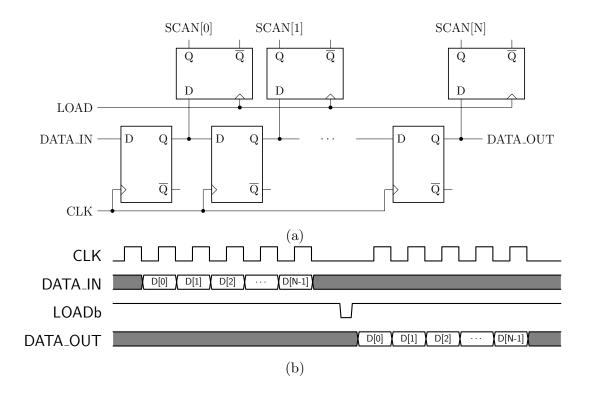

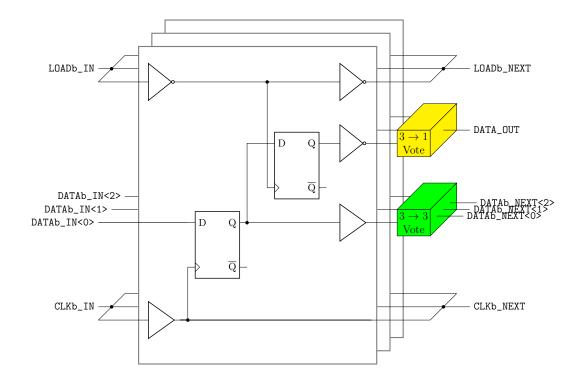

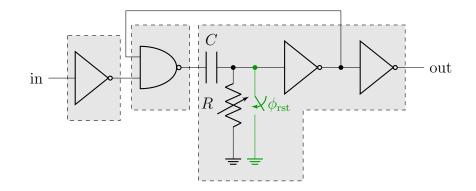

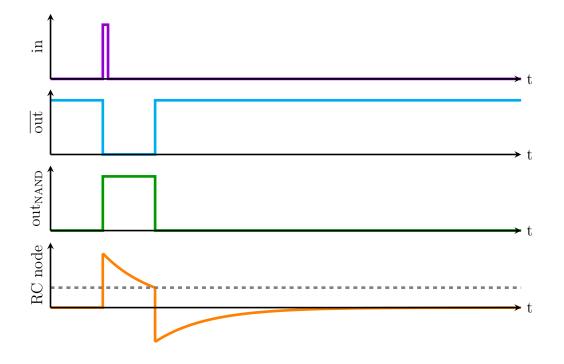

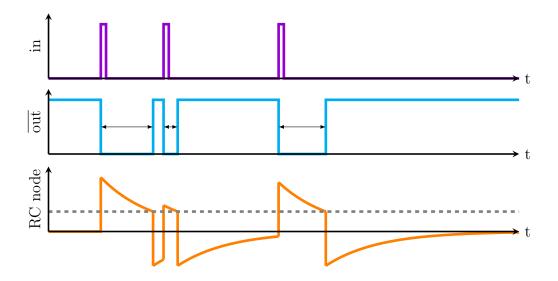

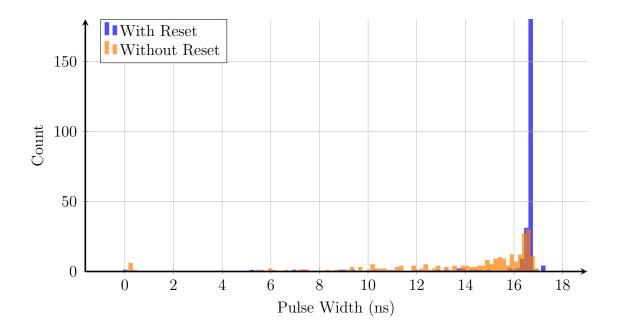

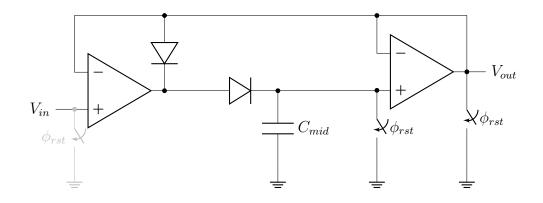

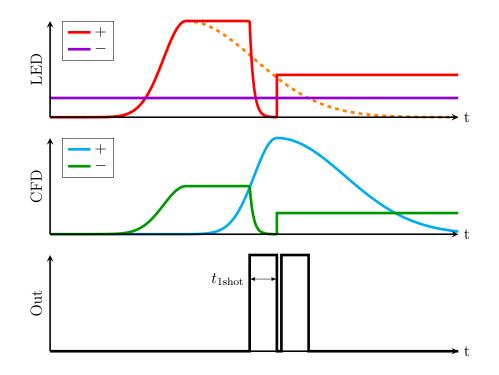

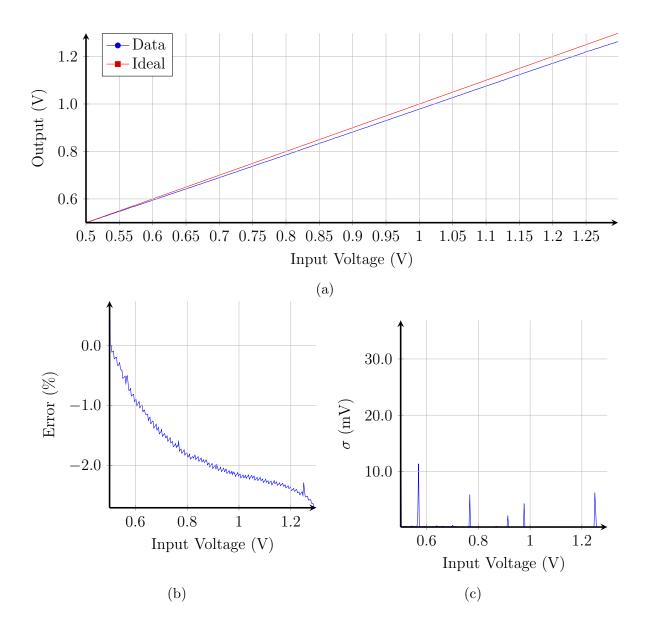

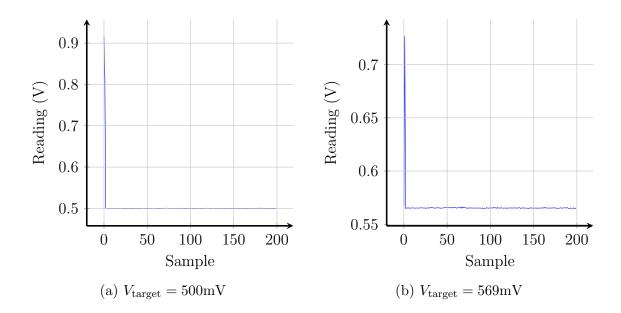

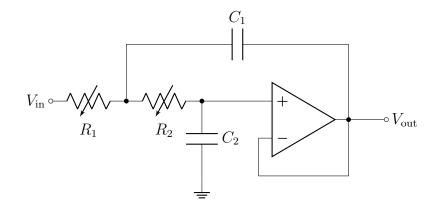

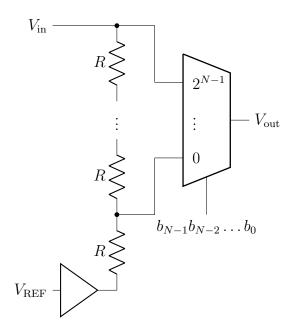

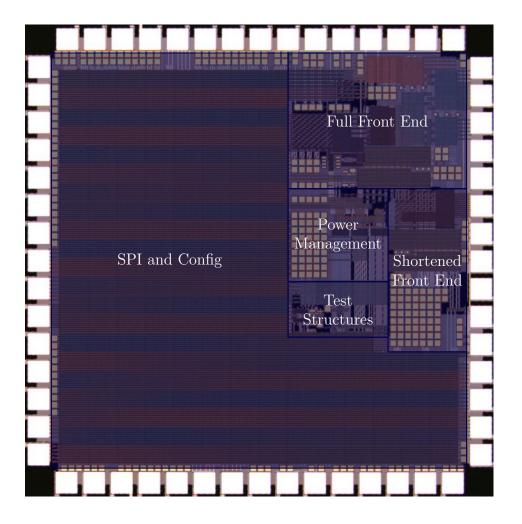

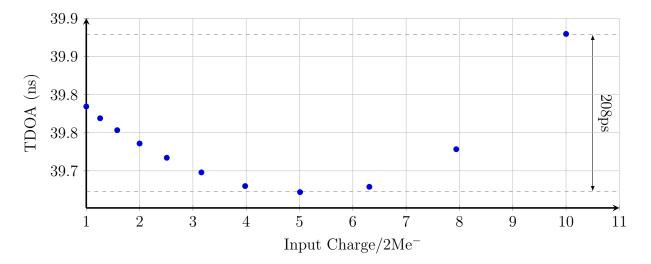

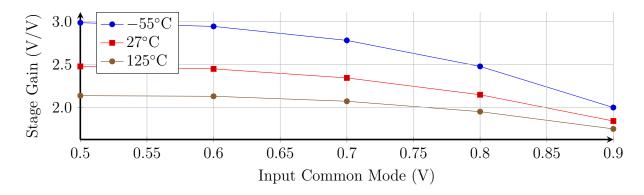

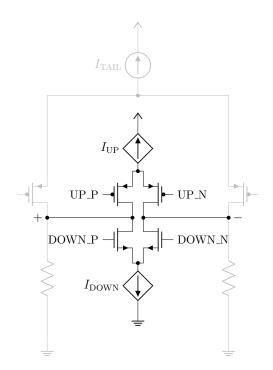

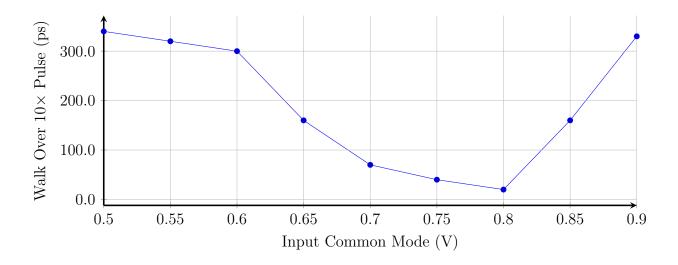

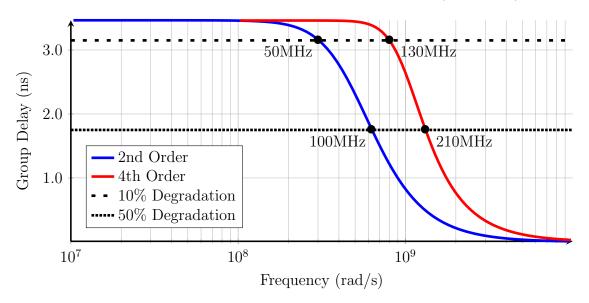

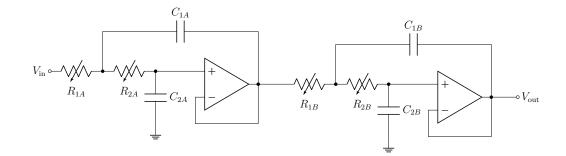

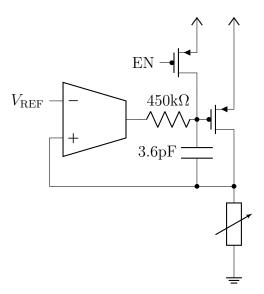

Figure 1.9: [76] Standard deviation of the current factor mismatch between identically designed pairs of a regular and b enclosed transistors before and after  $\gamma$  irradiation up to 100kGy.