# **UC Berkeley**

## **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Thermal Ground Plane for Chip-Level Electronics Cooling

#### **Permalink**

https://escholarship.org/uc/item/61v0s8q3

#### **Author**

So, Hongyun

### **Publication Date**

2014

Peer reviewed|Thesis/dissertation

### Thermal Ground Plane for Chip-Level Electronics Cooling

by

### Hongyun So

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Mechanical Engineering

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Albert P. Pisano, Chair Professor Liwei Lin Professor Tsu-Jae King Liu

Fall 2014

# Thermal Ground Plane for Chip-Level Electronics Cooling

Copyright © 2014 by Hongyun So

#### Abstract

Thermal Ground Plane for Chip-Level Electronics Cooling

by

#### Hongyun So

Doctor of Philosophy in Mechanical Engineering

University of California, Berkeley

Professor Albert P. Pisano, Chair

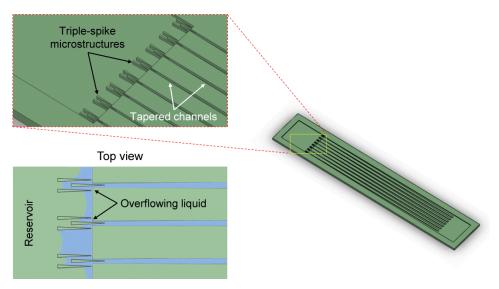

The three-dimensional thermal ground plane was developed in response to the needs of high-power density electronics applications in which heat must be removed as close to the chip surface as possible. The novel design for this planar cooling device was proposed with three key innovations in the evaporator, wick, and reservoir layer, which provided enhanced and reliable cooling performance without wick dryout and back flows. For the evaporator and reservoir layer, a combination of a tapered channel and a triple-spike microstructure was designed to break up the pinned meniscus at the end of the vapor and liquid channels. The overall microstructure had three spikes where the main liquid meniscus was separated by a middle spike and then continued to flow between the tapered walls of the middle and side spikes. For the wick layer, a nanowire-integrated microporous silicon membrane was developed to overcome dryout by driving the coolant out of the channels and spreading the coolant on top of the wick surface with the assistance of extended capillary action. This innovative design used nanowires to extend and enhance capillary force, especially at the end of the pores where the coolant was pinned and unable to overflow out of the pores. The chronic dryout problem in micro cooling devices could be solved by these innovative designs.

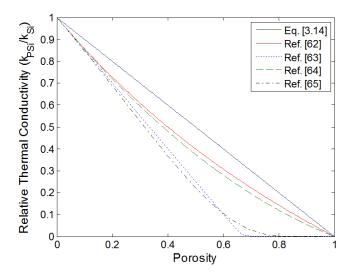

To analyze the thermal-fluid system, fluid dynamic and phase-change models were used to calculate thermodynamic and fluidic properties, such as operating temperature, pressure, vaporliquid interface radius of curvature, and rate of bubble formation. The microscale heat conduction theory derived from traditional Fourier's law with classical size effect and effective medium theory were used to calculate the thermal conductivities of nanowires and porous silicon wick in the cross-plane direction, respectively. The theoretical results of porous silicon showed good agreement with the experimental results measured by the  $3\omega$  technique, demonstrating the reduction of thermal conductivity from bulk silicon. Cooling performance of the developed device was demonstrated experimentally with a micro ceramic heater, thermocouple modules, and microfabrication techniques, including photoelectrochemical etching to create porous silicon, deep reactive-ion etching to form a thin wick membrane, and hydrothermal synthesis to grow nanowires on top of the wick membrane. This study shows the feasibility of reliable, continuous, and high-performance micro cooling devices using enhanced capillary forces to address the increasing requirements of thermal management for chip-level electronics.

To my family

### **TABLE OF CONTENTS**

| Dedication  | n                       |                                                                                                  | i  |

|-------------|-------------------------|--------------------------------------------------------------------------------------------------|----|

| Table of C  | Content                 | s                                                                                                | ii |

| List of Fig | gures                   |                                                                                                  | iv |

| List of Ta  | bles                    |                                                                                                  | ix |

| Acknowle    | dgemei                  | nts                                                                                              | X  |

| Chapter 1   | Intro                   | oduction                                                                                         | 1  |

| 1.1         | Motiv                   | ation                                                                                            | 1  |

|             | 1.1.1<br>1.1.2          | Current Cooling Technologies                                                                     |    |

| 1.2         | Disser                  | tation Outline                                                                                   | 3  |

| Chapter 2   | Desi                    | gn and Operating Principles                                                                      | 5  |

| 2.1         | Three-                  | -Dimensional Stacked Design                                                                      | 5  |

|             | 2.1.1<br>2.1.2<br>2.1.3 | Evaporator: Self-Transport of Condensed Liquid                                                   | 8  |

| 2.2         | Opera                   | ting Principles for Heat Removal                                                                 | 11 |

|             | 2.2.1<br>2.2.2<br>2.2.3 | Continuous Feeding of Coolant  Thermal Barrier of Coherent Wick  Drop Propulsion in Microchannel | 13 |

| Chapter 3   | Heat                    | Transfer Analysis                                                                                | 15 |

| 3.1         | Micro                   | scale Heat Conduction                                                                            | 15 |

|             | 3.1.1<br>3.1.2          | Kinetic Theory of Thermal Transport                                                              |    |

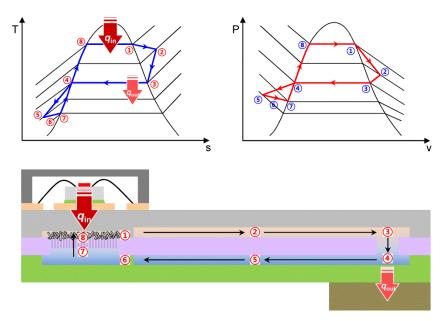

| 3.2         | Therm                   | nodynamics Analysis of Closed Loop System                                                        | 23 |

|             | 3.2.1<br>3.2.2          | Thermal Resistance Network of System Thermodynamic Cycle during Operation                        |    |

| Chapter 6            | Conc                    | clusions                                                                             | 60 |

|----------------------|-------------------------|--------------------------------------------------------------------------------------|----|

|                      | 5.3.2                   | Experimental Results                                                                 |    |

|                      | 5.3.1                   | Final Feature of Device                                                              |    |

| 5.3                  | Coolin                  | ng Performance Test                                                                  | 55 |

|                      |                         | Principles of 3ω Method<br>Experimental Results                                      |    |

| 5.2                  |                         | nal Conductivity Measurement                                                         |    |

|                      | 5.1.1<br>5.1.2          | Self-Transport of Condensed Liquid  Continuous Wicking through Hierarchical Membrane |    |

| 3.1                  | _                       | I Feeding Performance Test                                                           |    |

| <b>Chapter 5</b> 5.1 | -                       | Proding Performance Test                                                             |    |

|                      |                         | ,                                                                                    |    |

|                      | 4.3.1<br>4.3.2          | Vapor-Liquid-Solid Mechanism                                                         |    |

| 4.3                  |                         | Oxide Nanowire Synthesis by Bottom-Up Approach                                       |    |

|                      | 4.2.3                   | Fabrication Results                                                                  |    |

|                      | 4.2.1<br>4.2.2          | Principles of Photoelectrochemical Etching                                           |    |

| 4.2                  |                         | ent Porous Silicon Wick Fabrication                                                  |    |

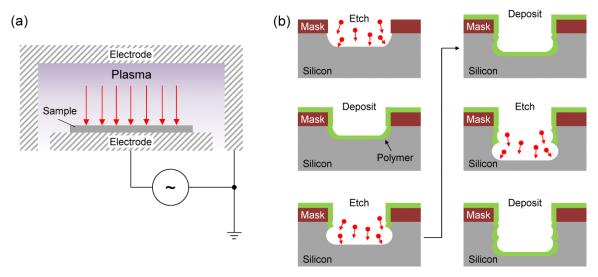

|                      | 4.1.1<br>4.1.2<br>4.1.3 | Principles of Deep Reactive-Ion Etching                                              | 33 |

| 4.1                  |                         | orator and Reservoir Fabrication by Top-Down Process                                 |    |

| -                    |                         | ce Fabrication                                                                       |    |

| CI                   | D.                      |                                                                                      | 20 |

|                      | 3.3.2                   | Two-Phase Nucleation Analysis                                                        |    |

|                      | 3.3.1                   | Analysis for Fluidic and Thermal Properties                                          |    |

| 3.3                  | Liquid                  | d-Vapor Phase Change                                                                 | 27 |

# **List of Figures**

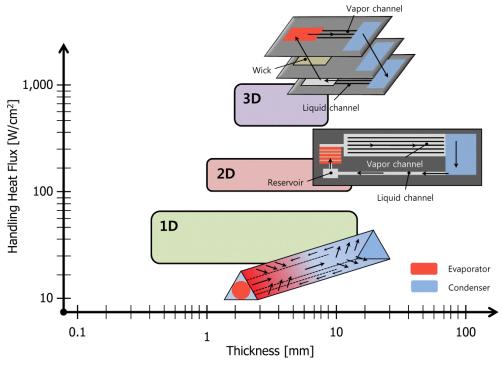

| Figure 2.1 | General limit of handling heat flux with respect to the critical dimension of the devices.                                                                                                                                                                                                                                                                                                        | 5  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

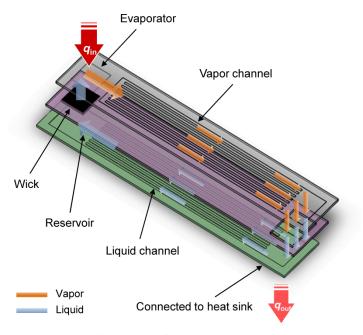

| Figure 2.2 | Three-dimensional schematic illustration of the three-layer stacked thermal ground plane device for chip-level electronics cooling.                                                                                                                                                                                                                                                               | 6  |

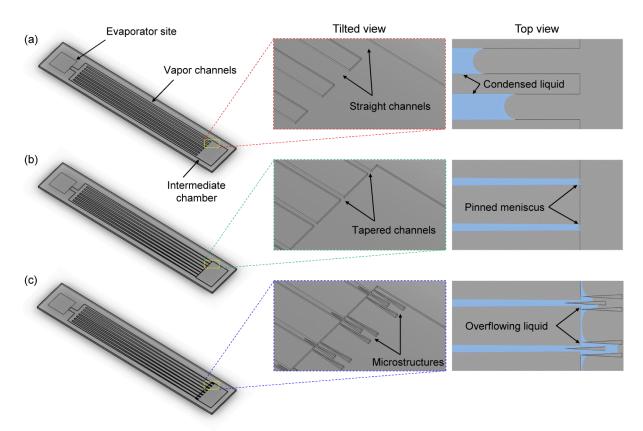

| Figure 2.3 | Schematic illustration of the design development process for evaporator channels: (a) straight vapor channels for simple design, (b) tapered vapor channels with specific tapered angle to enhance the capillary pressure, and (c) tapered vapor channels with crown-shaped triple-spike microstructures at the end of channels to distribute the liquid meniscus inducing overflowing of liquid. | 7  |

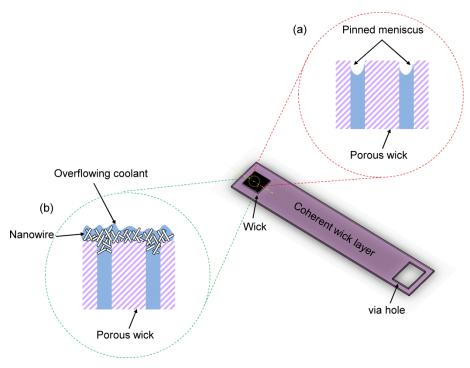

| Figure 2.4 | Schematic illustration of the design for coherent wick layer: (a) pinned liquid meniscus at the end of vertically aligned microchannels and (b) overflowing liquid by the enhanced and extended capillary force using nanowires grown over the top surface of the wick.                                                                                                                           | 9  |

| Figure 2.5 | Schematic illustration of the design for reservoir layer with a combination of tapered microchannels and triple-spike microstructures at the end of each channel to rapidly collect the condensed liquids into the reservoir.                                                                                                                                                                     | 10 |

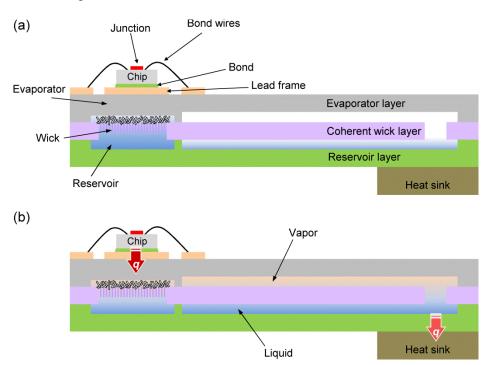

| Figure 2.6 | Scheme of cross-sectional view of the thermal ground plane with hot chip integrated on the evaporator layer for cooling purposes and internal fluid status at (a) device off-mode and (b) device on-mode.                                                                                                                                                                                         | 11 |

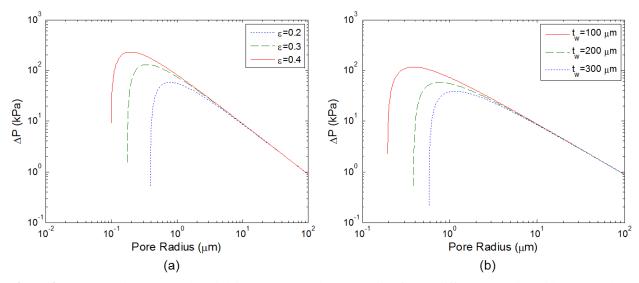

| Figure 2.7 | Pressure drop across the wick in response to the pore radius for (a) different porosity with constant heat flux of $40~\text{W/cm}^2$ and wick membrane thickness of $200~\mu\text{m}$ and (b) different wick membrane thickness with constant heat flux of $40~\text{W/cm}^2$ and porosity of $0.2$ .                                                                                            | 13 |

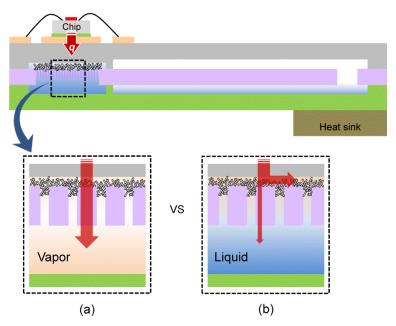

| Figure 2.8 | Schematic illustration of the role of the coherent wick layer as a thermal barrier to initiate boiling on the evaporator site: (a) dryout limitation when the thermal resistance of the wick is low and (b) desirable operation of the device when the thermal resistance of the wick is high enough.                                                                                             | 14 |

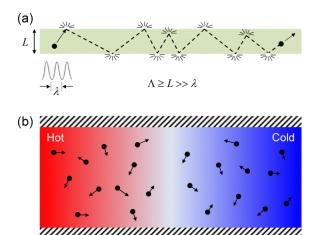

| Figure 3.1 | Schematic of (a) classical size effect when the characteristic length ( $L$ ) is smaller than the mean free path ( $\Lambda$ ) and larger than the wavelength ( $\lambda$ ) and (b) control volume for a derivation of modified Fourier's law rested on kinetic theory.                                                                                                                           | 16 |

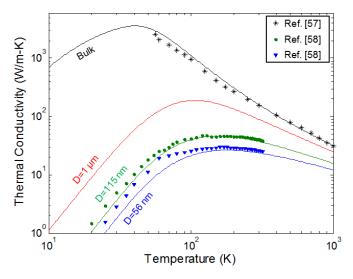

| Figure 3.2 | Calculated thermal conductivities for silicon from kinetic theory and comparison with experimentally measured thermal conductivities for a different diameter of silicon nanowires.                                                                                                                                                                                                               | 18 |

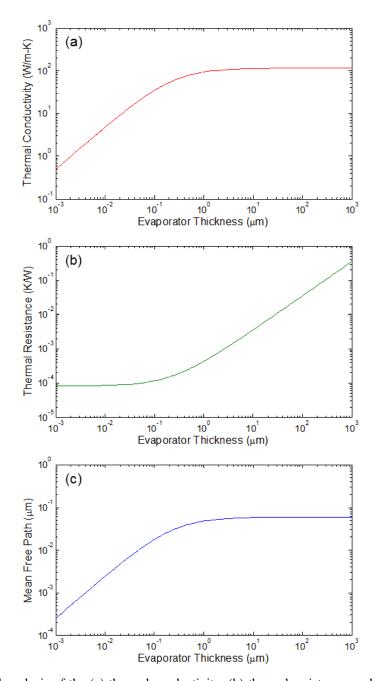

| Figure 3.3 | Calculated thermal conductivities of (a) zinc oxide (ZnO) with experimental results for a bulk sample and nanowires of different diameters and (b) silicon of the same diameter as ZnO for comparison purpose. The result shows that the thermal conductivities of ZnO are lower than those of silicon for all temperature ranges.    | 18 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

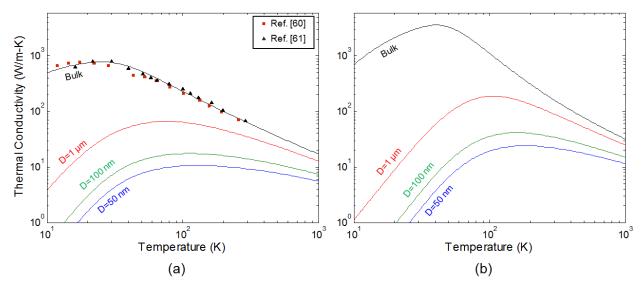

| Figure 3.4 | Theoretical analysis of the (a) thermal conductivity, (b) thermal resistance, and (c) effective mean free path of the evaporator layer at $100^{\circ}$ C with respect to the thickness. Active cooling area is $5 \times 5 \text{ mm}^2$ .                                                                                           | 20 |

| Figure 3.5 | Comparison of theoretical models to predict the effective thermal conductivity of porous silicon with respect to the porosity.                                                                                                                                                                                                        | 22 |

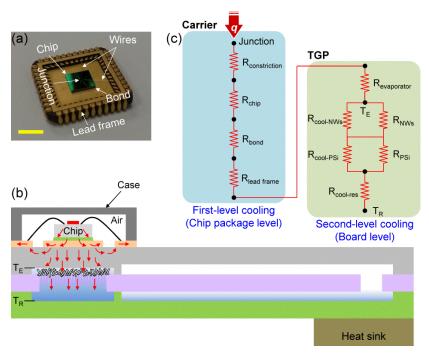

| Figure 3.6 | (a) Image of the MEMS chip mounted on a chip carrier for first-level cooling, (b) schematic illustration of the chip integrated on a thermal ground plane for second-level cooling, and (c) thermal resistance network of the combined devices for simultaneous cooling. Scale bar: (a) 5 mm.                                         | 24 |

| Figure 3.7 | T (temperature)-s (specific entropy) and P (pressure)-v (specific volume) thermodynamic diagram during the operation in the thermal ground plane with a schematic illustration for each state point in the device.                                                                                                                    | 26 |

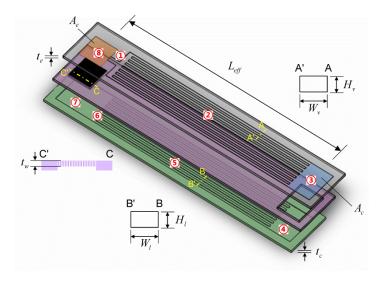

| Figure 3.8 | Schematic illustration of the overall thermal ground plane device with geometry and noticeable points for the thermal system analysis.                                                                                                                                                                                                | 28 |

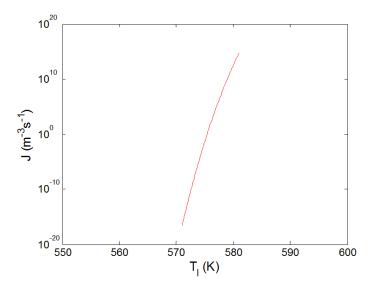

| Figure 3.9 | Computed rate of bubble formation with different liquid temperatures for homogeneous nucleation based on the kinetic limit of superheat.                                                                                                                                                                                              | 31 |

| Figure 4.1 | Schematic illustrations of (a) asymmetrical reactive-ion etching system chamber and (b) working principles of deep reactive-ion etching using alternative etching and polymer deposition cycles.                                                                                                                                      | 33 |

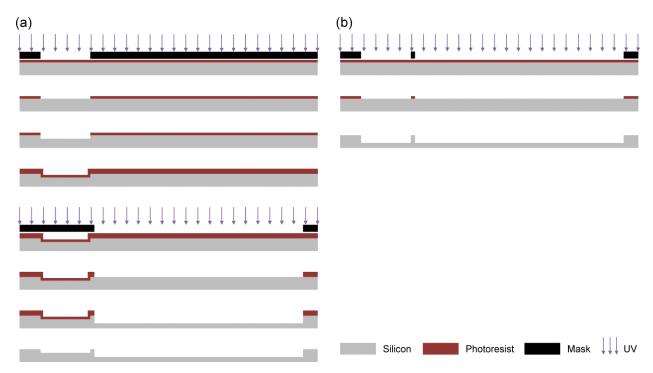

| Figure 4.2 | Fabrication flow schematic of (a) evaporator layer and (b) reservoir layer using standard photolithography and deep reactive-ion etching.                                                                                                                                                                                             | 34 |

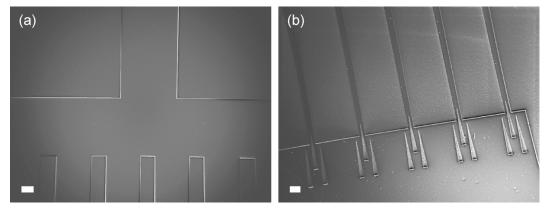

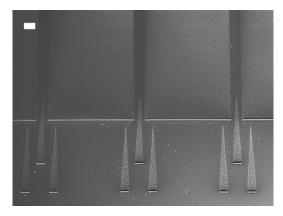

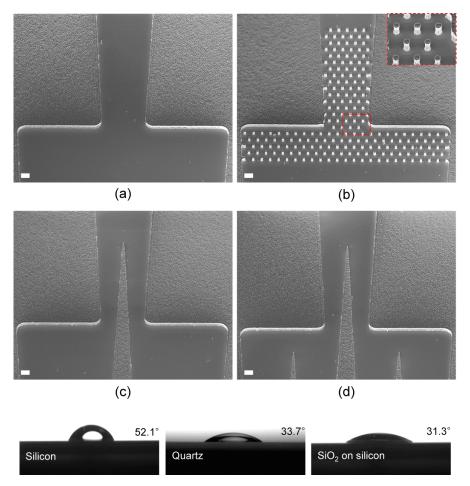

| Figure 4.3 | SEM images of deep reactive-ion etched evaporator layer: (a) neck part where the evaporator site and vapor channels are connected and (b) intermediate chamber, which is the end of the tapered vapor channels where the condensed liquid meniscus overflows by triple-spike microstructure. Scale bars: 200 µm for both (a) and (b). | 35 |

| Figure 4.4 | Zoomed-in view of triple-spike microstructures at the end of tapered vapor and liquid channels to drive the liquid meniscus out of the channels by extending the capillary action. Scale bar: 100 µm.                                                                                                                                 | 35 |

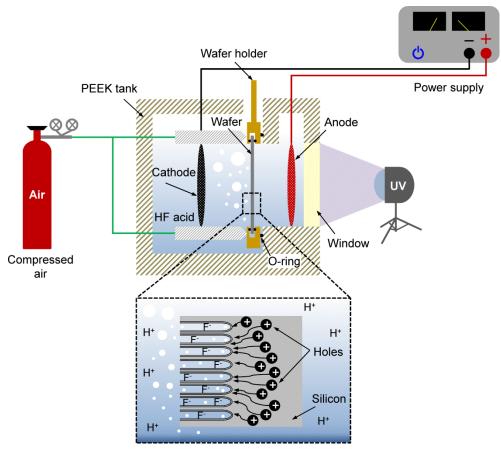

| Figure 4.5  | Schematic illustration of the coherent porous silicon fabrication process by photoelectrochemical etching process. The minority carriers in n-type silicon move to the hydrofluoric acid-silicon contact surface to attack the weaken silicon-silicon bond.                                                                                                                                                                                                                                           | 37 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

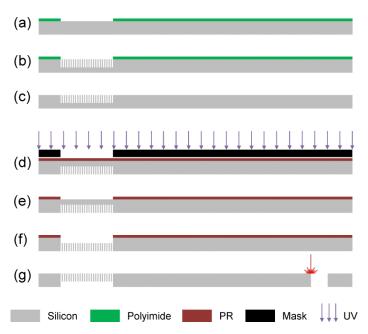

| Figure 4.6  | Fabrication flow of (a-c) coherent porous silicon wick by local photoelectrochemical etching, (d-f) deep reactive-ion etching of backside of wafer, and (g) laser etching through the layer for via hole connected to the condenser.                                                                                                                                                                                                                                                                  | 38 |

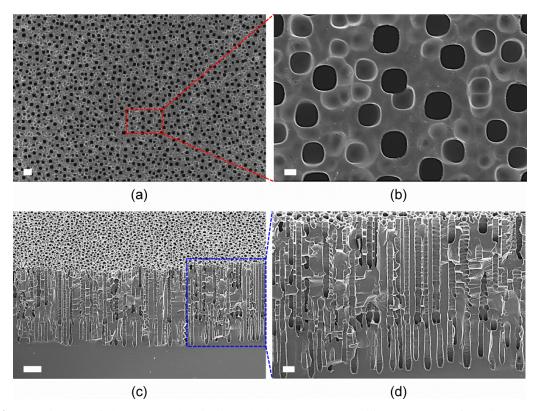

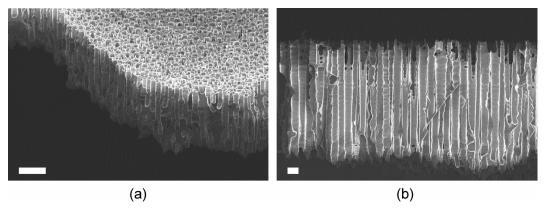

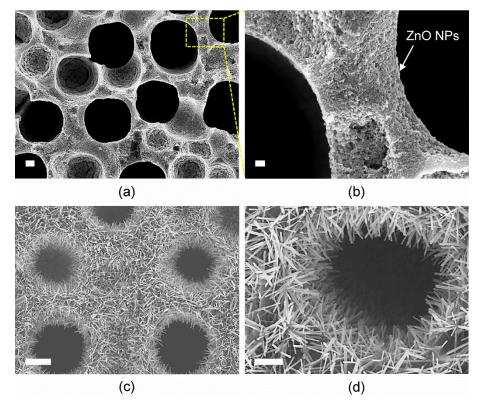

| Figure 4.7  | SEM images of photoelectrochemically etched coherent porous silicon: (a) top surface view, (b) zoomed-in view of micropores, (c) 45° tilted view, and (d) zoomed-in view of straight and vertically aligned microchannels generated by coherent porous silicon. Scale bars: (a) 10 $\mu$ m, (b) 2 $\mu$ m, (c) 30 $\mu$ m, and (d) 10 $\mu$ m.                                                                                                                                                        | 39 |

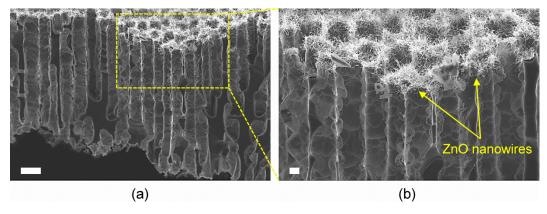

| Figure 4.8  | SEM images of coherent porous silicon wick membrane after backside deep reactive-ion etching: (a) $30^\circ$ tilted view and (b) cross-sectional view. Scale bars: (a) $30~\mu m$ and (b) $10~\mu m$ .                                                                                                                                                                                                                                                                                                | 40 |

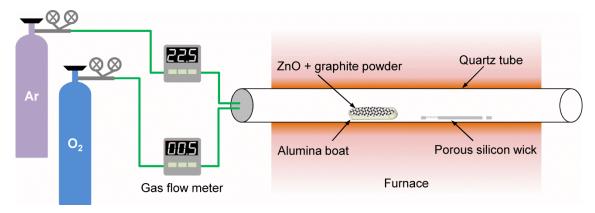

| Figure 4.9  | Schematic illustration of experimental setup for vapor-liquid-solid zinc oxide nanowires growth on the photoelectrochemically etched porous silicon wick layer.                                                                                                                                                                                                                                                                                                                                       | 41 |

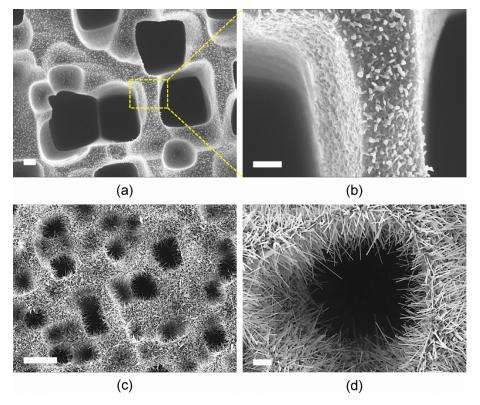

| Figure 4.10 | SEM images of the porous silicon wick membrane decorated by zinc oxide nanowires synthesized by vapor-liquid-solid mechanism: (a) initiation of growth from the gold catalyst particles on the porous silicon substrate, (b) zoomed-in view of initial formation of whiskers, (c) top surface view of nanowire-integrated porous silicon wick, and (d) zoomed-in view of micropore ends covered by zinc oxide nanowires. Scale bars: (a) 2 $\mu$ m, (b) 1 $\mu$ m, (c) 10 $\mu$ m, and (d) 1 $\mu$ m. | 41 |

| Figure 4.11 | Fabrication flow of nanowire-decorated porous silicon wick layer by (a-b) standard photolithography, (c-d) deposition of zinc oxide nanoparticles by lift-off, and (e-f) hydrothermal synthesis in precursor solution.                                                                                                                                                                                                                                                                                | 43 |

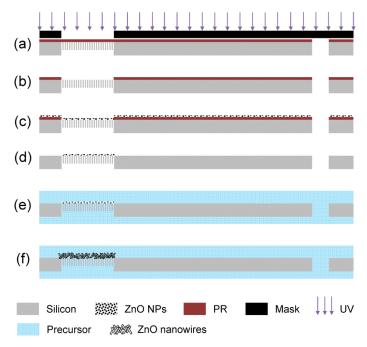

| Figure 4.12 | SEM images of the porous silicon wick membrane covered by zinc oxide (ZnO) nanowires synthesized by hydrothermal methodology: (a) seeded porous silicon wick by ZnO nanoparticles, (b) zoomed-in view, (c) top surface view of nanowire-integrated porous silicon wick, and (d) zoomed-in view of micropore ends covered by ZnO nanowires. Scale bars: (a) 1 $\mu$ m, (b) 200 nm, (c) 2 $\mu$ m, and (d) 1 $\mu$ m.                                                                                   | 44 |

| Figure 4.13 | SEM images of the hierarchical porous silicon wick layer decorated by zinc oxide nanowires to drive the coolant out of the pore by the assistance of extended capillary action: (a) $20^{\circ}$ tilted view and (b) zoomed-in view. Scale bars: (a) $10~\mu m$ and (b) $2~\mu m$ .                                                                                                                                                                           | 44 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

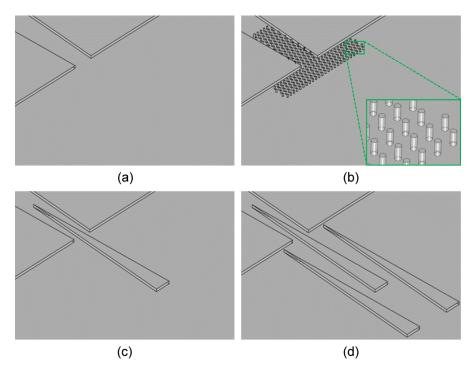

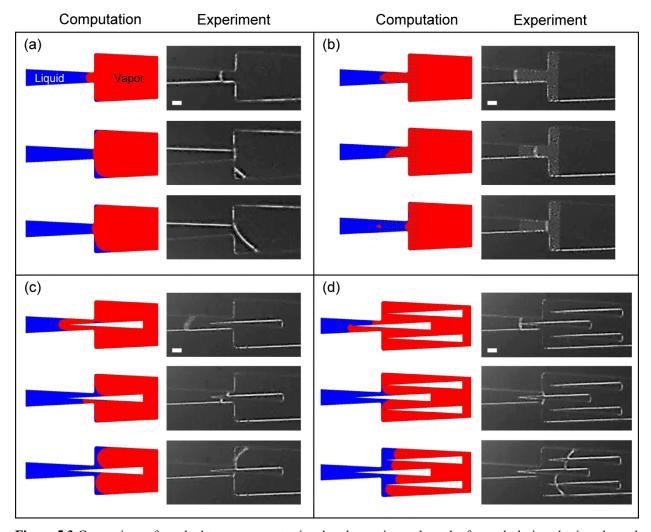

| Figure 5.1  | Schematic illustrations of microchannel designs in the evaporator layer to transport the condensed liquid into the reservoir chamber: (a) tapered design, (b) micropost design in the tapered design, (c) single-spike design in the tapered design, and (d) triple-spike design in the tapered design.                                                                                                                                                       | 45 |

| Figure 5.2  | SEM images of four different fabricated designs for vapor and liquid channel in the thermal ground plane: (a) tapered channel, (b) microposts design in the tapered design, (c) single-spike design in the tapered design, and (d) triple-spike design in the tapered design. Scale bars: 20 µm for (a), (b), (c), and (d). Lower images: measured contact angles on the different surfaces including silicon with native oxide, quartz, and silicon dioxide. | 46 |

| Figure 5.3  | Comparison of results between computational and experimental results for each designed microchannel to transport the liquid liquid by extended capillary action. Scale bars: $100~\mu m$ for (a), (b), (c), and (d).                                                                                                                                                                                                                                          | 47 |

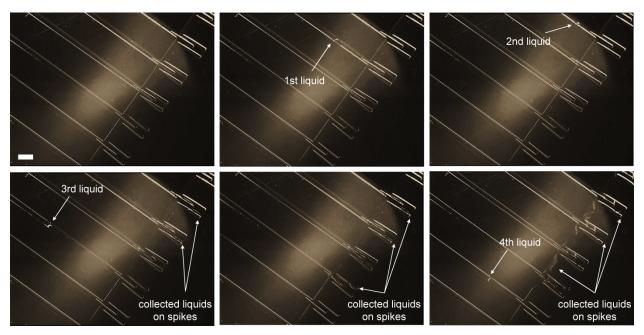

| Figure 5.4  | Sequential images of self-transporting condensed liquids in the evaporator channel (from top left to bottom right). The liquids were first transported along the tapered channels and then collected on the triple-spike microstructures by distributing menisci. Scale bar: $400~\mu m$ .                                                                                                                                                                    | 48 |

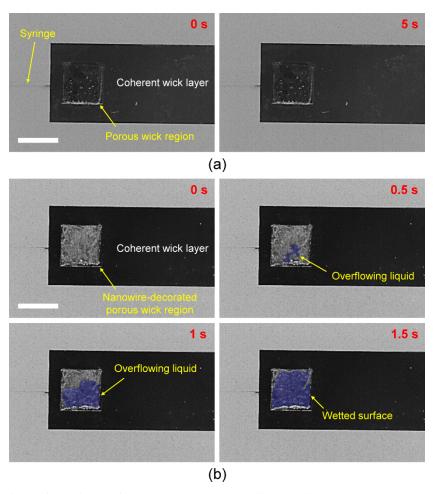

| Figure 5.5  | Comparison of wicking performance between (a) traditional wick structure and (b) nanowire-decorated coherent porous silicon wick structure. Sequential images were taken by a high-speed camera. Scale bars: 5 mm for (a) and (b).                                                                                                                                                                                                                            | 49 |

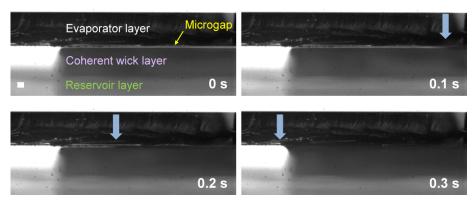

| Figure 5.6  | Feeding of coolant from reservoir to evaporator surface by nanowire-decorated coherent porous silicon wick structure. The microscale gap between evaporator and wick layer was filled with coolant in a short period of time. The blue arrow indicates the moving meniscus. Scale bar: $100~\mu m$ .                                                                                                                                                          | 50 |

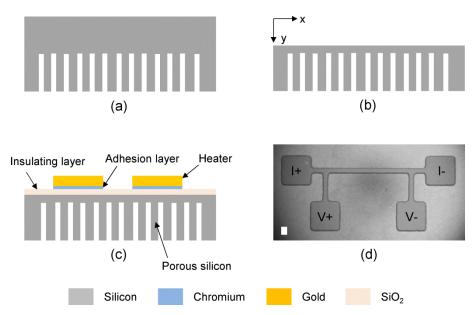

| Figure 5.7  | Sample preparation process for thermal conductivity measurement of the porous silicon wick structure by $3\omega$ method: (a) photoelectrochemical etching for forming the porous silicon wick, (b) deep reactive-ion etching of bulk silicon, (c) deposition of electrically insulating layer, followed by the microheater line, and (d) SEM image of fabricated heater line on the back side of porous silicon wick. Scale bar: (d) $100~\mu m$ .           | 52 |

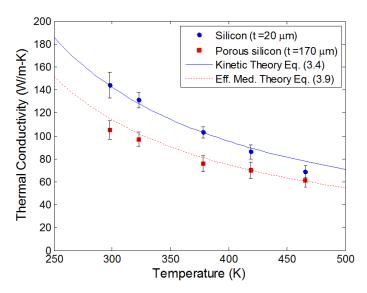

| Figure 5.8  | Thermal conductivities of bulk silicon (20 $\mu$ m) and porous silicon wick (170 $\mu$ m) measured by the 3 $\omega$ method as compared to computational results calculated by the kinetic theory and effective medium theory                                                                                                                                                                                                                                 | 55 |

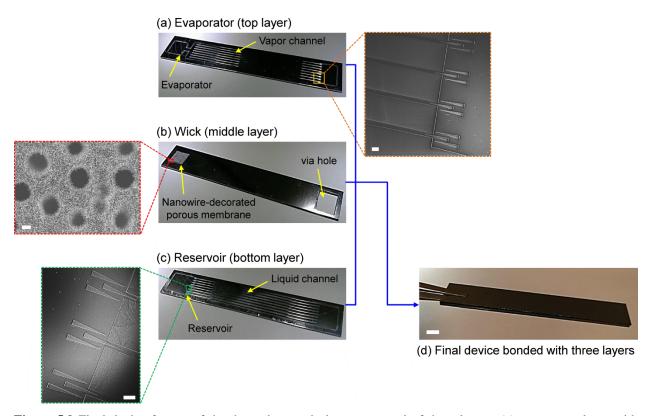

| Figure 5.9  | Final device feature of the thermal ground plane composed of three layers: (a) evaporator layer with triple-spike microstructure, (b) wick layer with nanowire-decorated coherent porous silicon, and (c) reservoir layer with triple-spike microstructure. Scale bars: (a) 200 $\mu$ m, (b) 2 $\mu$ m, (c) 200 $\mu$ m, and (d) 5 mm. | 56 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

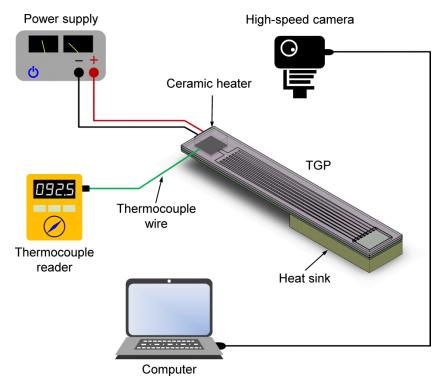

| Figure 5.10 | Schematic illustration of the experimental setup to analyze both qualitative and quantitative cooling performance of final fabricated thermal ground plane.                                                                                                                                                                            | 57 |

| Figure 5.11 | Transient phase-change of coolant in the evaporator site and movement of condensed liquid along vapor channels toward the intermediate chamber. The condensed liquids were collected on the triple-spike microstructures and continued to flow into the liquid channels in the reservoir layer. Time interval: 5 s; scale bar: 5 mm.   | 58 |

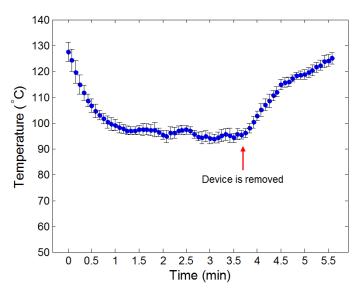

| Figure 5.12 | Temperature change of the micro ceramic heater during cooling by the fabricated thermal ground plane device. The device was removed from the heater after 3 min and 40 sec to verify the cooling performance of the device.                                                                                                            | 59 |

### **List of Tables**

| Table 3.1 | Parameter values determined by a combination of theory and fitting thermal conductivities with respect to temperature for bulk silicon and zinc oxide (ZnO) samples.                                | 17 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.2 | Thermal conductivities, lengths, and heat transfer area of each component participating heat conduction across the thermal ground plane layers from top of the junction to bottom of the reservoir. | 25 |

| Table 3.3 | Dimensions of the thermal ground plane device used for thermal and fluidic analysis.                                                                                                                | 29 |

| Table 3.4 | Calculated thermal and fluidic properties in the thermal ground plane based on the designed specifications.                                                                                         | 29 |

| Table 5.1 | Input parameters to extract the thermal conductivity from out-of-phase 3ω voltage for anisotropic porous silicon wick structure.                                                                    | 54 |

#### Acknowledgements

First and foremost, I would like to express my sincere appreciation to my research advisor, Professor Albert P. Pisano, for his technical guidance and financial support during my Ph.D. program. This research could not have been completed without the exceptional degree of freedom and encouragement Professor Pisano gave, which will always be remembered.

I also greatly acknowledge Professor Liwei Lin for providing the research environments in his laboratory and supporting active collaboration in my other project—microfluidic microdevices. All his classes inspired me with enthusiasm and helped broaden my perspectives in the field of nanoscience and technology. I am also very grateful to Professor Tsu-Jae King Liu for serving as a committee member for my doctoral qualifying examination and dissertation. Professor Liu offered me valuable feedback on my dissertation. I also wish to thank Professor Chris Dames for serving as a committee member for my doctoral qualifying examination and providing research collaboration for thermal conductivity measurement.

My fellow colleagues in the Berkeley Micromechanical Analysis and Design (BMAD) lab have played a large part in making my graduate life at Berkeley enjoyable. I especially want to thank Dr. Jim Cheng and Ms. Lilla Smith for their valuable discussions and instrumentation assistance for my research. I also wish to thank to Geoff Wehmeyer and Fan Yang in Professor Dames' group for their friendship and help in measurement of thermal conductivity.

I wish to express my deep gratitude to Professors Yongmo Kim and Sukkee Um at Hanyang University for their continuous encouragement, which always motivated me to chase my dream since I was an undergraduate. They were not only excellent advisors in academic aspects but also great mentors in my life. I also cannot forget to acknowledge Professor Young Ho Seo at Kangwon National University for providing various research collaborations with insightful ideas and invaluable advice during his sabbatical at the BMAD lab.

Last but not least, I would like to extend my deepest gratitude to my family, especially my parents. Without their unconditional support, endless love, and encouragement over many years, I could never have earned my doctorate in the United States. I also would like to thank my elder and younger brothers for their enduring care and belief in me no matter what I do. Thank you all again for making me appreciate what I have earned here at the University of California, Berkeley.

# Chapter 1

### Introduction

#### 1.1 Motivation

Thermal management for electronics is a chronic, essential issue for achieving a high performance level of electronic devices by preventing thermal damages including degradation, thermal shock, and vibration. In general, poor removal of heat flux causes device failure with severe problems, which can affect whole operating systems. Efficient cooling of hot electronic devices is one of the key pieces for achieving high performance of devices. During the past decade, developments in semiconductor industries have allowed electronics such as sensors and actuators to be miniaturized in microscale to increase the yield in a limited space. Consequently, thermal management of chip-level electronics is now becoming critical for next-generation electronics. To satisfy the increasing market demand for cheaper, smaller, faster, and more reliable cooling, new miniaturized active and passive cooling devices are being developed for efficient and rapid heat removal away from the heat sources.

The advent of microelectromechanical systems (MEMS) and nanotechnologies has allowed for the development of new microscale cooling devices that are compact and compatible with traditional semiconductor devices to efficiently remove high heat flux from heat sources. Among various heat removal methods including active, passive, or a combination of both, passive cooling is now prevailing in current chip-level applications because it does not require an additional power source that might need supporting electric circuit on the platform. The main passive cooling systems use the basic heat transfer mechanisms—conduction [1,2], convection [3,4], and radiation [5,6]—where the heat transfer rate generally relies on the thermal conductivity of substrates, properties of surrounding gases, or emissivity of surfaces. However, these systems are not suitable for many chip-level electronic applications because the systems' efficiency significantly depends on the material properties. Therefore, the combination of emerging MEMS technology and rapidly increasing demands for thermal management for advanced miniaturized electronics has led to the phase-change cooling techniques using superior heat absorption properties when the liquid coolants change to vapor [7-9].

Miniaturized planar-type cooling devices have recently been proposed to handle higher heat flux in a wide range of applications, from ground to space environments [10-13]. In these systems, the microchannels have been fabricated by various silicon etching technologies to utilize the capillary force of coolants during the device operation. However, unexpected dryout problems [14], backward bubble flow [15], and liquid-vapor interface oscillating [16] were caused by unstable capillary forces during the phase-change process. Consequently, the development of a MEMS-based phase-change micro cooling device, which would be able to overcome dryout problems with continuous, reliable, and controllable operation, has remained an engineering challenge.

#### 1.1.1 Current Cooling Technologies

Based on the physical mechanism, current cooling technologies can be categorized as active, passive, or hybrid systems. The most well-established active cooling device is a fan utilizing the forced convection to enhance the air velocity and thus the convective heat transfer coefficient and heat transfer rate [17-19]. The fan does not rely on the thermal conductivity of substrate materials and has an advantage for large area cooling applications. However, these active cooling systems require additional supporting power supply equipment and generate noise during the operation. The traditional passive cooling systems are thermal spreaders and heat pins utilized widely because of their advantages of zero noise and zero power consumption. These systems are based on the thermal conductivity of the solid substrate by contacting the substrate surface and heat source surface. To enhance the efficiency of heat removal, a heat pipe using the principles of both thermal conductivity and phase transition of a working fluid has been developed for many electronic applications [20,21]. A liquid in contact with conductive solid surface changes to a vapor by absorbing heat from the hot substrate. While traveling to the heat sink where the latent heat is released, the vapor turns into a liquid again and completes a cycle by returning the condensed liquid to the hot substrate through the capillary action. Although heat pipes require no maintenance because of the absence of mechanical moving parts, noncondensed gases may diffuse through the pipe walls, which may increase the thermal resistance and operating temperature and thus result in the breakdown of circulation of coolant and destruction of the device by increased pressure from non-condensed gases [22,23]. In addition, heat pipes developed thus far are more suitable in large-scale applications, such as solar power plants or building systems, rather than chip-level electronics. To maximize the efficiency of heat removal, hybrid cooling systems integrating both active and passive systems have been recently developed and are now being used for many applications [24,25].

#### 1.1.2 Thermal Management for High-Power Density Electronics

According to Moore's law, the number of transistors in an integrated circuit (IC) doubles approximately every two years, while the size of the individual chip decreases [26,27]. The decrease in the size of chips has led to increased heat dissipation per unit area of chip surface, while overall performance of ICs has improved, and the cost of individual transistors has been reduced [28]. Heat dissipation is considered to be a well-known reason for energy loss and a potential issue that may limit the performance of information processing [26,28]. Most MEMS actuators, which allow mechanical actuating parts to have a large surface-to-volume ratio, also generate tremendous heat flux during the operation using Joule heating through the electrodes. In such systems, current chip-level heat fluxes have already reached 10 W/cm<sup>2</sup> and are expected to exceed 200 W/cm<sup>2</sup> within a decade for many high-power density electronic applications. When these high heat fluxes exceed critical heat flux levels, which is the maximum heat flux that can be loaded on the chip and represents the operational limit of the device because of significantly reduced heat transfer coefficients, the device temperature will be dramatically increased, resulting in device failure [29,30]. Therefore, the increasing demand for thermal management of high-power density electronic devices, including laptops, mobile phones, light emitting diodes, solar cells, and batteries, has led to the development of various innovative cooling technologies [31-33].

#### 1.2 Dissertation Outline

This dissertation reports the development of a new three-dimensional planar-type cooling device. The overall outline for the dissertation is composed of five main chapters: (a) design of the device and operating principles, (b) heat transfer and thermodynamic analysis of the device, (c) device fabrication, (d) experimental testing of the fabricated device, and (e) conclusion and outlook. This dissertation is expected to provide promising and significant groundwork for next-generation cooling technologies to address the thermal management demands for high-power density electronics. The detailed overview of each chapter is as follows.

In Chapter 2, the novel design for a MEMS-based three-dimensional planar cooling device is described with three key innovations in each layer (i.e., evaporator, wick, and reservoir layer). To remove heat coming from hot chips through the evaporator layer, continuous feeding of the coolant without dryout is most important and key innovation in the overall system. In this chapter, the scheme of continuous fluid transport by a hierarchical micro- or nano-structured wick layer is proposed to prevent severe dryout problems during operation. This first novel structure in the wick layer was designed to maintain the circulation of coolant in the device during the steady-state operation. However, when the chip was turned off, droplets suddenly condensed due to decreased vapor pressure and temperature became stuck in the middle of the microchannels on the evaporator layer, which may cause dryout again, as these droplets did not return to the reservoir. Therefore, a second novel structure in the evaporator was designed to transport the stuck liquids automatically from microchannels to the reservoir for the preparation of the next cycle before the chip is turned on again. The last innovation in the device is directly related to the first innovation mentioned above. To induce the boiling of coolant near the evaporator site, the wick layer must act as a thermal barrier to prevent the nucleation of coolant in the reservoir by providing reasonably high thermal resistance. For this innovation, zinc oxide (ZnO) nanowires that have low thermal conductivity were selected and characterized rather than the other type of nanowires. The design and fabrication of nanowire-integrated porous silicon wick have been disclosed elsewhere [H. So, J. C. Cheng, and A. P. Pisano, "Nanowire-integrated microporous silicon membrane for continuous fluid transport in micro cooing device," Appl. Phys. Lett., vol. 103, 163102, 2013 and H. So, J. C. Cheng, and A. P. Pisano, "Multi-scale pore membrane for continuous, passive fluid transport in a micro cooling device," in Tech. Dig. Int. Conf. Solid-State Sensors., Actuat. Microsyst., 2013, pp. 2197–2200].

Chapter 3 describes microscale heat conduction theory derived from traditional Fourier's law with classical size effect to estimate the thermal conductivity of nanowires and evaporator layer in the cross-plane direction. Because the thermal conductivity of the device depends on the operating temperature, the temperature dependence on thermal conductivity in each layer is discussed with the kinetic theory. The effective medium theory is also discussed to estimate the thermal conductivity of porous silicon wick structure in cross-plane direction practically. After calculating the thermal conductivities for all components with the kinetic theory and effective medium theory, the thermal resistance network analysis is performed to determine the values of design parameters. Finally, numerical analysis for two-phase flow during the phase-change is discussed with various two-phase models and corresponding thermodynamic cycles to calculate the fluidic and thermal properties, such as operating pressure, temperature, interface radius of curvature, and rate of bubble formation.

In Chapter 4, the detailed overall fabrication process and results are presented for each layer. The overall fabrication process for the device includes four main processes: (1) photoelectrochemical (PEC) etching to create coherent porous silicon, (2) deep reactive-ion etching (DRIE) to form a thin wick membrane, (3) the hydrothermal method to synthesize nanomaterials on top of the wick membrane, and (4) surface treatment for changing the device surface property from hydrophobic to hydrophilic, which enhances the capillary action in the microchannels. The fabrication process is described in detail, layer by layer, using either a top-down or a bottom-up approach. Scanning electron microscope (SEM) images are shown in this chapter to characterize the fabrication results.

In Chapter 5, experimental results are shown, including the thermal conductivities in the cross-plane direction for each layer that were measured by the  $3\omega$  technique, wicking performance through the fabricated wick structure, and self-transported liquid along the tailored microchannel, along with acquired data and captured images. These experimental data are compared with the data from the numerical analysis from Chapter 3 to demonstrate the reliability of the proposed device. The detailed experimental setups and a sample preparation process are also presented, along with necessary images. Finally, the efficiency and heat removal capability of the fabricated device are discussed at the end of the chapter, along with the temperature change of the chip during cooling performance.

In Chapter 6, the entire content of the dissertation is summarized, and future works are discussed, including hermetic device sealing, the feasibility of the direct integration with ICs, and applications in harsh environments. The chapter concludes with a future outlook of the proposed device in relation to the field of MEMS-based micro cooling devices.

# Chapter 2

# **Design and Operating Principles**

### 2.1 Three-Dimensional Stacked Design

The dimensions of micro cooling devices rely on the heat flux handling limit. Figure 2.1 shows the general limit of handling heat flux with respect to the dimension of MEMS-based cooling devices. In general, a one-dimensional design of a device is able to be fabricated easily by anisotropic silicon etching using potassium hydroxide (KOH) or tetramethylammonium hydroxide (TMAH). After etching, wick materials such as mesh screen, nickel foam, or stainless steel fibers can be filled out along the edges of the triangle-shaped passage. After hermetic sealing of the evaporator layer, heat dissipation can be removed by phase-change inside the device, as shown in Fig. 2.1. Once the liquid receives heat from chips, the liquid in contact with the edges turns into a vapor, and this vapor travels to the other side of the device (i.e., condenser) across the middle of the chamber. After the vapor is condensed to liquid, liquid droplets return to the evaporator section through the wick materials. However, because the traveling vapor is in direct contact with turning liquid in the wick material, there is parasitic heat transfer from vapor to liquid during the circulation, which may cause oscillating vapor-liquid interface [15].

Figure 2.1 General limit of handling heat flux with respect to the critical dimension of the devices.

The two-dimensional design has been recently proposed and widely investigated, both theoretically and experimentally [11,34,35]. The critical innovation of these planar cooling devices is to use a thermal barrier between vapor and liquid channels to prevent parasitic heat transfer to the compensation chamber (see Fig. 2.1). Therefore, the condensed liquid can continue to remove heat from the sources within a thermodynamically stable state, which may maximize the efficiency of cooling performance. The wick structure—vertically aligned rectangular walls with a certain pitch distance—was also integrated using anisotropic silicon etching to maintain coolant contact with the evaporator surface. At initial state of the operation, the spaces between walls were filled with coolant, and thus there was contact with evaporator surface. However, as the liquid changed to vapor on the evaporator surface, a thin vapor film began to cover the heated evaporator surface and disturbed continuous feeding of the coolant from the wick structure, resulting in dryout problems. Furthermore, the fabrication of a vapor channel and a liquid channel on the same plane allowed vapor bubbles to form during boiling near the evaporator surface and to flow back to the coolant chamber. Therefore, a new and novel design microscale planar cooling device needed to be developed for improvement of cooling efficiency with a reliable operation that prevents severe dryout.

In this study, the three-dimensional Thermal Ground Plane (TGP), which is analogous to an electronic ground plane, was developed in response to high-power density electronic applications in which heat is removed as close to the chip surface as possible, which provides enhanced and reliable cooling performance without dryout and back flows. The TGP includes three main layers: evaporator, wick, and reservoir layer, as seen in Figure 2.2. It is noticeable that the wick layer also acts as a thermal barrier to separate the liquid channel from the vapor channel. The basic cooling mechanism is to use phase-change of coolant, similar to the process used in one- and two-dimensional devices. However, in the present study, novel and innovative structures were developed to feed the coolant continuously from the reservoir to the evaporator surface and to prevent the back flows of both bubbles and condensed liquids (i.e., achievable one-way flow).

**Figure 2.2** Three-dimensional schematic illustration of the three-layer stacked thermal ground plane device for chip-level electronics cooling.

#### 2.1.1 Evaporator: Self-Transport of Condensed Liquid

The evaporator layer that is in direct contact with hot chips on top of the layer is basically composed of three sections: an evaporator site, vapor channels, and an intermediate chamber connected to the condenser on the reservoir layer, as seen in Figure 2.3(a). The dimension of the evaporator site can be scaled up or down in response to the size of the chip. The vapor channels play an important role in transporting vapors from the evaporator site to the intermediate chamber with minimum pressure loss. A number of channel, length, and cross-section areas of the channel depend on the desirable heat flux that can be handled by the TGP device. One of the most important roles of this vapor channel is that channels must be able to transport unexpected liquid droplets to the reservoir without external forces to prevent dryout. For example, when the operation of a chip mounted on the evaporator site is turned off, some portion of vapors that were flowing along the vapor channels turn into liquid in the middle of the channel due to the suddenly decreased temperature near the evaporator site. In such a case, the condensed liquids can be stuck in the middle of the vapor channel and thus affect the next cooling cycle by making a dryout in the reservoir. Consequently, a novel design for vapor channels was necessary to safely and rapidly transport condensed liquids in the channels to the liquid chamber. For this design, three different designs were first considered to use capillary pressure, as seen in Fig. 2.3. As the size of the channel becomes microscale, liquids can propel themselves using capillary

**Figure 2.3** Schematic illustration of the design development process for evaporator channels: (a) straight vapor channels for simple design, (b) tapered vapor channels with specific tapered angle to enhance the capillary pressure, and (c) tapered vapor channels with crown-shaped triple-spike microstructures at the end of channels to distribute the liquid meniscus inducing overflowing of liquid.

force, forming a meniscus along the wall with a contact angle. However, because the capillary force cannot transport fluid without a sufficient force gradient, even in the microscale channels, very few liquids may reach the end of the channels, as seen in Fig. 2.3(a). To enhance capillary force in the channel, a tapered channel with a small angle can be used to propel the liquids farther [36]. Because the tapered shape makes a difference in curvature of the liquid surface (i.e., a narrower region has smaller curvature of the liquid), a liquid droplet flows in the direction of lower pressure (i.e., narrower region) due to the differences in the axial pressure resulting from different curvatures. Fig. 2.3(b) shows the tapered vapor channel with a tapered angle of 0.286°. Due to the gradually narrowed width of the channel, liquid is expected to flow faster and farther than in a straight channel and also expected to reach the end of the channel due to enhanced capillary pressure. Unfortunately, however, it is also obvious that the liquid meniscus in this design cannot be advanced beyond the end of the channel without an external driving pressure pushing the liquid into the intermediate chamber [37-40]. This means that the liquid meniscus is pinned at the end of the channel and thus unable to flow farther. Therefore, to break up the pinned meniscus at the end of the channel, a crown-shaped triple-spike microstructure was finally introduced, as seen in Fig. 2.3(c). The overall microstructure has three spikes where the main liquid meniscus is separated by a middle spike and then continues to flow between the tapered walls of the middle and side spikes. After liquids overflow into the intermediate chamber, these liquids fall down to the condenser part of the reservoir layer via a hole in the wick layer and then must be transported again through the liquid channels to the reservoir chamber (see Fig. 2.2). The design of liquid channels is almost equal to that of vapor channels, except for liquid flow direction. The detailed strategy will be explained in subsection 2.1.3.

#### 2.1.2 Coherent Wick: Continuous Fluid Transport through Micropores

The capillary force also limits the feeding of coolant from the liquid reservoir to the top surface of the evaporator layer. Although the condensed liquids can return to the reservoir with the assistance of a combination of tapered channels and triple-spike microstructures, liquid coolant must be pumped to the evaporator surface again for reliable operation without dryout. Therefore, in a three-dimensional TGP device, continuous pumping of coolant from reservoir to evaporator site is also significantly important to maintain the device's operation. One of the key components for achieving this continuous liquid pumping is the coherent wick, which consists of vertically aligned cylindrical microchannels on the second layer (i.e., coherent wick layer) between the evaporator and reservoir layer, as seen in Fig. 2.2. This crucial component needs to provide reliable and continuous pumping capability against gravity (even several times that of gravity for aviation applications). Figure 2.4 depicts the design of the coherent wick layer for sufficient coolant pumping. The area of the wick also depends on the area of evaporator site, as mentioned in the previous subsection. If a typical wick structure is used in the TGP, as seen in Fig. 2.4(a), the liquid would be sucked into the micropores and then surge up through the vertically aligned cylindrical microchannels against gravity because of primary capillary action. However, the surged liquid would not be able to advance out of the micropores forming a meniscus again at the edge of the pores, which would cause a severe dryout problem in the entire TGP device. Therefore, a novel design and innovation for the wick layer is necessary to allow the pinned liquid meniscus to overflow out of the microchannels so that coolant is able to remove the heat flux by touching the evaporator surface.

**Figure 2.4** Schematic illustration of the design for coherent wick layer: (a) pinned liquid meniscus at the end of vertically aligned microchannels and (b) overflowing liquid by the enhanced and extended capillary force using nanowires grown over the top surface of the wick.

Figure 2.4(b) shows the proposed nanowire-integrated microporous silicon membrane to overcome the dryout problem by driving the liquid out of the channels and spreading it on top of the wick surface with the assistance of extended capillary action [41]. The innovation in this design is the use of nanomaterials (i.e., nanowires) to extend and enhance the capillary force, especially at the end of the pores where the liquid is pinned and not able to overflow out of the pores. The nanowires synthesized on top of the wick surface would help break up the pinned meniscus, forming tremendous nanochannels with a nano-gap and thus pulling it up between the nanowires, as seen in Fig. 2.4(b). In this study, ZnO nanowires were carefully selected and used due to their low thermal conductivity related to a role as a thermal barrier and a simple synthesis method as opposed to other types of nanowires. The role and impact of ZnO nanowires on the thermal properties of the whole TGP system will be discussed in section 2.2. Because the surface property of ZnO to water is hydrophobicity, surface treatments with ultraviolet irradiation [42-44] or silicon dioxide (SiO<sub>2</sub>) deposition [45,46] were additionally needed to change the surface wettability from hydrophobicity to hydrophilicity. The detailed fabrication process for nanowire-integrated microporous silicon membranes is described in Chapter 4.

#### 2.1.3 Reservoir: Rapid Refilling of Coolant

The reservoir layer in the TGP device includes three main parts: a liquid chamber, liquid microchannels, and an intermediate chamber connected to a heat sink. As the vapor channels in the evaporator layer, the liquid microchannel in the reservoir layer also plays a pivotal role in

**Figure 2.5** Schematic illustration of the design for reservoir layer with a combination of tapered microchannels and triple-spike microstructures at the end of each channel to rapidly collect the condensed liquids into the reservoir.

transporting the condensed coolant from the intermediate chamber to the liquid chamber. Therefore, the dryout limitation can be prevented by a rapid refilling of coolant into the reservoir. To collect the condensed liquids into the reservoir, the same innovative design used for the evaporator layer was adopted to the reservoir layer. Figure 2.5 illustrates the scheme of the reservoir layer, which includes tapered channels to transport the coolant from the intermediate chamber to the entrance of reservoir and triple-spike microstructures to drive the liquid out of the microchannels, spreading liquids across the reservoir by distributing meniscus with the assistance of triple-spike microstructures. To complete the operating cycle, the flow direction on the reservoir layer is reversed to that of the evaporator layer. The reservoir layer would be etched deeper than the other layers are to contain more coolant in the chamber. Because of the gradually narrowed width of the tapered channel and tailored microstructures at the end of the channels, coolant would move rapidly, refill the chamber, and finally touch the bottom of the coherent wick structure for the next cooling cycle. In the present study, a cooling test has been performed with three different kinds of polar fluids: deionized (DI) water, methanol, and isopropyl alcohol (IPA). As mentioned previously, the surface wettability is an important factor to transport the liquids through the microchannels. Even though methanol and IPA, which have relatively low surface energy, are completely wetted on the silicon surface of the channels, DI water is preferred as a coolant for TGP in this study because of water's larger latent heat of vaporization (2257 kJ/kg at 1 atm) [47]. In addition, the volatility of alcohol-type coolants may accelerate coolant loss to the atmosphere when the sealing between the main three layers has a leakage problem. Because using a partial wetting fluid (i.e., water) may reduce the propulsion of liquids due to the contact angle hysteresis, a few droplets of a wetting agent should be added to the coolant if the silicon surface was not handled with surface treatments to enhance the wettability.

### 2.2 Operating Principles for Heat Removal

The principal operating principle of the TGP to remove heat flux is to use the latent heat of vaporization of the coolant, similar to conventional heat pipes. One of main advantages of TGP is that the device can be directly integrated with ICs because the TGP is essentially fabricated from the silicon substrate. For example, the MEMS-based sensors and actuators can be fabricated directly onto the evaporator surface of the TGP, resulting in reduced fabrication cost and enhanced cooling efficiency due to the direct contacting interface. Figure 2.6 illustrates the design of the final device integrated with the chip directly contacting the evaporator surface. To integrate many other semiconductor chips with cooling devices, the material of the system must be thermally and electrically matched with semiconductor chips. Hence, the developed cooling device fabricated with all-silicon substrate is superior to the conventional cooling devices. Fig. 2.6(a) shows a device off-mode when the chip mounted on the evaporator stops operating or the chip temperature does not reach the critical temperature to operate the TGP. At this state, the coolant is collected in the reservoir and wets the evaporator surface by enhanced capillary actions from nanowires underneath the evaporator. Once the chip starts operation and increases the evaporator temperature, liquid in contact with the evaporator surface turns into a vapor by absorbing heat incoming from the hot chip, as seen in Fig. 2.6(b). After the vapor travels along the vapor microchannels, the vapor changes its phase from vapor to liquid again by transferring the heat to the heat sink connected to the end of the reservoir layer. Then, the condensed liquid moves back to the chamber through the liquid microchannels on the reservoir layer. This process continues during the operating cycles until the chip temperature has cooled down to the desired temperature. Thus, the chip can be operated safely without thermal damages such as thermal shock, vibration, or degradation.

**Figure 2.6** Scheme of cross-sectional view of the thermal ground plane with hot chip integrated on the evaporator layer for cooling purposes and internal fluid status at (a) device off-mode and (b) device on-mode.

#### 2.2.1 Continuous Feeding of Coolant

The principal operating mechanism of the TGP is the phase-change of the coolant, which absorbs the tremendous heat flux from hot chips. To provide continuous cycles during the operation, vapors and liquids must be circulated smoothly along the microchannels. Therefore, the capillary forces on each layer play an important role in keeping operations reliable and without dryout limitations. As described in the previous section, each layer forming the entire TGP has an innovative design that overcomes the dryout limitation by using enhanced and extended capillary pressure. The tailored microstructures and nanomaterials were introduced to the evaporator-reservoir layers and the coherent wick layer, respectively. The design of the coherent wick layer was based on the device on-mode, whereas the design of the evaporator and reservoir layer was developed based on the device off-mode. The mass flow rate across the wick structure depends on a variety of parameters of the wick structure. To calculate a mass flow rate through the wick theoretically and to demonstrate the enhanced capillary action, a model based on hydrodynamic steady-state can be used in the present study. Assuming the flow surging up to pore ends by the primary capillary pressure is fully developed laminar steady-state with constant properties, the pressure drop across the interface (meniscus) can be given by the Young-Laplace equation as follows [48]:

$$\Delta P_{capillary} = P_{sat,v} - P_{sat,l} = \frac{2\sigma_l}{r} \cos \theta \tag{2.1}$$

where  $P_{sat,v}$  and  $P_{sat,l}$  are the saturated vapor and liquid pressure, respectively.  $\sigma_l$  is the surface tension of the liquid (i.e., free surface energy per unit area at the liquid-vapor interface), r is the radius of the pore, and  $\theta$  is the contact angle at the liquid-vapor interface. Because the vertically aligned cylindrical microchannels in the wick are expected to be filled with liquid to maintain the stable interface, the pressure difference across the membrane is accounted for [15]:

$$P_2 - P_1 = \frac{2\sigma_l}{r} \cos \theta - \left(\frac{8\dot{q}}{\rho_l \varepsilon h_{fg}} \mu_l t_w\right) \left(\frac{1}{r^2}\right)$$

(2.2)

where  $P_1$  and  $P_2$  are the pressure of the bottom surface and upper surface of the wick, respectively;  $t_w$  is the thickness of wick membrane;  $\dot{q}$  is the heat transfer rate per cross-sectional area of the wick;  $\rho_l$  is the density of fluid;  $\varepsilon$  is the porosity of the wick structure;  $h_{fg}$  is the latent heat of vaporization of the coolant; and  $\mu_l$  is the dynamic viscosity of fluid.  $\dot{q}$  is also related to latent heat and mass flow rate:  $\dot{q} = \dot{m}h_{fg}/A$ , where  $\dot{m}$  is the mass flow rate of fluid through the wick. Physically, the first and second terms on the right side of Equation (2.2) represent the capillary pressure in the microscale channel and Hagen-Poiseuille pressure loss due to friction along the wall of the channel, respectively [48]. From Eq. (2.2), the volumetric flow rate across the coherent wick structure can be estimated theoretically. The contact angle can be experimentally determined by dropping the coolant onto the wick surface. Figure 2.7 shows the pressure drop across the wick layer versus the pore radius for different porosity (Fig. 2.7(a)) and thickness of wick membrane (Fig. 2.7(b)). From these preliminary results, pore radius of the

**Figure 2.7** Pressure drop across the wick in response to the pore radius for (a) different porosity with constant heat flux of  $40 \text{ W/cm}^2$  and wick membrane thickness of  $200 \mu m$  and (b) different wick membrane thickness with constant heat flux of  $40 \text{ W/cm}^2$  and porosity of 0.2.

coherent wick structure can be determined for fabrication once the desirable pressure drop across the wick is calculated from the two-phase analysis. It is noticeable that the effect of porosity and wick thickness becomes weaker at the region where the pore radius is larger than 6–7 µm. This means that the maximum pressure drop across the wick membrane significantly depends on pore radius rather than on the other parameters. The detailed fabrication strategy to adjust both porosity and pore size will be discussed in Chapter 4.

#### 2.2.2 Thermal Barrier of Coherent Wick

When the chip mounted on the evaporator layer starts operating, waste heat will penetrate across the TGP device, initiating cooling of the chip. If the heat passes across the all layers of the TGP, the coolant in the reservoir will start boiling, resulting in a dryout limitation, as seen in Figure 2.8(a). Therefore, there must be a thermal barrier between the evaporator and reservoir layer to minimize the heat transfer rate coming to the reservoir when the device starts cooling. In other words, the coherent wick layer must have a low thermal conductivity (i.e., high thermal resistance) to initiate the first boiling near the evaporator surface, as seen in Fig. 2.8(b). Because the active height from the bottom of evaporator surface to the reservoir surface is less than 1 mm and coolant is stationary at the initial state, the heat conduction from the evaporator across the reservoir with thermal conductivities of the coolant, nanowires, and porous silicon wick becomes a main mechanism in this case. Therefore, the estimation of the nucleation location by the thermal network analysis with thermal properties is necessary to analyze the overall thermalfluidic system. Assuming the one-dimensional heat conduction and steady-state, thermal resistances of each component have a combination of parallel and serial connection from the chip to the bottom of the reservoir. To estimate the thermal conductivity of ZnO nanowire and the porous silicon wick, microscale heat conduction theory will be discussed in Chapter 3.

**Figure 2.8** Schematic illustration of the role of the coherent wick layer as a thermal barrier to initiate boiling on the evaporator site: (a) dryout limitation when the thermal resistance of the wick is low and (b) desirable operation of the device when the thermal resistance of the wick is high enough.

#### 2.2.3 Drop Propulsion in Microchannel

As described in section 2.1, the microchannels were designed with decreasing gap thickness to transport the coolant by itself to the liquid chamber. In general, the contact angle ( $\theta$ ) is the equilibrium angle between the liquid-vapor interface and the wetted solid surface when the fluid droplet is placed on a solid surface. For wetting fluids such as silicone oil or methanol, the contact angle goes to zero, whereas partial wetting fluids such as water have a finite angle with advancing and receding contact angles. An important hysteresis of so-called contact angle hysteresis is the difference between advancing and receding contact angles and acts to resist the sliding of partial wetting fluids on the surface [49-51]. Due to this hysteresis, although the vapor and liquid channels are tapered with decreasing gaps, the droplet of a partial wetting fluid may be pinned between two walls, causing the liquid to be stuck in the middle of the channel. Consequently, either surface treatments for solids or wetting agents for liquids play an important role in changing the wettability between the solid surface and liquid because a wetting fluid confined in a tapered channel can be self-transported toward the narrower end with the assistance of axial force arising from the different curvature pressures [52].

# Chapter 3

# Heat Transfer Analysis

#### 3.1 Microscale Heat Conduction

#### 3.1.1 Kinetic Theory of Thermal Transport

By definition, heat transfer is the energy flow involving the motion of heat carriers across a boundary under temperature difference. The well-known macroscopic Fourier's law for heat transfer is derived from averaging microscopic motions over a long period in a sufficiently large boundary. Fourier's law is useful for analyzing the average behavior of mass, energy, and momentum in macrosystems. However, such classical macroscopic averaging equations may no longer represent the motion of heat carriers in microscale or nanoscale domains because the conditions for average behavior are no longer valid [53]. Figure 3.1(a) depicts a wavepacket, which represents an energy carrier propagating through a system, traveling from left to right in the medium with the characteristic length L[54]. The wavepacket can be treated as a particle unless the characteristic length is comparable to the wavelength  $\lambda$ . However, the wavepacket collides with the boundary of the medium, impurities, or another wavepacket in the system with L, which is comparable or smaller than the mean free path  $\Lambda$ , as seen in Fig. 3.1(a) (e.g., thickness of a thin film or diameter of a nanowire). In this case, these numerous collisions impede the energy flow from left to right, resulting in "classical size effect" [53,54]. Therefore, heat conduction at the microscale is quite different from heat conduction at the macroscale, where the characteristic length is much larger than the mean free path.

The major difference between microscale and macroscale is that the effective thermal conductivity of microscale material is not equal to that of bulk material, even if they are the same material. In most cases, the values of thermal conductivities that can easily be found in textbooks or handbooks are valid for only bulk materials. Consequently, a microscopic approach is necessary to apply the effective thermal conductivity for microstructures, such as a thin film or nanowire. As a first step, the macroscopic Fourier's law must be modified based on kinetic theory to be useful at microscale domains. Considering a one-dimensional domain where the net heat flux flows from a hot surface to a cold surface as shown in Fig. 3.1(b), the net heat flux transported by heat carriers in x-direction is given by [53]:

$$\dot{q}_x = \frac{1}{2} \eta E v_x \bigg|_{x_0 - \Lambda} - \frac{1}{2} \eta E v_x \bigg|_{x_0 + \Lambda}$$

(3.1)

where  $\eta$  is the number of heat carriers per unit volume, E is the internal energy in J, and  $v_x$

**Figure 3.1** Schematic of (a) classical size effect when the characteristic length (L) is smaller than the mean free path ( $\Lambda$ ) and larger than the wavelength ( $\lambda$ ) and (b) control volume for a derivation of modified Fourier's law rested on kinetic theory.

is the x-component of the heat carriers' random velocity. By using a Taylor expansion and assuming that  $v_x$  is in an isotropic system and does not have preferred direction (i.e.,  $v_x^2 = (1/3)v^2$ ), Equation (3.1) can be expressed as follows:

$$\dot{q}_x = -\frac{v}{3}\Lambda \frac{dU}{dT} \frac{dT}{dx} \tag{3.2}$$

where v is the average velocity of the heat carriers, U is the internal energy density per unit volume in  $J/m^3$ , and dU/dT is the volumetric heat capacity C in  $J/m^3$ ·K. Comparing Equation (3.2) with the classical Fourier's law ( $\dot{q}_x = -k(dT/dx)$ ) leads to the thermal conductivity equation as follows:

$$k = \frac{1}{3}Cv\Lambda. (3.3)$$

By treating C, v, and  $\Lambda$  in the above equation as lumped and frequency-independent quantities, most physical cases can be analyzed by calculating the thermal conductivity. However, because the particular nanostructures and energy carriers depend on frequency ( $\omega$ ) in real nature, kinetic theory can be expressed as an integral form to account for the frequency dependence [54]:

$$k = \frac{1}{3} \int C(\omega, T) v(\omega) \Lambda_{eff}(\omega, T) d\omega$$

$$= \frac{1}{3} \int \hbar \omega D(\omega) \frac{\partial f(\omega, T)}{\partial T} v(\omega) \Lambda_{eff}(\omega, T) d\omega$$

(3.4)

where  $\hbar$  is the reduced Planck constant,  $D(\omega)$  is the density of state  $(D(\omega) = D(\kappa)d\kappa/d\omega)$ ,  $f(\omega,T)$  is the Bose-Einstein distribution, and  $\Lambda_{eff}(\omega,T)$  is the effective mean free path expressed by  $\Lambda^{-1}_{eff}(\omega,T) = \Lambda^{-1}_{umkl}(\omega,T) + \Lambda^{-1}_{imp}(\omega) + \Lambda^{-1}_{bdy}$  based on the Matthiessen's rule. Each mean free path, due to phonon-phonon Umklapp scattering (denoted  $\Lambda_{umkl}$ ), impurity scattering (denoted  $\Lambda_{imp}$ ), and boundary scattering (denoted  $\Lambda_{bdy}$ ), is also expressed with frequency  $(\omega)$ , temperature (T), and diameter of the sample (D) [55,56]:

$$\Lambda^{-1}_{umkl}(\omega, T) = \frac{B_1 \omega^2 T \exp(-B_2/T)}{v_g} \qquad \Lambda^{-1}_{imp}(\omega) = \frac{A_1 \omega^4}{v_g} \qquad \Lambda^{-1}_{bdy} = D^{-1}$$

(3.5)

where  $v_g$  is the group velocity and given by  $v_g = d\omega/d\kappa$ . To account for the frequency dependence, the Born-von Karman dispersion relation ( $\omega = \omega_0 \sin(\pi\kappa/2\kappa_D)$ ) can be used, where  $\omega_0 = 2v_s\kappa_D/\pi$  and  $\kappa_D = (6\pi^2\eta_{PUC})^{1/3}$  for the Debye cutoff wave vector, where  $v_s$  is the average sound velocity, and  $\eta_{PUC}$  is the number density of a primitive unit cell in m<sup>-3</sup>. The coefficients  $A_1$ ,  $B_1$ , and  $B_2$  in Equation (3.5) depend on the material. By integrating Equation (3.4) with all parameters described above, more accurate thermal conductivity can be calculated for microscale and nanoscale samples.

### 3.1.2 Temperature Dependence of Thermal Conductivity

To validate the kinetic modeling, the silicon, which is well and widely investigated for both experimental value and theory, was tested with previously reported experimental data. Table 3.1 shows the values of physical parameters and fitting parameters determined by matching the modeling to experimental data for bulk silicon. Using these parameters, the thermal conductivities of silicon for different sample sizes were calculated in response to the temperature and compared with the experimentally measured data [57,58], as seen in Figure 3.2. As a result, the estimated thermal conductivity of silicon was able to reproduce the experimental results for bulk and nanowires in low temperature regions. In the same manner, fitting parameters for ZnO samples in Table 3.1 were carefully selected based on the effective sound velocity of ZnO [59] to match the calculated results to experimental data for a bulk sample. Figure 3.3(a) shows the calculated thermal conductivities of ZnO for bulk and nanowires from a temperature of 10 to 1000 K. As seen in the figure, the modeling shows good agreement with experimental data [60,61] for the bulk sample, and the significant reduction in thermal conductivity appears as the

**Table 3.1** Parameter values determined by a combination of theory and fitting thermal conductivities with respect to temperature for bulk silicon and zinc oxide (ZnO) samples.

|         | $\eta_{PUC}$ (m <sup>-3</sup> ) | <i>v<sub>s</sub></i> (m/s) | $A_1$ (s <sup>3</sup> ) | <i>B</i> <sub>1</sub> (s/K) | B <sub>2</sub> (K) |

|---------|---------------------------------|----------------------------|-------------------------|-----------------------------|--------------------|

| Silicon | 2.5e28                          | 5880 [54]                  | 2.4e-45                 | 1.7e-19                     | 210                |

| ZnO     | 2.1e28                          | 3186 [59]                  | 8.0e-44                 | 2.6e-19                     | 100                |

**Figure 3.2** Calculated thermal conductivities for silicon from kinetic theory and comparison with experimentally measured thermal conductivities for a different diameter of silicon nanowires.