### **UC Berkeley**

#### **UC Berkeley Electronic Theses and Dissertations**

#### **Title**

Design Techniques for Energy-Efficient, Low Latency High Speed Wireline Links

#### **Permalink**

https://escholarship.org/uc/item/62s7r4sn

#### **Author**

Sutardja, Nicholas

#### **Publication Date**

2018

Peer reviewed|Thesis/dissertation

#### Design Techniques for Energy-Efficient, Low Latency High-Speed Wireline Links

By

#### Nicholas Sutardja

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Elad Alon, Chair Professor Borivoje Nikolić Professor Xin Guo

Spring 2019

Design Techniques for Energy-Efficient, Low Latency High-Speed Wireline Links

Copyright 2019

by

Nicholas Sutardja

#### Abstract

Design Techniques for Energy-Efficient, Low Latency High Speed Wireline Links

by

#### Nicholas Sutardja

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Elad Alon, Chair

As data and computing systems get larger with more elements composing a single system, streamlined computation and data communication has put an ever-increasing demand on throughput of high speed SerDes. Industrial standards have responded to this trend by increasing the data-rate of chip I/Os, demanding doubling per-pin data-rate around every four years while the power budget remains the same. This implies that the energy efficiency of these links must improve all while being able to handle the harsher equalization environments seen at higher frequencies. To address the challenge of per-pin bandwidth, this thesis first presents various receive side equalization techniques used in a 60Gb/s non-return-to-zero (NRZ) link. In particular, a double data-rate (DDR) architecture uses current integration in several front-end equalization circuits, including the continuous-time linear equalizer (CTLE), feed-forward equalizer (FFE), and decision-feedback equalizer (DFE), demonstrated in a receiver frontend to achieve 60Gb/s operation with > 0.2 UI-timing margin at 1e-9 BER, while consuming 173mW. The same architecture was utilized within a complete non-return-to-zero transceiver with adaptive equalization achieving 60Gb/s with >0.3 UI opening at 10<sup>-12</sup> Bit Error Rate (BER), while consuming 288 mW and occupying 2.48 mm<sup>2</sup>.

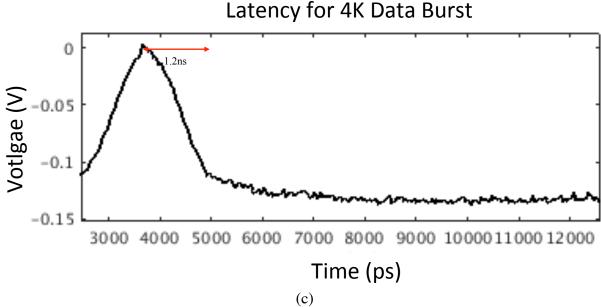

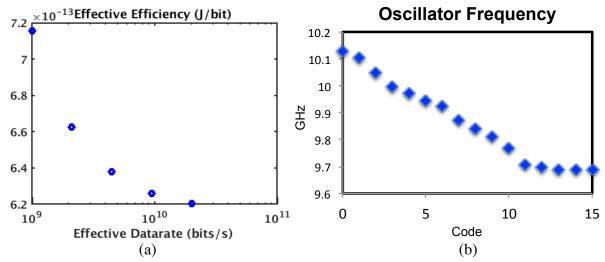

Furthermore, supporting this throughput in distributed system with a ubiquitous communication standard calls for links, which are able to quickly turn on and off and operate efficiently in low utilization modes while supporting capability for maximum throughput. This thesis then goes into an analysis of the requirements motivating our architectural and circuit level decisions for a burst-mode, energy proportional wireline link. To achieve energy proportionality, a 2-tap switched-capacitor transmitter with FFE equalization is presented that allows for a fully dynamic architecture operating at a nominal data-rate of 20Gb/s while maintaining energy-efficiency during both high and low link utilization. Additionally, a rapid-on/off voltage controlled LC oscillator uses resonant clocking to save power by directly driving the data-path capacitive loads all while improving overall latency, and a phase interpolator with a phase

adjustable clock divider allows for the lowest achievable latency design for a 64:1 1-latch serializer implementation. The transmitter was taped out in TSMC's 28nm GP process, and achieves 1.2ns startup time and 0.72-0.62 pJ/bit at 1-20Gb/s while occupying 0.19mm<sup>2</sup>.

Learn how to see.

Realize that everything connects

to everything else.

Leonardo Da Vinci

To My Family

# Contents

| C | onte   | nts                                                             | ii  |

|---|--------|-----------------------------------------------------------------|-----|

| L | ist of | Figures                                                         | iv  |

| L | ist of | Tables                                                          | vii |

| 1 | Intr   | oduction                                                        | 1   |

|   | 1.1    | Background                                                      | 1   |

|   | 1.2    | Wireline communication                                          | 2   |

|   | 1.     | 2.1 Intersymbol interference                                    | 4   |

|   | 1.3    | Equalization                                                    | 4   |

|   | 1.     | 3.1 Continuous time linear equalizer                            | 5   |

|   | 1.     | 3.2 Feed-forward equalizer                                      | 7   |

|   | 1.     | 3.3 Decision feedback equalizer                                 | 8   |

|   | 1.4    | Thesis organization                                             | 10  |

| 2 | Ene    | rgy-efficient receive side design techniques for 60-Gb/s        | 11  |

|   | 2.1    | Current integration vs. resistive summation                     | 11  |

|   | 2.2    | Current integrating CTLE and DMUX                               | 12  |

|   | 2.3    | RX feed-forward equalization                                    | 13  |

|   | 2.     | 3.1 Dynamic latches                                             | 14  |

|   | 2.     | 3.2 FFE coefficient control                                     | 15  |

|   | 2.     | 3.3 Integrating FFE+DFE                                         | 17  |

|   | 2.     | 3.4 DDR receiver frontend                                       | 19  |

|   | 2.4    | 50Gb/s receiver frontend results                                | 20  |

|   | 2.5    | 50Gb/s complete transceiver results                             | 23  |

|   | 2.6 (  | Conclusion                                                      | 26  |

| 3 | Ene    | rgy proportional communication                                  | 27  |

|   | 3.1 l  | Energy proportional efficiency                                  | 29  |

|   | 3.     | 1.1 Comparison between burst-mode and data-rate back-off        | 30  |

|   | 3.     | 1.2 Efficiency vs. effective data-rate and P <sub>standby</sub> | 31  |

|   | 3.     | 1.3 Multilane signaling                                         | 32  |

| 3.2 Transmitter design for energy efficiency                  | 34                          |

|---------------------------------------------------------------|-----------------------------|

| 3.2.1 Comparison between voltage mode and current mode        | e logic transmitters35      |

| 3.2.2 VM and CML TX driver start-up considerations            | 36                          |

| 3.2.3 Switched-capacitor TX driver                            | 38                          |

| 3.3 Switched-capacitor feed-forward equalization              | 42                          |

| 3.3.1 Switched-capacitor feed-forward equalizer               | 42                          |

| 3.3.2 Variable capacitance using capacitive DAC               | 44                          |

| 3.3.3 Tap control with clock gating                           | 45                          |

| 4 A 2-tap switched-capacitor FFE transmitter achieving 1-20 G | Gb/s at 0.72-0.62 pJ/bit 47 |

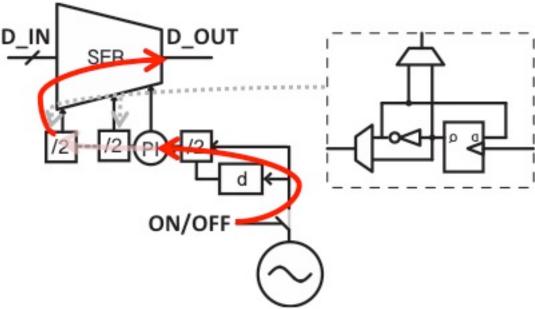

| 4.1 Transmitter architecture and circuit design               | 47                          |

| 4.1.1 Switched-capacitor feed forward architecture            | 48                          |

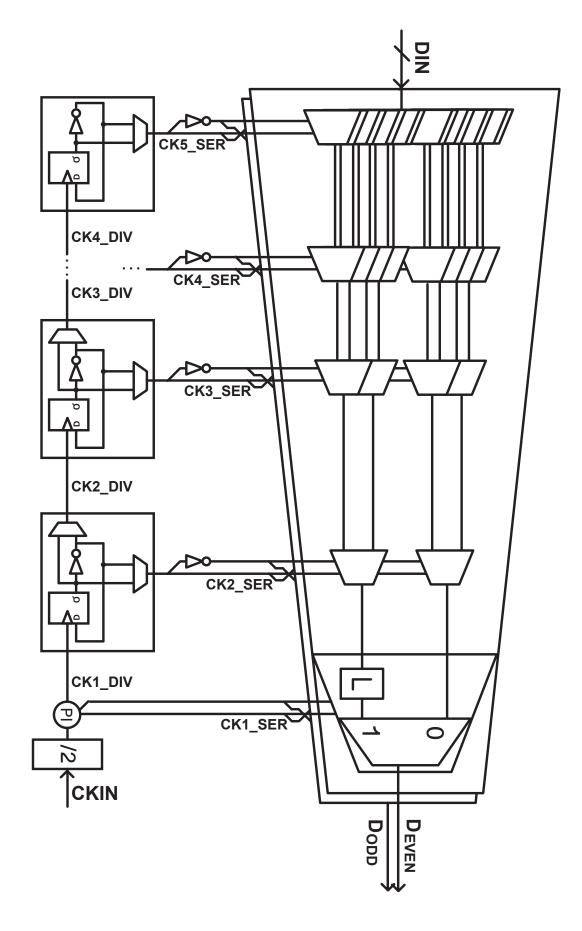

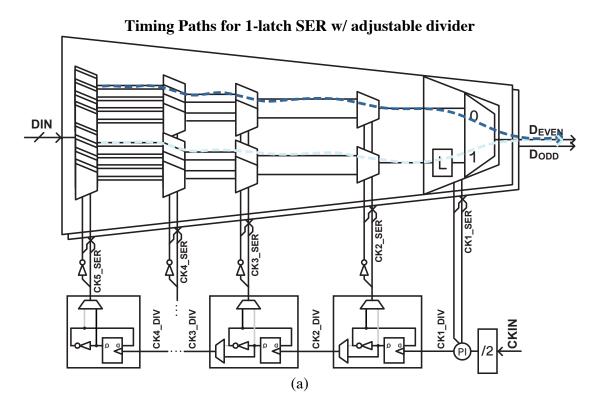

| 4.2 Serializer design challenges                              | 50                          |

| 4.2.1 MUX serializer timing constraints                       | 51                          |

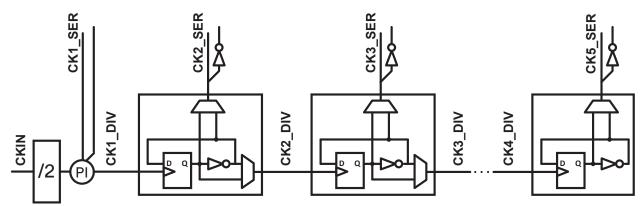

| 4.2.2 Divider with buffering for a 1-latch SER                | 53                          |

| 4.2.3 1-latch serializer w/ phase adjustable divider          | 54                          |

| 4.3 On/off clocking                                           | 59                          |

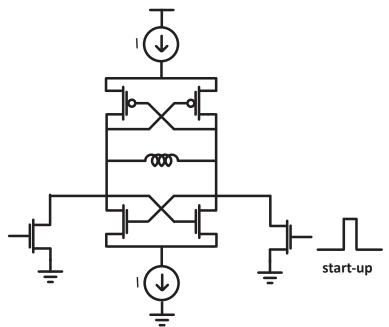

| 4.3.1 Cross-coupled oscillator startup time                   | 60                          |

| 4.3.2 Rapid-on/off LC oscillator                              | 61                          |

| 4.3.3 Resonant clocking                                       | 62                          |

| 4.4 High-speed phase alignment                                | 64                          |

| 4.4.1 Phase interpolator design                               | 65                          |

| 4.4.2 High-speed clock divider phase alignment                | 66                          |

| 4.5 Measurement results                                       | 69                          |

| 4.6 Conclusion                                                | 72                          |

| 5 Conclusion                                                  | 74                          |

| 5.1 Thesis summary                                            | 74                          |

| 5.2 Future directions                                         | 75                          |

| Bibliography                                                  | 76                          |

| Appendix A                                                    | 82                          |

# List of Figures

| Figure. 1. 1. Ubiquitous links in the wide area network                                                                                                                                                                               | 1  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure. 1. 2. I/O per-pin bandwidth                                                                                                                                                                                                   | 2  |

| Figure. 1. 3. I/O Data-rate vs. process node for recent (2015-2018) transceiver designs                                                                                                                                               | 3  |

| Figure. 1. 4. Intersymbol interference                                                                                                                                                                                                | 4  |

| Figure. 1. 5. Wireline link architecture.                                                                                                                                                                                             | 5  |

| Figure. 1. 6. CTLE equalization                                                                                                                                                                                                       | 6  |

| Figure. 1.7. Continuous time linear equalizers (a) Passive CTLE (b) Active CTLE                                                                                                                                                       | 6  |

| Figure. 1. 8. Feed-forward equalizer                                                                                                                                                                                                  | 8  |

| Figure. 1. 9. Decision feedback equalizer                                                                                                                                                                                             | 9  |

|                                                                                                                                                                                                                                       |    |

| Figure. 2. 1. (a) Resistive summation (b) Current integration (c) Voltage vs. time for current integration vs. resistive summation                                                                                                    | 11 |

| Figure. 2. 2. (a) Current integrating CTLE + DMUX (b) CTLE odd and even outputs over tim                                                                                                                                              |    |

| Figure. 2. 3. (a) TX FFE (b) RX FFE.                                                                                                                                                                                                  | 13 |

| Figure. 2. 4. CTLE + DMUX and following FFE latches                                                                                                                                                                                   | 14 |

| Figure. 2. 5. Transconductance implementations for FFE coefficient (fi) control (a) Current-b control (b) Differential pair unit cells (c) Source degeneration (d) Cascode with duty cycle control (e) Cascode with variable DC bias. |    |

| Figure. 2. 6. (a) Cascode DC bias control integrator output voltage (b) Linearity comparison between current-bias control and cascode DC bias control                                                                                 |    |

| Figure. 2. 7. FFE + DFE integrator                                                                                                                                                                                                    | 17 |

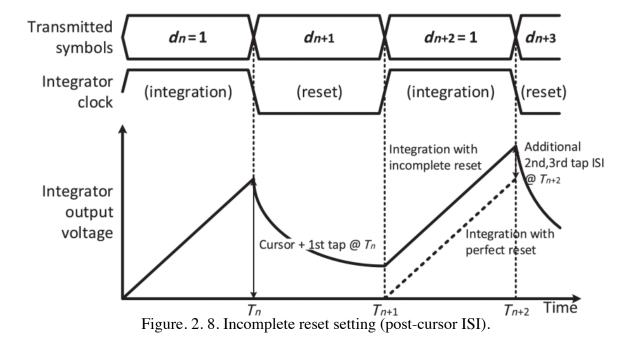

| Figure. 2. 8. Incomplete reset setting (post-cursor ISI).                                                                                                                                                                             | 18 |

| Figure. 2. 9. (a) Simplified DFE circuit diagram (b) Optimal reset accuracy                                                                                                                                                           | 19 |

| Figure. 2. 10. Receiver frontend architecture.                                                                                                                                                                                        | 20 |

| Figure. 2. 11. (a) Die photo (b) Measurement setup and measured waveforms (All clock sourcare synchronized.)                                                                                                                          |    |

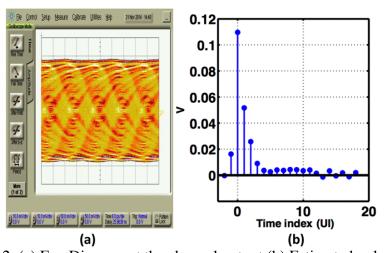

| Figure. 2. 12. (a) Eye Diagram at the channel output (b) Estimated pulse response                                                                                                                                                     | 21 |

| Figure. 2. 13. Bathtub curve after equalization                                                                                                                                                                                       | 22 |

| Figure. 2. 14. Transceiver architecture.                                                                                                                                                                                              | 23 |

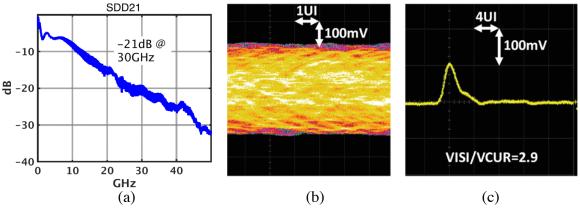

| Figure. 2. 15. Measurement setups for (a) channel frequency response, (b) pulse response, and (c) equalizer and CDR characterization.                                                                                                                                       | 24 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure. 2. 16. (a) Measured channel frequency response (b) TX + channel eye diagram (c) TX - channel pulse response.                                                                                                                                                        |    |

| Figure. 2. 17. (a) Eye diagrams (b) Bathtub curve (c) Die photo.                                                                                                                                                                                                            | 25 |

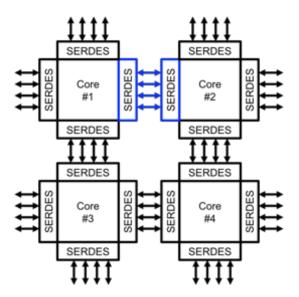

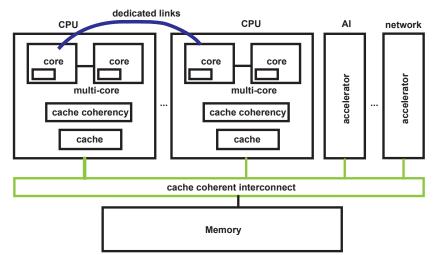

| Figure. 3. 1. Parallel processing.                                                                                                                                                                                                                                          |    |

| Figure. 3. 2. Unified communication.                                                                                                                                                                                                                                        | 28 |

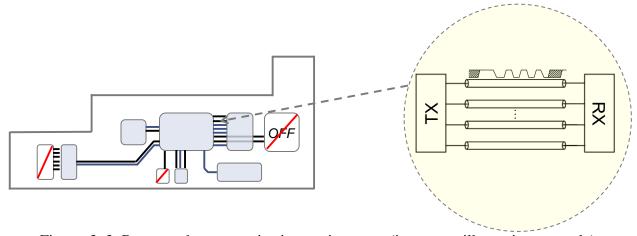

| Figure. 3. 3. Burst-mode communication environment (interposer illustration example)                                                                                                                                                                                        | 28 |

| Figure. 3. 4. Burst-mode data stream.                                                                                                                                                                                                                                       | 29 |

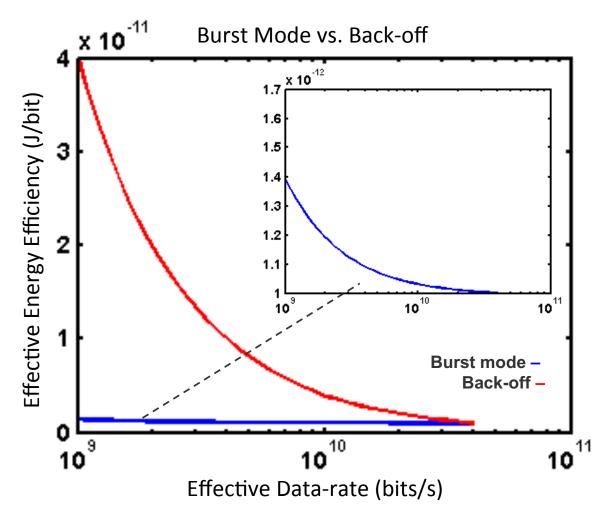

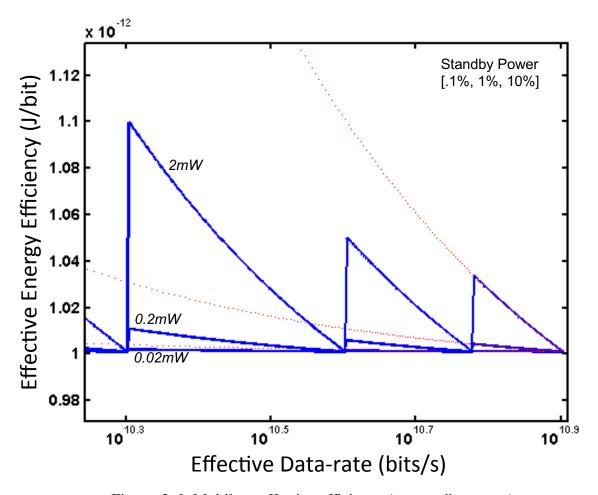

| Figure. 3. 5. Comparison between effective efficiency of burst-mode (blue) Data-rate back-off (red). Assumes a 1pJ/bit 40Gb/s nominal link is burst at 4KByte intervals with standby-power being 100x less than on-power.                                                   |    |

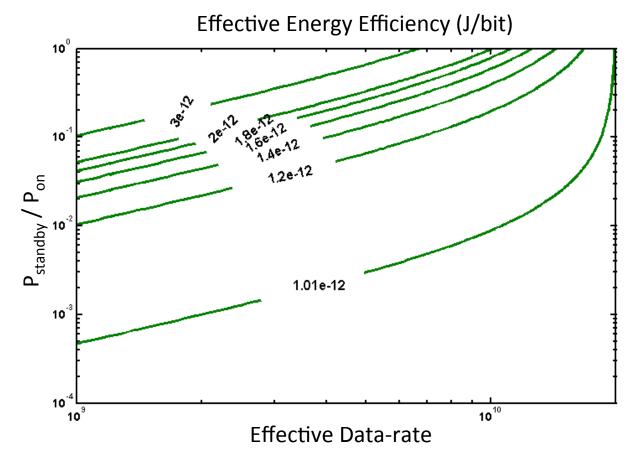

| Figure. 3. 6. Effective energy efficiency contour plot. (assumes tdata /(tstartup + tshutoff) = 1e3, 1pJ/bit nominal efficiency, 20Gb/s nominal data-rate)                                                                                                                  | 32 |

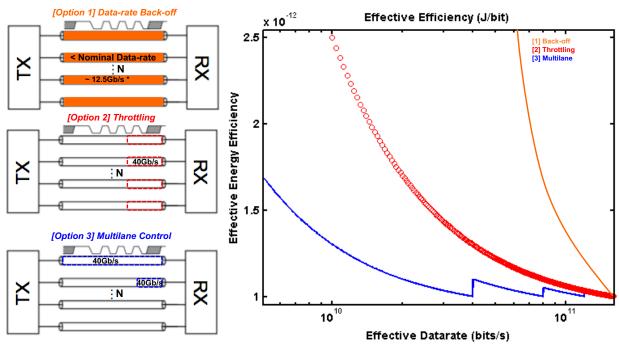

| Figure. 3. 7. Comparison between data-rate back-off, throttling, and multilane control in a multilane signaling system.                                                                                                                                                     | 33 |

| Figure. 3. 8. Multilane effective efficiency (vs. standby power)                                                                                                                                                                                                            | 34 |

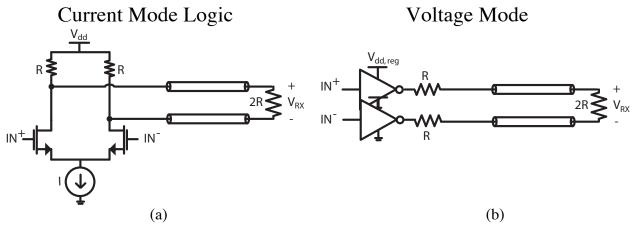

| Figure. 3. 9. Comparison between voltage mode and current mode logic transmitters. (a) CML transmitter with differential termination at RX (b) VM transmitter with differential termination RX. ( $R=Z_0=50\Omega$ , where $Z_0$ is the impedance of the transmission line) | at |

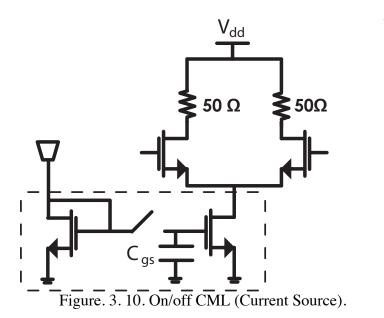

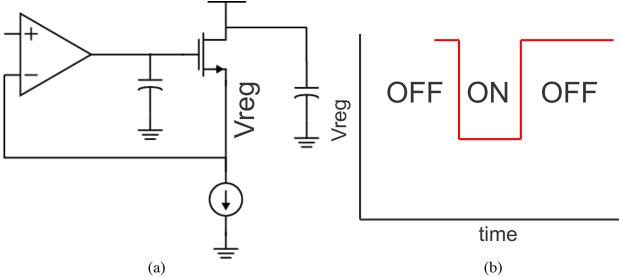

| Figure. 3. 10. On/off CML (Current Source)                                                                                                                                                                                                                                  | 37 |

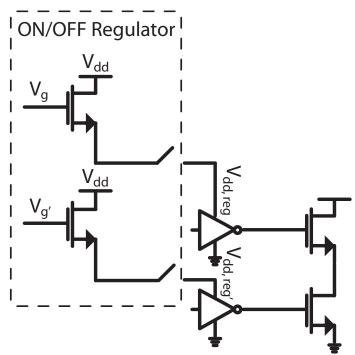

| Figure. 3. 11. On/off regulator desired for voltage mode driver designs                                                                                                                                                                                                     | 37 |

| Figure. 3. 12. (a) NMOS LDO for TX supply regulation. (b) On/off instantaneous voltage drop                                                                                                                                                                                 |    |

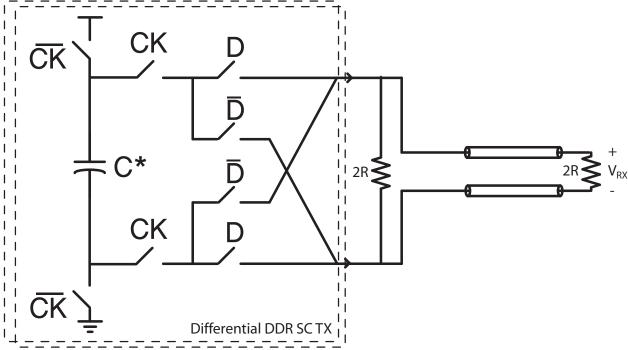

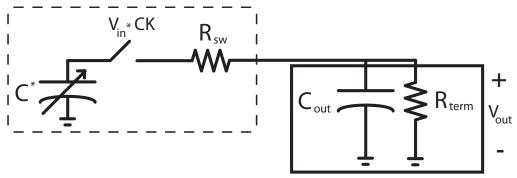

| Figure. 3. 13. Switched-capacitor driver with differential termination at RX                                                                                                                                                                                                | 39 |

| Figure. 3. 14. SC driver circuit model.                                                                                                                                                                                                                                     | 39 |

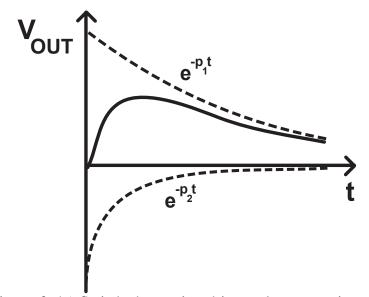

| Figure. 3. 15. Switched-capacitor driver voltage over time                                                                                                                                                                                                                  | 41 |

| Figure. 3. 16. Switched-capacitor circuit model with 3-tap FFE.                                                                                                                                                                                                             | 43 |

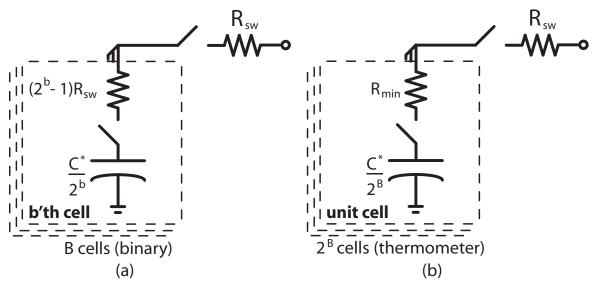

| Figure. 3. 17. (a) B-bit binary capacitor DAC B binary weighted cells (b) B-bit thermometer capacitor DAC with 2B unit cells.                                                                                                                                               | 44 |

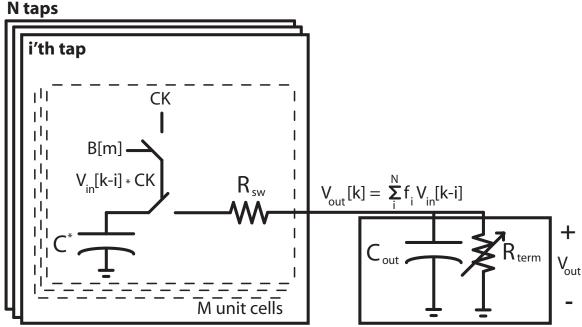

| Figure. 3. 18. N-tap SC FFE circuit model with tap strength control                                                                                                                                                                                                         | 45 |

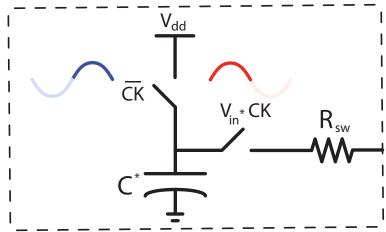

| Figure. 3. 19. Pre-charge and charge of SC driver                                                                                                                                                                                                                           | 46 |

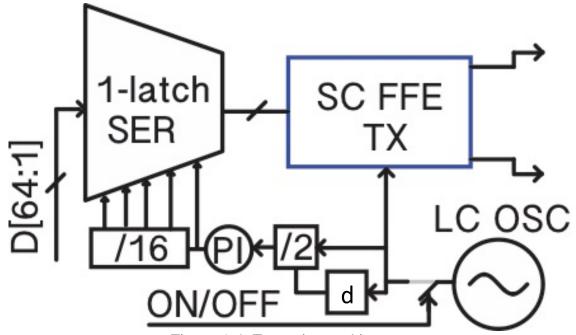

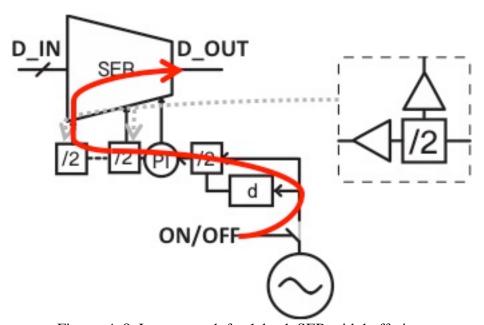

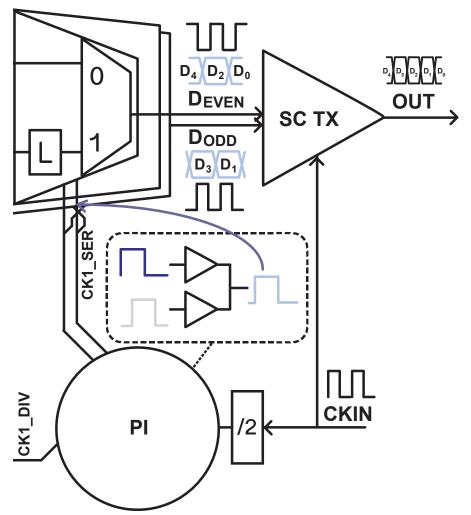

| Figure. 4. 1. Transmitter architecture                                                                                                                                                                                                                                      | 47 |

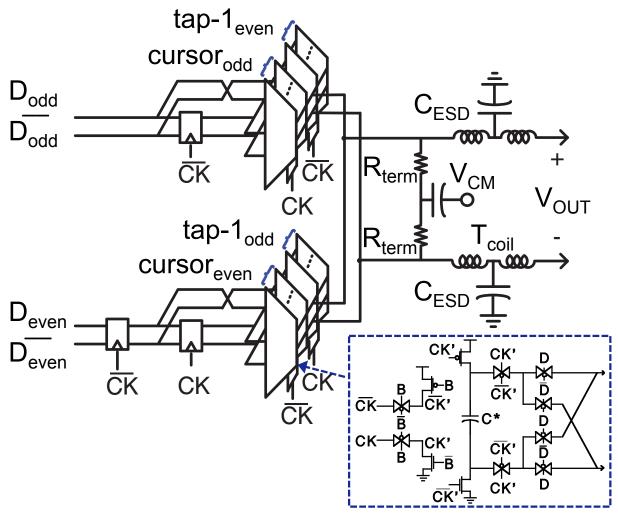

| Figure. 4. 2. 2-tap SC FFE TX.                                                                                                           | 48 |

|------------------------------------------------------------------------------------------------------------------------------------------|----|

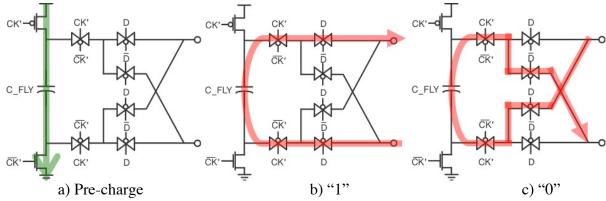

| Figure. 4. 3. Switched-capacitor TX cell operation. (a) pre-charge (b) "1" (c) "0"                                                       | 49 |

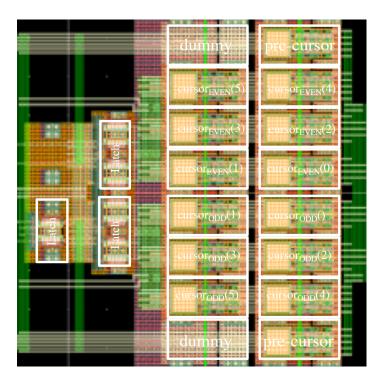

| Figure. 4. 4. 2-tap DDR SC FFE layout.                                                                                                   | 50 |

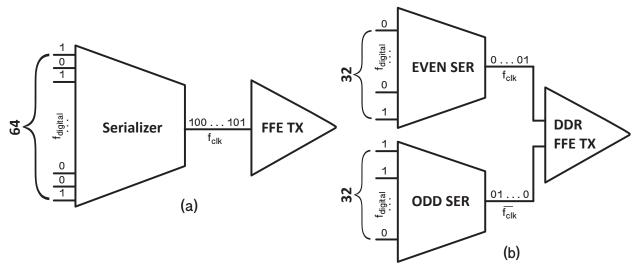

| Figure. 4. 5. (a) Line rate serializer (b) DDR serializer.                                                                               | 50 |

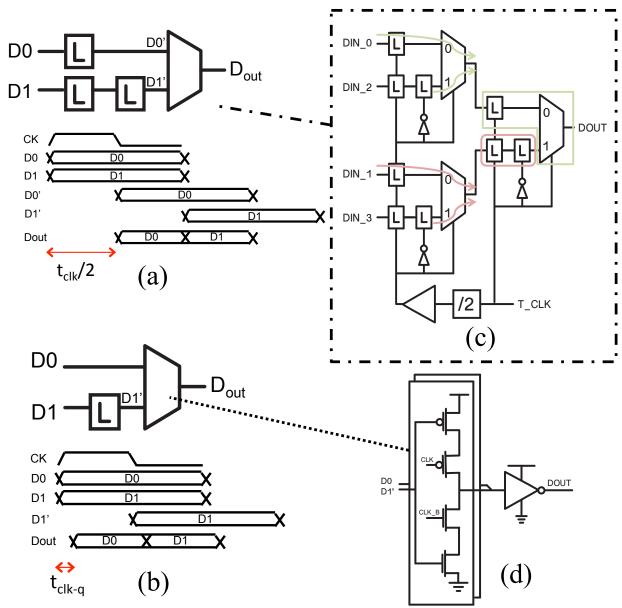

| Figure. 4. 6. (a) 2-latch MUX & timing (b) 1-latch MUX & timing (c) Example 2-latch MUX, two-stage serializer timing paths (d) CMOS MUX. |    |

| Figure. 4. 7. CMOS latch.                                                                                                                | 52 |

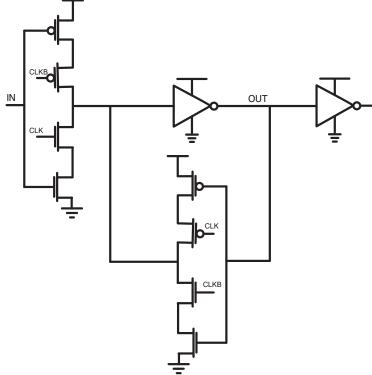

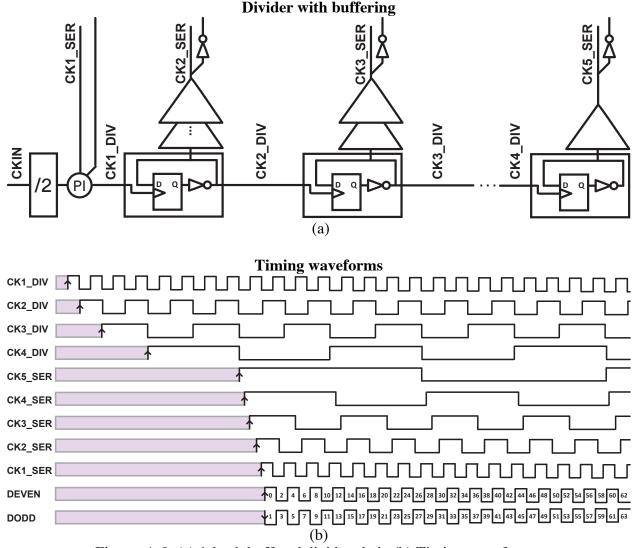

| Figure. 4. 8. (a) 1-latch buffered divider chain (b) Timing waveforms                                                                    | 53 |

| Figure. 4. 9. Latency path for 1-latch SER with buffering.                                                                               | 54 |

| Figure. 4. 10. 1-latch adjustable divider chain.                                                                                         | 55 |

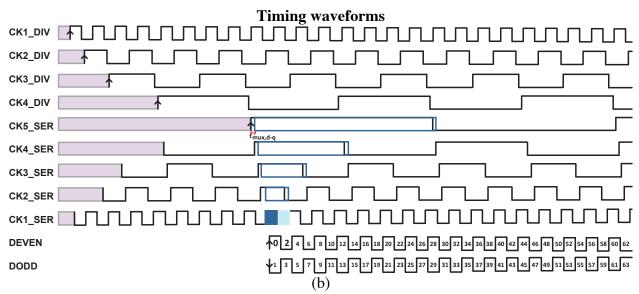

| Figure. 4. 12. (a) Adjustable clock to serializer and divider timing paths (a) timing waveforms.                                         | 58 |

| Figure. 4. 13. Latency path for 1-latch serializer w/ adjustable divider.                                                                | 59 |

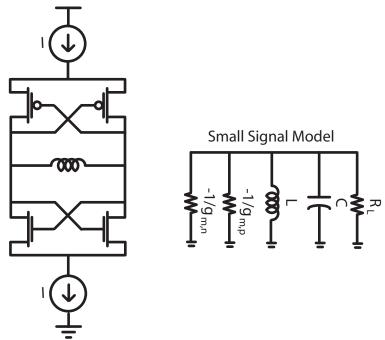

| Figure. 4. 14. Complementary cross-coupled LC oscillator.                                                                                | 59 |

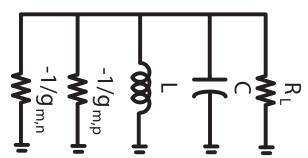

| Figure. 4. 15. Small signal model of a complementary cross-coupled LC oscillator                                                         | 60 |

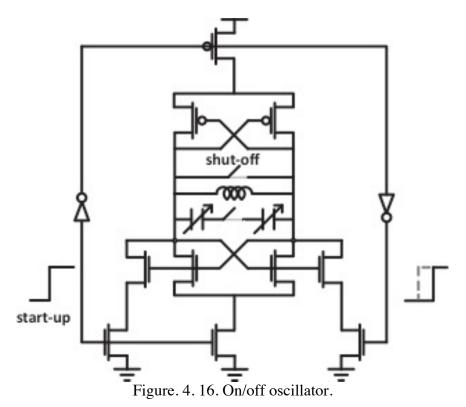

| Figure. 4. 16. On/off oscillator                                                                                                         | 61 |

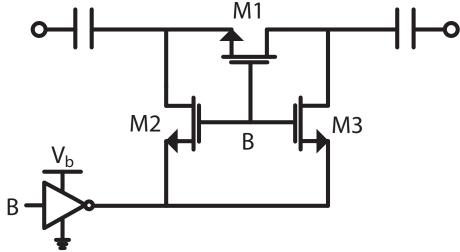

| Figure. 4. 17. Capacitor Array Unit Cell (C <sub>VAR</sub> ).                                                                            | 62 |

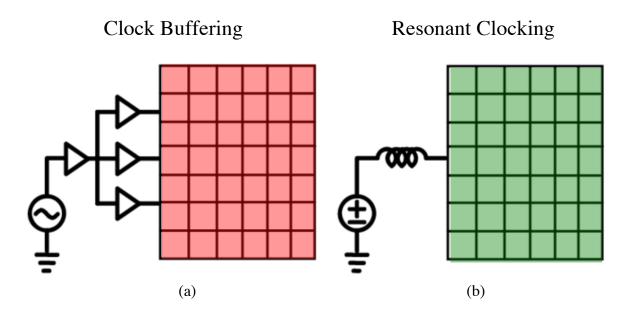

| Figure. 4. 18. (a) Clock buffering (Red) (b) Resonant clocking (Green).                                                                  | 63 |

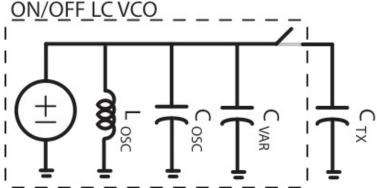

| Figure. 4. 19. On/off LC VCO resonant clocking.                                                                                          | 64 |

| Figure. 4. 20. Divider and data phase alignment.                                                                                         | 65 |

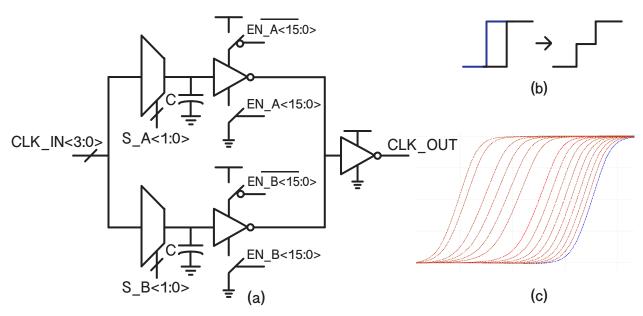

| Figure. 4. 21. (a) 6-bit PI (b) Inverter PI ideal output (c) PI output waveform.                                                         | 66 |

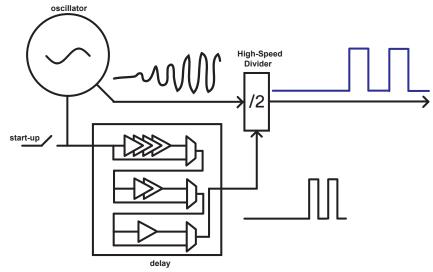

| Figure. 4. 22. High-speed clock and divider phase alignment.                                                                             | 67 |

| Figure. 4. 23. Oscillator waveform timing.                                                                                               | 67 |

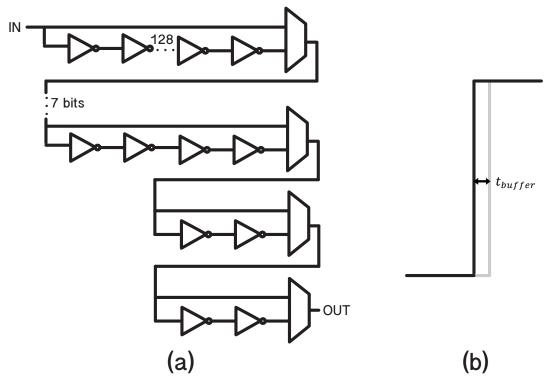

| Figure. 4. 24. (a) 7-bit tunable delay circuit (b) Delay resolution (tbuffer)                                                            | 68 |

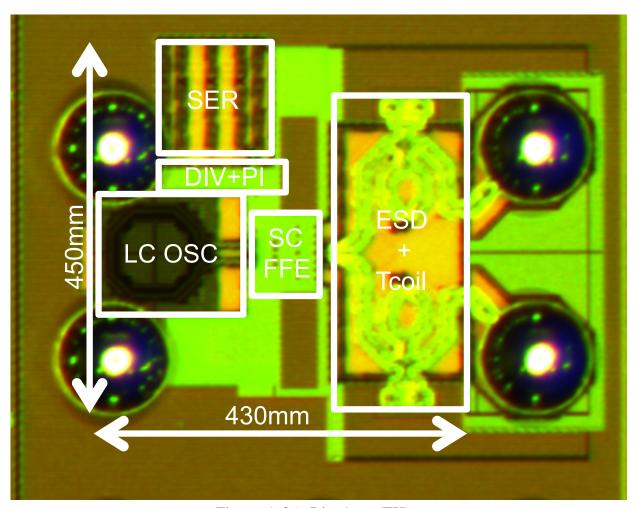

| Figure. 4. 25. Die photo (TX).                                                                                                           | 69 |

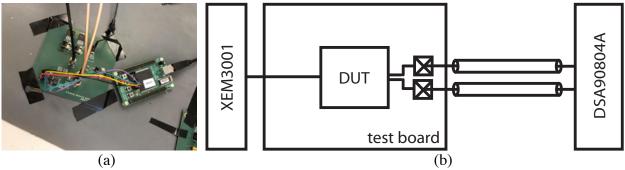

| Figure. 4. 26. (a) Testing setup image (b) Testing setup block diagram.                                                                  | 70 |

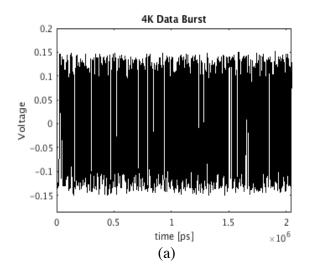

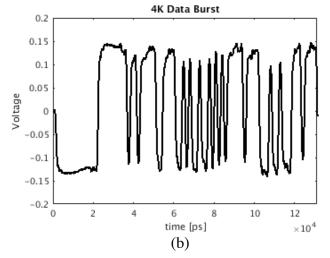

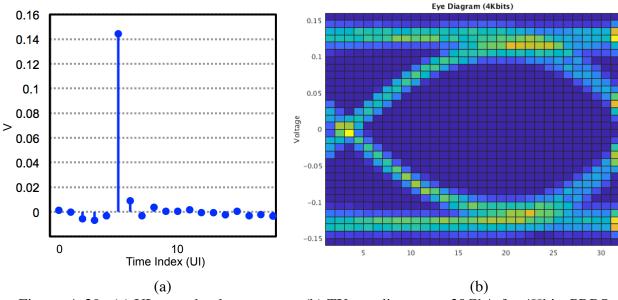

| Figure. 4. 27. (a) 4Kbit Data. (b) 4Kbit Data (zoomed in). (c) Latency (zoomed in further)                                               | 71 |

| Figure. 4. 28. (a) UI spaced pulse response. (b) TX eye diagram at 20Gb/s for 4Kbits PRBS pattern.                                       | 71 |

| Figure. 4. 29. (a) Effective efficiency from 1Gb/s to 20Gb/s. (b) OSC frequency vs. code                                                 | 72 |

| Figure. A. 1. Complementary cross-coupled oscillator and its small signal model                                                          | 82 |

# List of Tables

| Table 2. 1: Comparison of high-speed receiver equalizers                  |    |  |

|---------------------------------------------------------------------------|----|--|

| Table 2. 2: Comparison of high-speed transceivers                         | 25 |  |

|                                                                           |    |  |

| Table 4. 1: Comparison of energy proportional and SC driver architectures | 72 |  |

#### Acknowledgements

First, I would like to wholeheartedly thank my professors: Professor Elad Alon and Professor Borivoje Nikolić for their continued support and belief in me over all these years.

Throughout my Ph.D., I have had the opportunity to work with many talented students here at Berkeley. I would like to thank Hanh-Phuc Le and Ruzica Jevtic for working with me on my first tape out ever, Jaeduk Han and Yue Lu for the many tapeouts together, Andrew Townley, Greg LaCaille, Bonjern Yang, and Nathan Narevsky on general tapeout and Cadence guidance, and Zhongkai Wang for BAG support. I would also like to thank the professors on my thesis committees: Professor Vladmir Stojanovic and Professor Xin Guo and the rest of my fellow BWRC colleagues and the BWRC staff.

Finally, I would like to thank my family: my mother for being the most positive person I know and imparting her mindset on me, my father for proving that passion is the most important thing in life, and my brother for his continued belief in me and camaraderie during graduate school, which helped during some of the hardest times of the Ph.D. journey.

# Chapter 1

#### Introduction

## 1.1 Background

From our everyday personal devices to the massive, compute intensive clusters in the cloud, wireline links are ubiquitous. Whenever any data is transmitted over the Internet, countless wireline links operate in the background to send and receive data wherever it needs to go.

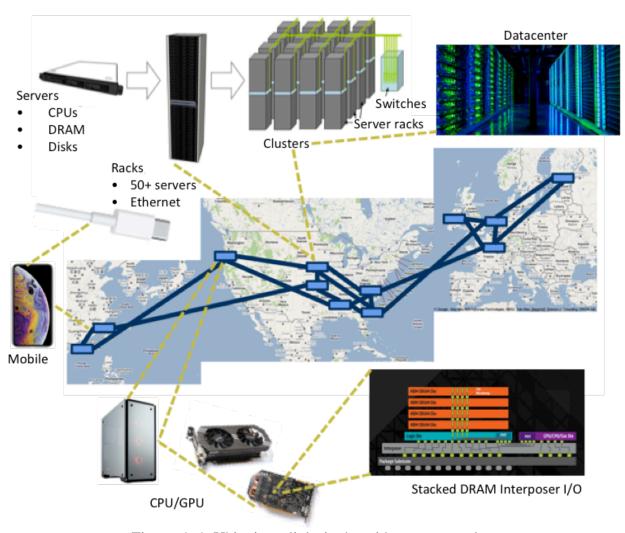

Figure. 1. 1. Ubiquitous links in the wide area network.

The rapid growth of Internet connectivity has required systems to become more distributed and data oriented. Specifically, computing systems have grown larger with more interconnections between various ASICs, with more of these ASICs being application specific [1].

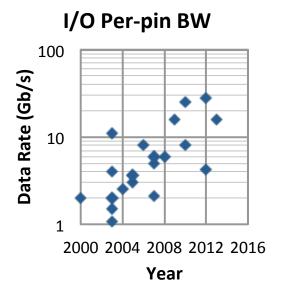

Physical limitations on pins and a limited energy budget for this streamlined computation and data communication have put an ever-increasing demand on communication and throughput of high-speed links. Throughput must improve by increasing per-pin bandwidth [2] and clustering massive I/Os [3], all while improving per-lane efficiency. Industrial standards have responded to this trend by increasing the data-rate of chip I/Os, demanding doubling per-pin data-rate around every four years while the power budget remains the same.

Figure. 1. 2. I/O per-pin bandwidth.

As Moore's Law comes to an end [25], the introduction of more modules (versus one monolithic IC) implies more off-chip communication, meaning that link latency (a nanosecond) becomes more significant. Supporting this throughput in multi-chip module, distributed systems as seen in stacked 3-D and 2.5-D GPU-memory machine-learning driven systems calls for links, which are able to quickly turn on and off and operate efficiently in low utilization modes while supporting capability for maximum throughput. The future of intelligent computing will evolve with this mentality in that highly specialized functional blocks will need to communicate not only with high throughput but also with extremely low latency to accomplish specific tasks [4].

#### 1.2 Wireline communication

Off-chip communication without equalization is limited up to a certain frequency (~100 MHz over a 1 meter wire) [13]. Wireline communication systems aim to make use of modern VLSI techniques to allow for the capability of sending data at much higher throughputs over significant distances. Various channel non-idealities and the increasing attenuation at higher frequencies has lead to significant efforts in the design of wireline transceivers.

Over the years a large amount of effort has been put into designing circuits to transmit and receive data through communication links in large backplane environments at higher data-rates by serializing digital data to be transmitted and then deserializing it in the receiver (SerDes). While these environments often remain the same due to legacy considerations, over the years, links have been tasked with operating at higher and higher data-rates. Increasing demands on off-

chip throughput and limited energy budgets require transceivers to operate in harsher link environments as there is more attenuation at higher frequencies due to the skin-effect and more dielectric losses [5].

Faster technology nodes have allowed us push data-rate through higher frequencies allowed through transistor improvements in digital (and mixed-signal) circuits. However, while scaling has aided us on some fronts, various advancements in transceiver equalization techniques as well as simultaneous channel design as seen in CPU-CPU links [6] and capacitively coupled links [7] have helped to ease data-rate and energy limitations that legacy backplane conditions have presented. In fact, our CPU-CPU link uses a 0.7m Twinax cable to operate at 60Gb/s in 65nm. Today, data-rates of published transceivers have been designed to operate upwards of 60Gb/s/channel especially at the more recent technology nodes [2].

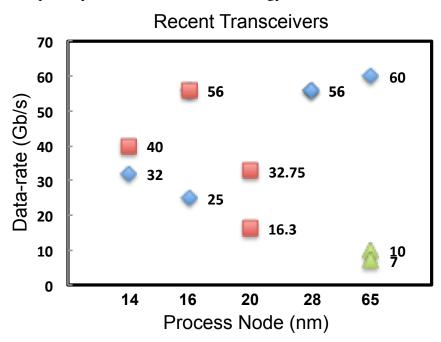

Figure. 1. 3. I/O Data-rate vs. process node for recent (2015-2018) transceiver designs.

Fig. 1.3 shows the data-rate of various, selected transceiver designs published by 2018 and their associated technology nodes (always-on transceivers in blue, data-rate flexible transceivers in red, and energy proportional transceivers in green). From this plot, we can see that there have been several designs approaching 60Gb/s, with the one 65nm 60Gb/s design described in further detail in Chapter 2. Furthermore, while technology improvements have lead to some level of data-rate scaling, there is a wide design space, for varying applications. For all of these links, differences in architectural choices due to variations on data-rate and/or channel losses, have lead to this range of designs.

Specifically, more designs are moving toward data-rate flexibility or energy proportionality, where links are not always expected to be utilized at maximum data-rate. The data-rate flexible transceivers (in red), while having flexibility in functional data-rate, are often only energy efficient at their maximum data-rate, since this flexibility is achieved through changing nominal data-rate, while system power remains largely the same. The energy proportional transceivers (in green) demonstrate burst-mode links which operate comparatively more efficiently during low link utilization, but are limited in their speeds.

Ultimately, all high-speed off-chip I/O requires a wireline transceiver due to physical limitations electrical signaling presents. Described in the next section, intersymbol interference (ISI) is at the core of this discussion, and is the starting point to explaining why equalization is necessary, especially as higher demands on throughput require links to operate at higher datarates.

## 1.2.1 Intersymbol interference

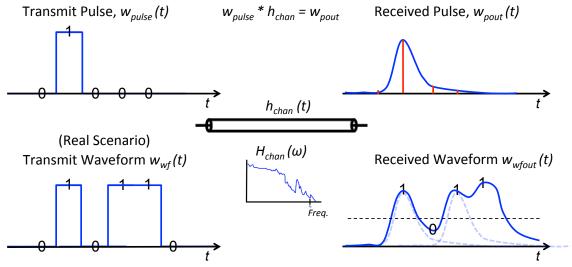

Examining how various bits are affected after going through a non-ideal channel, Fig. 1.4 depicts the received waveforms from an ideal pulse  $(\omega_{pulse}(t))$  and data waveform  $(\omega_{wf}(t))$ .

Figure. 1. 4. Intersymbol interference.

The received pulse response  $(\omega_{pout}(t))$  when sampled at the data-rate contains energy that is spread out in time after the channel. These UI spaced signal values are known as pre-cursors and post-cursors depending on if they are before or after the largest signal value, usually chosen to be the cursor. The channel  $(h_{chan}(t))$  spreads out the energy, making the correct values of  $\omega_{wfout}(t)$  harder or impossible to resolve. Especially as our sampling rate increases and more energy leaks into neighboring bits, resolving the difference between a "1" and "0" data level (compared to a threshold) becomes ambiguous or data-dependent. This interference degrades noise margins, reducing the maximum frequency at which the link can operate. This phenomenon is known as intersymbol interference, and it only intensifies at higher frequencies. To counteract these bandwidth limitations caused from both pre-cursor and post-cursor ISI, various equalization techniques are implemented in the transmitter and receiver.

### 1.3 Equalization

<sup>&</sup>lt;sup>1</sup> At high data-rates, when the channel contains a comparable pre-cursor, it is often more efficient to choose the pre-cursor as the cursor, and subsequent taps (including the largest energy value) are cancelled by the DFE [9].

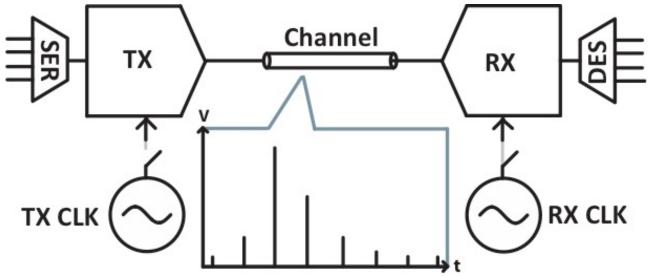

Equalization is the effort that is performed to clean up signals before the slicer to make sure the received bits are the "same" as those that were transmitted. Typically, a wireline link seeks to have enough equalization to achieve error free operation over a significant amount of bits (>  $10^{12}$ ) to avoid having to restart, causing interruption in communication. In order to ensure this, transceivers seek a bit error rate (BER) of <  $10^{-12}$  through a large enough timing window so that they are tolerant to noise and clock jitter. A generic wireline link architecture is shown in Fig. 1.5 where data must go through the channel with its associated pulse response.

Figure. 1. 5. Wireline link architecture.

First, a serializer translates the digital (coming from CPU, GPU, memory, etc. ...) data bits into a serial bitstream. Equalizers are employed before the RX slicer to cancel pre-cursor and post-cursor ISI seen from sending data through the non-deal pulse response. These equalizer structures include the continuous time linear equalizer (CTLE), feed-forward equalizer (FFE), and decision feedback equalizer (DFE), all of which are instrumental in providing ISI cancellation by mitigating errors caused by pre-cursor and post-cursor taps introduced from the channel. Finally, data is deserialized and made available to the rest of the system for further processing. The following sections discuss the various uses for RX equalizers in a wireline link.

# 1.3.1 Continuous time linear equalizer

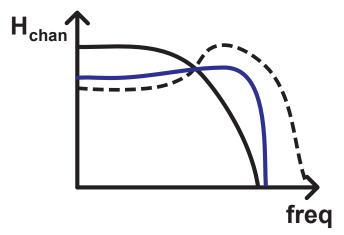

The continuous time linear equalizer is typically used as the first linear equalizer in the RX to boost high frequency content that has been attenuated in the channel and to attenuate low frequency content to flatten out the overall frequency response. This accomplishes equalization by placing a high pass filter following the (typically) low pass filter caused by the channel (Fig. 1.6).

Figure. 1. 6. CTLE equalization.

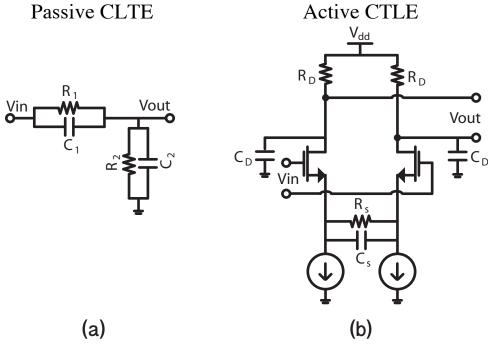

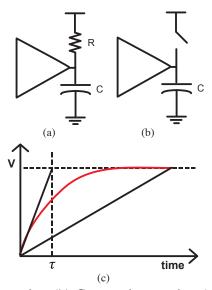

CTLEs are commonly realized as a passive CLTE or active CLTE shown in Fig. 1.7.

Figure. 1. 7. Continuous time linear equalizers (a) Passive CTLE (b) Active CTLE.

The following analysis determines how we can size the passive CTLE (Fig. 1.7(a)) for the amount of peaking (equalization) desired. Simple KCL leads us to the frequency response  $H(s) = V_{out}(s)/V_{in}(s)$  as

$$H(s) = \frac{R_2}{R_1 + R_2} \frac{1 + R_1 C_1 s}{1 + \frac{R_1 R_2}{R_1 + R_2} (C_1 + C_2) s}$$

(1.1)

where

$$\omega_Z=\frac{1}{R_1C_1}$$

and  $\omega_p=\frac{1}{\frac{R_1R_2}{R_1+R_2}(C_1+C_2)}$ , and the DC gain and high frequency gain are  $A_{DC}=\frac{R_2}{R_1+R_2}$  and  $A_{HF}=\frac{C_1}{C_1+C_2}$ .

The amount of peaking achieved is simply

Peaking<sub>passive CLTE</sub> =

$$\frac{A_{HF}}{A_{DC}} = \frac{R_1 + R_2}{R_2} \frac{C_1}{C_1 + C_2}$$

(1.2)

We can similarly find the peaking from the active CTLE (Fig. 1.7(b)) from calculating the frequency response as

$$H(s) = \frac{g_m}{C_D} \frac{s + \frac{1}{R_s C_s}}{(s + \frac{1 + g_m R_s/2}{R_s C_s})(s + \frac{1}{R_D C_D})}$$

(1.3)

where the DC gain and high frequency gain are

$$A_{DC} = \frac{g_m R_D}{1 + g_m R_S/2}$$

and  $A_{peak} = g_m R_D$  (assuming the  $\frac{1}{R_D C_D}$  pole is the second pole).

$$Peaking_{active\ CLTE} = \frac{A_{peak}}{A_{DC}} = 1 + g_m R_s / 2 \tag{1.4}$$

The addition of the pole and zero of the CTLE allows us to flatten out the overall frequency response seen after the channel by boosting high frequency content compared to low frequency content. This allows for a flatter frequency response that provides long-tail ISI cancellation to mitigate ISI induced from many post-cursors that are often too costly to equalize for directly. On the other hand, large amounts of ISI compared to the cursor value  $(V_{ISI}/V_{CURSOR})$  usually are not directly handled by the CLTE. This ISI usually appears, due to the low pass nature of a channel, at the pre-cursors and post-cursors closest to the cursor. While the CTLE presents a continuous time solution for pre-emphasis, channels at high-speeds often require more sophisticated methods of equalization. A feed-forward equalizer can be designed in the discrete domain for further equalization.

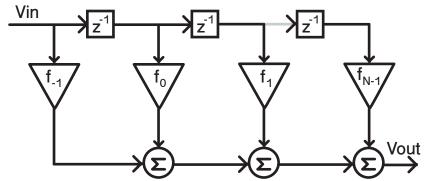

# 1.3.2 Feed-forward equalizer

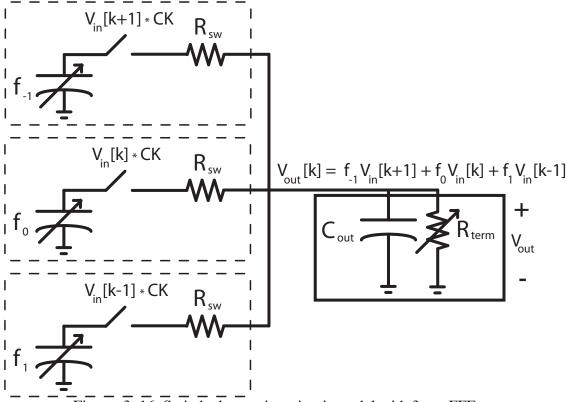

The feed-forward equalizer is typically used to provide more gain at higher frequencies and to mitigate pre-cursor ISI. This is achieved through sending bits through a finite impulse response filter (FIR) filter. Fig. 1.8. Figure presents an N+1-tap FFE with 1 pre-cursor and N-1 post-cursors that achieves this function.

Figure. 1. 8. Feed-forward equalizer.

The following FFE equation demonstrates the functionality an N+1-tap FFE with 1 pre-cursor, cursor, and N-1 post-cursors.

$$V_{OUT}[k] = \sum_{i=-1}^{N-1} f_i * V_{IN}[k-i]$$

(1.5)

The FFE allows us to transmit a weighted sum of shifted bits to cancel ISI. Since  $V_{OUT}[k]$  is a sum of linearly scaled delayed signals and we can choose which k is the desired cursor, precursor ISI can be cancelled, making the FFE a worthwhile equalizer even with a limited number of taps.

For instance, a 2-tap FFE with a negative  $f_1$  (and positive  $f_0$ ) can provide useful equalization as the negative  $f_1$  value (and positive  $f_0$ ) can realize a high pass characteristic to provide gain to the channel's high-frequency content compared to the low-frequency content. Two opposite sign bits (as in a clock pattern) give us a maximum gain of  $(f_0 + f_1)$ . Conversely, two consecutive bits (as in a DC pattern) give us minimum gain of  $(f_0 - f_1)$ .

While the FFE is useful to equalize pre-cursor ISI and provide high frequency gain, it amplifies high frequency noise as well. Furthermore, additional equalization in the FFE implies the reduction of the cursor tap weight, since headroom limits the output swing of the design  $(\sum |f_i| = 1)$ .

Since the high frequency gain of the FFE amplifies more high-frequency noise, more equalization leads to more noise enhancement. This leads us to our next equalizer, the decision feedback equalizer, which takes advantage of a slicer to erase noise and memory effects introduced from the channel.

## 1.3.3 Decision feedback equalizer

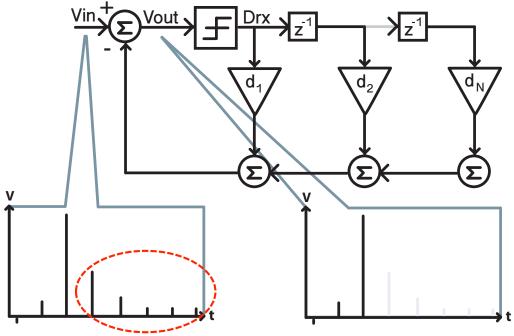

A decision feedback equalizer (DFE) is a non-linear equalizer that allows us to make a symbol decision by quantizing the input with a slicer and subtract out ISI using a feedback FIR filter (Fig. 1.9). The N-tap DFE shown cancels out N post-cursors up to the resolution of the DFE tap  $(d_i)$  coefficients. As the slicer allows us to remove all noise due to post-cursors from the channel, the  $d_i$  can be directly chosen to equal the equalized channel response post-cursor values right before the DFE (at  $V_{in}$ ). Enough ISI needs to be cancelled prior to the slicer, so that noise does not allow for wrong decisions to be made, for a certain amount of consecutive bits.

Figure. 1. 9. Decision feedback equalizer.

This non-linear nature (due to the slicer) of the DFE allows the  $k^{th}$  post-cursor to be directly cancelled out as

$$V_{out,k} = V_{in,k} - d_1 * D_{out,k-1} - d_2 * D_{out,k-2} \dots - d_N * D_{out,k-N}$$

(1.6)

Since only subsequent bits are fed back to the summing node, only post-cursor ISI can be cancelled. Even though it cannot cancel pre-cursor ISI, the DFE can directly cancel out post-cursor ISI without any noise amplification (unlike in the case of the FFE, where the additional linear noise-enhancing, amplifiers are necessary before the slicer). This circuit is extremely valuable since post-cursors are completely eliminated up to the resolution and dynamic range of the DFE tap coefficients. Typically, earlier  $d_i$ 's are designed to handle more current to be able to equalize larger post-cursors.

As DFEs approach higher-speeds (equalizing for higher data-rates), the limiting factor for high-speed DFE operation is closing the feedback timing path within 1 Unit Interval (UI). Specifically this is dependent on the technology's  $f_t$  (when current gain is unity or approximately  $\frac{1}{2\pi}\frac{g_m}{c_{gs}}$ ). Loop unrolling [8] has been used to get around this feedback loop by creating concurrency (performing look-ahead computation in order resolve the previous bit before the next arrives) but introduces additional delay into the critical paths of later (non-unrolled) DFE taps. Furthermore, loop enrolling does not scale well as it would involve  $2^N$  comparators for N taps. Various other techniques are introduced in the 66Gb/s DFE design in [9], where the summer is merged with the latch to reduce loading on the first tap, pushing the data-rate for high-speed DFEs. We take advantage of this technique, along with several other techniques for equalization at high speeds.

### 1.4 Thesis organization

As this chapter has motivated the need for equalization and high-speed links, the following chapter explains various techniques that push the boundaries of throughput and energy efficiency in the receiver through design of energy efficient CTLE, RX FFE and DFE. Various techniques including double data-rate (DDR) architecture, cascode tap control, integration, and incomplete reset settling are employed to enable efficient, receive-side equalization at 60Gb/s. These techniques are demonstrated in two separate designs. First a receiver frontend was taped out in a 65nm TSMC process achieving 60Gb/s, equalizing an ISI of  $1.54 \, V_{ISI} / V_{CURSOR}$  and error free operation over 1e12 bits. Then, a complete 60Gb/s transceiver taped out in a 65nm TSMC process achieves  $4.8 \, \mathrm{pJ/bit}$ , equalizing 21dB of loss at 30GHz over a 0.7-m Twinax cable.

Chapter 3 introduces the concept of energy proportional communication, motivating the need for low-latency, burst-mode communication. Furthermore, various system and architectural level considerations and how they affect startup time and quiescent current are discussed for an energy proportional transmitter. With the design constraints for an efficient, burst-mode transmitter in mind, Chapter 4 explains various techniques for limiting quiescent current consumption and startup time and presents a 2-tap switched-capacitor FFE transmitter achieving 1-20 Gb/s at 0.72-0.62 pJ/bit achieving a latency of 1.2ns with a 64:2 1-latch serializer in a 28nm TSMC process. Finally, Chapter 5 summarizes the thesis and points out future areas of research.

## Chapter 2

## Energy-efficient Receiver Design Techniques for 60-Gb/s

While various designs have demonstrated high-speed receiver circuits including high-speed DFEs in [9][10][11], further power reductions are required to meet the stringent power constraints and make these more attractive for widespread implementation. In particular, current integration is implemented in various receiver circuits allowing for power savings compared to the continuous-time summation counterparts. Furthermore, receive side FFE is demonstrated for pre-cursor ISI cancellation in the receiver, saving power compared to doing the same in the transmitter. Finally, incorporating all these techniques together, a DDR, integrating CTLE, FFE and DFE is demonstrated in a 60Gb/s non-return-to-zero transceiver with adaptive equalization achieving 60Gb/s with >0.3 UI opening at  $10^{-12}$  Bit Error Rate, while consuming 288 mW and occupying  $2.48 \ mm^2$ .

## 2.1 Current integration vs. resistive summation

Figure. 2. 1. (a) Resistive summation (b) Current integration (c) Voltage vs. time for current integration vs. resistive summation.

The first technique that allows for energy-efficient, high-speed operation is known as current integration, which was first proposed in [12] for a low-power DFE. A current integration circuit (Fig. 2.1(b)) as opposed to resistive current summation circuit (Fig. 2.1(a)) makes use of the clock to pre-charge (or reset) the output voltage to  $V_{dd}$  (or a common mode voltage as in [13]) and then discharges the output voltage based on the output capacitance C and transconductance in the integration phase. This technique is well suited for DDR architectures since there is a natural reset phase for half the clock period. Fig. 2.1 compares current integration and resistive current summation.

While resistively loaded summation experiences exponential settling time to achieve a desired gain (in red), current integration allows for the same gain to be achieved in a shorter time or power to be saved given the same time to achieved the desired gain (Fig. 2.1(c)).

An extensive analysis in the current integrating DFE and FFE shows a  $\sim 3x$  power savings compared to resistively loaded stages [13]. Current integration, as opposed to continuous-time allows for  $N_{\tau}$  savings in power (1.7).

$$\frac{I_{integrating \ summer}}{I_{continuous-time \ summer}} \approx \frac{T_{bit}}{\tau} = N_{\tau}$$

(1.7)

We use this technique in our CTLE, DFE + FFE summer described in the following sections.

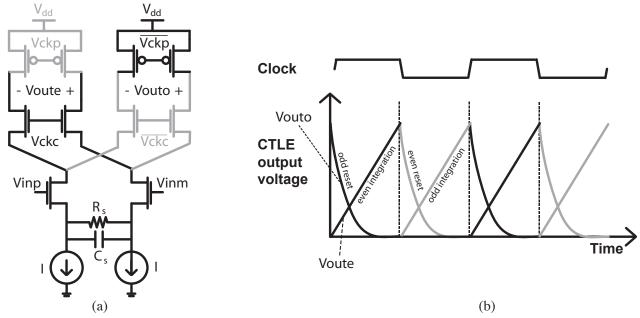

#### 2.2 Current integrating CTLE and DMUX

The resistively loaded CTLE as in (Fig. 1.7) is not sufficient for high-speeds, as it requires a lot of power as described in the previous section. Current integration for the CTLE through replacing the resistors with PMOS resetting switches allows the CTLE to function as an integrator, and it also gives us the added benefit of a two-phase system (for DDR operation). With one modification (adding an additional NMOS cascode transistor similar to the cascode sampling proposed in [14]) to provide two distinct differential outputs (*Voute* and *Vouto*)), we can demultiplex our full-rate data with this integrating stage to provide the odd and even data for the rest of the DDR receive chain. This first CTLE + DMUX stage provides an energy efficient way to have CTLE and provide a demultiplexer (DMUX) for odd and even data paths.

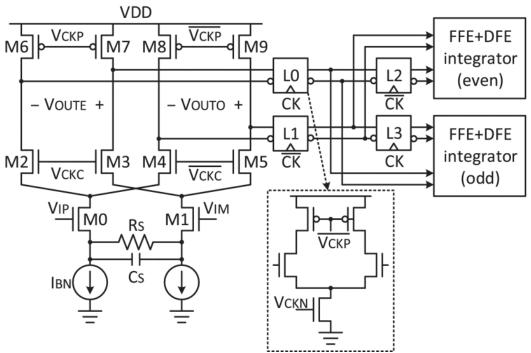

We employ current integration, with two cascode resetting stages and a shared NMOS input pair with resistive and capacitive degeneration (Fig. 2.2).

Figure. 2. 2. (a) Current integrating CTLE + DMUX (b) CTLE odd and even outputs over time.

The odd PMOS and even NMOS cascode switches in the upper part of the circuit are activated at the same time (same with the even PMOS and odd NMOS cascode), while the bottom NMOS differential inputs are always on. This alternating integration and reset is delineated by the black and grey shading in the circuit in Fig. 2.2(a). Fig. 2.2(b) shows the ideal CTLE odd and even output voltages, where each path resets and integrates in opposite phases. Reset in this diagram occurs fully, as the differential output voltages reach 0V differential every cycle. Furthermore, the DC level of the cascode clock can allow for additional control over overall gain.

The next technique that we use to save energy is receiver feed-forward equalization (RX FFE) explained in the following section.

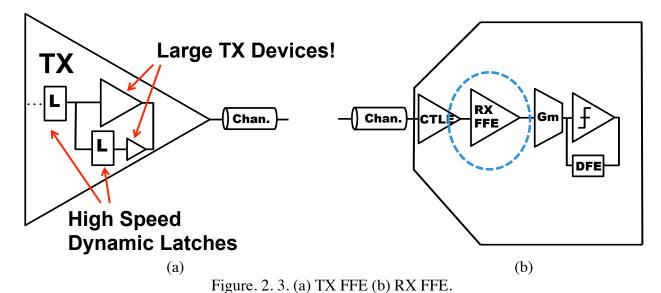

# 2.3 RX feed-forward equalization

We compare TX feed-forward equalization with RX feed-forward equalization in Fig. 2.3.

Receive-side equalization is commonly achieved using predominantly CTLE and DFE. Since FFE requires multiple stages of delay, it is typically done in the digital domain at the transmitter.

Implementing FFE in the TX might require more power compared to having the same function in the receiver. Some high-speed TX FFE's are shown with various implementation differences in [15] where 7-tap feed-forward equalizer is designed with current mode logic delay elements and output driver and in [16] where a 1-UI delay line consisting of inductors and capacitors is used to create delay for a 4-tap FFE. These delay elements and drivers consume considerable amounts of current to achieve FFE equalization in these designs.

However, the presence of pre-cursor ISI from our channel means that we still need feed-forward equalization. As in the TX-FFE, the RX FFE achieves the same FIR filter function to sum delayed and amplified versions of the signal. Especially for multi-tap designs as in [13], considerable power can be saved, since power is based on the analog delay elements needing to only drive  $g_m$  stages in the RX rather than large digital delay elements needing to drive  $50\Omega$  loads in the TX driver. However, one of the challenges lies in how to actually realize linear,

analog delay elements in the receiver. We make use of analog dynamic latches to create the UI spaced delay in our DDR RX FFE.

#### 2.3.1 Dynamic latches

Since integrating CTLE's resetting (or return-to zero or RZ behavior) waveforms (Fig. 2.2(b) mean that the output signal of one stage is not available to the next during integration, we need to first convert the RZ waveforms into non-return-to-zero (NRZ) before using the CTLE output for further receiver stages. An analog dynamic latch can be used for this purpose, shown in Fig. 2.4. In addition to creating the NRZ waveforms, the latches naturally create the UI-delay for the FFE + DFE integrator.

Figure. 2. 4. CTLE + DMUX and following FFE latches.

Since any gain before the slicer must be analog in nature, linearity must be preserved in the delay elements. The high-speed analog delay latch is similar to the digital dynamic latches in [9], but is designed to have higher input transistor overdrive voltage  $(V^*)$  for linear signal-transfer characteristics. The Dynamic latch provides gain when both  $V_{ckn}$  and  $V_{ckp}$  are high (both on), and the parasitic capacitance at the output nodes hold the value while off. Input NMOS devices are sized to have enough overdrive voltage to support the expected swing seen at the inputs.

Careful consideration is placed into designing these latches with appropriate common mode voltages with gains around or slightly above 1 (to ensure linearity and not amplify noise unnecessarily). Hence, multiple DACs are used for the individual bias voltages of  $V_{ckn}$ ,  $V_{ckp}$ , and  $V_{ckc}$  to be able to control both latch gain and integration window. Furthermore, swing control of the gate voltage is also implemented for the current sources (to keep them in saturation) using explicit capacitive division, added to the clock network.

#### 2.3.2 FFE coefficient control

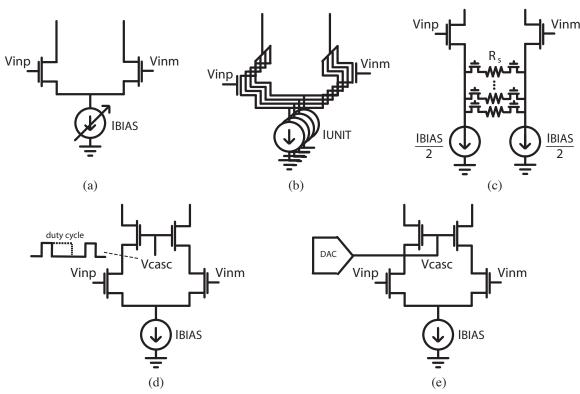

To implement the coefficients ( $f_i$ 's) in (1.5), variable effective transconductance at the integrating node controls how much current is integrated per tap. Five different possible methods to achieve this are shown in Fig. 2.5.

Figure. 2. 5. Transconductance implementations for FFE coefficient ( $f_i$ ) control (a) Current-bias control (b) Differential pair unit cells (c) Source degeneration (d) Cascode with duty cycle control (e) Cascode with variable DC bias.

The first, most common method is current-bias control (Fig. 2.5(a)), which is widely used in DFEs, allowing for a variable amount to be integrated in the differential pair. However, this approach is infeasible for feed-forward equalization because FFE requires linear signal-transfer characteristics. Specifically, the input signals to the FFE ( $V_{inp}$  and  $V_{inm}$ ) are both still analog and must be further equalizer by later stages. Reducing tail current (for the same sized input pair) when smaller  $f_i$  is desired would reduce the  $V^*$  of the input pair, making the input pair start to clip as signals get large. This leads to nonlinear distortion that cannot be directly compensated through equalization. Alternatively, the DFE gets away with this implementation because the inputs to the differential pair are digital (and the input transistors operate as switches).

To get around this linearity issue, Fig. 2.5(b) employs unit cells of differential pairs to modulate the amount of current integrated. Multiple differential pair unit cells are configured in parallel, and a subset is turned on to achieve the desired  $f_i$ . Since  $V^*$  remains constant with gain control, linear signal-transfer characteristics are preserved. Fig. 2.5(c) presents another solution to linearity by adding a variable degeneration resistance ( $R_s$ ). While they both preserve linearity,

these solutions suffer from limited minimum transistor-size constraints, limiting tap resolution or power efficiency. In order to achieve a high resolution (high number of bits b) using the unit cell method, minimum size constraints would soon limit how small each differential pair could be sized. Due to many minimum-sized switches introducing a lot of capacitance on the tail, gain at high frequency will not be as expected, but instead much higher. Additionally, capacitive loading on the integration node would be determined by the  $2^b$  times the minimum size and not the actually desired current, making this architecture's per-tap power scale exponentially with the number of bits. Resistive degeneration suffers from a similar issue, as there is a limit as to how much degeneration can be achieved with minimum-sized switches.

To support a large dynamic range with high resolution without sacrificing linearity or directly increasing power consumption, we propose a cascode current control scheme in Fig. 2.5(d) and Fig. 2.5(e) where an additional cascode NMOS switch is added in between the input pair and output node.  $V_{casc}$  is controlled by modifying the duty cycle of the input into the cascode in Fig. 2.5(d), where integration time is modulated to vary the gain. A digital to time converter [17] can be used for this purpose.

For our design, we use a DAC to set the DC bias of  $V_{casc}$ , which sets the drain voltage and input impedance of the input differential pair devices changing the overall gain. Since the overdrive voltage of the input pair is preserved, the signal linearity is largely unaffected by the gain setting. Both the duty cycle control and variable DC bias for the cascode achieve the linearity we desire; however, we go with the DC bias, since a DAC costs less power (compared to power introduced from digital switching in a digital to time converter). It is important to note that, if no DACs (and no quiescent current) are desired for energy proportional communication as we will introduce in Chapter 3, duty cycle control can be a more attractive choice.

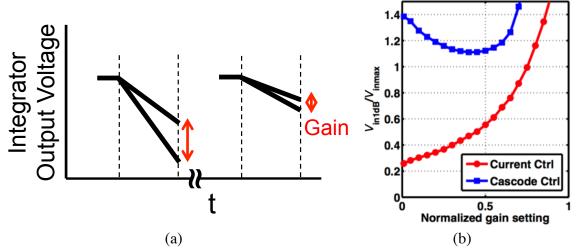

Fig. 2.6 shows the integrator output voltage time domain characteristics for different gain settings and compares the linearity of the cascode control method to conventional current-bias control.

Figure. 2. 6. (a) Cascode DC bias control integrator output voltage (b) Linearity comparison between current-bias control and cascode DC bias control.

From Fig. 2.6(a), gain variation is achieved from varying differential output strength as transconductance impedance is modulated by the DC bias of the cascode switch. In Fig. 2.6(b),

$V_{in1dB}$  is the input voltage at which the gain drops by 1 dB from its target value, and  $V_{inmax}$  is the maximum input swing expected to be fed into the FFE stage. In the conventional, current-bias control (in red),  $V_{in1dB}/V_{inmax}$  varies from 0.2 to above 1.4 across gain settings. This variation in gain is not acceptable for a linear amplifier; hence, it cannot be used in the FFE, since it would add ISI that cannot be equalized. Instead, the cascode DC bias control (in blue) shows much better linearity with  $V_{in1dB}/V_{inmax}$  being relatively flat across gain settings (1.4 to 1.1).

It is important to note the while linear signal-transfer characteristics must be preserved as to not introduce signal-dependent ISI, tap strength vs. code does not need to be linear. Instead, it only has to be monotonic so that the adaptation loops settle appropriately.

#### 2.3.3 Integrating FFE+DFE

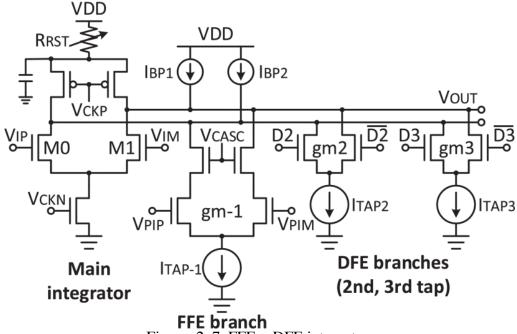

Since DFE taps do not need to have linear signal-transfer characteristics as in the FFE taps, the DFE employs current-bias control for DFE taps. Rather than summing the FFE and DFE with separate summers, an FFE+DFE can be combined into an integrating summer stage (Fig. 2.7).

Figure. 2. 7. FFE + DFE integrator.

Variable  $R_{RST}$  at the supply of the integrating summer allows for variable common-modereset voltage. Additional decoupling capacitance is added to this supply for robustness. The FFE pre-cursor and DFE's tap-2 and tap-3 post-cursors are summed at this node, while the DFE's tap-1 is summed at a following stage shown in the following section.

Instead of trying to settle the output node completely in the short reset window ( $\sim 16ps$  at our data-rate) to avoid introducing any ISI, the resetting switch was sized to only settle to  $\sim 85\%$  of the final value ( $2\tau$  of settling) since the PMOS switches in 65nm are substantially worse than NMOS switches, and hence introduce considerably more capacitive loading. Not fully settling introduces extra ISI, which is demonstrated in Fig. 2.8 below.

Fig. 2.8 shows the integrator output voltage during integration and reset for sequential cycles assuming  $2\tau$  of settling. As seen from the incomplete settling at  $T_{n+1}$ , the integrator is not given enough time to completely settle to 0V differential (compared to the perfect reset from the dotted line and also shown in the ideal integrator output voltages in Fig. 2.2(b)). This incomplete settling time translates to second and third tap ISI (and also in later taps, but these are assumed to be small due to the suppression from multiple resets). This extra ISI is handled by overdriving the DFE (using increased  $d_i$  coefficients), costing additional power in the form of increased loading from increased maximum current in the post-tap differential pairs.

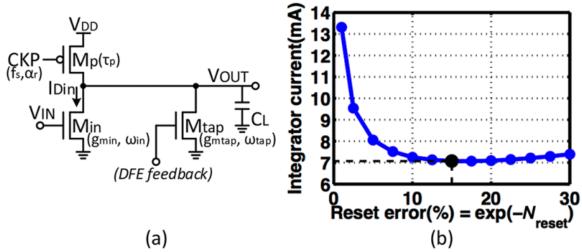

This tradeoff of incomplete resetting (due to the increased time constant of PMOS devices) and the additional tap strength required to cancel the introduced ISI (Fig. 2.9(a)) can be quantified through the following equations and the optimal reset error desired for minimal power is simulated to be 85% from Fig. 2.9(b).

From [13], the power consumption of a current-integrating DFE  $(P_{int})$  at data-rate  $f_s$ , gain G, and load capacitance  $C_L$  was shown to be

$$P_{int} \propto \frac{I_{nom} \cdot 2(1 + k_{reset})}{1 - \frac{G \cdot f_s}{\omega_{T,in}} \cdot \gamma \left(1 + k_{tap0} \frac{v_c}{V_i^*} \beta\right) \cdot 2(1 + k_{reset})}$$

(1.8)

where  $I_{nom} = C_L V_i^* G f_s$  is the current-consumption of a class-A amplifier without self loading,  $\omega_{T,in}$  is the transit frequency of the input transistor,  $V_i^*$  is the overdrive voltage of the input transistor,  $v_c$  is the input cursor amplitude,  $k_{tap0}$  is the ratio between the ISI and cursor,  $\gamma$  is the drain-to-gate-capacitance ratio,  $\beta = \omega_{T,tap}/\omega_{T,in}$  is the ratio between the transit frequencies of the tap transistors and the input transistor, and  $k_{reset}$  is the factor by which the capacitance of the summing node needs to be increased to include reset capability. The effects of incomplete reset

are captured by an equivalent RC network composed of a PMOS reset device and load capacitances at the output where the time constant of the reset network can be expressed as

$$\tau_{reset} = \tau_p \left( \frac{1 + k_{reset}}{k_{reset}} \right) = \frac{\alpha_r}{f_s N_{\tau, reset}}$$

(1.9)

where  $\tau_p = r_{op}C_{Dp}$  is the PMOS time constant without additional loads,  $\alpha_r$  is the fraction of each UI spent for resetting, and  $N_{\tau,reset}$  is the number of reset time constants desired.

$$k_{reset} = \frac{\tau_p}{\frac{\alpha_r}{f_s N_{\tau.reset}} - \tau_p} \tag{1.10}$$

Tap strength is increased by  $e^{-N_{\tau,reset}}$  to compensate for the increased ISI induced from incomplete settling.

Figure. 2. 9. (a) Simplified DFE circuit diagram (b) Optimal reset accuracy.

The optimal reset accuracy is relatively flat around 15% reset error and saves almost half the power compared to almost completely resetting (Fig. 2.9(b)).

# 2.3.4 DDR receiver frontend

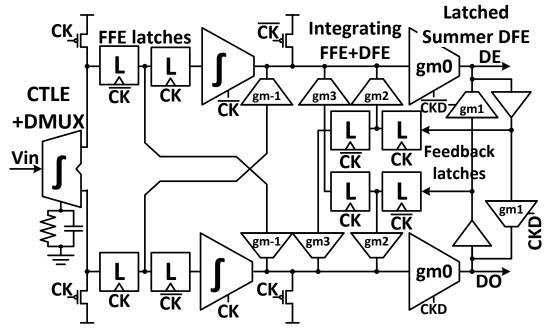

Figure. 2. 10. Receiver frontend architecture.

The receiver frontend architecture is shown in Fig. 2.10, where full-rate data is equalized and demultiplexed by an integrating CTLE + DMUX. Latches turn the CTLE output into NRZ signals, which are further delayed and taken as the UI-delayed signals for the DDR FFE. The integrating FFE+DFE summer combines the pre-cursor FFE tap and the DFE's tap-2 and tap-3 summing. A dedicated latch is used as the summer for the first DFE tap as in the DFE in [9] to meet the stringent-timing requirements of closing the first DFE tap.

#### 2.4 60Gb/s receiver frontend results

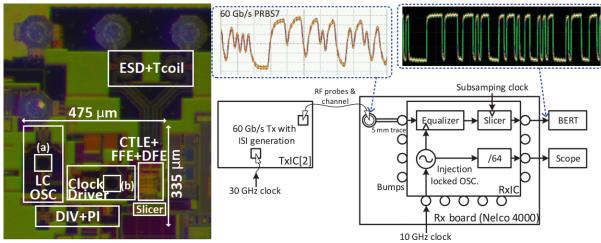

This architecture was first demonstrated in a receiver frontend in a 65nm process (Fig. 2.11(a)). The equalizer-core circuit occupies  $0.012 \ mm^2$ , and the fabricated chip occupies  $0.16 \ mm^2$  (except for the pad, ESD, and t-coil area). The chip was as directly soldered onto a Nelco 4000-13 PCB via flip-chip bumps to minimize parasitic loading from package structures.

Figure. 2. 11. (a) Die photo (b) Measurement setup and measured waveforms (All clock sources are synchronized.).

Since no 60Gb/s signal source was available for the measurement, the pattern-generator/channel-emulator circuit from the chip described in [9] was reused for testing the receiver (shown in the measurement setup in Fig. 2.11(b)). The band-limited transmitter provided differential PRBS7 signals with emulated channel profiles for our receiver to equalize.

Eye diagram measured at the input of the receiver frontend evaluation board shows a closed eye before equalization (Fig. 2.12(a)) with an estimated pulse response in Fig. 2.12(b).

Figure. 2. 12. (a) Eye Diagram at the channel output (b) Estimated pulse response.

The chip was tested with a 10 GHz clock generator (Keysight E8267D) synchronized with a 30 GHz transmitter clock source (Keysight E8257D) to provide the injection clock (with the oscillator injection locking enabled) with different phases for bathtub characterization. Furthermore, a Keysight 86130A BERT measures the BER of the reconstructed PRBS7 pattern from 1/128x sub-samplers, clocked by an external source (Keysight E8267D). Under these conditions, the receiver front-end recovers the transmitted PRBS pattern and operates at 60Gb/s error-free over 10<sup>12</sup> bits for the phase offset shown in the bathtub curve in Fig. 2.13 (and with > 0.2 UI-timing margin at 1e-9 BER).

Figure. 2. 13. Bathtub curve after equalization.

The receiver achieves 60 Gb/s, consuming 173mW (138mW from a 1.2V and 35mW from 1.0V supply) in a 65nm process, demonstrated to equalize 1.54 times the cursor amplitude of ISI. Table I compares the design with prior 56-80 Gb/s equalizer designs.

Table 2. 1: Comparison of high-speed receiver equalizers

| Table 2. 1. Comparison of high specu receiver equalizers   |                  |                   |                                                   |                                |

|------------------------------------------------------------|------------------|-------------------|---------------------------------------------------|--------------------------------|

| Reference                                                  | [9]<br>JSSC'2013 | [10]<br>JSSC'2014 | [11]<br>VLSI'2014                                 | This work                      |

| Process                                                    | 65nm CMOS        | 130nm SiGE        | 20nm CMOS                                         | 65nm CMOS                      |

| Data-rate (Gb/s)                                           | 66               | 80                | 56                                                | 60                             |

| Equalizer                                                  | 3-tap DFE        | 1-tap DFE         | External 2-tap<br>FFE (6 dB)<br>CTLE<br>1-tap DFE | CTLE<br>2-tap FFE<br>3-tap DFE |

| V <sub>ISI</sub> /V <sub>CURSOR</sub> or channel loss (dB) | 1.65             | 12 dB             | 23 dB                                             | 1.54                           |

| Power (mW)                                                 | 46               | 4000              | 177*                                              | 173                            |

| Equalizer                                                  | 46               | 1772              |                                                   | 48                             |

| Deserializer                                               | N/A              | N/A               |                                                   | 28                             |

| Clock generation                                           | N/A              | N/A               | N/A                                               | 52 <sup>◊</sup>                |

| Clock<br>distribution                                      | N/A              | 2228              |                                                   | 45                             |

| Efficiency (pJ/bit)                                        | 0.7              | 50                | 3.16                                              | 2.88                           |

\*Includes equalizer, 4:16 DES, clock distribution

Includes output buffer

Integration (in the CTLE, FFE, and DFE) is shown to be an energy-efficient technique for equalization at high speeds, as the complete receiver frontend consumes 2.88pJ/bit, equalizing ISI of 1.54 times the cursor.

<sup>&</sup>lt;sup>⋄</sup>LC oscillator + divider + PI

The receiver frontend was demonstrated again in a complete transceiver design, and the results shown next.

# 2.5 60Gb/s complete transceiver results

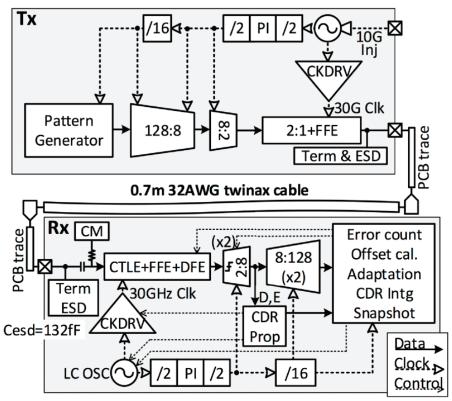

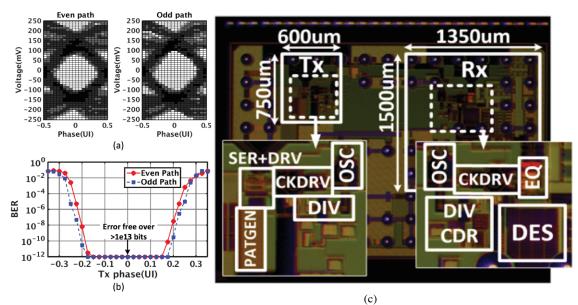

The data-path circuitry adapted from the receiver was implemented in a complete transceiver architecture operating at 60Gb/s with adaptive equalization and a baud-rate CDR. A current mode logic (described in further detail in chapter 3) transmitter was used to implement the transmitter at higher speeds. The transceiver architecture with 1:128 SERDES ratio, 3-tap TX FFE, 2-tap RX FFE, CTLE, and 3-tap DFE, is shown in Fig. 2.14, and the clocking, adaptation and CDR is described in detail in [18].

Figure. 2. 14. Transceiver architecture.

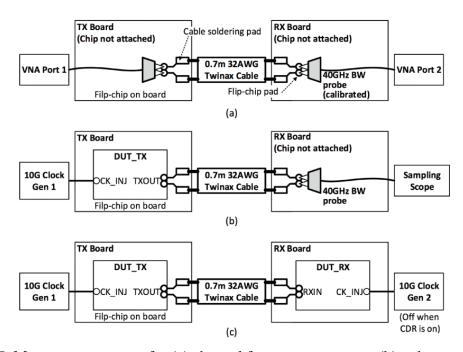

Figure. 2. 15. Measurement setups for (a) channel frequency response, (b) pulse response, and (c) equalizer and CDR characterization.

Figure. 2. 16. (a) Measured channel frequency response (b) TX + channel eye diagram (c) TX + channel pulse response.

Figure 2.16(a) shows the measured S21 of the channel from the configuration in Fig. 2.15(a), showing -21dB of insertion loss at 30GHz. The measurement setup in Fig. 2.15(b,c) where the a Keysight E8267D is used to generate a 10-GHz reference clock to injection lock the transmitter's 30-GHz LC oscillator is used to characterize the TX + channel eye diagram before equalization, showing a closed eye (Fig. 2.16(b)) and  $V_{ISI}/V_{cursor}$  of 2.9. In particular, pre-cursor ISI, significant post cursor ISI, and long-tail ISI are observed in the measured pulse response (Fig. 2.16 (c)), necessitating the use of the complete CTLE+FFE+DFE equalizer chain.

With equalization turned on, on-chip eye diagrams and a bit error rate bathtub curve were measured with the setup in Fig. 2.15(c).

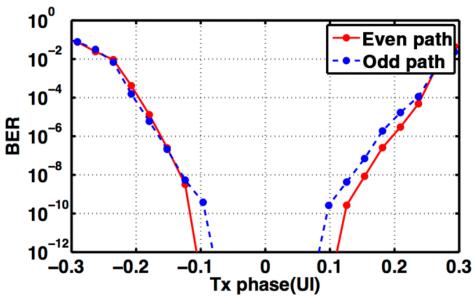

Figure. 2. 17. (a) Eye diagrams (b) Bathtub curve (c) Die photo.

The design achieves >0.3 UI eye opening at  $10^{-12}$  BER for both the odd and even paths (Fig. 2.17(a,b)). The die photo is shown in (Fig. 2.17(c)) with the transceiver occupying 2.48  $mm^2$  (TX: 0.45  $mm^2$  and RX: 2.03  $mm^2$ ), and the performance is compared against various prior PAM4 and NRZ 54+ Gb/s transceivers in Table II below.

Table 2. 2: Comparison of high-speed transceivers

| and a supplied to the supplied |           |                  |                       |           |                    |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|-----------------------|-----------|--------------------|-------------|

| Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | [19]      | [20]             | [21]                  |           | [22]               | This work   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VLSI'2016 | ISSC'2017        | VSL'2015              |           | ISSCC'2016         | THIS WOLK   |