## **UC Riverside**

### **UC Riverside Electronic Theses and Dissertations**

#### **Title**

Thermal and Power Estimation and Reliability Management for Commercial Multi-Core Processors

#### **Permalink**

https://escholarship.org/uc/item/63r4g0kv

#### **Author**

Zhang, Jinwei

#### **Publication Date**

2023

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA RIVERSIDE

Thermal and Power Estimation and Reliability Management for Commercial Multi-Core Processors

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

by

Jinwei Zhang

March 2023

#### Dissertation Committee:

Dr. Sheldon X-D Tan, Chairperson

Dr. Daniel Wong

Dr. Hyoseung Kim

University of California, Riverside

#### Acknowledgments

This dissertation represents the culmination of work that would not have been possible if I had not received the support, mentorship, and collaboration from numerous individuals. I wish to thank many people who gave me the support, help and assistance, both academically and mentally, throughout the journey of my Ph.D. program.

Firstly, I would like to convey my sincere gratitude to my Ph.D. primary advisor Dr. Sheldon X-D Tan for giving me the precious opportunity to pursue this degree and for all his guidance and support that were invaluable to my work. I would also like to thank my committee members, Dr. Daniel Wong and Dr. Hyoseung Kim, for their insightful and invaluable advice. Additionally, I would like to thank my fellow researchers at the VLSI Systems and Computation Lab (VSCLab) for their collaboration, feedback, and friendship. Namely, I would like to thank Dr. Sheriff Sadiqbatcha, Dr. Liang Chen, Dr. Han Zhou, Dr. Shaoyi Peng, Dr. Zeyu Sun, Wentian Jin, Shuyuan Yu, Jincong Lu, Sachin Sachdeva, Yibo Liu, Subed Lamichhane, Maliha Tasnim, Mohammad Amir Kavousi and Chinmay Raje. In addition to my mentors and colleagues at VSCLab, I would also like to thank a few scholars from other research groups who have contributed to some of my research projects. Namely, Dr. Nanpeng Yu, Dr. Yuanqi Gao, and Dr. An Zou with Washington University in St. Louis. In addition to my mentors and colleagues at UC Riverside, I would like to thank a few additional individuals who have had an enormous impact on my personal and professional life. Namely, I want to thank my parents, Bin and Yunchuan, and my girl friend Xiaohan for their love and encouragement.

The content of this thesis is fully or partially rewritten from these published materials.

Please note that the contents of Chapter 3, which were rewritten from the 5th work in the following

publication list, were contributed equally by Jincong Lu and myself, where I mainly focused on the initial idea of the framework (Section 3.1) and data preparation (Section 3.2), and Jincong Lu focused more on the construction and Training of machine-learning-based model (Section 3.3), and we both have equal contributions to the experiments and results of this work.

- Jinwei Zhang, Sheriff Sadiqbatcha, Wentian Jin and Sheldon X-D Tan, "Accurate Power Density Map Estimation for Commercial Multi-Core Microprocessors," 2020 Design, Automation and Test in Europe Conference and Exhibition (DATE), Grenoble, France, 2020, pp. 1085-1090.

- 2. Jinwei Zhang, Sheriff Sadiqbatcha, Michael O'Dea, Hussam Amrouch and Sheldon X-D Tan, "Full-Chip Power Density and Thermal Map Characterization for Commercial Microprocessors Under Heat Sink Cooling," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 41, no. 5, pp. 1453-1466, May 2022, doi: 10.1109 / TCAD.2021.3088081.

- 3. Jinwei Zhang, Sheriff Sadiqbatcha, Yuanqi Gao, Michael O'Dea, Nanpeng Yu, and Sheldon X-D Tan. 2020. HAT-DRL: Hotspot-Aware Task Mapping for Lifetime Improvement of Multicore System using Deep Reinforcement Learning. In Proceedings of the 2020 ACM/IEEE Workshop on Machine Learning for CAD (MLCAD'20). Association for Computing Machinery, New York, NY, USA, 77-82.

- 4. Jinwei Zhang, Sheriff Sadiqbatcha and Sheldon X-D Tan, "Hot-Trim: Thermal and Reliability Management for Commercial Multi-core Processors Considering Workload Dependent Hot Spots," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2022, doi: 10.1109/TCAD.2022.3216552.

5. Jincong Lu, Jinwei Zhang, Wentian Jin, Sachin Sachdeva, and Sheldon X-D Tan. 2023. Learning Based Spatial Power Characterization and Full-Chip Power Estimation for Commercial TPUs. In Proceedings of the 28th Asia and South Pacific Design Automation Conference (ASPDAC'23). Association for Computing Machinery, New York, NY, USA, 98-103, doi: 10.1145/3566097.3568347. To my parents for all the support.

#### ABSTRACT OF THE DISSERTATION

Thermal and Power Estimation and Reliability Management for Commercial Multi-Core Processors

by

#### Jinwei Zhang

Doctor of Philosophy, Graduate Program in Electrical Engineering University of California, Riverside, March 2023 Dr. Sheldon X-D Tan, Chairperson

Power, thermal and related reliability issues are among the major limiting factors for today's high performance multi-core processors. This is especially true after the breakdown of the

so-called Dennard scaling, since power density starts to increase as IC technology advances. To

enhance reliability, researchers have proposed many power/thermal regulation or dynamic management methods, including clock gating, power gating, dynamic voltage and frequency scaling

(DVFS), and task migration. In this thesis, we present our findings to address the challenges of

post-silicon power and thermal characterization, and dynamic thermal managements for lifetime

reliabilities. We first address the problem of accurate full-chip power and thermal map estimation

for commercial off-the-shelf multi-core processors. The novel scheme is developed to generate

the true 2D power density maps based on the thermal measurements of the processor with backside cooling and facilitated with an advanced infrared (IR) thermal imaging system, the proposed

method achieves both higher resolution and considerable speedup than a recently proposed state-ofart method. Then the second, we propose a novel approach for the real-time estimation of chip-level

spatial power maps for commercial TPU chips based on a machine-learning technique for the first

time. In detail, we achieve estimating the spatial power for commercial TPUs from the hyperparameters of the neural networks (workloads) that are deployed on the TPUs in real-time. Thirdly, processors operating with heat sink cooling remains a challenging problem due to the difficulty in direct measurement. We build an FEM model to reconstruct the full-chip thermal maps for commercial processors while they are under heat sinks. Lastly, based on the spatial power characterization, we propose a new dynamic thermal and reliability management framework via task mapping and migration to improve the thermal performance and lifetime reliability of commercial multi-core processors. Compared to the existing works, the new approach is the first to optimize VLSI reliabilities by exploring workload-dependent power hot spots. The advantages of the proposed method over the Linux baseline task mapping and the temperature-based mapping method are demonstrated and validated on real commercial processors.

# **Contents**

| Li             | List of Figures |                                                               | xiii |

|----------------|-----------------|---------------------------------------------------------------|------|

| List of Tables |                 | xvi                                                           |      |

| 1              | Intr            | oduction                                                      | 1    |

|                | 1.1             | Post-Silicon Full-Chip Power Map Modeling                     | 1    |

|                |                 | 1.1.1 Contributions                                           | 4    |

|                | 1.2             | Full-Chip Power Map Modeling for TPUs                         | 6    |

|                |                 | 1.2.1 Contributions                                           | 8    |

|                | 1.3             | Thermal Characterization Under Heat Sink Cooling              | 8    |

|                |                 | 1.3.1 Contributions                                           | 9    |

|                | 1.4             | Thermal and Reliability Management Considering Hot Spots      | 11   |

|                |                 | 1.4.1 Contributions                                           | 13   |

|                | 1.5             | Organization of This Thesis                                   | 14   |

| 2              | Post            | -Silicon Full-Chip Power Map Modeling                         | 15   |

|                | 2.1             | Related Work and Motivation                                   | 15   |

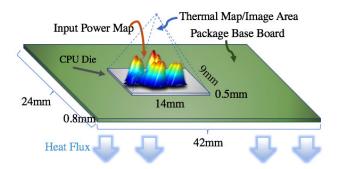

|                | 2.2             | The Power Map Modeling Setup                                  | 18   |

|                |                 | 2.2.1 The Power Density Modeling Framework                    | 18   |

|                |                 | 2.2.2 Thermal Imaging System                                  | 19   |

|                | 2.3             | New Power Density Map Estimation Method                       | 22   |

|                |                 | 2.3.1 Proposed Power Density Map Based on Laplace Operation   | 22   |

|                |                 | 2.3.2 Estimation of Real Thermal Conductivity                 | 26   |

|                |                 | 2.3.3 Thermal Conductivity Estimation for Real Chip Die Area  | 30   |

|                |                 | 2.3.4 FEM Model Architecture to Imitate Real Experiment Setup | 32   |

|                | 2.4             | Experimental Results and Discussions                          | 35   |

|                |                 | 2.4.1 Power Map Estimation and Comparison Results             | 36   |

|                | 2.5             | Summary                                                       | 40   |

| 3              | Pow             | er Estimation for Commercial TPUs                             | 42   |

|                | 3.1             | Power Map Estimation Framework                                | 42   |

|                |                 | 2.1.1 Estimation Flow Occamions                               | 40   |

|   |                | 3.1.2 Thermal IR Imaging System                                      |

|---|----------------|----------------------------------------------------------------------|

|   | 3.2            | Data Preparation and Feature Selection                               |

|   |                | 3.2.1 Offline Power Map Acquisition                                  |

|   |                | 3.2.2 Feature Selection Considering TPU Workloads                    |

|   | 3.3            | CGAN-Based Estimation Model                                          |

|   |                | 3.3.1 Review of CGAN                                                 |

|   |                | 3.3.2 Proposed CGAN-Based Power Estimation Framework                 |

|   | 3.4            | Experimental Results and Discussions                                 |

|   | J. <b>T</b>    | 3.4.1 Validation of the Total Power Consumption                      |

|   |                |                                                                      |

|   |                | ± • • • • • • • • • • • • • • • • • • •                              |

|   | 2.5            | 3.4.3 Computational Efficiency                                       |

|   | 3.5            | Summary                                                              |

| 4 |                | -Chip Thermal Characterization With Heat Sink Cooling 60             |

|   | 4.1            | Identify Exact Locations of On-Chip Thermal Sensors                  |

|   | 4.2            | FEM Thermal Modeling With Heat Sink                                  |

|   | 4.3            | Ensuring the Same Power Density Maps for Both Cooling Conditions 66  |

|   | 4.4            | Application for Different Workloads                                  |

|   | 4.5            | Thermal Map Results Under Real Working Conditions                    |

|   | 4.6            | Summary                                                              |

| 5 | The            | rmal and Reliability Management Considering Hot Spots 76             |

| _ | 5.1            | Related Work                                                         |

|   | 5.2            | Reliability Models                                                   |

|   |                | 5.2.1 EM Model                                                       |

|   |                | 5.2.2 NBTI Model                                                     |

|   |                | 5.2.3 HCI Model                                                      |

|   |                | 5.2.4 Summary of Reliability Models                                  |

|   | 5.3            | Observation and Motivation                                           |

|   |                | 5.3.1 Thermography System Setup                                      |

|   |                | 5.3.2 A Glance of Hot Spots                                          |

|   | 5.4            | Proposed Hotspot-Aware Task Allocation Framework                     |

|   |                | 5.4.1 Learning-Based Hot Spot Modeling and Detection                 |

|   |                | 5.4.2 Task Management Controller                                     |

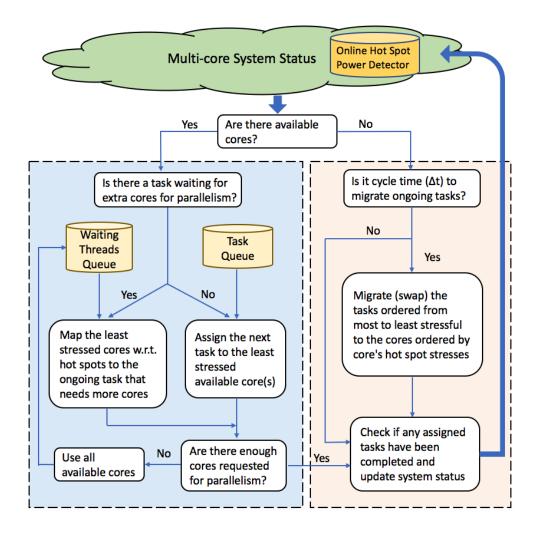

|   |                | 5.4.3 Proposed Mapping Control Algorithm                             |

|   | 5.5            | Experimental Results and Discussions                                 |

|   | 0.0            | 5.5.1 Comparison in System Performance                               |

|   |                | 5.5.2 Thermal and Reliability Improvement                            |

|   | 5.6            | Summary                                                              |

| , | C              | ·                                                                    |

| 6 | <b>Con</b> 6.1 | clusions       115         Post-Silicon Full-Chip Power Map Modeling |

|   | 6.2            | Power Estimation for Commercial TPUs                                 |

|   | 6.3            | Full-Chip Thermal Characterization With Heat Sink Cooling            |

|   | 6.4            | · ·                                                                  |

|   | 0.4            | Thermal and Reliability Management Considering Hot Spots             |

Bibliography 119

# **List of Figures**

| 1.1        | Measured temperature of a hot spot versus the nearest sensor reading                                                                                                                                                                                                | 12       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

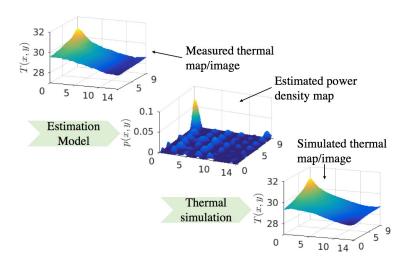

| 2.1        | Framework overview: (a) power modeling flow; (b) power inference flow                                                                                                                                                                                               | 20       |

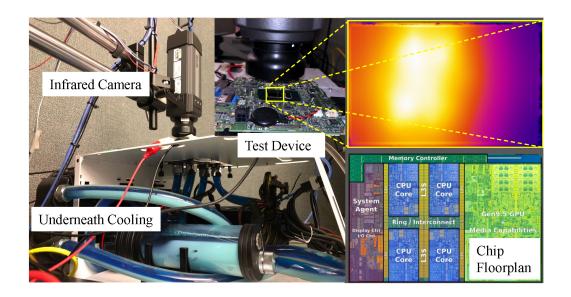

| 2.2        | Thermal imaging system                                                                                                                                                                                                                                              | 21       |

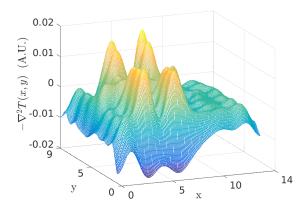

| 2.3        | A negative-Laplacian map (raw power map) example of experimental thermal measurements in 3D view                                                                                                                                                                    | 23       |

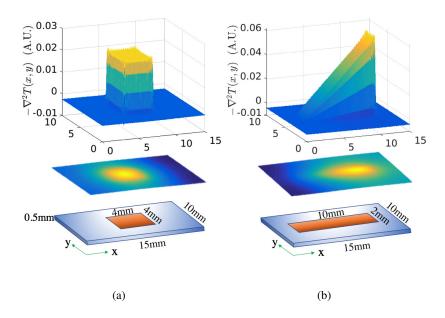

| 2.4        | Simple ideal cases: (a) homogeneous heat source in orange region with total power $3W$ ; (b) linear heat source in orange region $(10 \times 2 \text{mm})$ , with areal power density                                                                               |          |

| 2.5        | $0.05(x-2) \text{ W} \cdot \text{mm}^{-2}$ , $x \in [2, 12]$ and total is 5W                                                                                                                                                                                        | 24       |

|            | power density maps of (a) and (b)                                                                                                                                                                                                                                   | 28       |

| 2.6        | Estimated thermal conductivity of die area with respect to multiple workloads in                                                                                                                                                                                    |          |

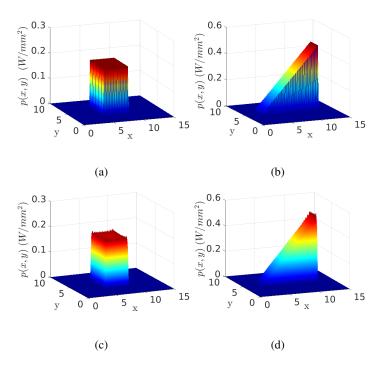

|            | time domain                                                                                                                                                                                                                                                         | 31       |

| 2.7<br>2.8 | Thermal structure created to imitate the real experiment setup Setting proper boundary conditions for thermal simulation model using measure-                                                                                                                       | 33       |

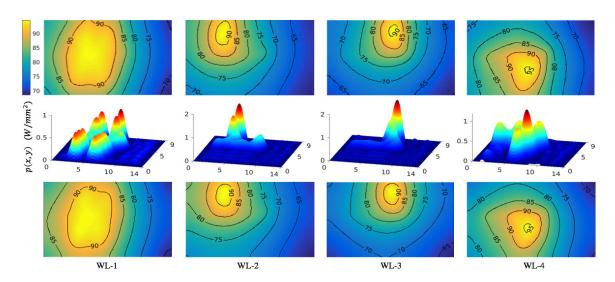

| 2.9        | ments of CPU's idle status                                                                                                                                                                                                                                          | 34       |

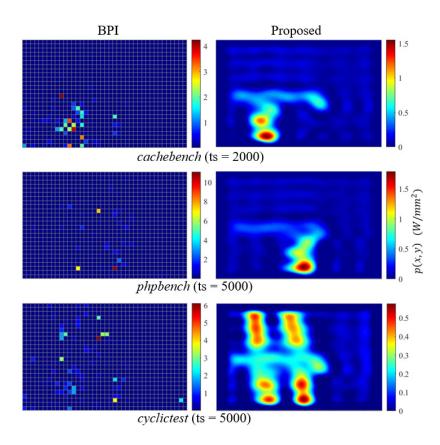

| 2.10       | maps, respectively. Each column is related to one workload at one steady state Comparison of the estimated power maps between the BPI (27×41 resolution) and the proposed method for three benchmarks ( <i>cachebench</i> , <i>phpbench</i> and <i>cyclictest</i> ) | 36       |

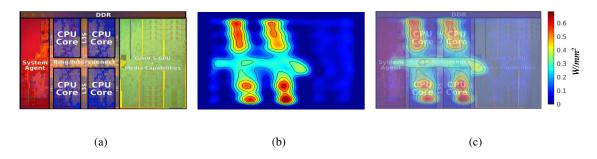

| 2.11       | with respect to a specific time step during their full execution, respectively (a) Intel i7-8650U processor die floor-plan [Wik]; (b) an estimated power density                                                                                                    | 37       |

|            | map; (c) projection of power density map onto the processor die floor-plan                                                                                                                                                                                          | 39       |

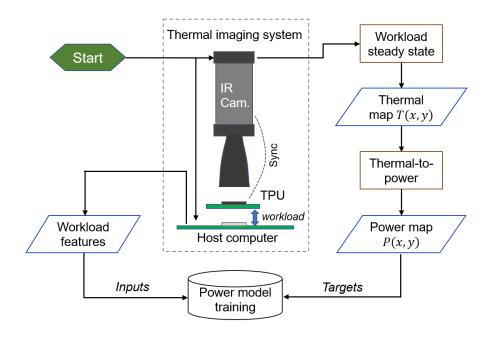

| 3.1        | Framework and data acquisition flow                                                                                                                                                                                                                                 | 43<br>44 |

| 3.3        | TPU module is shown in the blue box                                                                                                                                                                                                                                 | 44       |

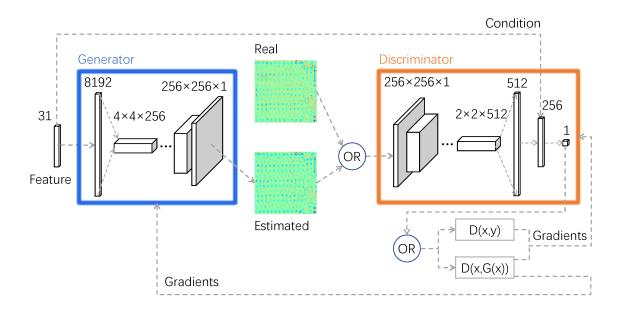

| 3.4        | Architecture of CGAN model                                                                                                                                                                                                                                          | 51       |

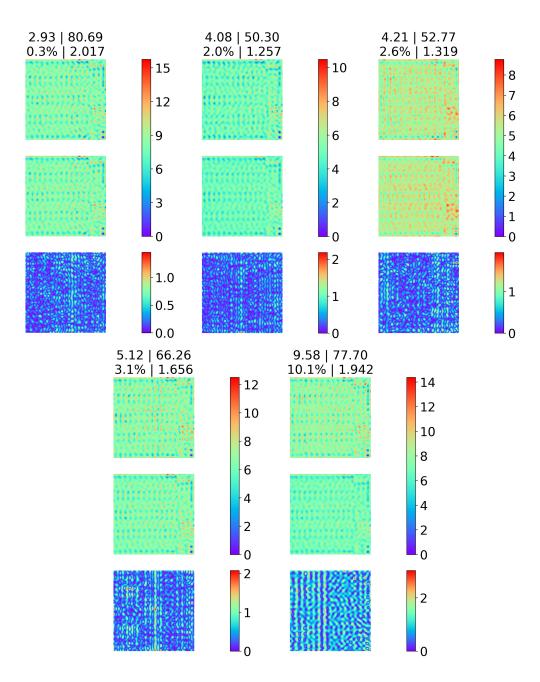

| 3.5  | Measured power maps (row #1), estimated power maps (row #2), and error maps (row #3). The numbers in the first row indicate the <i>Power Density RMSE</i>   <i>Average Power Density</i> (unit: mW/mm <sup>2</sup> ). And numbers in the second row indicate the <i>Total Power Percentage Error</i>   <i>Total Power</i> (unit: W) | 56  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

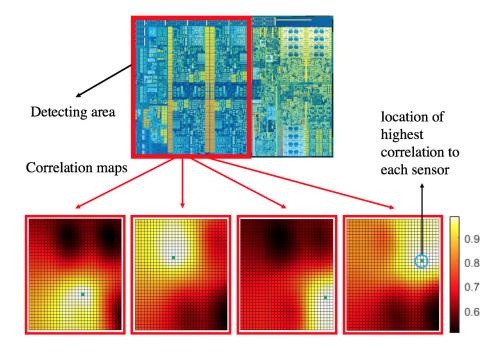

| 4.1  | The correlation between pixel blocks and sensor values of each core. In each correlation map the pixel block that has the highest correlation to the core sensor measurement is marked in green dots, which infers to the on-chip sensor location                                                                                   | 62  |

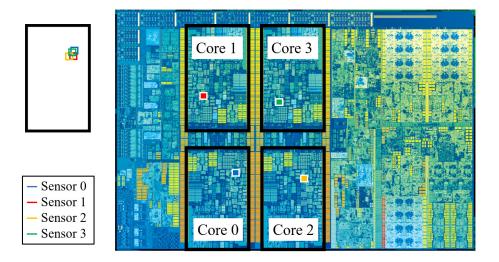

| 4.2  | The sensor locations of CPU cores are identified in colored squares on an Intel i7-8650U quad-core processor [Wik]                                                                                                                                                                                                                  | 63  |

| 4.3  | Processor without heat sink (left) and with heat sink (right)                                                                                                                                                                                                                                                                       | 64  |

| 4.4  | (a) Thermal structure created to imitate the real experiment setup (without heat sink); (b) transparent view of processor area when with heat sink mounted on                                                                                                                                                                       | 64  |

| 4.5  | The computed temperature of processor with heat sink under idle status. The small red boxes mark the on-chip thermal sensor locations.                                                                                                                                                                                              | 66  |

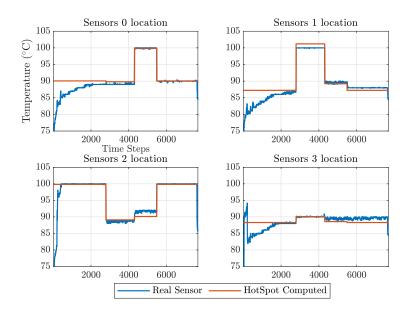

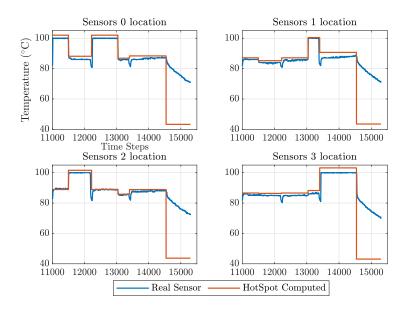

| 4.6  | Thermal sensor values when processor uses the back-side liquid cooling with respect to workloads                                                                                                                                                                                                                                    | 67  |

| 4.7  | Thermal sensor values when processor is mounted with heat sink with respect to workloads                                                                                                                                                                                                                                            | 68  |

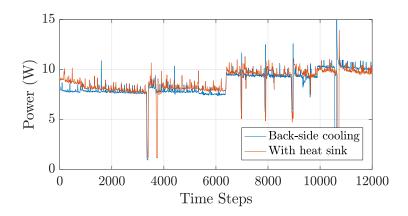

| 4.8  | Total processor power with back-side liquid cooling and with heat sink during the time line                                                                                                                                                                                                                                         | 68  |

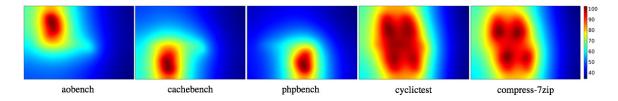

| 4.9  | Full-chip thermal maps of processor under real working conditions with heat sink mounted on with respect to various workloads                                                                                                                                                                                                       | 70  |

| 4.10 | *                                                                                                                                                                                                                                                                                                                                   | /(  |

|      | duration                                                                                                                                                                                                                                                                                                                            | 73  |

| 5.1  | Infrared thermography system                                                                                                                                                                                                                                                                                                        | 82  |

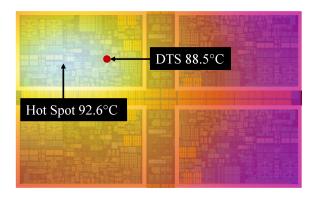

| 5.2  | Measured temperature of a hot spot versus the nearest sensor reading                                                                                                                                                                                                                                                                | 83  |

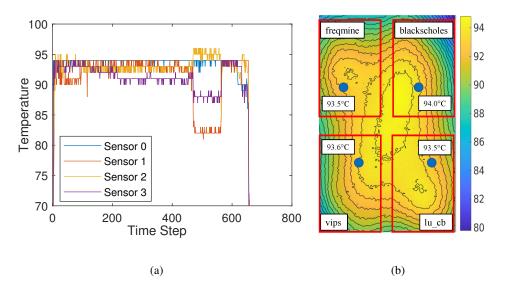

| 5.3  | (a) On-chip sensor readings (one sensor per core). (b) Measured temperature at the                                                                                                                                                                                                                                                  |     |

|      | sensor locations (blue dots).                                                                                                                                                                                                                                                                                                       | 84  |

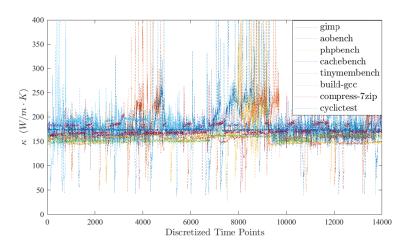

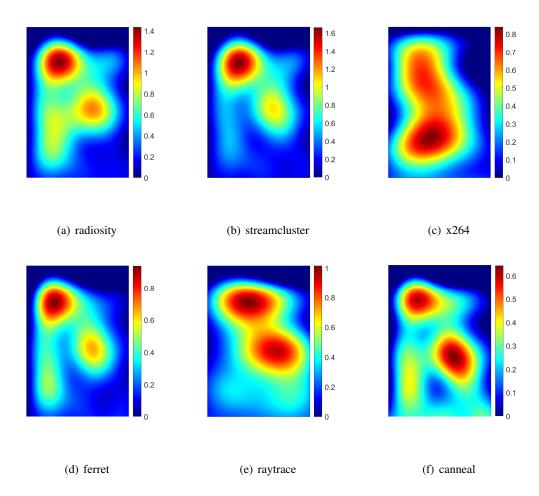

| 5.4  | Power patterns of PARSEC-3.0 and Splash-2 benchmark workloads on a real Intel                                                                                                                                                                                                                                                       |     |

|      | Core-i7 processor at the core scale (within the core)                                                                                                                                                                                                                                                                               | 85  |

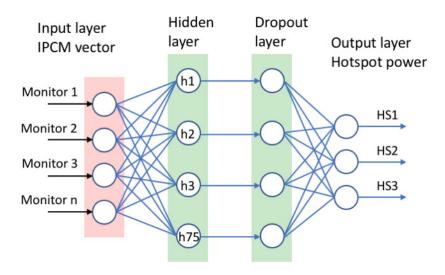

| 5.5  | Power detector network architecture                                                                                                                                                                                                                                                                                                 | 88  |

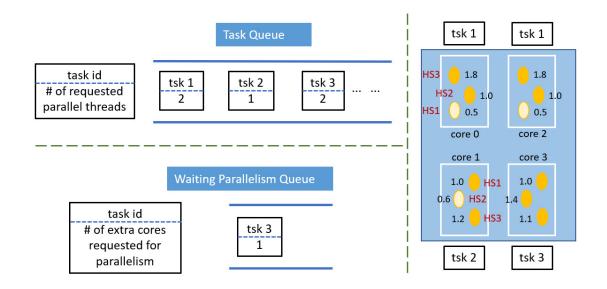

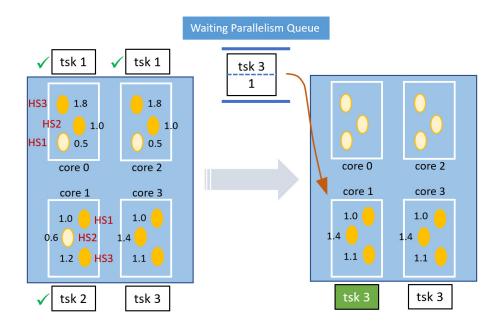

| 5.6  | Example of task queue, waiting thread queue and the initial instant mapping                                                                                                                                                                                                                                                         | 92  |

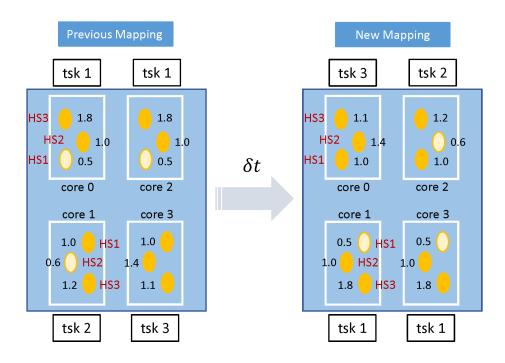

| 5.7  | Task management workflow.                                                                                                                                                                                                                                                                                                           | 93  |

| 5.8  | Task migration in a management cycle                                                                                                                                                                                                                                                                                                | 97  |

| 5.9  | Example of mapping a waiting thread to the available cores                                                                                                                                                                                                                                                                          | 98  |

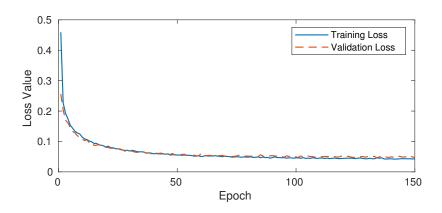

|      | Power density detector neural network learning curves                                                                                                                                                                                                                                                                               | 99  |

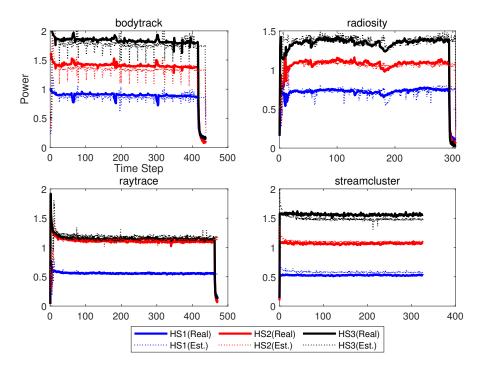

| 5.11 | Power density (W/mm <sup>2</sup> ) V.S. time steps (60 Hz) for workloads. Estimated power                                                                                                                                                                                                                                           | 100 |

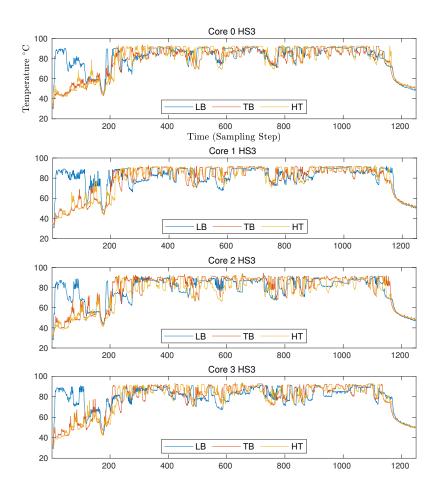

| 5 12 | density compared to the measured power density at the identified hot spots Temperature at the identified true hot spot location HS3 for each core under three                                                                                                                                                                       | 100 |

| 3.12 | manning techniques (Case 4)                                                                                                                                                                                                                                                                                                         | 106 |

| 5.13 | Core frequencies (GHz) V.S. time steps when processor under different mapping        |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | policies: (a) Linux baseline (b) Temperature-based (c) Hot-Trim. Red lines are the   |     |

|      | mean lines of each frequency series (Case 4)                                         | 108 |

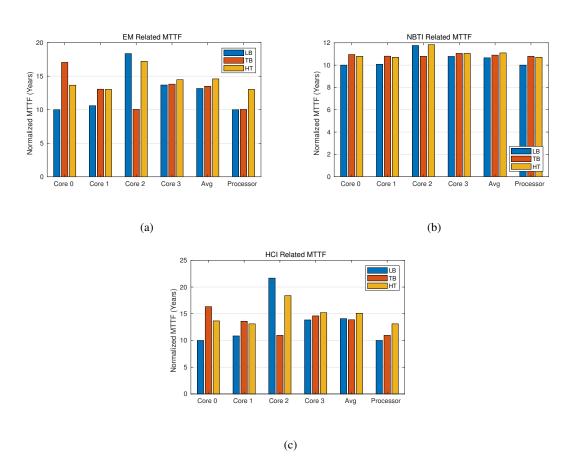

| 5.14 | Normalized MTTF considering (a) EM, (b) NBTI and (c) HCI reliability effects         |     |

|      | regarding test case 4 where task release intervals satisfy $\Delta t \sim U(4,12)$   | 110 |

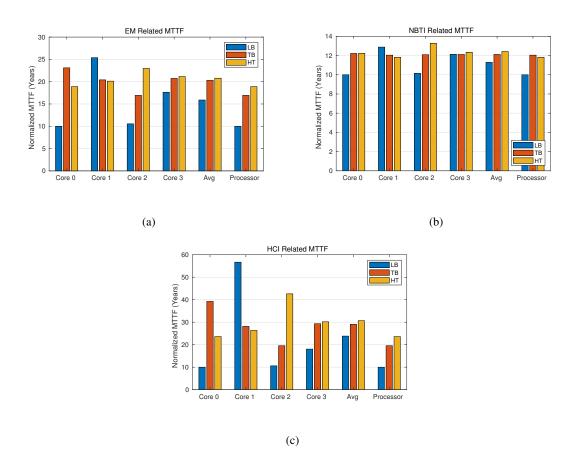

| 5.15 | Normalized MTTF considering (a) EM, (b) NBTI and (c) HCI reliability effects         |     |

|      | regarding test case 5 where task release intervals satisfy $\Delta t \sim U(10, 20)$ | 112 |

## **List of Tables**

| 2.1 | Computational cost comparison for power map estimation                             | 38  |

|-----|------------------------------------------------------------------------------------|-----|

| 2.2 | Estimated power example for processor component (i7-8650U)                         | 39  |

| 3.1 | Selected Workload Features (Coral M.2 TPU, Google Edge)                            | 50  |

| 3.2 | Architecture and Parameters                                                        | 53  |

| 3.3 | Total Power Comparison                                                             | 55  |

| 4.1 | FEM computed temperature at sensor locations VS. real sensor values with heat sink | 71  |

| 5.1 | Average Power Density ( $W/mm^2$ ) at Hot Spots for Various Workloads              | 86  |

| 5.2 | High-level Performance Metrics (Intel PCM)                                         | 89  |

| 5.3 | Exemplary Ordering of Tasks and Cores and Migration                                | 96  |

| 5.4 | Test Cases of Task Series                                                          | 102 |

| 5.5 | Linux V.S. Hot-Trim: Performance and Temperature                                   | 104 |

| 5.6 | Mean of Temperature over Time at the Worst Stressed Hot Spot Location HS3 of       |     |

|     | Each Core                                                                          | 107 |

## **Chapter 1**

## Introduction

## 1.1 Post-Silicon Full-Chip Power Map Modeling

Power, thermal and related reliability issues are among the major limiting factors for to-day's high performance multi-core processors. This is especially true after the breakdown of the so-called Dennard scaling, since power density starts to increase as IC technology advances [EBSA+12, Tay13]. To enhance reliability, researchers have proposed many power/thermal regulation or dynamic management methods, including clock gating, power gating, dynamic voltage and frequency scaling (DVFS), and task migration [BM01, HV14, LTHW15, WMT+16].

However, one important aspect of those works depends on how to correctly estimate the full-chip temperature map. Currently, the on-chip temperature is mainly obtained by performing the thermal analysis based on the run-time functional unit (or component-wise) power estimation of the processor. Estimating component power inputs, however, still remains challenging for commercial off-the-shelf microprocessors.

To obtain accurate on-chip temperature, we need to look at two important aspects of this problem: the accurate estimation of the input power and the accurate calculation of on-chip temperature from the thermal model and the input power.

Traditional power estimation methods focus on the functional unit (component-wise or core-wise) power estimation based on the measured temperature and total power [JM01, IM03, WJY<sup>+</sup>07, DNR13]. But those methods require understanding of the architecture details and functional units of each chip and many approaches are still ad-hoc, involving manual turning. At the same time, post-silicon full-chip power (density) map estimation is also important for power verification and package design. Power map is a 2D spatial distribution of heat dissipation in an IC chip. This problem was also coined as the *inverse thermal map to power map* problem as temperature can be more easily measured either directly or indirectly. Many approaches have been investigated in the past [WFMS09, CNR10, PSSK13, NWR13, BBVB16, RDB18a]. Most of the proposed methods tried to frame the problem as a nonlinear optimization problem (deterministically) or statistically) once the thermal models are known. However, those methods do not work for general off-the-shelf commercial multi-core processors where only core-level power can be obtained [RDB18a]. Many of those only work for specialized silicon such as FPGAs [CNR10, PSSK13, NWR13, RDB18a]. In addition, they suffer from high computing cost and measurement noise although some mitigation techniques have been proposed such as using AC power [NWR13]. Recently, a new heat source identification method based on the measured temperature and 2D spatial Laplace transformation was proposed for general commercial multi-core processors [SZA<sup>+</sup>19], but this is not enough for full-chip power or thermal characterization.

Once we know the power inputs, thermal models are needed to compute the temperature outputs. Many power-based thermal models have been proposed including equivalent thermal RC networks [LVRW95, GW02], architecture level thermal modeling speed up [LLJ<sup>+</sup>06, LTPT09], finite difference based methods, such as HotSpot [HGV<sup>+</sup>06], and finite element based methods (FEM) [GJK<sup>+</sup>08].

Most existing power modeling methods and related thermal models, however, do not work well for commercial multi-core processors as mentioned before. It is even more challenging for modeling of commercial multi-core processors running in the normal working environment with heat sink cooling as it is difficult to directly measure the temperature of the chip's surface. On the other hand, we notice that commercial multi-core processors have many on-chip sensors, for instance, the Intel i7-8650U has one sensor for each core. One can leverage those sensor readings to validate the proposed thermal models. However, the exact locations of these temperature sensors are generally not known, neither provided by the processor's manufacturer.

The obtained full-chip power maps and thermal maps are instrumental for many applications. For instance, once power density maps are obtained, component power can be easily obtained by area integration over the chip layout. The estimated power map also provides many insights into power consumption of different modules, cores and uncore blocks in a microprocessor. Additionally, the power map and thermal maps obtained in real-time can be instrumental in exploring many power/thermal management techniques with various package and cooling solutions.

To mitigate the aforementioned problems, in this work, first, we try to obtain the full-chip power density map from the measured thermal maps/images of the commercial multi-core micro-processor when heat sink is removed. Second, we provide a new methodology to accurately estimate

the thermal map and hot spots of commercial multi-core processors running in the normal working environment with heat sink cooling. The obtained full-chip power and thermal maps under normal heat sink cooling can provide many insightful hot spot information, which can't be obtained by physical sensors and will enable new applications for dynamic thermal/power/reliability management.

#### 1.1.1 Contributions

The specific contributions of Chapter 2 are as follows:

- First, different than all the existing power estimation methods, the new method, based on the first principle of heat transfer, performs a much more efficient 2D spatial Laplace operation on a given thermal map to obtain the so-called *raw* power density map. This consists of both positive and negative values due to the steady-state nature and boundary conditions of the microprocessors. We study two motivation cases to provide many insights into the relationship between raw power density maps and real power density maps. Our work is enabled by an advanced thermal measuring platform with a high-precision thermal camera and a cooling system installed on the back side of the CPU. This allows us to take explicit temperature images (thermal maps) of CPU die while the CPU is under load.

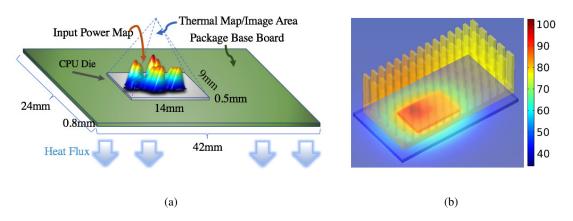

- Then based on the total power of the microprocessor obtained using an online CPU monitoring tool, we develop a novel scheme to generate the true positive-only power density map from the measured raw power density map. At the same time, we develop a novel method to compute effective thermal conductivity of the microprocessor die, which is an important parameter for the subsequent thermal modeling.

- To validate the power density map and the estimated actual effective thermal conductivity of the microprocessors, we construct a thermal model with COMSOL Multiphysics [Mul14]. The model mimics the real experimental setup (without heat sink), with the same boundary conditions used in the IR imaging system. We use the thermal measurements when CPU is in idle status to determine the boundary conditions of the thermal simulation model. Then we use FEM method to compute the thermal map based on the estimated power density map to ensure the computed thermal maps match the measured thermal maps using the FEM method.

- Numerical results show that the proposed power map estimation method is not only more than 100× faster but also more fine-grained than the state-of-art blind power identification (BPI) method [RDB18a].

Experimental results on an Intel i7-8650U 4-core processor with back side cooling technique demonstrate 96% similarity (2D correlation) between the measured thermal maps and the computed thermal maps, which are computed using the estimated power maps and accurately built FEM thermal model.

Chapter 2 is organized as follows. Section 2.1 reviews the existing relevant work. Section 2.2 shows the power modeling framework and IR thermography setup used in this study. Section 2.3 presents the proposed power density map estimation method and the effective thermal conductivity estimation method. Section 2.4 presents the experimental results and comparisons with the current state-of-art method. Section 2.5 summarizes the work of this chapter.

### 1.2 Full-Chip Power Map Modeling for TPUs

With the continuing trend of rapid integration and technology scaling, today's high-performance processors have become more thermally constrained than ever before. An increase in temperature has been shown to exponentially degrade the reliability of the semiconductor chips [ITR03], and hence has become one of the leading concerns in the industry today. To address this trend, runtime power and thermal control schemes are being implemented in most, if not all new generations of processors and are crucial in any modern processor [EBSA+12, Tay13]. However, these control schemes require accurate real-time thermal information, and essentially the power information, ideally the spatial power density map of the entire chip area, in order to be effective [KSH+06, KCS12]. On-chip temperature sensors alone cannot provide the full-chip temperature information since the number of sensors that are typically available is very limited due to their high area and power overheads [SZZ+20b]. Furthermore, power characterization for commercial tensor processors (TPUs) is rarely studied and reported.

To obtain precise thermal and power control, we need to look at two important aspects of this problem: the accurate estimation of the on-chip power and the accurate calculation of temperature from the thermal model and the on-chip power inputs. Traditional power estimation methods focus on the functional unit (component-wise or core-wise) power estimation based on the measured temperature and total power [JM01, IM03, WJY+07, DNR13]. But those methods require an understanding of the architectural details and functional units of each chip and many approaches are still ad-hoc, involving manual turning. At the same time, post-silicon (no prior layout information is needed) spatial power map estimation from thermal information has been widely studied. This problem was also coined as the *inverse thermal map to power map* problem as the temperature can

be more easily measured either directly or indirectly. Many approaches have been investigated in the past [WFMS09, CNR10, PSSK13, NWR13, BBVB16, RDB18a]. Most of the proposed methods tried to frame the problem as a nonlinear optimization problem (deterministically or statistically) once the thermal models are known. However, those methods do not work for general off-the-shelf commercial processors where only core-level power can be obtained [RDB18a]. Many of those methods only work for specialized silicon such as FPGAs [CNR10, PSSK13, NWR13, RDB18a]. Recently, new spatial power map estimation methods based on the measured spatial temperature, 2D spatial Laplace transformation, and processor's performance monitors were proposed for general commercial multicore processors [ZSO+21]. Specifically, the machine-learning based power source hot spot estimation [SZZ+20b] and full chip thermal map estimation [SZAT21] have been proposed. Those methods estimate the hot spot or the full chip thermal maps based on the real-time on-chip performance information such as Intel's Performance Counting Monitor (IPCM) [Int].

However, these methods can hardly be applied to TPUs (like the Google Coral M.2 TPU used in this paper) as there is no real-time utilization information such as IPCM from the TPU chips.

As a result, the existing full-chip power map estimation methods cannot be applied to commercial TPUs.

In Chapter 3, we try to address the aforementioned issues and propose a novel machinelearning based approach to estimate the full-chip power density distribution of commercial TPU chips.

#### 1.2.1 Contributions

The key contributions of this chapter are as follows:

- We developed a generalized full-chip power map estimation method that is based on the hyperparameters of the TPU's workloads (i.e., neural networks inferencing on the TPU), without the knowledge of TPU's performance monitors or supply power.

- We treat the full-chip power density map estimation problem as an image generation problem,

where the input features are given number of hyperparameters and TPU resource information

(generated by the TPU compiler). We propose to use the Conditional Generative Adversarial

Networks (CGAN) to generate such power map images from the given features.

- Experimental results show that the predictions of power maps are quite accurate, with the RMSE of only 4.98mW/mm<sup>2</sup>, or 2.6% of the full-scale error. The speed of deploying the proposed approach on an Intel Core i7-8650U is as fast as 6.9ms, which is suitable for realtime estimation.

Chapter 3 is organized as follows. Section 3.1 shows the power modeling framework and IR thermography setup used in this study. Section 3.2 models the spatial power from the workload features that are available in real time. Section 3.3 describes the architecture of the proposed CGAN-based neural net model for power map estimation. Section 3.4 presents the experimental results and comparisons. Section 3.5 summarizes the work of this chapter.

## 1.3 Thermal Characterization Under Heat Sink Cooling

Most existing power modeling methods and related thermal models, however, do not work well for commercial multi-core processors as mentioned before. It is even more challenging for

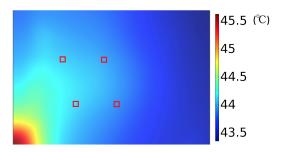

modeling of commercial multi-core processors running in the normal working environment with heat sink cooling as it is difficult to directly measure the temperature of the chip's surface. On the other hand, we notice that commercial multi-core processors have many on-chip sensors, for instance, the Intel i7-8650U has one sensor for each core. One can leverage those sensor readings to validate the proposed thermal models. However, the exact locations of these temperature sensors are generally not known, neither provided by the processor's manufacturer.

To mitigate the aforementioned problems, in Chapter 4, first, we try to obtain the full-chip power density map from the measured thermal maps/images of the commercial multi-core microprocessor when heat sink is removed. Second, we provide a new methodology to accurately estimate the thermal map and hot spots of commercial multi-core processors running in the normal working environment with heat sink cooling. The obtained full-chip power and thermal maps under normal heat sink cooling can provide many insightful hot spot information, which can't be obtained by physical sensors and will enable new applications for dynamic thermal/power/reliability management.

#### 1.3.1 Contributions

In this chapter, we aim to address the aforementioned issues with the novel contributions summarized below:

To develop the thermal models with heat sink cooling, we first try to identify the exact locations of on-chip sensors of commercial multi-core processors based on the correlation analysis of measured thermal map traces and on-chip sensor readings for the first time.

- Next, we construct the second thermal model with COMSOL Multiphysics that mimics the real set up of multi-core processors with heat sinks under real working conditions. The model is validated by ensuring that the computed thermal maps using the estimated power density maps match the temperature values obtained from the real sensors of the chip with heat sink.

We also manage to keep power maps consistent for both the back cooling and heat sink cooling to minimize the leakage impacts on power.

- Numerical results show that the proposed power map estimation method is not only more than 100× faster but also more fine-grained than the state-of-art blind power identification (BPI) method [RDB18a].

Experiments were conducted on an Intel i7-8650U 4-core processor by taking advantage of the power maps obtained in Chapter 2. In detail, FEM simulations with COMSOL Multiphysics [Mul14] were implemented based on such estimated power maps and the accurately built FEM thermal model with heat sink that imitates the real setup. Results show that under the real working condition with heat sink obscured, the average absolute error is only 2.2°C over a 56°C dynamic temperature range and about 3.9% percentage error between the computed thermal maps and the real thermal maps at the sensor locations.

Chapter 4 is organized as follows. Section 4.1 describes the new method to identify the locations of physical thermal sensors of commercial off-the-shelf processors. Section 4.2 presents the FEM architecture that imitates the real working situation when processor is under the heat sink. Section 4.3 details how to ensure the power maps obtained with back-side cooling match the power maps with heat sink cooling. Section 4.4 describes the proposed FEM thermal model with heat sink

can be applied to different workloads once it has been built. Section 4.5 presents the experimental results. Section 4.6 summarizes the work of this chapter.

### 1.4 Thermal and Reliability Management Considering Hot Spots

Power density increases with technology scaling, which can cause severe thermal and reliability problems in high performance multi-core systems [EBSA+12]. Temperature and power has significant impacts on all major long-term reliability effects such as electro-migration (EM) for interconnects, bias-temperature-instability (BTI) and hot-carrier-injection (HCI) for CMOS devices [AvE+14]. As a result, many research works have been investigated to find efficient methods to improve both system performance and reliability via dynamic thermal/reliability management (DTM/DRM) methods, which control the thermal and reliability behavior of multi-core systems by online control such as task migration strategies [CRW07, GMQ10, LFQ12, LTHW15, PMJH20].

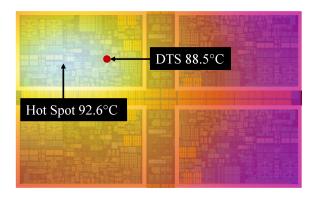

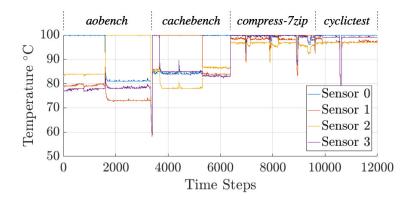

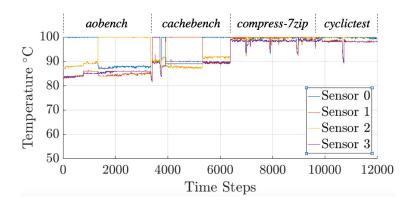

However, existing DTM techniques either using DVFS or task migration are highly dependent on the on-chip location-fixed temperature sensors. Due to high design overheads, currently only a limited number of on-chip digital temperature sensors (DTS) can be allocated on a silicon chip. A recent study shows that the number of hot spots on a typical commercial processor far exceeds the amount of embedded sensors [SZZ<sup>+</sup>20b]. Consequently, thermal and reliability management algorithms that solely depend on the sensors become insufficient for modern multi-core systems, as power and thermal hot spots distinguish within cores under different workloads while having the same sensing temperature.

Figure 1.1: Measured temperature of a hot spot versus the nearest sensor reading

Fig. 1.1 shows a significant temperature difference<sup>1</sup> between a hot spot and the nearest sensor location on an Intel Core i7 quad-core processor under the SPLASH-2 workload *radiosity* (only displaying the quad-core area). Therefore, as the reliability of a core is mainly determined by the thermal hot spots, temperature per-core information alone is insufficient for DTM/DRM techniques. On the other hand, recent studies [RDB18a, ZSJT20] show that one can identify the power density distribution of a multi-core processor with advanced thermal characterization.

Based on this observation, in this article, we introduce a new efficient and scalable task mapping algorithm for the thermal and reliability management for **commercial multi-core processors** via machine learning based modeling for power density at the true hot spots<sup>2</sup>. Our work is facilitated by an advanced thermal imaging system for measuring the spatial temperature across the full processor. Once temperature maps are measured, one can obtain the power density maps (the corresponding heat sources or hot spots) through the thermal-to-power technique using thermal measurements [ZSJT20]. After that, we build a learning-based model for power density at the major hot spots in cores. We remark that the power or hot spot identification for commercial multi-core

<sup>&</sup>lt;sup>1</sup>Temperatures are measured with a calibrated thermal imaging system (see Section 5.3.1).

<sup>&</sup>lt;sup>2</sup>In the paper, hot spot is designated for power density hot spot instead of the traditional thermal hot spot. Power density hot spots are a superset of thermal hot spots and can be viewed as the potential thermal hot spots in general.

processors under different workloads can also be carried out on chips with heat sink cooling in practical work settings [ZSO<sup>+</sup>21].

#### 1.4.1 Contributions

The following summarizes key contributions of this chapter.

- First, we show that the existing task mapping techniques, which solely depend on per-core sensor temperature, may lead to subpar quality solution for chip reliability as the true hot spots of cores can be stressed unevenly.

- Second, based on this observation, we employ a fast, run-time accurate machine learning

model to estimate the exact spatial hot spots from the given workloads. With this, we propose

a scalable and efficient task mapping approach to optimize the reliability of the multi-core

system.

- Third, compared to existing works, the new task mapping approach is the first one to explore the workload-dependent power hot spots and its advantages over the existing Linux task scheduling method and temperature-based method, and has been demonstrated, validated on real commercial multi-core processors. Experiments on a real Intel Core i7 quad-core processor executing PARSEC-3.0 and SPLASH-2 benchmarks show that, compared to the Linux baseline, the core and hot spot temperature can be reduced by 1.15~1.31°C. In addition, Hot-Trim can improve the chip's EM, NBTI and HCI related reliability by 30.2%, 7.0% and 31.1% respectively compared to Linux baseline without any performance degradation. Furthermore, it improves EM and HCI related reliability by 29.6% and 19.6% while further reduces the

temperature by half a degree compared to the conventional temperature-based mapping technique.

This paper is organized as follows: Section 5.1 reviews some related works. Section 5.2 discusses three major reliability effects and their models used in this work. Section 5.3 presents the thermal imaging system setup and a motivation example for this work. Section 5.4 introduces the proposed hot-spot-aware task migration method. Section 5.5 presents the results and comparisons on a real Intel i7 quad-core processor. Section 5.6 summarizes the work of this chapter.

### 1.5 Organization of This Thesis

The rest of this thesis is organized as follows. Chapters 2 and chapter 3 describes the post-silicon full-chip power modeling approach for commercial multi-core processors and commercial TPU chips, respectively. Chapter 4 introduces the full-chip thermal modeling method while the multi-core processor is obscured by a heat sink. Chapter 5 elaborates a dynamic thermal and lifetime reliability management method for commercial multi-core processors. Each chapter begins with related work review or motivation, followed by details of the work and experimental results, and ends with a chapter-specific summary, and the corresponding published paper is indicated in the summary. Finally, chapter 6 summarizes the overall thesis.

## Chapter 2

## **Post-Silicon Full-Chip Power Map**

## **Modeling**

#### 2.1 Related Work and Motivation

Post-silicon power modeling is concerned with finding the powers of functional blocks or power density maps of a whole chip under various workloads. A few existing works have proposed to estimate the component power and the total power of a *real* microprocessor [JM01, IM03, WJY+07, DNR13]. One idea is to tune each component unit power until the summation matches with the total power that is measured experimentally [JM01, IM03]. The main difficulty of those approaches, however, is that searching for component unit power values still remains an ad-hoc approach, which almost always involves manual tuning. Wu *et al.* [WJY+07] tried to mitigate this problem by performing linear regression with K-means method to identify the unique power track patterns from the running programs. Dev *et al.* [DNR13] frames the problem as constrained

optimization problem once the thermal models are obtained from finite element simulation and measurement. Recently an recurrent-neural-network (RNN) based approach has been proposed to quickly estimate the thermal and power hotspots based on the system performance metrics such as Intel's performance counter monitor (IPCM) [SZA<sup>+</sup>19].

At the same time, many post-silicon full-chip power map estimation works have been proposed [WFMS09, CNR10, PSSK13, NWR13, BBVB16, RDB18b]. Most of those proposed methods tried to frame the *inverse thermal to power* problem as the nonlinear optimization problems as follows:

$$\min||M \cdot \mathbf{p} - \mathbf{t}||^2 \tag{2.1}$$

where M represents the steady-state power to temperature map matrix, which is dependent on the specific thermal models used.  $\mathbf{p}$  is a vector that gives the power density at a set of discrete die locations.  $\mathbf{t}$  is a vector of the measured or calculated temperatures at the same locations of corresponding power signals. M can be directly measured from the FPGAs [CNR10, PSSK13, NWR13, RDB18b] or by using some approximation methods such as the power blurring method [WFMS09], or by using pre-defined parameterized analytic forms for a special 3D IC chip along with a parameter regression method [BBVB16]. Reda *et al.* [RDB18b] shows the power estimation for commercial multi-core processors. However, it can only deliver core-wise power information based on total power and core-wise thermal sensor measurement.

Paek *et al.* [PSSK13] added some statistical spins into this problem by computing the maximum likelihood of power **p** given a condition of the thermal map **t**. But it requires an accurate thermal model, i.e. using HotSpot [HGV<sup>+</sup>06] for simulation results to start with for the required accuracy. The author indeed tested the method on a real FPGA chip, but they only achieve 90.7%

accuracy on average. This shows the difficulty in building accurate thermal models for real silicon chips.

In summary, first of all, the existing methods do not work well for off-the shelf commercial multi-core processors as many of them only work for specialized silicon such as FP-GAs [CNR10, PSSK13, NWR13, RDB18b] or special 3D chips [BBVB16]. Second, they suffer from large computing costs as they try to solve nonlinear optimization problems shown in (2.1). Some of those methods also require special regulation items [WFMS09] or scaling or permutations for matrix M [RDB18b] during the optimization to enforce some physics laws, which will lead to more computational costs.

On the other hand, recent study show that the relative power density map can be easily obtained by 2D spatial Laplace transformation of measured or calculated temperature maps based on the first principle of heat conduction [SZA+19, SZZ+20b]. However, there exist several major differences between this work and the published work. Firstly, this work targets a different set of problems: finding the true 2D power density maps of multi-core processors, validating the results via thermal measurements and applying the power maps for thermal map estimation with different cooling configurations and different workloads. The proposed techniques will bring much more useful applications.

Second, the previous two works simply applied Laplace method to obtain the power maps from the thermal maps. However, such power maps, called *raw power maps*, are not physical power density maps since the raw power maps have negative values as shown in Fig. 2.3. Furthermore, the prior works mainly identify a few major heat source locations by locating the local maxima from the raw power maps, whereas this work tries to estimate power density values  $(W \cdot mm^{-2})$  quantitatively

across the full chip. With the full-chip power map, one can further perform the full-chip thermal map estimation for different heat sink cooling configurations. To the best of the authors' knowledge, this is a novel thermal modeling capability achieved for the first time.

### 2.2 The Power Map Modeling Setup

In this section we briefly outline the framework of the proposed approach, thermal imaging system, and necessary data collection from the commercial multi-core processor.

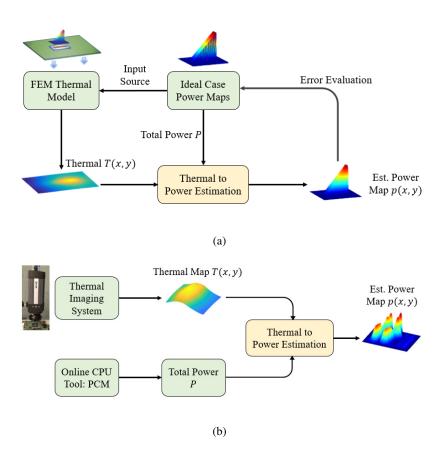

#### 2.2.1 The Power Density Modeling Framework

Power map (surface power density distribution) has tight relationship with the temperature distribution, the Laplace transform of temperature and the thermal conductivity. Our proposed approach involves two kinds of data. The first dataset is the thermal maps of CPU measured through a high-precision thermal camera, which senses the infrared emissions from CPU surface and transforms them into images of temperature distribution. The second is the total CPU power consumption over time, which can be obtained through the processor's Performance Counter Monitor (PCM).

For real processors, as we do not know the exact power density distribution, to verify the estimated power density maps, we compare their corresponding thermal maps. The idea is to build a thermal simulation framework, which mimics the real experimental setup of the chip in the thermal imaging system with similar thermal boundary conditions and thermal structures. Hence, the verification flow of the real chip can be summarized as follows:

- Obtain sufficient number of estimated power maps based on the proposed method. The experimental measurements should include an *idle* status, meaning CPU has extremely low power, which will be used to set boundary conditions.

- 2. Build an FEM thermal simulation model that mimics the real structure of the processor die in the thermal imaging system.

- 3. Substitute the estimated thermal conductivity  $\kappa$  as well as the estimated power map into thermal simulation model as parameters and inputs.

- Examine similarities between the computed thermal maps and the experimentally measured thermal maps. Higher degree of identity indicates higher precision of power map estimation, vice versa.

Fig. 2.1(a) illustrates the *power modeling flow* of the proposed power density map estimation model and evaluates the accuracy of the estimations based on the ideal cases. Fig. 2.1(b) shows the *power inference flow* from data resources to the estimated results for real processors during the run-time.

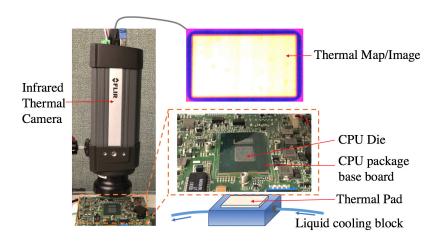

#### 2.2.2 Thermal Imaging System

High precision and resolution of thermal map measurements are critical to the estimation results. One thermal imaging method proposed in [AH15] maximized the explicitness of thermal maps by directly exposing the top surface of CPU die to the camera, while ensuring the CPU's normal thermal condition by cooling it from the back side of the motherboard. Massive heat generated

Figure 2.1: Framework overview: (a) power modeling flow; (b) power inference flow

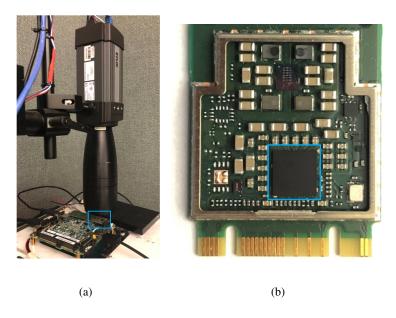

Figure 2.2: Thermal imaging system

from CPU flows downwards through the motherboard into the cooling system, and is dissipated by the quickly circulating coolant.

This work adopts the thermal imaging method proposed in [AH15] where the coolant flow does not contact the chip directly. It uses a Peltier device (electrothermal devices) with soft thermal pads stacked together between the liquid pipe and the back side of motherboard. Further, we take advantage of a high-precision thermal camera installed closely over the CPU die, as shown in Fig. 2.2. The model of our thermal camera is FLIR A325SC ( $240 \times 320$ px images with 16 bit precision and 60 Hz capturing rate). Thanks to a close-up lens, the camera makes temperature difference 50mK clearly visible within as small as  $50\mu$ m/px.

We remark that another thermal imaging system was proposed for power map estimation for commercial processors in [DNR13]. The system uses a transparent silicon window over the surface of the chip and pumps the liquid oil to flow through the window to remove heat from the chip surface directly. After this, FEM method is used to model the setup and generate the power-to-thermal transfer matrix R. Such front-cooling techniques typically require more delicate setup, post

imaging processing and more complicated thermal modeling as the oil based liquid cooling affects the thermal images directly.

# 2.3 New Power Density Map Estimation Method

In this section, we present our new method to estimate the full-chip power density from the real multi-core processors. We start with a simple example, which leads to an important observation for the proposed power map estimation method. Then we will present the approach to compute the thermal conductivity of the real chip, which is a critical parameter for thermal modeling and validation.

#### 2.3.1 Proposed Power Density Map Based on Laplace Operation

Recently Sadiqbatcha *et al.* [SZZ<sup>+</sup>20b] proposed an idea of identifying power sources from thermal maps using Laplace transformation. The work starts from the fundamental heat diffusion equation (2.2), which gives the relationship between temperature and heat generation:

$$\rho C_P \frac{\partial T}{\partial t} - \nabla(\kappa \nabla T) = g \tag{2.2}$$

where T is temperature (K),  $\rho$  is the mass density of the material (kg · m<sup>-3</sup>),  $C_P$  is the mass heat capacity (J · kg<sup>-1</sup> · K<sup>-1</sup>),  $\kappa$  is the thermal conductivity (W · m<sup>-1</sup> · K<sup>-1</sup>) and g is the spatial heat energy generation (W · m<sup>-3</sup>).

When CPU runs into steady state, the transient term can be ignored and equation (2.2) can be simplified as:

$$-\kappa \nabla^2 T = g_T(x, y) \tag{2.3}$$

where  $\nabla^2$  is the Laplace operator. From the simplified heat equation (2.3), we can see that the *negative spatial Laplacian* of the temperature distribution across the die is proportional to the spatial heat generation, i.e., the underlining heat-sources  $g_T(x,y)$ , called the *raw power map*.

This paper distinguishes from the prior work in the way this paper finds the true 2D power density maps  $(p(x,y), \mathrm{W}\cdot\mathrm{mm}^{-2})$  of multi-core processors and validates the results via thermal measurements. Specifically, [SZZ+20b] simply applied Laplace method to obtain the power maps from the thermal maps. However, such power maps, called *raw power maps*, are not physical power density maps as they contain negative values. Negative values are clearly shown in Fig. 2.3. They cannot be explained by CPU power distribution since CPU power will never be negative. Furthermore, the prior work mainly identifies a few major heat source locations by locating the local maxima from the raw power maps without solving for the physical parameter of thermal conductivity  $\kappa$ . However, this paper quantitatively estimates the power density values  $(\mathrm{W}\cdot\mathrm{mm}^{-2})$  across the full chip as well as the thermal conductivity  $\kappa$  of the chip die. This means we are able to learn the spatially continuous heat sources and their actual power densities.

Figure 2.3: A negative-Laplacian map (raw power map) example of experimental thermal measurements in 3D view

Figure 2.4: Simple ideal cases: (a) homogeneous heat source in orange region with total power 3W; (b) linear heat source in orange region  $(10 \times 2 \text{mm})$ , with areal power density  $0.05(x-2) \text{ W} \cdot \text{mm}^{-2}$ ,  $x \in [2, 12]$  and total is 5W.

In order to closely study the relationship between the Laplace transform of temperature and the CPU power distribution, we build a simple ideal case in COMSOL Multiphysics heat transfer tool [Mul14]. This structure contains a rectangular base whose geometric dimension is  $10\times15\times0.5$ mm, and a  $4\times4\times0.5$ mm heat source block embedded in the base, whose total power is set at 3W (0.1875W · mm<sup>-2</sup>) and homogeneous in space (Fig. 2.4(a)). The geometries can be flexible, we set it to approximately match the general size of CPU die and core. The  $\kappa$  of the material of the structure in this case is 400W · m<sup>-1</sup> · K<sup>-1</sup>. For the boundary conditions, a convective heat flux set at 1000W · m<sup>-2</sup>K<sup>-1</sup> is applied to the bottom surface. This convective heat flux mimics the heat dissipation through bottom surface. Ambient temperature is set to room temperature 297K.

As shown in Fig. 2.4(a), it is obvious that the high-rising portion of negative-Laplacian map reflects the area of active power density. Furthermore, we observe that *integration of negative*-

Laplacian map over all the area (pixels) is always zero, no matter how the power setting or geometry changes. The reason is that the thermal map we obtained comes from steady state of the CPU with specific thermal boundary conditions. This means that power generation and power dissipation are balanced in such equilibrium state. The negative power density value actually stands for more power dissipation than generation at the specific location due to thermal transfer and convection process at the boundaries. Where positive value means the opposite. For the very positive high-rising portion, which means the heat generation is significantly larger than the dissipation, typically indicates the hotspots of the chip.

In another example, we have an ideal linear heat source, whose power density increases linearly along the x-axis with total power 5W. Fig. 2.4(b) illustrates the location of power source, power setting and its corresponding negative-Laplacian map. We can observe that the negative-Laplacian in such rectangular power region shows an important linear trend as well, while the surrounding region is negative.

Based on the observations from these examples, we can see that the positive part of the negative-Laplacian map are the region where most of the real power densities are located. In this two simple cases, they cover the 100% real power density distribution. As a result, we can just use the *positive part* of the negative-Laplacian map to represent the estimated power map. Though the actual values of power map in those region are yet to be determined, which will be answered in the following section by calculating the accurate thermal conductivity  $\kappa$ .

## 2.3.2 Estimation of Real Thermal Conductivity

Modern microprocessor die is usually as thin as 0.5mm or below. Thus thermal characteristics along z-axis can be viewed as homogeneous. Power density distribution is only important on the surface x-y plane.

In reality, heat density is a combination of CPU power and heat dissipation by heat sink. Assume the thickness of CPU die is  $\Delta z$ , p(x,y) stands for surface power density (W · mm<sup>-2</sup>) at location (x,y) and  $p_d(x,y)$  denotes heat dissipated locally. Heat density can be expressed as:

$$g_T(x,y) = \frac{p(x,y) - p_d(x,y)}{\Delta z}$$

(2.4)

Then for location (x, y), (2.3) can be rewritten as:

$$-\kappa \nabla^2 T(x,y) = \frac{p(x,y) - p_d(x,y)}{\Delta z}$$

(2.5)

Considering the entire chip, integrate both sides on the whole die area,

$$-\kappa \int \nabla^2 T(x,y) dx dy = \int \frac{p(x,y) - p_d(x,y)}{\Delta z} dx dy$$

(2.6)

Suppose P is total CPU power, and  $P_d$  is total heat dissipation (mainly through convective heat flux), (2.6) can be further written as:

$$-\kappa \int \nabla^2 T(x,y) dx dy = \frac{P - P_d}{\Delta z}$$

(2.7)

At steady state P should be equal to  $P_d$ . This infers the integration on the right hand side of (2.7) would give zero total heat, as CPU power is balanced with heat removal. It also implies the integrated Laplacian should be zero. In fact, this zero result has been observed both in our experiments and aforementioned simulation. Based on the discussion in the previous sub-section,

(2.7) can be approximated as:

$$-\kappa \int_{S_{P}} \nabla^{2} T(x, y) dx dy \approx \frac{P}{\Delta z}$$

(2.8)

$$\kappa \approx \frac{P/\Delta z}{-\int_{S_P} \nabla^2 T(x, y) dx dy}$$

(2.9)

where  $S_P$  indicates area where negative-Laplacian of temperature is positive. Since die thickness  $\Delta z$  is constant, once negative-Laplacian map is obtained from temperature image, the equivalent thermal conductivity  $\kappa$  can be obtained. It basically means that the proportional factor  $\kappa$  can be acquired from dividing total power by thickness and by areal integration of the positive parts of negative-Laplacian. Having this  $\kappa$ , CPU power density map becomes straightforward, which is expressed as:

$$p(x,y) = \begin{cases} \kappa \Delta z [-\nabla^2 T(x,y)], & -\nabla^2 T(x,y) > 0\\ 0, & -\nabla^2 T(x,y) \le 0 \end{cases}$$

(2.10)

Using the above equations to estimate the power map for the homogeneous heat source example and the linear heat source example, the results are shown in Fig. 2.5. Fig. 2.5(c) and Fig. 2.5(d) are the estimated power densities for the two cases, while Fig. 2.5(a) and Fig. 2.5(b) are the corresponding original power density maps. As we can see, some spikes exist at corners in the estimation results due to numerical noise.

To compare the similarity of the two power maps, we introduce 2D correlation coefficient, or simply correlation to evaluate the similarity between the real power map and the estimated power map, which is defined as

$$r = \frac{\sum_{m} \sum_{n} (A_{mn} - \overline{A}) (B_{mn} - \overline{B})}{\sqrt{\left(\sum_{m} \sum_{n} (A_{mn} - \overline{A})^{2}\right) \left(\sum_{m} \sum_{n} (B_{mn} - \overline{B})^{2}\right)}}$$

(2.11)

Figure 2.5: Comparison between estimated power density maps and exact ones for simple ideal examples. (a) and (b) are original power density maps for homogeneous heat source and linear heat source, respectively; (c) and (d) are the corresponding estimated power density maps of (a) and (b).

where  $\overline{A}$  and  $\overline{B}$  are mean of all entries in A and B, respectively. r is a scalar between 0 and 1, the more it approaches 1 the more they look alike. For the above two examples, the correlations of the first and second example are 0.977 and 0.973 respectively. In addition, RMSE of estimated power map on the active powered region is  $0.005 \, \mathrm{W} \cdot \mathrm{mm}^{-2}$  and  $0.015 \, \mathrm{W} \cdot \mathrm{mm}^{-2}$  respectively for the two cases as well. As a result, we can see that the proposed power map estimation method is quite accurate.

The thermal conductivity  $\kappa$  of silicon is about  $130W \cdot m^{-1} \cdot K^{-1}$ , copper is about  $400W \cdot m^{-1} \cdot K^{-1}$ . Due to the mixture of silicon, copper and some other materials in real die, the overall  $\kappa$  could be somewhere around  $130{\sim}400W \cdot m^{-1} \cdot K^{-1}$ . The material in the motivation examples in

simulation has  $\kappa$  of  $400 \text{W} \cdot \text{m}^{-1} \cdot \text{K}^{-1}$ . In our case, the estimated  $\kappa$  by the proposed method is about  $417 \text{W} \cdot \text{m}^{-1} \cdot \text{K}^{-1}$ , about 5% error for the estimation.

One may wonder why the estimation error is 5% for  $\kappa$  based on those ideal simulation cases. There are several reasons. The first is the non-zero thickness of the chip hence the thermal distribution is not perfectly homogeneous along the vertical z-axis of chip die. The second reason is the nature of finite-element method, meaning elements are not infinitely-fine on the object. We can see some glitches on the power map surface. The side surfaces are not absolutely vertical but with a small angle from the vertical plane. Ideally, the sides should be absolutely vertical. Thirdly, a very small part of the low powered area that only has slight power density (e.g., smaller than  $3 \sim 5\%$  of the average power) are computed as zero power because of ignoring the negative values in the raw power map. In reality, the above mentioned extremely low powered area may still show negative Laplacian values due to the heat diffusion behavior, such as vertical diffusion within the chip. To look at the error more closely, we repeat the trials with reduced thickness and the finest mesh structure in FEM in COMSOL for several ideal cases. The  $\kappa$  estimation error could be improved to within  $\pm 1\%$  for ideal homogeneous heat sources (square or rectangle shaped, etc.), and  $0\sim3\%$  for the ideal linear heat source case. Further from this observation, the error is workload dependent due to the aforementioned third reason. As we see, the error is different for ideal cases. One consideration is the linear heat source case has more errors happening at the border of heat source, where there is a small part of places at the border with positive power are still shown as negative values in the simulation setup and hence are zeroed out. In another words, the proposed  $\kappa$ approximation method is not perfect but is a reasonable estimation.

Therefore, we have verified the approach of estimating the power map in simulations. Moreover, the estimated power density maps sufficiently match the original power setting. We further note that the estimation error for  $\kappa$  can be smaller or equal to 5% from the simple ideal cases. However, it is difficult to know the true accuracy since we do not know the actual  $\kappa$  for the commercial chips.

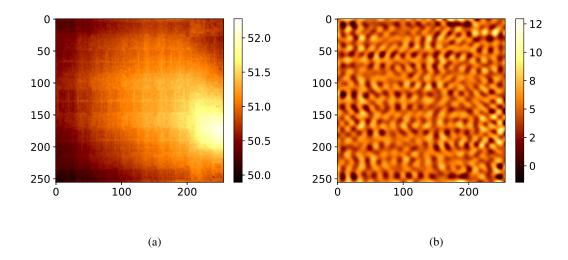

### 2.3.3 Thermal Conductivity Estimation for Real Chip Die Area

Another important parameter for the thermal model is the thermal conductivity of the chip. Based on the power map model derived in Sec. 2.3.2, we show in this section how to estimate the equivalent thermal conductivity  $\kappa$  of the die from the measurement of thermal maps.

For our work, the total power of CPU is also needed. Intel Performance Counter Monitor (PCM) provides users a software interface that estimates the internal resource utilization of the latest Intel core processors. One metric of the PCM dataset is CPU energy consumption between two accesses. To ensure precision, power data has to be synchronized with the thermal maps. As mentioned in the system setup, if the capturing frequency of infrared camera is f, PCM data should be recorded in this same frequency. Suppose the CPU energy along discretized time points is series E, then total power  $P = E/\Delta t$  is also a time series, and  $\Delta t = 1/f$ .