# UC Santa Barbara

**UC Santa Barbara Electronic Theses and Dissertations**

# Title

Novel Circuits and Systems with Analog-Grade Memories

# Permalink

https://escholarship.org/uc/item/66527063

Author Mahmoodi, Mohammad Reza

# Publication Date 2021

Peer reviewed|Thesis/dissertation

# UNIVERSITY OF CALIFORNIA

Santa Barbara

Novel Circuits and Systems with Analog-Grade Memories

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

M. Reza Mahmoodi

Committee in charge: Professor Dmitri Strukov, Chair Professor Tim Sherwood Professor James Buckwalter Professor Li-C Wang

June 2021

The dissertation of M. Reza Mahmoodi is approved.

Tim Sherwood

James Buckwalter

Li-C Wang

Dmitri Strukov, Committee Chair

March 2021

Novel Circuits and Systems with Analog-Grade Memories

Copyright © 2021

By

M. Reza Mahmoodi

Dedicated to you.

#### ACKNOWLEDGEMENTS

There are no words to truly describe the depth of my gratitude toward my advisor, Dmitri Strukov. Thanks for the unlimited support, guidance, supervision, and inspiration that still wakes me up early in the morning and keeps me up late at night. Thank you for setting an example of excellence as a researcher, academic, and human being, and thank you for taking a chance on me. Your unapproachable high standard and outstanding work ethic will drive me forever. I owe you big time.

I thank my friend, colleague, wife, and partner in crime, Zahra Fahimi, who never deserted me in this expatriate life. Thanks for pushing to the limits and for keeping up with my constant nonsense philosophies. Many thanks also go to the past and present labmates, including Dr. Hussein Nili, Dr. Mohammad Bavandpour, Dr. Michael Klachko, Dr. Xinjie Guo, Dr. Adrien Vincnet, and Dr. Mirko Prezioso. I learned a lot from you guys and inherited a fortune of experience and information. Thank you for creating a nutritious environment in the lab. I also appreciate the brilliant collaborators I was lucky to work with: the inspiring Prof. Lanza, Dr. Omid Kavehi, Prof. V. Polishchuk, my friends in Applied Materials Inc., M. Graziano, and Irina Kataeva.

I am also so thankful to DARPA, BAE, NSF, SRC, Applied Materials, and all the funding agencies which financially supported me during these years. Thank you, Brook and Shan Byers, and thank you, IEE. Your support made a lot of difference.

I thank my parents, Ezollah and Faterme; my sisters, Safien and Batoul; and my brothers, Mohsen, Alireza, and Saeed. I am everything I am because you loved me.

# VITA OF M. REZA MAHMOODI March 2021

# Education

Bachelor of Science in Electrical Engineering, Isfahan University of Technology, 2012. Master of Science in Electronics, Isfahan University of Technology, 2015. Doctor of Philosophy in Electronics, University of California, Santa Barbara, March 2021 (expected).

Selected Publications<sup>1</sup>

**M. R. Mahmoodi**, Prezioso, D.B. Strukov. Versatile stochastic dot product circuits based on nonvolatile memories for high performance neurocomputing and neurooptimization, *Nature Communications* **4**, 1-10, (2019).

M. Prezioso\*, M. R. Mahmoodi\*, *et al.* Spike-timing-dependent plasticity learning of coincidence detection with passively integrated memristive circuits, *Nature Communications* 9, 1-8 (2018).

H. Nili, G. C. Adam, B. Hoskins, M. Prezioso, J. Kim, **M. R. Mahmoodi**, F. Merrikh Bayat, O. Kavehei, and D. B. Strukov. Hardware-intrinsic security primitives enabled by analogue state and nonlinear conductance variations in integrated memristors, *Nature Electronics* **1**, 197-202 (2018).

S. Chen, **M. R. Mahmoodi**, *et al.* Wafer-scale integration of two-dimensional materials in high-density memristive crossbar arrays for artificial neural networks, *Nature Electronics* **3**, 638-645 (2020).

H. Kim\*, **M. R. Mahmoodi**\*, H. Nili\*, D. Strukov. 4K-memristor analog-grade passive crossbar circuit, *arXiv preprint arXiv:1906.12045* (2019).

**M. R. Mahmoodi**\*, Z. Fahimi\*, H. Nili, Valentin Polishchuk, D. B. Strukov. Combinatorial Optimization by Weight Annealing in Memristive Hopfield Networks, *Nature Scientific Reports*, (2021).

Awards

IEE Excellence in Research Fellowship Recipient (2018-2019).

<sup>&</sup>lt;sup>1</sup> See https://scholar.google.com/citations?user=ATd-RqUAAAAJ&hl=en&oi=ao for a full list of publications.

### ABSTRACT

#### Novel Circuits and Systems with Analog-Grade Memories

by

### M. Reza Mahmoodi

The neural computation field had finally delivered on its promises in 2013 when the University of Toronto group reported a deep neural network that outperformed other machine learning approaches in image classification accuracy. That breakthrough was not due to algorithmic advances but rather the availability of high-performance graphical processors that enabled large-scale neural network modeling. Since then, the biologically-inspired neural network algorithms have become state-of-the-art approaches in many artificial intelligence tasks, and the future progress in this field hinges on even more powerful hardware. Such hardware, however, is unlikely to be implemented with the conventional digital circuit technology, whose performance seems to be saturating due to the faltering Moore's law.

On the other hand, further opportunities are presented by neuromorphic hardware that mimics critical features of biological neural networks, most importantly analog in-memory computing, in an attempt to match their energy-efficiency. Most importantly, neuromorphic hardware takes advantage of the physical-level analog implementation of vector-by-matrix multiplication (VMM), which is the most frequent operation in any neural network. The key component of such a circuit is a nanodevice with adjustable conductance —essentially an analog nonvolatile memory—used at each crosspoint of a crossbar array and mimicking the biological synapse. Prior work showed that analog VMM circuits based on redesigned eFlash memories and metal-oxide memristors, the most promising analog memory device technologies for neuromorphic computing, are much more energy-efficient as compared to the digital counterpart implemented in similar process node and performing a similar function.

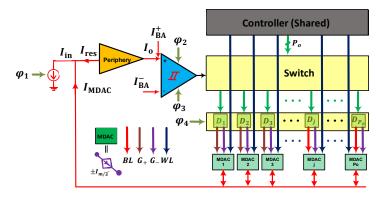

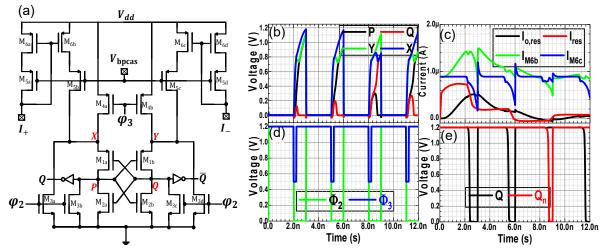

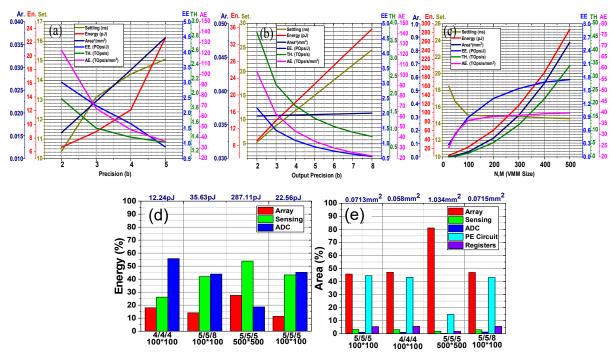

The main goal of this dissertation is to advance neuromorphic circuits based on memristors and eFlash memories on several fronts. The first part of the thesis is devoted to improving functional and physical performance of analog-domain vector-by-matrix multiplication with a specific focus on neuromorphic inference applications, including the development of novel programming algorithms, mitigation approaches for various device and circuit non-idealities, and design of efficient peripheral circuits. For example, we use novel programming algorithms to experimentally demonstrate <4% relative tuning error in a 64x64 passively integrated crossbar circuit despite significant variations, with 25% normalized standard deviation in device I-V characteristics. The developed post-fabrication methods for mitigating IR drops, I-V static nonlinearity, and device variations enable software-equivalent accuracy for the largescale neural networks for the studied memristor technology. The efficacy of novel peripheral circuits is verified via SPICE modeling, which shows, e.g., POp/J-scale energy-efficiency for current-mode 55-nm NOR-flash memory circuits. The section is concluded with the discussion of our ongoing work on the design and fabrication of several large-scale neuromorphic chips.

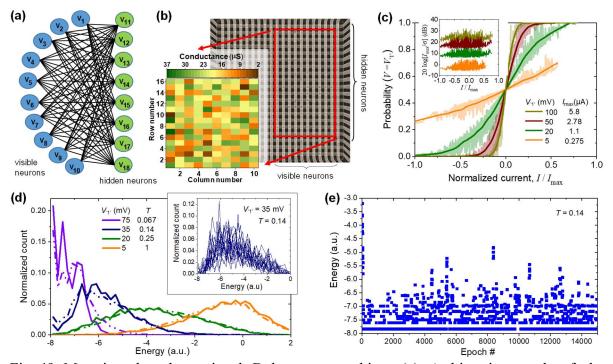

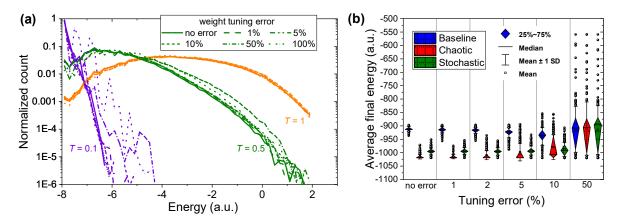

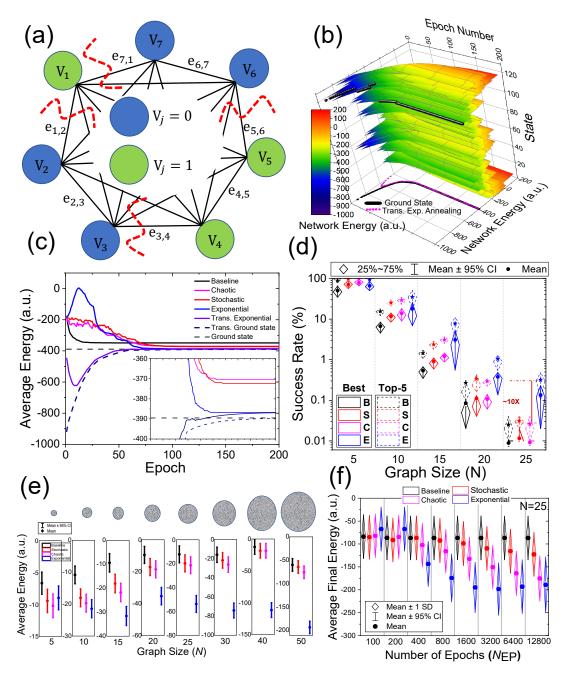

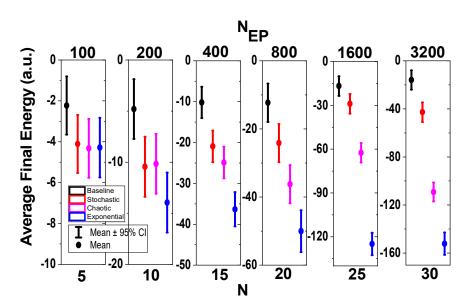

The second part of this thesis extends the work on analog VMM circuits to enable the implementation of more advanced probabilistic neuromorphic hardware, which is especially effective in solving combinatorial optimization problems. By operating the previously developed analog VMM circuit in a lower signal-to-noise-ratio regime, we achieve stochastic VMM functionality and utilize such circuits to prototype small-scale restricted Boltzmann

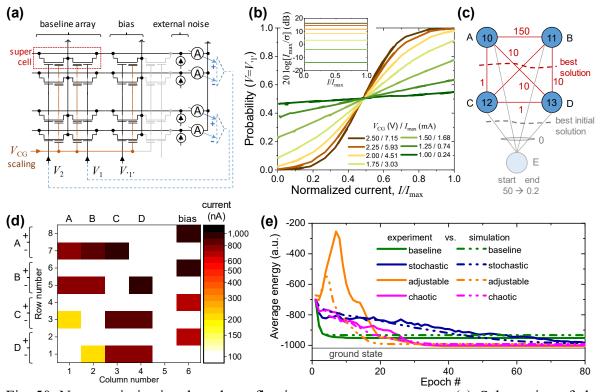

machine and Hopfield neural network with runtime-controlled effective temperature. Furthermore, we suggest several novel hardware-friendly annealing approaches and successfully verify them by solving experimentally typical combinatorial optimization problems.

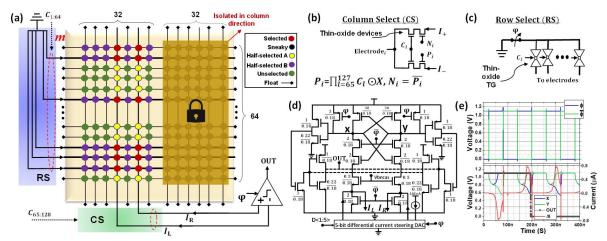

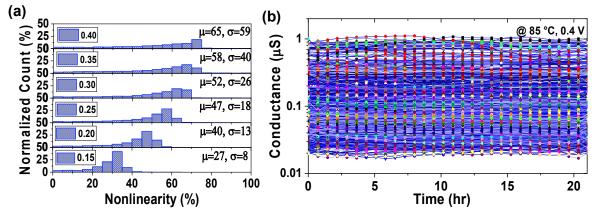

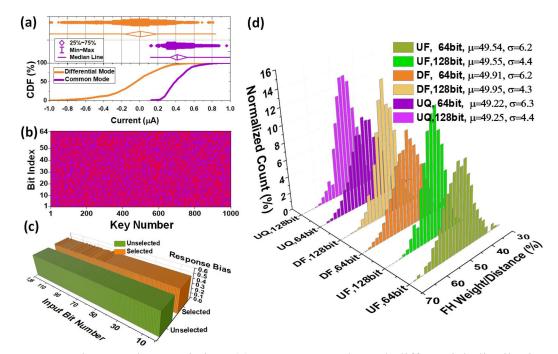

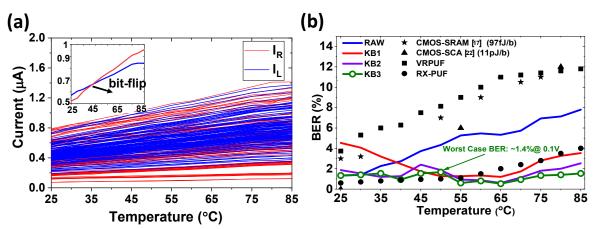

The last part of this dissertation is devoted to hardware security primitives, such as physically unclonable functions and true random number generators. At the core of our idea are analog circuits based on metal-oxide memristors and eFlash memories, which are very similar to analog VMMs developed for neuromorphic computing. The main difference is that memory device non-idealities, e.g., randomness in tuning and memory *I-V* variations, are utilized as a rich source of static entropy, which is essential for implementing hardware security primitives. We developed three architectures - RX-PUF and VR-PUF that avoid the need for conductance tuning procedure in previously proposed memristor-based PUFs, and ChipSecure, which exploits variations in leakage current, subthreshold slope, nonlinearity, and stochastic tuning error in eFlash memory arrays to create a unique digital fingerprint. The key novelties of the proposed designs include enormous challenge-response pairs to enable strong PUF properties and a low-overhead key-booking scheme to dramatically improve the PUF reliability across a wide temperature range of operation. The analysis of the measured data in all our PUF demonstrations shows strong resilience against machine learning attacks.

| 1.   | Introduction                                      |                                                           |     |  |  |

|------|---------------------------------------------------|-----------------------------------------------------------|-----|--|--|

|      | 1.1. N                                            | Motivation                                                | 1   |  |  |

|      | 1.2. Background and Significance                  |                                                           |     |  |  |

| 2.   | Analog Computing with Memory Devices              |                                                           |     |  |  |

|      | 2.1.                                              | Introduction                                              | 17  |  |  |

|      | 2.2.                                              | Developing Large-scale Uniform Passive Crossbars          | 22  |  |  |

|      | 2.3.                                              | The role of Uniformity in Passive Memristive Circuits     | 44  |  |  |

|      | 2.4.                                              | IR-drop and Nonlinearity Analysis in Memristive Circuits  | 69  |  |  |

|      | 2.5.                                              | Low-Power Sensing Circuit for Current-Mode VMMs           | 82  |  |  |

|      | 2.6.                                              | Low-Power Mixed-Signal VMM Design                         | 95  |  |  |

|      | 2.7.                                              | Designing DNN Inference Accelerators                      | 103 |  |  |

|      | 2.8.                                              | A Novel Temperature Compensated Current reference         | 111 |  |  |

|      | 2.9.                                              | Design of A General-Purpose Characterization Setup        | 120 |  |  |

|      | 2.10.                                             | Summary and Future Works                                  | 122 |  |  |

| 3.   | Neuromorphic Computing with Analog-Grade Memories |                                                           |     |  |  |

|      | 3.1.                                              | Introduction                                              | 128 |  |  |

|      | 3.2.                                              | Neurocomputing and Neurooptimization with Analog Memories | 132 |  |  |

| 3. N | 3.3.                                              | Weight Annealing in Memristive Hopfield Networks          | 150 |  |  |

|      | 3.4.                                              | Mixed-Signal Neurooptimization with Adaptable Annealing   | 170 |  |  |

|      | 3.5.                                              | Summary and Future Works                                  | 176 |  |  |

| 4.   | Hardware Security Primitives with Analog Memories |                                                           |     |  |  |

|      | 4.1.                                              | Introduction                                              | 180 |  |  |

# TABLE OF CONTENTS

| 4.2.       | RX-PUF                   | 190 |  |  |

|------------|--------------------------|-----|--|--|

| 4.3.       | Ultra-Low Power VRPUF    | 193 |  |  |

| 4.4.       | Low BER VRPUF            | 199 |  |  |

| 4.5.       | ChipSecure Design        | 205 |  |  |

| 4.6.       | Summary and Future Works | 218 |  |  |

| References |                          |     |  |  |

# 1. Introduction

# 1.1. Motivation

The field of neural computation has had its highs and lows in the last three decades. Still, the huge milestone happened only recently: high-performance graphical processors and the availability of massive labeled datasets enabled the development of deep neural networks (DNNs) that exhibit superior performance in various pattern recognition tasks [1]. The progress is still ongoing: breakthroughs in algorithms are fueled by increasingly powerful hardware accelerators, processors, and aggressively scaled custom digital circuits. Unsurprisingly, further progress hinges on the use of more efficient hardware as well. Biological systems have played an undeniable role in this progress and have served as a massive inspiration for building intelligent systems. Yet, even advanced digital neural networks fail to compete with them in terms of performance. The human brain outperforms artificial systems in many tasks, e.g., it can recognize an intricate object in an image faster while consuming orders of magnitude less energy [2]. The main reason stems from the fact that using digital operations to mimic noisy redundant biological systems is inherently natural. In other words, this efficiency gap originates from the use of elementary physical phenomena as computational primitives and the analog representation of information in biosystems [3] the observation that initiated the field of neuromorphic engineering [4].

A tremendous body of research predicts analog neuromorphic networks could bridge the gap between artificial and biological prototypes [5-7] and offer comparable areal density to biological prototypes at a better processing time. The background for this improvement is the physical level implementation of the vector-by-matrix multiplication (VMM), the frequent

operation in neuromorphic networks, and the efficient realization of an analog synapse capable of both holding a learnable parameter (or weight) and performing useful computations.

One key challenge in achieving the promised excellent performance is developing a technology that offers reliable analog-grade programmability and can be easily integrated with CMOS. In general, a promising synaptic device should offer several primary features: 1) long-term retention, that is, the device should hold the stored information for a reasonable time period, 2) high endurance, that is, the device should be reprogrammable for a reasonable amount of time, 3) analog-storage, that is, the device should be able to store the parameters with reasonable accuracy, 4) low-power operation, that is, the energy consumption needed to access and perform the computation on the device should be reasonably low, 5) compact footprint, that is, the device should be scalable and dense to ensure a large number of synapses can be integrated within a single chip with minimum parasitics and high-speed access time.

In every neuromorphic network, there are many infrequent operations that standalone synaptic devices cannot implement, and in some cases, they are very inefficient to do so. Fortunately, the mature CMOS technology is extremely flexible and can efficiently implement various functionalities. The second challenge is designing efficient peripheral circuits in CMOS technology that perform and implement less frequent and sparser functionalities of these systems.

Besides accelerating deep neural networks, addressing these challenges would be a significant milestone in implementing other neuromorphic tasks, such as Boltzmann machines [8], spiking neural networks [9,10], Hopfield neural networks [9,11,12], reinforcement learning [13], etc., all of which have been proven to be very efficient when implemented with

analog-grade nonvolatile memories (NVMs). Further, integrated circuits based on analog memories are promising for designing very efficient security primitives such as physically unclonable functions [13] and random number generators [15], as they offer extra sources of randomness and functionalities in far better densities than purely-CMOS circuits.

The recent development of continuous-state nonvolatile memory synapses is perhaps a milestone that paves the way for efficiently building these systems [16]. The most notable device candidates that excel in primary features are metal-oxide passive memristors [17] and redesigned eFlash memories. In this Ph.D. thesis, we focus on developing these technologies and harnessing them for designing novel circuits and systems targeting neuromorphic applications and hardware security. Our study spans different design levels, from developing nonvolatile memory technologies, addressing their reliability issues, studying their scaling prospects, to designing energy-efficient and high-speed peripheral circuits and using them for building large-scale integrated neuromorphic networks and hardware security primitives.

The remainder of this chapter focuses on background works. Chapter 2 reviews various devices and topologies for building the basic building block of neuromorphic computing systems, i.e., VMMs. Then, we report our results on the successful fabrication of large-scale passively-integrated memristive crossbars. The study is followed by an in-depth analysis of the role of uniformity, IR drop, and nonlinearity in 0T1R (transistorless) memristive circuits. Then, we propose two circuit techniques for developing a low-power peripheral circuit, leading to a high-speed and energy-efficient current-mode VMM design. Finally, we introduce three large-scale integrated inference engines: a 6-layer convolutional neural network and a 3-layer multilayer perceptron (MLP) based on eFlash memories in 55 nm

CMOS, and a massive general-purpose accelerator engine based on 1T1R (1 transistor + 1 resistor) memories.

Chapter 3 is devoted to neuromorphic computing systems and circuits, in which we show the efficient design of restricted Boltzmann machines, Hopfield neural networks, and various annealing techniques for solving combinatorial optimization problems. Finally, in chapter 4, we discuss multiple successful demonstrations of strong physical unclonable function circuits and hardware security primitives based on resistive memories and redesigned eFlash arrays.

# 1.2. Background and Significance

#### 1.2.1. Devices

The principles of analog computing date back to half a century ago [3,18,19]. Up until recently, such devices were implemented mostly as "synaptic transistors" [7], fabricated in some double-poly CMOS technologies. Several sophisticated analog computing systems were proposed using these devices [20]. However, these devices have relatively large areas, leading to sparse implementation and large interconnect parasitics. An efficient realization of analog computing is enabled only recently, with the emergence of novel analog-grade nonvolatile memories that implement VMM operation using the fundamental Ohm and Kirchhoff laws. Among different candidates [21], the resistive switching memories, including phase change [22], conductive bridge memories [23], and metal-oxide memristors [24,25], are promising candidates. These synaptic devices are implemented in 0T1R [24] and 1T1R [25] topologies. In comparison with 1T1R, the fabrication and upscaling of 0T1R arrays are more challenging, in part due to the large uniformity requirements in 0T1R arrays, which explains few experimental demonstrations of these circuits. In a uniform 0T1R technology, the devices

have a tight distribution of switching thresholds, which leads to minimum half-select disturbance in the crossbar, facilitating individual tuning of the devices. In 1T1R technology, this requirement is waived due to the presence of the selector in each memory cell. However, this comes at the cost of dramatic density reduction. In addition, the 0T1R technology offers 3-dimensional integration [26], which is not feasible in 1T1R memories.

The high prospective integration density of passive memristive crossbar circuits, enabled by both aggressive lateral feature scaling and vertical monolithic integration, would be essential for hardware implementations of large neural network models, such as those used for the end-to-end automatic speech recognition, natural language translation, and text summarization, on a single chip without having to perform very energy-taxing and slow data transfer with the off-chip memory. For example, the largest multilingual neural model for automatic translation among seven common languages contains 640 million parameters [27]. The functional performance of the transformer networks, the state-of-the-art models for text summarization, dramatically improves with the scale of the network, e.g., almost linearly improving when increasing the number of parameters in GPT-2 model from few hundreds to ten billion [28]. Furthermore, mixture-of-expert networks with up to 137 billion parameters have been recently suggested to improve the functional performance of language modeling [29].

Storing that many parameters on-chip could hardly be accommodated with planar embedded memory technologies. Earlier work showed that memory devices in the generalpurpose neuromorphic computing chips could occupy up to 25% of the total area, with the remaining area devoted to memory array peripheral circuits and other functions [16]. The memory efficiency would be naturally higher, and hence memory density is more important in more-specialized circuits, e.g., large-scale models that do not rely on weight sharing. In fact, our crude estimates show that even with largely suboptimal (higher) cell currents, memory efficiency is above 10% for neuromorphic inference accelerators with 100M+ weights. At the same time, though the complexity of the mentioned above large-scale neural networks might reduce with further improvements in algorithms, it is clear that extremely large models will still be useful. This can be indirectly evidenced by the complexity of the human brain, which, with its  $\sim 10^{15}$  synapses, can serve as a proxy for the complexity of the future highly cognitive neuromorphic systems [30].

While the most promising synaptic device option for realizing neuromorphic systems are analog-grade (i.e., multi-bit) devices, low-precision (e.g., binary weight) neural network models have also received significant attention [31,32,33]. However, it seems that understanding and dealing with the impact of reduced weight and computing precisions is still a very active area of research. For example, though little or no loss in accuracy can be achieved when using binary weights for some of the earlier (very redundant) deep convolutional networks, such as AlexNet or VGG, 4 to 8 bits of precision for both weights and activations might be necessary for the most advanced image classifiers [34]. A related observation is that the accuracy loss can often be recovered by increasing the network depth or width [35,36], which, however, naturally results in decreased physical performance. Therefore, the prospects for lowering precision in the neural network, which might enable using simpler binary resistive random access memory (ReRAM) devices, can only be understood by considering both functional and physical performances at the system level [37].

The main advantages of using passively integrated metal-oxide memristors [24,26,38] are their superior density and lower fabrication cost [29]. In fact, due to excellent scaling prospects and analog properties, vertically integrated ReRAMs might challenge much slower 3D NAND memories in effective density to enable human-brain-scale integrated electronics. The progress in developing passive ReRAM technology is still ongoing, and the technology is still in need of improvement.

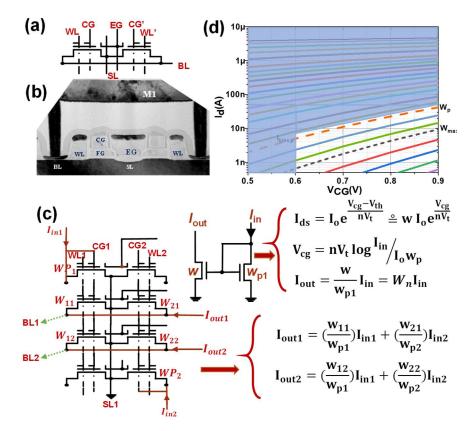

Another perfect candidate is commercially available eFlash memory technology from Silicon Storage Technology (SST) Inc. This technology has been successfully scaled down to 28 nm and is embedded in many standard CMOS foundries and processes [39]. However, the baseline floating-gate technology is designed for digital NOR flash memory applications and does not allow setting a precise analog state of each cell, necessary for analog applications. Recent work from our group has shown that redesigning the routings in the cells mitigates the half-select disturbance in these arrays and allows their high-precision tuning [40,41]. Such redesigning has increased the cell area by  $\sim$ ×3 but has enabled analog tuning capability in the devices. The main advantage of this technology is their mature, CMOS-compatible fabrication technology and their high-precision capability, which is offered in a density of only  $\sim$ 100  $F^2$ /cell.

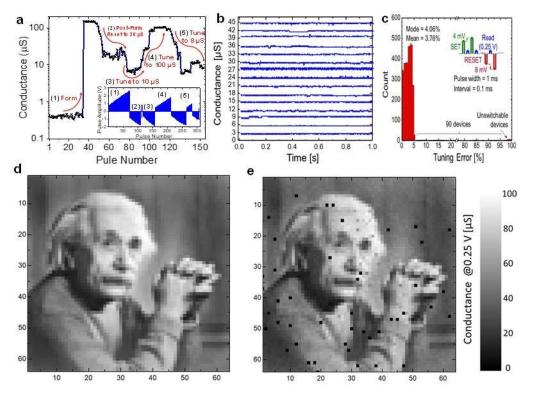

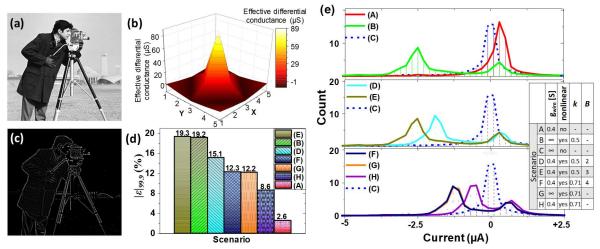

Chapter 2 studies and qualitatively compares various topologies and device candidates for implementing dot-product operation in the mixed-signal domain. Then, we demonstrate a  $64 \times 64$  passive crossbar circuit with ~ 99% functional nonvolatile metal-oxide memristors featuring etch-down patterning and low-temperature budget (hence conducive to vertical monolithic integration) based on a foundry-compatible fabrication process. Most importantly, the achieved device uniformity, < 26% coefficient of variance in memristor switching voltages, is sufficient for programming a 4K-pixel gray-scale pattern with a smaller than 4% relative tuning error on average. Chapter 2 also reports the results of an in-depth analysis of uniformity in passive memristive circuits and investigates how it impacts the computing accuracy of analog memristive circuits.

#### 1.2.2. Circuits and Systems

#### a) Neurooptimization and Annealing Hardware

The enormous computational power required to solve large-scale optimization problems poses a great challenge for their efficient implementation. Hence, hardware accelerators, e.g., based on superconductors [45], CMOS circuits [46], nanomagnetic devices [47], and photonic technologies [48]. These circuits employ annealing techniques such as CMOS annealing [46], quantum [45], stochastic [49], and chaotic annealing [50] to boost performance.

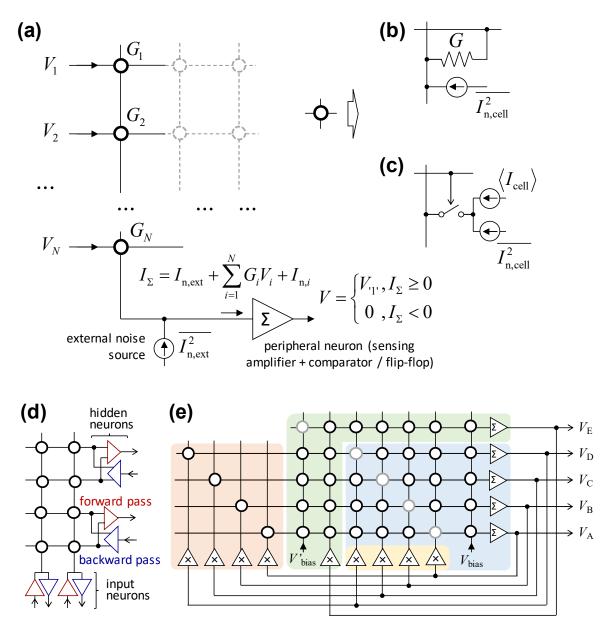

The stochastic dot-product computation is the most common operation performed during inference and training in the Boltzmann machine and simulated annealing. Hence, its efficient hardware realization is of utmost importance. Even with a relatively large synapse to neuron ratio (~1,000) and deterministic dot-product functionality, the neuron circuitry might constitute a substantial part of the neuromorphic inference systems. Because of such concerns, purely CMOS implementations, see, e.g., CMOS probabilistic gates [51] and CMOS-based Ising chip for combinatorial optimization problems [46], may not be very practicable. CMOS annealing may require a random number generator, reports low area efficiency (1.225  $\mu$ m<sup>2</sup>/4spins in 40 nm), and has many constraints (e.g., weights must be binary). Quantum computing systems, on the other hand, are yet to be explored more, e.g., to achieve scalability, overcome the challenges of operation at room temperature and at the presence of environmental noise.

Recent progress in developing analog-grade NVMs has created exciting opportunities for the experimental realization of Hopfield networks and annealing machines. This, in part, stems from the fact that the implementation overhead of stochastic functionality might be less of a problem for some memory devices, in which switching between memory states is inherently stochastic. Ferromagnetic [52,53], phase-change [54,55], ionic [56,57] and thermally-driven metal-oxide [12], and solid-state electrolyte devices [58,59] are the recent proposed candidates to implement stochastic functionality. Ref. [60] uses discrete Pt/TiO<sub>2-x</sub>/Pt memristive devices to implement a small-scale 4-bit data converter with the Hopfield model. Ref. [61] implements a 3-bit associative memory using digital HfO<sub>2</sub> memristors. In Ref. 12, simulation results demonstrate the effectiveness of using the inherent chaos in sub-100 nm NbO<sub>2</sub> memristors to implement simulated annealing within Hopfield networks. Ref. [8] shows an 18-node restricted Boltzmann machine (generalized Hopfield network) and a 4-node graph partitioning problem based on a versatile stochastic dot-product engine using TiO<sub>2</sub> memristive crossbars. Ref. [62] uses Y-flash memories to implement a 3-bit associative memory.

Unfortunately, many of such devices come with other severe challenges. For instance, an efficient implementation of large-scale dot-product computation is a major challenge for magnetic devices. The hybrid option of combining magnetic stochastic neurons with the already mentioned mixed-signal dot-products is not appealing because the interface typically compromises an extreme energy efficiency of spin-based computing with charge-based devices. The technology of magnetic devices is also relatively immature, judging by very few (and rather low-complexity) experimental demonstrations [60,61]. The biggest challenge for the remaining devices would be low switching endurance and cycle-to-cycle and device-to-device variations in switching characteristics.

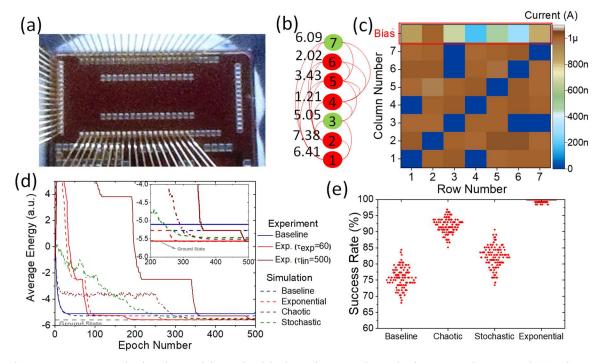

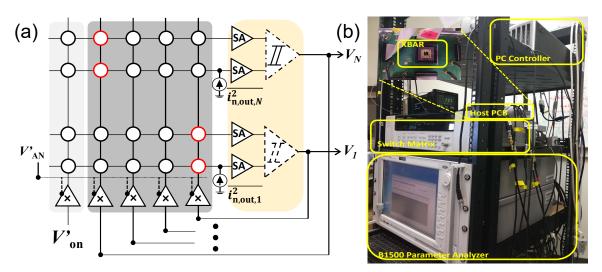

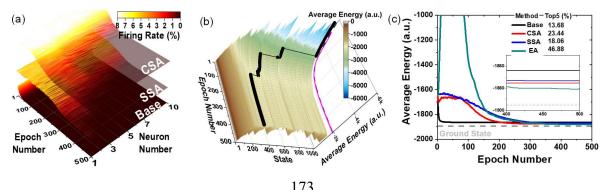

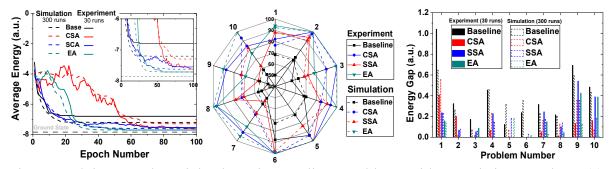

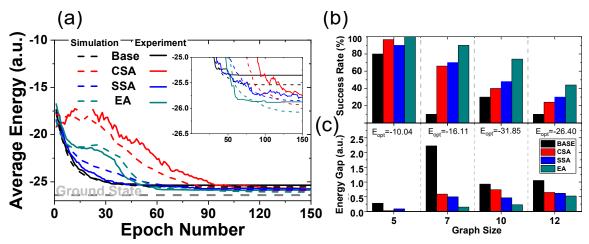

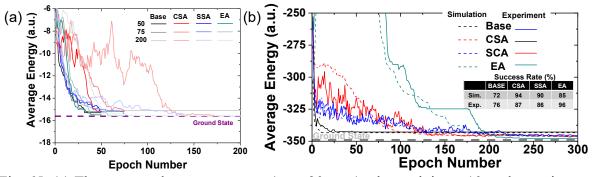

Chapter 3 discusses our approach for addressing these limitations through novel circuits and algorithms for implementing restricted Boltzmann machine (RBM) and Hopfield networks. We experimentally demonstrate hardware implementation of a 10×12 RBM, simulated annealing, chaotic annealing, and novel weight annealing, using crossbars of analog NVMs.

#### b) MLP and Deep Neural Network Accelerators

The vast majority of the proposed neuromorphic accelerators from industry and academia are digital [63-65]—see also extensive review in Ref. [66]. The most natural approaches, however, are based on analog and mixed-signal circuits. The majority of accelerators based on analog memories have been theoretical (for a list of these architectures and their pros and cons, see the supplementary information in our recent work [67]). Several works also utilize binary ReRAM for building neural network accelerators. Ref. [68] uses a 1 Mb 1T1R array in a 65 nm process to perform the binary dot-product operation in <16 ns. Panasonic [69] also developed a 2 Mb 1T1R ReRAM array for implementing a huge MLP, which surprisingly achieves only ~94% on MNIST.

Few works also use the more interesting analog resistive memories. The first perceptron was implemented based on a very uniform  $12 \times 12$  0T1R crossbar array to classify  $3 \times 3$  binary images [24]. The second generation of UCSB's crossbars were  $20 \times 20$ , which were used to implement an MLP network [17]. Ref. [25] demonstrates in-situ training techniques of perceptron networks based on very sparse  $128 \times 64$  1T1R arrays. The largest ReRAM-based demo is presented in [69], which includes board-level integration of 8  $128 \times 16$  100  $\mu$ m<sup>2</sup> 1T1R devices, and is used for the implementation of a convolutional neural network.

A milestone in the field of neural computation also happened recently, when an MLP image classifier with  $<1 \ \mu$ s inference time and  $<20 \ n$ J inference energy was demonstrated using redesigned 180 nm embedded eFlash memories [70]. This chip offers 10<sup>6</sup> better energy-

delay in comparison with IBM's TrueNorth [71]. More importantly, the results have been reproducible, reliable, and temperature insensitive.

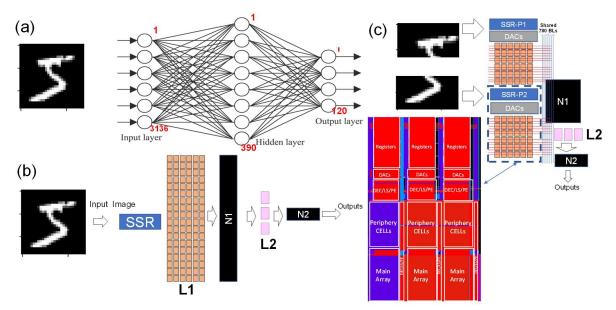

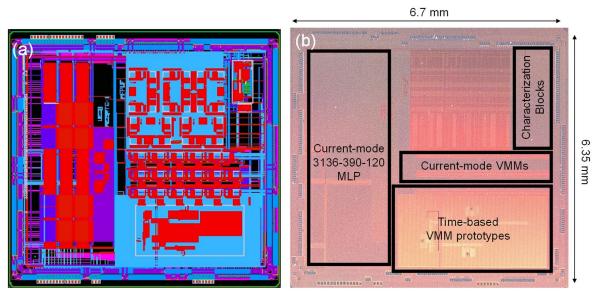

Section 2.7 discusses the design and fabrication of two large-scale eFlash-based neuromorphic networks based on 55 nm eFlash memories and a general-purpose neuromorphic network fabricated in 65 nm CMOS, including  $>25 \times 10^6$  analog 1T1R devices.

# c) Hardware Security Primitives

Physical unclonable functions (PUFs) are crypto primitives that leverage the intrinsic (nanoscopic physical) variations of a system to generate unclonable secrets. Hence, PUF circuits generate a unique response even if they are similar by design and layout. They are typically classified as weak and strong based on security performance [72,73]. The former is used to generate and store secret keys and feature a relatively small access-restricted CRP space. For a weak PUF, a complete mapping function can be deduced by observing a limited number of CRPs. Strong PUFs, on the other hand, are used for authentication applications, and a complex mapping behavior is constructed by incorporating many nonlinear random components. Strong PUFs have a large CRP space and are unpredictable and resilient toward modeling attacks.

When it comes to designing PUFs, NVMs offer various advantages over conventional CMOS devices, not just due to their superior scalability prospects but because of reconfigurability and low-cost local computing capability. Besides, stochastic switching in NVMs is a rich entropy source. Such properties have been recently leveraged in building novel promising security primitive circuits. Reconfigurability could be useful when the end-user needs a new key. This is when the original one has been revealed, or the ownership is revoked or updated. Analog-grade NVMs offer potentially better security prospects considering local

computing capabilities such as nonlinear characteristics and multi-bit storage capacities. On the other hand, retaining the stored information during power shut down, NVMs may pose additional challenges to data protection [74]. In Ref. [73], we have reviewed experimental demonstrations of NVM-based security primitives. Let us mention few seminal papers in this area.

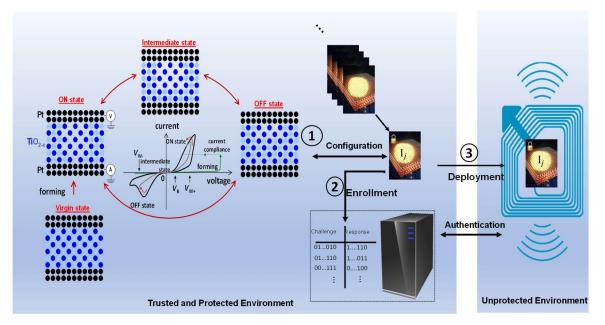

The security primitive proposed in [75] is the first demonstration that takes advantage of variations in the nonlinear *I-V* characteristics of passive memristors for building PUF. This feature is enabled by the capability of analog tuning of device conductance to maximize the security of the PUF. A CMOS-compatible 3D stack of monolithically integrated 10×10 TiO<sub>2</sub> memristors was used as a proof of concept to demonstrate this potential of memristors in cryptography. This work has been extended in [76] and introduced as RX-PUF (Resistive-XOR PUF). In the configuration phase, the 20×20 crossbar array with passively integrated 250 nm half-pitch devices has been programmed using a Gaussian distribution of conductances. It is showed that the devices in the tails of the distribution could weakly bias the responses, and a simple circuit technique is proposed to tackle this issue. The preliminary results showed high resiliency against machine learning attacks.

X-point PUF [77] is another design that begins with resetting all devices in a cross and then applying a single pulse to all the devices to program them to random states. The resultant conductance distribution is widely distributed between  $10^{-10}$  to  $10^{-5}$  S. Hence, the highly conductive devices, even if not unselected, would bias and determine the responses. X-point PUF achieves ~46% average Hamming distance on a  $12 \times 12$  and has demonstrated good aging characteristics. Note that when the response is determined by a few devices, the responses remain unchanged as long as they retain their states.

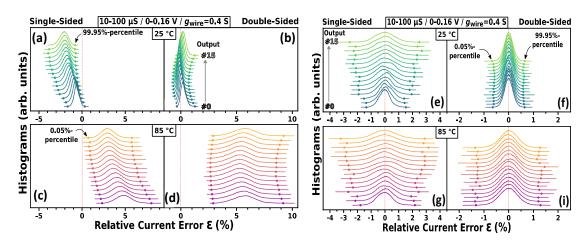

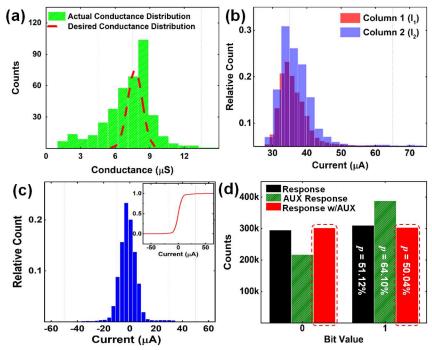

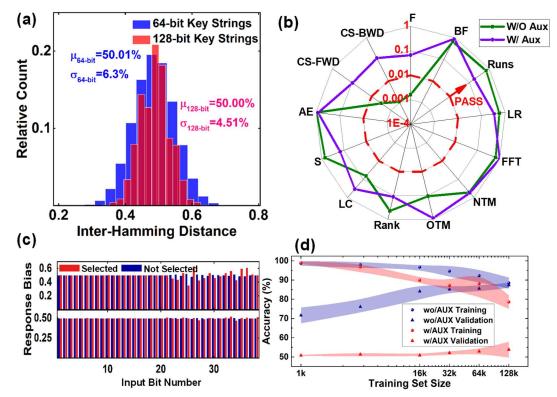

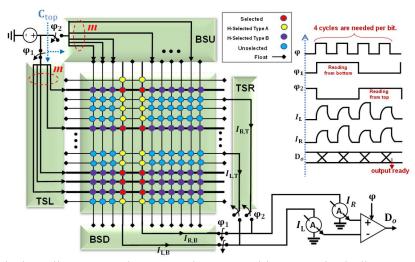

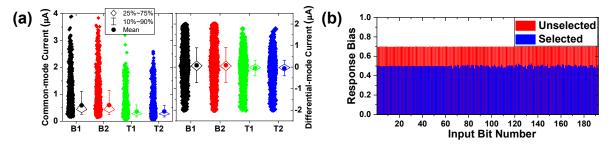

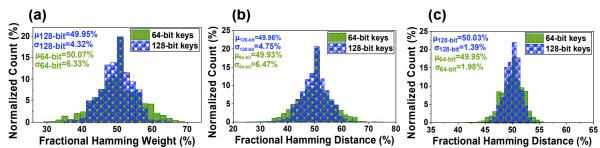

Chapter 4 discusses our findings and experimental results of designing security primitives with NVMs. We show how the analog tuning and nonlinear conductance variations of memristors can be used to build a fundamental building block for implementing physically unclonable functions that are resilient, dense, fast, and energy-efficient. Using two vertically integrated  $10 \times 10$  metal-oxide memristive crossbar circuits, we experimentally demonstrate a security primitive that offers a near-ideal functional performance. We present a novel architecture, called VRPUF, and prototype it using unformed 4K-ReRAM passive crossbar circuits. The architecture utilizes intrinsic process variations in crossbar circuits, manifested as variations in device I-V nonlinearities and the leakage currents, and allows for a huge (~10<sup>25</sup>) number of challenge-response pairs (CRPs). The VRPUF design does not require forming/ programming crosspoint devices, which simplifies peripheral circuits, leading to  $\sim$  $4 \times$  better density compared to the architectures which rely on switching the states of ReRAM devices. Moreover, uniform IVs of the virgin-state devices, coupled with lower conductance and stronger static nonlinearity, allow for  $\sim 100 \times$  improvement in power consumption and more robust security metrics. To boost the PUF's robustness, we propose a key-booking scheme, which dramatically improves reliability across a wide temperature range of operation and further increases PUF circuit density by reducing error-correcting overheads. Finally, introduce ChipSecure, a PUF architecture based on eFlash memories that exploit randomness in static *I-V* characteristics and reconfigurability of embedded flash memories to design efficient physically unclonable function.

# 2. Analog Computing with Memory Devices

Analog-grade nonvolatile memories, such as those based on floating-gate transistor [78,79], phase-change [80-82], ferroelectric [83,84], magnetic [85], solid-state electrolyte [86-89], organic [90,91], and metal-oxide [24,31,32,92,93] materials, are enabling components for mixed-signal circuits implementing vector-by-matrix multiplication, which is the most common operation in any artificial neural network. Most importantly, such circuits allow for physical-level in-memory computations in the analog domain using the fundamental Ohm and Kirchhoff laws, thus enabling dramatically higher energy and area efficiency in comparison with digital solutions.

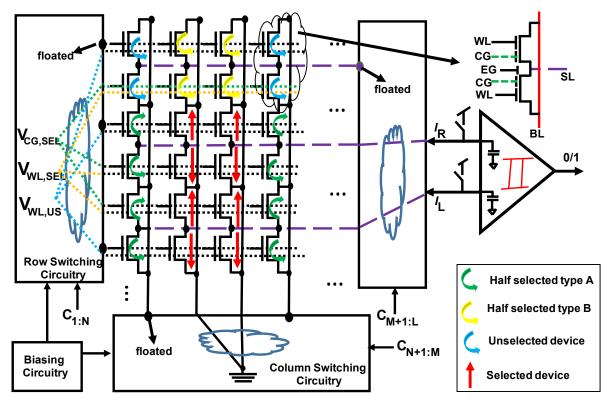

This chapter first studies and qualitatively compares various topologies and device candidates for implementing dot-product operation in the mixed-signal domain. A brief review of major analog synaptic device candidates, i.e., 0T1R and 1T1R memristors and eFlash memories, is provided, and VMM topologies such as time-based, current-mode, and switch capacitor multiplier are analyzed from the perspectives of precision, speed, and energy efficiency.

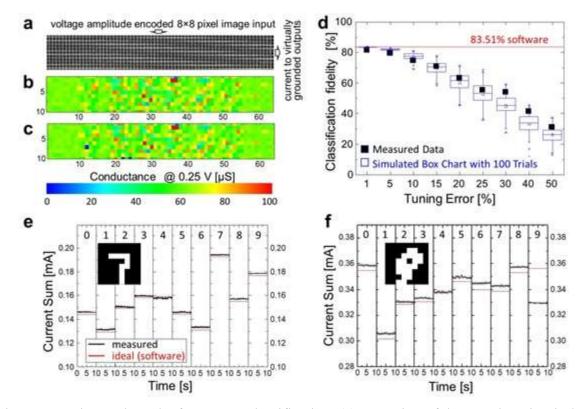

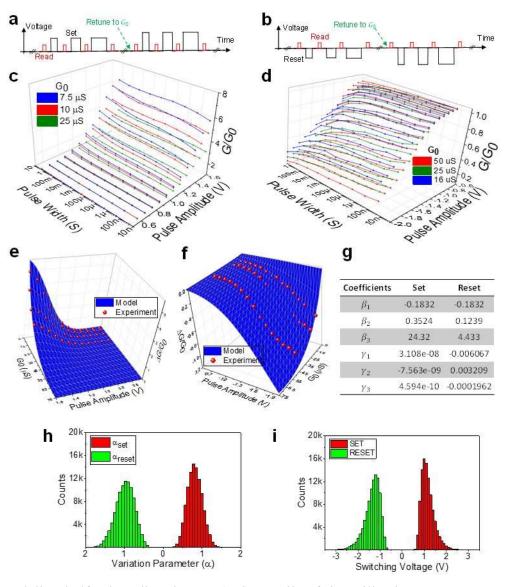

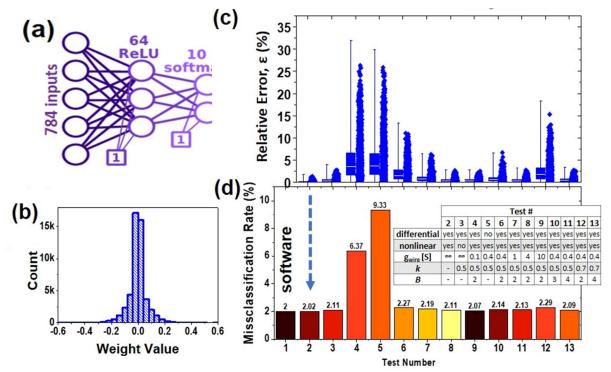

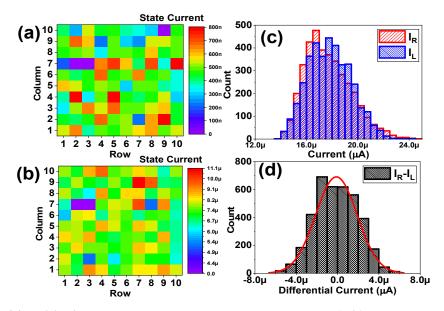

Then, we report our results on the development of large-scale passively-integrated memristive crossbars. We demonstrate a  $64 \times 64$  passive crossbar circuit with ~ 99% functional nonvolatile metal-oxide memristors featuring etch-down patterning and low-temperature budget (hence conducive to vertical monolithic integration) based on a foundry-compatible fabrication process. Most importantly, the achieved device uniformity, < 26% coefficient of variance in memristor switching voltages, is sufficient for programming a 4K-pixel gray-scale pattern with a smaller than 4% relative tuning error on average. Analog properties are also successfully verified via experimental demonstration of a  $64 \times 10$  vector-by-matrix

multiplication with an average 1% relative conductance import accuracy to model the MNIST image classification by ex-situ trained single-layer perceptron. Finally, an advanced conductance tuning algorithm is proposed to reduce tuning error further, and its effectiveness is validated by simulating the performance of a multilayer perceptron classifier.

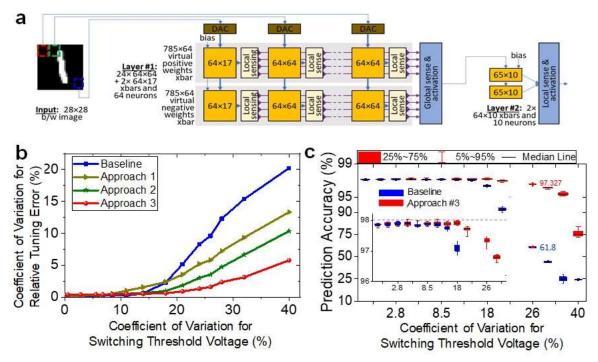

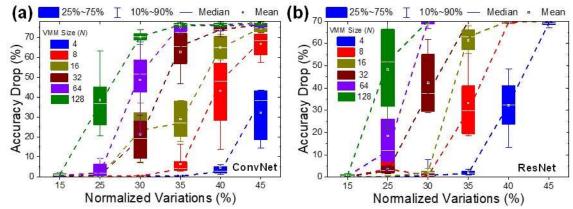

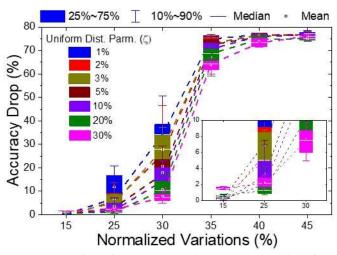

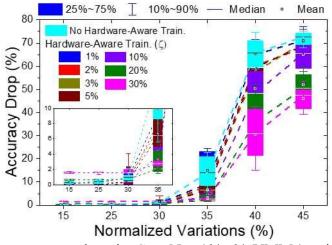

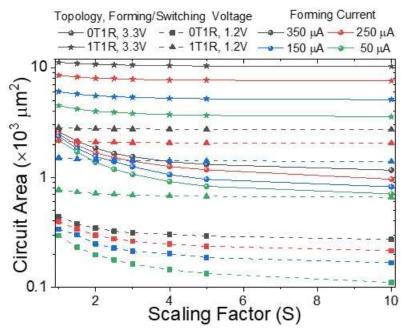

The third section expands upon the role of uniformity in passive memristive circuits and investigates how uniformity impacts the computing accuracy of analog memristive circuits, focusing on neuromorphic applications. Specifically, we explore the tradeoffs between computing accuracy, crossbar size, switching threshold variations, and target precision. All-embracing simulations of matrix multipliers and deep neural networks on CIFAR-10 and ImageNet datasets are performed to evaluate the role of uniformity on the accuracy of computing systems. Further, we study three post-fabrication methods that increase the accuracy of nonuniform 0T1R neuromorphic circuits: hardware-aware training, improved tuning algorithm, and switching threshold modification. The application of these techniques allows us to implement advanced deep neural networks with almost no accuracy drop, using current state-of-the-art analog 0T1R technology. Finally, we have analyzed the density prospects of memristive circuits and showed >5× superior density of 0T1R against 1T1R circuits, subjected to increase by downscaling the device properties.

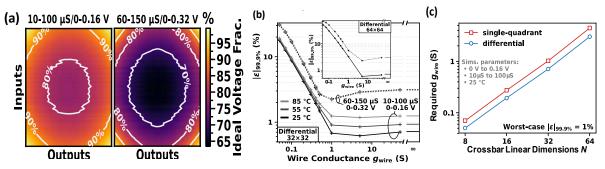

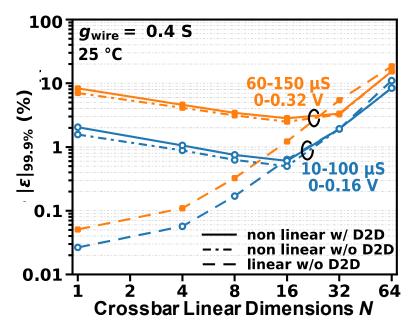

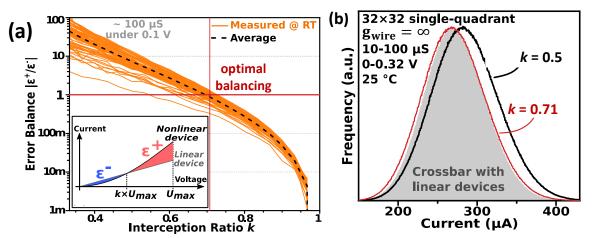

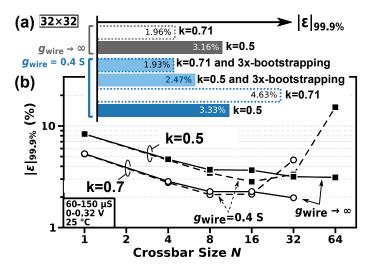

We investigate the impact of device nonlinearity and interconnect parasitics in analog current-mode memristive VMMs in section 2.4. We show that there is an optimal tuning voltage to minimize the computation error. Furthermore, error balancing and bootstrapping are introduced as two techniques for improving computing accuracy. It is also shown that when the crossbar size is scaled up, the optimum interconnect wire conductance should increase quadratically to preserve the computing precision when using naive error balancing approach and that the differential scheme is imperative for temperature insensitive operation and also to reduce the IR-drop effect.

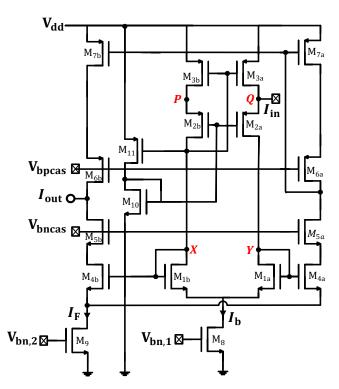

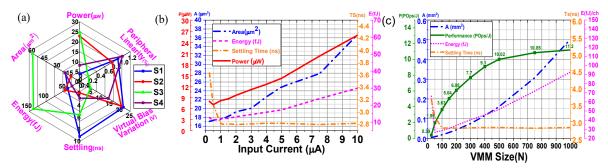

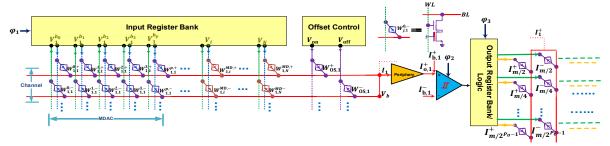

Section 2.5 proposes an energy-efficient compact sensing circuit in a 55 nm CMOS process that enables a dramatic reduction of sensing circuit overhead in mixed-signal VMMs. Specifically, we argue that the redesigned eFlash memory technology is currently the most energy-efficient candidate for implementing analog synapses due to its excellent retention characteristics at deep subthreshold <100 nA regimes. Using this local sensing circuit, we develop an energy-efficient, fully current-mode analog VMM topology with digital interfaces. In this design, we use a current-mode algorithmic analog-to-digital converter (ADC), in which the analog eFlash memory is additionally used for unit current generations and offset compensation. Such considerations allow us to achieve POp/J energy efficiency at the VMM level

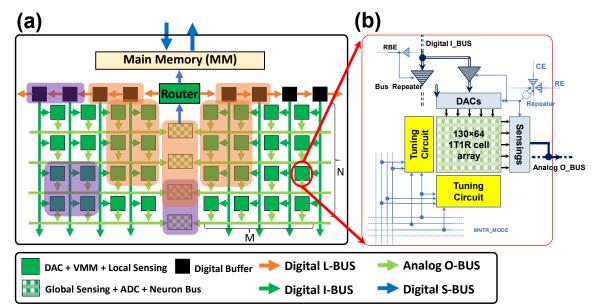

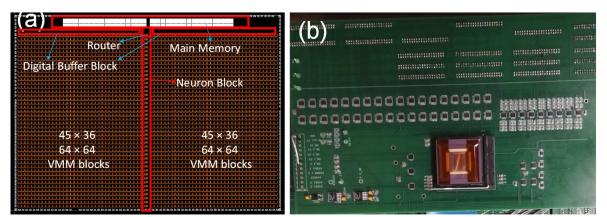

The remainder of this chapter focuses on the design of large-scale integrated neuromorphic computing systems and their efficient-enabling analog building blocks. A network-specific 6-layer DNN accelerator with  $\sim 1.5 \times 10^6$  training parameters and  $\sim 3 \times 10^3$  neurons is implemented. This network is fabricated with embedded Flash memories in 55 nm CMOS and could be used for performing high-speed image classification tasks, e.g., with CIFAR-10, CIFAR-100, and MNIST datasets. The second neuromorphic system is a 3-layer multi-layer perceptron suitable for the classification of 4-bit 56×56 images. Preliminary simulation results indicate the chip will be able to perform the MNIST classification task with ~98% accuracy with 100 ns/pattern and 0.25 nJ/pattern throughput and speed, far better than our previous work with 180 nm embedded Flash. Finally, we present the design and fabrication of a general-purpose DNN accelerator in 65 nm CMOS based on 1T1R memories. We discuss the

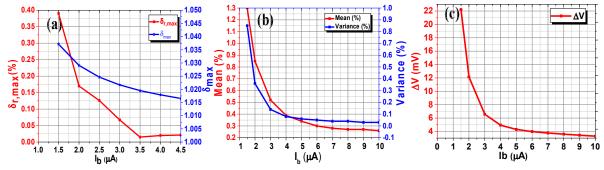

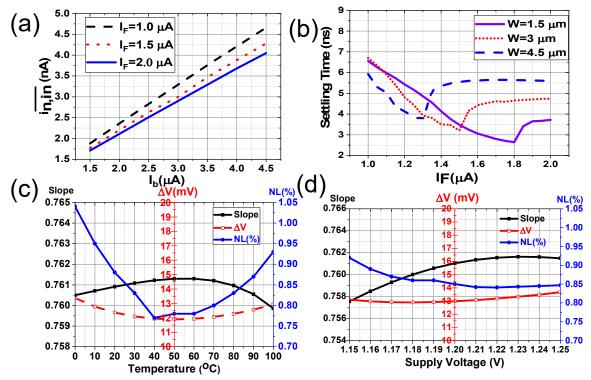

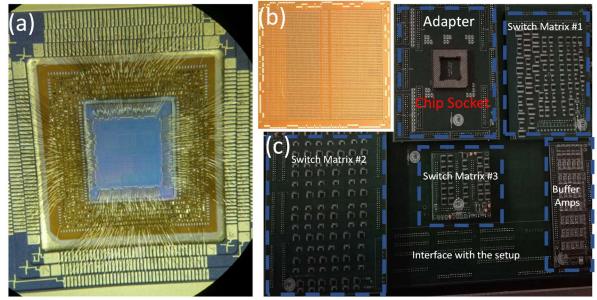

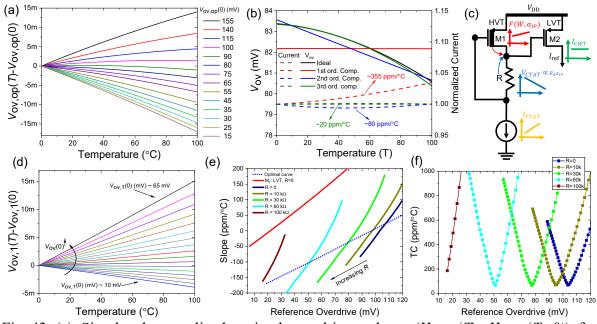

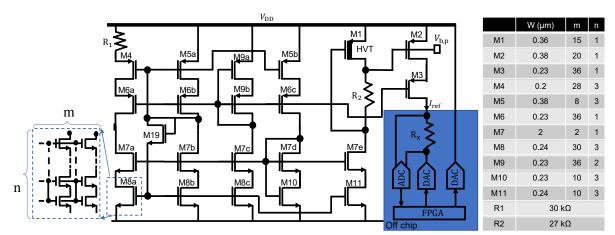

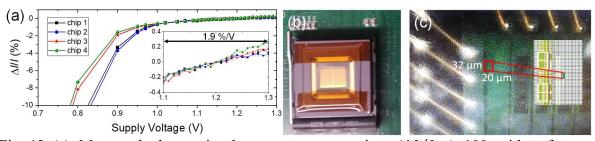

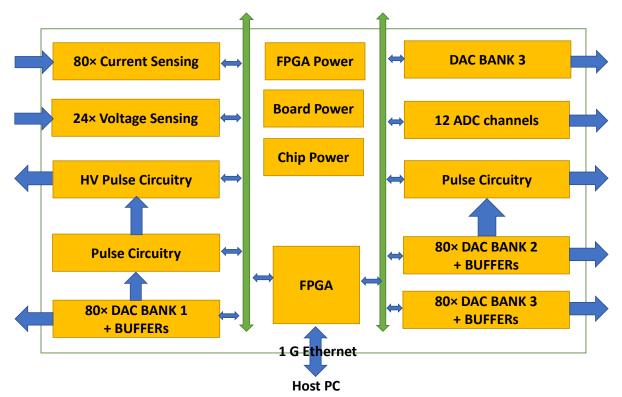

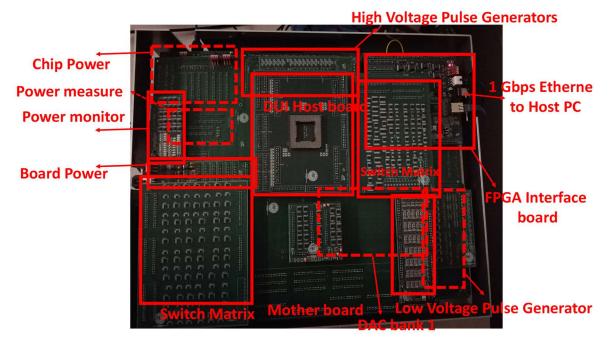

unique features of this design along with the innovative design of peripheral circuits and analog blocks which enable a compact footprint of the network, which includes  $\sim 26 \times 10^6 1$  T1R cells. The chip could be used to accelerate a wide range of deep neural network inference models, e.g., ResNet-18. We also propose a lightweight, microampere-range constant with temperature (CWT) current reference generator suitable for neuromorphic accelerators. The circuit exploits a beta-multiplier block to generate a proportional-to-absolute temperature (PTAT) current. The PTAT reference is used in a block that consists of only two multithreshold PMOS transistors and a resistor for generating a temperature-insensitive current reference. We show that when a low-threshold device (LVT) is gate-coupled with a highthreshold MOSFET (HVT), the HVT can be sized such that current variations in the LVT device due to the temperature fluctuations are minimized. A resistor is also added to the circuit to optimize the performance with respect to process variations. This simple circuit topology allows resiliency toward supply variations as well and leads to a very compact structure suitable for a distributed usage in mixed-signal neurocomputing systems. Measurement results from 4 samples of fabricated chips in a 65 nm CMOS process show an average temperature coefficient of 276 ppm/°C. The proposed circuit also achieves an average line regulation of 1.9 %/V and consumes ~15.8  $\mu$ W while occupying only 640  $\mu$ m<sup>2</sup>. The last section of the chapter discusses the architecture of a general-purpose experimental setup suitable for the characterization and testing of mixed-signal neuromorphic networks.

# 2.1. Introduction

The rapidly growing range of applications of machine learning algorithms for image classification, speech recognition, and natural language processing has led to an urgent need for specialized neuromorphic hardware. There is much more demand for fast, low-precision inference accelerators than for higher-precision systems for network training [94]. Despite the fact the vast majority of demonstrated accelerators from industry [71,95] and academia [65,96] belong to the category of custom digital integrated circuits, the most natural approach is based on analog and mixed-signal circuits [17,40,97,98]. Indeed, analog computing principles were developed almost four decades ago [3,7]. But, its efficient implementations are enabled only recently by the appearance of novel continuous-state, nonvolatile memory devices- the most crucial elements of analog circuits. Recent advances in analog-grade dense nonvolatile memories now enable extremely fast, compact, and energy-efficient analog and mixed-signal circuits are perfectly suited, in particular, for hardware implementations of the inference operation in advanced neuromorphic networks, which requires a massive amount of low-to-medium precision dot-product operations.

Floating-gate technology (or so-called "synaptic transistors") is one of the earliest forms of realizing an analog synapse, and the idea of using floating-gate transistors to implement programmable analog VMMs dates back to decades ago [7,99]. Such devices can be fabricated in standard CMOS processes, and few learning systems [78,100] have been developed based on them. One important downside of synaptic transistors is their relatively large areas (>1000 $F^2$ , where *F* is the minimum feature size), leading to higher interconnect capacitances, larger dynamic energy losses, and delays in massive circuits. A dramatic change in the course of this technology has been made recently by redesigning the arrays of the ubiquitous NOR flash memories with their highly optimized cells [16,101], which have enabled superior density and performance. The modification of the cell writing triples the original cell size by ×3, meanwhile allowing the cells to be fine-tuned with <1% accuracy. The density of the modified arrays (in 180 nm and 55 nm processes) is ~120  $F^{2}$ , and the technology is

commercially available to 28 nm. Another subtle important improvement stems from the fact that these cells are highly optimized in terms of retention and endurance properties.

An ideal synaptic device offers both long-term (and repeatable) analog storage and lowenergy local computing capabilities in a dense structure. Analog-grade passively-integrated (0T1R) memristor is perhaps the most prospective candidate, offering excellent scalability, density, and analog memory functionality [24]. Memristor is a nanodevice with adjustable conductance G—essentially an analog nonvolatile memory cell—used at each crosspoint of a crossbar array, which (naturally and efficiently) implements the dot-product operation in the analog domain. The most appealing aspect of memristor technology is its scalability prospects. The conductance modulation in filamentary metal-oxide memristors is attributed to the reversible modulation of the concentration of oxygen vacancies. The atomic-scale of the vacancy position modulation implies the feasibility of downscaling memristors to sub-deca nanometers [24,26]. The density of a device could be as small as  $4F^2$ , bounded by the halfpitch metal size F. Emulating these adjustable devices with purely CMOS circuits requires orders of magnitude larger footprint. However, further progress in fabricating large memristive crossbars faces few challenges. One critical challenge is the presence of large device-to-device variations [102]. The stochastic nature of oxide rupture in such small scales complicates the reproducibility of device parameters, e.g., the voltage required for electroforming and switching. Indeed, such variabilities are the very reason for the limited demonstrations of memristive neuromorphic networks so far. One solution to alleviate this issue is the usage of selector transistors (1T1R memories) [81,98], which is inconsistent with the main driving force of this technology (i.e., scalability and three-dimensional integration compatibility).

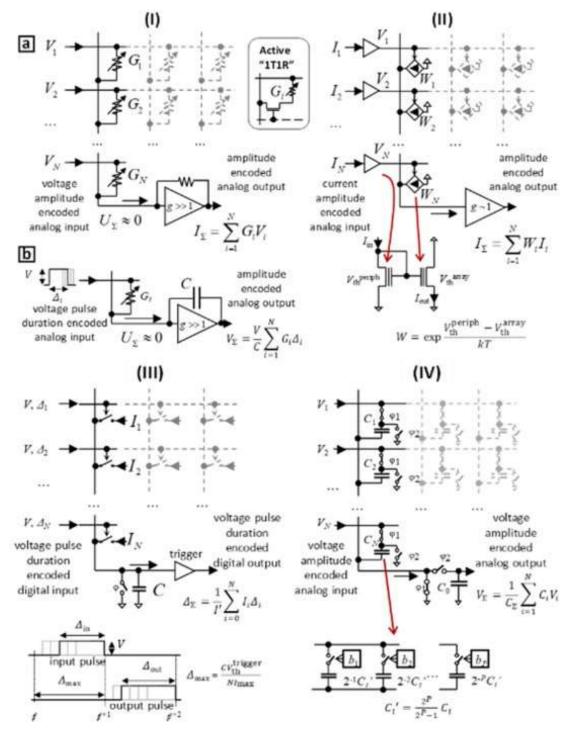

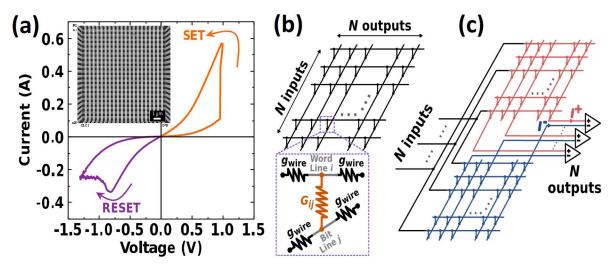

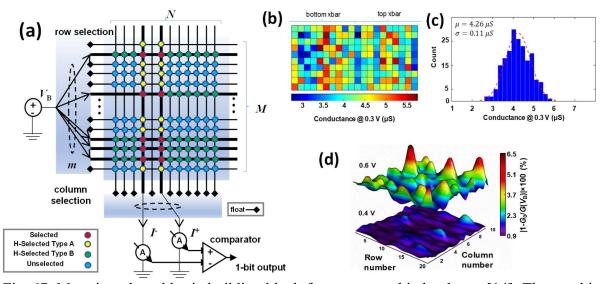

Fig. 1 shows typical mixed-signal circuits for implementing the vector-by-matrix multiplication (VMM), the most important operation in inference accelerators and other neuromorphic tasks, while Fig. 2 provides their qualitative comparison. Specifically, due to their superior integration density, VMMs based on passive crossbars with resistive switching devices (Fig. 1.I), including metal-oxide memristors, conductive-bridge, and phase-change memories, might be the most promising in the long term. Though the integration density of the floating-gate (FG) circuits (Figs. 1.II and 1.III) is comparable with that of systems using 1T1R cells, the fabrication technology available for the latter approach is more scalable. The main relative advantage of the former approach is the FG cell's amplification, that relaxes the requirement for the gain of sensing circuitry, and enables very compact peripheral circuits. Finally, the lack of tunable capacitance devices in the switch capacitor approach (Fig. 1.IV) typically allows only 'near memory computing (instead of 'in-memory computing possible with other candidates) and leads to inferior density and other metrics.

Fig. 1: Major types of mixed-signal VMM circuits: In (I), the matrix elements ('synaptic weights') are represented by continuous states of adjustable nonvolatile resistive devices (e.g., memristors), while the input signals are encoded with either (a) amplitudes, or (b) durations of voltage pulses. The top right inset shows an active ('1T1R') cell, which may also be used in circuits (a, b). In (II, III), each weight is stored in subthreshold-mode floating-gate (FG) cells, implemented as either (II) a current mirror pair formed by peripheral and array FG transistors or (III) a voltage-gated current source. In (III), both inputs and outputs are encoded

by the duration of pulses, generated within the corresponding time frame t, as shown at the bottom of panel III. In the switch capacitor approach (IV), P-bit weights are typically stored in binary-weighted fixed-value crosspoint capacitors, and the computation is performed by controlling the capacitor charge/discharge, using the switches  $\varphi$ 1 and  $\varphi$ 2.

| Fig | Хрс       | oint | Input/output | Density | Precision | Speed | Energy<br>Efficiency | Maturity |

|-----|-----------|------|--------------|---------|-----------|-------|----------------------|----------|

| la  | от        | R    | amp/amp      | ++      | +         | +++   | ++                   | -        |

| Ib  | - OT -    | R    | time/amp     | +++     | ++        | ++    | +++                  | -        |

| la  | -<br>- 1T | R    | amp/amp      | +       | ++        | ++    | +                    | +        |

| Ib  |           | R    | time/amp     | ++      | +++       | +     | ++                   | +        |

| П   | FG        |      | amp/amp      | +       | ++        | ++    | +                    | ++       |

| 111 | FG        |      | time/time    | ++      | +++       | +     | ++                   | ++       |

| IV  | С         |      | amp/amp      | -       | -         | +     | ++                   | +++      |

Fig. 2: Qualitative comparison of various VMM approaches outlined in Fig. 1: '+++' - the best, '-' – the worst. The score for precision is based on a combination of input, weight, and computing accuracies. The scores for density, speed, and energy efficiency (EE) reflect contributions from both the arrays and the peripheral circuits. Besides the maturity, all scores are for the expected level of each technology after it has been matured, rather than for its current state-of-the-art.

#### 2.2. Developing Large-Scale Passive Crossbars

The superior density of passive analog-grade memristive crossbar circuits could enable storing extremely large neural network models directly on specialized neuromorphic chips, thus avoiding costly off-chip communication. However, to ensure efficient use of such circuits in neuromorphic systems, variations in current-voltage characteristics of crosspoint devices must be substantially lower than those of memory devices coupled with select transistors, which partly explains very limited demonstrations of neuromorphic prototypes using passive crossbars. Here we report a 64×64 passive crossbar circuit with ~ 99% functional nonvolatile metal-oxide memristors. The developed technology is based on a foundry-compatible fabrication process that features etch-down patterning and low-temperature budget, and hence conducive to vertical monolithic integration. The achieved device uniformity, most

importantly below 26% coefficient of variance in memristor switching voltages, is sufficient for programming a 4K-pixel gray-scale pattern with a smaller than 4% relative tuning error on average. Analog properties are also successfully verified via experimental demonstration of a 64×10 vector-by-matrix multiplication with an average 1% relative conductance import accuracy to model the MNIST image classification by ex-situ trained single-layer perceptron. Finally, an advanced conductance tuning algorithm is proposed to reduce tuning error further, and its effectiveness is validated by simulating the performance of a multilayer perceptron classifier. We believe that our results are a significant improvement in both complexity and analog properties over previously reported passive crossbar memories and an important step towards realizing human-brain-scale integrated neuromorphic systems.

There has been substantial progress in the development of 1T-1R memory arrays, in which a memory cell based on a two-terminal resistive switching element ("1R") also includes one dedicated select transistor ("1T"), and numerous demonstrations from academia and industry of using such active memories in neuromorphic computing circuits. Perhaps, the most impressive neuromorphic functionality was reported based on nonvolatile TaO<sub>2-x</sub> devices integrated in 128×64 active crossbar arrays - see details of such devices in [103] and review of many experimental demonstrations based on such technology in [104]. The main weakness of that technology, however, is extremely large, of the order of 2500  $\mu$ m<sup>2</sup>, size of 1T1R cell, and high (mS-scale) device conductance, which necessitates bulky and energy-hungry peripheral circuits. Additionally, the reported excellent conductance tuning results are in part due to the use of the select transistor in 1T1R cell, which inhibits half-select disturbance - the main challenge for achieving high precision tuning in passively integrated circuits.

The progress in the most prospective, passive analog-grade ReRAM, however, has been much slower, mainly because of much stricter requirements for the uniformity of memory cells' I-V characteristics. For example, Xpoint memory - the most advanced commercialized technology using passively-integrated memory devices - operates in a digital mode. (Such memory is also most likely based on phase-change materials, which are less appealing for analog computing applications due to larger conductance drift over time.) A promising I-Vuniformity results with very tight variations were reported for stand-alone devices based on organic [91] and epitaxial [87] materials. The main concern for these recently developed analog-grade memristors is the compatibility of the utilized fabrication flows with conventional semiconductor foundry processes. Ref. 105 describes 500-nm half-pitch 32×32 circuits based on W/WOx/Pd/Au devices, which were tuned with 25% precision (estimated from Fig. S3d data of [105]) to implement a sparse encoding algorithm. A similar device technology was recently used by the same group to demonstrate large-scale fully-integrated complementary metal-oxide-semiconductor (CMOS) / memristor circuits [106]. It is not clear, however, if the reported results in Ref. 106 were obtained based on reading conductances after completing the tuning process for all devices in the crossbar circuit or just a fraction of them, as it was performed by the same authors in Ref. 11. An even more serious and related concern is a lack of detailed statistics and, most importantly, data on retention because similar devices were shown to be volatile due to interfacial switching mechanisms, according to previous studies [107]. Another very recent work reported analog-grade  $32 \times 32$  crossbar arrays based on passively integrated Si-alloy: Ag electrochemical devices [89]. Though a very impressive 100% device yield and highly linear state update characteristics were reported, the main weakness of that work is also poor retention of the devices. Additional concerns are whether

the yield results reported for  $10 \times 10 \ \mu m^2$  footprint crosspoint devices will hold for nanoscale devices and the use of silver in the device stack, a contaminant typically avoided in CMOS foundry processes. Ref. 33 proposed a very promising concept for a three-dimensional memristive memory. Unfortunately, all presented experimental results in that paper were obtained for a rather unpractical structure based on microscale binary-switching devices with non-overlapping footprints so that the demonstrated three-dimensional integration does not improve the effective memristor density.

Table I summarizes experimental work on analog-grade 1T1R and 0T1R metal-oxide memristor crossbars. As evident from this table, the uniformity, density, and analog properties of previously reported memristive crossbar circuits are not sufficient for making practical neuromorphic hardware, especially for running large-scale neural models.

To address this need, our group has developed uniform CMOS-compatible fabrication technology for building larger, conducive for back-end-of-the-line 3D integration crossbar array circuits. The main contribution of this work is to mitigate the remaining challenges at the circuit and application levels and to show the prospects of such technology in neuromorphic computing applications. The developed circuits have ten times more devices and excellent uniformity allowing for significantly better array-scale conductance tuning precision as compared to the previous work [17] that reported the largest passive analog-grade memristive crossbar circuits with detailed characterization statistics. Moreover, the demonstrated artificial neural network is close in complexity to the state-of-the-art neuromorphic prototypes based on (> 10,000 sparser and 10× more conductive) 1T1R ReRAM devices [103].

Table. 2.1: Comparison of memristive circuits. The specific focus of the table is on the stateof-the-art nonvolatile (filamentary) analog-grade 0T1R metal-oxide devices, while only few representative works are listed for metal-oxide 1T1R and solid-state-electrolyte 0T1R circuits. Note that the common concern for the solid-state electrolyte type devices (rows #1 to #3) and interfacial switching WO<sub>x</sub> devices (rows #4 to #6) is poor state retention.

| Cell type |                                | Ref.      | Crossbar<br>size <sup>0</sup> | Yield<br>(%) | Largest<br>working<br>demo <sup>0</sup> | $\begin{array}{c} \text{Cell} \\ \text{size}^1 \\ \left( \mu m^2 \right) \end{array}$ | Forming <sup>2</sup><br>current<br>(µA)/<br>Voltage(V) | Endur-<br>ance <sup>3</sup><br>(cycles) | Array<br>level<br>tuning<br>precision | Set<br>switching<br>statistics<br>μ/σ(V) | G <sub>max</sub> /G <sub>min</sub> <sup>4</sup><br>(µS) | Retention<br>(@°C)      | Type of integration /<br>patterning technique /<br>Substantial CMOS foundry<br>integration challenges <sup>5</sup> |

|-----------|--------------------------------|-----------|-------------------------------|--------------|-----------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------|---------------------------------------|------------------------------------------|---------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------|

| 0T1R      | Si/Ag                          | [89]      | 32×32                         | ~100         | 32×32                                   | ~12008                                                                                | 5000/3.7                                               | >10M                                    | -                                     | 2.25/ 0.1                                | 10 / 1º                                                 | ~hours                  | SA/RIE/High-T epitaxy&Ag                                                                                           |

|           | SiGe-aSi/Ag                    | [108]     | 40×40                         | -            | 8×810                                   | 0.01                                                                                  | -                                                      | -                                       | ~ 50%11                               | 3.5/ -                                   | 4/0.1                                                   | -                       | BEOL / lift-off / Ag                                                                                               |

|           | wo <sub>x</sub>                | [59]      | 11×3                          | -            | 11×3                                    | -                                                                                     | 1000/~1.8                                              | -                                       | -                                     | 0.85/0.05                                | -                                                       | -                       | SA / lift-off / none                                                                                               |

|           |                                | [105]     | 32×32                         | -            | 25×20                                   | ~9                                                                                    | >170 / -                                               | -                                       | ~ 35%12                               | 1.7/ -                                   | 3/113                                                   | ~mins @RT <sup>14</sup> | SA / lift-off / none                                                                                               |

|           |                                | [106]     | 108×54 <sup>15</sup>          | -            | 26×10                                   | > 25616                                                                               | -                                                      | -                                       | -                                     | -                                        | 2.4/1                                                   | ~mins @RT <sup>14</sup> | FI-BEOL / lift-off / none                                                                                          |

|           | Ta <sub>2</sub> O <sub>x</sub> | [109]     | 18×2                          | ~100         | 18×2                                    | -                                                                                     | 250 / ~1.1                                             | -                                       | -                                     | -                                        | 1500/850                                                | -                       | SA / lift-off / none                                                                                               |

|           |                                | [110]     | 16×3                          | 78           | 4×3                                     | -                                                                                     | 1000 / ~2                                              | > 100k                                  | -                                     | 1.25/0.1                                 | 1800/1300                                               | -                       | SA / lift-off / none                                                                                               |

|           | TiO <sub>2-x</sub>             | [24]      | 12×12                         | >50          | 10×6                                    | 0.16                                                                                  | 200 / 1.9                                              | >200k                                   | -                                     | 0.9/0.17                                 | 200/6                                                   | >140h@76                | SA / lift-off / none                                                                                               |

|           |                                | [17]      | 20×20                         | >95          | 17×20+8×11                              | 0.25                                                                                  | 220 /1.5                                               | >100k                                   | < 8%                                  | 1.0/0.18                                 | 200/6                                                   | >20h@120                | SA / lift-off / none                                                                                               |

|           |                                | [26]      | 2×10×10                       | ~100         | 2×10×10                                 | 0.49/2                                                                                | 100/2.517                                              | -                                       | -                                     | 1.1/0.15                                 | 100/0.1                                                 | >25h@100                | SA/ion beam milling/ none                                                                                          |

|           |                                | this work | 64×64                         | ~99          | 64×64                                   | 0.5625                                                                                | 100 / 3.2                                              | >100k                                   | < 5%                                  | 1.2/0.13                                 | 100/6                                                   | >20h@100                | SA /RIE/ none                                                                                                      |

|           | HfO <sub>2-x</sub>             | [33]      | 3D 8×8 <sup>18</sup>          | -            | ~12019                                  | ~1000/820                                                                             | -                                                      | -                                       | binary                                | -                                        | 1200/~300                                               | -                       | SA / lift-off / none                                                                                               |

| 1T1R      | HfO <sub>2-x</sub>             | [25]      | 128×64                        | >9921        | 128×64                                  | ~250022                                                                               | -                                                      | -                                       | <3.1%23                               | 2/-                                      | 900/100                                                 | 10yr @RT                | BEOL/lift-off / none                                                                                               |

|           |                                | [32]      | 128×8                         | -            | 960                                     | -                                                                                     | >150 / >3                                              | -                                       | < 35%                                 | -                                        | 40/5                                                    | -                       | BEOL/ lift-off / none                                                                                              |

|           |                                | [69]      | 128×16                        | >99          | 128×16                                  | > 5                                                                                   | -                                                      | -                                       | 3.3 %                                 | -                                        | 20/2                                                    | ~ days @RT              | BEOL /lift-off / none                                                                                              |

|           |                                | [111]     | 158K                          | -            | 158 K                                   | 1.69                                                                                  | 100 / >1.8                                             | < 1k                                    | ~ 2-bit                               | 1/-                                      | 10 / 0.1                                                | -                       | NA / NA / none                                                                                                     |

|           |                                | [112]     | 1K                            | -            | 448                                     | ~25                                                                                   | -                                                      | -                                       | ~ 20%                                 | 3.5 / -                                  | 100/0.1                                                 | ~1m @30                 | NA / NA / none                                                                                                     |

<sup>6</sup> "Crossbar size" refers to the largest-dimension fabricated integrated crossbar circuit (not necessarily fully-functional), while the "largest working demo" refers to the largest number of devices employed at once in the demo, i.e., without relying on post-processing / combining the results from separate measurements. <sup>1</sup> Based on the full pitch of the integrated memory cells. <sup>2</sup> Largest set voltages are used if statistical data are not reported. <sup>3</sup> The test conditions may be different. <sup>4</sup> Specified at 0.1V for the devices with nonlinear static *I-V* characteristics unless noted otherwise. <sup>5</sup> SA = Stand-alone integrated crossbar circuit, RIE = reactive ion etching, BEOL = Back end of line integrated crossbar circuit on CMOS wafer containing access transistors, FI-BEOL = BEOL with fully integrated CMOS peripheral circuits. <sup>6</sup> Denser single devices are reported, though most experimental results are for 25 µm<sup>2</sup> devices. <sup>7</sup> Data for the low-resistance state. Significant retention loss at high resistance levels. <sup>8</sup> Based on Fig. 4c. <sup>9</sup> From Fig. 1d. <sup>10</sup> 40×40 conductance map is based on combining results from separate tuning all devices or measured immediately after programming each device. <sup>13</sup> Average range of conductance values observed in the crossbar. There is a significant variation between different devices. <sup>14</sup> Communications with the authors. <sup>15</sup> 126 6×8 physical subarrays utilized for a logical 108×54 array with the conductances measured after programming each subarray. <sup>16</sup> From Supplementary Note 10. <sup>17</sup> For the top crossbar, while it is 2 V / 50 µA for the bottom one. <sup>18</sup> Effective crossbar dimensions based on Fig. 4d. <sup>20</sup> Based on Fig. 2g. Though SEM images of 300-nm-scale devices are shown, all experimental results are based on microscale devices. <sup>21</sup> Based on Fig. 1c of [103]. <sup>22</sup> Based on Fig. 1c of [25, 13].

### 2.2.1. Device and Circuit Characterization

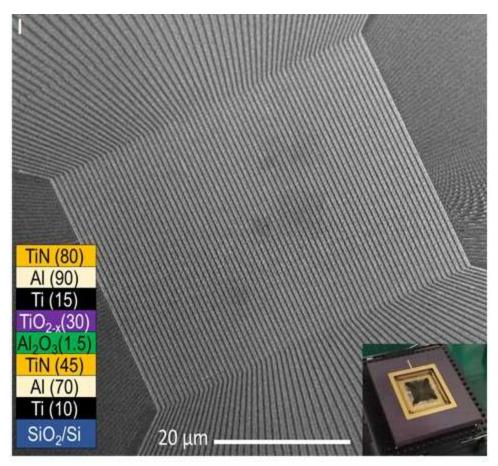

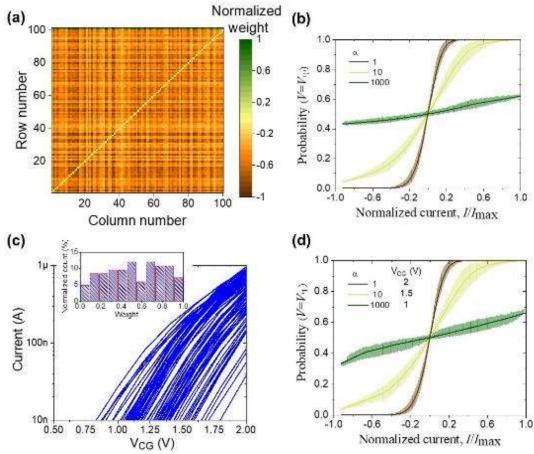

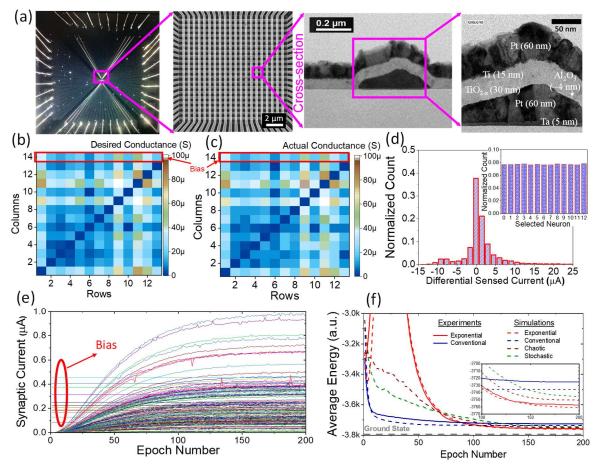

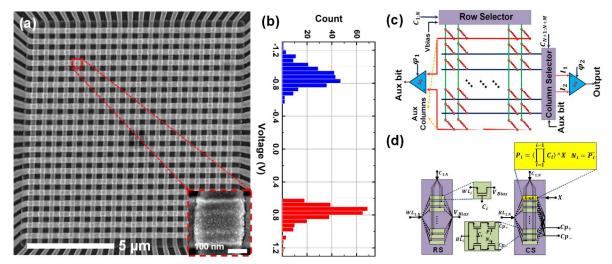

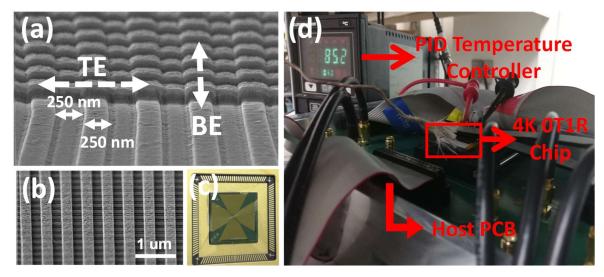

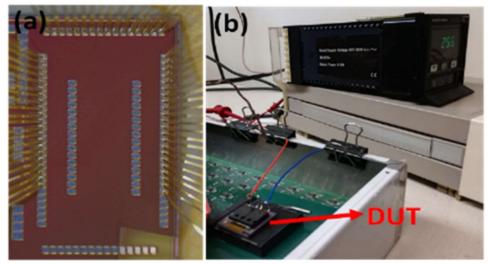

The developed  $64 \times 64$  crossbar circuit consists of Ti/Al/TiN-based top and bottom electrodes and an Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2-x</sub> switching layer (Fig. 3). The actual crossbar array dimensions are  $(64+2)\times(64+2)$ , with an additional line added at both sides of the circuit for the top and bottom layers to achieve better uniformity for the devices in the main array. The details of the fabrication process are provided in [113]; here, we only focus on characterization and demonstration results.

Fig. 3: SEM image of the full 64×64 memristor crossbar array. The bottom left, and bottom right insets show, correspondingly, material layers at the device cross-section with corresponding thicknesses in nanometers and the packaged chip.

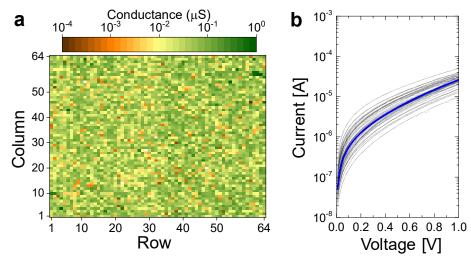

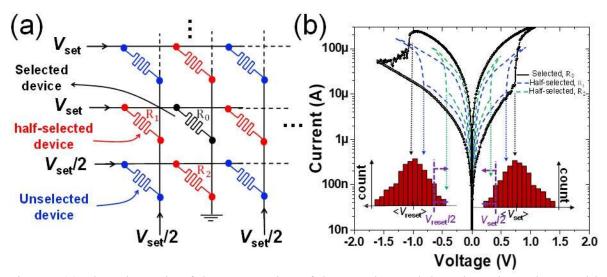

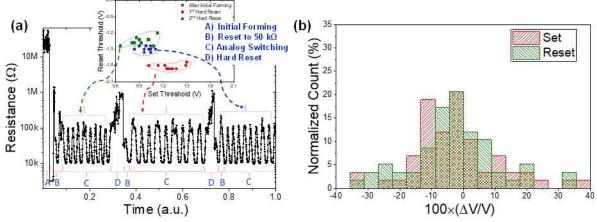

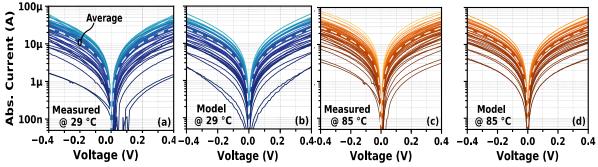

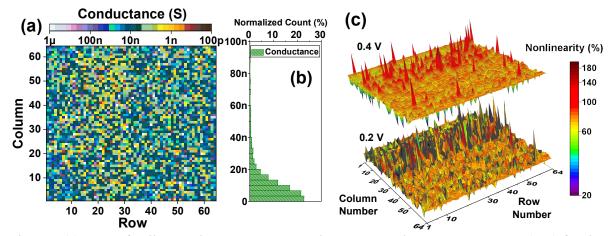

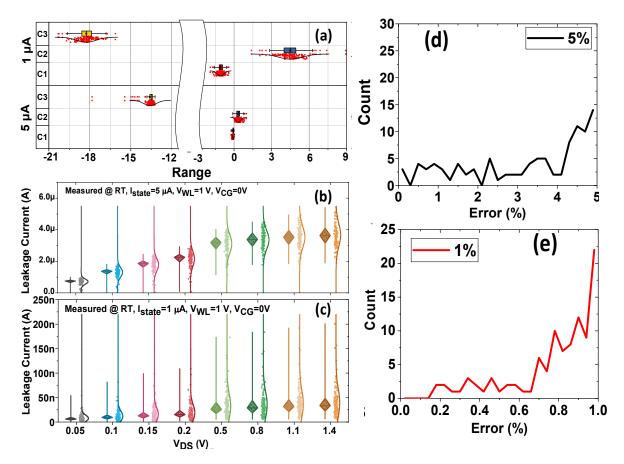

Current-voltage characteristics for the as-fabricated devices, i.e., before applying the electroforming process, are fairly uniform (Fig. 4), which is an essential prerequisite for lowering variations in functional memristors [17, 24]. To electroform devices, a positive voltage is applied to the top electrode while all unselected lines in the crossbar are floated. Because of more extensive annealing compared to previous work [24], the currents via as-fabricated devices (Fig.4.4b) are just slightly less compared to the device smallest (off-state) current after forming (Fig. 5a) – see, e.g., the highlighted curves for a specific device in both figures. The forming voltages are only slightly higher on average than set voltages and completely overlap for some, making such devices effectively forming-free. The formed devices show similar in magnitude set and reset voltages (Fig. 5a), from 200 µA to 400 µA

reset and set switching currents,  $2-\mu$ A-to-50- $\mu$ A dynamic current range at 0.25 V, and balanced *I-V* characteristics, i.e.,  $I(V) \approx I(-V)$  at small voltages. The average nonlinearities, i.e.,  $0.5 \times I(V)/I(V/2)$ , are ~1.1 and ~1.3 for the on and off state, respectively, at V = 0.25 V.

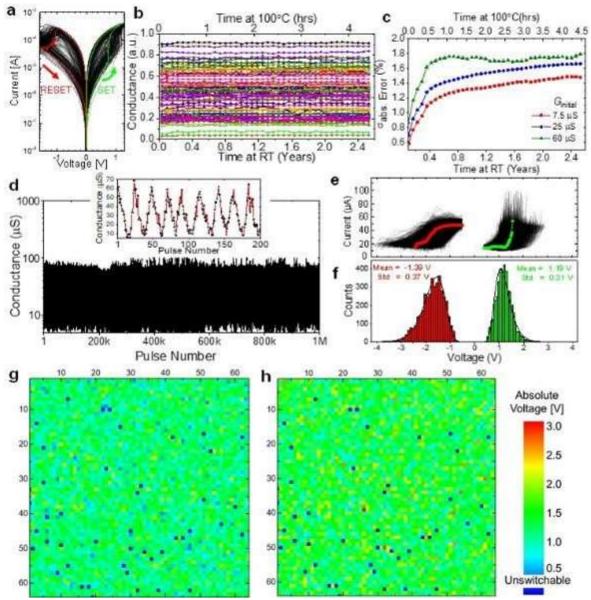

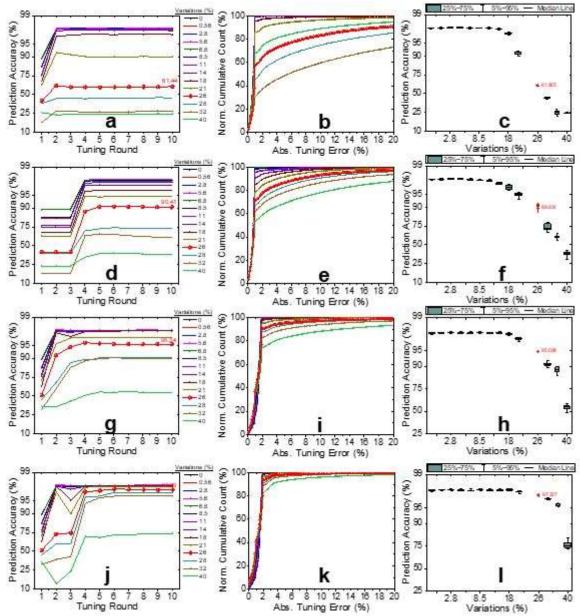

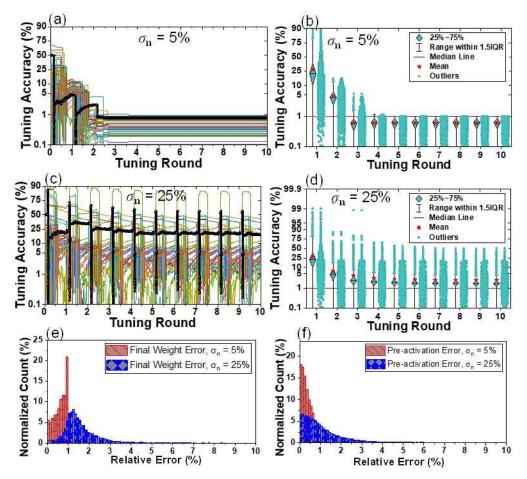

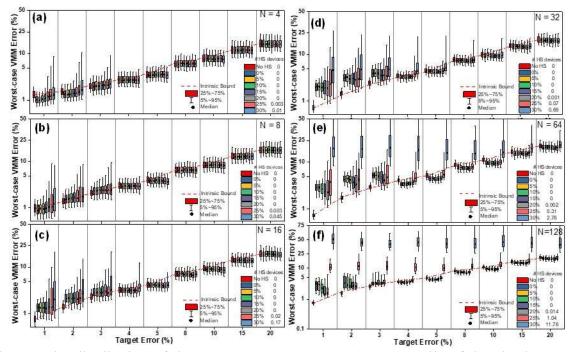

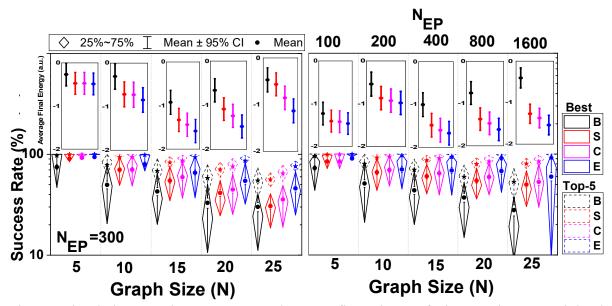

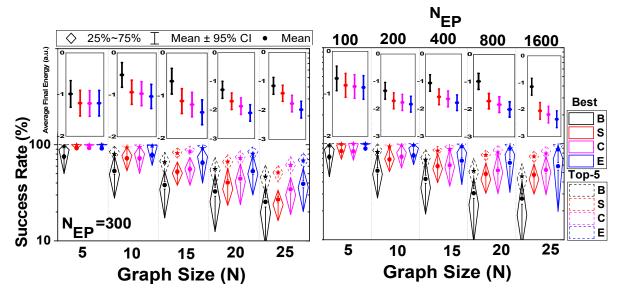

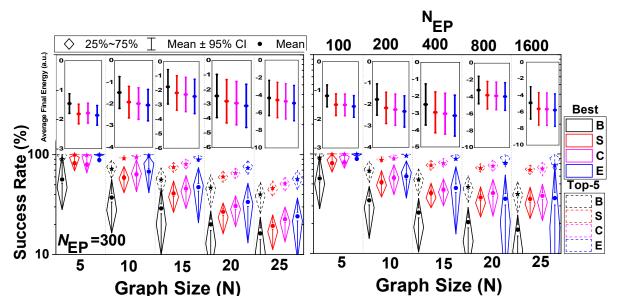

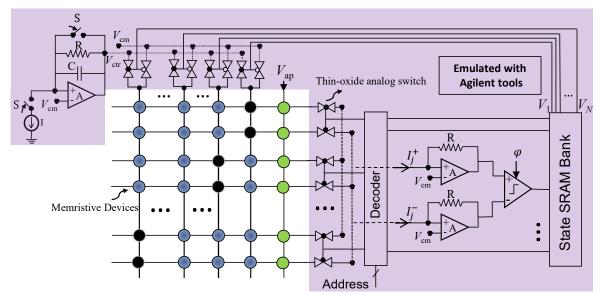

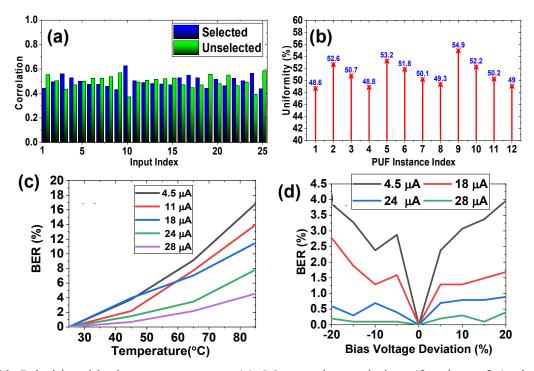

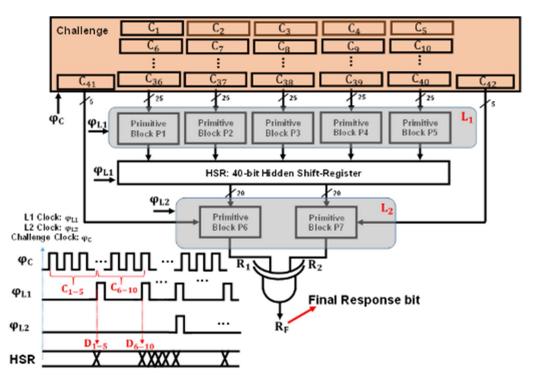

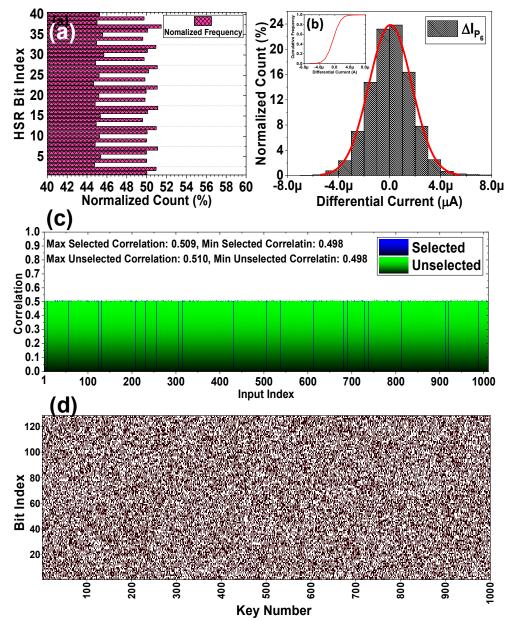

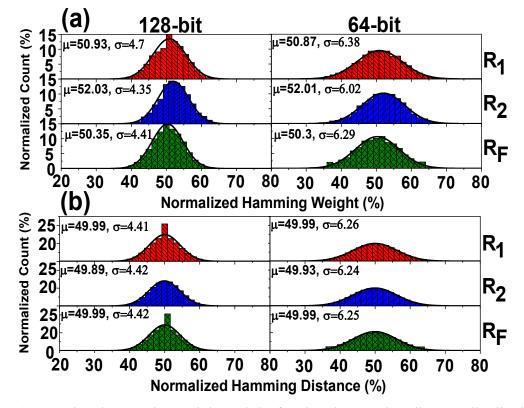

Accelerated retention tests at 100 °C are performed for 500 devices, with each device tested in 9 different random states (Fig. 5b). Post-processed experimental results and their extrapolation for room temperature operation show very promising retention characteristics (Fig. 5b,c). For example, the extrapolated results predict that the normalized conductance will drift on average by  $\sim 0.7\%$  over 1 month at room temperature, while the average spread is expected to be less than 1.6% after 2 years (Fig. 5c). Fig. 5d confirms excellent switching endurance. It shows the results of applying 1 million tuning pulses, or effectively, switching gradually device  $\sim 10^5$  times between its extreme on and off states. Note that the experiment was stopped after reaching 1M pulses because of the limitations of the experimental setup and not due to a device failure. Furthermore, decent retention was observed even after the switching endurance experiment. Fig. 5e shows measured switching dynamics characteristics for all the devices in the 64×64 array. These data are obtained by first setting the conductance of each device to 14 µS with 10% precision. Next, 1-ms-long pulses, with amplitude increased incrementally in 50 mV steps, are applied to the device. The device's conductance is read between each programming pulse at 0.25 V, and the sequence of pulses is stopped once the small-voltage conductance exceeded 50 µS. After that, we apply a similar reset/read pulse sequence until the conductance is switched back to 14 µS. The raw experimental data are used to extract effective switching thresholds, defined as the smallest amplitude of a voltage pulse at which the device conductance changes by more than 20% compared to its initial state (Fig. 5f-h). According to Fig. 5f, the average set and reset threshold voltages are 1.19 V and -1.39