## Reasoning about High-Level Constructs in Hardware/Software Formal Verification

by

Jiang Long

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Robert K. Brayton, Chair Professor Alberto Sangiovanni Vincentelli Professor Xinyi Yuan

Summer 2017

# Reasoning about High-Level Constructs in Hardware/Software Formal Verification

Copyright 2017

by

Jiang Long

#### Abstract

Reasoning about High-Level Constructs in Hardware/Software Formal Verification

by

Jiang Long

Doctor of Philosophy in Electrical Engineering and Computer Science

University of California, Berkeley

Professor Robert K. Brayton, Chair

The ever shrinking feature size of modern electronic chips leads to more designs being done as well as more complex chips being designed. These in turn lead to greater use of high-level specifications and to more sophisticated optimizations applied at the word -level. These steps make it more difficult to verify that the final design is faithful to the initial specification. We tackle two steps in this process and their formal equivalence checking to help verify the correctness of the steps.

First, we present LEC, a combinational equivalence checking tool that is learning driven. It focuses on data-path equivalence checking with the goal of transforming the two logics under comparison to be more similar in order to reduce the complexity of a final Boolean (bit-level) solving. LEC does equivalence checking of combinational logic between two RTL (word-level) designs, one the original and one an optimized RTL version. LEC features an open architecture such that users and developers can learn with the system as new designs and optimizations are met, and then it can be modularly extended with new proof procedures as they are discovered.

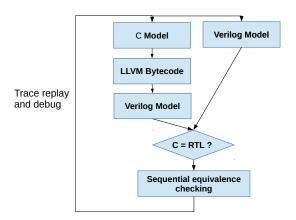

To address the use of higher level specifications, we build a simple trusted C to Verilog translation procedure based on the LLVM compiler infrastructure. The translator was designed to implement an almost vertatim translation of the C language operators and control structures

into the Verilog *always\_ff* and *always\_comb* blocks through traversing LLVM Bytecode programs. The procedure reliably bridges the language barrier between software and hardware and allows hardware synthesis and verification techniques to be applied readily.

In combination, these two procedures allow for equivalence checking between a software-like specification and an optimized word-level RTL implementation.

## Contents

| Contents |                                                      |                                                                                                                                                                                                                                                      | i                                |

|----------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Li       | st of                                                | Figures                                                                                                                                                                                                                                              | $\mathbf{v}$                     |

| Li       | st of                                                | Tables                                                                                                                                                                                                                                               | vii                              |

| 1        | Intr<br>1.1<br>1.2                                   | Motivation                                                                                                                                                                                                                                           | 1<br>1<br>3                      |

| 2        | Dat<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5               | Introduction                                                                                                                                                                                                                                         | 4<br>5<br>6<br>10<br>11<br>15    |

| 3        | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8 | C: Learning-Driven Equivalence Checking Overview: A Learning Process - Philosophy Tool Flow and Organization The LEC Widgets System Integration: Proof-tree Infrastructure Case Studies Experimental Results Comparison with Related Work Conclusion | 29 31 33 53 56 61 65             |

| 4        | A S<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5               | Simple Trusted Translation Procedure from C to Verilog Introduction                                                                                                                                                                                  | 68<br>69<br>74<br>81<br>90<br>95 |

|                                             | ii |

|---------------------------------------------|----|

| 4.6 Conclusions                             | 96 |

| 5 Conclusion and Possible Future Extensions | 97 |

| Bibliography                                | 99 |

|                                             |    |

#### Acknowledgments

First and foremost, I would like to thank my advisor Prof. Robert K. Brayton for accepting me into his PhD program in Fall 2008. I remembered his Phil Kaulfman award ceremony at DAC 2008, where he concluded this award speech by answering a question from the audience on what is his secrets in advising his students:

Leave them alone, don't mess them up, give a hand when they are in need of a help.

At times, I was indeed left alone, given space(maybe too much) to explore my interest, stretch my ability and forge forward on my own, but obtaining his guidance and support at times of doubt and breaking point which carried me through the PhD journey. I would not start nor reach the finishing point without Bob's support or guidance.

I would also like to thank Dr. Alan Mishchencko for introducing me to Bob's research group in the first place. His enthusiasm, deep devotion and extertise to the design and implementation of ABC not only provides us with a research foundation but also bring us closer to the industry for accessing real practical problems. In that, I would like to thank Dr. Mike Case for sharing an interesting problem with our research group which led to the starting point of this thesis work in data-path equivalence checking.

I am thankful to my Qual exam committee members, Prof. Sanjit Seisha, Prof. Andreas Kuehlmann, and Prof. Xinyi Yuan for overseeing the exam.

The thesis work is built upon Verific Inc.'s HDL compiler frontends, without them, it would not be possible. Personally, I would like to thank Baruch Sterin, Niklas Een, Yen-sheng Ho, Yu-yun Dai for the invigorating group discussions and introducing me to Python, bitbucket, hg and many other new tools which are the building blocks in the thesis implementation.

吾生也有涯, 而知也无涯。 以有涯随无涯, 殆已; 已而为知者, 殆而已矣。

庄子 (300. BC)

Life has its bound,

Thou learning does not.

With the bounded to follow the unbounded,

Trying thee;

Knowningly pursue the unknown,

Trying trying thee.

Zhuang Zi (300. BC)

# List of Figures

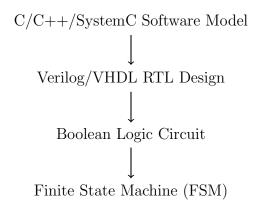

| 1.1  | Design Abstraction Levels                                                                                               | 2  |

|------|-------------------------------------------------------------------------------------------------------------------------|----|

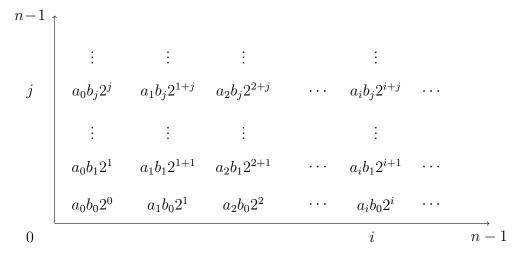

| 2.1  | $A \times B = \text{Sum of } n^2 \text{ partial products } \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$ | 11 |

| 2.2  | Linear Adder Tree described in Verilog                                                                                  | 12 |

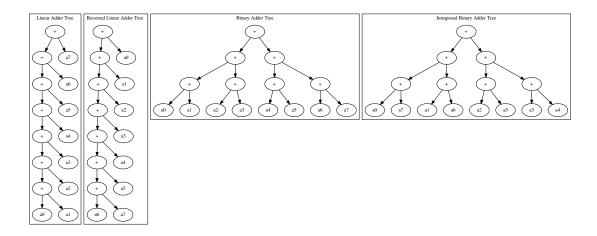

| 2.3  | adder tree structure                                                                                                    | 13 |

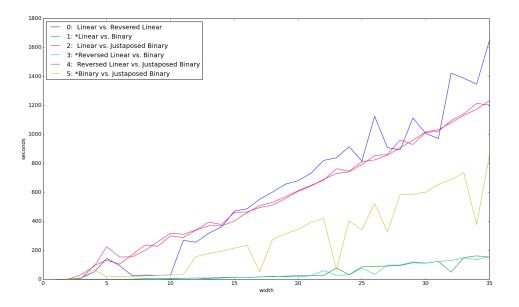

| 2.4  | ABC's deec results                                                                                                      | 14 |

| 2.5  | Complexity scale of SAT-Sweeping                                                                                        | 14 |

| 2.6  | Bit-level to word-level transformation                                                                                  | 15 |

| 2.7  | Use of UIF                                                                                                              | 17 |

| 3.1  | Miter logic                                                                                                             | 30 |

| 3.2  | Overall tool flow                                                                                                       | 32 |

| 3.3  | Illustration WNK node in C++ class                                                                                      | 32 |

| 3.4  | Proof process                                                                                                           | 34 |

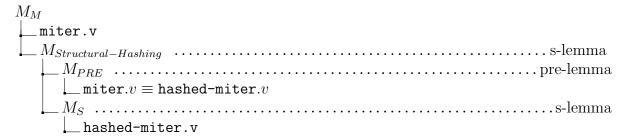

| 3.5  | Model Tree from Structural Hashing Widget                                                                               | 37 |

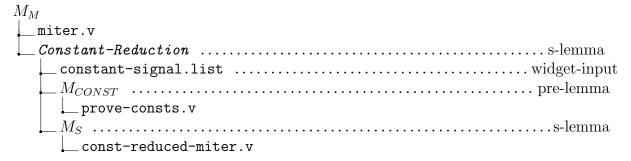

| 3.6  | Model Tree from Constant Reduction Widget                                                                               | 38 |

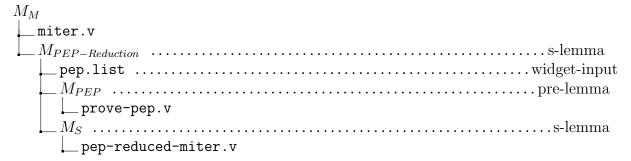

| 3.7  | Model Tree from PEP Reduction Widget                                                                                    | 39 |

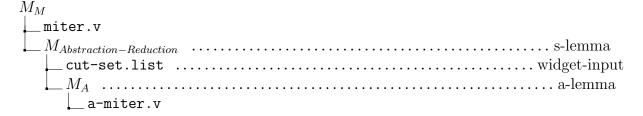

| 3.8  | Model Tree from the Abstraction Widget                                                                                  | 39 |

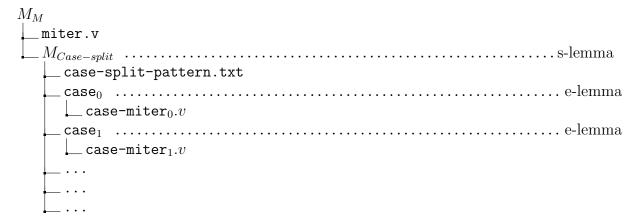

| 3.9  | Case-split Transformation Widget                                                                                        | 43 |

| 3.10 | Algebraic Transformations                                                                                               | 43 |

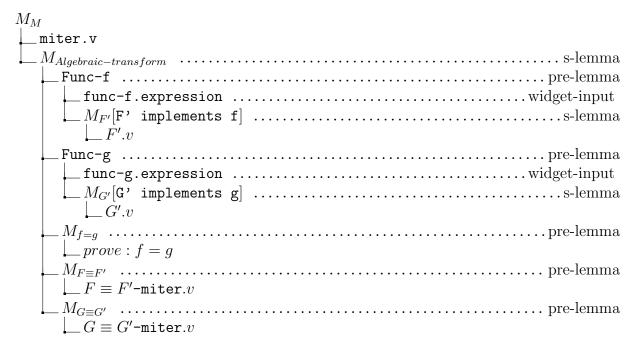

| 3.11 | Algebraic transformation Widget                                                                                         | 44 |

| 3.12 | Miter network                                                                                                           | 46 |

| 3.13 | Constant Learning and Reduction Widgets                                                                                 | 48 |

|      | PEP Learning and Reduction Widgets                                                                                      | 49 |

|      | Annotated reduced graph                                                                                                 | 52 |

|      | Branching sub-model tree                                                                                                | 54 |

|      | Illustration of proof log                                                                                               | 55 |

|      | Sub-model proof tree                                                                                                    | 57 |

|      | Addition implementation                                                                                                 | 59 |

|      | Proof log                                                                                                               | 60 |

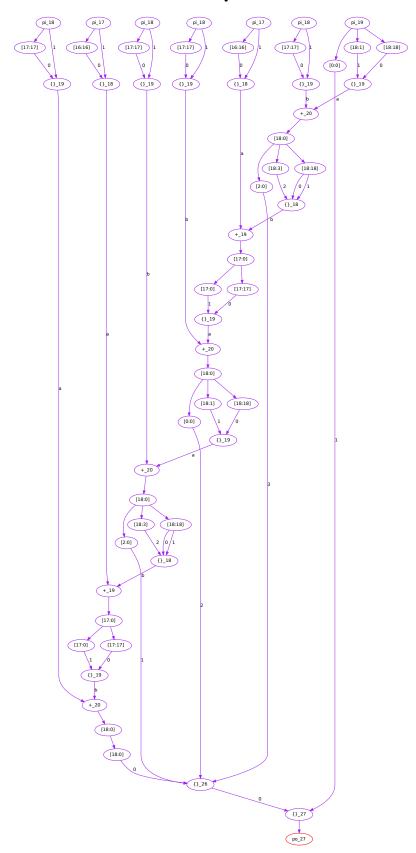

| 3.21 | WNK network for adder-shift tree of lemma_64 (Figure 3.20 line 26, equation $(3.33)$ ) ( $pi$ , $po$ . +,{},[m:n] are input, output, full-adder, concat and extract |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | operators. The number after '_' is the bit-width of the node. )                                                                                                     |

| 4.1  | C vs RTL equivalence checking                                                                                                                                       |

| 4.2  | $sum02\_true-unreach-call.c$                                                                                                                                        |

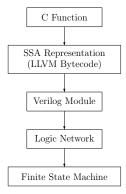

| 4.3  | C-to-Verilog Translation                                                                                                                                            |

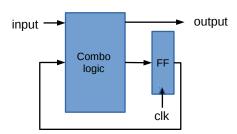

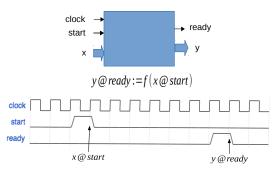

| 4.4  | A single-clock synchronous circuit                                                                                                                                  |

| 4.5  | Verilog factorial implementation                                                                                                                                    |

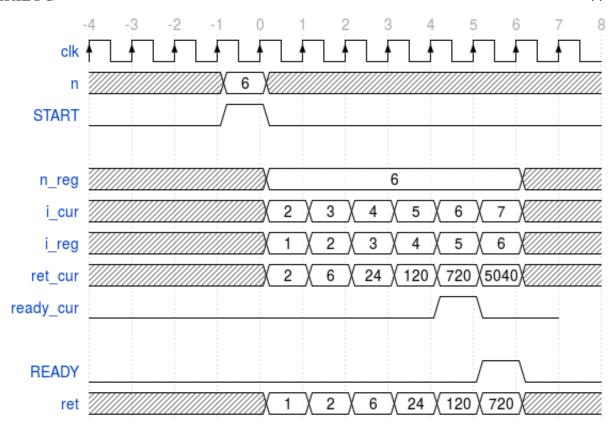

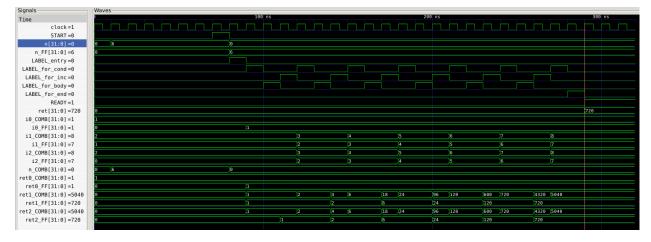

| 4.6  | Waveform for Module $verilogfactorial with n = 6 \dots 77$                                                                                                          |

| 4.7  | C to SSA IR illustration                                                                                                                                            |

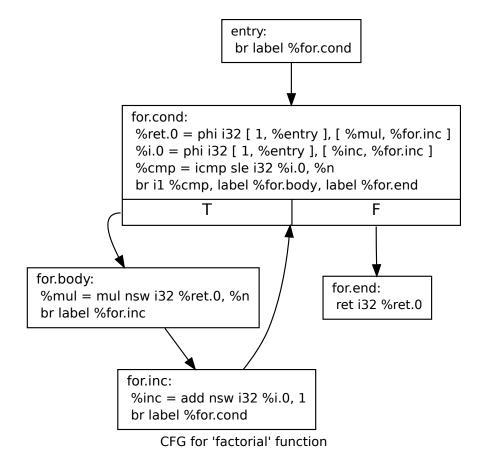

| 4.8  | LLVM CFG                                                                                                                                                            |

| 4.9  | $SSA^b$ from SSA in Figure 4.7c with $phi$ node reverted                                                                                                            |

| 4.10 | Verilog Model                                                                                                                                                       |

|      | SSA access and utility functions                                                                                                                                    |

|      | $SSA^b$ to Verilog Translation                                                                                                                                      |

|      | Translation to Verilog continued                                                                                                                                    |

|      | Translated Verilog module from the $SSA^b$ in Figure 4.9                                                                                                            |

|      | Waveform for Verilog module factorial                                                                                                                               |

|      | test:bitvector-loops/overflow_false-unreach-call1.i                                                                                                                 |

|      | Software Verification Benchmark: bitvector category                                                                                                                 |

## List of Tables

| 2.1 | Result of three data-path transformations                                                                                                                          | 10 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Internal similarities between Adder Trees in Figure 2.3                                                                                                            | 13 |

| 2.3 |                                                                                                                                                                    | 22 |

| 3.1 | Supported operators (unsigned)                                                                                                                                     | 32 |

| 3.2 | Lemma Types $(M_M \text{ is the current model}) \dots \dots$ | 35 |

| 3.3 | Rewriting rules                                                                                                                                                    | 40 |

| 3.4 | Rewriting Widget                                                                                                                                                   | 41 |

| 3.5 |                                                                                                                                                                    | 54 |

| 3.6 |                                                                                                                                                                    | 54 |

| 3.7 |                                                                                                                                                                    | 33 |

| 4.1 | 2015 Software Verification Competition: Bit-Vector category                                                                                                        | 72 |

| 4.2 | Verilog language elements                                                                                                                                          | 75 |

| 4.3 | C language elements                                                                                                                                                | 76 |

| 4.4 | fpu_100: 32-bit FPU                                                                                                                                                | 91 |

| 4.5 |                                                                                                                                                                    | 92 |

## Chapter 1

### Introduction

One of the driving force of high-level language constructs is the need to raise the abstraction level for productivity.

#### 1.1 Motivation

The technological driving force of the chip-design industry is the feature width in the semi-conductor device fabrication process, which reduces from  $10\mu m$  in 1971 to 10nm in 2016. As of 2014, leading SoC (System-on-Chip) designs, such as Apple A8 chip, contains over two billion transistors on a  $89mm^2$  piece of silicon. Ignoring the manufacturing aspect of the chip production process, just focusing on the functions these chips implement, the sheer task of assembling two billion transistors together is a daunting one for human minds to attain. To achieve this, programming languages are relied on to design the functionality and compiler and synthesis technologies are used to generate the circuit.

Figure 1.1 illustrates the conceptual levels of abstraction encountered in a digital design process. The base mathematical model is the finite-state-machine, an enumeration of all states and transitions in the design. At the Boolean logic level (bit-level), design space and state-transitions are abstracted using Boolean variables and logic functions. At the RTL

Figure 1.1: Design Abstraction Levels

level (word-level), the design functionalities are described using programming language constructs and the underlying mathematical model is bit-vector or integer arithmetic. High-level languages provide syntax and semantics for hierarchical and modular design methodologies, which makes it possible to build a chip with billions of transistors.

Hardware design languages, like Verilog or VHDL, have syntactical constructs for clocks, flops, logical gates, bit-vectors, etc. They statically allocate memory and computation resources which corresponds directly to the physical elements in the circuits. On the other hand, software based design languages do not have a clocking concept nor basic logic gates explicitly, but have constructs for integers, while/for loops, dynamic memory allocation, run-time function calls, and threads, etc. This expedites design productivity by describing the functionality through more powerful and expressive programming constructs. In industrial practice, software based languages have been used for prototyping, creating reference models and performance models. These are built in advance and maintained as the RTL design process progresses. In Colwell's "Pentium Chronicles" book[20], the idea for out-of-order pipelined micro-code instruction execution was first validated on VAX's instruction sequences using a software model. During Pentium's design creation at Intel, a behavior model in C was created first and maintained rigorously throughout the design process. The author attributed the use of a C-model as a crucial element in Pentium's product success.

As the design functionality is more frequently being captured in a C program, more recent efforts further utilizing these behavior models are being developed in the following two directions:

- 1. Conducting formal equivalence checking [15][38] between the software model and the RTL design.

- 2. High-level synthesis[14][21][27] is being used to synthesize C/C++/SystemC directly into RTL and Boolean logic circuit models.

#### 1.2 Thesis Contribution

In this thesis, we focused on verification aspects of both of these developments. First, we present LEC: an open system for checking data-path logic equivalence to verify the correctness of high-level synthesis transformations. Second, we present a simple trusted C to Verilog translation procedure to build a finite state model for any C program as long as it does not use dynamic resource allocation. This can be used to build a golden RTL model that can be equivalence checked against the RTL created by the chip design team.

## Chapter 2

# Data-path Design Space and Verification

Know yourself, know your enemy.

Art of War, Sunzi

At times, during the PhD years, I read a bit of Chinese and world history. For the past 2000+ years, history books are marked with battles and wars. Although these were fought individually to determine victories or defeats, winning and losing are mostly pre-determined many many years earlier.

There is a similar notion in designing an algorithm or software: we need to decide if we are fighting a battle or engaging in a war: e.g. are we solving a very specific problem or are we building a system to solve a large class of problems. The strategic planning and preparation phase in such a process decides what problem to solve: a long-term or short-term project, what are the existing techniques available, what will be the foreseeable and unforeseeable obstacles, and how to learn and tackle new obstacles so that the system can grow and evolve over time. These implicit understandings and decisions eventually determine the consequent software architecture and methodology.

In this chapter, we survey the design transformation space in the context of design optimization of arithmetic functions as an introduction to the type of the problems that will be solved. A simple example of adder-tree equivalence checking is used to show that many datapath equivalence checking problems derived from arithmetic optimizations are very difficult to solve using just modern equivalence checking methods, such as Boolean SAT-sweeping: for those problems, we need different methods. We survey techniques in Boolean solving, SMT solving, and theorem proving to illustrate the strengths and weaknesses of existing approaches – which leads to the following strategic observation/conclusion:

There will be no single algorithmic procedure to solve all data-path equivalence checking problems within a practical time limit. Domain specific techniques are required. Therefore, we position the equivalence checking process that we address as a learning process. We build our solver system to be able to integrate existing and future techniques and provide users with aids to extract bottleneck logic and devise new solutions for new problem domains.

#### 2.1 Introduction

From a general perspective, our objective is to compare two combinational logic designs for equivalence. Each logic design has its individual characteristics, so we are looking to take advantage of these during the proof process. At different stages in the chip design process, designs might be crafted or transformed to have very different structural characteristics. The data-path logic targeted in this thesis are inputs to and outputs of the high-level synthesis steps in the design flow. In such a setting, the data-path logic is either in the form of human-written Verilog or C programs obtained from high-level C/Verilog synthesis procedures. These can be created by either automated tools like [14][27] or by human designers. For these design styles, we will assume that they contain bit-vectors and bit-vector operators such as  $+,-,\times,$  detc. (we also refer to these as word-level operators in contrast to bit-level Boolean operators). Data-path equivalence checking is the procedure to validate the correctness of design transformations during this part of the design phase.

In addition to word-level operators, there are also many Boolean structures which we will refer to as control logic. Control logic is used to implement more complex design control structures such as case splitting, pipe-line control, exception handling etc. Thus, the design style being targeted is the implementation of complex arithmetic functions involving both bit and word-level operators. Before formal verification came into play, simulation was the sole

method in validating design correctness. In many cases, the result achieved using simulation was insufficient, as demonstrated by the infamous FPU bug of Intel [54], which cost hundreds of millions of dollars in product recall. There are also many designs such as mission critical applications in the security domain, which require more rigorous validation. In the SoC era, increasingly more complex computations are put into chip designs for image, video, and audio processing. It is beneficial and increasingly necessary to have an effective and efficient way to verify correctness through formal verification, improving both the quality and the productivity of validation.

We refer to the above combinational logic as data-path logic in this thesis. Recognizing the fact that arithmetic logic is a major component in data-path logic, in the next section 2.2 we survey the design scope of arithmetic logic transformations. In Section 2.3, we show that integer addition is a basic operator of these many arithmetic operations. In Section 2.4, a case-study is used to show how proving equivalence of adder-trees can be very challenging in the Boolean domain, leading to the conclusion that reasoning is needed at a higher level of abstraction than Boolean space. In Section 2.5, we survey existing data-path equivalence techniques ranging from Boolean solving to theorem proving.

#### 2.2 Data-path Optimization: The Design Space

Many examples cited here are from the book [35]. The particular optimization techniques that lead to the various transformations are not relevant to this thesis; instead we highlight the possible end results to illustrate the amount of dissimilarities that can be created compared to the original design. This leads to the conclusion that pure Boolean techniques will not be able to solve many of the post-optimization data-path equivalence checking problems efficiently.

#### Constant Multiplication

Multiplication by a constant number is a basic operation implemented using adder trees. For example, decimal number 151 is  $10010111_b$  in binary; and multiplication of 151 and x,  $151 \cdot x$ , can be decomposed into the addition of the following terms:

$$151 \cdot x = (x \ll 7) + (x \ll 4) + (x \ll 2) + (x \ll 1) + x \tag{2.1}$$

$$151 \cdot x = (x \ll 7) + (x \ll 5) - (x \ll 3) - x \tag{2.2}$$

Formula (2.1) adds 5 terms together while (2.2) adds/subtracts 4 terms together. Considering addition and subtraction as having the same cost using two's complement representation of the integers, (2.2) is a better implementation as it uses fewer computation elements. After the constant multiplication is broken up into linear sums, the optimization procedure would then decide on the construction of an adder tree by choosing the order of which pairs of terms are to be added.

Using two's complement representation, -x is converted to  $(\sim x) + 1$ . Formula (2.3) is further optimized to have only adders plus an integer constant:

$$151 \cdot x = (x \ll 7) + (x \ll 5) + (\sim x) \ll 3 + (\sim x) + 9 \tag{2.3}$$

The final choice is determined by the overall optimization objective in the context of the surrounding logic.

#### Finite Impulse Response (FIR) Filter

One step more complex than constant multiplication is a sum of constant multiplication terms, which is a common form of computation for FIR (Finite Pulse Response) filters in Digital signal processing (DSP). An L-tap FIR filter involves a convolution of the L most recent input samples with a set of constants. This is denoted as

$$y[n] = \sum h[k] \cdot x[n-k], \quad k = 0, 1, ..., L-1$$

(2.4)

in which, h[k] are the constants, while x[n-k] are the input bit-vector variables. For such a linear sum formula, the optimization procedure [35] would first decompose each constant multiplication term into a sum of shifted-terms (potentially signed) as those in (2.2) and then apply algebraic techniques to identify common sub-expressions and perform kernel extraction. The end result is an adder-tree structure.

#### Linear Transforms: Constant Matrix Multiplication

A linear transform, in the form of a constant matrix multiplication, is a set of linear sums. This allows even more complexity and transformation possibilities. We use  $Y = C \cdot X$  to

represent constant matrix multiplication, where C is a constant matrix, X is a vector of input variables, Y is the resulting output vector:

$$Y[i] = \sum_{j=0}^{N-1} C_{i,j} X[j]$$

(2.5)

To illustrate the space of transform possibilities, the following [35]  $4 \times 4$  constant matrix is used in a four-point discrete cosine transform (DCT):

$$C = \begin{bmatrix} \cos(0) & \cos(0) & \cos(0) & \cos(0) \\ \cos(\pi/8) & \cos(3\pi/8) & \cos(5\pi/8) & \cos(7\pi/8) \\ \cos(\pi/4) & \cos(3\pi/4) & \cos(5\pi/4) & \cos(7\pi/4) \\ \cos(3\pi/8) & \cos(7\pi/8) & \cos(\pi/8) & \cos(5\pi/8) \end{bmatrix}$$

(2.6)

Using the identities  $cos(\pi/8) = -cos(7\pi/8)$ ,  $cos(3\pi/8) = -cos(5\pi/8)$  etc. and denoting A = cos(0),  $B = cos(\pi/8)$  etc. the matrix multiplication can be written concisely as,

$$\begin{bmatrix} y_0 \\ y_1 \\ y_2 \\ y_3 \end{bmatrix} = \begin{bmatrix} A & A & A & A \\ B & C & -C & -B \\ D & -D & -D & D \\ C & -B & B & -C \end{bmatrix} \begin{bmatrix} x_0 \\ x_1 \\ x_2 \\ x_3 \end{bmatrix}$$

(2.7)

The end result is a forest of adder-trees.

#### Approximation Algorithm

In the above examples, addition is the basic operator of the arithmetic expression. In the case of high-order polynomials, multiplication becomes the target operator for optimization considerations. Consider the Taylor expansion of sin(x) approximated with four terms:

$$sin(x) = x - \frac{x^3}{3!} + \frac{x^5}{5!} - \frac{x^7}{7!}$$

(2.8)

This polynomial of degree 7 approximates the *sine* function very well. Assuming the terms,

$$S_3 = 1/3!, S_5 = 1/5!, S_7 = 1/7!$$

are pre-computed, the naive evaluation of the polynomial requires 3 additions/subtractions, 12 variable multiplications and 3 constant multiplications. However, it is possible to compute this using the following sequence:

$$d_1 = x \cdot x \tag{2.9}$$

$$d_2 = S_5 - S_7 \cdot d_1 \tag{2.10}$$

$$d_3 = d_2 \cdot d_1 - S_3 \tag{2.11}$$

$$d_4 = d_3 \cdot d_1 + 1 \tag{2.12}$$

$$sin(x) = x \cdot d_4 \tag{2.13}$$

Thus only 3 additions/subtractions, 4 variable multiplications and one constant multiplication are needed.

Another example where high-order polynomials are used for approximation is in (2.14) below. This is used in computing quadratic splines, which are used in computer graphics. Such polynomials have degrees not more than 4, and are smooth in both the first and second derivative and continuous in the third derivative.

$$P = zu^4 + 4avu^3 + 6bu^2v^2 + 4uv^3w + qv^4$$

(2.14)

The original formula (2.14) requires 23 multiplications and 4 additions. The following three techniques transform the above polynomial into different implementations.

1. Two-term CSE (common sub-expression) algorithm:

$$d_1 = u^2 (2.15)$$

$$d_2 = v^2 (2.16)$$

$$d_3 = uv (2.17)$$

$$P = d_1 z + 4ad_1 d_3 + 6bd_1 d_2 + 4wd_2 d_3 + qd_2^2$$

(2.18)

2. Using the Horner form:

$$P = zu^{4} + v \cdot (4au^{3} + v \cdot (6bu^{2} + v \cdot (4uw + qv)))$$

(2.19)

3. Using algebraic factoring:

$$d_1 = u^2 \tag{2.20}$$

$$d_2 = 4v \tag{2.21}$$

$$P = u^{3} \cdot (uz + ad_{2}) + d_{1} \cdot (qd_{1} + u \cdot (wd_{2} + 6bu))$$

(2.22)

| Optimization Method | Num Multiply | Num Add |

|---------------------|--------------|---------|

| Two-term CSE        | 16           | 4       |

| Horner              | 17           | 4       |

| Algebraic           | 13           | 4       |

Table 2.1: Result of three data-path transformations

Table 2.1 shows the number of variable multiplications and addition operations needed after the design transformations. The actual implementation decision depends on the context, design constraints and the surrounding logic in which these polynomials are to be implemented.

Equivalence checking of individual multipliers is a well-known challenge already, but verification of these transformed polynomials is even more difficult. This further motivates the need to reason at a higher level rather than purely at the Boolean level.

#### 2.3 About Adding a Set of Numbers

In the above data-path optimization procedures, addition is a basic operation. Multiplier design is a good example of this. An n-bit binary number itself,  $A = a_{n-1}a_{n-2} \dots a_1a_0$ , is defined using a binary integer format by adding n numbers together:

$$A = \sum_{i=0}^{n-1} 2^i \cdot a_i \tag{2.23}$$

$$B = \sum_{j=0}^{n-1} 2^j \cdot b_j \tag{2.24}$$

Then, the multiplication two n-bit binary numbers, equation (2.25), can be seen as a sum of  $n \times n$  partial products of  $2^i a_i \cdot 2^j b_j$ , which forms an  $n \times n$  matrix in Figure 2.1. While

implementing the multiplier, one has to decide the order in which these partial-products are be added, e.g. equation (2.25) adds the columns first, while (2.26) adds the rows first.

$$A \times B = \sum_{i=0}^{n-1} \sum_{j=0}^{n-1} 2^{i+j} \cdot a_i \cdot b_j$$

(2.25)

$$B \times A = \sum_{j=0}^{n-1} \sum_{i=0}^{n-1} 2^{i+j} \cdot a_i \cdot b_j$$

(2.26)

Figure 2.1:  $A \times B = \text{Sum of } n^2 \text{ partial products}$

Multiplication is commutative:  $A \times B \equiv B \times A$ . However, these two multiplier implementations results in a Boolean satisfiability problem from  $A \times B \equiv B \times A$  that is very difficult to solve at the bit level. This is because the two multiplier logics are completely different internally, and applying knowledge of the commutative law at the Boolean level is all but impossible.

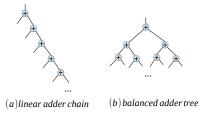

# 2.4 Empirical Study: Eight-Operand Adder-Tree Equivalence Checking

From the above survey, addition is seen to be the basic operator for adder-trees and multiplier implementations. In this section, we evaluate the capacity and performance of the SAT-sweeping procedure in proving pure adder-trees equivalence. As SAT-solving is classified as an NP-complete algorithm, we wonder in what situations it gets easier and in what situations

it gets more difficult. We use the following case-study to help understand the strengths and weaknesses of Boolean methods. The objective is to show that a Boolean solving method has inherent limitations which cannot be resolved within itself; in order to solve these data-path equivalence checking problems, higher level information needs be captured to help reduce the problem complexity. This leads to our belief that we have to enable a tool to reason beyond Boolean logic.

```

module LinearAdderTree

#(

parameter WIDTH = 16)

(

input [WIDTH-1:0] a[7:0],

output [WIDTH+4-1:0] y);

reg [WIDTH+4-1:0] ret;

always_comb begin

ret = 0;

for (int i=0;i<7;i++)

ret = ret + a[i];

end

assign y = ret;

endmodule</pre>

```

Figure 2.2: Linear Adder Tree described in Verilog

The Verilog code in Figure 2.2 implements an eight-operand addition in integer arithmetic: the use of the WIDTH parameter definition guarantees there are no overflow situations.

There are many ways to implement such an adder tree logic. Figure 2.3 shows four examples using linear tree or binary tree topologies, and with different orders of adding terms. Table 2.2 compares the internal similarities between the four structures. Columns 1 and 2 are the two structures being compared. Column 3 gives a ranking of the amount of internal structural similarity between the compared adder-trees. Column 4 shows terms where similarities exist. The first two pairs share the top similarity ranking as they are symmetric and have the same amount of internal similarities. The third pair has slightly more similarities than the remaining three pairs because the two adder tree structures are symmetric and both are full binary trees. The remaining three pairs are dissimilar in roughly the same degree. The

Figure 2.3: adder tree structure.

significance of the similarities are illustrated in the following experiments, which conducted equivalence checking between the varous pairs.

| $Adder_0$       | $Adder_1$         | Similarity Rank | Similarities                                            |

|-----------------|-------------------|-----------------|---------------------------------------------------------|

| Linear          | Binary            | $1^{st}$        | $a_0 + a_1$ , $((a_0 + a_1) + (a_2 + a_3))$             |

| Reversed Linear | Binary            | $1^{st}$        | $a_6 + a_7$ , $((a_4 + a_5) + (a_6 + a_7))$             |

| Binary          | Juxtaposed Binary | $3^{rd}$        | $a_0 + a_1$ , $a_6 + a_7$ vs. $a_0 + a_7$ , $a_1 + a_6$ |

| Linear          | Reversed Linear   | $4^{th}$        | None                                                    |

| Linear          | Juxtaposed Binary | $4^{th}$        | None                                                    |

| Reversed Linear | Juxtaposed Binary | $4^{th}$        | None                                                    |

Table 2.2: Internal similarities between Adder Trees in Figure 2.3

We conducted equivalence-checking between these four adder-tree structures using ABC[2]'s deec command, which is a state-of-art combinational equivalence checking procedure using SAT-sweeping at the bit-level. Such a procedure uses SAT solvers as the main solving engine to establish equivalence by identifying and utilizing internal match-points, i.e. signals in the design that are functionally equivalent to each other. Figure 2.4 shows the run-time results on pair-wise equivalence checking with operand WIDTH from 1 to 35.

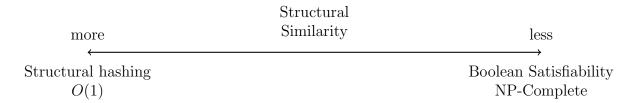

Comparing with Table 2.2, the run-times inversely follow the rankings in similarity. The first two pairs of comparison scale well with WIDTH while the others do not scale. As illustrated in Figure 2.5, the complexity of solving equivalence checking problem ranges from constant time to apparently exponential time; the actual difficulty depends on the amount of internal

Figure 2.4: ABC's deec results

similarities. On the left side is the extreme case that both logic structures are exactly the same, then equivalence can be determined through structural hashing; the output functions are hashed into the same node value. On the right side is the other extreme; logic equivalence has to be established through exhaustively searching the entire Boolean function space: i.e. solving an NP-complete problem.

Figure 2.5: Complexity scale of SAT-Sweeping

The total number of different n operand adder trees is  $P_n^n \times \prod_{i=n}^2 C_i^2$ . From the complexity growth of the 8-operand adder tree example, it seems that pure Boolean methods are unable to solve problems where design transformations render them structurally dissimilar. Knowledge of high-level design functionality is seemingly required.

# 2.5 Survey: Data-Path Formal Verification Techniques

Boolean logic is defined over Boolean space B,  $B = \{0,1\}$ . A Boolean function f of m variables is a mapping of  $B^m \to B$ . Boolean logic functions can be represented as a directed acyclic graph, with each node annotated as a Boolean function, such as an and-invertor graph (AIG). A bit-vector is a set of Boolean variables; a bit-vector function is a collection of Boolean functions.

For convenience, we will refer to a single Boolean variable as a bit, a bit-vector as a word, a function over words as a word-level function or word-level operators. A network which contains word-level operators is called a word-level network.

As illustrated in Figure 2.6, the bit-blasting procedure transforms a word-level operator into a set of bit-level functions; the inverse of this, the procedure to group bit-level functions into word-level operators is sometimes called reverse-engineering, a significantly difficult operation.

$$\begin{array}{c} \text{bit-level} & \xleftarrow{\quad \text{bit-blasting} \quad } \text{word-level} \\ \text{network} & \xrightarrow{\quad \text{reverse engineering}} \end{array}$$

Figure 2.6: Bit-level to word-level transformation

The data-path logic discussed in this thesis refers to any set of arbitrary bit and word-level operators. The focus of the techniques to be developed in this thesis to analyze data-path logic, is to use reasoning on the word-level operators to help in checking bit-level equivalence.

Conceptually, data-path logic specification provides the following:

- 1. a directed graph, with nodes annotated as word level operators with specified input and output widths.

- 2. the word-level operators are from a known library of arithmetic functions.

The remaining sections in this chapter gives an overview of the various techniques available, from Boolean solving to pure theorem proving of first order logic.

#### **Boolean Solvers**

Boolean solving techniques are fundamental and generic in that all data-path logic can be converted into Boolean functions. There are essentially four basic categories for establishing that two Boolean networks are equivalent:

- 1. Structurally the same

- 2. Equivalence through exhaustive simulation

- 3. Equivalence established by SAT solving

- 4. Equivalence established by BDDs

One direction in optimizing Boolean solvers is to improve the performance of the SAT solver and BDD packages. The other direction is to simplify the Boolean logic structure through transformations. The technique of the SAT-sweeping procedures in [12] uses all four categories, structural hashing, simulation, SAT, and BDDs to identify and merge internal equivalent points, thus reducing overall complexity. In [70], the authors further attempted to find more internal points to merge by extending the definition of equivalent nodes under the condition of observability don't cares. [11] tries to minimize intermediate BDD size through converting a BDD relation into a corresponding parametric representation with a smaller set of BDD variables. State-of-art equivalence checking procedures [52] provides a highly integrated and optimized implementation of AIG [43] rewriting, simulation, SAT-sweeping and logic synthesis techniques. This has led to dramatic improvements over earlier implementations.

The advantage of these Boolean solvers is that they are generic and fully automated. They are very good at finding discrepancies and providing error traces if the designs are not equivalent. However, on proving equivalence, their strengths becomes their own weakness, as the complexity is NP-complete. If two designs are structurally dissimilar, then obtaining an equivalence proof can be very difficult. On the other hand, there can exist a trivial proof even when structural dissimilarity exists, e.g. for summing eight integers, equivalence can be established through commutative, associative and distributive laws of the '+' operator. Clearly an advantage can be obtained if knowledge of the '+' operator can be integrated into the Boolean solving methods.

#### The Use of Un-Interpreted Functions (UIFs)

The use of un-interpreted functions (UIFs) tries to simplify the equivalence checking program by introducing constraints from the functional level. The principle of UIF derives from the general definition of what is a function: a function is a mapping from its input domain to its output domain which requires that for the same inputs, the output is always the same:

if

$$f \equiv g$$

then

$$\forall X \forall Y, \quad s.t. \quad X = Y \Rightarrow f(X) = g(Y)$$

We use the miter logic formulation in Figure 2.7 to illustrate the utilization of the knowledge of a function. In Figure 2.7, the left side has two multiplier instances while the right side has only one; this might have been the result of minimizing the number of computation units during an optimization phase. If the multipliers are wide, it is a difficult problem to prove equivalence using purely Boolean techniques.

Figure 2.7: Use of UIF

For this particular design, the detailed functionality of the multiplier is not needed proving the logic equivalence. In this case, the multiplier function can be replaced with any function, and the equivalence would still hold provided the two functions being paired are the same function. The UIF technique utilizes such an observation and performs the following two steps:

- Remove the internal logic of each multiplier and create new free-input variables for each multiplier output.

- Add the following constraints/lemmas to the miter logic

$$(a=j) \& (b=k) \quad \Rightarrow \quad m=g \tag{2.27}$$

$$(c=j) \& (d=k) \quad \Rightarrow \quad m=h \tag{2.28}$$

and similarly when j and k are interchanged. Each of these implications is known as a UF constraint. In this case, a UF constraint is put between every multiplier on the left and every one on the right. By taking advantage of the knowledge that functions m, g and h are the same functions, the transformed Boolean satisfiability problem is then easily proven using SAT solvers, thereby proving the original problem. Note that even if the internal logic of the multipliers is not removed, the UF constraints still can be asserted and may be effective because they establish a relation between the two halves of the miter to be proved equivalent. Note also that although the UF constraints are implied by the Boolean logic of the miter, it would be essentially impossible to establish this from reasoning at the bit-level. This information comes from a higher level knowledge that m, g and h are the same functions.

#### Satisfiability Modulo Theory(SMT) Solvers

The UIF approach is the simplest framework to utilize the knowledge that part of the design is implementing a high-level function, while the details of the function's definition are not needed. To extend the use of high-level functions, the next level is to be able to reason about a function's input/output definition. In the data-path equivalence checking domain, it requires the prover to represent and reason about quantifier-free first order logic.

Formally, an SMT instance [59] is a formula in quantifier-free first-order logic, and SMT is the problem of determining whether such a formula is satisfiable. Imagine a Boolean SAT instance in which some of the binary variables are replaced by "predicates" over a suitable set of non-binary variables. A predicate is basically a binary-valued function of non-binary variables. Example predicates include (integer) linear inequalities (e.g., 3x + 2y > 6, z >= 4) or equalities involving so-called uninterpreted terms and function symbols (e.g., f(f(u, v), v) = f(u, v) where f is some unspecified function of two unspecified arguments.) We are still dealing with a satisfiability problem, except that its solution now depends on our ability to determine the satisfiability of the underlying predicates.

In summary, an SMT instance is a generalization of a Boolean SAT instance in which various sets of variables are replaced by predicates from a variety of underlying theories. Practically, SMT formulas provide a much richer modeling language than what is possible with Boolean SAT formulas. In particular, for data-path equivalence checking, the QF\_BV SMT [59] constructs allows us to model the data-path operations at the word rather than the bit level, which is equivalent in expressiveness to Verilog operators.

Early attempts at solving SMT instances involved translating them to Boolean SAT instances (i.e. bit-blasting the word-level operators into bits) and passing this (much larger) formula to a Boolean SAT solver. This approach has its merits: by pre-processing the SMT formula into an equivalent Boolean SAT formula we can use existing Boolean SAT solvers "as-is" and leverage their performance and capacity improvements over time. On the other hand, the loss of the high-level semantics of the underlying theories means that the Boolean SAT solver has to work a lot harder than necessary to discover "obvious" facts (such as  $x \cdot y = y \cdot x$  for integer multiplication.) This observation was the impetus behind the development, over the last several years, of a number of SMT solvers that tightly integrate the Boolean reasoning of a DPLL-style search with theory-specific solvers that handle conjunctions (ANDs) of predicates from a given theory.

Dubbed DPLL(T) [63], or Generalized DPLL [50], this architecture gives the responsibility of Boolean reasoning to the DPLL-based SAT solver which, in turn, interacts with a solver for theory T through a well-defined interface. The theory solver need only worry about checking the feasibility of conjunctions of theory predicates passed on to it from the SAT solver as it explores the Boolean search space of the formula. For this integration to work well, however, the theory solver must be able to participate in both propagation and conflict analysis, i.e., it must be able to infer new facts from already established facts, as well as to supply succinct explanations of infeasibility when theory conflicts arise. In other words, the theory solver must be incremental and back-trackable while the theory's implementation varies and is domain-specific.

Relevant to the data-path equivalence checking problems is the SMT QF\_BV(Quantifier Free Bit Vector Arithmetic) solvers. One of its contributions is the introduction of word-level operators that allows word-level structures to be represented in the problem formulation. In some of the leading SMT solvers [13][23][34], word-level techniques such as rewriting, abstraction refinement and reduction etc. are applied. Depending on the underlying theory

used or extracted from the QF\_BV formulation, the generalized DPLL framework is used to integrate the Boolean SAT solvers. Furthermore, when the problem remains unsolved, bit-blasting the QF\_BF formulation into a CNF formula is the last resort for most of the leading SMT bit-vector solvers, Boolector [13], z3 [23], Beaver [34]. If this bit-blasting does not solve the problem, the programs terminate without an answer.

The advantages of SMT solving using the Generalized DPLL framework are that it is a generic, automated method and empirically often effective in finding counterexamples if the designs are not equivalent. However, this strength leads to a weakness that the SMT solvers still treats the underlying problems as a Boolean satisfiability problem which is inherently NP-complete – potentially very difficult or impossible to solve.

#### Theorem Proving

While Boolean SAT solvers inherently are solving an NP-Complete problem, theorem prover attempts to provide an alternative. By reasoning in first order logic, a theorem prover integrates Boolean logic and high-level functions natively. In comparing to a pure theorem proving approach, SMT solving is a hybrid approach as it has the ability to represent first order logic for a specialized theory and integrates Boolean solvers at the same time. For theorem proving in the data-path equivalence checking domain, the subject of interest is quantifier-free first order logic. We use an example, from [36], to illustrate the thought process of theorem proving. We show that theorem proving is not only a method but also a necessity in its problem formulation. Theorem proving differs fundamentally from Boolean solvers because a proof is based on symbolic rewriting and mathematical induction rather than Boolean SAT solving – hence theorem proving does not try to solve the data-path equivalence checking problem as an NP-complete problem.

The Verilog module in Figure 2.8a implements a 32-bit ripple-adder and we create an equivalence checking problem by comparing it with adder 32 in Figure 2.8b:

$$ripple\_adder32 \equiv adder32$$

(2.29)

The proof objective is the following:

Does above (2.29) check that Verilog module  $ripple\_adder32$  implement the addition of two binary integer numbers correctly.

```

module ripple_adder32(

module adder32(

input cin,

input cin,

input [31:0] a0,

input [31:0] a0,

input [31:0] a1,

input [31:0] a1,

output [31:0] o,

output reg [31:0] o,

output reg cout );

output cout ) ;

assign cout, o = a0 + a1 + cin;

always_comb begin

endmodule

cout = cin;

(b) Verilog Adder

for (i=0;i<32;i++) begin

o[i] = a0[i] ^ a1[i] ^ cout;

cout = (a0[i] \& a1[1])

| (a0[i]& cout)

| (a1[i] & cout);

end

end

) ;

endmodule

```

(a) Verilog Ripple Adder

The answer seems to be a either "YES" or "NO", but the truth is: the equivalence checking of (2.29) cannot answer the question. The reason is a problem formulation mismatch: the proof objective is about natural numbers adding together, whereas the Verilog module is in the Boolean domain which does not have the concept of what a natural number is. The above proof objective about integer addition can not be answered in the Boolean domain solely (i.e. using the formula 2.29), because in Boolean logic, one cannot reason about '+' in integer domain. To prove  $ripple\_adder32$  correctly adds two natural numbers together, first order logic is needed to express what is a natural number, as well as to formulate the definition of '+' as a function connecting it to Boolean logic.

Thus the objective of the verification is no longer a data-path equivalence checking problem at the RTL level, but a mathematical one using first-order logic. We use ACL2 to illustrate such a process by constructing a ripple adder in ACL2 and illustrate the correctness formulation along with the proof procedure.

| Name    | Axiom, Definition, or Theorem                     |

|---------|---------------------------------------------------|

| Thm 1   | $t \neq nil$                                      |

| AX 2    | $x = nil \longrightarrow (if \ x \ y \ z) = z$    |

| AX 3    | $x \neq nil \longrightarrow (if \ x \ y \ z) = y$ |

| Def not | $(not \ p) = (\ if \ p \ nil \ t)$                |

| Ax 4    | $(car\ (cons\ x\ y)) = x$                         |

| Ax 5    | $(cdr\ (cons\ x\ y)) = y$                         |

| Ax 6    | $(consp\ (cons\ x\ y)) = t$                       |

| Thm 7   | $(endp \ x) = (not \ (consp \ x))$                |

|         |                                                   |

Table 2.3: ACL2 Axioms

#### ACL2 Introduction

ACL2 functions and theorems are established using a small set of basic axioms and theorems. Everything else is constructed from these basic logic elements. Table 2.3 shows the list of Axioms and Theorems that are used by the ACL2 theorem prover [37]. The first four define two basic values t and nil, along with the definition of the if and not functions. Note, they are just symbols, although t and nil can be thought of as true and false in Boolean logic. Computation in ACL2 logic is symbolic, using the rules of substitution, inference, and mathematical induction. In ACL2, a list is also a first order object. cons is the function that takes an element and a list as inputs, and prepends the element to the head of the list. The Operator car gets the first element of the list, while cdr gets the rest of the list by removing the head of the list.

To illustrate the semantics, we use Python to model the car and cdr functions as follows:

```

def car(lx) :

if lx == nil :

return nil

assert len(lx) > 0

return lx[0]

def cdr(lx):

if lx == nil or len(lx) == 1:

return nil

else :

```

```

return lx[:-1] pass

```

By ACL2 definition, it is illegal to call car over an empty-list value, but car over nil returns nil, so does cdr (nil is not equivalent to the empty-list value). In Ax 6, the predicate 'consp' returns t if its operand can be represented as  $(cons \ x \ y)$ . endp is the opposite of consp. So we have the following results:

```

( car nil ) = nil

( cdr nil ) = nil

( car (cons t nil) ) = t

( cdr (cons t nil) ) = nil

(endp (const t nil)) = nil

(consp (const t nil)) = t

```

#### ACL2 Boolean Logic Definition

Using ACL2 functions, the following defines Boolean-valued functions: and, or, xor and the majority function (bmaj).

A full adder function has three inputs (bits) and returns a multi-value (mv is the keyword for multi-value): a sum and a carry, which is defined as follows:

```

(defun full-adder ( p q c )

( mv (bxor p ( bxor q c ) )

```

This is a recursive definition of a ripple-adder tree. The bit-vectors x and y are ordered lists of binary values, i.e. nil and t. The least significant bit of the bit-vector (LSB) is the first element and most significant bit (MSB) is the last element in the lists x and y. The operation  $(car\ x)$  returns the LSB of x and  $(cdr\ x)$  returns the rest of the bits. In ACL2, value nil and a list of nil values are practically the same, as car and cdr on both values return nil. Because of this, the above formulation doesn't require x and y to have the same length. One can think of the shorter operand as having been appended with nil, just as the high order bits of a binary number is prepended with 0.

#### ACL2 Integer and Integer Addition Definition

The following function 'n' is defined that maps a binary integer number from the list of t and nil values:

To illustrate the above semantics in Python, the function n would be defined as follows:

```

def n(v):

if len(v) == 0:

```

```

return 0

elif v[0] == True:

return 1 + 2*n(v[1:])

else :

return 2 * n(v[1:])

```

#### ACL2 Proof of Serial Adder Implementation

Both + and \* operators are first class objects and are just symbols, which carries no computational semantics. The proof obligation of correctness of the serial-adder is formulated as the following theorem:

The above is essentially proving that adding x, y, c together using + is the same as the natural number obtained after they are added together using the serial-adder function.

$$n(serial-adder(x, y, c)) \equiv n(x) + n(y) + n(c)$$

(2.30)

The proof is obtained by mathematical induction. The reader can check the basic step of the induction. For the inductive step, ACL2 effectively checks the following implication:

In English, the above is proving that if serial-adder is correct for list x and list y then serial-adder would be correct for list  $(x0 \ x)$  and list  $(y0 \ y)$ , i.e. the lists with one more element prepended to the front. ACL2 has rigorous theories and procedures for reasoning using induction, and for the scope of this thesis, ACL2 obtains the proof by proving the following two lemmas first:

Not so surprisingly, the above two lemmas are proving that the serial-adder is adding '0' and '1' correctly. Different from Boolean equivalence checking, the proof of correctness is generic over any length of input list x and list y.

The above proof formulation and proof is not a data-path equivalence checking problem where two Boolean logics are compared. However, the theorem prover approach can be applied to data-path equivalence checking as a bridge: the proof is obtained by proving both designs implement the same high-level function. In our example, the equivalence of the adder trees in Section 2.4 can be established if we can prove they all implement the same binary-number-adding function, e.g.

#### Theorem Proving Summary

In the ACL2 methodology for data-path equivalence checking, SAT-sweeping in the Boolean domain is not used; instead, it uses a proxy function in first order logic to establish the equivalence. Theorem proving is a complementary approach to Boolean solvers as it does not explore the Boolean space, therefore it does not need to solve an NP-Complete problem.

First order logic is expressive enough to formulate any arithmetic or algebraic function. In theory, for equivalent data-path designs, a proof can always be constructed using a theorem prover. Although this seems to be a promising technique by not casting into an NP-complete problem, in practice, theorem proving has very limited applications for three reasons:

- 1. It is a usability issue. Designs are mostly expressed in hardware or software programming languages. To reason in first order logic, designs must be translated into first order logic which imposes extra overhead required for debugging and validation. Also, first order logic is an abstract and difficult-to-use language for most people, and only for very specific application domains is the theorem proving method used.

- 2. The main strength of theorem proving is mathematical induction, which is also a weakness. For it to work, the target function needs to have a regular pattern such that it can be defined recursively. A recursive definition framework may fit for arithmetic functions such as integer addition, multiplications, divisions etc, but it is unsuited for arbitrary Boolean control logic. For this particular reason, theorem provers are limited practically to proofs in the purely arithmetic domain. There are two natural directions to improve the application of theorem proving. One is to build extensive libraries such that it can be applied to more complex functions. In ACL2, these are called ACL2 books. The other direction is to incorporate Boolean engines into the theorem prover by integrating the definitions of AIGs and SAT solvers in order to handle arbitrary Boolean logic. To preserve the rigor of theorem proving, AIG and SAT solvers need to be defined from the ground up. Once this is done, the usability of theorem proving can be extended to more complex design spaces.

- 3. Successful application of theorem proving techniques requires a deep understanding of the design implementation because the proof is obtained through breaking down internal structures. From the ripple-adder example, the proof is built upon the recursive structure of the ripple-adder implementation. The implication of such a proof is that the verification effort may not be reusable: a change in the design internals may potentially require a completely different proof. Also, it takes effort and is a productivity cost to gain such deep knowledge of a design's internal details. On the other hand, using simulation or Boolean solving methods, verification engineers only need to model the design functionality at the interface level and the validation model is reusable as long as the design functionality remains the same the internal implementation decisions and changes do not impact the validation model.

In the next Chapter, we present our LEC data-path equivalence checking system which has the following characteristics:

- LEC's ultimate goal is to find a way to solve all data-path equivalence checking problems.

- For ease of use, LEC uses Verilog/VHDL as the input language and retains the original design structure throughout the proof finding process.

- Similar to ACL2 books, the LEC system achieves reuse by integrating new techniques into an existing system, and thus LEC becomes more powerful when it is applied to a new problem domain.

- As design knowledge is needed inevitably to obtain a proof, LEC is a learning aid to extract and understand logic that presents a *bottleneck* in the proof process.

LEC is extensible. Building and using LEC are both learning processes, while the learning is expedited by LEC.

# Chapter 3

# LEC: Learning-Driven Equivalence Checking

We build a system to learn, expand and grow with the unknown.

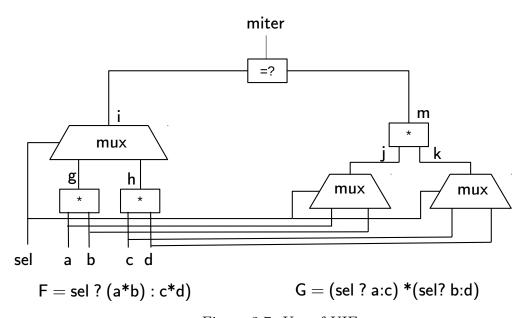

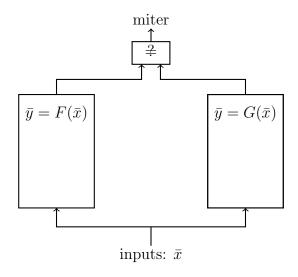

The problem formulation in this chapter is to compare two logic functions, F and G , for equivalence :

$$\forall \bar{x} \quad F(\bar{x}) = G(\bar{x}) \tag{3.1}$$

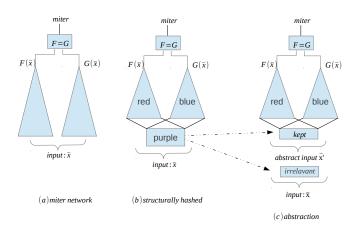

Both F and G are combinational logic circuits described in Verilog/VHDL. For equivalence checking, a miter logic, shown in Figure 3.1, is formed to compare the two. The formulation is also a Boolean satisfiability model of trying to satisfy  $F \neq G$ . The proof result is either UNSAT if  $F \equiv G$ , SAT if  $F \neq G$  or UNRESOLVED if  $F \equiv G$  can not be determined.

# 3.1 Overview: A Learning Process - Philosophy

One of the key aspects of this work is to view the equivalence checking problem as a learning process and to implement a Learning-Driven Equivalence Checking (LEC) tool flow to enable and expedite the process. Our learning process and our implementation of LEC recognizes that:

Figure 3.1: Miter logic

- 1. There will always be a new problem that can not be resolved,

- 2. But a LEC-type tool can be extended to solve many un-solved problems.

This is a limited claim because the data-path optimization techniques in the previous chapter would seem to be able to introduce a new miter problem that is beyond LEC's current proof capabilities. On the other hand, LEC is implemented to enable learning about un-solved problems encountered, identifying bottleneck components and discovering and enabling new techniques to solve them. Hence, we expect that our LEC system (henceforth just called LEC) should evolve over time. We believe that

- 1. every unsolved miter logic is an opportunity for LEC to grow, improve and become more powerful,

- 2. by using LEC, we can gain knowledge of the underlying Boolean logic, identify bottleneck components, reverse engineer and abstract it into high-level arithmetic or algebraic formulae, and that

- 3. learning itself expedites future learning.

LEC is architected to facilitate the integration of different approaches, automate reuse of implemented methods, and enable the development of new techniques in future applications.

In some sense, every tool development is a learning process. However, we embrace this as a strategic view and try to build LEC to enable and expedite learning for both user and tool developer. The LEC system is designed with an open architecture so that it can be used also as a manual aid to unravel a miter logic. The process to get to a proof should be one that gradually learns about the design and develops/integrates new techniques which help to transform an unknown into an identified unknown, and eventually to a known.

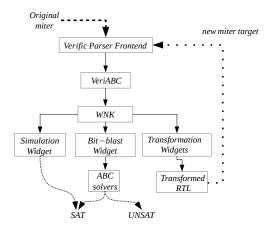

# 3.2 Tool Flow and Organization

LEC takes Verilog/VHDL designs as inputs and is divided into a front-end and a back-end, with a WNK (word-level-network) as an intermediate representation. A WNK is a data-structure that explicitly represents the bit-vector arithmetic operators expressed in Verilog language or SMT QF\_BF specification[59]. Shown in Figure 3.2, the LEC front-end uses a Verific RTL parser [64] to compile the input RTL into the Verific Netlist Database and then translates this into a WNK. The Verific Netlist Database is a graph structure that captures the design hierarchy and connectivity information. Our VeriABC[48] system processes a Verific Netlist, flattens the hierarchy and obtains a WNK representation, which captures the circuit function topologically. Except for the hierarchical information, WNK is a close-to-verbatim representation of the original RTL description. Most importantly, it keeps all high-level information of the original RTL. A WNK is the central core of the LEC infrastructure.

The LEC back-end consists of a set of *widgets* which perform various transformations, solving tasks, or learning tasks on WNK data structures. The use-model of LEC is a sequence of recursive applications of the LEC widgets.

### Word-Level Network(WNK)

A LEC word-level network (WNK) is a directed acyclic graph representing the logic function. Each node in the graph contains three attributes: operator type, width, and an array of fanin nodes. In Figure 3.3 it is defined in the C + + class definition.

(rkb you have two captions here???)

The type of operator indicates the logic function at the node. Table 3.1 lists the unsigned

Figure 3.2: Overall tool flow

Figure 3.3: Illustration WNK node in C++ class

operators in WNK which correspond to the operators in the Verilog language definition. The operators also have their equivalents in the SMT QF\_BV[59] specification. Along with the operator attributes, the node is associated with an integer  $\_width$  to indicate the length of the bit-vector it represents. The incoming edges at a node are represented by the  $\_faninx$  array.

|            | Verilog operator types                   | SMT QF_BV operator types               |

|------------|------------------------------------------|----------------------------------------|

| Boolean    | &&, $\parallel$ , $!$ , $\oplus$ , $mux$ | and, or, not, xor, ite                 |

| bit-wise   | $\&,  , \sim, \oplus, mux$               | bv and, bv or, bv not, bv x or, bv ite |

| arithmetic | +,-,*,/,%                                | bvadd, bvsub, bvmul, bvdiv, bvmod      |

| extract    |                                          | extract                                |

| concat     | {}                                       | concat                                 |

| comparator | <,>, <, ≥                                | bvugt, bvult, bvuge, bvule             |

| shifter    | ≪,≫                                      | bvshl, bvshr                           |

Table 3.1: Supported operators (unsigned)

Any synthesizable Verilog module can be translated to such a WNK, which has the same expressiveness as SMT Bit-Vector Arithmetic. Book-keeping information is kept during the translation so that the signal names in the Verilog source code are mapped onto the WNK nodes. A topological traversal of the network from inputs to outputs evaluates the output logic function depending on the input values. For LEC, the WNK structure is self-contained as it captures both the structural and functional information of the miter logic. Learning, reasoning and transformations are executed on this structure.

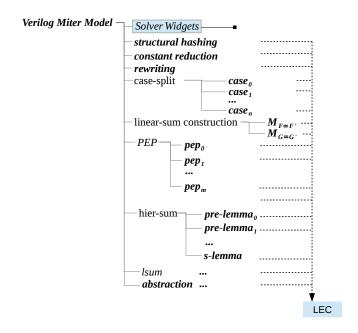

# 3.3 The LEC Widgets

The LEC back-end is organized as a collection of widgets. LEC proofs are obtained through iterative applications of these widgets. LEC has three categories of widgets based on their functionality:

- 1. Solver widget,

- 2. Transformation widget,

- 3. Learning widget.

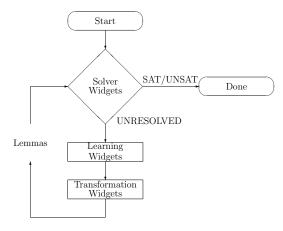

The LEC proof process is illustrated in Figure 3.4. Solver widgets are used to solve the problem directly, which can return SAT, UNSAT or UNRESOLVED as the proof result. If it returns UNRESOLVED, then learning and transformation widgets are applied to try to transform the unresolved problem into a set of sub-models. These can be seen as lemmas derived/decomposed from the original model. Each such lemma sub-model is a possible proof target in the next LEC iteration. A LEC iteration basically calls LEC again so that all the widgets can be used to break down the unresolved parts further. The final LEC proof consists of an iterative application of these widgets.

# Solver Widgets

The goal of a solver widget is to produce a definitive answer: SAT or UNSAT. The following lists the set of basic solver widgets currently implemented in LEC:

1. Random simulation using Verilator [60]

Figure 3.4: Proof process

- 2. Word-level network simulation using a WNK

- 3. Parallel bit-level simulation on an AIG model

- 4. SAT-sweeping using ABC's deec and iprove [52] commands

- 5. LEC's internal SAT solving over the AIG based on ABC's minisat[25] implementation.

The first three use simulations as the underlying algorithm and the other two use SAT sweeping algorithms. The set of solver widgets can be extended by integrating a set of widgets together into a single composite widget (solver widget script), as long as the result is able to return SAT, UNSAT given the proof target.

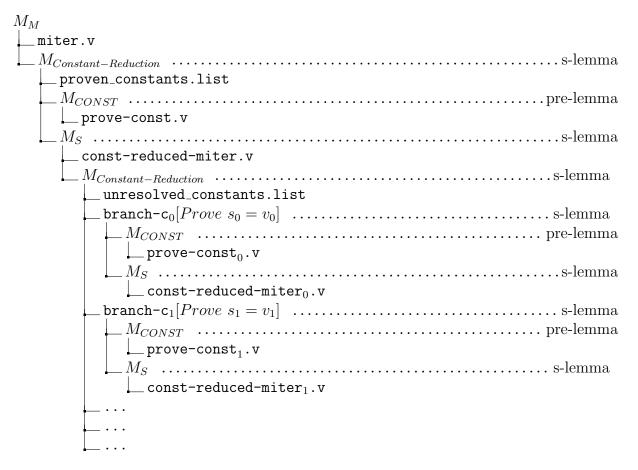

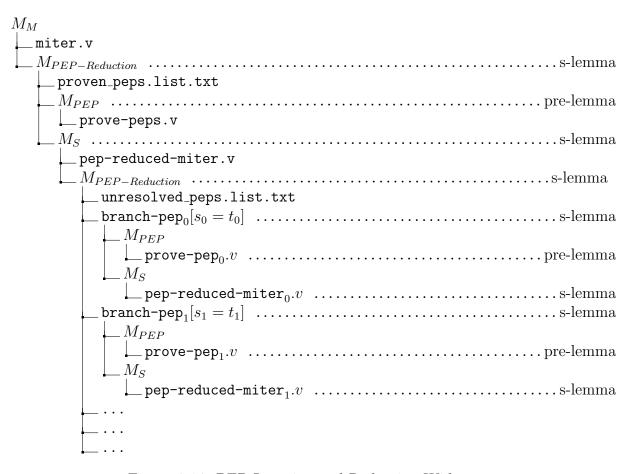

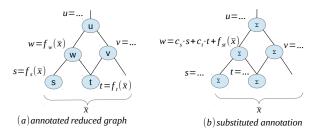

# Transformation Widgets and Sub-model Trees

LEC proofs are built on the use of the transformation widgets. Each transformation widget performs a deterministic function following a set of input instructions to convert the root miter model into a set of sub-models. There is an implicit logical relationship between the root model the generated sub-models, where logical inference rules are applied to derive the sub-models from the root model. We would like to capture these inference rules explicitly to record the proof process.

For logical inference, the most generic rule is **modus ponens**:

"if p then q" is accepted, and the antecedent (p) holds, then the consequent (q) may be inferred.

In LEC, this is cast as an assume-guarantee (A/G) framework:

if the assumptions hold (i.e. are proven) then the satisfiability of original miter model can be derived from the set of generated sub-model lemmas.

| Lemma Types                  | Inference Rule                                                                                                        | Example use scenario       |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------|--|

| $\operatorname{pre-lemma}_i$ | preconditions: must all be proven UNSAT                                                                               | assume/guarantee reasoning |  |

| s-lemma                      | $UNSAT(s-lemma) \Rightarrow UNSAT(M_M)$<br>$SAT(s-lemma) \Rightarrow SAT(M_M)$                                        | structural hashing         |  |

| $e$ -lemma $_i$              | $\exists i  SAT(\text{e-lemma}_i) \Rightarrow SAT(M_M) \\ \bigwedge_i UNSAT(\text{e-lemma}_i) \Rightarrow UNSAT(M_M)$ | case-split enumeration     |  |

| a-lemma                      | $UNSAT(a-lemma) \Rightarrow UNSAT(M_M)$                                                                               | over-approximation         |  |

| u-lemma                      | $SAT(\text{u-lemma}) \Rightarrow SAT(M_M)$                                                                            | under-approximation        |  |

Table 3.2: Lemma Types  $(M_M$  is the current model)

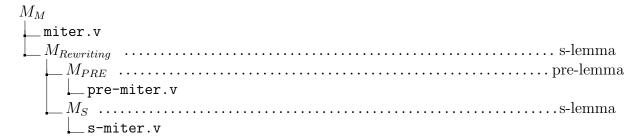

Given the above insight, we explicitly captures the inference rules used in all LEC proofs through the five lemma-types in Table 3.2. The satisfiability of the original miter model  $M_M$  is inferred from the satisfiability of its sub-model lemmas. The presence of pre-lemma<sub>i</sub> captures the assumption components in the A/G reasoning, all of which need to be proven UNSAT in order for this transformation to be valid. The rest of the lemma types are for the "guarantees" which are used to infer  $M_M$ 's proof results from its sub-model lemmas. An s-lemma indicates equisatisfiability: its (un)satisfiability is equivalent to the (un)satisfiability of original miter model  $M_M$ . The {e-lemma<sub>i</sub>} set is the result of case-split enumerations where their conjunction is equivalent to  $M_M$ . An a-lemma is an over-approximation (e.g. resulting from abstraction techniques), while the u-lemma is an under-approximation of the original  $M_M$ .

The method of lemma generation from the transformation widgets allows transformations to be carried out arbitrarily, allowing both valid and invalid transformations during LEC proof process. The correctness of the final LEC proof is guaranteed through the existence of *pre-lemma*<sub>i</sub>: transformations with falsified or unresolved pre-lemma<sub>i</sub> are omitted from the

final proof construction. These invalid transformation intuitively corresponds to failed trial efforts.

In summary the transformation widgets and the generated lemma sub-models achieve the following:

- 1. The task of a LEC transformation widget is to perform an atomic operation which transforms the current model into a set of lemma sub-models using a specific set of inference rules. The widget is a deterministic function given a set of input instructions on how the transformation is to be carried out no complex procedures such as Boolean solving, refinement, etc are involved.

- 2. The correctness of LEC's implementation of the transformation widgets is highly assured due to the simpleness of the procedure itself.