# UC San Diego UC San Diego Electronic Theses and Dissertations

## Title

CAFE : a framework for cell application development

## Permalink

https://escholarship.org/uc/item/6b2233c8

### Author Hammer, Joseph Keith

# Publication Date 2007

Peer reviewed|Thesis/dissertation

## UNIVERSITY OF CALIFORNIA, SAN DIEGO

CAFE: A Framework for Cell Application Development

A thesis submitted in partial satisfaction of the requirements for the degree Master of Science

in

**Computer Science**

by

Joseph Keith Hammer, Jr.

Committee in charge:

Professor Scott Baden, Chair Professor Sheldon Brown Professor Geoffrey M. Voelker

2007

Copyright

Joseph Keith Hammer, Jr., 2007

All rights reserved.

The Thesis of Joseph Keith Hammer, Jr. is approved:

Chair

University of California, San Diego

2007

## Dedication

To my parents:

For my father, who always pushed me to be the best I could be... For my mother, who always supported me in what I wanted to do...

## **Table of Contents**

| Dedication                                                                                                                                                                                                                                                                                                                          | iv                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Table of Contents                                                                                                                                                                                                                                                                                                                   | v                          |

| List of Figures                                                                                                                                                                                                                                                                                                                     | viii                       |

| Acknowledgments                                                                                                                                                                                                                                                                                                                     | x                          |

| Abstract                                                                                                                                                                                                                                                                                                                            | xii                        |

| Chapter 1: Introduction                                                                                                                                                                                                                                                                                                             | 1                          |

| <ul> <li>1.1 Architecture Trends and Revolutions</li> <li>1.2 Parallelism</li> <li>1.2.1 Control-Level Parallelism</li> <li>1.2.2 Data-Level Parallelism</li> <li>1.3 Next-Gen Architecture: IBM Cell</li> <li>1.4 CAFE: Cell Architecture Framework and Extensions</li> <li>1.5 Conventions</li> <li>1.6 Thesis Outline</li> </ul> | 3<br>3<br>4<br>6<br>8<br>9 |

| Chapter 2: Introducing the Cell Processor                                                                                                                                                                                                                                                                                           | 12                         |

| 2.1 The Cell Processor                                                                                                                                                                                                                                                                                                              | 12                         |

| 2.2 PPU: PowerPC Processing Unit                                                                                                                                                                                                                                                                                                    |                            |

| 2.3 SPU: Synergistic Processing Unit                                                                                                                                                                                                                                                                                                |                            |

| <ul><li>2.3.1 Processor</li><li>2.3.2 Local Store</li></ul>                                                                                                                                                                                                                                                                         |                            |

| 2.3.3 Branch Prediction                                                                                                                                                                                                                                                                                                             |                            |

| 2.4 Communication Mechanisms                                                                                                                                                                                                                                                                                                        |                            |

| 2.4.1 Mailboxes                                                                                                                                                                                                                                                                                                                     |                            |

| 2.4.2 Direct Memory Access (DMA)                                                                                                                                                                                                                                                                                                    | 19                         |

| 2.4.3 Signals                                                                                                                                                                                                                                                                                                                       | 21                         |

| 2.5 Programming Models                                                                                                                                                                                                                                                                                                              |                            |

| 2.5.1 Function-Offload Programming Model                                                                                                                                                                                                                                                                                            |                            |

| 2.5.2 Chaining Programming Model                                                                                                                                                                                                                                                                                                    |                            |

| 2.6 Summary                                                                                                                                                                                                                                                                                                                         | 24                         |

| Chapter 3: Related Work                                                                                                                                                                                                                                                                                                             | 26                         |

| 3.1 Stream Processing Solutions                                                                                                                                                                                                                                                                                                     | 26                         |

| 3.1.1 Brook Programming Language                                                                                                                                                                                                                                                                                                    |                            |

| 3.1.2 PeakStream Platform                                                                                                                                                                                                                                                                                                           |                            |

| 3.2 Function-Offload Solutions for Cell                                                                                                                                                                                                                                                                                             | 30                         |

| 3.2.1 Offload API                                                                                                                                                                                                                                                                                                                   |                            |

| 3.2.2 RapidMind Development Platform                                                                                                                                                                                                                                                                                                |                            |

| 3.3 Alternative Programming Models for Cell                                                                                                                                                                                                                                                                                         | 35                         |

| 3.3.1 Sequoia Programming Language                         |    |

|------------------------------------------------------------|----|

| 3.3.2 MultiCore Framework                                  |    |

| 3.3.3 Cell Superscalar                                     |    |

| 3.4 Potential of Cell for Scientific Computing             |    |

| 3.4.1 Architectural Modifications                          |    |

| 3.4.2 Performance Benchmarks                               |    |

| 3.5 Analysis and Insight                                   |    |

| 3.5.1 Portable Development Solutions                       |    |

| 3.5.2 Solutions for Cell Development                       |    |

| 3.5.3 Framework Performance                                |    |

| 3.5.4 Final Thoughts                                       |    |

| 3.6 Summary                                                |    |

| Chapter 4: Cell Microbenchmarks                            | 53 |

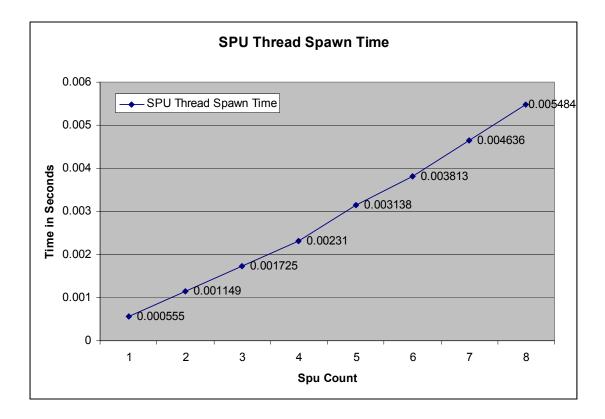

| 4.1 SPU Threads                                            | 54 |

| 4.1.1 SPU Thread Startup Time                              |    |

| 4.1.2 SPU Thread Startup Timing Results                    |    |

| 4.2 DMA Test                                               |    |

| 4.2.1 DMA Timings                                          |    |

| 4.2.2 DMA Method Comparison Test                           |    |

| 4.2.3 Final Recommendation                                 |    |

| 4.3 A Few Words on DMA                                     |    |

| 4.3.1 Memory Alignment.                                    |    |

| 4.3.2 Data Transfer Size                                   |    |

| 4.4 Summary                                                |    |

| Chapter 5: CAEE: Call Architecture Fromework and Extension | 60 |

| Chapter 5: CAFE: Cell Architecture Framework and Extension |    |

| 5.1 Goals and Motivation                                   |    |

| 5.2 Framework Mechanics                                    | 72 |

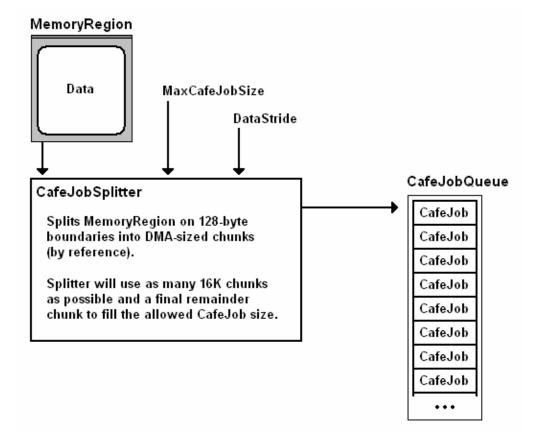

| 5.2.1 MemoryRegion                                         |    |

| 5.2.2 CafeJobs and Data-Partitioning                       |    |

| 5.2.3 DMA Manager                                          |    |

| 5.3 Programming Paradigms Using CAFE                       |    |

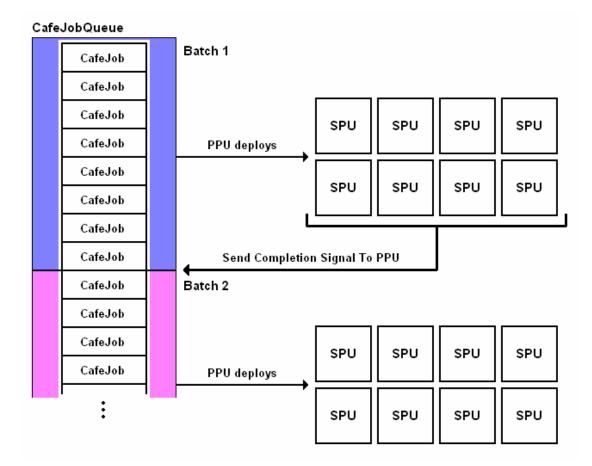

| 5.3.1 Batch-Sync Programming Model                         |    |

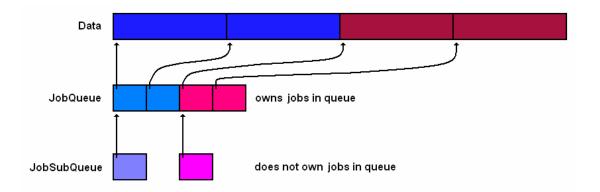

| 5.3.2 Subqueue Streaming Programming Model                 |    |

| 5.4 Summary                                                |    |

| Chapter 6: Example Applications and Results                |    |

| 6.1 SAXPY                                                  |    |

| 6.1.1 Batch-Sync SAXPY                                     |    |

| 6.1.2 Subqueue Streaming SAXPY                             |    |

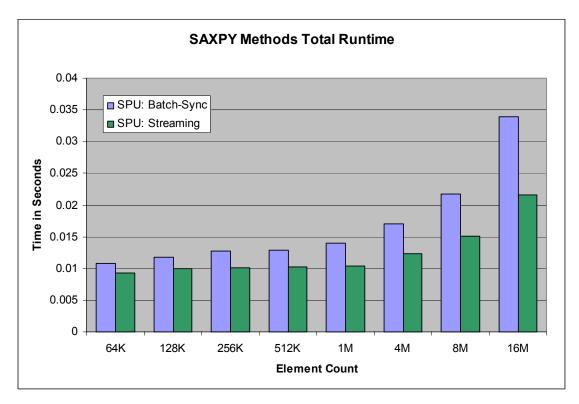

| 6.1.3 SAXPY Results                                        |    |

| 0.1.3  SAA1  I  AUSUIDS                                    |    |

| 6.2 Ray Tracer                               | 108 |

|----------------------------------------------|-----|

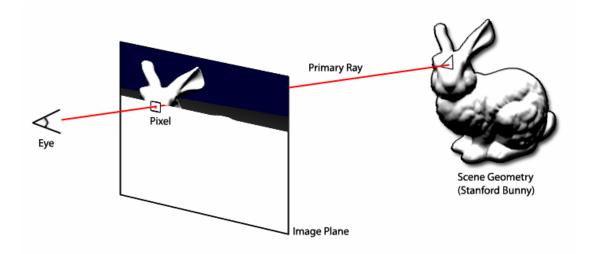

| 6.2.1 Ray Tracing, Briefly                   |     |

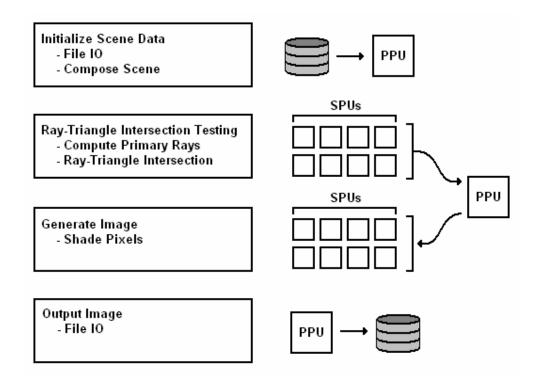

| 6.2.2 Ray Tracing on Cell                    | 111 |

| 6.2.3 Ray Tracer Results                     |     |

| 6.3 Image Filtering via Chaining             | 117 |

| 6.3.1 Parallel Image Processing              |     |

| 6.3.2 CAFE Support for Windowed Partitioning | 121 |

| 6.3.3 Chaining Implementation Details        | 122 |

| 6.3.4 Image Filter Results                   | 123 |

| 6.4 Bitonic Sort                             |     |

| 6.4.1 Source Modifications                   |     |

| 6.4.2 Runtime Performance                    |     |

| 6.4.3 Final Outlook: CellSDK and CAFE        |     |

| 6.5 Summary                                  | 130 |

|                                              |     |

| Chapter 7: Future Work                       | 132 |

| Chapter 8: Conclusion                        | 134 |

| Appendix A: Scalable City                    | 138 |

| Scalable City Pipeline                       |     |

| Scalable City Application                    |     |

| Scalable City and Cell                       |     |

|                                              |     |

| Appendix B: CAFE API Reference               | 141 |

| References                                   | 151 |

## List of Figures

| Figure 1.1: Quadword SIMD Operation                                      | 5     |

|--------------------------------------------------------------------------|-------|

| Figure 2.1: Cell Processor Floorplan                                     | 13    |

| Figure 2.2: SPU Select Intrinsic                                         | 17    |

| Figure 2.3: Cell Memory and Communications Structure                     | 20    |

| Figure 2.4: Function-Offload Programming Model                           | 23    |

| Figure 2.5: Chaining Programming Model                                   | 24    |

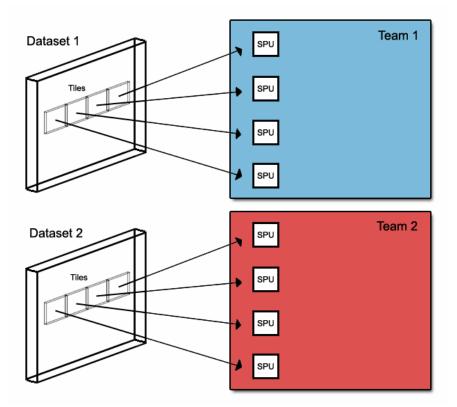

| Figure 3.1: MultiCore Framework Task-Parallelism via Teams               | 39    |

| Figure 3.2: Framework Platform Comparison Chart                          | 44    |

| Figure 3.3: Framework Parallelism and Paradigm Comparison Chart          | 45    |

| Figure 4.1: SPU Event-Driven Pipeline Pseudocode                         | 55    |

| Figure 4.2: SPU Thread Startup Time for Single Cell Processor            | 56    |

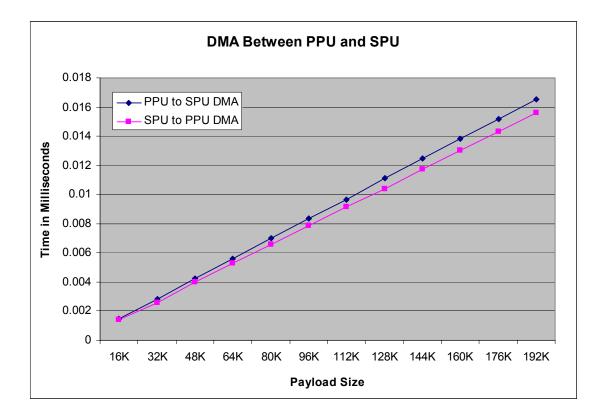

| Figure 4.3: DMA Transfer Time between the PPU and SPU                    | 58    |

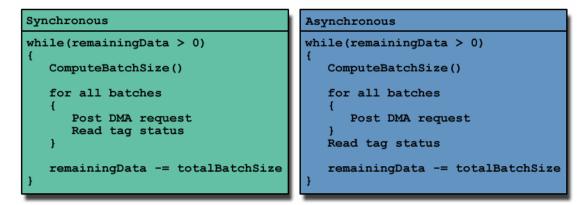

| Figure 4.4: Synchronous vs. Asynchronous DMA Methods                     | 60    |

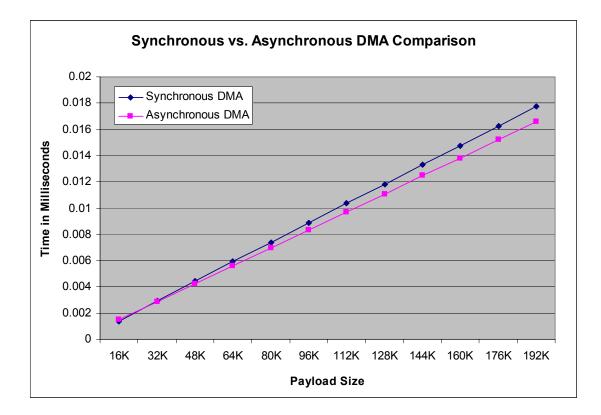

| Figure 4.5: Synchronous vs. Asynchronous DMA Transfer Comparison         | 61    |

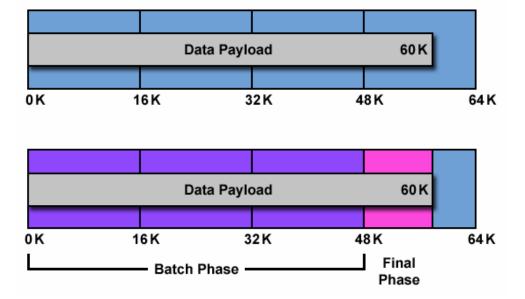

| Figure 4.6: DMA Transfer Split into Batch Phase and Final Phase          | 62    |

| Figure 4.7: Vertex Packing: Mesh vs. Stream Processing                   | 65    |

| Figure 5.1: CAFE Data-Partitioning Pipeline: Generating the CafeJobQueue | 74    |

| Figure 5.2: Batch-Sync Programming Model Pipeline                        | 79    |

| Figure 5.3: CafeJobQueue Partitioning into Subqueues                     | 89    |

| Figure 6.1: Batch-Sync SAXPY Pseudocode                                  | .100  |

| Figure 6.2: Subqueue Streaming SAXPY Pseudocode                          | .102  |

| Figure 6.3: SAXPY SPU Implementation Runtimes                            | .104  |

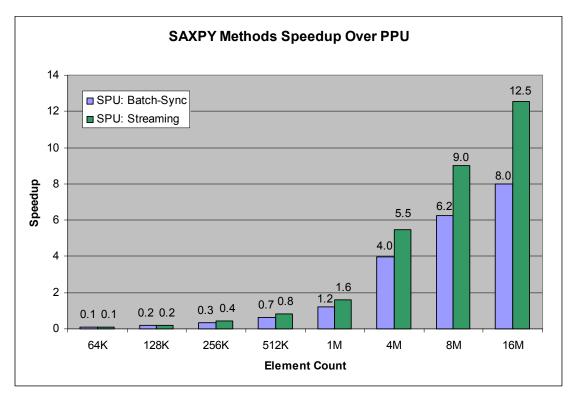

| Figure 6.4: SAXPY SPU Speedup over PPU                                   | .105  |

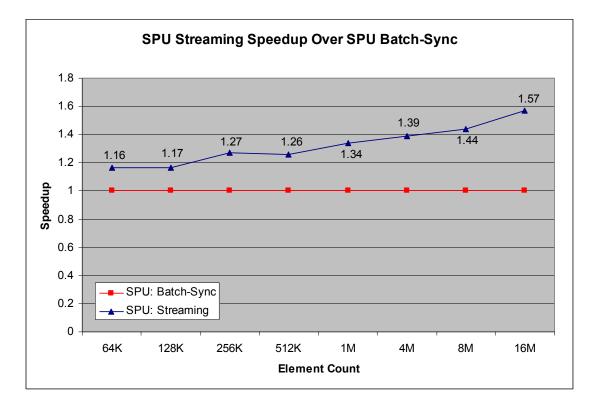

| Figure 6.5: SAXPY SPU Streaming Speedup over SPU Batch-Sync              | .106  |

| Figure 6.6: SAXPY Implementation Runtimes and GFLOP Rates                | .107  |

| Figure 6.7: SAXPY Implementation Line Counts                             | .108  |

| Figure 6.8: Serial Brute-Force Ray Tracing Algorithm                     | . 109 |

| Figure 6.9: Ray Tracing in Action                                        | .110  |

| Figure 6.10: Ray Tracer Pipeline on Cell                              | 112 |

|-----------------------------------------------------------------------|-----|

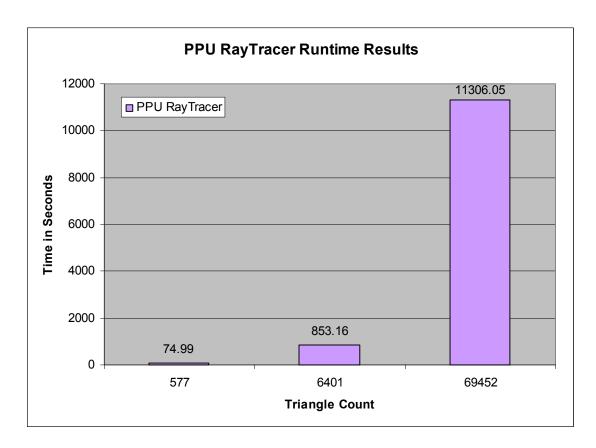

| Figure 6.11: PPU Ray Tracer Runtime                                   | 114 |

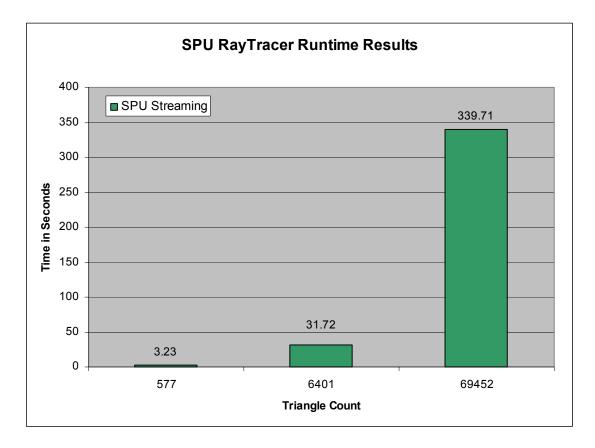

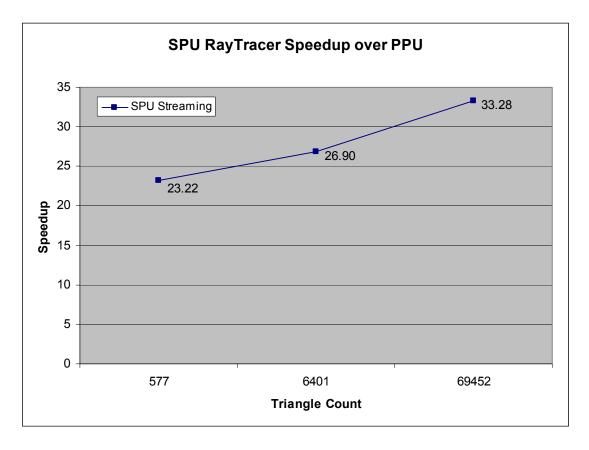

| Figure 6.12: SPU Ray Tracer Runtime                                   | 115 |

| Figure 6.13: SPU Ray Tracer Speedup over PPU                          | 116 |

| Figure 6.14: Ray Tracer Implementation Line Counts                    | 117 |

| Figure 6.15: Sliding a 3x3 Kernel across the Pixels of an Image       | 119 |

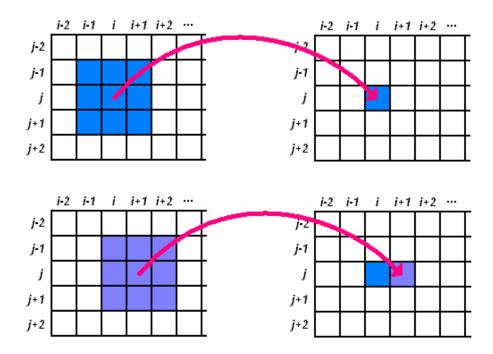

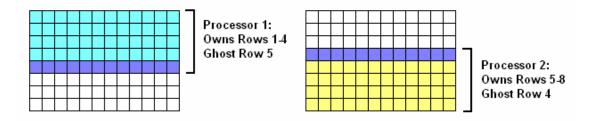

| Figure 6.16: Windowed Partitioning of an Image between Two Processors | 120 |

| Figure 6.17: Template for Chaining Application using CAFE             | 123 |

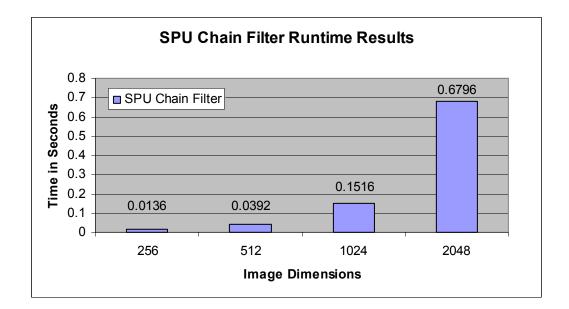

| Figure 6.18: SPU Chain Filter Runtime Results                         | 124 |

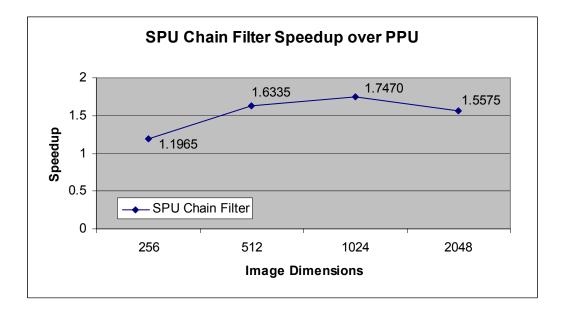

| Figure 6.19: SPU Chain Filter Speedup over PPU (Normalized to 1)      | 125 |

| Figure 6.20: SPU Image Filter Statistics                              | 125 |

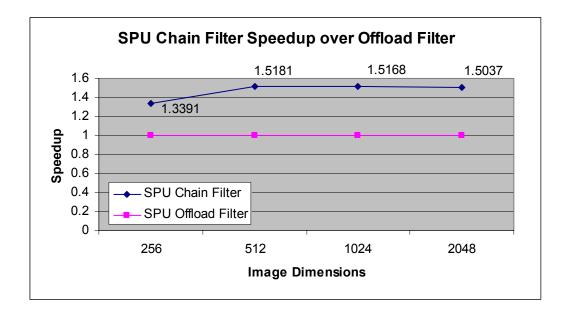

| Figure 6.21: SPU Chain Filter Speedup over Offload Filter             | 126 |

| Figure 6.22: Bitonic Sort Implementations Line Count Comparison       | 128 |

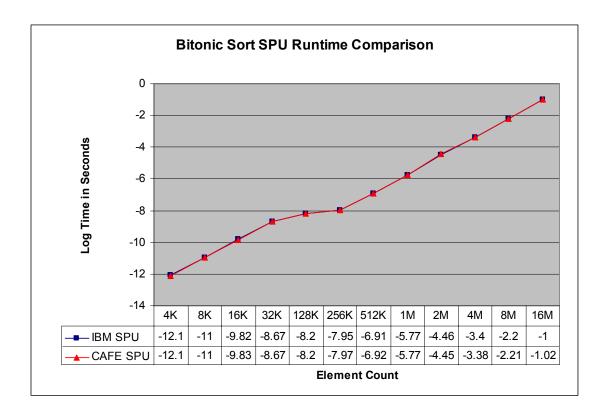

| Figure 6.23: Bitonic Sort SPU Runtime Comparison                      | 129 |

#### Acknowledgments

First and foremost, I would like to acknowledge Kristen Kho for her valiant efforts in helping me write the CAFE framework and keeping me sane. Without her help I would most certainly still be coding or running around in circles trying to make another design decision. Thank you for being an invaluable pair programming partner and willing to jump in and hit the ground running with this project.

I would also like to acknowledge the team we worked with at IBM: Bruce D'Amora, Gordon Ellison, Sidney Manning, and Bob Szabo, for their assistance with our work and questions about the Cell BladeServer. I would also like to extend thanks to Rob Todd and Jessica Schupp for their additional support during the Cell Workshop at High Moon. IBM was the industrial sponsor for the UC Discovery Grant (dig05-10197): "Implementing Cell Processor Engines for Resolving Constraints in Real-Time Graphics Environments" which funded this work.

I would like to thank CRCA Technical Director Todd Margolis for all of his efforts to setup and maintain the Cell BladeServer at UC San Diego. Also, I would like to extend thanks to Helena Bristow for all of her time and support.

Thank you to all of the members of the Experimental Game Lab team: Alex Dragulescu, Mike Caloud, Erik Hill, Carl Burton, and Daniel Tracy, for the great times over the last three years on the Scalable City project.

Also, I would like to thank the Research and Development Team from High Moon Studios: Noel Llopis, Jim Tilander, Charles Nicholson, and Rory Driscoll, for their patience in teaching me the ins and outs of real-world systems coding and

Х

software engineering. Also, their advice on aspects of particular problems we ran into during development proved to be extremely valuable.

Finally, I would like to thank my advisors. Thank you to Professor Scott Baden, who taught me the fundamentals of parallel programming—without his abundance of patience and wisdom this could not have been possible. Thank you to Professor Sheldon Brown for believing in me over the last three years and allowing me to pioneer the development on the Cell for the gamelab. Thank you to Professor Geoff Voelker for the continuous flow of encouragement that started on the day I first met with him to ask about taking the big step into the Computer Science graduate program and never stopped.

#### ABSTRACT OF THE THESIS

CAFE: A Framework for Cell Application Development

by

Joseph Keith Hammer, Jr. Master of Science in Computer Science University of California, San Diego, 2007 Professor Scott Baden, Chair

The IBM Cell processor is a heterogeneous multi-core architecture designed to demonstrate exceptional levels of performance improvement for compute-intensive applications. The streamlined design of its Synergistic Processing Units (i.e. small local store, no cache, limited branch prediction, no dynamic instruction reordering) presents a new set of challenges for application developers as they are now required to explicitly control the flow of data amongst the processors.

Therefore, in this thesis we introduce a lightweight, flexible framework library called Cell Architecture Framework and Extensions (CAFE) to assist developers in taking advantage of this computational power without forcing a single programming model onto their applications. CAFE takes a more minimalistic approach than other frameworks by presenting low-level abstractions and utilities designed to help partition and transfer data between the cores. As a result, programmers can develop

applications using a reasonably high level interface, yet still retain explicit control over the flow of data. We believe that these characteristics are very important to developing high-performance applications in the Cell environment.

To motivate our design decisions, we provide an in-depth examination of where these aforementioned implementation challenges appear and discuss a range of countermeasures that may be successfully employed. We also present an assortment of example applications that each utilize CAFE in a different manner to help show its versatility.

#### **Chapter 1: Introduction**

#### **1.1** Architecture Trends and Revolutions

Undoubtedly, programmable computer architecture has come a long way since its beginnings in the mid-twentieth century. It is reasonable to say that for the past half-century we have been "living under the cover" of Moore's Law, which states that "the complexity for minimum component costs has increased at a rate of roughly a factor of two per year" and that "certainly over the short term this rate can be expected to continue, if not to increase." [Moore65]. This prediction has remained as a comfortable trend in computer hardware engineering, despite the fact that the speed of memory has not been able to match the pace.

However, although the size of transistors continues to shrink with each new generation, we have found ourselves in an interesting time when Moore's Law has started to fail due to some fundamental physical laws, such as power consumption and heat dissipation. These obstacles have pushed computer architects in a different direction: rather than using the next generation of transistors to increase the complexity of the processor in an effort to gain operational speed, architects have started to duplicate more simplified versions of processors across the chip in a stamplike manner. This has given rise to the dual- and quad-core processors available on the conventional hardware market today.

Before this transition occurred, another revolution took place during the mid-90's: the advent of conventional graphics hardware accelerator. Graphics Processing Units (GPUs) are a type of coprocessor specialized for performing common operations

1

found in computer graphics: transformations, interpolations, etc. In particular, they are designed to take a chunk of data (from hereon also referred to as the "payload") and perform the same set of operations on each of its components. For instance, at a high-level, a simple three-dimensional object is composed of a mesh of triangles that define its geometric shape and a set of texture coordinates associated with each triangle vertex to define its appearance. When we want to place the model in a scene for visualization, we must apply a transformation to all of the vertices of the triangles in the mesh, followed by an interpolation of the texture using the corresponding texture coordinates across each triangle for the sake of rendering. Since there may be thousands (or millions!) of triangles for each object, it is easy to appreciate the benefits in having dedicated hardware support for such operations. It is also readily apparent that such operations are independent of each other (no triangle vertex transformation, and so on...), and therefore can be computed in parallel.

As graphics hardware has matured, there has been a definitive movement in the direction of programmability and generality. It now presents us with an architecture that performs the aforementioned operations in parallel at a very high rate of throughput via a paradigm called *streaming*. Streaming (or more formally: stream processing) performs the same computation across the elements of a single payload. Until recently, the streaming components supported on the GPU were strictly graphics-specific, including dedicated vertex and texture memory buffers and operation kernels in the form of vertex and pixel shader programs. However, this meant that anyone who wanted to use the GPU simply as a coprocessor for performing

non-graphics-specific computations was forced to repackage and mask the data as if they were a vertex or texture buffer as well as reformulate computations as if they were vertex or pixel shaders. Such a task can actually be quite an undertaking and is somewhat analogous to asking someone to cram a square peg into a round hole—it can probably be done, but it will take a lot of unnecessary force and the end result isn't going to be pretty. As it turned out, after seeing the effectiveness of the GPU in the realm of graphics, other areas of computer science—especially the scientific computing community—began to take an interest in utilizing its power for their own purposes, producing a new demand for more generality in the native operations and pipeline. The hardware and research that stemmed from this movement has been labeled General-Purpose Computing on the GPU (GPGPU).

#### 1.2 Parallelism

There are two types of parallelism exploited in modern computing: controllevel parallelism and data-level parallelism. As we will see, both types of parallelism are useful and important in their own respects and each contributes to hardware and software efficiency in their own unique way.

#### **1.2.1** Control-Level Parallelism

Control-level parallelism is the action of processing two different courses of execution at the same time. This is made possible on many different levels within a machine (hardware threads, hardware operations on different units) and applications (software threads). On a single processor, the façade of performing multiple tasks simultaneously (or *multitasking*) is simulated by managing the amount of time each task is allotted to spend on the processor. This act of scheduling is typically performed by the operating system (or a user-level thread scheduler) to ensure that each task is given a chance to make progress. On multi-core processors, the operating system will usually split the task queue among the available processor cores and handle the scheduling on each core individually.

Control-level parallelism is also very important to utilizing the processor efficiently. The classic example is when an application requires a piece of data from a slower device (e.g. hard drive) or from across a network. Since many hundreds or thousands of cycles may pass before that data arrives, it would be more efficient to allow the processor to attend to the computational needs of other tasks in the meantime.

We can draw a correspondence between the CPU and control-level parallelism. This is the reason why conventional CPUs are designed to switch among different tasks (more formally known as *context-switching*) as efficiently as possible: during normal operation, the CPU must handle frequent context-switches amongst all the software applications running on the machine, each with its own program counter and application-specific data processing operations.

#### 1.2.2 Data-Level Parallelism

As one may have suspected, data-level parallelism is the act of performing the same set of operations on different pieces of data simultaneously. In accordance with convention, we will refer to this set of operations as a *kernel*. What's more is that the

techniques of data parallelism can be applied to many different levels within the code: from the aforementioned kernel level even down to the level of individual instructions.

The best concrete example of this is type of parallelism is found in a Single Instruction Multiple Data (SIMD) instruction [Tommesani03]. For instance, consider how vector arithmetic finds the sum of two vectors *A* and *B*: we simply add each of the components independently:

$$(a_1 \ a_2 \ \cdots \ a_n) + (b_1 \ b_2 \ \cdots \ b_n) = (a_1 + b_1 \ a_2 + b_2 \ \cdots \ a_n + b_n).$$

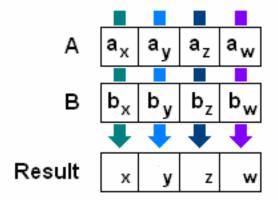

This is exactly the mechanics behind SIMD addition, and can be extended to a number of other computational and conditional logic operations. In the interest of multimedia applications, SIMD operations are conventionally performed on 128-bit quadwords at a time, as shown in Figure 1.1 below.

Figure 1.1: Quadword SIMD Operation

Data-level parallelism is at the heart of processing on the GPU since its purpose (at a low level) is to perform the same operation over a large set of data. In fact, we can also identify the multiple layers of data parallelism being performed: at the highest level we have multiple triangle meshes that make up our scene; at the component (triangle vertex) processing level we have a list of independent transformations; and at the instruction level we have SIMD operations.

#### **1.3** Next-Gen Architecture: IBM Cell

Although we have dedicated an entire chapter to the Cell architecture, we will briefly introduce it here enough to present the context of the work that follows.

In short, the Cell processor is currently on the bleeding edge of hardware technology. In terms of its architecture, it is a hybrid between the multi-core processors and the GPUs we introduced earlier, though assembled heterogeneously. Cell has nine separate cores: one for running the operating system and performing control-level parallel tasks (PPU), while the other eight conventionally serve as coprocessors for data parallelism though they can operate independently of the PPU's control (SPUs). As a whole, the Cell was designed around the streaming paradigm, though in a more general fashion as the eight coprocessors are not built on graphicsspecific structures like a GPU.

The Cell processor was specifically designed to perform massive amounts of single-precision floating-point operations as quickly and efficiently as possible. Unlike a conventional CPU which is designed to perform reasonably well for a general mix of applications, the Cell is specialized to demonstrate excellent performance on a core set of target applications (including multimedia processing and compression, real-time simulation, and games), while exhibiting less-than-desired performance results for other types of applications (such as operating systems or database management software). As such, software packages from each of these core target application

categories require an enormous amount of computational power. Thus, the eight coprocessors within the Cell were designed to perform extremely fast single-precision floating-point operations in parallel.

However, although it makes for a very interesting configuration for a parallel machine, the Cell's architectural design promotes a few fundamental differences within code development practices from those found in conventional parallel computing say, with MPI [MPI03]. These differences include a rigid constraint on memory alignment and a limited remote local store. However, the foremost of these differences is the exposure of the memory hierarchy to the programmer, who is now expected to carefully manage *both* code and data across the coprocessors. In fact, developers can dynamically upload code to the SPUs. While this capability gives developers a great deal of control and the opportunity to achieve previously unattainable performance benchmarks, it also imposes a steep learning curve, which requires even the novice programmer to have a deep understanding and intimate knowledge of the underlying hardware.

In consequence, the work presented in this thesis shows the struggles and triumphs that have been required in an attempt to tame this beast, and presents a solution in the form of a set of libraries, which we refer to as a "framework", to ease the efforts of other aspiring Cell developers.

#### 1.4 CAFE: Cell Architecture Framework and Extensions

Data partitioning and, more generally, data transfer preparation is a common problem in *all* non-trivial Cell applications. However, while the IBM-distributed software development kit (commonly referred to as the CellSDK) does an excellent job at providing low-level hooks into the hardware, it also makes the partitioning of data a meticulous and error-prone task, due to the level of intimacy required between the programmer and hardware (previously introduced in Section 1.3). It has come with our own experience that the mechanics of data partitioning can distract developers from spending their time on the more interesting areas of the application, such as scheduling, data flow, and vector processing, not to mention the ubiquitous issues behind the design and implementation of the algorithms and overall architecture of the code base.

We are not the only ones to have recognized this trend as both commercial and academic solutions have been developed to help alleviate this issue and offset the learning curve set forth by the Cell processor. Unfortunately, these solutions have also taken it upon themselves to provide their clients with a proxy pipeline that confines application development into a particular paradigm as opposed to allowing the programmers to retain control of the scheduling and data transfer methods utilized in order to accomplish their tasks. We believe that the power to manage the scheduling and transfer of data is particularly important in the area of high performance computing, and recognize that they should always be approached on an application-to-application basis since it is more often the case that *the programmer knows their data far better than any library ever could*.

8

In the light of this observation and others, we set out to create a minimalistic framework to assist the Cell development community without usurping the control over performance critical application components. The thesis that follows is a discussion of our work and a presentation of our framework libray: Cell Architecture Framework and Extensions (CAFE). Our main contributions include a module to automatically assess and partition data sets into suitable payload sizes for the Cell's SPUs, where the bulk of the computational load is resolved. We have also formalized and provided the structures required to establish a data transfer preparation paradigm for ferrying payloads to and from the SPUs without seizing control of the method of scheduling. Finally, due to the nature of our research lab, we designed the framework to ease the porting and development of the graphic and algorithmic processes employed by the Scalable City project (see Appendix A).

#### 1.5 Conventions

Briefly, we would like to lay out a few conventions used throughout this thesis. First and foremost, we are primarily concerned with developers as opposed to application end-users. In fact, we refer to programmers who utilize our framework or the framework of others as *clients*. Consequently, we will use the words *developer*, *programmer*, and *client* interchangeably.

Additionally, in this thesis we will discuss various *design patterns* for Cell application development. These patterns are also referred to as *templates* and *programming models*. Furthermore, these patterns are usually focused around the

*pipeline* (read: flow of data) between the cores. As such, we will sometimes simply refer to the patterns by the pipelines they entail.

The term *kernel* is used throughout the thesis, yet is very context-dependent. For example, in Chapter 3 different APIs refer to their SPU programs as kernels, while in the image processing application of Chapter 6 kernel refers to the image filter. We have been careful to define this term as the context changes.

#### 1.6 Thesis Outline

To conclude our introduction, we present an outline of the thesis to follow and highlight some of the important features of the road ahead.

First, we will introduce the Cell processor in detail and touch on some of the finer points required for developing non-trivial applications for it. While a complete overview of the hardware would require a more in-depth discussion, we believe that Chapter 2 provides sufficient detail for a solid understanding of the hardware and the capabilities that it provides.

Second, in Chapter 3 we will review prior and current work on APIs and languages. In particular, our discussion will revolve around how prior solutions help ease the steep learning curve that has been set by the complexity and exposure of the Cell architecture to the programmer.

Third, we will examine the initial work that was done to explore some of the limitations of the hardware as well as produce some baseline results in order to help motivate some of the design decisions made in CAFE. We believe this to be a very important chapter as it reveals the difficulties found in Cell development at the

implementation level. Furthermore, we will also present and evaluate various possible approaches to augmenting these difficulties. It is from this set of methodologies that we generate a foundation for our framework.

In Chapter 5, we will formally introduce the framework library and the various design decisions that lie behind its conception and implementation. In addition to a presentation of the structures and mechanisms available at a conceptual level, we also provide a pair of complete templates for utilizing CAFE in a Function-Offload manner.

Afterwards, Chapter 6 presents of a few implementation examples using our framework to build Cell applications. We have chosen these applications based on a number of factors including exhibiting the versatility of applications our framework constructs support.

Finally, we will discuss some future work that could be done to continue to extend the framework as well as further improve application development on the Cell processor.

#### **Chapter 2: Introducing the Cell Processor**

We now provide a brief introduction to the IBM Cell Broadband Engine (or as it is more conventionally called: "Cell") hardware. This chapter is by no means comprehensive, but is sufficient to give the reader an appreciation for the capabilities of the system. Throughout, we will be sure to visit particular programming aspects which stem from the unique design decisions made for the Cell.

We would also like to note that unless specified otherwise the specs given below are for a single Cell processor only and scale within the Cell BladeServer, which has two Cells per blade and up to four blades in the system at UC San Diego.

The following specifics and details have been gathered from [Kahle05], [Gschwind00], [Hofstee05], the *IBM Cell Broadband Engine Architecture Guide* [IBM05], and the *IBM Cell Programming Handbook* [IBM06a].

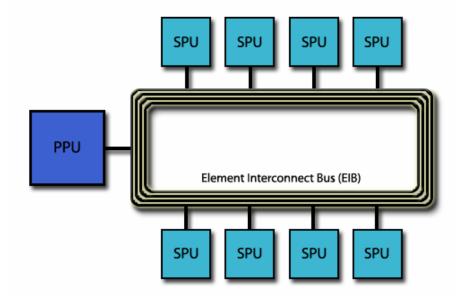

#### 2.1 The Cell Processor

The Cell is made up of two types of processors: a PowerPC front-end (Power Processing Unit: PPU) and eight synergistic vector processors (Synergistic Processing Units: SPUs). Each processor type requires a different, separate program to be written and compiled with different modified versions of gcc (or g++) provided in the CellSDK. It is interesting to note that the generated binaries can be run individually on their respective processors; programs for the PPU are just like any other application written for the PowerPC architecture, while the programs written for the SPUs, called "spulets", are designed to be simple and "encourage porting and incremental

12

refinement of legacy code on the SPU" [IBM spulet sample]. In our case, we will only discuss the instance when the two types of processors are interdependent.

Figure 2.1: Cell Processor Floorplan

#### 2.2 **PPU: PowerPC Processing Unit**

As mentioned above, the PPU is just like a conventional PowerPC. It is a 64bit RISC processor, clocked at 3.2 GHz. It includes a VMX vector processing unit which supports the AltiVec SIMD vector instruction set extensions. It has 32 128-bit vector registers, separate instruction and data L1 caches (32 KB each), and a unified 512 KB L2 cache. There are also two available hardware threads and a traditional virtual memory subsystem.

The PPU's main purpose is to run the operating system, manage system resources, and serve as the control manager for the SPUs. In general, there is little difference (if any) in programming for this side of the Cell from conventional C/C++ application development practice.

#### 2.3 SPU: Synergistic Processing Unit

Synergistic Processing Units are named for the mutual dependence they have with the PPU. In terms of architecture, the PPU is designed to handle controlintensive tasks and perform efficient task-switching, while the SPUs are designed to handle compute-intensive tasks. Essentially, this means that the SPUs rely on the PPU to run the application control-thread and feed them both code and data, whereas the PPU relies on the SPUs to perform most of the computational heavy-lifting<sup>1</sup>.

#### 2.3.1 Processor

The SPU is also a 64-bit RISC 3.2 GHz processor, but runs its own custom "vector only" instruction set. We say "vector only" because even scalar operations are loaded into vector registers and run using vector operations during execution. This translates to the following:

- 1. Insert scalar value into the preferred  $slot^2$  of the vector register

- 2. Perform the operation using the corresponding vector operation

- 3. Extract the scalar result from the preferred slot of the vector register As one might presume, this is a very important fact to keep in mind when programming for the SPU as scalar operations are not truly as atomic as they look from a code perspective.

The SPU has a unified register file containing 128 128-bit vector registers. By "unified" we mean that all supported data types (integer, single-precision floating-point, and even logical operators) use the same register file.

Also, the SPU is a dual-issue processor. This means that it has two separate pipelines, named *odd* and *even*, for executing instructions and can execute one instruction from each pipeline every cycle. All load and store instructions are processed in the odd pipeline, while all other operations are executed in the even pipeline. The pipeline can issue a single-precision floating-point operation every cycle with a latency of six cycles, while a double-precision floating-point operation can be issued every 7 cycles in addition to the same 6-cycle latency.

#### 2.3.2 Local Store

One of the major design goals for the SPU was predictability. Essentially, the designers at STI<sup>3</sup> wanted a *deterministic operating environment* in which one can statically determine the performance of code. In other words, they wanted to establish a set of rules such that the running time of the same code would always be the same. While at first glance this may sound a bit silly, but consider the flow of data that goes on under the hood of a conventional system: when an instruction is to be executed, the data operands must be loaded into registers, but this data may currently reside anywhere in the memory hierarchy... L1, L2, L3 (if available), main memory, on-site storage, or maybe even storage located across a network. This implies that we may not know how long it could be before that data may be ready for the instruction to use. Certainly, in most cases the data is close to the top of the hierarchy thanks to spatial or temporal locality, or both, but the fact still remains that the time it takes for a piece of data to be loaded into a register is unknown and can only be narrowed down to a range of cycles depending upon where in the hierarchy the data currently resides.

This brings us back to the issue of predictability on the SPU. To attain the goal of creating a deterministic operating environment, the designers at STI wanted to avoid the irregular latency times built up by moving data up and down memory hierarchies. The solution was the aforementioned large register file in combination with a 256 KB SRAM local store (LS). The LS is allotted for both code and data, and can *always* be accessed in 6 cycles. Also, all loads and stores are made on a 16-byte aligned boundary without translation, paging, or protection.

We would like to make it clear that although it is a relatively small, fast memory close to the processor, the local store is *not* a cache, wherein pieces of data are brought in and swapped out under automatic hardware control. In fact, there is no cache anywhere on the SPU. This leads to the exciting and important observation that since there is no cache, there can be no cache misses!

One final detail must be added to complete our discussion of the SPU's characteristic of predictability: *in-order execution*. In the interest of speed, most conventional processors today have the ability to execute instructions out of their specified issue order (referred to as *out-of-order execution*), provided that the ordering does not affect the program correctness. This feature is, by design, *not* available on the SPU. Thus, we gain the ability to walk down the assembly code instruction by instruction and assign cycle times to each line for the entirety of the program. This allows for SPU binaries to be statically timed, providing Cell developers with a definitive guide to help them examine and streamline any stalls that may be present in their code.

#### 2.3.3 Branch Prediction

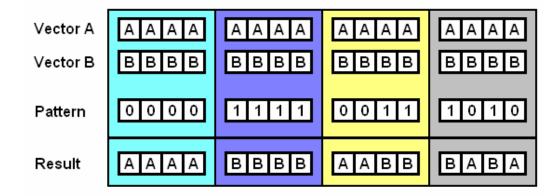

While the predictability attribute of the SPU architecture sounds pretty nice, there is one final, yet important feature to discuss: branch prediction. There is *no* hardware branch predictor present on the SPU. In other words, all branch prediction is done at the software level. There is an 18-cycle latency for mispredicted branches. To counter this performance penalty, there are a couple of software mechanisms in place, including an inline branch-hint directive and a *select* intrinsic<sup>4</sup>.

The inline branch-hint directive is exactly what it sounds like: in the code, the programmer can specify whether the branch should be predicted as taken or not taken (by default, all branches are predicted as not taken). The directive can be used for either static or dynamic branch prediction (see Section 1.6 of *IBM C/C++ Language Extensions for Cell Broadband Engine Architecture* [IBM06e] for more details).

Given a bit pattern, the *select* intrinsic allows for individual bits to be selected from one vector or another. For example, given two vectors A and B, we can choose bits from A or B with a bit pattern P, where a 0 in P says to choose the bit from A and a 1 in P says to choose the bit from B.

Figure 2.2: SPU Select Intrinsic

The significance of the select intrinsic from a programming perspective is that one can compute both routes of a branch and then select the result based on a pattern vector which can be created via one of the comparison intrinsics. This is often desirable since it puts the issue back in the SPU's dominant domain of raw computation.

#### 2.4 Communication Mechanisms

Communication between the two types of processors is handled via three mechanisms: mailboxes, Direct Memory Access (DMA), and signal notification registers. It should also be noted that SPUs can communicate with other SPUs, which allows developers to employ a programming model called Chaining (see Section 2.6); however, in the interest of simplicity, here we will focus the discussion on communication between the PPU and SPU.

#### 2.4.1 Mailboxes

Mailboxes are queues used to pass small (32-bit) messages back and forth between the PPU and an SPU. Each SPU has two types of queues: a pair of outbound (SPU to PPU) queues, and an inbound (PPU to SPU) queue. It should be noted that messages cannot be passed between two SPUs via mailboxes.

Both outbound mailbox queues are only a single message deep; one is for general purpose messages to the PPU and the other is used for interrupts. The PPU may poll these queues before making the blocking call to actually read from them. A practical use for this is when the SPU has finished processing its current batch of data and needs to tell the PPU it is done; we certainly do not want to hold up any other tasks the PPU may need to do (data preparation, checking other SPU threads to see if they have finished, etc...), so we poll the SPU outbound mailbox, respond appropriately, and continue on. We will take a look at the other side of this technique in Chapter 4 when we discuss the SPU-driven pipeline.

The inbound queue can hold up to four messages at a time for the PPU to send to the SPU. However, if the PPU sends more than four messages to an SPU, the fourth message will continue to be overwritten by subsequent sends until the SPU performs a mailbox read. To avoid this undesired side-effect, one could have the PPU send the first four messages and then wait on the SPU to reply through the outbound mailbox that all the messages have been read, signaling the PPU that mailbox message sending may resume. This simple design pattern serves as a way to synchronize the two processors if the application requires such a sequence of short messages to be dispatched to the SPU.

Mailboxes are useful for sending addresses and action codes (e.g.: exit / continue, success / failure) as we shall see in Chapter 5. However, sending 32-bits at a time will not suffice for real-world data processing – that's where DMA comes in.

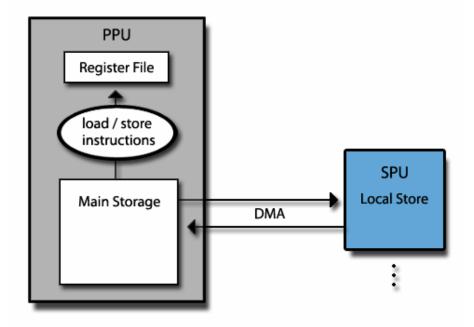

#### 2.4.2 Direct Memory Access (DMA)

The main method of data transfer on the Cell processor is Direct Memory Access (DMA), which takes place on the Element Interconnect Bus (EIB). Briefly, the EIB (see Figure 2.1) is composed of four rings for transferring data at an internal bandwidth of 96 bytes per cycle. Two of the rings are directed in the clockwise direction while the other two are counter-clockwise.

On the EIB, DMA requests are handled asynchronously, allowing for 128 simultaneous transfers between main storage and a SPU local store (shared across all eight SPUs). Each DMA transfer is invoked with a user-defined tag which can later be used to wait on the transfer's completion by reading the tag status. It is important to note that DMA requests can be made in batches by simply invoking multiple transfers with the same tag t; then, when the tag status for t is read, the program will wait for all of the corresponding requests made with t to complete. We will discuss further applications for tags in Chapter 4.

Figure 2.3: Cell Memory and Communications Structure

The SPUs are designed to input / output data in increments of 128-bytes up to 16 KB per request. This is also subject to the constraint that all memory DMAed to and from the PPU must be 16-byte aligned, though the vendor recommends that transfer data be 128-byte aligned for best performance.

It is interesting to note that either processor type may invoke a DMA request from the other; however, the Memory Flow Controller (MFC) resides on the SPU so no matter where the request originated, all requests are actually made from the SPU under the hood (this is also why the queue names "inbound" and "outbound" are designated from the perspective of the SPU). Therefore, to attain peak performance it recommended that DMA requests are exclusively made from the SPU.

#### 2.4.3 Signals

The SPU signal notification channels are kind of like another pair of inbound mailboxes. There are two channels, each for 32-bit signals. An important difference between notification channels and configuration mailboxes is that the former can be configured in a reduction (many-to-one) in addition to their single direct-line configuration (one-to-one).

We note that we have never employed the use of signal notification channels as mailboxes and DMA have been sufficient for the needs of all of our applications to date. Signals have been suggested as a means of implementing a barrier construct for synchronizing the execution of the SPUs (see IBM DeveloperWorks Forum: *Barrier* Post [IBM07]). However, a barrier can also be more efficiently implemented through the use of mailboxes, which is the method we chose to employ in our framework and use in the Chaining example discussed in Section 6.3.

#### 2.5 Programming Models

There are a few different programming models described in the Cell Programming Handbook. The two most notable models are *Function-Offload* and *Chaining*. As we shall later discover, the Function-Offload model is the more prominent of the two, largely due to its simple structure and function. However, although the Function-Offload model serves as the basis for most of the program examples discussed in this thesis, we would like to emphasize the importance of Chaining and have dedicated an entire section on examining it usefulness and implementation in Section 6.3.

#### 2.5.1 Function-Offload Programming Model

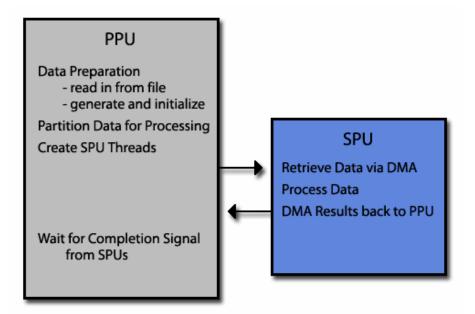

At its core, the Function-Offload programming model is analogous to a Remote Procedure Call [STI05]. It entails using the PPU for data preparation and SPU thread management, while the SPU is used for the data processing. Figure 2.4 shows this exchange of data between the two processors and an outline of their duties.

The Function-Offload paradigm is intuitive with respect to data parallel programs: simply create multiple SPU threads, each running the same SPU program, and partition the data such that each SPU has a portion of the workload. This way the data can easily be operated on in parallel.

Figure 2.4: Function-Offload Programming Model

Certainly, the SPU binaries need not be the same across all eight SPU's. This means that we could setup half of the SPUs to do one operation and the other half to do another (or whatever configuration may be needed to best fit the data and requirements of the application). Implementing this technique allows us to employ task-level parallelism on top of the aforementioned data-level parallelism. To be sure, this flexibility is an extremely important characteristic of the Function-Offload programming model and should be exploited whenever appropriate.

# 2.5.2 Chaining Programming Model

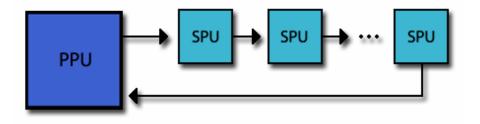

The Chaining programming model is based on the idea of a firefighter bucket brigade. First, the PPU sends a chunk of data to a SPU, which performs some amount of processing on the data. Once complete, the SPU hands the data off to the next SPU in line, which, in turn, performs its own operations. This continues down the chain until the processing is complete and the data is finally sent back to the PPU, as shown in Figure 2.5. Most assuredly, we can add the mechanics of pipelining into this procedure so that once the data has left the first SPU in the chain it can retrieve the next chunk of data to process in parallel.

This paradigm works best with data that must be processed in stages, such as applying filters for image processing. It can also be seen as an extension to the Function-Offload programming model where the chain in a Function-Offload setup has only one link.

**Figure 2.5: Chaining Programming Model**

As with the Function-Offload programming model, we will have more to say about Chaining in Chapter 4 when we examine some of the fundamental operations inherent in every Cell application.

# 2.6 Summary

In this chapter we have introduced the Cell processor's two processor types: the PPU and the SPU, how they communicate through mailboxes, DMA, and signal notifications, and a pair of useful programming models for developing applications on the Cell. We have also tried to point out important programming related aspects throughout the hardware discussion in hopes to give the reader a firm grounding for some of the higher-level details to come.

# **Chapter 2 Notes:**

- We acknowledge the fact that the SPUs can operate on their own (as "spulets") but for the purposes of this work we will only discuss the SPUs as helper coprocessors to the PPU.

- 2. The *preferred slot* refers to a 32-bit slot in a 128-bit vector register where results from reduction operations are stored. This is also the slot where scalar operations are performed.

- 3. STI refers to the Sony Toshiba IBM Cell Design Center in Austin, Texas, which was established in March of 2001.

- 4. An *intrinsic* is a lightweight function corresponding to a single or small set of assembly instructions performing a fundamental operation.

#### **Chapter 3: Related Work**

While Cell is still a very new platform, it is amazing how many "solutions" have been presented to assist developers in the new challenges presented by the hardware architecture. In this chapter we will discuss several of these projects in hopes to set the playing field for the forthcoming discussion of our contribution. Additionally, we will study a pair of solutions that have been presented on the more general topic of programming stream processors to help establish some of the common ideas related to Cell in this area. Finally, we will examine some of the published performance benchmarks for Cell, as well as compare and contrast the designs and features of the framework solutions.

#### **3.1** Stream Processing Solutions

A streaming processor independently executes a kernel over all elements in a given input stream and places results in a corresponding output stream. Examples of stream processors include conventional GPUs such as the [ATI R600] or [nVidia G80], the AMD Stream Processor [AMD Stream], and, in the light of its SPUs, Cell.

As alluded to earlier, stream processing can yield enormous boosts in program performance for particular application classes by exploiting data parallelism. This very same concept applies to the Cell SPUs and should be employed whenever possible.

In this section we will discuss a pair of related solutions designed to assist programmers in developing software applications to efficiently take advantage of the

26

powerful benefits offered by stream processors: the Brook programming language and the PeakStream Platform.

# 3.1.1 Brook Programming Language

Brook is an extension of the C programming language designed to assist developers in writing applications for stream processors. It was initially designed for the Merrimac Streaming Supercomputer Project at Stanford University. Since then, it has stemmed a descendant language called BrookGPU (from hereon just "Brook"), which allows developers to use the same language semantics to write stream programs for GPUs. For the purposes of our discussion, we are primarily interested in the GPU derivative as described in [Buck04] and [BrookGPU].

The Brook programming language presents the GPU as a general coprocessor rather than a graphics-specific one. Similar to other stream-oriented solutions, it was designed for computationally-intensive data-parallel applications with an emphasis on portability across consumer GPU platforms without sacrificing performance.

Brook defines programming constructs for *streams* and *kernels*. A *stream* is a collection of data to be processed independently in parallel. A *kernel* defines the scope in which streams may be operated on. More precisely, a kernel is a special function (designated by the kernel keyword) that internally loops over the input stream(s), performing the set of operations within the body of the function for each element. Brook also provides the mechanics for writing reduction operations to compute a single value from an input stream in a data-parallel fashion.

On the GPU, streams are stored as textures and kernels are compiled into pixel shaders. The Brook compiler is responsible for splitting the kernel into multiple passes if the number of outputs requested is greater than what the hardware supports (this varies depending upon the shader version supported by the particular GPU). This process maps onto the programmable graphics pipeline nicely since it is analogous to the method graphics programmers employ to produce composite effects (lighting is computed in one pass, blur is applied in another, etc.).

The Brook Runtime (BRT) software layer sits on top of OpenGL [OpenGL] and Direct3D [Direct3D] (the leading software interfaces for graphics programming) for both nVidia and ATI APIs, allowing it to utilize the benefits of GL or D3D directly in order to achieve the best possible performance. BRT also has a CPU backend, as well as a "close to metal" (CTM) backend [AMD CTM] to utilize the new initiative put forth from the ATI/AMD merger [Stokes06a]. Backends are chosen at runtime (either by hardware detection or user request) so there is no need to recompile Brook source code to switch.

#### 3.1.2 PeakStream Platform

The PeakStream Platform stemmed out of the Brook project outlined in the previous section [Stokes06b]. It was targeted to serving the High-Performance Computing (HPC) community<sup>1</sup>, with a standardized platform for developing computationally-intensive applications in C/C++ based on the stream programming model. Although the platform is no longer available in the commercial market<sup>2</sup>, we

still would like to discuss the main ideas behind their feature set as they continue to remain quite relevant to our own interests in developing for the Cell.

The PeakStream Platform was a full product suite that included a compiler, virtual machine, system profiler, and a developer API with semantics similar to MATLAB [MATLAB] (in terms of its native support for matrix/vector operations) [Stokes07b]. Similar to other virtual machine based solutions, this implied that once compiled, the application could be run on any PeakStream supported platform.

Under the hood, the PeakStream virtual machine handled the threading and scheduling for the execution of applications on specific hardware configurations, such as multi-core CPUs and CPUs with available GPUs [Woo07]. Programmers did not need to be aware of which hardware they were running on—only the structures and mechanics presented to them through the PeakStream API. This meant that the PeakStream platform was essentially an architecture-agnostic standard for writing applications for stream processors.

Parallel kernels were created by the virtual machine at runtime, which allowed for configuration-specific optimizations to be performed before the kernels were sent down the pipe to the hardware cores. The company took care to emphasize the point that since "target processors may have widely divergent architectures, it is important to make kernel density and boundary decisions at runtime rather than hardcoding them at application design time" [PeakStream07].

The API included several data types, the foremost of which was the *Array* (akin to a matrix in MATLAB). It also included an extensive math library that contained routines ranging from basic arithmetic operations to matrix multiplications

and convolutions. Moreover, the available math functions were written to be far more accurate than those native to the GPU hardware—another key point appealing to the targeted High-Performance and Scientific Computing communities. For example, [PeakStream07] presents a plot of the relative error for the exp() functions from a GPU (unspecified) and the PeakStream VM; while the GPU implementation results in relative error approaching 1.0e-05 as the magnitude of the function input grows, the PeakStream implementation results remain grouped around 1.0e-07 throughout.

The PeakStream Platform certainly sounded like a serious solution to many of the current problems facing application developers of this new generation of stream processor architectures, especially in the areas of hardware abstraction and platform portability. Unfortunately for Cell developers, their emphasis was always more on exploiting the power of GPUs than hardware such as the Cell (undoubtedly due to their foundations in Brook).

### **3.2 Function-Offload Solutions for Cell**

We will now turn our attention to the most prominent programming paradigm for Cell: the Function-Offload programming model. While there are other solutions which employ the Function-Offload model (some of which we will discuss in the next section), the Offload API and the RapidMind Development Platform proved to be the purest implementation examples of this paradigm. However, it is interesting to note that these frameworks provide two very different interfaces for presenting the same programming paradigm to their clients. As such, we will examine each of these in detail and compare their benefits and limitations.

### 3.2.1 Offload API

The Offload API was developed by the Parallel Programming Lab at the University of Illinois at Urbana-Champaign as a byproduct of porting the Charm++ runtime system to the Cell [Kunzman06a] [Kunzman06b]. Although Charm++ uses the Offload API to extend the portability of applications that utilize Charm++ to the Cell, the Offload API is independent of Charm++; therefore, we will limit our discussion purely to the Offload API.

In the Offload API, developers designate a *work request* to be executed on the SPU. A work request associates processing code with a set of three data buffers: read-only, read-write, and write-only. To ensure data-parallelism, a work request must be independent of the other work requests that may be currently executing on the SPUs. Work requests are asynchronously dispatched to an event-driven SPU runtime that handles the mechanics of transferring input data to the SPU, executing the processing code, and transferring the output data back to the PPU.

However, the Offload API operates under the following constraint: code must already be loaded onto the SPUs previous to the initialization of the Offload API. This implies that there is a major caveat to their paradigm: developers are forced to package all of their processing code into a single binary to be distributed across all of the SPUs, a characteristic that may be prohibitive to certain applications since, as we noted earlier, the 256 KB local store houses both code and data.

Another caveat, though not as acute as the first, is that the Offload API does not expose any methods for bringing more data to the SPU during the work request execution. This means that large operations must be serialized into several work requests, which, in turn, invokes an unnecessary pair of data transfers in between the stages as intermediate data must be returned to the PPU only then to be DMAed back to the local store where it once was.

Finally, we note two other minor caveats. First, the Offload API, as its name suggests, does not support other programming paradigms, such as Chaining, which may prove to be more efficient for particular applications. Secondly, the Offload API does not allow the programmer to specify a particular SPU to run on. This is handled by the API automatically. Such knowledge is useful for tasks like sorting as well as running a non-homogeneous set of programs on the available SPUs.

In spite of these limitations, the Offload API provides a nice library solution that allows developers to easily push jobs onto the SPUs without attending to the matters of scheduling.

### 3.2.2 RapidMind Development Platform

The RapidMind Development Platform [RapidMind] is a commercial product developed by RapidMind Inc. (formerly Serious Hack Inc.). It grew out of an opensource research project from the University of Waterloo Computer Graphics Lab called *Sh*, a metaprogramming language that is embedded inside C++ for programming GPUs [libSh06]. Like Sh, code for the RapidMind Development Platform (from hereon just "RapidMind") is evaluated and compiled at runtime for the target platform (multi-core CPUs, GPUs, or Cell), but is far more general purpose.

With RapidMind, clients write a single source program as a single thread of execution. Then, within this source developers specify which parts of the code they

want RapidMind to split and execute on multi-core processors in a data-parallel manner through the use of the metalanguage constructs [Du Toit07] [RapidMind07a].

The RapidMind API supplies its own *value* and *array* types. RapidMind values are fixed-sized tuples of scalars; they can contain any of the C++ standard types (such as int or float) or any of the supported non-standard types (such as a half-precision floating-point). Values can come in different sizes, though those with one to four elements are the most common. As one might expect, a RapidMind array is simply a contiguous sequence of RapidMind values. By using RapidMind arrays, the developer informs the backend that all operations performed on the elements contained within can be considered independent of each other, which allows the dynamic compiler to exploit data-parallelism and split the data accordingly so that computations can be divided amongst the cores.

Also, in the RapidMind API kernel functions are called *programs*. RapidMind programs are actually objects that are executed like a function but make special use of the *value* and *array* types. When arrays are passed in as parameters to a program, it is analogous to calling the program on each of the array elements individually, which is an act of data-parallelism that can be exploited by the RapidMind backend without the need of any further direction by the programmer in terms of the data's alignment, partitioning, or transfer to the other cores for parallel processing.

To be sure, the main benefit to using RapidMind is that it allows the programmer to quickly gain the benefits of multi-core processors without having to explicitly deal with the issues of threading, message-passing, or data transfer. As a close second, once the code is written, it is portable to any platform that RapidMind supports, including a wide range of multi-core CPUs, GPUs, and Cell-based systems.

Another notable aspect of developing with RapidMind is that there is no need for programmers to uproot their present development environment. All of the aforementioned functionality is wrapped in a library that is linked via the C++ compiler—no strings attached. Furthermore, the API supports incremental development by giving the programmer the freedom to choose which parts of the code will use RapidMind, which allows them to quickly parallelize "low-hanging fruit" components. These characteristics are very important for developers who wish to parallelize large projects or legacy code.

On the other hand, RapidMind is an industrial-strength commercial package with a deployment license starting at \$1500, which places it out of the reach of a portion of the Cell development community [Hearst07]. While it has been stated on the Sh site that developers at RapidMind Inc. plan to release an open-source version in the likeness of the commercial one, it may be some time before this actually happens. In addition, RapidMind covers up the scheduling of the SPUs. Since the inner workings of the package are unavailable, it is unknown if the RapidMind backend is capable of employing different programming paradigms, such as Chaining, in situations when it may be more efficient to do so. Finally, like the Offload API, the ability to choose a specific SPU or group of SPUs to run on is not an option when using RapidMind, though, again, this may not be one of the programmer's primary concerns when it comes to writing or porting an application to Cell.

# 3.3 Alternative Programming Models for Cell

In this section, we present some of the more exotic solutions to programming applications on the Cell: the Sequoia programming language, the MultiCore Framework, and Cell Superscalar. These solutions are each based on their own unique programming paradigms different from the ones covered so far.

#### **3.3.1** Sequoia Programming Language

The Sequoia group claims that when writing a high-performance application, the developer must have "non-trivial knowledge of the underlying machine's architecture" [Fatahalian06]. However, this requirement naturally discourages portability as there is always a trade-off between portability and performance. Sequoia responds to the emergence of so-called "exposed-communication" architectures where data movement is controlled in *software* between local and remote address spaces. This additional level of control that these architectures provide comes at the price of further complicating the design and implementation of software applications. As such, the Sequoia programming language [Sequoia] is intended to allow the developer to construct bandwidth-efficient parallel applications for exposedcommunication architectures while maintaining portability.

The Sequoia language presents an abstract hierarchical memory model (also referred to as a "tree of memories" [Sequoia]) that hides the lower level architecture configuration, e.g. a multi-core chip, Cell blade, or even a cluster of uniprocessors. This differs from approaches in other parallel languages such as Unified Parallel C [UPC] and Titanium [Titanium] since they are primarily designed to facilitate the movement of data "horizontally" across the processors of a parallel machine, while Sequoia's model facilitates the movement of data "vertically" through the memory hierarchy. Consequently, the programmer is required to design their applications to map onto this hierarchy in a divide and conquer tree-like manner.

One of the main benefits to Sequoia is that the architecture-specific method of communication via DMA, MPI message passing, or even a cache prefetch instruction, is all hidden under the hood, yet exposed through a uniform interface. This ensures developers can still gain the benefits of explicit communication while producing a portable solution. However, it should be noted that only vertical communication is allowed throughout the memory hierarchy, and thus it is not possible to directly pass data between sibling nodes. In order to cater to a node cluster in which there is no physical hierarchy of memory, Sequoia provides programmers with the ability to virtualize levels within the memory hierarchy utilized by the software. Data stored within a virtual memory level will be distributed across the physical memories of its children and when communication takes place between a virtual parent and its physical child, the appropriate horizontal transfers are employed. All of these virtual mechanics are transparent to the programmer and are handled by the Sequoia compiler and runtime. As a result, memory level virtualization provides developers with the flexibility to design their software around a memory hierarchy that best fits the needs of the application without having to be concerned with the possibility that levels of this custom hierarchy may be absent in the target platform(s).

Sequoia's core abstraction is the *task*, a pure function similar to a Brook kernel though without the syntactical sugar provided via a stream data type. Tasks are run in

36

parallel (or serially if not run on a parallel architecture), and mark the granularity of parallelism presented by the language. Each task is isolated into its own address space without the ability to communicate with other tasks. Hence, Sequoia exclusively handles data-parallelism through the Function-Offload programming model.