## **UC San Diego**

## **UC San Diego Electronic Theses and Dissertations**

#### **Title**

A Compute Capable SSD Architecture for Next-Generation Non -volatile Memories /

#### **Permalink**

https://escholarship.org/uc/item/6c08r3qq

#### **Author**

De, Arup

#### **Publication Date**

2014

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA, SAN DIEGO

#### A Compute Capable SSD Architecture for Next-Generation Non-volatile Memories

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Computer Science (Computer Engineering)

by

Arup De

#### Committee in charge:

Rajesh Gupta, Co-Chair Steven Swanson, Co-Chair James Buckwalter Maya Gokhale Ryan Kastner Michael Taylor

Copyright

Arup De, 2014

All rights reserved.

| The dissertation of Arup De is approved, and it is ac-    |

|-----------------------------------------------------------|

| ceptable in quality and form for publication on microfilm |

| and electronically:                                       |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

| Co-Chair                                                  |

|                                                           |

| Co-Chair                                                  |

University of California, San Diego

2014

## DEDICATION

To my family and friends for their unwavering support and encouragement over the years.

#### EPIGRAPH

Arise! Awake! and stop not until the goal is reached.

—Swami Vivekananda (Katha Upanishad)

## TABLE OF CONTENTS

| Signature Pa  | ge ii                                                                                                                                                                                                                                                                                                                                  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dedication .  |                                                                                                                                                                                                                                                                                                                                        |

| Epigraph .    |                                                                                                                                                                                                                                                                                                                                        |

| Table of Con  | tents                                                                                                                                                                                                                                                                                                                                  |

| List of Figur | es                                                                                                                                                                                                                                                                                                                                     |

| List of Table | s                                                                                                                                                                                                                                                                                                                                      |

| Acknowledge   | ements                                                                                                                                                                                                                                                                                                                                 |

| Vita          |                                                                                                                                                                                                                                                                                                                                        |

| Abstract of t | the Dissertation                                                                                                                                                                                                                                                                                                                       |

| Chapter 1     | Introduction                                                                                                                                                                                                                                                                                                                           |

| Chapter 2     | Emerging Storage Technologies and Motivation72.1 Emerging non-volatile memory technologies72.2 NVMs on Memory Bus vs. I/O Bus102.3 Why XSSD for NVMs?112.4 Motivation13                                                                                                                                                                |

| Chapter 3     | XSSD System Overview       17         3.1 Host Software Interface       19         3.2 Request Scheduler       19         3.3 Storage Processing Unit       21         3.4 NVM Controller       22         3.5 Programming Model       23         3.6 Example       24         3.7 Prototype       29         3.8 Power Model       29 |

| Chapter 4     | Applications       32         4.1       Fgrep-8       33         4.1.1       Fgrep-IO       33         4.1.2       Fgrep-RPC       34         4.1.3       Fgrep-HW       34         4.1.4       Evaluation       36                                                                                                                    |

|              | 4.2 Saxpy                        |

|--------------|----------------------------------|

|              | 4.2.1 Saxpy-IO                   |

|              | 4.2.2 Saxpy-RPC                  |

|              | 4.2.3 Evaluation                 |

|              | 4.3 2D-FFT                       |

|              | 4.3.1 2D-FFT-IO                  |

|              | 4.3.2 2D-FFT-RPC                 |

|              | 4.3.3 Evaluation                 |

|              | 4.4 Key-value store              |

|              | 4.4.1 KVS-IO                     |

|              | 4.4.2 KVS-RPC                    |

|              | 4.4.3 Evaluation                 |

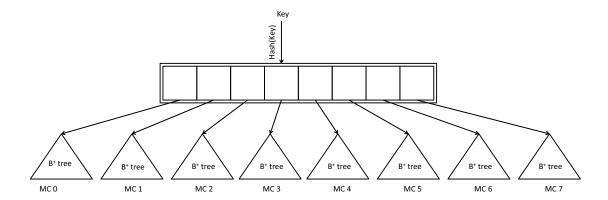

|              | 4.5 B+ Tree                      |

|              | 4.5.1 B+tree-IO                  |

|              | 4.5.2 B+tree-RPC                 |

|              | 4.5.3 Evaluation                 |

|              | 4.6 Summary                      |

|              |                                  |

| Chapter 5    | Related Work                     |

|              | 5.1 Intelligent Storage          |

|              | 5.1.1 Active Disks               |

|              | 5.1.2 Intelligent Disks (IDISKs) |

|              | 5.1.3 Smart SSD                  |

|              | 5.1.4 BlueDBM                    |

|              | 5.2 Intelligent Memory 60        |

|              | 5.2.1 IRAM                       |

|              | 5.2.2 Active Pages               |

|              | 5.2.3 FlexRAM                    |

|              | 5.3 Comparison                   |

|              | 5.4 Stream Programming 64        |

|              | 5.5 Key-value Store              |

| Chapter 6    | Infrastructure                   |

| Chapter o    | 6.1 MIPS                         |

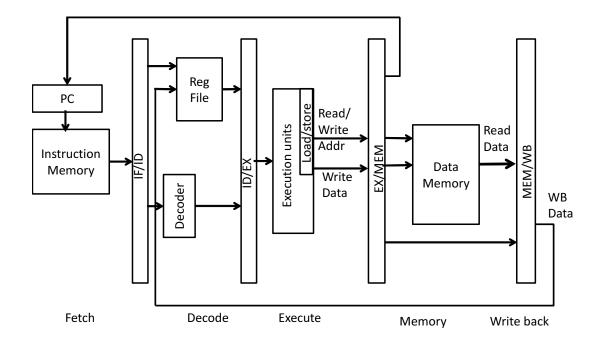

|              | 6.1.1 Pipeline Architecture      |

|              | 6.1.2 Software Tool Chain        |

|              |                                  |

|              | 0                                |

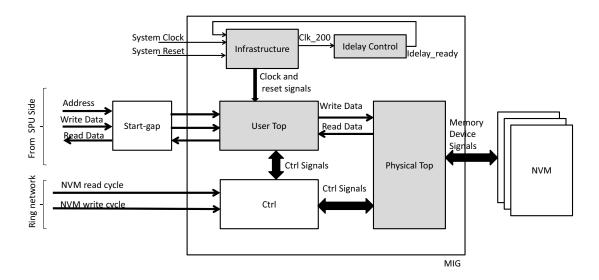

|              | 6.3 NVM Controller               |

| Chapter 7    | Conclusion and Future Work       |

| Ribliography | 8                                |

#### LIST OF FIGURES

| Figure 1.1:  | The conventional system storage hierarchy                               |

|--------------|-------------------------------------------------------------------------|

| Figure 1.2:  | The system storage hierarchy for XSSD                                   |

| Figure 2.1:  | The I/O latency breakdown for different storage technologies $$ . $$ 12 |

| Figure 3.1:  | XSSD system architecture                                                |

| Figure 3.2:  | Storage processing unit                                                 |

| Figure 3.3:  | Fgrep-8 kernel                                                          |

| Figure 3.4:  | XSSD RPC mechanism                                                      |

| Figure 3.5:  | XSSD RPC packet structure                                               |

| Figure 3.6:  | The execution flow on XSSD based system                                 |

| Figure 3.7:  | Fgrep-IO code                                                           |

| Figure 3.8:  | Fgrep-8 code                                                            |

| Figure 4.1:  | The execution time comparison                                           |

| Figure 4.2:  | The performance improvement of fgrep-HW as compared to                  |

|              | fgrep-IO                                                                |

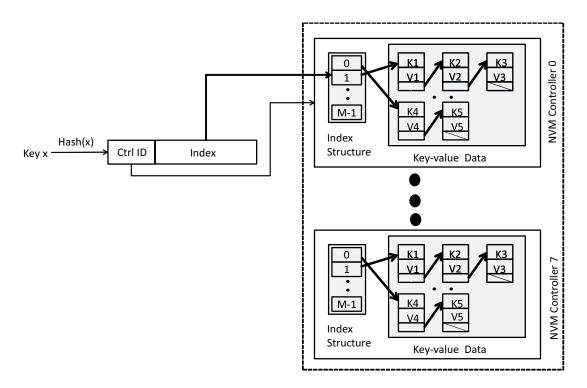

| Figure 4.3:  | KVS-IO GET operation                                                    |

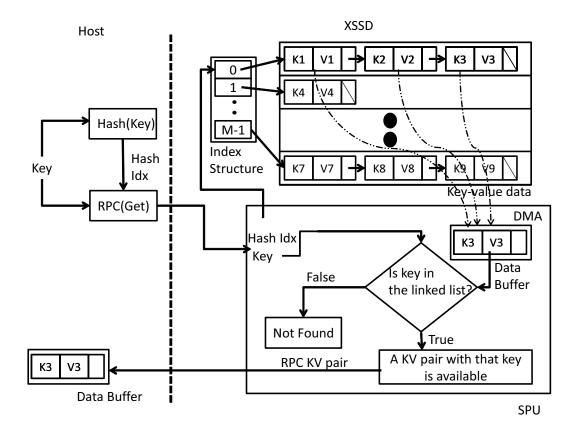

| Figure 4.4:  | Key-value store RPC implementation                                      |

| Figure 4.5:  | KVS-RPC GET operation                                                   |

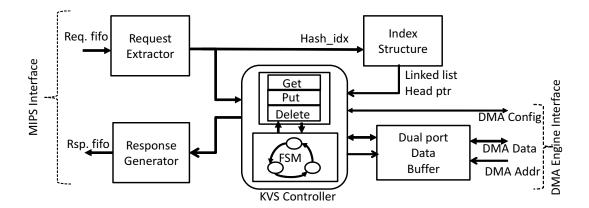

| Figure 4.6:  | Key-value store hardware accelerator                                    |

| Figure 4.7:  | MemcacheDB performance                                                  |

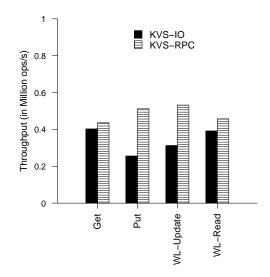

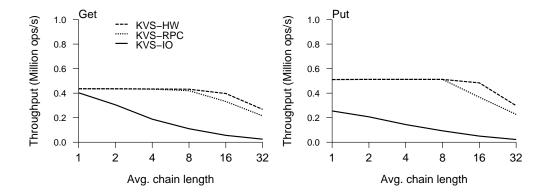

| Figure 4.8:  | Key-value operations as a function of chain length 48                   |

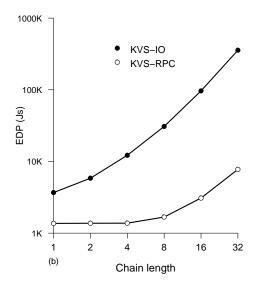

| Figure 4.9:  | The KVS EDP as a function of chain length                               |

| Figure 4.10: | B <sup>+</sup> tree traversal algorithm                                 |

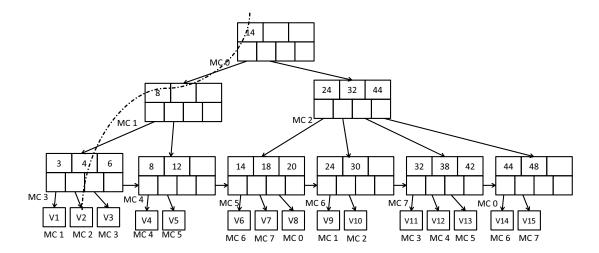

| Figure 4.11: | $B^+$ tree example                                                      |

|              | The RPC optimization on $B^+$ tree                                      |

| Figure 4.13: | The performance improvement of RPC based implementation . 54            |

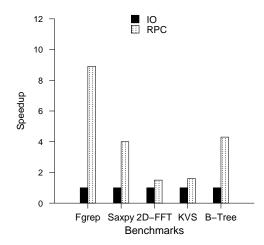

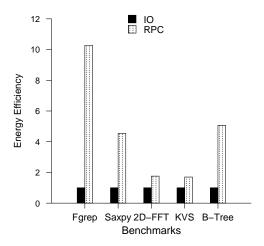

|              | The energy efficiency of RPC based implementation                       |

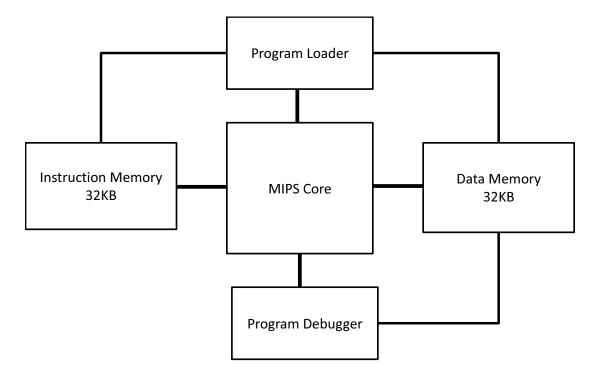

| Figure 6.1:  | MIPS block diagram                                                      |

| Figure 6.2:  | MIPS address space                                                      |

| Figure 6.3:  | MIPS pipeline architecture                                              |

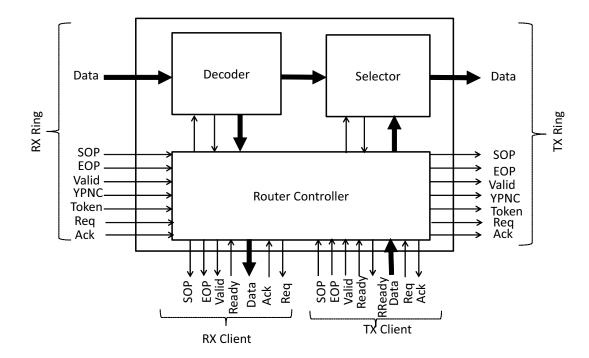

| Figure 6.4:  | Router architecture                                                     |

| Figure 6.5:  | NVM Controller                                                          |

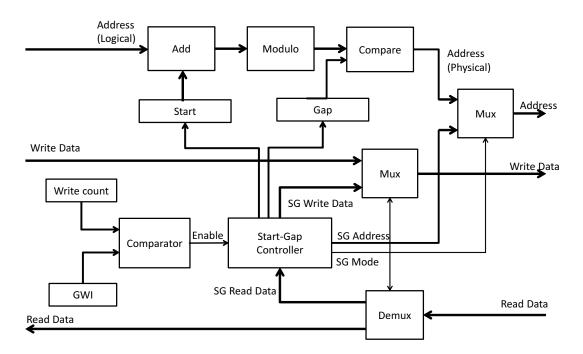

| Figure 6.6:  | Start-gap architecture                                                  |

|              |                                                                         |

## LIST OF TABLES

| Table 2.1: | Memory Technology Summary                     | 8  |

|------------|-----------------------------------------------|----|

| Table 2.2: | Storage Systems                               | .1 |

|            | RPC APIs                                      |    |

| Table 3.2: | XSSD power model                              | ίU |

|            | Applications                                  |    |

| Table 4.2: | The latency and bandwidth of access 8 KB data | 13 |

#### **ACKNOWLEDGEMENTS**

I am thankful to many people for their support and help to reach this point and prepare this dissertation.

I would like to thank my advisers Prof. Steven Swanson and Prof. Rajesh Gupta, and my supervisor Dr. Maya Gokhale for their constant support and guidance. They teach me various aspects of research work and give me a wonderful opportunity to build a smart storage system for next-generation non-volatile memories. This work provides me a deeper insight into the field of storage systems and significantly improves my system design skills starting from hardware design to application software. I would like to thank my other committee members for their comments and suggestions throughout this process.

I would like to thank the Non-Volatile Systems Lab (NVSL) and the Microelectronic Embedded Systems Lab (MESL) members. They help me in my research work. I spend an excellent time here.

I would like to thank the Persistent Memory Architecture (PerMA) group at LLNL. I work there as a Lawrence scholar (LSP) that gives me a nice opportunity to see one of the best US national laboratories. I meet with wonderful people and get to know about several other research work in my field.

I wish to thank those at UC Santa Barbara, UC San Diego, LLNL, IIT Kanpur, NVIDIA, Infineon and Skyworks. I have had some excellent friends, colleagues, mentors and managers along the path of this journey.

I would like to thank my parents, brothers, sisters and other family members. Their love and sacrifices are invaluable and I believe this is their success too.

Thank you all.

Chapters 1, 2, 3, 4, 5 and 7 contain material from "Minerva: Accelerating Data Analysis in Next-Generation SSDs", by Arup De, Maya Gokhale, Rajesh K. Gupta, and Steven Swanson, which appears in FCCM'13: Proceedings of the 21st IEEE International Symposium on Field-Programmable Custom Computing Machine. The dissertation author was the first investigator and author of this paper. The material in Chapters 1, 2, 3, 4, 5 and 7 is copyright ©2013 by

the Institute of Electrical and Electronics Engineers (IEEE). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than IEEE must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., IEEE, Inc., telephone +1 (732) 562-3966, or copyrights@ieee.org.

Chapters 1, 2, 3, 4, 5, 6 and 7 contain material from "Willow: A User-Programmable SSD", by Sundaram Bhaskaran, Trevor Bunker, Arup De, Mark Gahagan, Yanqin Jin, Robert Liu, Sudharsan Seshadri and Steven Swanson, which has been submitted for possible publication by USENIX in *Proceedings of the 11th USENIX Symposium on Operating Systems Design and Implementation*, (OSDI'14). The dissertation author was the third investigator and author of this paper.

Chapters 2 and 6 contain material from "Moneta: A High-Performance Storage Array Architecture for Next-Generation, Non-Volatile Memories", by Adrian M. Caulfield, Arup De, Joel Coburn, Todor I. Mollov, Rajesh K. Gupta, and Steven Swanson, wwhich appears in *MICRO-43: Proceedings of the 43rd Annual IEEE/ACM International Symposium on Microarchitecture*. The dissertation author was the second investigator and author of this paper. The material in Chapters 2 and 6 is copyright ©2010 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions@acm.org.

## ACADEMIC DISCLAIMER

The author wrote this dissertation in support of requirements for the degree Doctor of Philosophy in Computer Science at UC San Diego. The research is funded in part by the LLNL Graduate Scholars Program, and is not a deliverable for any United States government agency. The views and opinions expressed are those of the author, and do not state or reflect those of the United States government or Lawrence Livermore National Security, LLC.

## LLNL DISCLAIMER

Neither the United States government nor Lawrence Livermore National Security, LLC, nor any of their employees makes any warranty, expressed or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States government or Lawrence Livermore National Security, LLC, and shall not be used for advertising or product endorsement purposes.

#### VITA

| 2003      | B. Tech. in Electrical Engineering<br>Indian Institute of Technology<br>Kanpur, India    |

|-----------|------------------------------------------------------------------------------------------|

| 2003-2004 | Design Engineer<br>Skyworks Solutions, Inc.<br>New Delhi, India                          |

| 2004-2007 | Senior Design Engineer<br>Infineon Technoloigies<br>Bangalore, India                     |

| 2008-2008 | Teaching assistant<br>University of California, Santa Barbara                            |

| 2008      | Internship<br>NVIDIA<br>Santa Clara, California                                          |

| 2009      | M. S. in Computer Engineering<br>University of California, Santa Barbara                 |

| 2009-2014 | Research assistant<br>University of California, San Diego                                |

| 2011      | Internship<br>Lawrence Livermore National Laboratory<br>Livermore, California            |

| 2012-2014 | Lawrence scholar<br>Lawrence Livermore National Laboratory<br>Livermore, California      |

| 2014      | Ph. D. in Computer Science (Computer Engineering)<br>University of California, San Diego |

#### **PUBLICATIONS**

Arup De, Maya Gokhale, Rajesh Gupta, Steven Swanson, "Minerva: Accelerating Data Analysis in Next-Generation SSDs", *Proceedings of the 21st IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM)*, April 2013.

Adrian M. Caulfield, Todor I. Mollov, Louis Eisner, Arup De, Joel Coburn, Steven Swanson, "Providing Safe, User Space Access to Fast, Solid State Disks", Proceedings of the Seventeenth International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), March 2012.

Adrian M. Caulfield, Arup De, Joel Coburn, Todor I. Mollov, Rajesh K. Gupta, Steven Swanson, "Moneta: A High-Performance Storage Array Architecture for Next-Generation, Non-Volatile Memories", *Proceedings of the 43rd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO)*, December 2010.

Adrian M. Caulfield, Joel Coburn, Todor I. Mollov, Arup De, Ameen Akel, Jiahua He, Arun Jagatheesan, Rajesh K. Gupta, Allan Snavely, Steven Swanson, "Understanding the Impact of Emerging Non-Volatile Memories on High-Performance IO-Intensive Computing", Memories", *Proceedings of the 2010 ACM/IEEE International Conference for High Performance Computing, Networking, Storage and Analysis (SC)*, Novermber 2010.

#### ABSTRACT OF THE DISSERTATION

#### A Compute Capable SSD Architecture for Next-Generation Non-volatile Memories

by

#### Arup De

Doctor of Philosophy in Computer Science (Computer Engineering)

University of California, San Diego, 2014

Professor Rajesh Gupta, Co-Chair Professor Steven Swanson, Co-Chair

Existing storage technologies (e.g., disks and flash) are failing to cope with the processor and main memory speed and are limiting the overall performance of many large scale I/O or data-intensive applications. Emerging fast byte-addressable non-volatile memory (NVM) technologies, such as phase-change memory (PCM), spin-transfer torque memory (STTM) and memristor are very promising and are approaching DRAM-like performance with lower power consumption and higher density as process technology scales. These new memories are narrowing down the performance gap between the storage and the main memory and are putting forward challenging problems on existing SSD architecture,

I/O interface (e.g, SATA, PCIe) and software. This dissertation addresses those challenges and presents a novel SSD architecture called XSSD. XSSD offloads computation in storage to exploit fast NVMs and reduce the redundant data traffic across the I/O bus. XSSD offers a flexible RPC-based programming framework that developers can use for application development on SSD without dealing with the complication of the underlying architecture and communication management. We have built a prototype of XSSD on the BEE3 FPGA prototyping system. We implement various data-intensive applications and achieve speedup and energy efficiency of 1.5-8.9× and 1.7-10.27× respectively.

This dissertation also compares XSSD with previous work on intelligent storage and intelligent memory. The existing ecosystem and these new enabling technologies make this system more viable than earlier ones.

# Chapter 1

## Introduction

Existing memory hierarchy comprises of fast volatile SRAM-based caches, DRAM-based main memory and slow non-volatile disk or flash-based storage. The storage technologies (e.g., disk and flash) are orders of magnitude slower than the processor and volatile memories (SRAM and DRAM). Hence, those block-based storage technologies primarily use for persistence. The processor usually loads data from the storage to the main memory in form of byte stream, creates appropriate data structures and performs various computations on that data and finally, stores data to the storage. The existing software and hardware mainly optimize for block-based slow storage systems and use various techniques such as caching and prefetching to minimize the impact of those slow storage technologies on application's performance.

Recently, we have seen a growing interest for large scale I/O or dataintensive applications such as social networks, financial modeling, scientific simulations, data mining and enterprise applications. Those applications have large datasets (in order of petabytes or larger) that can not fit into the main memory (in order of gigabytes). Thus, we need to keep those data on storage and access via read and write I/O interfaces. Those large scale applications are either streaming over large data structures or randomly access different locations on storage. Thus the existing memory hierarchy is not very effective for those applications and the overall performance is limited by the slow storage technologies.

Emerging non-volatile memory (NVM) technologies such as phase-change

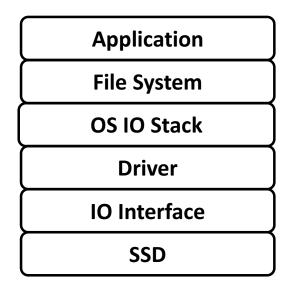

Figure 1.1: The conventional system storage hierarchy to access data from the storage by traversing the layers of software and the I/O bus.

memory (PCM) [Bre08], spin-transfer torque memory (STTM) [DSPE08] and memristor [Wil08] are very promising and are projected to have DRAM-like performance with lower power consumption and higher density as technology scales. They appear as a boon to those applications and achieve great attention in academia and industry as a viable replacement of existing storage technologies. However, the simple replacement of slow storage technologies with NVMs can not exploit the full potential of NVMs.

Figure 1.1 shows the conventional system storage hierarchy. It comprises of various layers: application software, file systems, operating system, driver, I/O interface (PCIe) and storage (e.g., disks and flash). The replacement of existing storage technologies with NVMs can significantly impact different layers. It can shift bottleneck from the storage to the software stack, and raise challenging problems on SSD architecture, I/O interface and software. Thus we need a thorough analysis and a broad perspective to find an efficient solution to best utilize NVMs.

This dissertation addresses various challenges with NVMs in the storage hierarchy and presents a novel SSD architecture called XSSD that colocates computation with data and supports various I/O or data-intensive computations on

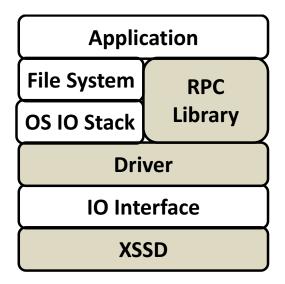

Figure 1.2: The system storage hierarchy for XSSD XSSD (gray boxes) extends the hardware and software to support application-specific processing close to the storage.

storage. Figure 1.2 shows the system hierarchy for XSSD. We make three major contributions: First, we extend the existing SSD architecture to offload I/O and data intensive application code to the storage array. By moving computation as close as possible to data, we can exploit the low latency and high bandwidth of these new storage technologies and reduce the data traffic between the storage and the host, resulting in a dramatic performance increase and significantly lower power consumption. Second, we enhance the existing system software stack with an RPC library to send the computational request from the host application to XSSD using simple RPC calls. We provide a runtime library that facilitates a smooth migration from the conventional I/O based storage to XSSD. Third, we develop a range of data or I/O intensive applications on XSSD using the RPC interface and compare them with the conventional I/O based implementation.

Chapter 2 discusses emerging NVM technologies. There are several NVM technologies (e.g., phase change memory (PCM), spin-transfer torque memory (STTM), memristor, magnetoresistive random access memory (MRAM), resistive random-access memory (RRAM), ferroelectric random access memory (FRAM), nano random access memory (NRAM) etc.) and they are at different levels of ma-

turity starting from the initial research and prototyping to manufacturing [KK09]. We discuss three most promising NVM technologies such as PCM, STTM and memristor. Then we study the latest work on NVM-based storage systems and discuss the advantages and disadvantages of NVMs on the memory bus and I/O bus. Based on our real measurement, we study the impact of NVMs on existing storage hierarchies. We present motivation for XSSD and discuss salient features of XSSD to best utilize NVMs.

Chapter 3 discusses XSSD system overview and various design enhancement to exploit the full potential of NVMs and reduce the redundant data movement between the storage and the host. We enhance the host software interface and the request scheduler to easily dispatch various computational requests to XSSD. XSSD's SPU has a heterogeneous processing architecture that executes control-intensive operations on a single-issue MIPS processor and data-intensive operations on hardware accelerators. The MIPS and hardware accelerator significantly improve performance and energy efficiency. XSSD facilitates a flexible RPC based framework that enables applications to offload any application-specific functions down to the storage and provide a simple programming environment that developers can use to process data stored in the SSD without dealing with the complication of the underlying architecture and communication management. We build a prototype of XSSD on the BEE3 FPGA prototyping system [bee] for our evaluation. We implement a power model for XSSD based system to measure the power dissipation to run various workloads.

Chapter 4 presents the implementation of different I/O and data-intensive applications on XSSD. We have chosen stream and random access applications for our evaluation. XSSD uniquely supports large scale applications with poor temporal and spatial locality. Example includes key-value store and tree-traversal which often have very little data reuse and frequent random access to different data locations. As a result, they make poor use of existing memory hierarchies and perform poorly on the conventional system due to the I/O limitation. We compare the performance and the energy efficiency of those applications on XSSD with the highly optimized I/O based implementation. XSSD improves performance

and energy efficiency by up to  $8.91 \times$  and  $10.27 \times$  for stream applications and up to  $4.39 \times$  and  $5.07 \times$  for applications with random accesses to storage.

Chapter 5 discusses some of the most prominent previous work on intelligent storage (e.g., Active Disks [RGF98, AUS98], Intelligent Disks [KPH98], Smart SSD [KsKMP13] and BlueDBM [JLFA14] ) and intelligent memory (e.g., IRAM [PAC+97], Active Pages [OCS98] and FlexRAM [KHH+99] ). Then we compare XSSD with previous work.

Chapter 6 presents XSSD infrastructure. XSSD infrastructure has several components such as PCIe, request scheduler, ring network, MIPS processor and NVM controller. We mainly focus on three main components: MIPS processor, ring network and NVM controller. In MIPS processor, we present the pipeline architecture and memory-mapped device interface. We discuss various utility applications such as loader, debugger and profiler to improve productivity. Then we discuss design details of ring network that ensures reliable communication among different components. Finally, we present NVM controller that can emulate different NVM technologies and support start-gap wear leveling technique [QKF+09].

Finally, in Chapter 7 we conclude and present some future work.

## Acknowledgments

This chapter contains material from "Minerva: Accelerating Data Analysis in Next-Generation SSDs", by Arup De, Maya Gokhale, Rajesh K. Gupta, and Steven Swanson, which appears in FCCM'13: Proceedings of the 21st IEEE International Symposium on Field-Programmable Custom Computing Machine. The dissertation author was the first investigator and author of this paper. The material in this chapter is copyright ©2013 by the Institute of Electrical and Electronics Engineers (IEEE). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than IEEE must be honored. Abstracting

with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., IEEE, Inc., telephone +1 (732) 562-3966, or copyrights@ieee.org.

This chapter contains material from "Willow: A User-Programmable SSD", by Sundaram Bhaskaran, Trevor Bunker, Arup De, Mark Gahagan, Yanqin Jin, Robert Liu, Sudharsan Seshadri and Steven Swanson, which has been submitted for possible publication by USENIX in *Proceedings of the 11th USENIX Symposium on Operating Systems Design and Implementation, (OSDI'14)*. The dissertation author was the third investigator and author of this paper.

# Chapter 2

# Emerging Storage Technologies and Motivation

In this chapter, we discuss emerging non-volatile memory (NVM) technologies and the recent work on NVM based storage systems. We study the advantages and disadvantages of NVMs on parallel memory bus and serial I/O bus (PCIe). Then we identify problems with the existing software stack and I/O interface (e.g., PCIe, SATA) for NVMs and present motivation for XSSD.

## 2.1 Emerging non-volatile memory technologies

In the last five decades, the disk has been the basic unit of persistent storage for small and large scale computing systems. Disks are highly reliable but generally suffer from poor latency and bandwidth, especially relative to processor and main memory advances. Recently, flash based PCIe-attached SSDs have become popular (e.g., FusionIO [FI09] and Virident [Vir10] as representative of the high end SSDs) and are significantly faster (100×) than disk but still have slow erase, high write latency and wear-out issues. In addition, flash does not support in-place update and requires extra erase cycle to update data at same location. To overcome that drawback, SSD vendors provide a flash translation layer (FTL) between the software and flash memory which creates an illusion of in-place update and maintains the logical to physical page mapping.

|            | •          | 0.0       | ٠.      | ,       |              | , ,           |

|------------|------------|-----------|---------|---------|--------------|---------------|

| Technology | Density    | Endurance | Latency |         | Energy       |               |

|            |            |           | Read    | Write   | Read         | Write         |

| Flash      | $4 F^2$    | $10^{5}$  | 25 us   | 200 us  | 250  pJ/bit  | 250  pJ/bit   |

| PCM        | $4 F^2$    | 108       | 67.5 ns | 215  ns | 3.4  pJ/bit  | 17.84  pJ/bit |

| STTM       | $10 \ F^2$ | $10^{15}$ | 29.5 ns | 95 ns   | 0.33  pJ/bit | 10.0  pJ/bit  |

| Memristor  | $6 F^2$    | $10^{10}$ | 100 ns  | 100 ns  | 2 pJ/bit     | 2 pJ/bit      |

| DRAM       | $4 F^2$    | $10^{18}$ | 25 ns   | 25 ns   | 2.4  pJ/bit  | 2.4  pJ/bit   |

Table 2.1: Memory Technology Summary [ITR09, LIMB09, PCM, GIS10, memb]

Emerging byte-addressable NVM technologies such as phase change memory (PCM), spin-transfer torque memory (STTM) and memristor are narrowing the performance gap between the storage and the main memory and have potential, with density improvements, to replace existing storage technologies in future. NVMs are fundamentally different than existing slow block-based storage technologies and offer orders of magnitude performance improvement and energy saving as compared to disks and flash. NVMs support in-place update and do not need the FTL between the software and memory device unlike flash.

There are several NVM technologies under research in academia and industry. Here, we present three well-known NVM technologies: phase change memory, spin-transfer torque memory and memristor. Table 2.1 briefly summarizes density, latency and energy dissipation of different memory technologies.

Phase change memory Phase change memory (PCM) is the most promising of the upcoming NVM technologies [Bre08]. It exploits the property of chalcogenide glass to switch between two states, amorphous (high-resistance) and crystalline (low-resistance), with application of current pulses. The crystalline state achieves by heating above crystallization temperature using a moderate, long current pulse, and logically stores "1". The amorphous state achieves by high, short current pulse and logically stores "0". A small read current (less than 100uA) used to sense data stored in a cell by measuring its resistance thus PCM consumes very small power for read. PCM approaches DRAM-like performance with lower power consumption and higher density as process technology scales. Despite this promise, PCM suffers from long write latency, high energy writes and limited write endurance

(on the order of 10<sup>8</sup>). Recent studies [LIMB09, QSR09, QKF<sup>+</sup>09, DAR09] proposed several hardware and software enhancements such as various wear-leveling methods, new row buffer design, selective writes, (DRAM/PCM) hybrid memory architecture, hot page swapping and write buffers to overcome PCM technology limitations and make them a viable option for charge-based memory replacement such as DRAM and flash.

Spin-transfer torque memory Spin-transfer torque memory (STTM) stores bits as the orientation of a magnetic layer in a magnetic tunnel junction. The junction's resistance is low (the anti-parallel) or high (the parallel state) based on the orientation [DSPE08]. STTM uses a spin-polarized current instead of electric fields of previous MRAM technologies to set the orientation. It offers low latency and high bandwidth read and writes accesses, and as technology scales, it will achieve SRAM's performance with zero standby power. It can significantly reduce the power consumption of a wide range of applications starting from mobile devices to data centers. Recent research [GIS10] also proposed a novel STTM-based resistive computation to replace the conventional CMOS technology based logic implementation in near future.

Memristor Memristor [Chu71] represents fourth passive element after the resistor, inductor and capacitor. It relies on a hysteresis effect between the current and voltage. Presently, it is a most promising Resistive RAM (RRAM) technology. The memristor device has a platinum crossbar with titanium dioxide switches. The titanium dioxide has a bipolar resistive switching that produces hysteresis loop behavior. In year 2008, HP Labs fabricated first memristor [Wil08]. The memristor is projected to offer better scalability, power, performance and endurance with scaling and is compatible with CMOS technology. The memristor is not only use as a non-volatile memory device but also use to perform arithmetic operations on stored data that can reignite the processing in memory (PIM) research.

## 2.2 NVMs on Memory Bus vs. I/O Bus

Recently, there is a huge interest in academia and industry for NVM-based storage systems. There are several research works on NVM-based storage systems where either NVMs are attached to the memory bus such as NV-Heaps [CCA<sup>+</sup>11], BPFS [CNF<sup>+</sup>09] and CDDS [VTRC11] or attached to the I/O bus (e.g. PCIe) such as Moneta [CDC<sup>+</sup>10]. Those systems made various software and hardware enhancements for better utilization of NVMs.

NVMs on memory bus provide fast access to NVMs using load and store operations. NV-heaps [CCA+11] project proposes a persistent object system for NVMs which facilitates a simple programming interface and protects against system and application failures by providing a model for persistence (to catch all sorts of programming errors) and supports transactional semantics. They implement various data structures such as search trees, hash tables, sparse graphs, and arrays using NV-heaps. The BPFS [CNF+09] project proposes a file system and the underlying hardware enhancement for better utilization of NVMs. They optimize short-circuit shadow paging for fast and consistent updates. The hardware ensures ordering and reliability of NVM accesses. CDDS (Consistent and Durable Data Structures) [VTRC11] safely exploits fast NVMs and provides atomic update using versioning. The versioning scheme also facilitates rollback for failure recovery. CDDS implements B-Tree data structure and optimizes lookup, insert, and delete operations. However, NVMs on memory bus may suffer from scalability issues due to parallel interface and limited package pin count of the processor [ITR09].

XSSD connects with the host using PCIe which facilitates safety and scalability to sustain fast growth of data as compared to the parallel memory bus interface. The recent work on PCIe-attached NVM-based SSD architecture called Moneta-D [CMD<sup>+</sup>12] focuses on optimizing read and write I/O performance for NVMs. Moneta-D provides a channel based I/O interface for each application and bypasses some portion of file system and OS overhead for different I/O calls. However, the PCIe interface and driver still limit the overall performance of Moneta-D. It inspires XSSD architecture that offloads application-specific functions down to the storage to eliminate the PCIe and driver overhead, and better utilize NVMs.

Name Technology Description Capacity RAID-Disk 4 TB RAID-0 of 4x 1 TB 7200 rpm hard Disk drives Fusion-IO Flash Fusion-IO 80 GB PCIe-attached flash-80 GB based SSD PCM Moneta-D 64 GB Moneta-D 64 GB PCIe-attached PCMbased SSD

Table 2.2: Storage Systems

## 2.3 Why XSSD for NVMs?

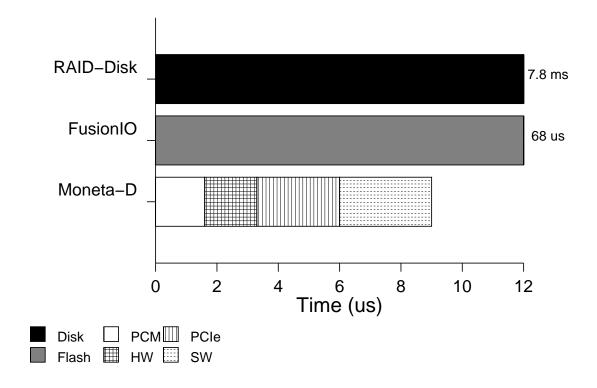

NVMs are shifting the bottleneck from the storage to I/O interface (e.g., SATA and PCIe) and system software stack. We measure the time spent on various components of I/O for different storage technologies to get the essence of XSSD for NVMs. Table 2.2 briefly describes different storage systems. Figure 2.1 shows the I/O latency for 4 KB random read accesses on different storage systems. The total I/O latency of RAID-disk is 7.8 ms and it spends more than 99% of total I/O latency on disk due to the disk seek latency and rotational delay. Fusion-IO shows  $114 \times$  improvement as compared to the disk and takes 68  $\mu$ s for accessing 4 KB pages. However, the raw storage access overhead is still more than 90% of total I/O latency for flash-based SSD. Moneta-D shows the huge improvement as compared to the disk and flash and achieves I/O latency of 9  $\mu$ s for 4 KB random reads. The raw NVM access overhead for Moneta-D is less than 20% of total I/O latency and the remaining overhead comes from the PCIe and software drivers. This indicates a huge scope of improvement in performance and energy efficiency with XSSD by offloading computations in storage. We also measure the read bandwidth of different storage technologies. The RAID-disk achieves 500 KB/s for 4 KB random page accesses and 125 MB/s for 4 KB sequential page accesses. The disk seek latency (~10 ms) limits the random access performance. Fusion-IO achieves 250 MB/s for 4 KB random page accesses and outperforms disk by  $250 \times$  due to relatively fast random read accesses on flash. PCM-based Moneta-D achieves 1.6 GB/s for 4 KB random page accesses which is more than  $6.4\times$  improvement as compared to Fusion-IO. However, the aggregate internal bandwidth of Moneta-

Figure 2.1: The I/O latency breakdown for different storage technologies the PCM access time is less than 20% of total I/O latency for 4 KB page access.

D is 23.8 GB/s and the PCIe bandwidth and software driver limit the overall Moneta-D's performance. XSSD exposes the large internal bandwidth to the end application by providing low latency and high bandwidth accesses to NVMs and eliminating PCIe and driver overhead. As the performance of NVMs increase with technology scaling, we get more advantage in terms of performance and energy efficiency by pushing the computation close to data.

XSSD also supports more flexible access patterns to leverage byte-addressable fast NVMs and provides a significantly higher level of programma-bility compared to the conventional storage stack. It offers a flexible RPC-based programming framework that developers can use for application development on SSD without dealing with the complication of the underlying architecture and communication management. XSSD is not limited to streaming applications and supports a wide range of I/O intensive applications with small random accesses to the storage such as key-value store and B<sup>+</sup>tree traversal.

#### 2.4 Motivation

XSSD extends the conventional SSD architecture to incorporate the computational capabilities in the SSD to achieve high performance and energy efficiency than the conventional SSD based system. XSSD considered all three P's of system design: performance, power and programmability. Several fundamental trends inspire XSSD architecture.

Inadequate existing SSD architecture The existing SSD architecture optimizes for block accessible flash where the overhead of I/O interface and software is negligible (less than 10%) as compared to the raw storage access overhead. NVMs are more than 1000× faster than flash and facilitate in-place update unlike flash. NVMs are radically changing the I/O latency breakdown among the software stack, PCIe and NVM. The overhead of PCIe and software stack is more than 80% of total I/O latency and the remaining overhead comes from NVM [CMD+12]. So, the simple replacement of flash with NVMs actually destroy the huge gain from fast NVMs and it instigates XSSD architecture to offload application-specific processing down to the storage to exploit the low latency and high bandwidth of NVMs and reduce the redundant data movement between the storage and the host.

Huge performance and energy gain XSSD is based on NVMs which have low latency and low power dissipation as compared to existing storage technologies such as disk and flash. XSSD significantly improves performance and energy efficiency by reducing data traffic between the host and the storage, and performing efficient application-specific execution in the SSD. XSSD has a heterogeneous processing architecture that executes control-intensive operations on single-issue MIPS processor and data-intensive operations on hardware accelerator (holds fixed function hardwares). The MIPS and hardware accelerator significantly improve performance and energy efficiency. There are several research work on heterogeneous computing such as EXOCHI [WCC+07] and C-cores [VSG+10] have demonstrated more than 10× performance improvement and 16× energy saving as compared to general-purpose processing. We implemented various data-intensive applications

on XSSD and achieved speedup and energy efficiency of  $1.5\text{-}8.9\times$  and  $1.7\text{-}10.27\times$  respectively.

Growing demand for large scale applications In the age of Big data, large scale applications such as scientific data analysis, social networks and enterprise applications need to process large amount of data in order of petabytes. For example, semantic graphs representing social networks of interest to the Department of Homeland Security will have 10<sup>15</sup> entities [KBC+05]. The execution time of such large data analysis algorithms is dominated by storage performance. They are continuously spanning on three dimensions: volume (petabytes per day), velocity (real-time analytics) and variety (structured and unstructured data web logs, audio and video images). These applications often have low temporal and spatial locality. As a result, they make poor use of existing memory hierarchies and perform badly on the conventional system due to large I/O overhead. XSSD exposes huge bandwidth and low latency of NVMs to those applications and improves performance by eliminating I/O and efficient data processing in the SSD. XSSD allows the processing of the system to scale with increasing storage demand for various applications.

Ecosystem Existing ecosystem favors XSSD architecture. There are three main reasons. First, the EDA tools and FPGA/ASIC technologies are more mature than before to build XSSD system. These design methodologies can reduce the design cycle time of the hardware development. Second, the software tools, compiler infrastructure and programming languages are more user-friendly to utilize the heterogeneous processing architecture of XSSD. We have seen OpenCL becomes the de facto standard for heterogeneous computing and significantly reduces the cost of adopting a new processor architecture. Third, XSSD keeps same PCIe interface to connect with the host analogous to the existing SSD that simplifies migration from the existing SSD to XSSD. Also, it can marginally increase cost to incorporate additional computing resources.

## Acknowledgments

This chapter contains material from "Minerva: Accelerating Data Analysis in Next-Generation SSDs", by Arup De, Maya Gokhale, Rajesh K. Gupta, and Steven Swanson, which appears in FCCM'13: Proceedings of the 21st IEEE International Symposium on Field-Programmable Custom Computing Machine. The dissertation author was the first investigator and author of this paper. The material in this chapter is copyright ©2013 by the Institute of Electrical and Electronics Engineers (IEEE). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than IEEE must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., IEEE, Inc., telephone +1 (732) 562-3966, or copyrights@ieee.org.

This chapter contains material from "Moneta: A High-Performance Storage Array Architecture for Next-Generation, Non-Volatile Memories", by Adrian M. Caulfield, Arup De, Joel Coburn, Todor I. Mollov, Rajesh K. Gupta, and Steven Swanson, wwhich appears in *MICRO-43: Proceedings of the 43rd Annual IEEE/ACM International Symposium on Microarchitecture*. The dissertation author was the second investigator and author of this paper. The material in this chapter is copyright ©2010 by the Association for Computing Machinery, Inc. (ACM). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., ACM, Inc., fax +1 (212) 869-0481, or permissions©acm.org.

This chapter contains material from "Willow: A User-Programmable SSD", by Sundaram Bhaskaran, Trevor Bunker, Arup De, Mark Gahagan, Yanqin Jin, Robert Liu, Sudharsan Seshadri and Steven Swanson, which has been submitted for possible publication by USENIX in *Proceedings of the 11th USENIX Symposium on Operating Systems Design and Implementation, (OSDI'14)*. The dissertation author was the third investigator and author of this paper.

# Chapter 3

# XSSD System Overview

As discussed in the previous chapter, emerging byte-addressable non-volatile memory (NVM) technologies are very promising and offer orders of magnitude faster accesses than existing storage technologies such as disks and flash. This huge improvement shrinks the performance gap between the storage and the main memory, and requires rethink in the storage architecture, I/O interface and system software stack to exploit fast NVMs and maximize application gain.

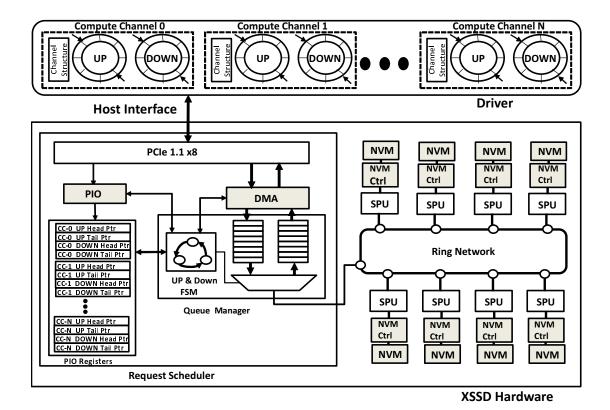

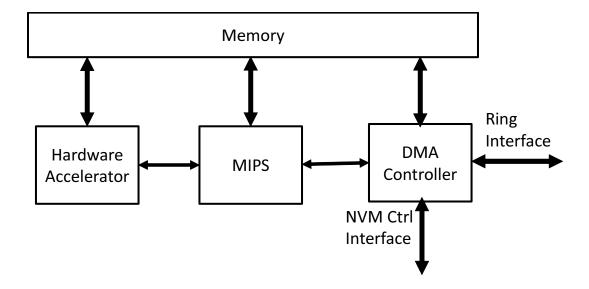

XSSD offloads various application-specific computations down to the storage to exploit the low latency and high bandwidth of emerging NVMs and significantly reduce data movement across the I/O bus. Figure 3.1 shows the XSSD architecture. We enhance the existing SSD with a new host software interface, request scheduler and storage processing unit to perform computation in storage. XSSD has four main components: request scheduler, storage processing unit (SPU), ring network and memory controller. We extend the host interface for XSSD to dispatch function calls from the host using Remote Procedure Call (RPC) over the PCIe. The driver offers a private communication channel interface per thread to issue an RPC call to the XSSD. The request scheduler receives it and dispatches it to the corresponding storage processing unit over the ring network. The storage processing unit (SPU) receives the RPC request and sends back acknowledgement. Then it executes that function with the given arguments and sends back a response to the host via the request scheduler using the RPC interface. The RPC hides complex message passing among different components and provides a sin-

Figure 3.1: XSSD system architecture extends the software driver and SSD hardware with an augmented request scheduler and SPUs.

gle programming interface for the application developer to dispatch computations from the host to SPUs. Each NVM controller connects with dual-rank DIMMs using the DDR2 interface. The ring network provides a packet based reliable communication among the request scheduler and storage processing units, and has peak bandwidth and round trip latency of 3.72 GB/s and 88 ns respectively. It dispatches an RPC request from the request scheduler to the SPU based on SPU ID and packet size information and similarly, sends back response from the SPU to the request schedule. It supports hardware flow control to efficiently utilize the ring network.

We describe each component in more detail below.

#### 3.1 Host Software Interface

Applications use a compute channel to offload computations to the storage. The channel provides a low-level communication mechanism between the SPU and the application thread. The channel has a set of control registers to manage communication, access permission and a pair of circular queues (downstream and upstream) for data communication between the request scheduler and the host. The kernel driver allocates a channel up on application request. The user space library mmaps it to application space and grants access to the control registers and circular queues. The application can write to the downstream queue and read from the upstream queue. The driver and hardware maintains the head and tail pointers for both the downstream and upstream queues. The host issues a Programmed IO (PIO) write to update the head pointer of the downstream queue to send data to the XSSD and issue a PIO write to update the tail pointer of the upstream queue to receive data from the XSSD. The tail pointer of the downstream queue and the head pointer of the upstream queue are managed by the request scheduler of XSSD. We use a DMA interface to send commands with various sizes along with data and the PIO interface updates different control registers, head and tail pointers of circular queues and notifies data availability to the request scheduler. When the host wants to send data to the XSSD, it opens a channel and writes the data into the downstream queue, and issues a PIO write to update the head pointer of the downstream queue. XSSD uses this information to fetch data from the host. During receive, the host polls on the upstream queue and reads all data and then issues a PIO write to update the tail pointer of the upstream queue. We provide an RPC library on top of the driver to call application-specific functions and exploit the compute resources inside XSSD. In Section 3.5 we describe our RPC library and low level message protocols in detail.

## 3.2 Request Scheduler

The request scheduler receives data from the host over the PCIe and sends to different SPUs over the ring network. The request scheduler has two main com-

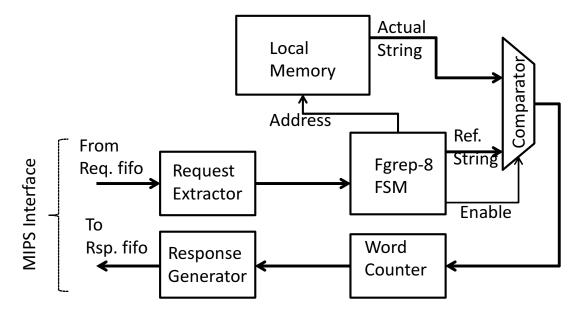

**Figure 3.2**: **Storage processing unit** executes application-specific functions in the SSD using MIPS. The DMA controller loads data from the NVM controller and the ring network and the hardware accelerator improves performance and energy efficiency.

ponents: PCIe interface (PIO and DMA) and queue manager. The PIO interface is responsible for read and write to various control registers and the DMA interface is responsible for issuing and handling DMA requests to send and receive data from the host. The queue manager is responsible for reading requests from the host, sending them to SPUs via ring network and writing the response back to the host. It has two finite state machines: down\_fsm and up\_fsm. When the host sends data to XSSD, it opens a compute channel, writes to the downstream queue and issues a PIO write to update the head pointer of the downstream queue. The down\_fsm uses this pointer to find how many new entries are available in the downstream queue and issues the appropriate DMA requests to read data from the host. Then it checks the message header for the destination SPU and dispatches over the ring network. The up\_fsm is similar to down\_fsm for sending data from the XSSD to the host.

# 3.3 Storage Processing Unit

The storage processing unit (SPU) receives an RPC from the host via the request scheduler, executes application-specific functions and sends back a response. It comprises of four main components: MIPS, DMA Controller, hardware accelerator and local memory. We use a single issue, 5-stage pipelined 32-bit MIPS processor to run application-specific functions in the SSD. The MIPS simplifies design, reduces gate count and improves energy efficiency. The DMA controller is a memory-mapped hardware device that enables fast movement of data from the NVM controller and ring network to the local memory and vice-versa. The MIPS configures various control registers of DMA controller to set source address, destination address and data size, initiates DMA operation and waits for completion. This movement of data by the DMA controller significantly reduces the load on the MIPS. The hardware accelerator holds fixed function hardware to improve performance and energy efficiency. The MIPS sends input arguments and receives response from the hardware accelerator using a memory-mapped interface. We developed several application-specific hardware accelerators manually in Verilog. They offer the highest performance at the corresponding cost of hardware design expertise.

As an example, Figure 3.3 shows a simple streaming kernel, fgrep-8, which receives input arguments from the MIPS using a memory mapped request FIFO. The request extractor receives them and extracts the reference string and data location information. The data may reside in a local NVM, in which case it is loaded by the local NVM controller, or may reside in a remote NVM. In the latter case, the data must be read by the remote NVM controller and transferred via the ring network to a memory block local to the SPU. The fgrep-8 FSM compares the reference pattern with the data in the local memory block. On matches, the kernel increments the match word counter and when all the requested data has been searched, it sends back the results to the MIPS via the response generator by writing to the response FIFO.

**Figure 3.3**: **Fgrep-8 kernel** receives compute requests from the MIPS, finds matching strings, updates the word match counter, and sends a response to the MIPS.

## 3.4 NVM Controller

XSSD has eight NVM controllers. Each controller connects with dual-rank DIMM using DDR2 interface with total capacity 8 GB. Each controller runs at 250 MHz, receives 16 bytes of data each cycle and has peak bandwidth of 3.72 GB/s. Each DIMM has 16 memory chips per rank, each chip has 8 banks and has a row buffer of 8 KB. NVM controller ensures persistence and writes back data from volatile row buffer to non-volatile NVM memory array in case of power failures to prevent data loss. Since phase change memory cells have limited life time (10<sup>6</sup> writes), the NVM controller performs the start-gap wear-leveling and address randomization scheme [QKF<sup>+</sup>09] to evenly distribute write memory accesses across different physical memory pages with very little (less than 1%) overhead.

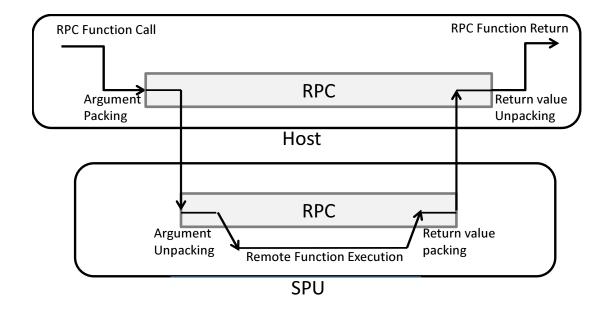

Figure 3.4: XSSD RPC mechanism between the host and the SPU.

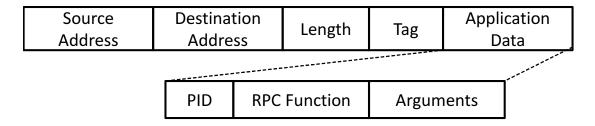

# 3.5 Programming Model

XSSD facilitates an RPC-based framework to exploit the processing capability in storage. RPC is simple to use and is often deployed in distributed services. It is based on procedure call in a client/server setting and provides simple programmability to implement various application-specific functions in storage. Figure 3.4 shows the RPC mechanism between the host and the SPU. The host application calls an RPC function with a given arguments. The RPC library creates a packet and dispatches it to the SPU. The destination SPU unpacks it, calls the RPC function and returns back result to the host. Figure 3.5 shows the RPC packet structure for communication. The packet has following fields.

- Source address identifies the sources address (host or SPU ID information)

- **Destination Address** identifies the destination address ( host or SPU ID information)

- Length holds the length of the packet

Figure 3.5: XSSD RPC packet structure to communicate with the SPU.

- Tag keeps sequence number to maintain ordering

- Application data holds application related information such as process ID (PID), RPC function and associated arguments.

The RPC library provides a set of APIs for simple communication between the host and SPUs. Table 3.1 briefly describes those RPC APIs that are responsible for creating RPC requests and responses, performing DMA operations, and sending and receiving RPC messages.

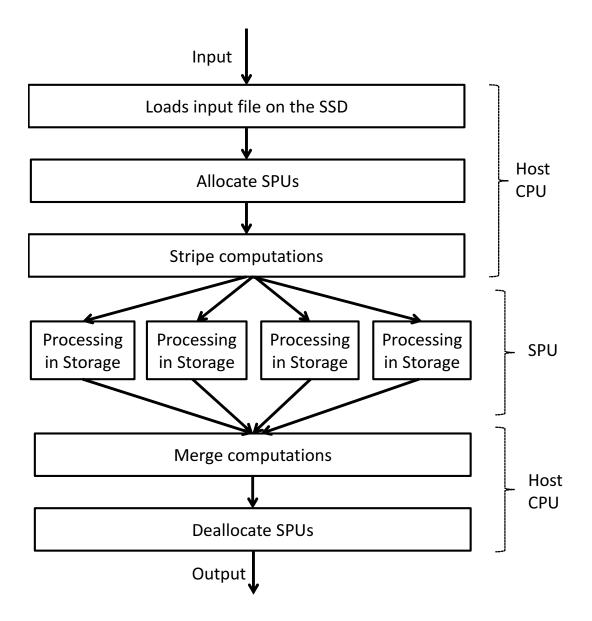

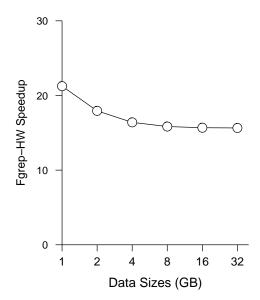

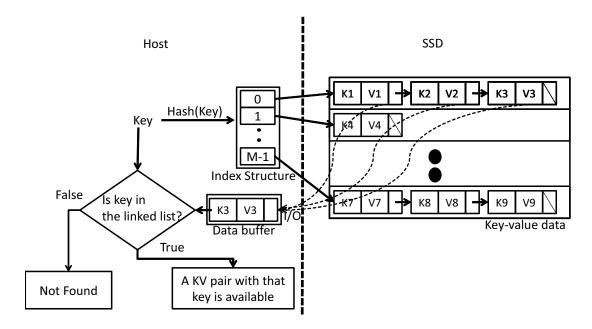

Figure 3.6 shows the typical execution flow of a data-intensive application using the XSSD architecture. If needed, the host CPU loads file data onto the XSSD. Files are striped across multiple NVM controllers for parallelism. Next, the host CPU allocates a compute channel per thread and distributes computations across multiple SPUs through RPC calls. The SPU receives a RPC request, executes it and sends back a response. The host receives RPC responses, extracts and merges results from different SPUs and produces the final output. Finally, the host CPU deallocates compute channels.

# 3.6 Example

As an example, the Fgrep-8 benchmark scans through a data file, searches for a specified 8-byte character pattern and counts the number of occurrences. We implement two versions of this benchmark. The first, Fgrep-IO uses the conventional I/O interface to read data from the SSD and perform computation on the host. Figure 3.7 presents a code snippet illustrating a parallel fgrep-IO function

## Table 3.1: RPC APIs

#### Create RPC request and response

BuildMsgHeader(CPUID\_t dst\_id, uint32\_t RPC\_Handler);

Create an RPC request header with the destination ID and RPC\_handler information.

AppendMsgBody(Port\_t src, uint32\_t size, Address\_t src\_addr); Append a message data from the given source (NV\_MEMORY\_PORT or LOCAL\_MEMORY\_PORT) and address.

CreateResponse(Msg\_t\* header, MsgResp\_t\* response, RPC\_Status

status);

Extract the source and destination information from the request header and then create RPC ack/nack response message.

#### DMA operation

DMATransfer(uint32\_t size, Port\_t src, Address\_t src\_addr, Port\_t

dst, Address\_t dst\_addr);

Supports various combinations of DMA operations: 1. NVM controller and network, 2. NVM controller and local memory, and 3. local memory and network

#### Send and receive of RPC messages

AppendMsgBodyAndFlush(Port\_t src, uint32\_t size, Address\_t

src\_addr);

Append a message data and then send the RPC request.

SendResponse(response);

Send an RPC ack/nack response.

ReceiveBytes(void\* buf, unsigned int size);

Receive "size" bytes from the network buffer to local memory buffer.

Figure 3.6: The execution flow on XSSD based system is initiated by the host, runs asynchronously on the SPU, and is terminated by the host.

Figure 3.7: Fgrep-IO code scans through a data file and counts the number of occurrences of a given 8-byte character pattern.

using pthreads. The data file is split across multiple threads and each thread reads the file at its assigned offset. The thread reads "size" bytes of data from the SSD into a local buffer. Then it searches for a specified character pattern and increments  $match\_count$  when a match found. Finally, the main program combines all the  $match\_counts$  to get the total number of matches.

The second, Fgrep-RPC implements an RPC function FGREP-8() to count the number of matches of a specified 8-byte character pattern using the SPU and sends back the number of matches instead of fetching the data file from the storage. The host application initiates computation using an RPC call to the SPU with input arguments of the RPC function such as file extents and key. Our run-time library function extracts information on the data file extents from the file system. Upon receiving RPC, the SPU calls the RPC function FGREP-8() as shown in Figure 3.8 that retrieves command comprises of file extents and key. Then it reads file data based on the extents information using DMA, and counts the number of matches. Finally, it sends back the number of matches to the host using RPC.

```

Algorithm 3.6.2: FGREP-8(Msg_t*header)

comment: Retrieves file extents and key

GrepCmd\_t\ cmd;

RECEIVEBYTES(cmd, sizeof(GrepCmd\_t));

comment: Sends ack/nack response

MsgResp\_t \ response;

CREATERESPONSE(header, &response, RPC_SUCCESS);

SENDRESPONSE(response);

comment: Compute number of matches

int64\_t \ spu\_match\_count = 0;

for i \leftarrow 0 to cmd.extents\_length

comment: Use DMA to read data from NVM controller

DMATRANSFER(buf_size,

NV_MEMORY_PORT,

cmd.extents\_addr + i,

LOCAL_MEMORY_PORT,

buf);

do

comment: Search for key and increment

for j \leftarrow 0 to buf\_size

i \leftarrow i + buf\_size;

comment: Sends number of matches to the host

CPUID\_t \ dst = cmd.src;

BuildMsgHeader(dst, GREP_COMPLETE_HANDLER);

APPENDMsgBodyAndFlush(LOCAL_MEMORY_PORT,

8, \&spu\_match\_count);

return;

```

**Figure 3.8**: **Fgrep-8 code** RPC-based implementation on SPU to count the number of occurrences of a given 8-byte key.

## 3.7 Prototype

We implemented XSSD on the BEE3 FPGA prototyping system jointly developed by Microsoft Research, UC Berkeley, and BEEcube Inc.. The BEE3 system holds 64 GB of 667 MHz DDR2 DRAM under the control of four Xilinx Virtex-5 LX155T FPGAs, and it provides a PCIe-1.1 x8 (2 GB/s full duplex) link to the host system. We used the high speed DDR2 ring network to connect multiple FPGAs with roundtrip latency of 88 ns and bandwidth of 3.7 GB/s. The system clock runs at 250 MHz. We implemented the hardware components such as request scheduler, SPUs and NVM controllers on the FPGAs. Since PCM is the most promising among different NVM technologies and receives great attention in research community as a viable future replacement of existing charge based memory technologies, we use PCM for our evaluation. We emulate PCM using the DRAM of the BEE3 system with access latency (read: 48 ns and write: 150 ns) as described in [LIMB09]. We modify the memory controller to add latency between the read address strobe and column address strobe commands during reads and extend the pre-charge latency after a write by inserting delay. We cannot stop DRAM refresh to preserve data which is not required for these NVM technologies. The memory controller delivers data at 3.7 GB/s. The MIPS in SPU runs at only 125 MHz, and has 32 KB instruction memory and 32 KB data memory. To overcome the slow processing of MIPS and effectively utilizing FPGA resources, we implement various application-specific hardware accelerators to improve performance.

## 3.8 Power Model

We implement power model of XSSD to evaluate energy consumption of XSSD based system. Table 3.2 briefly summarizes the power model of XSSD based system. The SPU power evaluation uses Synopsys CAD tools and 45 nm TSMC standard cell. The host Intel Xeon E5-2690, DDR3 DIMM and the remaining components power come from datasheets and published papers [Int08, LAS+09, CDC+10, LIMB09, MAC+11, Int]. We measure the utilization factor of each components in XSSD using hardware counters and the host

**Table 3.2: XSSD power model** that includes the host from [Int], DIMM power from [MAC<sup>+</sup>11], PCM from [LIMB09], the SPU components from Synopsys CAD tools, and other components come from datasheets [Int08] and papers [LAS<sup>+</sup>09, CDC<sup>+</sup>10]

| Component                     | Idle              | Active                  |

|-------------------------------|-------------------|-------------------------|

| Host Intel Xeon E5-2690 [Int] | 60 W              | 135 W                   |

| 4 GB DDR3 DIMM [MAC+11]       | 1 W               | 5 W                     |

| PCIe [Int08]                  | 0.12 W            | 0.4 W                   |

| Scheduler [Int08]             | 0.3 W             | 1.3 W                   |

| Network [LAS <sup>+</sup> 09] | 0.03 W            | 0.06 W                  |

| MIPS                          | 0.078 W           | 0.37 W                  |

| DMA Controller                | 0.01 W            | 0.09 W                  |

| Grep Hardware Accelerator     | 0.013 W           | 0.12 W                  |

| Saxpy Hardware Accelerator    | 0.06 W            | 0.3 W                   |

| FFT Hardware Accelerator      | 0.029 W           | 0.274 W                 |

| PCM controller [LAS+09]       | 0.24 W            | 0.34 W                  |

| PCM write [LIMB09]            |                   | 16.82 pJ/bit            |

| PCM read [LIMB09]             |                   | 2.47  pJ/bit            |

| PCM background [LIMB09]       | $264 \ \mu W/die$ | $20 \ \mu \text{W/bit}$ |

CPU utilization using "sar" command. We model each component's power as  $P = IdlePower \times (1 - UtilizationFactor) + ActivePower \times (UtilizationFactor).$

# Acknowledgments

This chapter contains material from "Minerva: Accelerating Data Analysis in Next-Generation SSDs", by Arup De, Maya Gokhale, Rajesh K. Gupta, and Steven Swanson, which appears in FCCM'13: Proceedings of the 21st IEEE International Symposium on Field-Programmable Custom Computing Machine. The dissertation author was the first investigator and author of this paper. The material in this chapter is copyright ©2013 by the Institute of Electrical and Electronics Engineers (IEEE). Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for compo-

nents of this work owned by others than IEEE must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from Publications Dept., IEEE, Inc., telephone +1 (732) 562-3966, or copyrights@ieee.org.

This chapter contains material from "Willow: A User-Programmable SSD", by Sundaram Bhaskaran, Trevor Bunker, Arup De, Mark Gahagan, Yanqin Jin, Robert Liu, Sudharsan Seshadri and Steven Swanson, which has been submitted for possible publication by USENIX in *Proceedings of the 11th USENIX Symposium on Operating Systems Design and Implementation, (OSDI'14)*. The dissertation author was the third investigator and author of this paper.

# Chapter 4

# Applications

In this chapter, we present a set of applications from various application domains such as scientific computing, artificial intelligence, image processing, enterprise computing and financial computing. Table 4.1 presents brief description about different applications for evaluation. These applications are data or I/O intensive. They are either stream over large data structures (e.g., fgrep-8, saxpy and 2D-FFT) or randomly accesses different data locations (e.g., key-value store and B<sup>+</sup> tree). The stream applications have poor temporal locality and the I/O bandwidth mainly limits the performance of those applications. The random access applications have poor temporal and spatial locality. As a result, they make poor use of existing memory hierarchies and perform poorly on the conventional system. XSSD exposes huge bandwidth and low latency of NVMs to those applications and improves the performance by eliminating I/O and performing efficient data processing in the SSD. We briefly discuss about the implementation of each

**Table 4.1**: Applications

| Name                | Description                                              |

|---------------------|----------------------------------------------------------|

| Fgrep-8             | Scans a file for a given fixed pattern matching.         |

| Saxpy               | Computes floating point scalar multiplication and vector |

|                     | addition.                                                |

| 2D-FFT              | Calculates 2D-FFT.                                       |

| Key-value Store     | Key-value store operations lookup, insert and delete.    |

| B <sup>+</sup> Tree | B <sup>+</sup> Tree traversal.                           |

Table 4.2: The latency and bandwidth of access 8 KB data

| Description | Latency (us) | Bandwidth (GB/s) |

|-------------|--------------|------------------|

| Host I/O    | 11.2         | 1.67             |

| SPU DMA     | 3.4          | 2.7              |

applications on XSSD.

We implement two versions of each applications. The first, [application name]-IO uses the highly optimized storage I/O interface [CMD+12]. The second, [application name]-RPC uses the RPC interface of XSSD. We also implement the hardware version of fgrep-8 and key-value store. We compare the performance and energy efficiency of each implementation. We use the power model to find the average power of each component as discussed in Section 3.8. Then we calculate the system energy consumption for an application by multiplying the execution time of the application with the total average power.

Before we measure the performance of each application, we measure the access latency and bandwidth of 8 KB data access from the host over the PCIe and inside XSSD. Table 4.2 summarizes the latency and bandwidth of the host I/O access and SPU DMA access. XSSD has aggregate internal bandwidth of 21.6 GB/s that outperforms the host I/O bandwidth by 12.93×.

# 4.1 Fgrep-8

Fgrep-8 is a file readonly application. It scans through a data file, searches for a specified 8-byte character pattern and counts the number of occurrences. It has sequential accesses and the I/O interface bandwidth limits the overall performance of fgrep-8. We implement three versions: Fgrep-IO, Fgrep-RPC and Fgrep-HW.

# 4.1.1 Fgrep-IO

Fgrep-IO reads the data file using I/O, searches for the pattern and counts the number of matches using the host. We implement a parallel fgrep-IO function using pthreads that splits the data file across multiple threads with assigned offset and size. Each thread reads data from the SSD using I/O read interface and searches a given character pattern on the host. If matches, it increments the number of matches. Finally, the main program combines the number of matches of each thread to get the total number of matches.

## 4.1.2 Fgrep-RPC

Fgrep-RPC implements an RPC function FGREP-8() to count number of matches of a specified 8-byte character pattern using SPU. The host application initiates computation using RPC to the SPU with input arguments of the RPC function such as file extents and 8-byte character pattern. Our run-time library function extracts information on the data file extents from the file system. Upon receiving, the SPU calls the RPC function with given arguments. Then it loads file data from the NVM controller to local buffer using DMA based on the extents information, and counts the number of matches. Since the MIPS processor runs very slowly (at 125 MHz) and is unable to exploit the full NVM bandwidth (3 GB/s). We implemented a hardware accelerator for key comparison that can process data at 4 GB/s. As an optimization, we implement double buffering to simultaneously load data from the NVM controller to one local buffer and perform computation on another buffer.

# 4.1.3 Fgrep-HW

We also implement a hardware version of fgrep-8. It has an FSM that receives the key and file extents information from the host. Then it issues DMA requests to load data from the NVM controller to the local memory buffer based on file extents information. The FSM configures the source address, destination address and data size of a DMA operation, and waits for the DMA completion. When DMA completes, it sends the key and local buffer information to fgrep-8 hardware kernel as discussed in Section 3.3. The fgrep-8 hardware kernel compares the key with the local buffer data, increments match count when it matches and finally, sends back match count to the host.

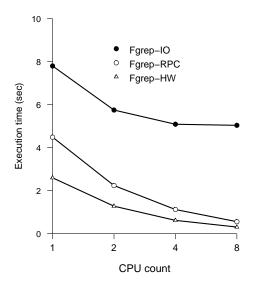

Figure 4.1: The execution time comparison with increasing CPU count for Fgrep-IO, Fgrep-RPC and Fgrep-HW (File size 8 GB).

Figure 4.2: The performance improvement of fgrep-HW as compared to fgrep-IO as we increase the size of data file from 1 GB to 32 GB.

## 4.1.4 Evaluation