## UC Berkeley UC Berkeley Electronic Theses and Dissertations

#### Title

Design and Characterization of Ferroelectric Negative Capacitance

**Permalink** https://escholarship.org/uc/item/6cz2z911

**Author** Chatterjee, Korok

Publication Date 2018

Peer reviewed|Thesis/dissertation

#### Design and Characterization of Ferroelectric Negative Capacitance

by

Korok Chatterjee

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Sayeef Salahuddin, Chair Professor Chenming Hu Professor Ramamoorthy Ramesh

Summer 2018

## Design and Characterization of Ferroelectric Negative Capacitance

Copyright 2018 by Korok Chatterjee

#### Abstract

#### Design and Characterization of Ferroelectric Negative Capacitance

by

Korok Chatterjee

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Sayeef Salahuddin, Chair

Because of the thermal distribution of electrons in a semiconductor, modern transistors cannot be turned on more sharply than 60 mV of gate voltage for an order of magnitude increase in drain current, the so-called "Boltzmann tyranny." This results in an inability to reduce supply voltage, increasing power dissipation in advanced complementary metaloxide-semiconductor (CMOS) technologies, which threatens the continuation of exponential transistor scaling, also known as Moore's Law. For this reason, there has been a push in the device research community to invent novel steep swing devices. Negative capacitance in ferroelectric materials was proposed in 2008 by Salahuddin and Datta to provide voltage amplification without needing to design a totally new device. A negative gate capacitance would step-up the applied gate voltage at the semiconductor channel, causing the surface potential to rise faster than the gate voltage, lowering the subthreshold slope below 60 mV/decade. In this work, we attempt to characterize the charge-voltage characteristics of ferroelectrics biased into the negative capacitance regime. Although negative capacitance was experimentally demonstrated in 2010, significant challenges have remained to the practical realization of negative capacitance field-effect transistors (FETs).

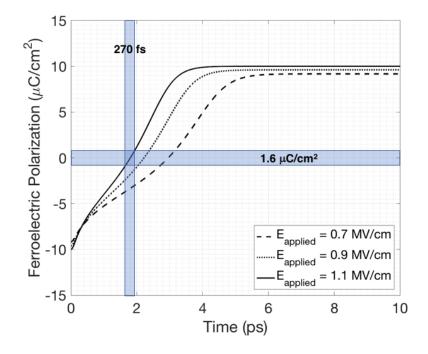

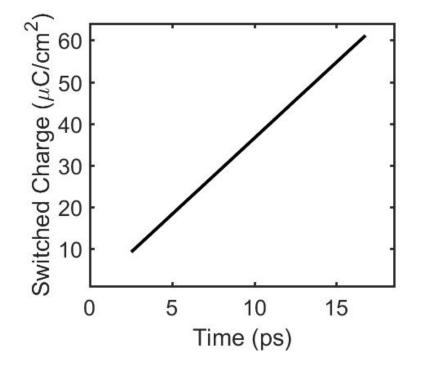

First, we investigate negative capacitance in an isolated ferroelectric capacitor, and show that the negative capacitance states can be directly observed during switching. Careful analysis of the switching dynamics and phase-field modeling show that the signature of negative capacitance arises from the accelerating growth of domain walls, when an increasing volume fraction of the ferroelectric is depolarized. Although this offers insight into the origins of negative capacitance and help to establish its existence scientifically, it does not address the problem of design. A primary concern is the speed of polarization response, which should be on the order of 1 picosecond or less in order to maintain circuit performance. By analyzing the electromagnetic absorption spectrum of hafnium oxide, the primary candidate for CMOS integration, we are able to estimate the intrinsic delay time as being on the order of 270 fs. Next, in order to maximize the amplification and provide adequate margins for hysteresis-free operation, it is necessary to understand how coupling of the ferroelectric material to the interfacial oxide and semiconductor affects its behavior, and to be able to predict what values of negative capacitance will be realized for a certain material and geometry. This is the problem of capacitance matching, which we aim to solve by using the underlying transistor itself as a charge sensor. By calibrating the drain current to the surface potential in reference devices, we may ascertain the characteristics of the ferroelectric in the negative capacitance devices. This is first carried out with an epitaxial ferroelectric capacitor externally connected to the gate of pre-fabricated Fin-FETs. Following this, we describe the development of an in-house fabrication process using silicon-on-insulator substrates, which allows for simple and efficient process flows. Then, we describe the characterization of these devices, including quasistatic and low-frequency current-voltage (I-V) and capacitance voltage (C-V) measurements, a fast pulse-gated I-V measurement, and an excursion into the memory characteristics of our fabricated FETs. Finally, we discuss efforts to build a computational model of our devices from which we can extract the ferroelectric characteristics needed for predictive design. "With four parameters I can fit an elephant, and with five I can make him wiggle his trunk." –John von Neumann

# Contents

| Co | Contents                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                |

|----|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Li | st of                                                               | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | iv                                                                                                                                             |

| Li | st of                                                               | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | xi                                                                                                                                             |

| 1  | <b>Intr</b><br>1.1<br>1.2                                           | oduction<br>Motivation: Power Dissipation in CMOS Electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>1</b><br>1<br>4                                                                                                                             |

|    | 1.3                                                                 | Summary of Previous Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7                                                                                                                                              |

| 2  | Dire<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9 | ect Observation of Negative Capacitance         Introduction       Dynamics of Ferroelectric Switching for a Single Domain         Fabrication and Material Characterization       Fabrication and Material Characterization         Experimental Setup       Negative Capacitance Transients         Identification of the Negative Capacitance Transient with Ferroelectric Switching         Variation of the External Resistor         Negative Capacitance Transients in Ferroelectric Hafnium Oxide         Conclusions | <ul> <li>11</li> <li>11</li> <li>14</li> <li>15</li> <li>15</li> <li>17</li> <li>20</li> <li>20</li> <li>22</li> <li>22</li> <li>22</li> </ul> |

| 3  | Dyn<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                | namics of Negative Capacitance in Isolated FerroelectricsIntroductionSingle-Domain Theory: The Landau-Khalatnikov (L-K) PictureResults of L-K SimulationsKolmogorov-Avrami-Ishibashi (KAI) TheoryFitting of Experimental Data to KAI TheoryPhase-Field ModelingConclusions                                                                                                                                                                                                                                                    | <ul> <li>26</li> <li>27</li> <li>28</li> <li>31</li> <li>35</li> <li>38</li> <li>41</li> </ul>                                                 |

| 4  | Intr                                                                | insic Speed Limitations of Negative Capacitance Transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44                                                                                                                                             |

|          | $4.1 \\ 4.2 \\ 4.3$ | Introduction                                                        | 44<br>45<br>47 |

|----------|---------------------|---------------------------------------------------------------------|----------------|

|          | 4.4                 | Conclusions                                                         | 50             |

| <b>5</b> | $\mathbf{Ext}$      | ernal Connection of a Ferroelectric Capacitor to Short-Channel Fin- |                |

|          | <b>FE</b>           | ſs                                                                  | 51             |

|          | 5.1                 | Introduction                                                        | 51             |

|          | 5.2                 | Experimental Setup                                                  | 52             |

|          | 5.3                 | Experimental Results                                                | 53             |

|          | 5.4                 | Conclusions                                                         | 57             |

| 6        | Fab                 | rication of Negative Capacitance FETs                               | 60             |

|          | 6.1                 | Introduction                                                        | 60             |

|          | 6.2                 | Ferroelectricity in Hafnium Oxide                                   | 61             |

|          | 6.3                 | Replacement Gate Process for Silicon-on-Insulator FETs              | 64             |

|          | 6.4                 | Gate-First Process for Silicon-on-Insulator FETs                    | 67             |

| 7        | Cha                 | racterization of Negative Capacitance FETs                          | 70             |

|          | 7.1                 | Introduction                                                        | 70             |

|          | 7.2                 | Quasistatic Measurements                                            | 71             |

|          | 7.3                 | Low-Frequency Transconductance Measurement                          | 78             |

|          | 7.4                 | Pulse-gated IV Measurement                                          | 79             |

|          | 7.5                 | Ferroelectric FET Memory Characterization                           | 81             |

|          | 7.6                 | Conclusions and Future Work                                         | 85             |

| 8        | Sim                 | ulation of Negative Capacitance FETs                                | 90             |

|          | 8.1                 | Introduction                                                        | 90             |

|          | 8.2                 | Theoretical Framework                                               | 91             |

|          | 8.3                 | Results for Gate-First HZO NCFETs                                   | 92             |

|          | 8.4                 | Conclusions and Future Work                                         | 97             |

| 9        | Cor                 | clusions and Future Work                                            | 99             |

| -        | 9.1                 | Conclusions                                                         | 99             |

|          | 9.2                 | Future Work   Future 1                                              | 101            |

| Bi       | bliog               | graphy                                                              | 103            |

# List of Figures

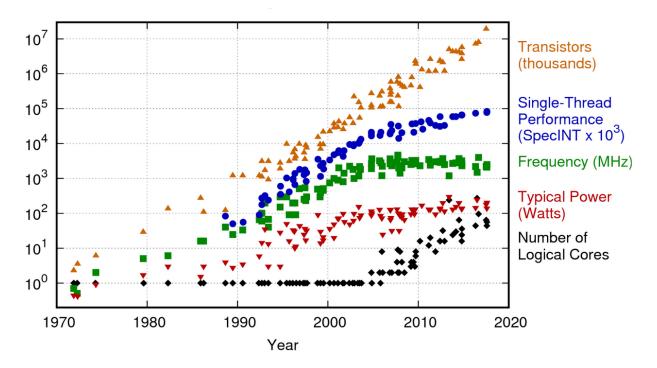

| 1.1 | Industry trends for microprocessors over the last 42 years. Taken from $[6]$                                                                                                                                                                                                                                                                                                                                    | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

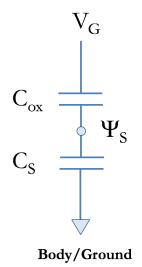

| 1.2 | Simplified depiction of a MOSFET as a capacitive divider                                                                                                                                                                                                                                                                                                                                                        | 5  |

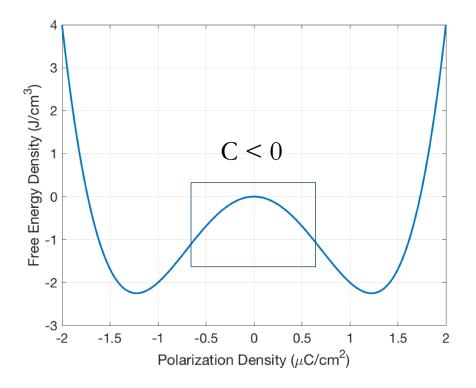

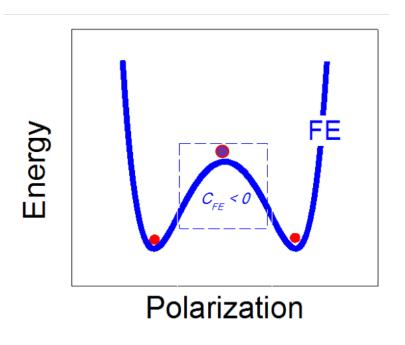

| 1.3 | Energy landscape of a hypothetical ferroelectric material. The region of negative capacitance states between the spontaneous polarization states is indicated                                                                                                                                                                                                                                                   | 6  |

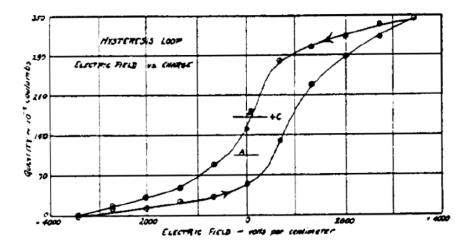

| 1.4 | The first reported ferroelectric hysteresis loop, by Joseph Valasek on Rochelle salt. From [17]                                                                                                                                                                                                                                                                                                                 | 8  |

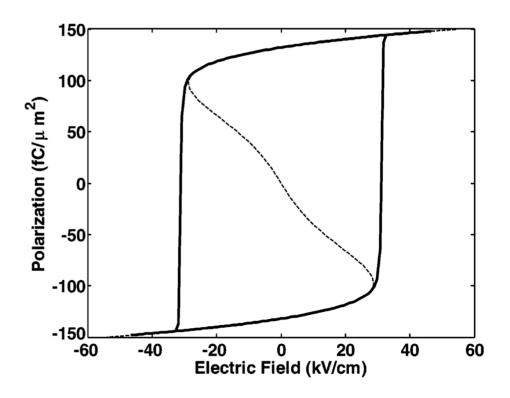

| 1.5 | Hysteresis loop of a $BaTiO_3$ sample, with the proposed negative capacitance states shown with a dashed curve                                                                                                                                                                                                                                                                                                  | 9  |

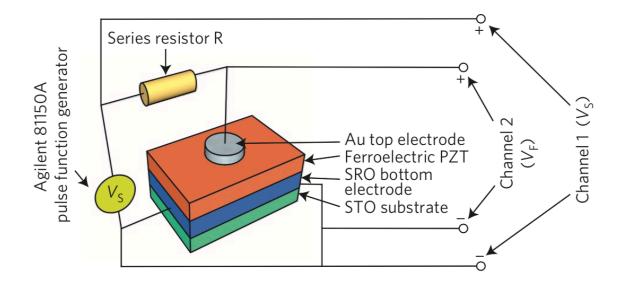

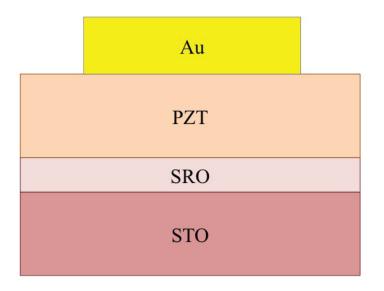

| 2.1 | Schematic diagram of the experimental setup. The resistor consists of a $0-100k\Omega$ potentiometer, and the ferroelectric Pb(Zr <sub>0.2</sub> Ti <sub>0.8</sub> )O <sub>3</sub> (PZT) capacitor is deposited and patterned on a substrate of SrTiO <sub>3</sub> (STO). Not pictured is a parasitic cable capacitance that appears in parallel with the ferroelectric capacitor. From [26].                   | 12 |

| 2.2 | Qualitative depiction of energy landscape as a function of ferroelectric polar-<br>ization with no applied voltage. The circles indicate critical points of the free<br>energy functional, and the dotted box shows the region in which the ferroelectric<br>capacitance is negative.                                                                                                                           | 13 |

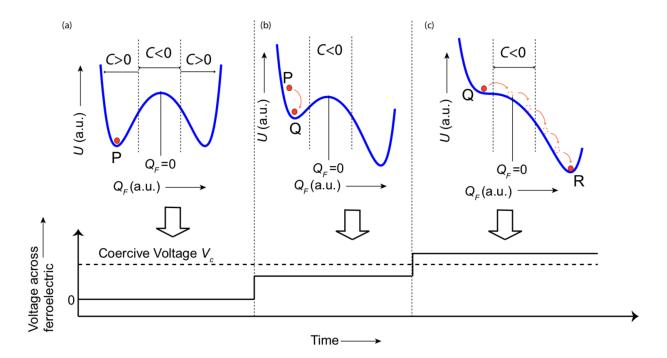

| 2.3 | Tilting of the energy landscape under an applied voltage. (a) The ferroelectric<br>under zero voltage. (b) The energy landscape tilts under the application of a<br>field below the coercive voltage, though a barrier remains. Thermal switching<br>may occur at long enough timescales. (c) Only the right-most minimum at R<br>remains, and the material spontaneously traverses the energy landscape, which | 10 |

| 9.4 | is the polarization switching                                                                                                                                                                                                                                                                                                                                                                                   | 14 |

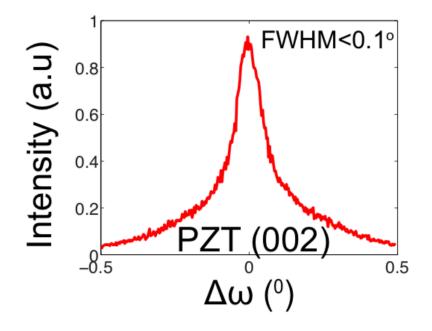

| 2.4 | X-ray diffraction rocking curve measurement for the 60 nm PZT film primarily<br>used for this work. The x-axis shows angular displacement from the center of the                                                                                                                                                                                                                                                |    |

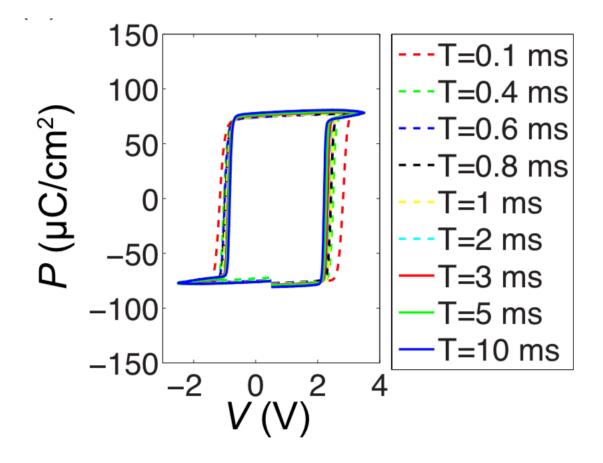

| 2.5 | (002) peak for PZT. From [26]                                                                                                                                                                                                                                                                                                                                                                                   | 16 |

|     | From [26]                                                                                                                                                                                                                                                                                                                                                                                                       | 17 |

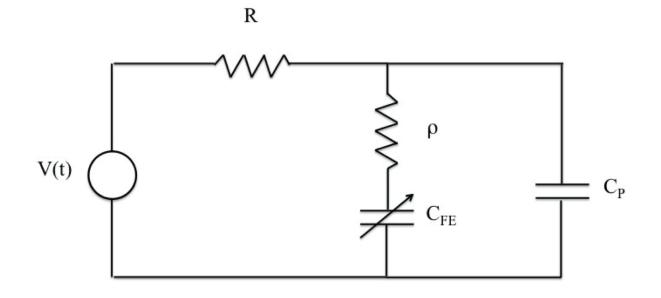

| 2.6  | Equivalent circuit of the experimental setup, showing the parasitic cable capac-<br>itance appearing in series with the ferroelectric capacitor. Here $\rho$ represents<br>dissipation internal to the ferroelectric.                                                                                                                                                                                                                                                                                                                                                                            | 18       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

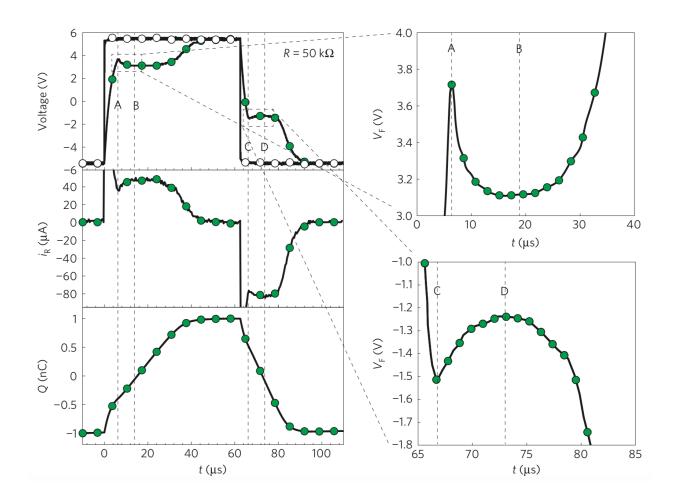

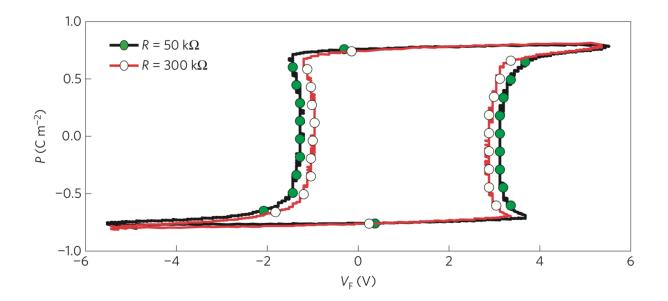

| 2.7  | Switching dynamics of a 60 nm PZT capacitor. The source voltage is marked<br>with white dots, and the ferroelectric transients are marked in green. The cur-<br>rent is calculated from Ohm's law by measuring the voltage across the resistor,<br>from which the parasitic displacement current $C_P \frac{\partial V_F}{\partial t}$ is subtracted to yield the<br>ferroelectric current. This is integrated in the bottom figure to show the change in<br>charge. The portions of the voltage transients which exhibit negative capacitance<br>are shown in close-up on the right. From [26]. | 10       |

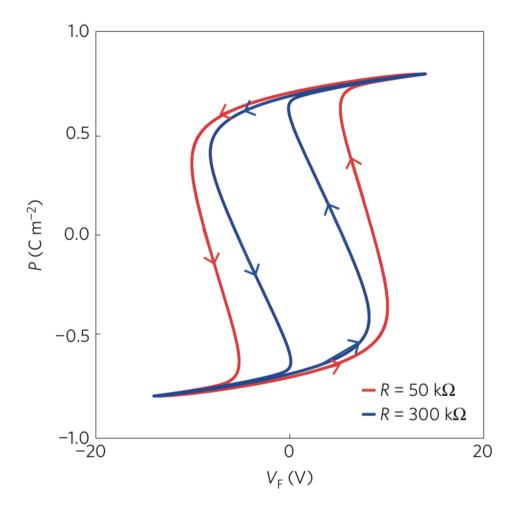

| 2.8  | Dynamic hysteresis loops for the same 60 nm PZT sample in 2.7 for two different values of series resistance. Widening of the loop occurs for lower values of $R$ , analogous to the widening of the quasistatic hysteresis loops with faster ramp rate. This widening is predicted by a simple single-domain model. The negative capacitance is apparent in the top left and bottom right corners of the dynamic                                                                                                                                                                                 | 19       |

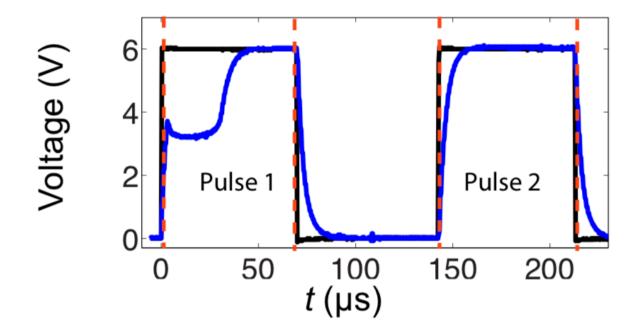

| 2.9  | hysteresis loops. From [26]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20       |

|      | capacitance signature only occurs in the first transient, showing that it correlates<br>with ferroelectric polarization switching. From [26]                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21       |

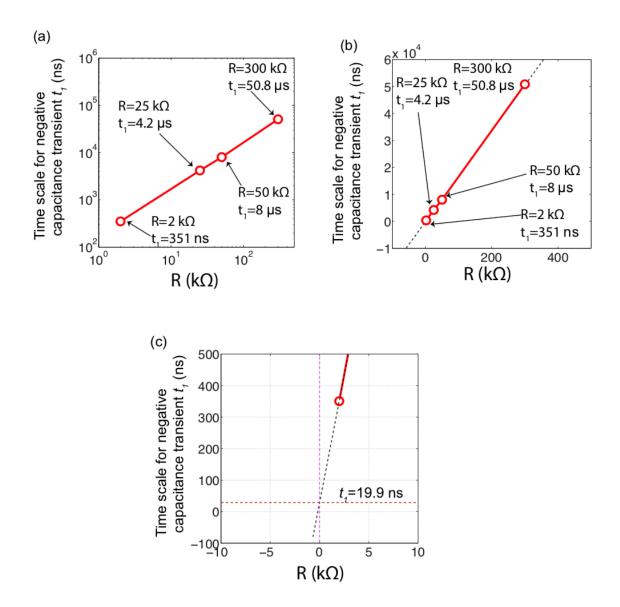

| 2.10 | (a). Duration for which the ferroelectric capacitance is negative $(t_1)$ for a switch-<br>ing voltage of +6 V, for varying values of resistance, plotted on a logarithmic<br>scale. (b). The same data on a linear scale. (c). Extrapolation of the least<br>squares linear fit to $R = 0$ . The expected minimum value of $t_1$ at this switching<br>voltage is 19.9 ns. $\rho$ is estimated to be 375 $\Omega$ m which, as will be seen in 4, is a                                                                                                                                            |          |

| 2.11 | gross overestimate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23       |

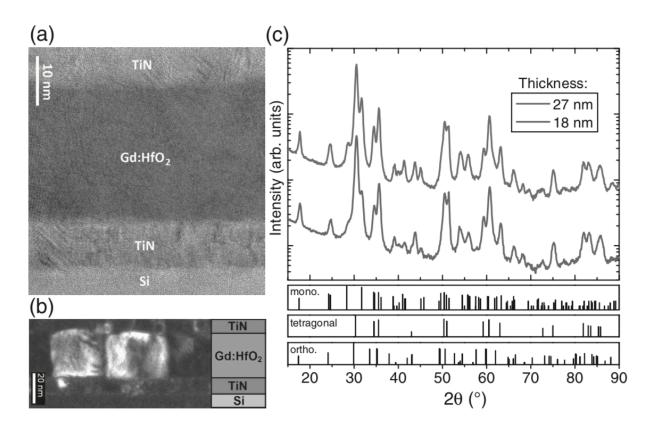

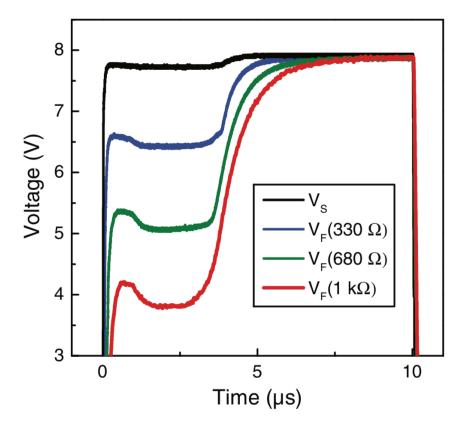

| 2.12 | for the expected crystalline phases present in the material. From [33] Switching transients for an 18 nm $Gd:HfO_2$ capacitor with different values of external series resistance. The negative capacitance signature is present in all of the transients, but its onset is at a reduced voltage for higher resistances. This is consistent with the predictions of the Landau-Khalatnikov equation. From [33].                                                                                                                                                                                  | 24<br>25 |

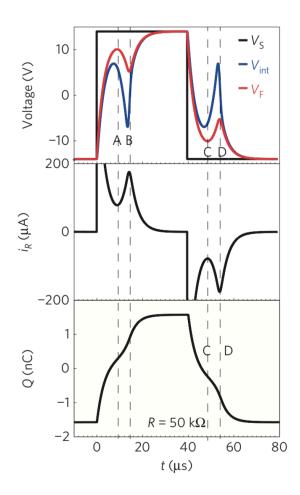

| 3.1  | Switching transients for a ferroelectric capacitor with applied voltages of $+/-14$ V. The top figure shows the internal voltage and the ferroelectric voltage alongside the source voltage. The middle figure shows the current flowing through the resistor. The bottom figure shows the charge on the ferroelectric capacitor. The                                                                                                                                                                                                                                                            |          |

|      | value of the external resistor is 50 k $\Omega$ . From [26]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29       |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

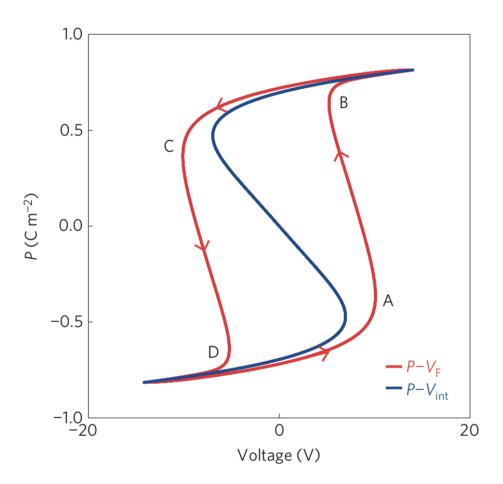

| 3.2  | Dynamic hysteresis loops for the single-domain Landau-Khalatnikov ferroelectric.<br>The loops are constructed from plotting the voltage transients with the simul-<br>taneous capacitor charge calculated from integrating the current. These are the<br>same data in 3.1. From [26]                                                               | 30       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.3  | Dynamic hysteresis loops for two different values of series resistance, 50 k $\Omega$ and 300 k $\Omega$ . For a higher series resistance, the ferroelectric voltage more closely                                                                                                                                                                  |          |

| 3.4  | follows the internal voltage. From [26]                                                                                                                                                                                                                                                                                                            | 32<br>33 |

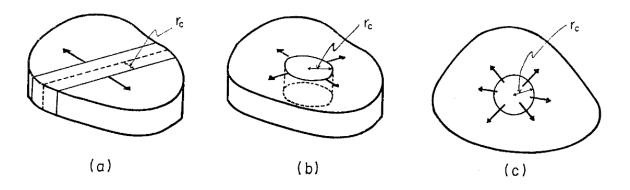

| 3.5  | The point $P$ is contained in the nucleation volume of size $S$ centered on $A$ , but not of the one centered on $B$ . $A$ is correspondingly inside the nucleation volume of size $S$ centered on $P$ , while $B$ is not. The inner circles of the nucleation volumes                                                                             |          |

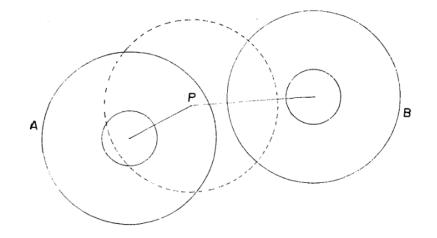

| 3.6  | indicate the size of the critical radius with which domains nucleate. From [34]<br>Schematic of the ferroelectric PZT capacitors used in this experiment. 10 nm of SRO is deposited on an STO substrate, followed by 60 nm of PZT, and finally a                                                                                                   | 34       |

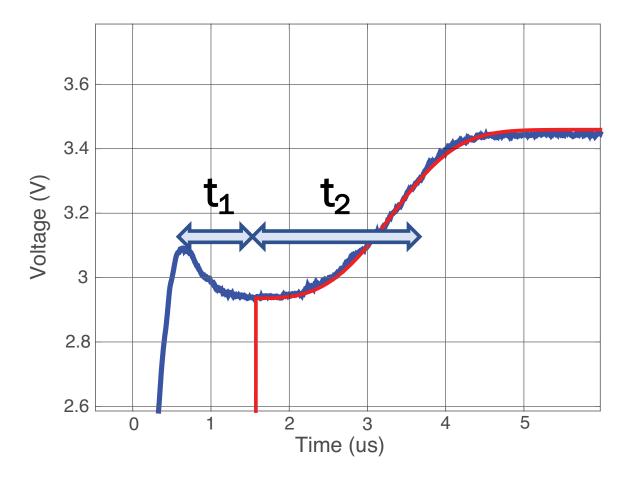

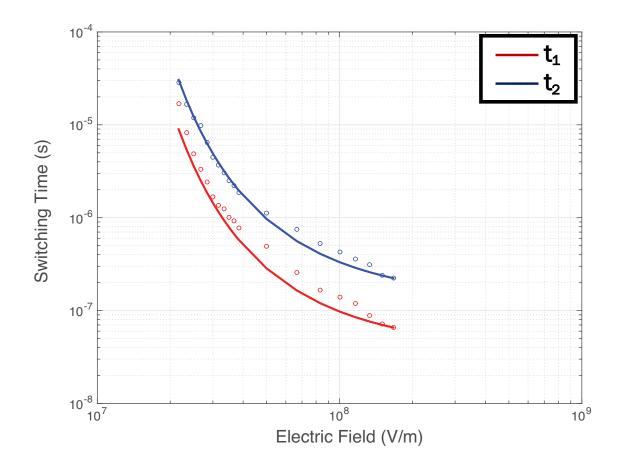

| 3.7  | stack of 5 nm Au / 40 nm Ti / 5 nm Au, which is patterned into a top contact.<br>The blue curve shows a typical $V_F$ for a switching ferroelectric. The source voltage $V_S$ is +3.45 V, and the external resistance $R = 1053\Omega$ . The red curve shows the ferroelectric voltage expected from this measurement according to best fit of the | 36       |

| 3.8  | KAI model                                                                                                                                                                                                                                                                                                                                          | 37       |

| 3.9  | is obtained                                                                                                                                                                                                                                                                                                                                        | 38       |

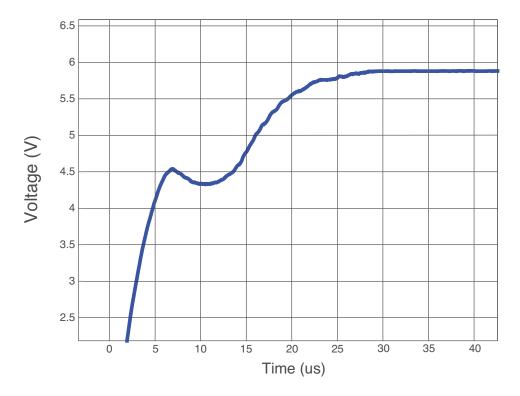

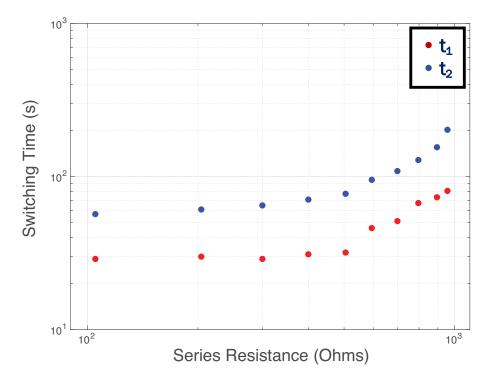

| 3.10 | resistance $R = 9600\Omega$                                                                                                                                                                                                                                                                                                                        | 39       |

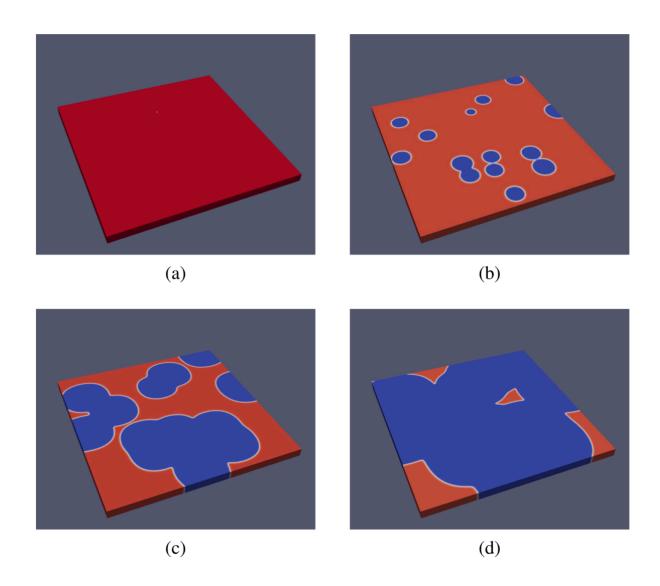

| 3.11 | slew-limited region is reached                                                                                                                                                                                                                                                                                                                     | 40       |

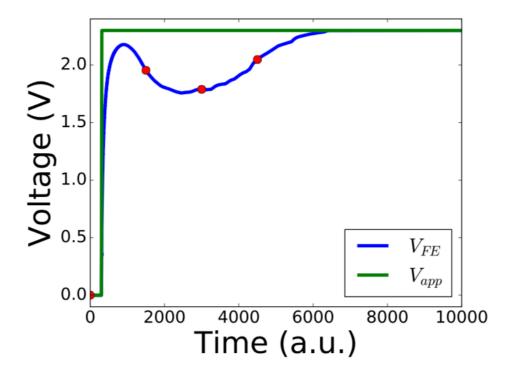

| 3.12 | 3.12 (a)-(d), from left to right. From [40]                                                                                                                                                                                                                                                                                                        | 41       |

|      | ferroelectric voltage approaches that of the source. From [40]                                                                                                                                                                                                                                                                                     | 42       |

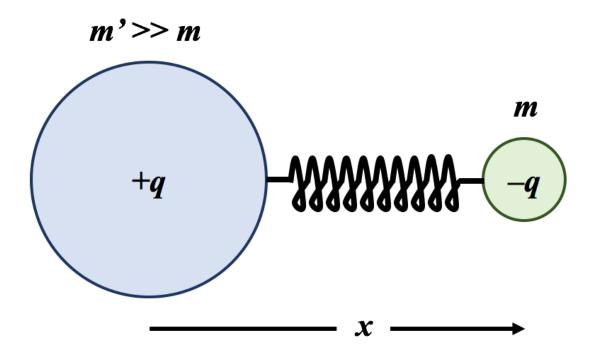

| 4.1 | Charge-mass spring system used to model polarization. The situation shown where the smallest mass $m$ is negatively charged is consistent with HfO <sub>2</sub>                                                                                                                                                                                                           | 46       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

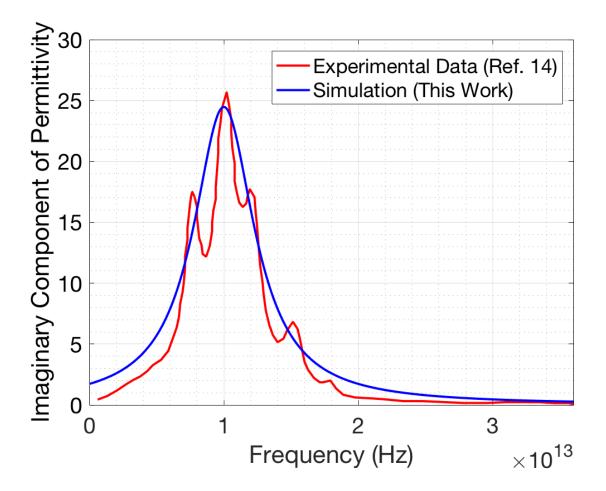

| 4.2 | Experimental vs. simulated electromagnetic absorption spectra for $HfO_2$ . Experimental data were obtained with FTIR. The right axis shows absorbed power equivalent to the imaginary component of the permittivity on the left axis. Adapted                                                                                                                            |          |

| 4.3 | from [45]                                                                                                                                                                                                                                                                                                                                                                 | 48       |

| 4.4 | delay is found to be around 270 fs. $\dots \dots \dots$                                                                                                                                                                                                                   | 49<br>50 |

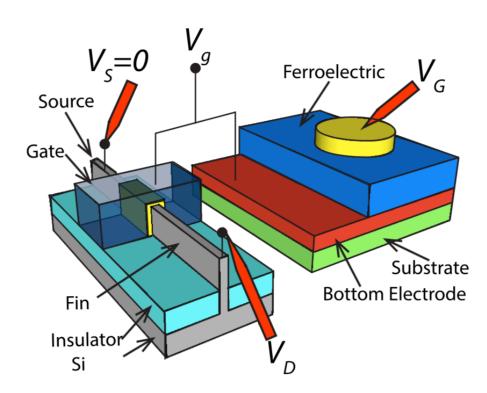

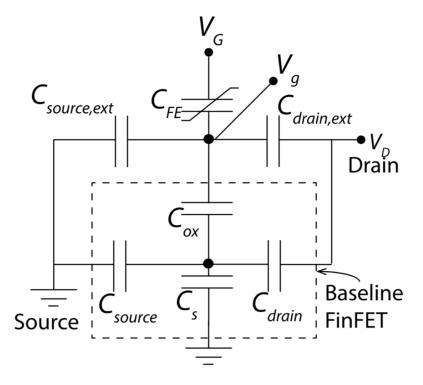

| 5.1 | Schematic of the devices. On the left is a FinFET with the source and drain indicated. The source and body are both tied to ground. The gate terminal is connected to one terminal of the ferroelectric capacitor; this node is labeled $V_g$ and referred to as the "internal gate." The other terminal of the capacitor, called the "external gate," is labeled $V_G$ . | 52       |

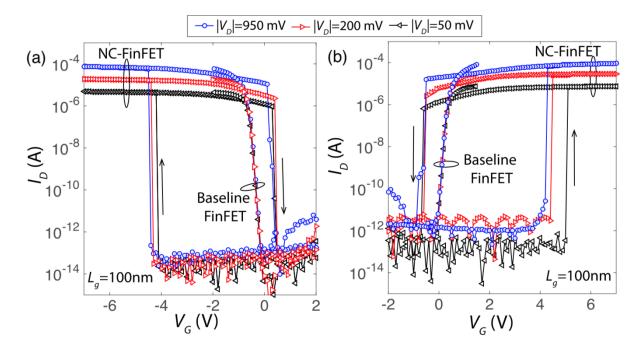

| 5.2 | Transfer characteristics of the baseline FinFETs and the NC-FinFETs, showing pMOS devices in (a) and nMOS devices in (b). Characteristics are shown for three different values of drain voltage, $ V_D  = 50mV$ , $200mV$ , and $950mV$ . The directions of the voltage sweeps for the NC-FinFETs are indicated with black                                                |          |

| 5.3 | arrows                                                                                                                                                                                                                                                                                                                                                                    | 54       |

| 5.4 | $C_{FE}$ follows Landau-Devonshire theory                                                                                                                                                                                                                                                                                                                                 | 56<br>57 |

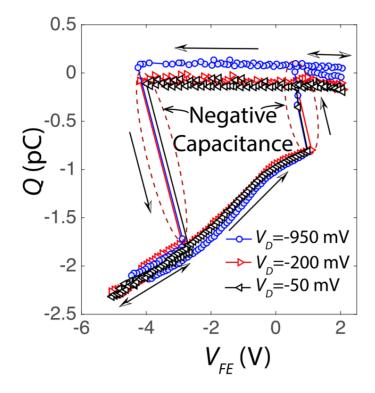

| 5.5 | Extracted Q- $V_{FE}$ characteristics for different values of drain voltage in the p-type NC-FinFET. Negative capacitance is apparent in both branches of the hysteresis                                                                                                                                                                                                  |          |

| 5.6 | loop                                                                                                                                                                                                                                                                                                                                                                      | 58<br>59 |

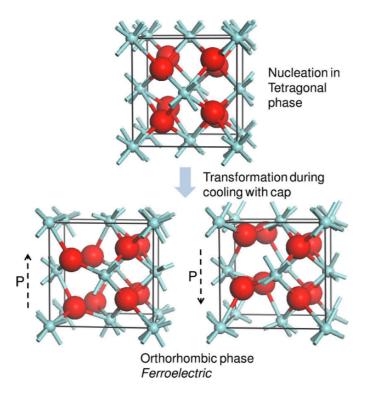

| 6.1 | Schematic showing the positions of atoms in the unit cell of $HfO_2$ . The orthorhom-<br>bic phase is the result of a symmetry-breaking distortion of the tetragonal phase. |     |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Rotation of lattice atoms modulates the net electric dipole moment. The large                                                                                               |     |

|     | red atoms are oxygen; the small blue atoms are hafnium. Figure adapted from [30]                                                                                            | 62  |

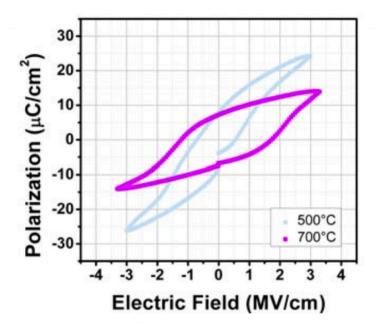

| 6.2 | Polarization-electric field (P-E) hysteresis loops for a 10 nm film of $Hf_{0.5}Zr_{0.5}O_2$                                                                                |     |

|     | capped with TiN. Figure adapted from [46].                                                                                                                                  | 63  |

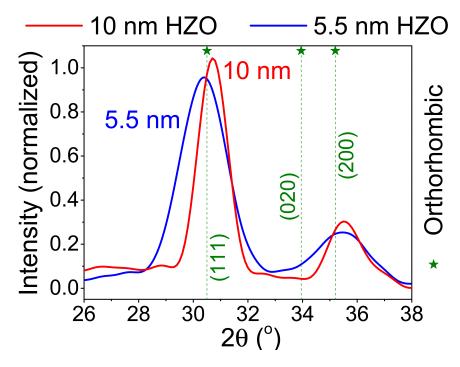

| 6.3 | GI-XRD measurements for $Hf_{0.8}Zr_{0.2}O_2$ films of two different thicknesses. The                                                                                       |     |

|     | stars indicate theoretically predicted peak positions. A slight dependence on film                                                                                          |     |

|     | thickness is noted. Taken from [62]                                                                                                                                         | 64  |

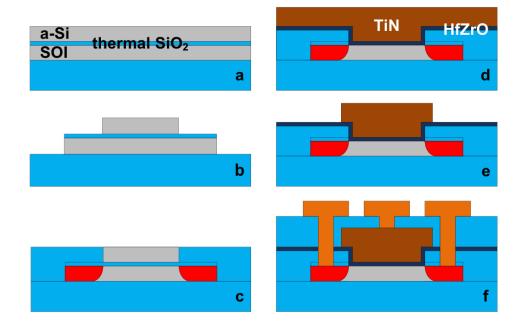

| 6.4 | Summary of the replacement gate transistor process flow. (a) Sacrificial gate                                                                                               |     |

|     | layers are grown/deposited on the SOI wafer. (b) The active area is defined and                                                                                             |     |

|     | the wafer is etched down to the BOX, followed by gate definition and etching of                                                                                             |     |

|     | the sacrificial polycrystalline silicon (poly-Si) layer. (c) After As ion implantation                                                                                      |     |

|     | into the source/drain regions, silicon dioxide is deposited at low temperature. The                                                                                         |     |

|     | wafer is polished to expose the sacrificial poly-Si. (d) The sacrificial gate layers,                                                                                       |     |

|     | a-Si and $SiO_2$ , are removed, and the real gate stack consisting of HZO and TiN                                                                                           |     |

|     | is deposited. (e) The real gate is patterned and etched back. (f) Inter-layer                                                                                               |     |

|     | dielectric is deposited, and contact holes are etched. After metal sputtering the                                                                                           |     |

|     | contacts themselves are formed. Figure taken from [62]                                                                                                                      | 66  |

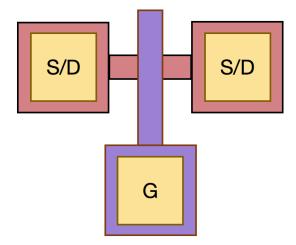

| 6.5 | Overhead view of the basic device structure. The source/drain contacts are                                                                                                  |     |

|     | marked "S/D" and the gate contact is marked with a "G." $\ldots$ .                                                                                                          | 67  |

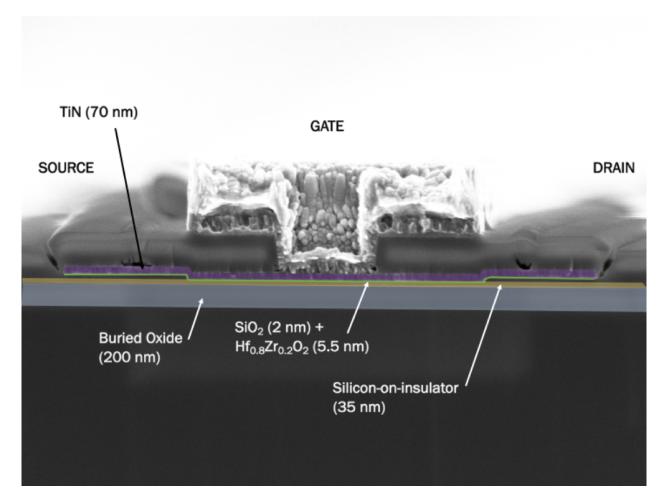

| 6.6 | SEM micrograph of the completed FET, with various material regions indicated                                                                                                |     |

|     | by color                                                                                                                                                                    | 68  |

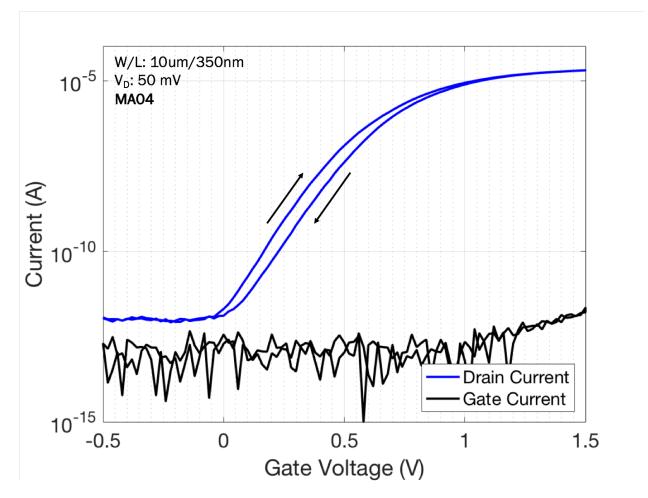

| 7.1 | Transfer characteristics of a ferroelectric-gated FET without a post-metallization                                                                                          |     |

| 1.1 | anneal. The threshold voltage shift in the reverse sweep compared to the forward                                                                                            |     |

|     | sweep is due to channel-side charge injection. Gate current is shown to be sig-                                                                                             |     |

|     | nificantly below drain current, even in the off-state, indicating potential leakage                                                                                         |     |

|     | through the buried oxide (BOX).                                                                                                                                             | 72  |

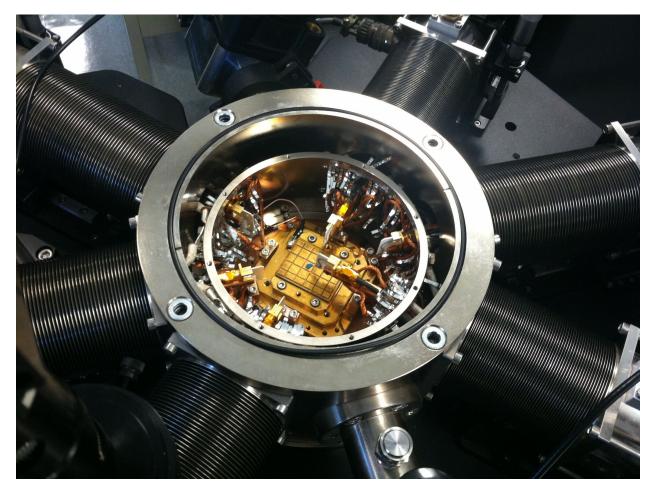

| 7.2 | Photograph of the sample chamber in the LakeShore TTPX probe station                                                                                                        | 73  |

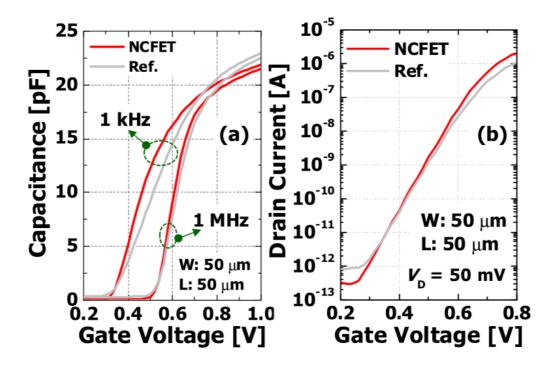

| 7.2 | (a) Capacitance versus gate voltage for large-area transistors (W/L: 50 $\mu$ m/50                                                                                          | 10  |

| 1.0 | $\mu$ m). Data are taken at both 1 kHz and 1 MHz. (b) I <sub>D</sub> -V <sub>G</sub> data for the same                                                                      |     |

|     | devices. Reduced subthreshold slope over many orders of magnitude of drain                                                                                                  |     |

|     | current as well as higher on-current is observed. Figure adapted from [71]                                                                                                  | 74  |

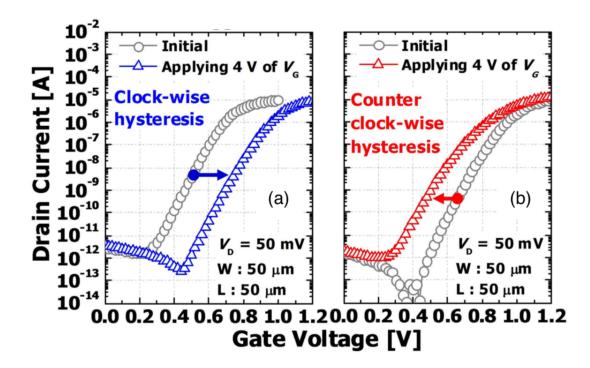

| 7.4 | (a) Transfer characteristics for a reference FET when the gate voltage is swept                                                                                             | • • |

| 1.1 | over a large range, showing charge-trapping induced hysteresis. (b) Transfer                                                                                                |     |

|     | characteristics for an NCFET when the gate voltage is swept over a large range.                                                                                             |     |

|     | Counter-clockwise hysteresis from ferroelectric polarization switching is apparent.                                                                                         |     |

|     | Figure adapted from [71].                                                                                                                                                   | 75  |

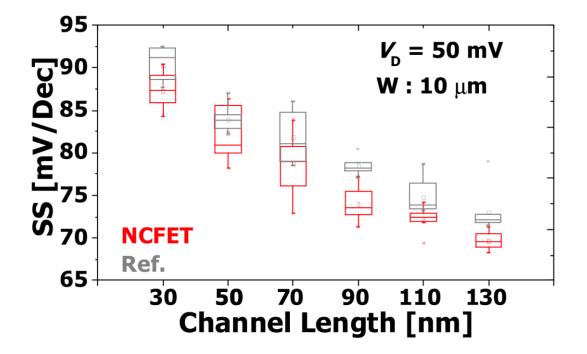

| 7.5 | Minimum subthreshold slope for both reference FET and NCFETs as a function                                                                                                  |     |

|     | of $L_q$ . Measurements are taken on multiple devices; the distributions are indicated                                                                                      |     |

|     | by the error bars. Figure adapted from [71]                                                                                                                                 | 76  |

|     | · · · · · · · · · · · · · · · · · · ·                                                                                                                                       |     |

| 7.6  | Comparison of drain-induced barrier between reference FETs and NCFETs, both                       |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | at $L_g = 90$ nm. Transfer characteristics for the NCFETs and reference FETs are                  |    |

|      | shown in (a) and (b), respectively. These data are summarized into one plot in                    |    |

|      | (c). Output characteristics for various overdrive voltages are shown in (d). Figure               |    |

|      | adapted from $[71]$ .                                                                             | 77 |

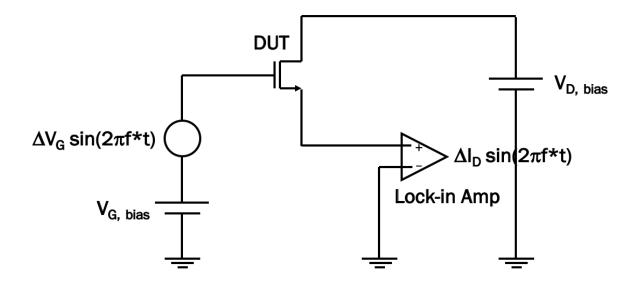

| 7.7  | Schematic of the small-signal transconductance measurement setup. DUT stands                      |    |

|      | for "Device Under Test." The small-signal amplitudes are used to calculated the                   |    |

|      | transconductance                                                                                  | 79 |

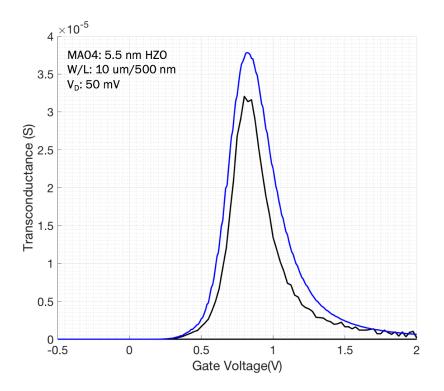

| 7.8  | Typical transconductance measurement of an NCFET. Data taken with the transcon-                   |    |

|      | ductance measurement setup (blue) are plotted against numerically calculated                      |    |

|      | values from a quasistatic measurement of the same device (black). $f = 1$ kHz.                    | 80 |

| 7.9  | Numerically integrated values of the transconductance data in 7.8 are plotted in                  |    |

|      | red alongside the raw measured quasistatic I-V data also corresponding to 7.8                     |    |

|      | (black). The reverse (right-hand) branch of hysteresis due to charge trapping is                  |    |

|      | also shown.                                                                                       | 81 |

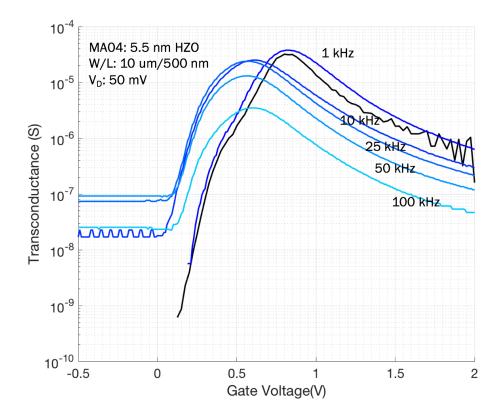

| 7.10 | Transconductance data for a range of measured frequencies. The numerically                        |    |

|      | differentiated quasistatic I-V curve is again shown in black. The measurements                    |    |

|      | suffer from peak $g_m$ variation and an unexplained pole at $\sim 10 \text{ k}\Omega$ .           | 82 |

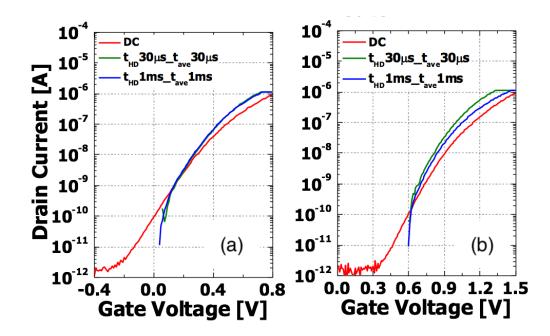

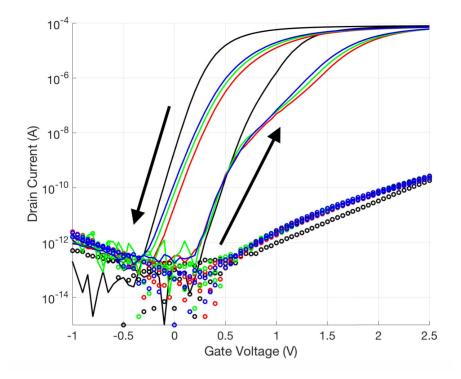

| 7.11 | Transfer characteristics for left (a) and right (b) branches of the ferroelectric                 |    |

|      | hysteresis. Pulsed I-V measurements for two different sets of pulse parameters                    |    |

|      | are shown. $t_{HD}$ is the time between the application of the gate voltage pulse and             |    |

|      | the measurement of the drain current when transients are allowed to settle. $t_{ave}$             |    |

|      | is the duration for which the current is measured                                                 | 83 |

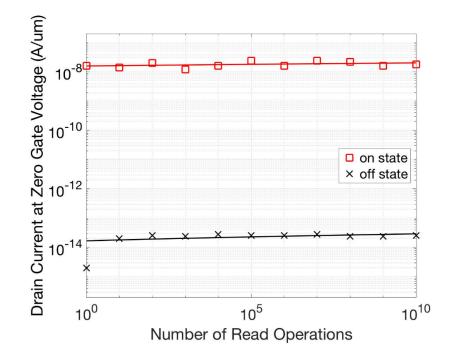

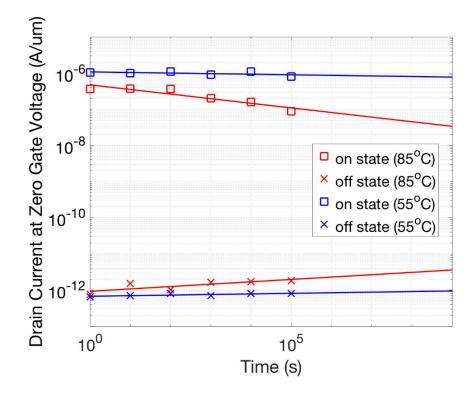

| 7.12 | Read endurance of both the on and off states of the ferroelectric memory tran-                    |    |

|      | sistor. Measurements are taken at 300 K. The straight lines are linear fits to the                |    |

|      | experimental data. Figure adapted from [62].                                                      | 84 |

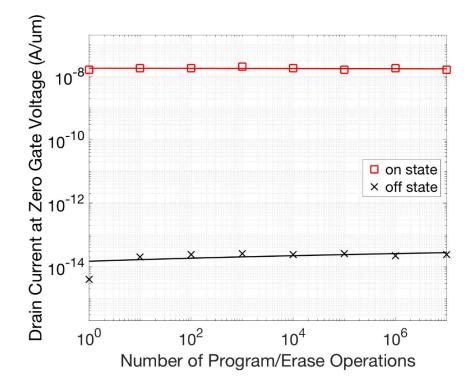

| 7.13 | Program/erase endurance of both the on and off states of the ferroelectric memory                 |    |

|      | transistor. Measurements are taken at 300 K. The straight lines are least-square                  |    |

|      | error linear fits to the experimental data. Figure adapted from [62]                              | 85 |

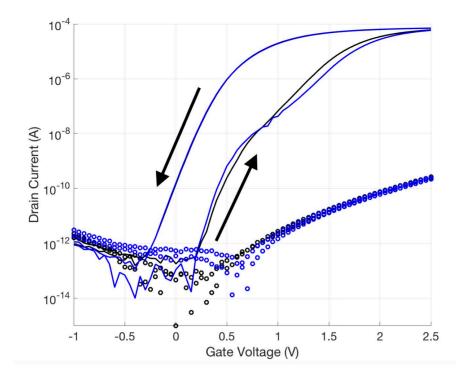

| 7.14 | $I_D V_{GS}$ transfer characteristics before (black) and after (blue) application of $10^7$       |    |

|      | program/erase cycles. Arrows indicate the direction of the hysteresis as counter-                 |    |

|      | clockwise. Figure adapted from [62].                                                              | 86 |

| 7.15 | $I_{D}$ - $V_{GS}$ transfer characteristics before (black) and after (red, green, and blue)       |    |

|      | breakdown and recovery. The red, green, and blue curves correspond to the first,                  |    |

|      | second, and third gate voltage sweeps after recovery, respectively. Figure adapted                |    |

|      | from [62]                                                                                         | 87 |

| 7.16 | J I                                                                                               |    |

|      | olated to $10^9 \text{ sec}$ (~ 10 years). Figure adapted from [62]                               | 88 |

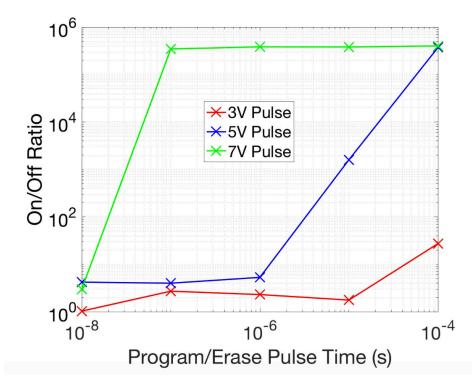

| 7.17 | $I_{\rm ON}/I_{\rm OFF}$ ratios as a function of pulse width for various pulse amplitudes. Higher |    |

|      | pulse amplitudes can switch the ferroelectric faster, but at the cost of degraded                 |    |

|      | program/erase endurance. Figure adapted from [62].                                                | 89 |

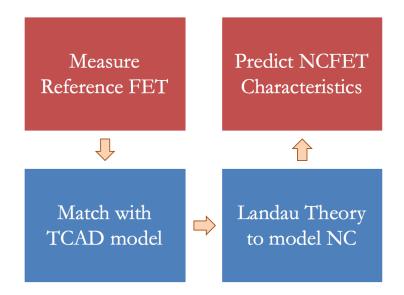

| 8.1 | Flowchart of the design process for extracting ferroelectric characteristics             | 90 |

|-----|------------------------------------------------------------------------------------------|----|

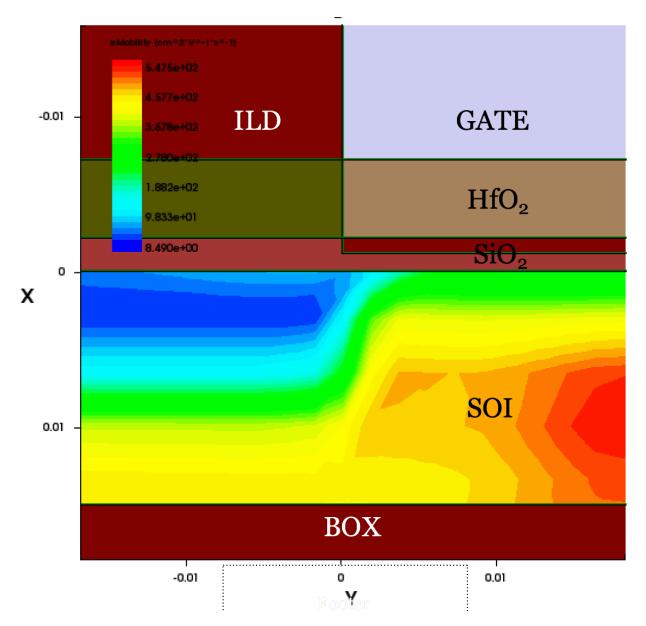

| 8.2 | Visualization of the TCAD FET structure with various regions indicated. Col-             |    |

|     | ormap shows electron mobility in the SOI device layer.                                   | 93 |

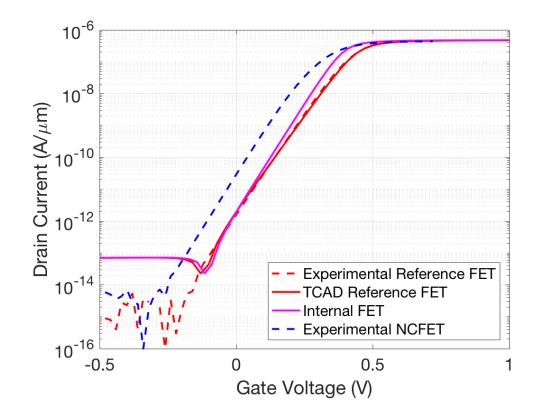

| 8.3 | $I_D$ - $V_G$ characteristics from TCAD simulation versus experimental data. The         |    |

|     | TCAD is matched closely to the experimental data for the reference FET. Addi-            |    |

|     | tionally the model yields the characteristics of the internal FET which is presumed      |    |

|     | to be common to both the reference FET and the NCFET                                     | 94 |

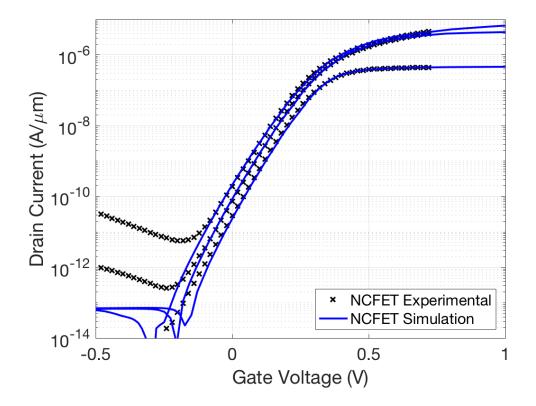

| 8.4 | A near-optimal ferroelectric model that closely reproduces NCFET transfer char-          |    |

|     | acteristics. The three sets of curves are for $V_{DS} = 50 \text{ mV}$ , 500 mV, and 1 V | 95 |

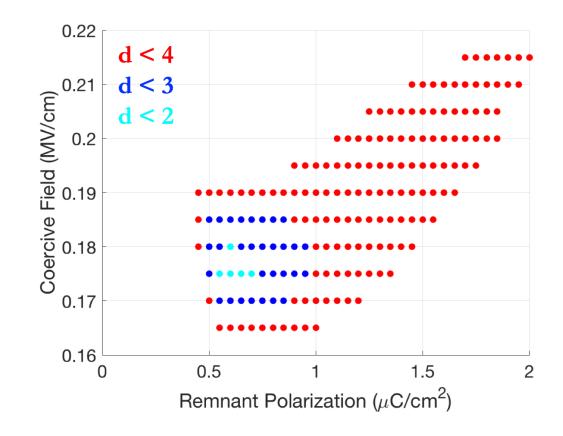

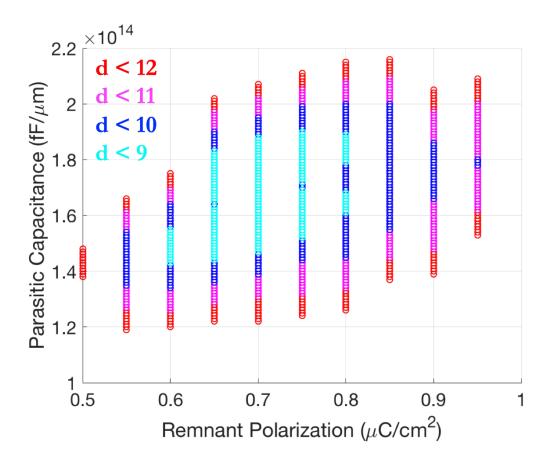

| 8.5 | Distribution of solutions for the first phase of parameter optimization over $P_r$ and   |    |

|     | $E_C$ . d here is the error metric defined in 8.4                                        | 96 |

| 8.6 | Distribution of solutions for the second phase of parameter optimization over $P_r$      |    |

|     | and $C_f$ . d here is the error metric defined in 8.4                                    | 98 |

|     |                                                                                          |    |

# List of Tables

| 1.1 | Dennard scaling results for circuit performance. Taken from [7]                                       | 3  |

|-----|-------------------------------------------------------------------------------------------------------|----|

|     | Summary of average subthreshold slopes for both pMOS and nMOS NC-FinFETs for different drain voltages | 54 |

#### Acknowledgments

I would like to thank my advisor and dissertation chair, Sayeef Salahuddin, for years of guidance and mentorship and maintaining an exciting research environment within the group. I would also like to thank Professors Chenming Hu, Tsu-Jae King Liu, and Ramamoorthy Ramesh for their continued support and guidance, and for sitting on my qualifying exam committee. I am also greatly indebted to my previous research mentors, Professors Ali Aliev, Ray Baughman, Murali Varanasi, Yves Chabal, Ronald Fearing, Connie Chang-Hasnain, and Eli Yablonovitch, as well as Professor Ming Wu for leading a pleasant and enriching teaching assistantship experience in microfabrication. A sincere thanks goes out to the EECS department staff of UC Berkeley, particularly Charlotte Jones, Derek Johnson, and Shirley Salanio for their invaluable help.

I am grateful to GlobalFoundries for a fruitful internship opportunity with Zoran Krivokapic in Santa Clara, CA, who has remained a mentor and collaborator. Thanks goes out to Srini Banna, who was also part of the negative capacitance efforts at GlobalFoundries.

The research presented here required significant financial investment, for which I am grateful. Thanks to the Center for Low Energy Systems Technology (LEAST), one of six SRC STARnet centers, to the Berkeley Center for Negative Capacitance Transistors (BCNCT), and to the NSF Center for Energy Efficient Electronics Science (E3S), through which I met Alexander Rosner as an REU student. Thanks also to the EECS department for a Nanotechnology Gold Fellowship, which supported me during my first year in the program.

Much of the fabrication work presented here was done in the Marvell Nanofabrication Laboratory, to whose staff I am grateful, particularly Bill Flounders, Joanna Bettinger, Kim Chan, Richelieu Hemphill, Ryan Rivers, Allison Dove, Anthony Bielecki, and Jeff Clarkson.

This work would not have been possible without collaboration and advice from my fellow researchers. In particular, the mentorship of Asif Khan as a senior graduate student was invaluable when I first joined the group. Many thanks to Praveen Gowtham, Justin Wong, Alexander Rosner, Sangwan Kim, Golnaz Karbasian, Ava Tan, Daewoong Kwon, Saidur Bakaul, Claudy Serrao, James Clarkson, Long You, Ajay Yadav, Niklas Roschewsky, Leonard Deuschle, Varun Mishra, Samuel Smith, Dominic Labanowski, Zhongyuan Lu, Debanjan Bhowmik, Hong Zhou, Charles-Henri Lambert, Suraj Cheema, Yu-Hung Liao, Michael Hoffman, Samuel Holladay, Haron Abdel-Raziq, Saavan Patel, Adi Jung, Nishita Deka, Jodi Loo, Gregg Scranton, Sapan Agarwal, Samarth Bhargava, Indrasen Bhattacharya, Phil Sandborn, Thomas Rembert, Mark Hettick, Andrew Gillies, Yen-Kai Lin, Juan Duarte, Ming-Yen Kao, Pragya Kushwaha, Harshit Agarwal, Angada Sachid, Vivek Mishra, Lucas Calderin, Sameet Ramakrishnan, Bonjern Yang, Nathan Narevsky, Krishna Settaluri, and Vinay Ramasesh for collaborations and discussions. Thanks also to Ajith Amerasekera, Ghulam Hasnain, Chandra Mouli, Wilman Tsai, Professor Ali Niknejad, Professor Andy Neureuther, and Professor Sanjay Banerjee for their valuable advice and discussions.

Finally, I express utmost gratitude to all my friends and family, especially my girlfriend Sowmya Somanath, whose love and encouragement have fueled me. My mother Radha, my sister Treena, and my father Amitava have given me unwavering support throughout my life, and I owe them immensely. I would like to give thanks in particular to my father, whose deep knowledge and persistent curiosity have always been an inspiration.

## Chapter 1

## Introduction

## 1.1 Motivation: Power Dissipation in CMOS Electronics

#### The Rise of the Electronic Age

Few inventions in human history have been as transformative as the integrated circuit. In the span of half a century, electronics has come to dominate virtually every aspect of modern life. When Shockley, Bardeen, and Brattain invented the transistor in 1947, science fiction writers and futurists were already fervently anticipating what has since come to fruition - smartphones, space flight, artificial intelligence, and guided missiles [1]. However, the dream was stalled by the so-called "tyranny of numbers," the seemingly insurmountable cost and reliability issues arising from needing to wire together a large number of discrete components. In 1958, Jack Kilby working at Texas Instruments proposed and demonstrated the first prototype of a monolithically integrated circuit. Soon afterwards, Robert Noyce at Fairchild Semiconductor devised the prevailing solutions to the problems of device isolation and metallization, and the first integrated circuits went on the market in 1961. Spurred by investment from NASA and the military, critical production mass was reached, and by 1964 costs had dropped enough to make mass-scale commercialization possible [2].

Powered by Moore's law [3], the exponential growth in the doubling of the number of transistors per dollar roughly every two years, total computational capacity has exploded. The internet has enabled near-instant communication across the globe and aggregated a vast compilation of human knowledge, removing almost all barriers to information. The compactness of electronic systems has allowed for distribution on a huge scale, the so-called "internet of things" (IoT). We can now monitor the structural integrity of concrete structures, seismic and atmospheric activity in remote locations, toxin and nutrient concentrations in industrial agricultural systems, and the glucose levels in our own blood. 1.1 summarizes the history of microprocessor performance metrics. This surge has been accompanied by the proliferation of computers for personal entertainment and communication, large-scale data

processing, and scientific computing. High-energy particle physics, genomic sequencing, modern drug design, and autonomous vehicles would all be impossible without the firehose of high performance digital logic. The economic impact is commensurate. IoT alone is estimated to become a \$6.2 trillion industry by 2025 [4]. Semiconductor manufacturing in just the last 20 years has nearly quadrupled its monthly revenue from \$10 billion to \$38.7 billion [5]. The pervasiveness of electronics in modern life is so extreme that its impact is comparable to that of agriculture or industrialization.

Figure 1.1: Industry trends for microprocessors over the last 42 years. Taken from [6].

#### The Boltzmann Tyranny

In 1974, Robert H. Dennard with others published a landmark analysis on the scaling of characteristics and fabrication requirements with continued reduction of the physical dimension of metal-oxide-semiconductor field-effect transistors (MOSFETs) [7]. Almost all modern processors are constructed using the complementary metal-oxide-semiconductor (CMOS) platform; MOSFETs are the workhorse of modern computing. The central result of this analysis for device characteristics is shown in 1.1. As long as Dennard scaling holds, the per stage delay scales with the physical dimension and the power density remains constant. This means the clock frequency can be increased with scaling, as is seen in the first part of 1.1, further amplifying the increase of computational throughput with technology generation. By the mid to late 2000s, increased off-state leakage had increased power dissipation

| Device or Circuit Parameter      | Scaling Factor |

|----------------------------------|----------------|

| Device dimension $t_{ox}$ , L, W | $1/\kappa$     |

| Doping concentration $N_a$       | $\kappa$       |

| Voltage V                        | $1/\kappa$     |

| Current I                        | $1/\kappa$     |

| Capacitance $\epsilon A/t$       | $1/\kappa$     |

| Delay time/circuit VC/I          | $1/\kappa$     |

| Power dissipation/circuit VI     | $1/\kappa^2$   |

| Power density VI/A               | 1              |

Table 1.1: Dennard scaling results for circuit performance. Taken from [7].

to the point that threshold voltage scaling and thus also frequency scaling were no longer possible [8]. To cope with this lack of scaling, circuit designers have made innovations at the architecture level, employing parallel processing and a larger number of cores per processing unit. The end of Dennard scaling has seen the rise of power dissipation as a critical problem which threatens the progress of digital logic performance [9].

The root of this problem is the statistical distribution of electrons in the semiconductor. In a MOSFET, the gate is capacitively coupled to the channel, where it populates carriers by changing the surface potential  $\Psi_S$  [10]. The Fermi-Dirac distribution can usually be approximated by a Boltzmann distribution, so the inversion charge density, and thus the subthreshold source-drain current, is proportional to  $exp\{q\Psi_S/k_BT\}$ , where q is the electron charge,  $k_B$  is Boltzmann's constant, and T is the absolute temperature. In the case where the gate has perfect electrostatic control over the channel, a factor of 10 increase of drain current requires 60 mV of gate voltage at room temperature. Thus, in order to maintain a certain ratio of on-current to off-current, the operating voltage must be held constant. This limit of 60 mV/decade on subthreshold slope is termed the "Boltzmann tyranny." Without changing the physical principles of operation behind the MOSFET, this limitation cannot be overcome. From this the impetus to "reinvent the transistor" was born [11].

A number of solutions to Boltzmann tyranny have been proposed. Nanoelectromechanical (NEM) relays, tunneling field-effect transistors (TFETs), nanomagnetic logic, resonant body transistors, and field-induced phase transition switches are all being investigated as alternatives to conventional FETs [9]. All of these approaches use some novel physical mechanism to control the conductance between two terminals. In addition to these exotic devices, it was proposed in 2008 by Salahuddin and Datta [12] that a negative differential gate capacitance in a MOSFET could amplify the surface potential relative to the gate voltage, bringing the subthreshold slope below 60 mV/decade thereby reducing the operating voltage, all without having to invent a new device.

The contention is that negative capacitance can be obtained by using a ferroelectric material as a gate dielectric. The depolarizing field from the semiconductor capacitance drives the ferroelectric material into a locally unstable state where  $\partial Q/\partial V$  is negative. This concept is elaborated subsequently.

### **1.2** The Case for Ferroelectric Negative Capacitance

#### Why Negative Capacitance?

To illustrate how negative capacitance can lower the subthreshold slope below 60 mV/decade, it is useful to consider a MOSFET as a simple capacitive divider, as shown in 1.2.  $V_G$  is the applied gate voltage,  $C_{ox}$  and  $C_S$  are the oxide and semiconductor capacitances, respectively. We acknowledge that this is a simplistic model. Fringing field, source-channel, drain-channel, and other parasitic capacitances are lumped into the quantity  $C_S$ . A MOSFET is a fourterminal device, and a comprehensive model needs to consider the full  $4 \times 4$  capacitance matrix [13]. Nevertheless, this simple model is valid in many cases and yields insight into the basic principle of operation of an NCFET. Noting that the capacitors are in series, they must share the same charge Q. Straightforward calculation shows that  $\Psi_S$  is related to  $V_G$ by 1.1.

$$\Psi_S = \frac{C_{ox}}{C_{ox} + C_S} V_G \tag{1.1}$$

Because in general capacitors are nonlinear, it is more useful to use the differential relationships between quantities, which we assume throughout this text ("capacitance" refers to differential capacitance, "amplification" to differential amplification, etc., unless explicitly stated otherwise. The relationship between surface potential and gate voltage is commonly termed the "body factor" denoted by m [12], and is given by:

$$m^{-1} = \frac{\partial \Psi_S}{\partial V_G} = (1 + \frac{C_S}{C_{ox}})^{-1}$$

(1.2)

Subthreshold slope (SS) is defined as  $\partial V_G / \partial log_{10}(I_D)$ , which is expanded in 1.3.

$$SS^{-1} = \frac{\partial log_{10}(I_D)}{\partial V_G} = \frac{\partial log_{10}(I_D)}{\partial \Psi_S} \frac{\partial \Psi_S}{\partial V_G} = \frac{1}{log(10)} \frac{q}{k_B T} \frac{1}{1 + C_S/C_{ox}}$$

(1.3)

Now it is manifestly apparent from the functional form of m and SS that a negative oxide capacitance amplifies the surface potential relative to the gate voltage, lowering the body factor below m, and thus the subthreshold slope below 60 mV/decade. One can also calculate the total equivalent capacitance seen from the gate  $C_{eq}^{-1} = C_{ox}^{-1} + C_S^{-1}$ . In the case of negative  $C_{ox}$ ,  $C_{eq}$  is larger than  $C_S$ , whereas for positive capacitors in series the equivalent capacitance is always lower than each of the individual capacitors. Negative capacitance can be understood to provide capacitance enhancement - less voltage is required to bring in a given amount of charge. This results in a negative differential voltage on the negative capacitor and a boosting of the internal node voltage, which, for a MOSFET can bring the subthreshold slope below the Boltzmann limit. In principle there is no limit on how far the subthreshold slope may be lowered.

Figure 1.2: Simplified depiction of a MOSFET as a capacitive divider.

It is worth noting that an isolated negative capacitance is inherently unstable. Capacitance is normally defined as  $\partial Q/\partial V$ , but it may equivalently be defined with respect to the internal energy U. In electrostatics,  $dU = V \ dQ$ , so that capacitance can be defined as  $C = (\frac{\partial^2 U}{\partial Q^2})^{-1}$  [14]. Therefore the capacitance is just the curvature of the internal energy with respect to its internal parameter(s), and work can be extracted out of a system in a state with negative capacitance - thus it is unstable. The key point is that in an NCFET, the system is not isolated. If the depolarization fields can overcome the internal dipole fields that give rise to ferroelectricity, a balance is reached, and the series condition asserted earlier,  $Q_{ox} = Q_S$ , is realized. In the simple lumped capacitor model, if  $|C_{ox}| > C_S$ , the total capacitance is positive, and the negative capacitance is stable. The internal energy of  $C_{ox}$ would be decreased by increasing Q, but this would require a greater energetic cost in the charging of  $C_S$ . Finally, we note that in strong inversion, the channel is effectively shorted to ground through the source terminal, and the capacitance seen at the gate is just  $C_{ox}$  [10]. Thus the gate capacitance must be engineered to only be negative in subthreshold.

#### Ferroelectricity: A Source of Negative Capacitance

Having established the potential benefits of negative capacitance, the question remains as to where such states may occur in nature. In thinking of capacitance as curvature of the internal energy landscape, one is led naturally to ferroelectric materials. A ferroelectric is defined as a material which exhibits a spontaneous polarization that can be reversed with an applied electric field [15]. In other words, the internal energy of a ferroelectric is minimized by a nonzero polarization, with at least two minima. This is referred to as the "spontaneous polarization," typically in the range of 1-100  $\mu$ C/cm<sup>2</sup>. If the internal energy is a smooth function of the out-of-plane component of polarization, then its qualitative form would be given by something like 1.3.

Figure 1.3: Energy landscape of a hypothetical ferroelectric material. The region of negative capacitance states between the spontaneous polarization states is indicated.

Now we must consider how this relates to charge on the plates of a capacitor. Recall that the charge density is given by the displacement electric field at the surface,  $D = \epsilon_0 E + P$ , where  $\epsilon_0$  is the permittivity of free space, E is the electric field, and P is the polarization density in the material between the capacitor electrodes [14]. So the charge Q is just the area A times the displacement field,  $Q = A(\epsilon_0 E + P)$ . In practice,  $P \gg \epsilon_0 E$ , and  $Q \approx AP$ , so that ferroelectric polarization and capacitor charge may be treated interchangeably in most contexts. Strictly speaking, the function shown in 1.3 is the free energy per unit volume, so its curvature is the dielectric susceptibility. These considerations suggest that, if the ferroelectric material can be brought near the P = 0 state, its capacitance will be negative.

### **1.3 Summary of Previous Work**

The story of ferroelectricity goes back to the 17th century, in the town of La Rochelle in the south of France. In 1665, an apothecary named Elie Seignette concocted potassium sodium tartrate tetrahydrate (NaKC<sub>4</sub>H<sub>4</sub>O<sub>6</sub>·4H<sub>2</sub>O), which came to be sold as "sel polychreste" as a mineral-derived medicine. Although its medicinal use eventually fell out of favor, it remained on the market for over two centuries and later came to be known as Rochelle salt [16]. In 1824, David Brewster, observed pyroelectricity in a number of materials, including Rochelle salt, and it entered the world of materials science. In 1880 Pierre and Paul-Jacques Curie systematically studied the temperature dependence of Rochelle salt, and identified its piezoelectricity, which lead to its use as a transducer material in military applications during WWI. In 1912, Peter Debye, who had been following the developments in piezoelectricity, hypothesized that the experimental results could be explained by the existence of a permanent electric dipole moment, analogous to the permanent magnetic dipole moments in ferromagnets. Furthering this analogy, Debye proposed that the dielectric susceptibility  $\chi$  should diverge at the Curie temperature according to the Curie-Weiss law, 1.4.

$$\chi = \frac{C}{T - T_C} \tag{1.4}$$

Here C is the material-dependent Curie constant, T is temperature, and  $T_C$  is the Curie temperature. Above the Curie temperature, the material behaves as a normal insulator, but as the temperature is lowered, the susceptibility diverges, and a spontaneous dipole moment appears even in the absence of a field [15]. Erwin Schrödinger generalized this work to the case of solids rather than just molecules, and coined the term "ferroelectricity" (German: "ferroelektrisch").

In 1920, Joseph Valasek, a graduate student at the University of Minnesota in Minneapolis carried out systematic studies on Rochelle salt, drawing an analogy between the relationship between the B and H fields of ferromagnets and the E and D fields of ferroelectrics [17]. His work lead to the first experimental observation of ferroelectric hysteresis, shown in 1.4.

The advent of WWII produced a surge of interest in ferroelectric research, which lead to the discovery of ferroelectricity in barium titanate (BaTiO<sub>3</sub>). This was the first discovery of ferroelectricity in a simple oxide, without hydrogen bonds. The class of materials to which BaTiO<sub>3</sub> belongs, the perovskite oxides, has dominated research in ferroelectricity and are by far the most well-studied class of ferroelectric materials. As one may expect from the susceptibility divergence in the Curie-Weiss law, these materials exhibit extremely high relative dielectric constants, which can exceed 1000. This saw the use of ferroelectrics in a variety of applications, mostly as transducers or low-volume discrete capacitors. Ferroelectrics have also found use in communications, where the nonlinear electro-optic effect results in an electrically controlled optical switch. Interestingly, the use of ferroelectricity as a non-volatile memory, where it is placed in the gate of a transistor and thus controls the threshold voltage with its polarization state, dates back to the the master's thesis of Dudley Allen Buck at MIT in 1952 [18].

Figure 1.4: The first reported ferroelectric hysteresis loop, by Joseph Valasek on Rochelle salt. From [17].

Ferroelectricity in solids can also be analyzed in terms of their symmetries. A nonzero spontaneous (or remanent) polarization requires the breaking of inversion symmetry. Of the 32 crystallographic point groups, 21 are noncentrosymmetric, of which all but 1 are piezoelectric. 10 of these are pyroelectric, which is a superset of ferroelectrics. Ferroelectrics are often classified according to whether they are displacive, where the force from internal dipole fields overwhelms the restoring force of the lattice, or order-disorder, where permanent dipoles align as temperature is reduced [19]. In reality, the strain fields of the lattice and the unit cell dipole moments must be solved self-consistently, and it is impossible to draw a clear line between the two [16].

In the 1930s, Soviet physicist Lev Landau developed a phenomenological theory of phase transitions. It is a phenomenological theory which, assuming coarse-graining of fluctuating internal fields, provides a relationship between microscopic theory and measurable macroscopic quantities. Landau recognized that a phase transition which breaks symmetry must be accompanied by the development of a corresponding order parameter. The state of the system is then represented by a thermodynamic free energy, which is expanded in a Taylor series in that order parameter. This formalism gave rise to the Ginzburg-Landau theory of superconductivity, which was important in the development of that field. In 1949, A. F. Devonshire adapted Landau's theory to ferroelectricity. This theory is called the Landau-Devonshire theory, and it remains a cornerstone of analyzing ferroelectric behavior today [20]. Its central result is the form of the free energy functional, given in 1.5 below.

$$u = \alpha_0 (T - T_C) P^2 + \beta P^4 + \gamma P^6 + \dots - EP$$

(1.5)

The last term represents coupling to the electric field. From this free energy, one can calculate

the temperature dependence of the susceptibility, and derive the Curie-Weiss law in 1.4, as well as a variety of physical quantities. The hysteresis loop can also be explained in terms of the Landau-Devonshire theory. A system in one of the two energy minima can be driven into the other when an applied field tilts the energy landscape until the energy barrier between the minima (and thus one of the minima) disappears. Turning off the field now leaves the ferroelectric in the other minimum, which produces the observed hysteresis. This process is explained in much greater detail in further chapters.

Since the second world war, ferroelectricity has become an active field of scientific research, with many tens of thousands publications in the literature today. A large number of materials have been discovered which exhibit ferroelectricity, many which exhibit more exotic origins, such as electronic ferroelectrics [15]. Antiferroelectricity, analogous to antiferromagnetism, was proposed by Charles Kittel and discovered in a number of materials [21]. Numerous advancements were made in ferroelectric materials synthesis and characterization as well as in the theoretical descriptions of ferroelectricity, which are too numerous to cover here.

Figure 1.5: Hysteresis loop of a  $BaTiO_3$  sample, with the proposed negative capacitance states shown with a dashed curve.

In 2008, searching for a way to combat the aforementioned "Boltzmann tyranny," Salahuddin and Datta noted that in the Landau-Devonshire theory, the equilibrium states of P corresponding to various values of E form an S-curve, which an experimental hysteresis loop encloses. This is conceptualized for BaTiO<sub>3</sub> in 1.5. The disappearance of the local minimum of the system at the coercive field is reflected in the S-shape of the dashed curve. A negatively poled ferroelectric subject to a positive electric field suddenly has no nearby states at the lower cusp of the "S," and the material is driven out of equilibrium to the other (remaining) minimum. The negative capacitance portion of the S-curve is necessary to produce the multiple solutions that result in hysteresis, but it had not been considered that those states could be stabilized with a series capacitor and used for voltage amplification.

In late 2010, experimental demonstration of ferroelectric negative capacitance was first reported. Khan et al. showed that the capacitance of a heterostructure comprised of ferroelectric lead zirconate titanate and dielectric strontium titanate could be increased beyond that of just the strontium titanate [22]. They reported a temperature-dependence which was totally consistent with Landau-Devonshire theory, and found that the Curie temperature was effectively lowered by the presence of strontium titanate. Similar characterization was performed soon after for a ferroelectric  $Ba_{0.8}Sr_{0.2}TiO_3$ -dielectric LaAlO<sub>3</sub> superlattice [23]. Almost simultaneously, Rusu et al. reported sub-60 mV/decade subthreshold slope in a polyvinylidene fluoride (PVDF) gated FET [24]. This work begins in this era, when relatively few experiments had been carried out on ferroelectric negative capacitance, and its existence was contentious. Since then, especially with the discovery of ferroelectricity in doped hafnium oxides, research involvement in negative capacitance has grown considerably, with the first industry results on negative capacitance transistors announced in 2017 [25].

## Chapter 2

## Direct Observation of Negative Capacitance

## 2.1 Introduction

The first demonstrations of negative capacitance involved two substantially different techniques. The work by A. Rusu et al. observed subthreshold slope in a ferroelectric-gated MOSFET below 60 mV/decade at room temperature [24]. The work by A. I. Khan et al. demonstrated a capacitance enhancement in a ferroelectric-dielectric stack as compared to the dielectric alone [22]. While both of these techniques are robust, they rely on indirectly observing the effects of negative capacitance - that is, voltage amplification - rather than a direct observation of capacitor charge changing in opposition to the voltage drop across it. The controversy surrounding the claim of passive, static negative capacitance provided the impetus to find a way to directly observe negative capacitance in an isolated ferroelectric capacitor. As the negative capacitance states of an *uncoupled* ferroelectric polarization switching. Thus the experimental setup in 2.1 was conceived. A voltage pulse above the coercive voltage is applied to a poled ferroelectric capacitor in series with a resistor R whose purpose is fourfold.

1. Limit the switching current, and therefore slow the rate of polarization switching, so that the transient can be measured using a standard oscilloscope.