## UC Santa Barbara

**UC Santa Barbara Electronic Theses and Dissertations**

## Title

Kernel-Centric Optimizations for Deep Neural Networks on GPGPU

### Permalink

https://escholarship.org/uc/item/6d82g5r7

## Author

Chen, Zhaodong

## **Publication Date**

2024

Peer reviewed|Thesis/dissertation

University of California Santa Barbara

## Kernel-Centric Optimizations for Deep Neural Networks on GPGPUs

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy in Electrical and Computer Engineering

by

#### Zhaodong Chen

Committee in charge:

Professor Yuan Xie, Co-Chair Professor Zheng Zhang, Co-Chair Professor Timothy Sherwood Professor Yufei Ding Professor Yao Qin

March 2024

The Dissertation of Zhaodong Chen is approved.

Professor Timothy Sherwood

Professor Yufei Ding

Professor Yao Qin

Professor Zheng Zhang, Committee Co-Chair

Professor Yuan Xie, Committee Co-Chair

March 2024

#### Kernel-Centric Optimizations for Deep Neural Networks on GPGPUs

Copyright  $\bigodot$  2024

by

Zhaodong Chen

#### Acknowledgements

Pursuing a Ph.D. degree is never an easy task. Throughout my five-year journey as a Ph.D. student, I have experienced stressful moments - from sleepless nights striving to meet deadlines and anxiety about rebuttals, to moments of frustration upon receiving negative comments from reviewers. There were also moments of joy, such as the excitement of paper acceptances, weekend hotpot parties, and the unforgettable spring break trip to Alaska. I have been incredibly fortunate to be surrounded by my advisors, mentors, colleagues, lab mates, family, and friends during all these moments.

I have always been grateful to have Prof. Yuan Xie as my advisor. His insights have consistently guided me over the past five years and will continue to do so in my future career. He has given me the freedom to devote myself to research topics that interest me while offering unwavering respect, support, and all the necessary resources.

I also want to express my gratitude to Professor Yufei Ding for her invaluable advice and support regarding my research. She has always encouraged me to delve into deeper and more impactful topics, offering detailed and constructive suggestions from paper writing to rebuttal responses.

I also thank Professor Zhang, my co-chair, for his support of both my research and life over the last two quarters. Additionally, I appreciate my committee members, Professor Timothy Sherwood, and Professor Yao Qin, for their insightful input and support.

I want to extend my special thanks to Prof. Guoqi Li, my undergraduate supervisor, who has always had faith in me and provided unwavering support.

I consider myself fortunate to have been allowed to join NVIDIA's CUTLASS group as an intern for the past two summers, and I am sincerely grateful for the chance to return as a full-time employee. My manager, Alan Kaatz, has consistently provided encouragement and support during our weekly meetings. Additionally, my mentors, Dr. Haicheng Wu, Dr. Andrew Kerr, Dr. Jack Kosaian, Richard Cai, as well as my colleague Dr. Yujia Zhai, have offered invaluable support and assistance throughout my internship.

I appreciate the opportunity to work with the hardworking, intelligent, and warmhearted lab mates from SEAL Lab, PICASSO Lab, and Professor Zhang's Lab. Dr. Lei Deng helped me with my first first-author paper and continued to offer invaluable support thereafter. Memories of our daily gathering in Lei's apartment, where a few lab mates and I would come together to prepare dinner, will always hold a special place in my heart. Dr. Maohua Zhu is my mentor in CUDA programming and GPU microarchitecture, guiding me with expertise and patience. Dr. Ling Liang has been kindly driving me to the grocery stores during the pandemic, and he is also my indispensable research collaborator. I have also collaborated with Dr. Zheng Qu and Dr. Liu Liu on deep learning acceleration topics, resulting in the co-authorship of several remarkable papers, which could not haven been done without their dedication, intelligence, and talent. Furthermore, I extend my gratitude to Prof. Xing Hu, Prof. Mingyu Yan, Prof. Fengbin Tu, Prof. Jiavi Huang, Dr. Jilan Lin, Dr. Bangtan Wang, Prof. Nan Wu, Dr. Tianqi Tang, Prof. Gushu Li, Dr. Peng Gu, Dr. Abanti Basak, Dr. Shuangchen Li, Dr. Wenqin Huangfu, Dr. Xinfeng Xie, Dr. Anbang Wu, Dr. Boyuan Feng, Yuke Wang, Zheng Wang, Zhengyang Wang, Siqi Li, Alvin Liu, Hao Li, Guyue Huang. It has been a great time working with all my lab mates.

I am deeply grateful to my friends, whose unwavering encouragement, understanding, and companionship have been invaluable throughout this journey. I extend special thanks to Jianyu Xu, my comrade since our undergraduate days at Tsinghua University. We came to UCSB together, and he is always been the person I can pour out my heart.

I would like to express my deepest gratitude to my family. My parents have always been my strongest backing, giving me the confidence and courage I needed at every turning point along this journey. My girlfriend, Carina Quan, has enlightened my life since the day we met. She has stood by my side through both storms and sunshine, offering unwavering support and love.

### Curriculum Vitæ Zhaodong Chen

#### Education

| 2024 | Ph.D. in Electrical and Computer Engineering (Expected), Univer- |  |  |  |  |

|------|------------------------------------------------------------------|--|--|--|--|

|      | sity of California, Santa Barbara.                               |  |  |  |  |

| 2021 | M.S. in Electrical and Computer Engineering, University of Cali- |  |  |  |  |

|      | fornia, Santa Barbara.                                           |  |  |  |  |

| 2019 | B.E. in Department of Precision Instrument, Tsinghua University  |  |  |  |  |

#### Publications

[1] Wenzhao Zheng, **Zhaodong Chen**, Jiwen Lu, and Jie Zhou. "Hardness-aware deep metric learning." In Proceedings of the IEEE/CVF Conference on Computer Vision and Pattern Recognition, pp. 72-81. 2019.

[2] Liu Liu, Lei Deng, **Zhaodong Chen**, Yuke Wang, Shuangchen Li, Jingwei Zhang, Yihua Yang, Zhenyu Gu, Yufei Ding, and Yuan Xie. "Boosting deep neural network efficiency with dual-module inference." In International Conference on Machine Learning, pp. 6205-6215. PMLR, 2020.

[3] Mingyu Yan, **Zhaodong Che**n, Lei Deng, Xiaochun Ye, Zhimin Zhang, Dongrui Fan, and Yuan Xie. "Characterizing and understanding GCNs on GPU." IEEE Computer Architecture Letters 19, no. 1 (2020): 22-25.

[4] **Zhaodong Chen**, Lei Deng, Guoqi Li, Jiawei Sun, Xing Hu, Ling Liang, Yufei Ding, and Yuan Xie. "Effective and efficient batch normalization using a few uncorrelated data for statistics estimation." IEEE Transactions on Neural Networks and Learning Systems 32, no. 1 (2020): 348-362.

[5] **Zhaodong Chen**, Lei Deng, Bangyan Wang, Guoqi Li, and Yuan Xie. "A comprehensive and modularized statistical framework for gradient norm equality in deep neural networks." IEEE Transactions on Pattern Analysis and Machine Intelligence 44, no. 1 (2020): 13-31.

[6] **Zhaodong Chen**, Mingyu Yan, Maohua Zhu, Lei Deng, Guoqi Li, Shuangchen Li, and Yuan Xie. "fuseGNN: Accelerating graph convolutional neural network training on GPGPU." In Proceedings of the 39th International Conference on Computer-Aided Design, pp. 1-9. 2020.

[7] **Zhaodong Chen**, Zheng Qu, Liu Liu, Yufei Ding, and Yuan Xie. "Efficient tensor core-based gpu kernels for structured sparsity under reduced precision." In Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis, pp. 1-14. 2021.

[8] Ling Liang, Zheng Qu, **Zhaodong Chen**, Fengbin Tu, Yujie Wu, Lei Deng, Guoqi Li, Peng Li, and Yuan Xie. "H2learn: High-efficiency learning accelerator for high-accuracy spiking neural networks." IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 41, no. 11 (2021): 4782-4796.

[9] Boyuan Feng, Tianqi Tang, Yuke Wang, **Zhaodong Chen**, Zheng Wang, Shu Yang, Yuan Xie, and Yufei Ding. "Faith: An Efficient Framework for Transformer Verification on GPUs." In 2022 USENIX Annual Technical Conference (USENIX ATC 22), pp. 167-182. 2022.

[10] Zheng Qu, Liu Liu, Fengbin Tu, **Zhaodong Chen**, Yufei Ding, and Yuan Xie. "Dota: detect and omit weak attentions for scalable transformer acceleration." In Proceedings of the 27th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, pp. 14-26. 2022.

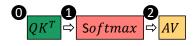

[11] **Zhaodong Chen**, Zheng Qu, Yuying Quan, Liu Liu, Yufei Ding, and Yuan Xie. "Dynamic n: M fine-grained structured sparse attention mechanism." In Proceedings of the 28th ACM SIGPLAN Annual Symposium on Principles and Practice of Parallel Programming, pp. 369-379. 2023.

[12] Ling Liang, **Zhaodong Chen**, Lei Deng, Fengbin Tu, Guoqi Li, and Yuan Xie. "Accelerating spatiotemporal supervised training of large-scale spiking neural networks on gpu." In 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE), pp. 658-663. IEEE, 2022.

[13] Liu Liu, Zheng Qu, **Zhaodong Chen**, Fengbin Tu, Yufei Ding, and Yuan Xie. "Dynamic sparse attention for scalable transformer acceleration." IEEE Transactions on Computers 71, no. 12 (2022): 3165-3178.

#### Abstract

#### Kernel-Centric Optimizations for Deep Neural Networks on GPGPUs

by

#### Zhaodong Chen

Deep learning has achieved remarkable success across various domains, ranging from computer vision to healthcare. General-Purpose Graphics Processing Unit (GPGPU) is one of the major driving forces behind this revolution. GPGPUs offer massive parallel computational power, enabling the training and deployment of large-scale neural networks within practical time and resource constraints. Their programmability also enables adaptability to emerging network architectures.

However, entering the post-Moore's Law era, the scaling of computational power offered by GPGPUs struggles to meet the demands of novel neural networks. On the other hand, existing GPGPUs face under-utilization challenges despite the computation power shortage.

This dissertation addresses the computation power shortage by improving the utilization of GPGPUs when running deep learning workloads. It presents a kernel-centric optimization approach with a focus on mapping neural networks to a more efficient set of kernels (parallel functions executed on GPGPUs) that ensures better utilization. This involves optimizations from multiple levels: algorithm level aiming to leverage more hardware-friendly formulations, operator level to harness on-chip high bandwidth on GPGPUs, and kernel implementation level that maximizes the utilization of computational resources.

# Contents

| Cı | culum Vitae vii                                                                                                                                                                                                                                                                                                            |                                         |  |  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|

| A  | bstract                                                                                                                                                                                                                                                                                                                    | ix                                      |  |  |

| 1  | Introduction1.1Characterize the utilization of GPGPU1.2Kernel-Centric Optimization1.3Manual Kernel-Centric Optimization1.4Compiler-based Kernel-Centric Optimization1.5Organization                                                                                                                                        | 3<br>4<br>7                             |  |  |

| 2  | Background and Related Work         2.1       Neural Network Models         2.2       General Purpose Graphic Processing Units         2.3       Related Work on Algorithm-level Optimizations         2.4       Related Work on Operator-level Optimizations         2.5       Related Work on Kernel-level Optimizations | 14<br>19<br>22                          |  |  |

| 3  | Algorithm-Kernel Codesign: Static Sparsity with Tensor Core3.1Introduction3.2Motivation3.3Algorithm-level Optimization: VecSparse3.4Kernel-level Optimization: SpMM3.5Kernel-level Optimization: SDDMM3.6Experiments3.7Discussion & Conclusion                                                                             | 27<br>32<br>34<br>40<br>46              |  |  |

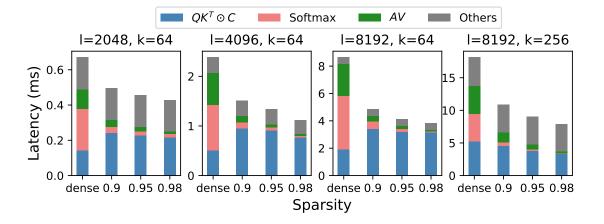

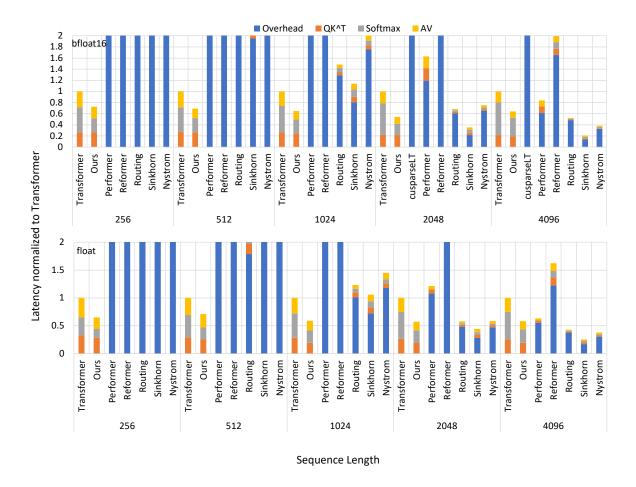

| 4  | Algorithm-Kernel Codesign: GPGPU-friendly Sparse Attention4.1Introduction4.2Algorithm-level Optimization: DFSS4.3Kernel-level Optimization: Dynamic SDDMM4.4Evaluation                                                                                                                                                     | $\begin{array}{c} 61 \\ 65 \end{array}$ |  |  |

|              | 4.5   | Conclusion and Discussion                               | 78  |

|--------------|-------|---------------------------------------------------------|-----|

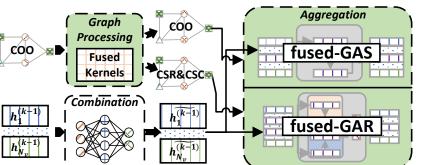

| <b>5</b>     | Alg   | orithm-Operator-Kernel Codesign: Efficient GNN Training | 79  |

|              | 5.1   | Introduction                                            | 79  |

|              | 5.2   | Motivation                                              | 81  |

|              | 5.3   | Overview                                                | 84  |

|              | 5.4   | Algorithm-level Optimization: Dual Aggregation Models   | 86  |

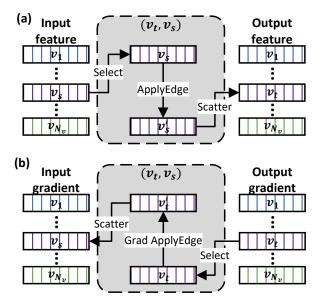

|              | 5.5   | Operator-level Optimization                             | 89  |

|              | 5.6   | Kernel-level Optimization                               | 90  |

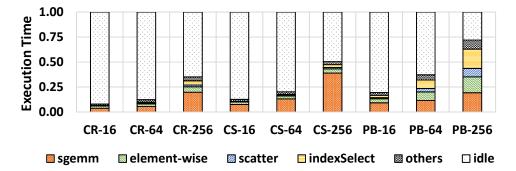

|              | 5.7   | Evaluation                                              | 98  |

|              | 5.8   | Conclusions                                             | 104 |

| 6            | Ker   | nel-Centric Optimization: Compiler Perspective          | 105 |

|              | 6.1   | Introduction                                            | 105 |

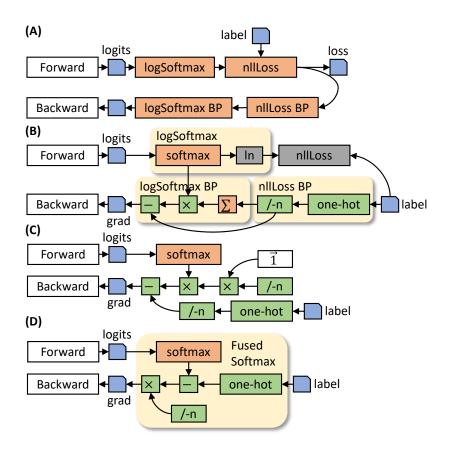

|              | 6.2   | Algorithm-level Optimizations                           | 109 |

|              | 6.3   | Operator-level Optimization                             | 114 |

|              | 6.4   | Kernel-level Optimization                               | 122 |

|              | 6.5   | Evaluation                                              | 131 |

|              | 6.6   | Conclusion & Discussion                                 | 137 |

| 7            | Cor   | nclusion                                                | 139 |

|              | 7.1   | Summary of Contributions                                | 139 |

|              | 7.2   | Future Research                                         | 141 |

| $\mathbf{A}$ | Sup   | plemental Materials for DFSS                            | 143 |

|              | A.1   | Theoretical Results                                     | 143 |

|              | A.2   | Empirical Results                                       | 148 |

|              | A.3   | Comparison with Performer                               | 151 |

|              | A.4   | Combination with the Existing Efficient Transformers    |     |

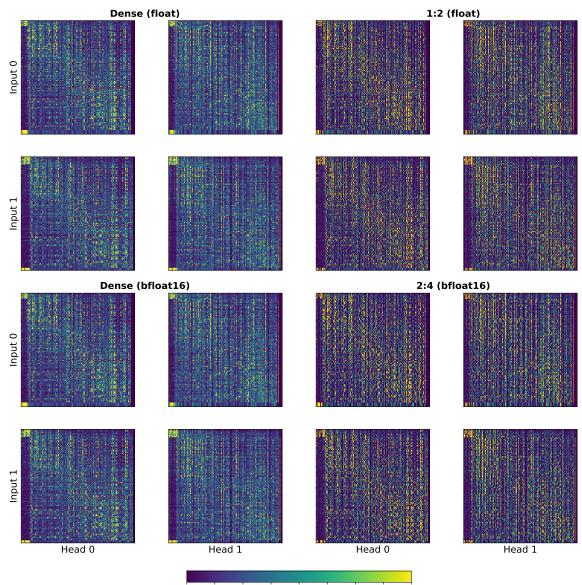

|              | A.5   | Visualize Attention Distribution                        | 157 |

|              | A.6   | Proof of Proposition A.1.2                              | 159 |

|              | A.7   | Proof of Proposition A.1.3                              | 162 |

| в            | Sun   | plemental Materials for EVT                             | 165 |

|              | -     | Proofs                                                  | 165 |

|              | B.2   | Benchmarks                                              | 168 |

| Bi           | bliog | graphy                                                  | 170 |

# Chapter 1

# Introduction

Deep learning with Deep Neural Networks (DNNs) has witnessed ground-breaking success across various domains, revolutionizing fields such as computer vision, natural language processing, speech recognition, healthcare, finance, and autonomous vehicles [1, 2, 3, 4, 5, 6].

The General-Purpose Graphics Processing Unit (GPGPU) is one of the major driving forces behind this progress [7]. It provides immense parallel processing power, enabling the training and deployment of neural networks with billions of parameters within reasonable time frames and resources. The programmability of GPGPU facilitates support for novel operators introduced in evolving neural network architectures, executed in parallel across multiple threads through functions known as "kernels" [8].

Entering the era of large language models and post-Moore's Law, the scaling of computational power provided by GPGPUs is struggling to keep pace with the rocketing requirements of novel deep neural networks [9]. Despite the computation shortage, existing GPGPUs suffer from low utilization of deep learning workloads. Jeon et al., 2019 [10] reported that the average hardware utilization of GPUs in use for training jobs is only around 52%. Additionally, Xiao et al., 2020 [11] found that in GPU clusters, only 10% of the GPUs achieve higher than 80% GPU utilization concerning the usage of computation units. A recent study on Meta's data centers in 2022 [12] also reveals a vast majority of deep learning experimentation utilizes GPGPUs at only 30-50%.

## 1.1 Characterize the utilization of GPGPU

This dissertation considers a broader sense of utilization, encompassing the following dimensions:

- Algorithm-level Utilization. The proportion of effective computation that contributes to the output. Low algorithm-level utilization may result from expending computation on outcomes close to zero or from overhead incurred by auxiliary modules in the neural network architecture.

- Device-level Utilization. The percentage of time during which at least one kernel is executing on the GPU. The primary cause of low device-level utilization is the overhead associated with kernel launching under single-GPGPU settings and communication delays under multi-GPGPU settings.

- Streaming Multiprocessor (SM)-level Utilization. The percentage of SM cores that have at least one active thread block. Insufficient parallelism leading to a shortage of thread blocks typically leads to low SM-level utilization.

- Execution Unit (EU)-level Utilization. The percentage of computation throughput and memory bandwidth utilized. Suboptimal kernel implementations that cause pipeline stalls usually lead to underutilization of both computation and memory bandwidth. Additionally, insufficient data reuse can cause memory bound that limits computation utilization.

## **1.2** Kernel-Centric Optimization

This dissertation aims to improve the above dimensions of utilization through kernelcentric optimization. Motivated by the fact that the utilization of programmable accelerators is majorly determined by the kernels running on them, the kernel-centric optimization constructs a mapping from the neural network to a set of kernels that better utilize the computational resources of the accelerators.

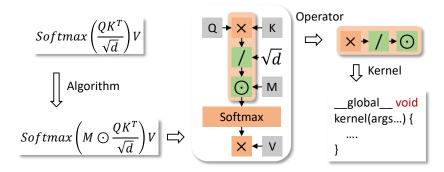

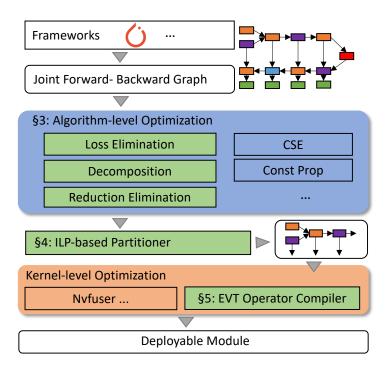

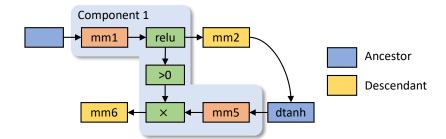

Figure 1.1: Illustration of the kernel-centric optimization.

As illustrated in Figure 1.1, this dissertation demonstrates that the mapping can be constructed by considering optimizations on three hierarchical levels: algorithm, operator, and kernel.

Algorithm-level Optimization. The algorithm-level optimizations aim to find the representation of the original neural networks that have higher algorithm-level utilization. This is usually achieved by leveraging mathematical equivalences or the resilience to sparsity and low precision, and selecting only hardware-friendly operators. For example, the  $M_{\odot}$  in Figure 1.1 represents a sparse mask applied to leverage the sparsity resilience of the softmax function.

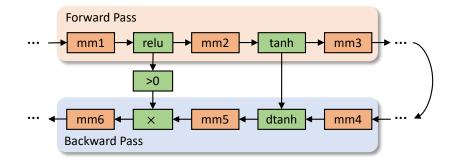

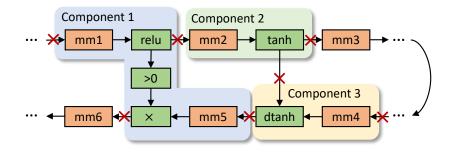

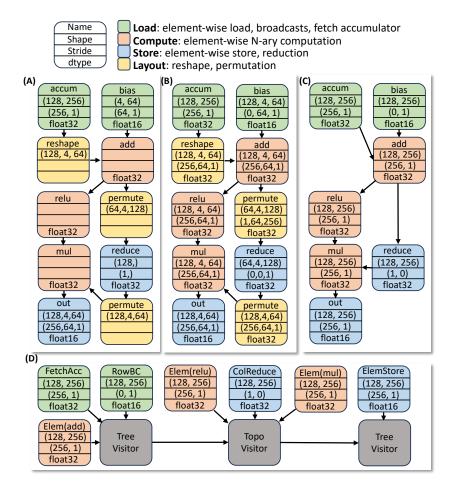

Besides algorithm-level utilization, it also opens up new optimization opportunities on lower levels of utilization. For instance, an algorithm composed of operators that are easy to parallelize could lead to higher SM-level utilization. **Operator-level Optimization**. Representing the algorithm as a data-flow graph, an operator is defined by a subgraph/partition satisfying two conditions: 1) all internal edges can be realized through on-chip faster memories (shared memory and registers) in GPGPUs; 2) all nodes in the subgraph can be implemented under the same parallelism.

Operator-level optimization involves identifying the partition of the data-flow graph that improves the device and EU-level utilization. For example, the  $\times$ , /, and  $\odot$  in Figure 1.1 are partitioned into the same operator. The kernel launching overhead regarding the latter two operators is eliminated which improves the device-level utilization. The intermediate data between these three operators are reused through the registers, which alleviates memory-bound constraints, thus enhancing computation utilization.

Kernel-level Optimization. Kernel-level optimization involves creating the optimal implementation of the kernel corresponding to each operator, as illustrated in Figure 1.1. Optimizations at the kernel level can effectively improve SM and EU-level utilization. The former can be achieved by parallelizing the operator across a sufficient number of thread blocks, while the latter involves leveraging data locality to cache data for reuse, thereby improving computation utilization. Additionally, optimizations that leverage accelerator-like features (e.g. Tensor Cores) or alleviate pipeline stalls can also be incorporated.

While optimizations on individual levels can effectively improve the utilization of GPGPUs on deep learning workloads, the thesis explores the codesign between optimizations at different levels both manually and with compiler techniques.

## **1.3** Manual Kernel-Centric Optimization

The kernel-centric optimization can be manually performed for specific neural network models and scenarios. The manual algorithm-level optimization typically involves simplifying the mathematical expression of the neural networks, identifying sparsity and low-precision resilience, and designing sparse patterns based on domain knowledge. Regarding operator-level optimization, the data-flow graph is manually examined to identify operators that can be partitioned together. The kernel-level optimization entails the manual design and optimization of efficient kernels in CUDA C++. This dissertation presents three case studies on manual kernel-centric optimizations as follows.

#### 1.3.1 Low-precision static Sparsity with Tensor Core

Low precision and sparsity are two major techniques for improving algorithm-level utilization when deploying neural networks on GPGPUs. However, using them simultaneously can result in low EU-level utilization, leading to inferior performance compared with dense operators under low precision alone. Chapter 3 presents VECSPARSE to address this issue on two most important sparse operators, sparse matrix-matrix multiplication (SpMM) and sampled dense-dense matrix multiplication (SDDMM), under half precision. It improves the low EU-level utilization through codesign between algorithm and kernel-level optimizations.

At the algorithm level, a novel GPGPU-friendly structured sparse pattern, column vector sparse encoding, is introduced. This pattern offers higher data reuse while preserving model accuracy better than existing approaches, providing opportunities to alleviate low computation utilization caused by the memory bound without compromising accuracy.

At the kernel level, dedicated kernel designs under the proposed sparsity pattern are introduced. These designs innovatively map the sparse computations to Volta Tensor Cores at sub-warp (Octet) granularity, addressing numerous pipeline stall reasons and significantly improving EU-level utilization.

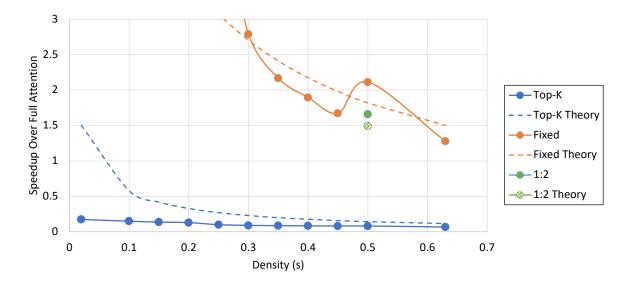

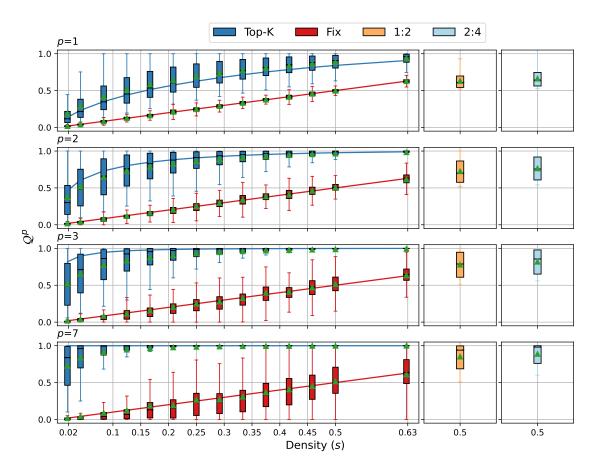

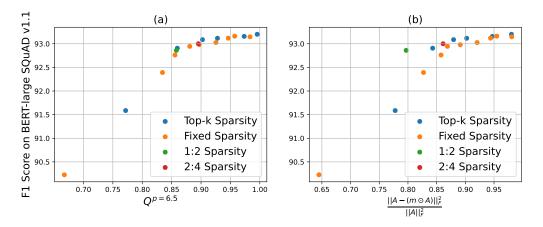

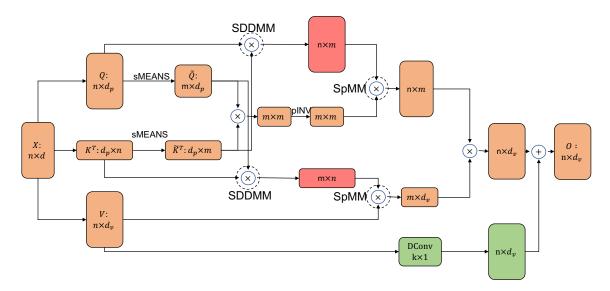

#### 1.3.2 Dynamic Sparsity with Sparse Tensor Core

While it has long been recognized that sparsity exists in the attention weight matrices of the attention mechanism and could potentially enhance its algorithm-level utilization, few approaches could effectively leverage this opportunity. This is because the dynamic (input-dependent) and fine-grained nature of this sparsity is unfriendly to GPGPUs and typically leads to low algorithm and EU-level utilization. Chapter 4 presents a novel sparse attention mechanism, DFSS, that effectively accelerates the attention mechanism with sparsity and achieves high utilization through co-design between algorithm and EU-level optimizations.

At the algorithm level, DFSS carefully selects the position to introduce sparsity to maximize the benefits while avoiding the introduction of auxiliary or GPU-unfriendly operators. This ensures high algorithm-level utilization. It also innovatively leverages the N:M fine-grained structured sparsity, originally designed for static weight pruning, at this dynamic scenario. This pattern is proven to be more GPGPU-friendly than patterns used by existing approaches, despite high pruning overhead caused by low EUlevel utilization.

The high pruning overhead of N:M sparsity is addressed by kernel-level optimization. A novel SDDMM kernel, the first of its kind, is introduced that prunes and encodes the output of a matrix multiplication into N:M sparsity without overhead. The encoded sparse matrix can be easily decoded by succeeding SpMM with sparse tensor core.

#### **1.3.3** Efficient Graph Neural Network Training

The graph neural network (GNN) is an emerging type of neural network model designed to represent data with graph topology, which has significant applications in social networks and recommendation systems. However, the inherent sparsity in GNNs' adjacency matrix results in low utilization when deploying them on GPGPUs. Chapter 5 presents FUSEGNN, a framework that combines optimizations at the algorithm, operator, and kernel levels to enhance the efficiency of GNN training on GPGPUs.

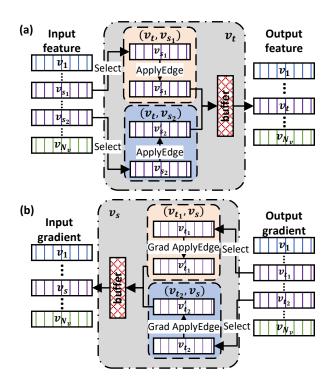

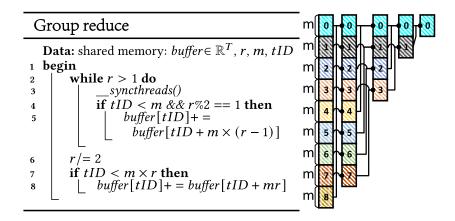

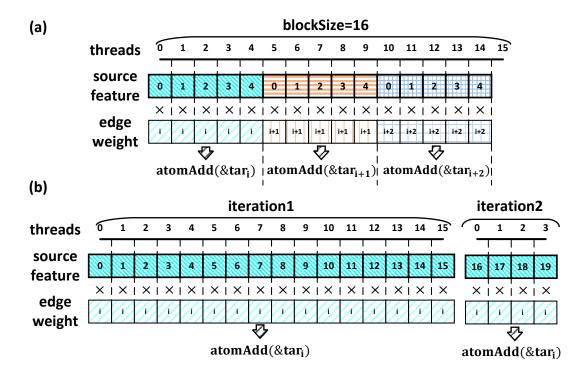

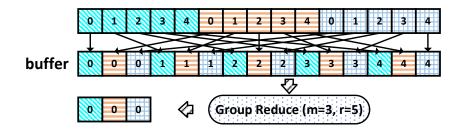

At the algorithm level, FUSEGNN introduces the novel dual aggregation strategy to select the more efficient abstraction of the aggregation stage based on the average degree. This improves the algorithm-level utilization at the low average degree by avoiding the graph format transformation overhead, while improving the EU-level utilization at the high average degree through on-chip reduction.

At the operator level, FUSEGNN identifies operators that can potentially be composed into a single kernel. This improves the device-level utilization as the kernel launching overhead is reduced. It also opens up opportunities to improve the EU-level utilization as intermediate results within each operator can be transferred through on-chip faster memory to relieve the memory bottleneck.

At the kernel level, an efficient fused kernel of each operator is developed that achieves higher EU-level utilization. Particularly, for the aggregation phase, fused kernels are developed for the two aggregation strategies presented in the algorithm-level optimization.

## **1.4** Compiler-based Kernel-Centric Optimization

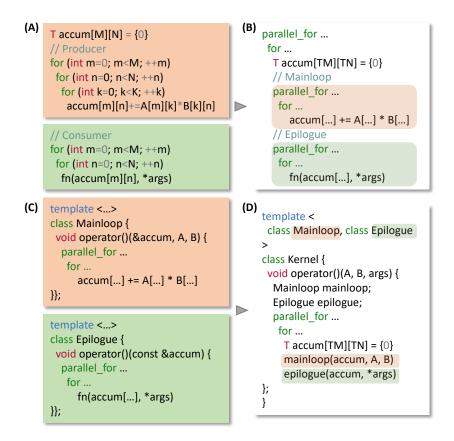

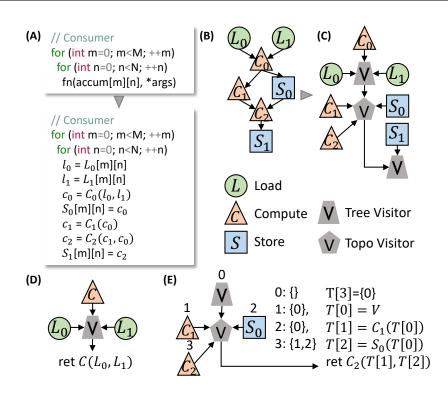

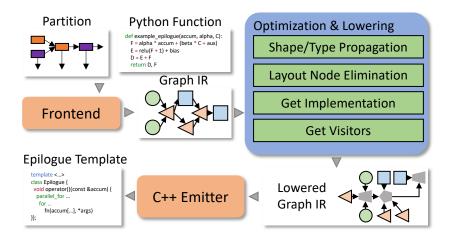

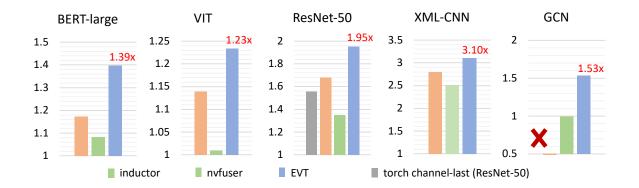

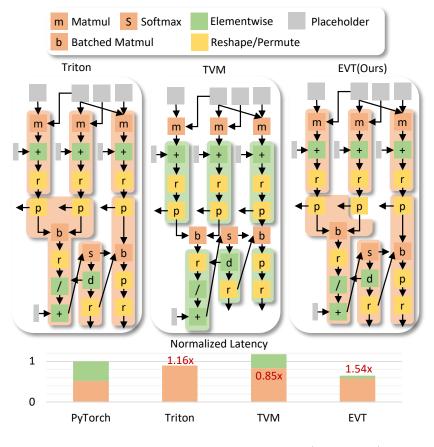

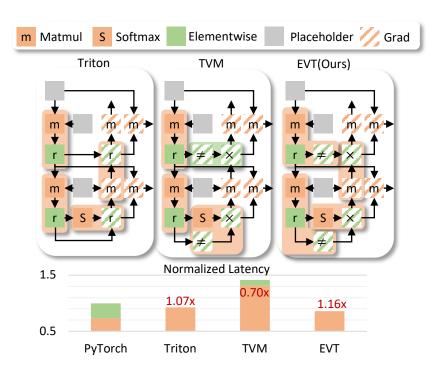

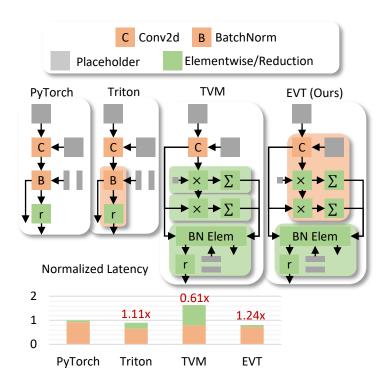

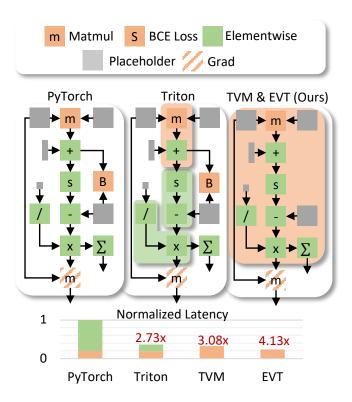

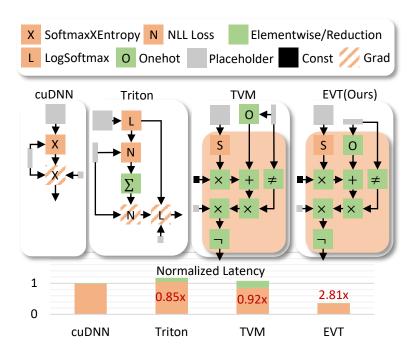

The previous case studies present how kernel-centric optimization improves the utilization of deep learning workload on GPGPUs. However, these techniques require high engineering effort and are model-specific. Chapter 6 demonstrates the application of kernel-centric optimization in the realm of compilers. It introduces the Epilogue Visitor Tree (EVT) compiler, which automates kernel-centric optimization across a wide range of NN models during training.

At the algorithm level, EVT automatically identifies more efficient mathematical

equivalents for neural network models through a series of transformations on the dataflow graph. This improves the algorithm-level utilization and reveals hidden optimization opportunities across other levels.

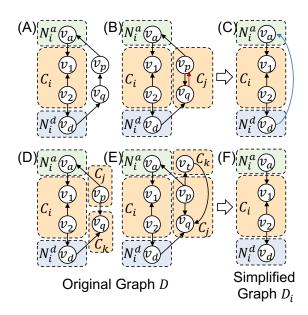

At the operator level, EVT integrates a novel integer linear programming (ILP)-based partitioner that efficiently solves the optimal and feasible partitions within complex joint forward-backward graphs.

At the kernel level, the EVT kernel-level compiler enables the construction of fused kernels with high-performance mainloops crafted by experts and the flexible compilergenerated epilogues. Utilizing handcrafted mainloops ensures state-of-the-art EU-level utilization by automatically incorporating dedicated optimizations, while integrating the compiler-generated epilogue enhances EU-level utilization by eliminating memory accesses caused by intermediate results within each partition.

## 1.5 Organization

This dissertation is organized as follows. Chapter 2 introduces the preliminaries and related work. Chapter 3, 4, 5 covers the manual kernel-centric optimizations, Chapter 6 covers the compiler-based kernel-centric optimizations. Chapter 7 concludes the thesis and discusses future research. The dissertation comprises work published elsewhere in conference papers:

- Chapter 3: Zhaodong Chen, Zheng Qu, Liu Liu, Yufei Ding, and Yuan Xie. "Efficient tensor core-based gpu kernels for structured sparsity under reduced precision." In Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis, pp. 1-14. 2021.

- Chapter 4: Zhaodong Chen, Zheng Qu, Yuying Quan, Liu Liu, Yufei Ding, and

Yuan Xie. "Dynamic n: M fine-grained structured sparse attention mechanism." In Proceedings of the 28th ACM SIGPLAN Annual Symposium on Principles and Practice of Parallel Programming, pp. 369-379. 2023.

- Chapter 5: Zhaodong Chen, Mingyu Yan, Maohua Zhu, Lei Deng, Guoqi Li, Shuangchen Li, and Yuan Xie. "fuseGNN: Accelerating graph convolutional neural network training on GPGPU." In Proceedings of the 39th International Conference on Computer-Aided Design, pp. 1-9. 2020.

- Chapter 6: Zhaodong Chen, Andrew Kerr, Richard Cai, Jack Kosaian, Haicheng Wu, Yufei Ding, and Yuan Xie. "EVT: Accelerating Deep Learning Training with Epilogue Visitor Tree.". To be appeared in Proceedings of the 27th ACM International Conference on Architectural Support for Programming Languages and Operating Systems, 2024.

# Chapter 2

# **Background and Related Work**

This chapter summarizes the background and related work of this dissertation. Firstly, Section 2.1 summarizes the background on transformers [13] and graph neural networks [14], two emerging neural network architectures accelerated in this dissertation. Section 2.2 introduces the background of general-purpose graphic processing units (GPGPUs). Then, Section 2.3, 2.4, and 2.5 discuss existing studies on optimizations at algorithm, operator, and kernel levels.

## 2.1 Neural Network Models

This section covers the background of transformers for Chapter 3, 4 and graph neural networks for Chapter 5.

#### 2.1.1 Transformers and Attention Mechanism

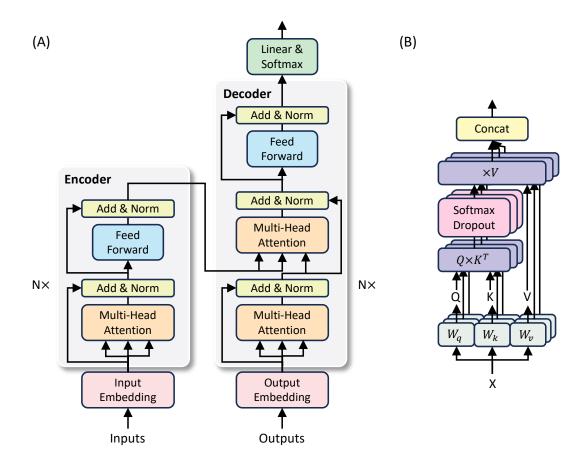

The transformers [13] have achieved state-of-the-art performance across various domains such as natural language processing and computer vision. The architecture of transformers, as illustrated in Figure 2.1 (A), consists of stacked encoder and decoder

Figure 2.1: Transformer model architecture. (A) The encoder-decoder architecture of transformers; (B) The multi-head attention mechanism.

blocks. There are also encoder-only transformers like BERT [2] and decoder-only models like GPT-2 [15] designed for different applications.

The key strength of transformers, differentiating them from traditional neural networks, lies in the multi-head attention mechanism (MHA) illustrated in Figure 2.1 (B). The MHA provides a scalable solution to capture long-range dependencies, which allows building large-scale neural networks for real-world problems. The scalability comes from its architecture which is easy to parallel on GPGPUs. Given an input sequence  $\boldsymbol{X} = (\boldsymbol{x}_1, ..., \boldsymbol{x}_n) \in \mathbb{R}^{n \times d}$ , each head of the attention mechanism can be defined as

$$\boldsymbol{O} = Softmax(\boldsymbol{Q}\boldsymbol{K}^T/\sqrt{d})\boldsymbol{V}, \qquad (2.1)$$

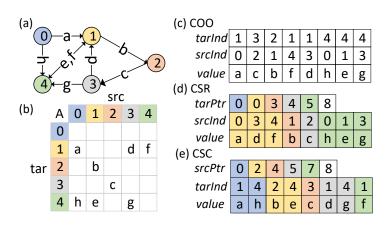

Figure 2.2: Graph Structured Data. (a) Graph; (b) Adjacent matrix; (c) COO format; (d) CSR format; (e) CSC format.

| Dataset       | #Vertex | Feature Len. | # Edge            | Avg. Degree |

|---------------|---------|--------------|-------------------|-------------|

| Cora (CR)     | 2,708   | 1,433        | $5,429 \times 2$  | 4.0         |

| Citeseer (CS) | 3,327   | 3,703        | $4,732 \times 2$  | 2.8         |

| Pubmed (PB)   | 19,717  | 500          | $44,338 \times 2$ | 4.5         |

| Reddit (RD)   | 232,965 | 602          | 114, 615, 892     | 492         |

Table 2.1: Dataset information

where  $\mathbf{Q} = \mathbf{X}\mathbf{W}_q$ ,  $\mathbf{K} = \mathbf{X}\mathbf{W}_k$ , and  $\mathbf{V} = \mathbf{X}\mathbf{W}_v$  are query, key, and value matrices.  $\mathbf{Q}\mathbf{K}^T$ forms a full-quadratic adjacency matrix, with edge weights being the dot-product similarity between all elements in the sequence. This adjacency matrix is standardized with  $1/\sqrt{d}$  to maintain the unit second moment and then normalized with softmax. Finally, the row feature vectors in  $\mathbf{V}$  are aggregated according to the normalized adjacency matrix by multiplying them together. Throughout this dissertation,  $\mathbf{Q}\mathbf{K}^T$  is referred to as the attention score matrix, and  $\mathbf{A} = Softmax(\mathbf{Q}\mathbf{K}^T/\sqrt{d})$  is named the attention weight matrix.

#### 2.1.2 Graph Neural Networks

The Graph Neural Network (GNN) is an emerging type of neural network specially tailored for graph-structured data. **Graph Structured Data**. A graph  $\mathcal{G} = (\mathcal{V}, \mathcal{E})$  consists of two components: vertices (nodes) and edges. For a graph with  $N_v$  vertices and  $N_e$  edges, each vertex  $v_i \in \mathcal{V}$ possesses a feature vector  $\boldsymbol{x}_i \in \mathbb{R}^{1 \times m}$  with these feature vectors organized into a matrix  $\boldsymbol{X} \in \mathbb{R}^{N_v \times m}$ . The edges  $(v_i, v_j) \in \mathcal{E}$  can be directed or undirected, and may also have a feature  $e_{ij}$ . Table 2.1 summarizes popular datasets used by GNNs.

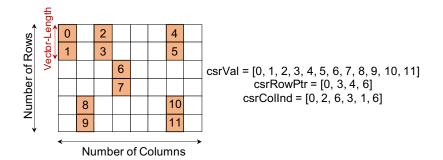

As illustrated in Figure 2.2 (a) & (b), edges can be represented as a sparse adjacency matrix  $\mathbf{A} \in \mathbb{R}^{N_v \times N_v}$ , where the row and column indices of each entry identify the target and source vertices. Three popular formats for the sparse matrix are shown in Figure 2.2(c), (d), and (e): Coordinate list (COO), Compressed Sparse Row (CSR), and Compressed Sparse Column (CSC).

**GNN Models**. The GNN models are designed under the neighborhood aggregation strategy [16]. With  $h_v^{(k-1)}$  represents the input feature vector of vertex v at layer k, the k-th layer of GNN is expressed as

$$\widetilde{\boldsymbol{h}_{i}^{(k-1)}} = MLP^{(k)}\left(\boldsymbol{h}_{i}^{(k-1)}\right), \boldsymbol{h}_{v}^{(k)} = AGG^{(k)}\left(\left\{\widetilde{\boldsymbol{h}_{u\in\mathcal{N}(v)}^{(k-1)}}, \widetilde{\boldsymbol{h}_{v}^{(k-1)}}\right\}\right), \quad (2.2)$$

where  $\mathcal{N}(v)$  is a set of nodes adjacent to vertex v,  $AGG^{(k)}$  is the aggregator in layer k. The aggregator updates each feature vector with the weighted sum of its neighbors.

$$\boldsymbol{h}_{v}^{(k)} = \sum_{u \in \mathcal{N}(v) \cup \{v\}} \widetilde{\boldsymbol{e}_{vu}} \otimes \widetilde{\boldsymbol{h}_{u}^{(k-1)}}, \qquad (2.3)$$

In Graph Convolutional Networks (GCN) [14], the weight  $\tilde{e}_{ij}$  is computed with  $\tilde{e}_{ij} = \frac{e_{ij}}{\sqrt{(d_i+1)(d_j+1)}}$ , where the  $e_{ij}$  is the initial scalar edge weight provided by the dataset. In Graph Attention Networks (GAT) [17], attention score of each neighbor is computed

based on the dot-product similarity between the feature vectors:

$$\widetilde{e_{ij}} = dropout \left( \frac{exp\left( lReLU\left( [\widetilde{\boldsymbol{h}_{i}^{(k-1)}} || \widetilde{\boldsymbol{h}_{j}^{(k-1)}} ] \boldsymbol{a}^{(k)} \right) \right)}{\sum_{q \in \mathcal{N}_{i}} exp\left( lReLU\left( [\widetilde{\boldsymbol{h}_{i}^{(k-1)}} || \widetilde{\boldsymbol{h}_{q}^{(k-1)}} ] \boldsymbol{a}^{(k)} \right) \right)} \right),$$

(2.4)

## 2.2 General Purpose Graphic Processing Units

Graphic Processing Units (GPUs) are hardware initially designed to accelerate computer graphics and image processing through their massive parallel processing power. In 2007, NVIDIA introduced CUDA, the widely adopted programming model for GPU computing, that allows GPUs to be programmed for general-purpose applications [18]. The programmability coupled with the parallel processing power of GPGPUs, quickly makes GPGPUs the most suitable and widely adopted accelerators for deep learning [7]. Throughout this dissertation, the terms GPU and GPGPU will be used interchangeably.

#### 2.2.1 GPU Architecture

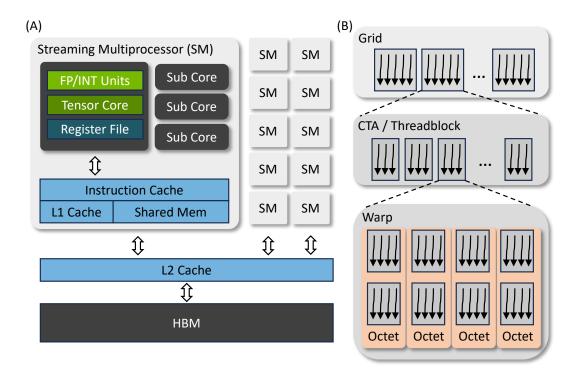

Figure 2.3 (A) illustrates the architecture of the GPGPUs. The GPGPU is composed of an array of streaming multiprocessors (SMs) that share the L2 cache and the off-chip High Bandwidth Memory (HBM). The HBM is usually referred to as global memory. Each SM has a private L1 data and instruction cache, and part of the L1 data cache can be configured as the shared memory managed by the programmer.

The SM is further partitioned into multiple sub-cores, each core contains a set of floating point and integer units, tensor cores, register file, and other components such as warp scheduler, dispatch unit, and L0 instruction cache.

For instance, the NVIDIA V100 GPU consists of 84 SMs sharing a 16GB HBM2 memory and 6144KB L2 cache. Each SM has a 128KB L1 data cache, 96 KB of which

Figure 2.3: (A) GPU architecture and memory hierarchy; (B) Thread hierarchy.

can be configured as the shared memory. The SM contains 4 sub-cores, each sub-core has 16 FP32 Cores, 8 FP64 Cores, 16 INT32 Cores, 2 mixed-precision Tensor Cores, one L0 instruction cache, one warp scheduler, one dispatch unit, and 64 KB register file.

#### 2.2.2 Programming Model

The programs of GPGPUs are organized into kernels: single instruction, multiple threads (SIMT) functions that are executed in parallel across thousands of threads. There are two key concepts in the GPGPU programming model: thread hierarchy and memory model. The former describes how the threads are dispatched to the SMs and sub-cores in GPGPU architecture, while the latter defines how the threads access different memory scopes including global memory, shared memory, and register files.

Thread Hierarchy. As illustrated in Figure 2.3 (B), the threads in a GPU kernel

are organized as a hierarchical structure. At the top level, the kernel is composed of grids of cooperative thread arrays (CTAs), also known as thread blocks. The total number of CTAs is referred to as *grid size*. When launching the kernel, the CTAs are dispatched to the SMs in a round-robin fashion, and a large enough grid size is required to achieve high utilization of the SMs. The number of CTAs an SM can accommodate depends on its resource allocation, including registers and shared memory. The number of threads in a CTA is referred to as *CTA size*. Within a CTA, 32 consecutive threads are organized into warps, and dispatched to sub-cores within each SM.

Memory Model. The global memory loads and stores issued by threads of a warp are coalesced into 2-, 64-, or 128-byte transactions. Non-coalesced memory access from a warp, such as strided access, results in transactions containing redundant data not requested by threads, leading to memory access inefficiency. To achieve the best bandwidth utilization, data accessed by threads in a warp should fall in aligned 128-byte memory segments. Additionally, CUDA provides vectorized memory access, enabling each thread to load or store up to 128-bit data per instruction. Leveraging this vectorized approach reduces total instructions, lowers latency, and enhances overall bandwidth utilization.

The shared memory offers roughly  $100 \times$  lower latency than uncached global memory. It is explicitly allocated per CTA and can be accessed by all threads in it. The shared memory is divided into 32 banks that can be accessed simultaneously. The banks are organized such that successive 32-bit data are assigned to successive banks. The bank conflict happens when the load and store from multiple threads of different data target the same bank, which leads to a performance penalty.

Each thread can use up to 255 32-bit registers. While the register is private to each thread, CUDA provides the warp shuffling instructions that allow threads in the same warp to access each other's data. Using more than 255 registers will lead to register spilling where the excess part will be stored in local memory, a part of global memory

Figure 2.4: Volta TCU Architecture. [19]

private to each thread. The register spilling has a significant negative impact on kernel performance and has to be avoided.

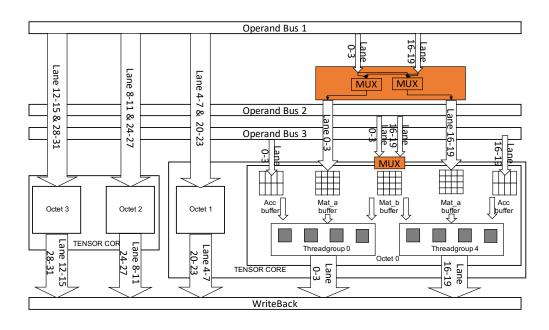

#### 2.2.3 Tensor Core

The Tensor Core Unit (TCU) is a specialized hardware unit designed to accelerate the matrix multiply-accumulate (MMA) operations. It significantly improves the performance of key operators in neural networks, such as matrix multiplication and convolution.

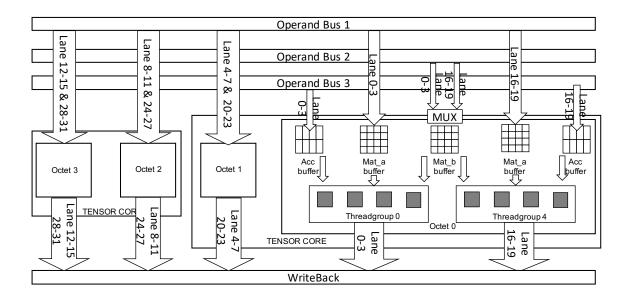

Volta Tensor Core. The Volta Tensor Core is the first generation tensor core introduced to GPGPUs by NVIDIA [20] that provides  $8 \times$  peak FLOPs than floating point units. Figure 2.4 shows the Volta TCU architecture. A warp uses two TCUs at the same time. Within each warp, consecutive 4 threads form a *thread group*, the thread group id of a thread is  $\lfloor \frac{threadIdx\%32}{4} \rfloor$ . Furthermore, thread group i  $\in \{0,1,2,3\}$  and thread group i+4 together form the *Octet* i. In this dissertation, thread group i and i+4 are referred to as low group and high group, respectively.

Each TCU is controlled by two octets. Each thread group in the octet has its own

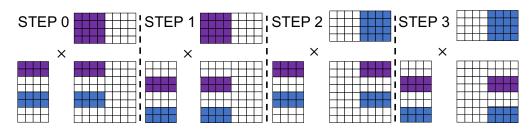

Figure 2.5: Visualization of the 4 steps in *mma.m8n8k4*. Purple blocks: low group; Blue blocks: high group.

buffer for storing the LHS matrix (Mat\_a buffer) and accumulation result (Acc buffer), and each thread can access a four-by-four inner product unit (gray blocks). The RHS matrix buffer (Mat\_b buffer) is shared by the two thread groups within each Octet. Its source is selected by a multiplexer.

CUDA provides two levels of APIs for Volta TCU. Firstly, warp-level matrix multiply and accumulate (WMMA) in C++ performs a dense matrix multiplication with a warp. For instance, wmma.m8n32k16 computes a  $8 \times 32 \times 16$  GEMM with a warp. Secondly, matrix multiply and accumulate (MMA) in PTX performs 4 dense matrix multiplications with a warp, one for each Octet. For instance, mma.m8n8k4 completes four  $8 \times 8 \times 4$ matrix multiplications. During the compilation, the mma.m8n8k4 is further decomposed into four *HMMA* instructions when lowing to SASS: *HMMA.884.F32.F32.STEP*{0,1,2,3} in Figure 2.5. In each step, every thread group loads its LHS tile to its Mat\_a buffer and the input accumulation values to its Acc\_buffer. The multiplexer for RHS tile selects the low group in step 0&1, and high group in step 2&3.

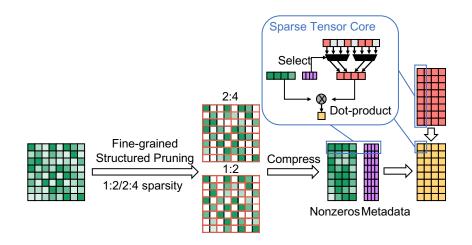

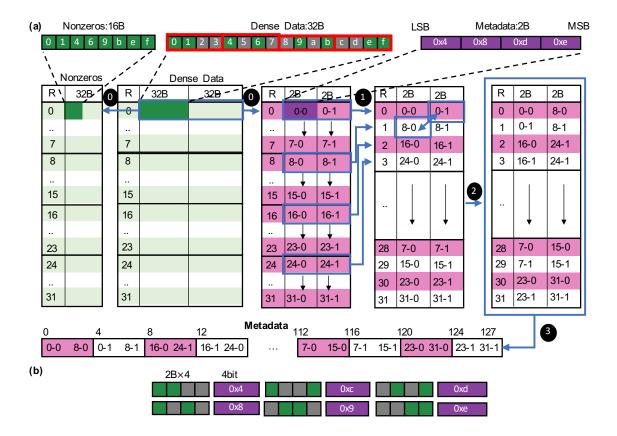

Ampere Sparse Tensor Core. The third-generation tensor core in Ampere GPG-PUs further supports the Sparse-Dense Matrix Multiplication (SpMM) under N:M finegrained structured sparsity. The N:M sparsity preserves N elements in every  $1 \times M$  vector from the original dense matrix and provides orders of magnitude more combinations than coarse-grained block sparsity while remaining GPU-friendly. NVIDIA introduces the 1:2 and 2:4 fine-grained structured pruning of weight matrices in neural networks [21]. As

Figure 2.6: A100 GPU 1:2 and 2:4 Fine-Grained Structured Sparsity Pruning. [21]

shown in Figure 2.6, the dense weight matrix is pruned and then compressed with APIs in cuSPARSELt library offline. During inference, the compressed weight matrix is multiplied with input activation with sparse-dense matrix multiplication (SpMM) accelerated by Ampere sparse tensor core. This brings up to  $1.9 \times$  speedup over the dense counterpart. Follow-up studies [22, 23, 24, 25, 26] propose algorithms to improve the accuracy, reduce training time, and accelerate the SpMM for N:M weight sparsity with new hardware designs.

## 2.3 Related Work on Algorithm-level Optimizations

This section summarizes existing studies on algorithm-level optimizations.

#### 2.3.1 Low Precision and Sparsity

Low precision and sparsity are two major methods to improve the algorithm-level utilization by reducing the computational and memory footprint of large neural networks [27].

The low precision reduces the number of bits that represent each operand from 32 to

Chapter 2

16 or even lower [28, 29]. Recent advances in GPGPU like Tensor Cores provide hardware acceleration for low-precision computation. Coupled with the lower memory requirement, the low precision significantly improves the efficiency of neural networks during training and inference.

The sparsity exploits the sparsity in the neural networks. For example, the dense weight matrices can be sparsified while maintaining comparable model quality [30, 27, 31, 32]. Existing studies [33, 34, 32, 35] have proposed different mechanisms to efficiently approximate and predict the zero values in the output feature map of CNNs, RNNs, and transformers to skip these computations during execution.

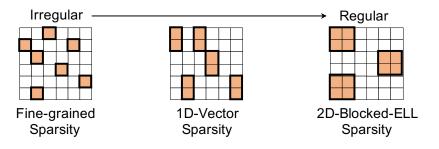

Figure 2.7: Different sparse structures.

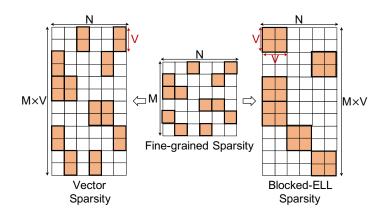

Efforts have been made to construct hardware-friendly sparsity by adding structured constraints to the pattern. As shown in Figure 2.7, apart from fine-grained sparsity, structures like 2D-block [36] can be enforced to the sparse matrix to improve the locality and the computation for efficiency. Chapter 3 of this dissertation also presents a 1D-Vector sparsity that well balances the accuracy and data reuse.

#### 2.3.2 Efficient Attention Mechanism

The high computation cost and memory footprint in the full attention mechanism come from the attention weight matrix A, whose size grows quadratically with the sequence length n. To address this issue, various efficient attention mechanisms have been proposed [37].

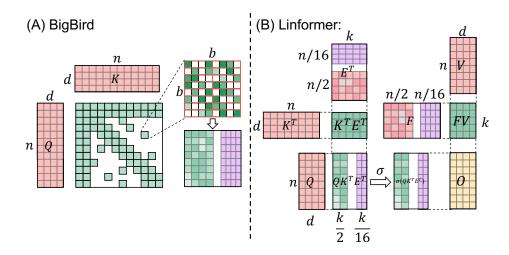

Fixed Sparse Patterns. Beltagy et al., 2020 [38] and Zaheer et al., 2020 [39] apply a set of fixed sparse attention patterns on A, like global attention and sliding window attention. These patterns are constructed from empirical observations and designed GPU-friendly to achieve speedup. The dynamic and fine-grained challenges are solved through costly retraining or finetuning to constrain the distribution of dominant entries.

**Dynamic Sparse Patterns**. Ham et al., 2021 [40] dynamically generate fine-grained sparse attention patterns on A with low-cost binary hashing. However, this technique requires specialized hardware to achieve speedup, so it is unavailable on GPGPU. Kitaev et al., 2020 [41], Tay et al., 2020 [37], and Roy et al., 2021 [42] apply various clustering methods and only compute the attention within each cluster. Although computing full attention in each cluster is more friendly to GPU compared with fine-grained sparsity, the clustering methods lead to low utilization as they contain several GPU-unfriendly operators like top-k and sorting that offset their benefits under moderate sequence length.

Low Rank / Kernel. Wang et al., 2020 [43] project A from  $n \times n$  to  $n \times k$  with linear projection. Choromanski et al., 2021 [44] introduce the FAVOR+ which approximates the softmax with the kernel method. This allows them to change the computation order and reduce the asymptotic complexity to linear. However, the low-rank projection and kernel construction also introduce considerable overhead. This makes these methods only effective under long sequence length. Besides, the low-rank projection drastically changes the attention mechanisms, tens of thousands of pre-training or finetuning steps are required to reach a comparable performance with the original full attention mechanism. So they require tremendous engineering effort to deploy.

#### 2.3.3 Automatic Algorithm-level Optimization

The algorithm-level optimization can be automated by regarding the neural networks as data-flow graphs and applying a series of transformations on the graph. Existing deep learning compilers have adopted various graph-level transformations to improve the efficiency of Deep Learning Systems. For instance, TVM [45] optimizes its graph-level IR, *relay*, with passes like constant-folding and data layout transformation.

## 2.4 Related Work on Operator-level Optimizations

Most existing studies employ simple heuristics when partitioning computation graphs. TVM[45], for instance, classifies the operators into four types: injective (element-wise), reduction, complex out-fusible (can fuse element-wise map to output), and opaque (cannot be fused). They define heuristic rules such as reduction can be fused with input injective operators and complex out-fusible nodes like GEMM can fuse element-wise operators to its output. However, as illustrated in Section 6.3, these heuristics would lead to infeasible partitions with cycles or suboptimal solutions.

There are also studies on the acyclic partitioning problem beyond the Deep Learning System community [46]. The ILP-based partitioner in Chapter 6 takes inspiration from Nosack et al., 2014 [47] which formulates the acyclic partitioning problem as ILP. The ILP-based formulation provides great extensibility to encode new constraints and heuristics through ILP constraints. However, the high complexity of the approach developed by Nosack et al., 2014 [47] makes it impractical to be directly used when solving large-scale neural networks with thousands of nodes, and their lower bound obtained from Kernighan's solution [48] is not valid when additional constraints are involved. In Section 6.3, a novel approach is developed that divides the large computation graph into smaller ones so that they can be solved in a reasonable amount of time.

## 2.5 Related Work on Kernel-level Optimizations

This section summarizes related kernel-level optimizations in existing studies.

#### 2.5.1 Sparse Kernels on GPGPU

Existing sparse kernels on GPGPU focus on two key operators: Sparse Matrix-Matrix Multiplication (SpMM) and Sampled Dense-Dense Matrix Multiplication (SDDMM). The former multiplies a sparse matrix with a dense one. The latter multiplies two dense matrices, while sparsity is located in the output matrix of the equation to help reduce the required computations.

Efficient sparse kernel implementations have been proposed for different sparse patterns. NVIDIA introduces the cuSPARSE library that targets 95% or higher sparsity and provides the *cusparseSpMM* and *cusparseSDDMM* APIs. The former one supports half, single, or higher precision, and the sparse matrix can be either fine-grained sparsity or Blocked-ELL format. Gale et al., 2020 [49] introduce a library called Sputnik that targets fine-grained sparsity and outperforms cuSPARSE under relatively low sparsity. Sputnik achieves speedup over the dense baseline under > 71% sparsity with single precision.

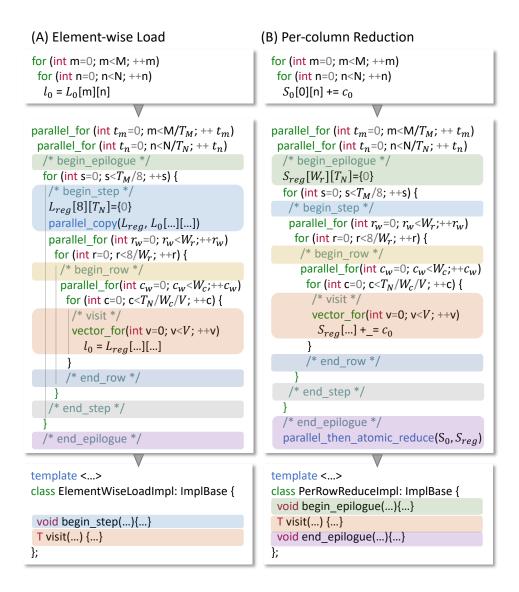

#### 2.5.2 Automatic Kernel Generation with Compiler

Kernel fusion is the key optimization applied in automated kernel-level optimization. During kernel fusion, multiple operators under the producer-consumer relationship are fused into a single one. The intermediate result can be directly cached in the register or shared memory to reduce memory access. The performance of the fused kernel is determined by the quality of the implementation of each operator, while the flexibility is determined by the ability of the operator compiler to align the loop structure of different operators. Template metaprogramming (TMP)-based compilers, such as AITemplate [50] and Bolt [51], use expert-developed template libraries [52, 53, 54] like CUTLASS to achieve optimal performance. However, these compilers lack abstractions for aligning operators with the intricate loop structure of the core operation, they can only support fusion patterns defined by the template library.

Loop-based compilers, such as TVM [45], Tiramisu [55], Nvfuser, and Tensor Comprehensions [56], represent operations as loops and apply schedules, such as loop fission, fusion, parallel, and vectorization, to map them to GPUs. However, the performance of the core operators generated by these compilers is inferior to the expert-designed kernels.

## Chapter 3

# Algorithm-Kernel Codesign: Static Sparsity with Tensor Core

This chapter presents the kernel-centric optimization with a specific focus on the algorithmkernel codesign. It improves the EU-level utilization of neural networks on GPGPUs when both sparsity and low precision are applied.

#### 3.1 Introduction

In recent years, areas such as computer vision and natural language processing have witnessed remarkable advancement driven by deep neural networks. However, the achievements come at the expense of the enormous memory footprint and computation cost. To address this issue, a common strategy involves the application of low precision and sparsity [27, 57, 58, 59]. Low precision represents data with fewer bits to save storage and memory bandwidth, and specialized computational units like Tensor Cores [20] have been introduced to improve the computation throughput under low precision. On the other hand, sparsity involves storing the tensors in the neural networks with compressed encoding, recording only non-zero elements and their positions. This not only reduces the memory footprint but also significantly decreases the FLOPS by replacing dense matrix multiplications with sparse matrix-matrix multiplication (SpMM) and sampled dense-dense matrix multiplication (SDDMM).

However, applying sparsity together with low precision leads to inferior performance due to the low EU-level utilization. In detail, SpMM and SDDMM under fine-grained sparsity, despite lower FLOPS, face limitations in EU-level utilization caused by the memory bottleneck. The sparse operators have much fewer data reuse opportunities compared with their dense counterparts. Although structured sparsity, such as 2D blocked-ELL, offers more data reuse opportunities, their large grain size introduces challenges in maintaining the model accuracy [60].

This chapter presents the VECSPARSE to address these challenges.

At the algorithm level, this chapter balances the data reuse and granularity size with a novel structured sparse pattern named column vector sparse encoding in Section 3.3. Inspired by the widely used compressed sparse row (CSR) encoding, the new pattern associates each index with a short nonzero column vector. With vector length  $V \times 1$ , it provides the same data reuse rate as the  $V \times V$  block sparsity in both SpMM and SDDMM operators, while maintaining the model accuracy with its smaller grain size.

Despite the data reuse opportunities offered by the new sparse pattern, existing floating-point unit (FPU) and tensor core unit (TCU)-based kernel implementations of SpMM and SDDMM face new challenges in achieving high EU-level utilization. The former's utilization is limited by pipeline stalls such as instruction cache miss, while the latter is constrained by shared memory bandwidth and waste of computations when mapping small Vs to TCUs.

At the kernel level, Section 3.2 presents five key guidelines for kernel-level optimization to improve the EU-level utilization in SDDMM and SpMM kernels, summarized from detailed profiling of existing implementations and the best practice of CUDA programming. A novel mapping between the warp tile and TCUs, namely TCU-based 1-D Octet Tiling (Section 3.4 and 3.5), is introduced that satisfies all the five guidelines simultaneously.

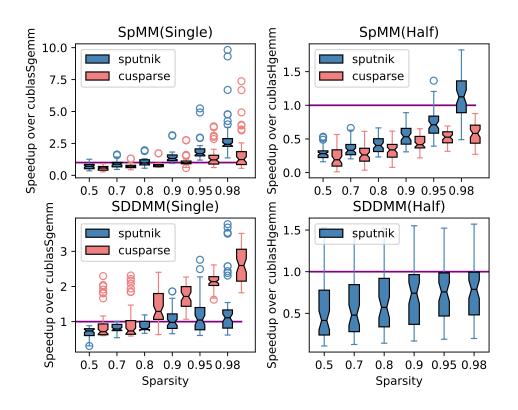

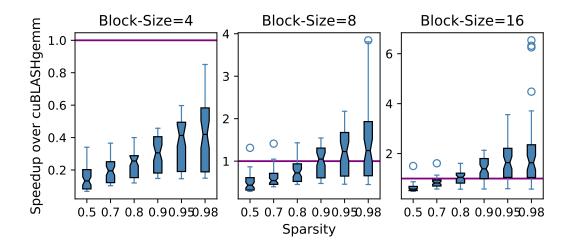

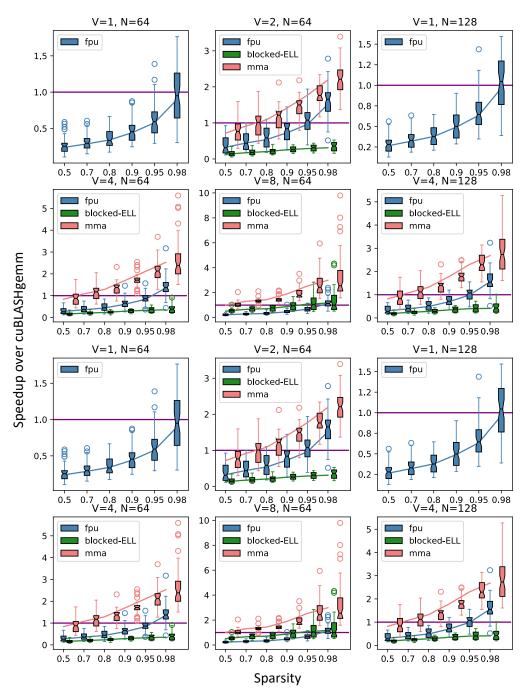

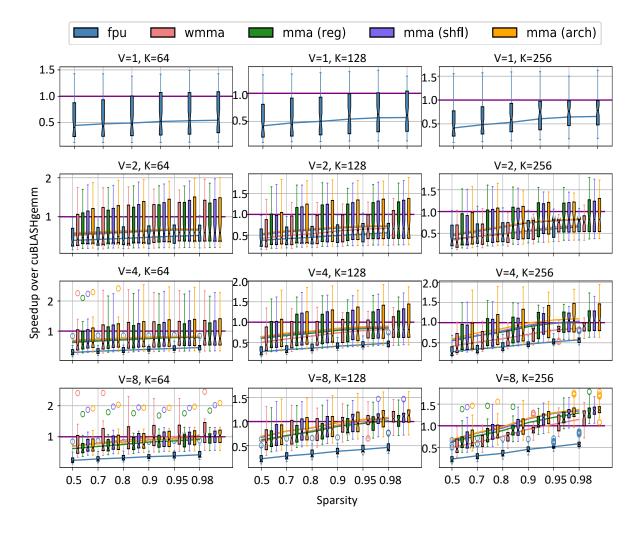

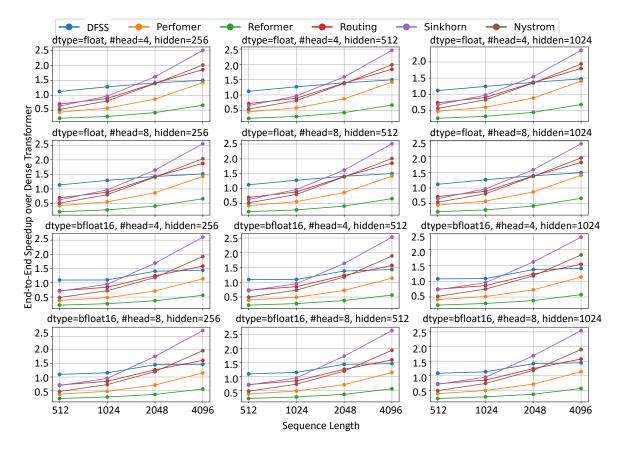

Section 3.6 extensively evaluates the proposed kernels on the sparse matrices from DLMC [61] dataset using different grain sizes, problem sizes, and sparsity ratios. In short, for SpMM, **1.71-7.19x** geometric mean speedup over the Blocked-ELL SpMM kernel from cuSPARSE and **1.34-4.51x** geometric mean speedup over an FPU-based kernel that directly extended from Sputnik [49] are achieved. For SDDMM, **1.27-3.03x** speedup over the FPU-based kernel extended from Sputnik [49] and **0.93-1.44x** speedup over the TCU-based kernel that uses the classic mapping between GEMM-like warp tile and TCU are achieved. Compared with the cuBLASHgemm, the proposed SpMM and SDDMM kernel achieve practical speedup under  $\geq 70\%$  and  $\geq 90\%$  sparsity with the tiny  $4 \times 1$  grain size. Further evaluation of VECSPARSE on sparse transformer inference task demonstrates 1.41x end-to-end speedup and 13.37x peak memory reduction.

#### 3.2 Motivation

This section discusses the limitations of existing sparsity patterns and corresponding SpMM and SDDMM kernels from the algorithm and kernel perspectives.

#### 3.2.1 Algorithm: Limitation of Existing Sparse Patterns

As summarized in Section 2.3.1, existing sparse patterns can be classified into finegrained sparsity and structured sparsity.

**Fine-grained Sparsity**. Figure 3.1 illustrates the speedup over the dense baseline (cuBLAS) achieved by the Sputnik [49] and cuSPARSE [62], two state-of-the-art libraries,

Figure 3.1: Speedup over cuBLAS with fine-grained sparsity.

under single and half-precision. Although considerable speedup is achieved under single precision <sup>1</sup>, under half-precision, the performance of SpMM and SDDMM kernels is inferior to their dense counterpart, reflecting low EU-level utilization. The performance degradation has two major causes: memory bottleneck and ineligibility of using tensor cores.

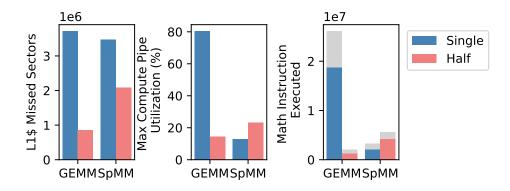

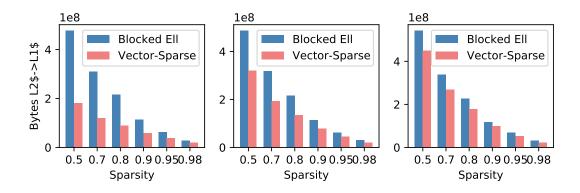

To reduce the memory bottleneck, dense GEMM leverages the data locality and caches tiles of multiplicand and multiplier in shared memory, while SpMM and SDDMM depend on the sparsity to skip the memory access related to zeros. As shown in Figure 3.2, under half-precision, the L1\$ Missed Sectors of GEMM is decreased by a factor of more than three times. This is from not only the halving of data size but also the improved locality as shared memory can cache more elements. In contrast, to compete

<sup>&</sup>lt;sup>1</sup>The SDDMM in cuSPARSE is faster than Sputnik [49] under cuSPARSE v11.2.2.

Figure 3.2: Profiling Metrics of GEMM and SpMM under different precision with problem size  $2048 \times 1024 \times 256$  with 90% sparsity.

with GEMM, SpMM and SDDMM can only increase their sparsity at the cost of model accuracy, as they lack data reuse opportunities.

The dense GEMM also benefits from the accelerated computation with tensor cores. Figure 3.2 shows that under half-precision, "Max Compute Pipe Utilization" and "Math Instruction Executed" of GEMM are significantly reduced, which indicates the relief of the computation bottleneck. The computations are offloaded to tensor cores that offer higher computation throughput with fewer instructions. Oppositely, the SpMM and SDDMM cannot be easily mapped to tensor cores, as the latter is only designed for dense matrix multiply accumulation.

**Structured Sparsity**. Existing structured sparse patterns like Blocked-ELL are usually composed of nonzero square blocks. With this pattern, the SpMM and SDDMM can be converted into a batch of small dense matrix multiplications. Although the blocked sparsity greatly improves the data locality and enables leveraging the tensor cores, its granularity increases quadratically with the data reuse ratio. Existing studies [60] have shown that large block size leads to accuracy degradation under the same sparsity. As a consequence, the design space is significantly limited due to the wrestling between kernel performance and model accuracy.

To conclude, a novel sparse pattern is required to be designed on the algorithm side

Figure 3.3: Speedup over cuBLAS with Blocked-ELL SpMM.

that better balances the data reuse opportunities and the granularity size, while enabling the use of tensor cores. This chapter introduces the column-vector sparse encoding in Section 3.3, which has finer granularity under the same data reuse rate as block sparsity.

#### 3.2.2Kernel: Limitation of Existing Kernel Implementation

Another limitation exists in the previous kernel implementation of structured sparsity. While the small structure sizes are desired to maintain model accuracy [60], Figure 3.3 illustrates that the Blocked-ELL-based SpMM exhibits suboptimal performance. It only surpasses the dense matrix multiplication with the block size greater than 8.

| Table 3.1: Stall Reasons in Blocked-ELL based SpMM kernel |                |       |                  |  |  |  |  |

|-----------------------------------------------------------|----------------|-------|------------------|--|--|--|--|

| Block Size                                                | No Instruction | Wait  | Short Scoreboard |  |  |  |  |

| 4                                                         | 42.6%          | 21.0% | 11.9%            |  |  |  |  |

Detailed profiling of Blocked-ELL SpMM kernel reveals that under small block size, the kernel suffers from low EU-level utilization of both memory bandwidth and computation units, which is primarily caused by pipeline stalls. Table 3.1 listed the top-3 stall reasons.

"No Instruction" is caused by the instruction cache miss. The SASS code of SpMM contains over 4600 lines of code, yet the 12 KB L0 instruction cache of each sub-core can only hold 768 instructions. This leads to L0 instruction cache capacity miss.

The "Wait" happens when a warp is stalled waiting on a fixed latency execution dependency. The instruction statistics show the IMAD (Integer Multiply & Add) and IADD3 (3-input Integer Add) account for 27.4% of total executed instructions. These integer instructions compute addresses and predicates, contributing to the "Wait" stall.

"Short Scoreboard" occurs when a warp is stalled, waiting for shared memory data loading. With block size 4, the  $\frac{\#shared\ memory\ load\ requests}{\#global\ load\ requests}$  ratio of SpMM is 0.87, compared to 4.17 of dense matrix multiplication. This implies the data stored in shared memory is not reused frequently, whereas the shared memory causes other overhead such as more complex data path and synchronization overhead. Moreover, configuring part of the L1 cache into shared memory reduces implicit data reuse through L1 cache.

In summary, at the kernel level, with the analysis above and the best practices guide for CUDA kernel design, five key guidelines can be proposed for the kernel-level optimization. Guideline I and II improve the overall SM and EU-level utilization, III focuses on the computation utilization, while IV and V influence the memory utilization.

- I. Minimize program size to prevent overflowing the instruction cache.

- II. Increase the grid size to hide the latency through thread-level parallelism (TLP).

- **III**. Reduce fixed latency operations through looping unrolling, computing offset and constants at compile time, and merging floating point operations to *HMMA* with TCU.

- **IV**. Directly load data with limited reuse opportunities to the register file, bypassing shared memory.

Figure 3.4: Generalized Block Sparse representation.

• V. Improve bandwidth utilization with 128B coalesced transactions and long vectorized memory access (*LDG.128*).

A novel TCU-based 1-D Octet Tiling in Section 3.4 and 3.5 is proposed to construct SpMM and SDDMM kernels that satisfy all the five guidelines simultaneously.

#### 3.3 Algorithm-level Optimization: VecSparse

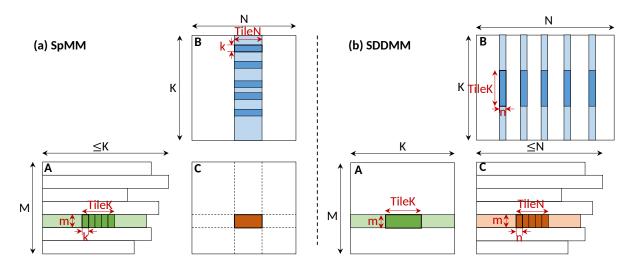

The key observation behind the algorithm-level optimization is that, for both SpMM and SDDMM, a block sparse matrix has the same data reuse regardless of the number of columns within each block. Building upon this observation, a novel sparsity pattern, namely column vector sparse encoding, is proposed that well balances the sparsity granularity and computation efficiency.

#### 3.3.1 Data Reuse Analysis

Figure 3.4 shows the SpMM and SDDMM under block sparsity. The nonzero blocks are aligned in the vertical dimension. The problem size is  $M \times N \times K$ , TileK and TileN

are the tiling sizes, which are constrained by the shared memory or register file capacity.

Regarding SpMM, each block represents an  $m \times k$  matrix, where m and k are userdefined sizes for block sparsity. Following the workflow in Sputnik [49], each tile computes the partial sums in matrix C with TileK/k consecutive nonzero blocks from A and a vector with width TilesN from the corresponding rows in B.

For SDDMM, each block within matrix C is an  $m \times n$  matrix, with user-defined grain size  $m \times n$ . In this scenario, each tile computes the partial sum of TileN/n consecutive nonzero blocks in matrix C by extracting TileK columns from the corresponding rows in A and TileK rows from the corresponding columns in matrix B.

With the above settings, it is obvious that in both SpMM and SDDMM, each operand from the LHS matrix is reused for TileN times, while each RHS operand is reused for mtimes. Therefore, the number of data reuse is determined by m and TileN, independent of the number of columns (k in SpMM and n in SDDMM) in each block.

#### 3.3.2 Column Vector Sparse Encoding

As the data reuse is independent of the column number, the number of columns of each block can be reduced to 1 to minimize the sparsity granularity. This results in the column vector sparse encoding shown in Figure 3.5. The new pattern is equivalent to

Figure 3.5: Column Vector Sparse Encoding.

replacing each nonzero scalar in the CSR sparse matrix with a nonzero column vector. The elements within each vector are consecutive in memory, and the vectors in the same row are sequentially arranged. With this encoding and small vector lengths such as  $\{2, 4, 8\}$ , the vectors can be loaded and stored with the CUDA vector types directly with coalesced memory access.

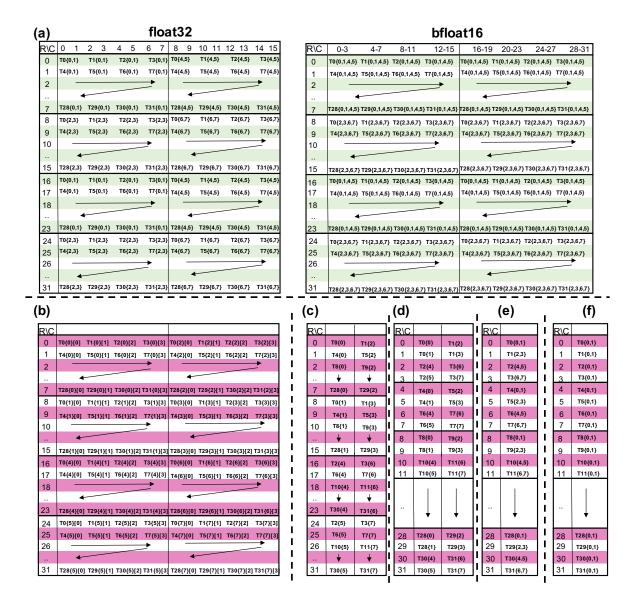

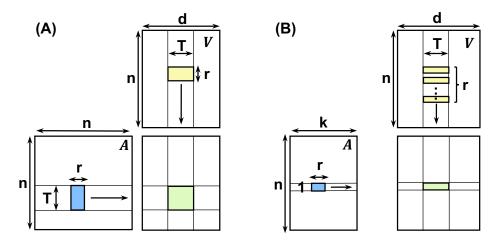

#### 3.4 Kernel-level Optimization: SpMM

This section details the kernel-level optimization on SpMM under the proposed sparse pattern. It is organized as follows. Firstly, the weaknesses of two classic baseline designs are discussed under the five guidelines, including an FPU-based design following Sputnik [49], and a TCU-based design following the classic GEMM-like tiling approach. Then, a more efficient design, TCU-based 1-D Octet Tiling, is presented that satisfies all the five guidelines simultaneously.

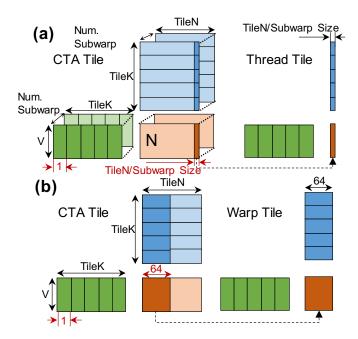

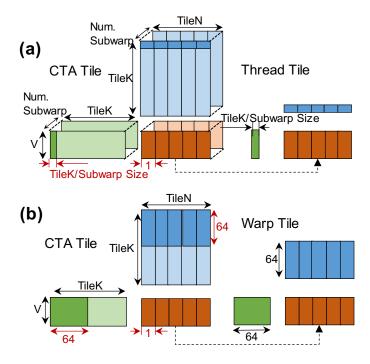

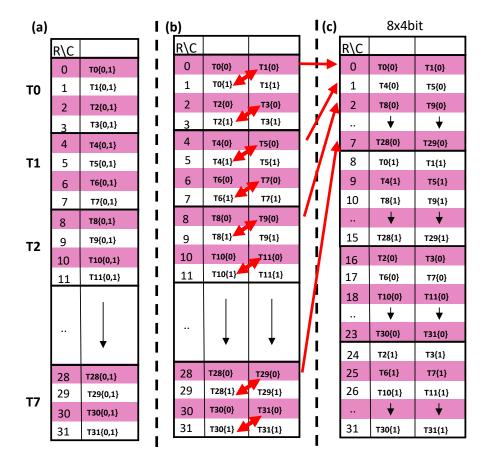

#### 3.4.1 Baseline I: FPU-based 1-D Subwarp Tiling

Gale et al., 2020 [49] propose the FPU-based 1-D subwarp tiling for the SpMM kernel under fine-grained sparsity that maximizes the memory access efficiency. It is called "1-D subwarp tiling" because under the fine-grained setup (V=1), as illustrated in Figure 3.6 (a), the LHS operand is a  $1 \times TileK$  1-D vector handled by a subwarp of threads. A CTA tile contains multiple independent 1-D tiles that are assigned to subwarps (Subwarp Size  $\leq$  32). Each 1-D tile is further decomposed to Subwarp Size independent ( $V \times TileK$ )·( $\frac{TileK \times TileN}{Subwarp Size}$ ) thread tiles. The threads in the same subwarp first load the LHS fragment into the shared memory corporately. Then, each thread loads the RHS fragment corresponding to its tile and computes the MMA.

This tiling design opts for maximizing memory access efficiency. First, it satisfies the

Figure 3.6: Decomposition of SpMM with 1-D tiling. (a) The FPU tiling extended from Sputnik[49]; (b) TCU-based tiling.

aforementioned guideline IV as the RHS operands are directly loaded to the register file. For guideline V, by choosing TileN = 64 and  $Subwarp \ Size = 8$ , each subwarp can load a row of consecutive 64 half operands from the RHS fragment with the vector memory operation LDG.128 in a single 128B transaction.

Despite the benefits, this design compromises guidelines I, II, and III. For guideline I, computing each subwarp tile requires fully unrolling the loops along V, TileK, and TileN. This results in a significant amount of instructions. The unrolling is essential as it enables the compiler to determine the index to RHS operands at compile time, preventing the usage of local memory for indexing.

This design also leads to conflict between guideline II and V. While guideline V expects  $\frac{TileN}{Subwarp \ Size} = 8$ , this ratio only produces grid size up to  $\frac{M \times N}{V \times \# Subwarp \times TileN} = \frac{M \times N}{256V}$ . Yet, by compromising guideline V and having  $\frac{TileN}{Subwarp \ Size} = 2$ , the grid size can be improved to  $\frac{M \times N}{64V}$  that is four times larger.

Figure 3.7: Classic mapping of the warp tile to TCU.

For computation efficiency, the design violates guideline III, as each thread computes its tile by a sequence of *HMUL* (FP16 Multiply) and *FADD* (FP32 Add) instructions.

#### 3.4.2 Baseline II: TCU-based 1-D Warp Tiling

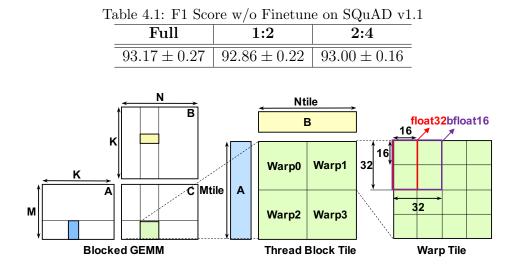

Guidelines I and III can be satisfied by mapping the computation to TCUs. The TCUs merge multiple *HMUL* and *FADD* into a single *HMMA* instruction, reducing the program size and fixed-latency instructions. Figure 3.6 (b) illustrates the TCU-based 1-D Warp Tiling that maps SpMM to TCUs. As TCUs are controlled by warps, the 1-D CTA tile is decomposed into warp-level tiles with size  $V \times 64 \times TileK$ . The 64 is chosen as it is the smallest number that perfectly fills the 128B transaction.

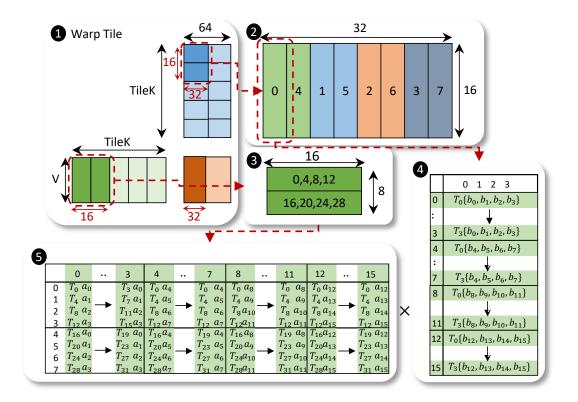

Figure 3.7 illustrates how the warp tile is further decomposed to each thread in the

traditional way. In  $\bigcirc$ , with  $V \in \{2, 4, 8\}$ , the warp tile is mapped to *wmma.m8n32k16* instruction to avoid the waste of computation. (2) and (3) show the mapping of the multiplicand and multiplier to the thread groups. In (2), each thread group is responsible for a 16 × 4 block. An example of thread group 0 is illustrated in (4), where  $T_i$  represents thread *i* and  $b_j$  indicates the register *j* of the thread. In (3), each block represents a 4 × 16 block and the number on it indicates the thread groups that hold a copy, the detailed layout is shown in (5).

Despite satisfying guidelines I and III, this design leads to conflict between guideline IV and V. When guideline IV is satisfied, the RHS fragment in 2 is loaded directly from global memory to registers, as shown in 4, each thread has 4 registers in each row, which prevents the use of *LDG.128* to achieve the optimal memory efficiency. On the other hand, to satisfy guideline V, the global memory access has to be coalesced through the shared memory, which violates guideline IV.

Besides, TileK has to be the multiple of 16, which introduces additional overhead during residue handling when the number of nonzero in the current row is not divisible by TileK. At last, when V is smaller than 8, each computation step with wmma.m8n32k16actually computes a  $V \times 32 \times 16$  tile, which indicates a portion of wasted computation.

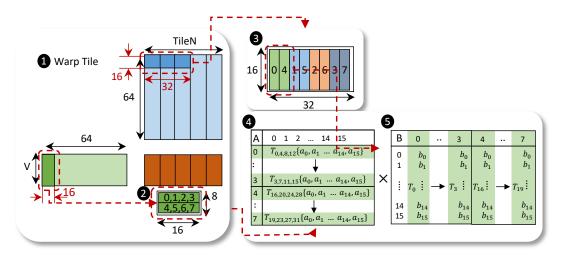

#### 3.4.3 Solution: TCU-based 1-D Octet Tiling

Unlike the performance of the previous two designs limited by the wrestling between kernel/compute and memory access efficiency, this section presents a new design, TCUbased 1-D Octet Tiling, that satisfies all five guidelines simultaneously. The high-level idea is to map the SpMM to tensor cores to achieve good kernel and compute efficiency (guideline I, II, and III). The memory access efficiency (guideline IV and V) is achieved by redesigning the mapping between the warp tile and the TCU on the fine-grained Octet

Figure 3.8: TCU-based 1-D Octet Tiling for SpMM.

level.

In detail, the CTA and warp tiling in the TCU-based 1-D Warp tiling in Figure 3.6 (b) is directly used, while the new mapping of warp tile to threads is redesigned as shown in Figure 3.8. There are two major differences from the classic mapping in Figure 3.7.

Firstly, the LHS and RHS fragments are swapped to put V in the horizontal direction. This is motivated by four steps in Figure 2.5 where step 0&1 generates the left four columns in the outputs while step 2&3 produces the rest. When  $V \leq 4$ , step 2&3 can be skipped to reduce the waste of computation.

Secondly, the warp tile is further partitioned into octets to guarantee both efficient computation and memory access. Specifically, the warp tile is decomposed to TileK/4

steps to be processed in serial by each warp, and each step processes a  $64 \times V \times 4$  subtile (after the swapping). With guideline IV, **4** is directly loaded to the register file as it has few reuse opportunities. For guideline V, as each column of consecutive 64 half operands in **4** are mapped to 8 different threads and each thread holds consecutive 8 half operands, **4** can be loaded with a single LDG.128 instruction and coalesced into four 128B coalesced global memory transactions. For **2**, as the LHS fragment in the warp tile is reused many times, it is directly loaded into the shared memory at the beginning of the tile, so it does not influence the memory access efficiency. Besides, the new mapping only requires TileK being the multiple of 4, which is more friendly to residual handling.

#### **3.4.4** Implementation Details

For an SpMM with size  $M \times N \times K$ , TileN = 64 and CTA size = 32 are set to have as many CTAs as possible while maintaining the best memory access pattern. Therefore,  $\lceil M/V \rceil \times \lceil N/64 \rceil$  CTAs are launched, each processes an  $V \times 64$  output tile.

To generate the output tile, each CTA traverses all the nonzero vectors in its row with stride TileK and accumulates the partial sums in the register file. For each stride, all the threads first work jointly to load the LHS fragment in Figure 3.8 0 to shared memory. Then, each thread group loads its share in the 64 × 4 RHS fragment in Figure 3.8 0. Next, an mma.m8n8k4 is launched to compute a  $64 \times V \times 4$  matrix multiplication  $(\textcircled{0} \times \textcircled{3} = \textcircled{0})$ . This is repeated for TileK/4 times until the warp tile is done.

To improve the instruction level parallelism (ILP), a  $\_-threadfence\_block()$  is inserted between the TileK/4 load instructions and the TileK/4 mma.m8n8k4 instructions. This prevents the *nvcc* compiler from reusing the registers that store the source operand of each mma.m8n8k4, which increases the dependencies between mma instructions and hurt ILP.

Figure 3.9: Decomposition of SDDMM with 1-D tiling. (a) The FPU tiling extended from Sputnik [49]; (b) TCU-based tiling.

When the last few nonzero vectors cannot fill the TileK width, the load and computation of each  $64 \times V \times 4$  tile will be interleaved until all the nonzero vectors are processed. This helps reduce the residual handling overhead. After all the nonzero vectors are processed, the data is reorganized with the warp shuffle primitives and then written to global memory with vectorized store.

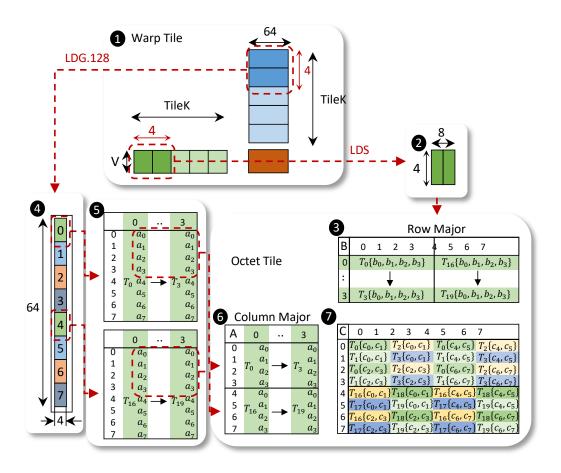

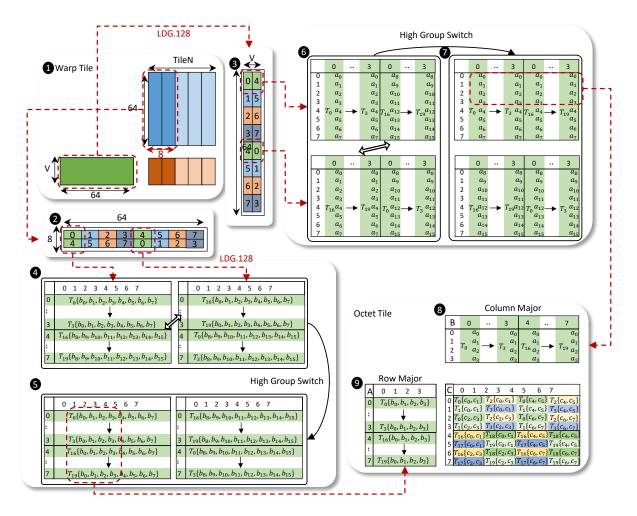

#### 3.5 Kernel-level Optimization: SDDMM

Similar to Section 3.4, this section first describes two baseline SDDMM designs. One is extended from Sputnik [49] that opts for memory access efficiency, and the other is based on the classic mapping between GEMM and TCU for high compute and kernel efficiency. Then, a novel design is present that achieves high EU-level utilization by satisfying all five guidelines.

#### 3.5.1 Baseline I: FPU-based 1-D Subwarp Tiling

The FPU-based 1-D subwarp tiling is illustrated in Figure 3.9 (a). Similarly, each CTA tile contains multiple independent 1-D tiles assigned to subwarps. Each 1-D tile is decomposed to *Subwarp Size* independent thread tiles with size  $V \times TileN \times \frac{TileK}{Subwarp Size}$ . Each thread loads its LHS and RHS tile into registers and computes partial sums. At last, partial sums stored by different threads in the same subwarp are reduced with warp shuffle.

This tiling design also has high memory access efficiency. Specifically, with TileK = 64 and Subwarp Size = 8, the rows in LHS fragment and columns in RHS fragment of the 1-D tile can be loaded with a single LDG.128 instruction in the 128B coalesced pattern. Therefore, it satisfies guideline IV and V. However, kernel and compute efficiency are suboptimal due to the same reasons as in the FPU-based SpMM. Moreover, each thread holds a  $V \times TileN$  array in the register file to store the partial sums. For instance, when V = 8 and TileN = 32, the partial sum consumes 256 registers of each thread, which exceeds the register file capacity and causes register spilling. Even without the register spilling, the large amount of registers reduces the occupancy.

Figure 3.10: Classic mapping of the warp tile to TCU.

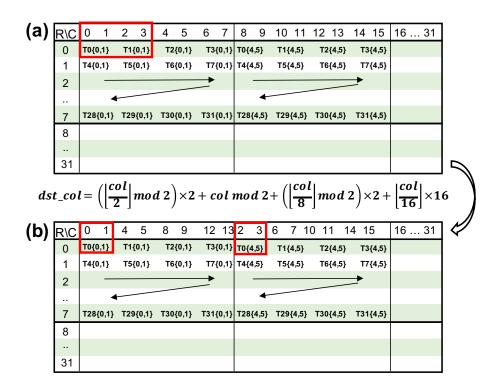

#### 3.5.2 Baseline II: TCU-based 1-D Warp Tiling

The TCU-based 1-D Warp Tiling for SDDMM is illustrated in Figure 3.9 (b). Each CTA tile has only one 1-D tile, which is further decomposed to warp tiles with size  $V \times TileN \times 64$ . Similarly, 64 is chosen because it is the smallest number that perfectly fills the 128B transaction. As shown in Figure 3.10  $\bigcirc$ , the warp tile is further processed with  $\frac{TileK \times 64}{32 \times 16}$  steps in serial, and each step is computed with a wmma.m8n32k16.

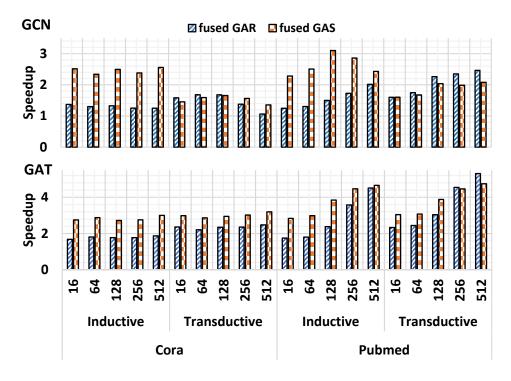

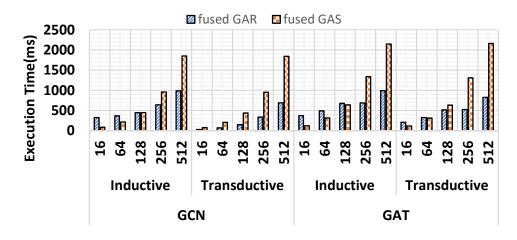

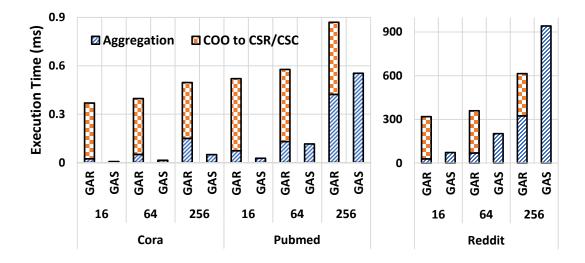

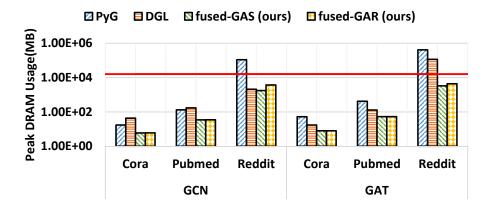

On the positive side, Similar to the SpMM kernel, it has high kernel and compution efficiency (guideline I, II, and III) for the same reasons. Besides, it uses fewer registers to store the partial sum. E.g., with TileK = 64, while the FPU-based implementation has Subwarp Size copies of the partial sums, this design only has one copy.